JP4014831B2 - El表示装置及びその駆動方法 - Google Patents

El表示装置及びその駆動方法 Download PDFInfo

- Publication number

- JP4014831B2 JP4014831B2 JP2001257163A JP2001257163A JP4014831B2 JP 4014831 B2 JP4014831 B2 JP 4014831B2 JP 2001257163 A JP2001257163 A JP 2001257163A JP 2001257163 A JP2001257163 A JP 2001257163A JP 4014831 B2 JP4014831 B2 JP 4014831B2

- Authority

- JP

- Japan

- Prior art keywords

- digital video

- display

- pixels

- tft

- gate signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 133

- 239000011159 matrix material Substances 0.000 claims description 10

- 239000010408 film Substances 0.000 description 150

- 239000010410 layer Substances 0.000 description 93

- 238000005530 etching Methods 0.000 description 49

- 239000012535 impurity Substances 0.000 description 43

- 239000000758 substrate Substances 0.000 description 31

- 239000000463 material Substances 0.000 description 27

- 230000008569 process Effects 0.000 description 22

- 239000004065 semiconductor Substances 0.000 description 22

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 21

- 229910052710 silicon Inorganic materials 0.000 description 21

- 239000010703 silicon Substances 0.000 description 21

- 239000011229 interlayer Substances 0.000 description 17

- 229910052760 oxygen Inorganic materials 0.000 description 15

- 239000003990 capacitor Substances 0.000 description 14

- 238000010586 diagram Methods 0.000 description 14

- 239000007789 gas Substances 0.000 description 13

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 12

- 239000001301 oxygen Substances 0.000 description 12

- 239000000126 substance Substances 0.000 description 12

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 12

- 230000015572 biosynthetic process Effects 0.000 description 10

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 9

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 8

- 229910052698 phosphorus Inorganic materials 0.000 description 8

- 239000011574 phosphorus Substances 0.000 description 8

- 238000002425 crystallisation Methods 0.000 description 7

- 229910052739 hydrogen Inorganic materials 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- 230000001681 protective effect Effects 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 238000001994 activation Methods 0.000 description 6

- 229910052757 nitrogen Inorganic materials 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 5

- 238000000137 annealing Methods 0.000 description 5

- 239000012298 atmosphere Substances 0.000 description 5

- 230000008025 crystallization Effects 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 238000009616 inductively coupled plasma Methods 0.000 description 5

- 238000000059 patterning Methods 0.000 description 5

- 229920005989 resin Polymers 0.000 description 5

- 239000011347 resin Substances 0.000 description 5

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 239000000945 filler Substances 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- 239000001257 hydrogen Substances 0.000 description 4

- 229910003437 indium oxide Inorganic materials 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 229920003023 plastic Polymers 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 239000003566 sealing material Substances 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 239000002356 single layer Substances 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 3

- 230000001133 acceleration Effects 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical group [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 238000005984 hydrogenation reaction Methods 0.000 description 3

- 239000011810 insulating material Substances 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- 239000004973 liquid crystal related substance Substances 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 3

- 238000002161 passivation Methods 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- 238000007740 vapor deposition Methods 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- 241001270131 Agaricus moelleri Species 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- 229920002799 BoPET Polymers 0.000 description 2

- 239000005041 Mylar™ Substances 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 239000003054 catalyst Substances 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 239000011231 conductive filler Substances 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 230000005525 hole transport Effects 0.000 description 2

- 238000005224 laser annealing Methods 0.000 description 2

- 238000005499 laser crystallization Methods 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920006267 polyester film Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 238000012827 research and development Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- NXHILIPIEUBEPD-UHFFFAOYSA-H tungsten hexafluoride Chemical compound F[W](F)(F)(F)(F)F NXHILIPIEUBEPD-UHFFFAOYSA-H 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- 150000005072 1,3,4-oxadiazoles Chemical class 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 241000287181 Sturnus vulgaris Species 0.000 description 1

- 229910001069 Ti alloy Inorganic materials 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- VBVAVBCYMYWNOU-UHFFFAOYSA-N coumarin 6 Chemical compound C1=CC=C2SC(C3=CC4=CC=C(C=C4OC3=O)N(CC)CC)=NC2=C1 VBVAVBCYMYWNOU-UHFFFAOYSA-N 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 210000003128 head Anatomy 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000000178 monomer Substances 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 239000002985 plastic film Substances 0.000 description 1

- 229920006255 plastic film Polymers 0.000 description 1

- 229920003227 poly(N-vinyl carbazole) Polymers 0.000 description 1

- 229920000553 poly(phenylenevinylene) Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- -1 polyphenylene vinylene Polymers 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 239000012495 reaction gas Substances 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- SBEQWOXEGHQIMW-UHFFFAOYSA-N silicon Chemical group [Si].[Si] SBEQWOXEGHQIMW-UHFFFAOYSA-N 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3266—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0251—Precharge or discharge of pixel before applying new pixel voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0247—Flicker reduction other than flicker reduction circuits used for single beam cathode-ray tubes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0261—Improving the quality of display appearance in the context of movement of objects on the screen or movement of the observer relative to the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0266—Reduction of sub-frame artefacts

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

- G09G3/2033—Display of intermediate tones by time modulation using two or more time intervals using sub-frames with splitting one or more sub-frames corresponding to the most significant bits into two or more sub-frames

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

Description

【発明の属する技術分野】

本発明は、マトリクス状に複数の画素を配置し、各画素が点灯する長さを制御することにより、階調表示を行うパネルを備えるEL表示装置の駆動方法に関するものである。特に、有機EL素子を用いたELパネルを有するEL表示装置の駆動方法に関するものである。

【0002】

【従来の技術】

放送局側における機器やシステムへのデジタル技術の導入が進んでおり、近年では放送電波のデジタル化、すなわちデジタル放送の実現に向けて研究開発が各国で行われている。

【0003】

また、放送電波のデジタル化に対応して、画像情報を有するデジタルのビデオ信号(デジタルビデオ信号)を、アナログに変換せずにデジタルのまま用いて画像を表示する、アクティブマトリクス型の表示装置の研究開発も、近年盛んに行われている。

【0004】

デジタルビデオ信号が有する2値の電圧により階調表示を行う方法として、面積分割駆動法と、時間分割駆動法とが挙げられる。

【0005】

面積分割駆動法は、1画素を複数の副画素に分割し、各副画素を独立にデジタルビデオ信号に基づいて駆動することによって、階調表示を行う駆動法である。この面積分割駆動法は、1画素が複数に分割されていなければならない。またさらに画素を分割するだけでなく、分割された副画素を独立して駆動するために、各副画素にそれぞれ対応する画素電極を設ける必要がある。そのために画素の構造が複雑になるという不都合が生じる。

【0006】

一方、時間分割駆動法は、画素の点灯する長さを制御することで階調表示を行う駆動法である。具体的には、1フレーム期間を複数の表示期間に分割する。そして、デジタルビデオ信号により、各表示期間において各画素が点灯または非点灯の状態になる。1フレーム期間中に出現する全ての表示期間の内、画素が点灯した表示期間の長さを積算することで、該画素の階調が求められる。

【0007】

一般的に、液晶などに比べて有機EL材料の応答速度は速いため、時間分割駆動に適している。

【0008】

【発明が解決しようとする課題】

時間分割駆動を行う場合、高階調を実現するには、二進コード法によるのが便利である。以下に、単純な二進コード法による時間分割駆動で中間階調を表示した場合について、図19を用いて詳しく説明する。

【0009】

図19(A)に表示装置の画素部を示し、図19(B)に、該画素部において、1フレーム期間中に出現する全ての表示期間の長さを示す。

【0010】

図19では、1〜64階調の表示が可能な6ビットのデジタルビデオ信号を用いて画像を表示している。画素部の右半分が33(32+1)階調の表示を行っており、左半分が32(31+1)階調の表示を行っている。

【0011】

6ビットのデジタルビデオ信号を用いる場合、一般的に1フレーム期間中に6つの表示期間(表示期間Tr1〜表示期間Tr6)が出現する。そしてデジタルビデオ信号の1ビット目〜6ビット目のデジタルビデオ信号は、それぞれ表示期間Tr1〜表示期間Tr6に対応している。

【0012】

表示期間Tr1〜表示期間Tr6の長さの比は、20:21:22:23:24:25となる。最上位ビット(この場合6ビット目)のデジタルビデオ信号に対応する表示期間Tr6の長さが一番長く、最下位ビット(1ビット目)のデジタルビデオ信号に対応する表示期間の長さが一番短い。

【0013】

32階調の表示を行う場合、表示期間Tr1〜Tr5において画素を点灯の状態にし、表示期間Tr6において画素を非点灯の状態にする。また33階調の表示を行う場合、表示期間Tr1〜Tr5において画素を非点灯の状態にし、表示期間Tr6において画素を点灯の状態にする。

【0014】

この駆動を行った場合、画素部において32階調の表示を行っている部分と33階調の表示を行っている部分との境界部で、偽輪郭が視認されることがある。

【0015】

偽輪郭とは、二進コード法による時間階調表示を行ったときに度々視認される不自然な輪郭線であって、人間の視覚の特性によって生じる知覚輝度の変動が主な原因とされている。図20を用いて、偽輪郭の発生のメカニズムについて説明する。

【0016】

図20(A)に偽輪郭が発生して見える表示装置の画素部を示し、図20(B)に、該画素部において、1フレーム期間中において出現する表示期間の長さの比を示す。

【0017】

図20では、1〜64階調の表示が可能な6ビットのデジタルビデオ信号を用いて画像を表示している。画素部の右半分が33階調の表示を行っており、左半分が32階調の表示を行っている。

【0018】

画素部の32階調の表示を行っている部分では、1フレーム期間の31/63の期間において画素が点灯の状態であり、1フレーム期間の32/63の期間において画素が非点灯の状態である。そして画素が点灯の状態の期間と、非点灯の状態の期間とが交互に出現している。

【0019】

また、画素部の33階調の表示を行っている部分では、1フレーム期間の32/63の期間において画素が点灯の状態であり、1フレーム期間の31/63の期間において画素が非点灯の状態である。そして画素が点灯の状態の期間と、非点灯の状態の期間とが交互に出現している。

【0020】

動画を表示する場合、例えば図20(A)において、32階調を表示している部分と33階調を表示している部分の境界が、点線の方向に移動したとする。つまり境界付近において、画素は32階調の表示から33階調の表示に切り替わる。すると、境界付近の画素では、32階調を表示するための点灯期間の直後に33階調を表示するための点灯期間が開始される。そのため人間の目には、該画素が1フレーム期間連続して点灯しているように見える。これは画面上に不自然な明るい線として知覚される。

【0021】

また逆に、例えば図20(A)において、32階調を表示している部分と33階調を表示している部分の境界が、実線の方向に移動したとする。つまり境界付近において、画素は33階調の表示から32階調の表示に切り替わる。すると、境界付近の画素では、33階調を表示するための点灯期間の直後に32階調を表示するための点灯期間が開始される。そのため人間の目には、該画素が1フレーム期間連続して非点灯の状態に見える。これは画面上に不自然な暗い線として知覚される。

【0022】

以上のような、画面上に現れて見える不自然な明るい線や暗い線が、偽輪郭(動画偽輪郭)と呼ばれる表示妨害である。

【0023】

ところで、静止画においても、動画において動画偽輪郭が発生するのと同じ原因により、表示妨害が視認されてしまうことがある。静止画における表示妨害は、階調の境界が揺れ動いて見えるというものである。以下、静止画においてこのような表示妨害が視認される理由を簡単に述べる。

【0024】

人間の目は一点を凝視しているつもりでも、視点は微妙に動いており、定まった一点を正確に見つめることは難しい。そのため、画素部の32階調の表示を行っている部分と、33階調の表示を行っている部分との境目を目で凝視したとき、境目を見つめているつもりでも、実際には視点が左右上下に微妙に動いてしまう。

【0025】

例えば、破線で示したように、視点が32階調の表示を行っている部分から、33階調の表示を行っている部分に移動したとする。そして視点が32階調を表示している部分に置かれたときに画素が非点灯の状態で、視点が33階調を表示している部分に置かれたときに画素が非点灯の状態だった場合、人間の目には1フレーム期間を通して、画素がずっと非点灯の状態であったかのように視認されてしまう。

【0026】

逆に例えば、実線で示したように、視点が33階調の表示を行っている部分から、32階調の表示を行っている部分に移動したとする。そして視点が33階調を表示している部分に置かれたときに画素が点灯の状態で、視点が32階調を表示している部分に置かれたときに画素が点灯の状態だった場合、人間の目には1フレーム期間を通して、画素がずっと点灯の状態であったかのように視認されてしまう。

【0027】

したがって、視点が左右上下に微妙に動いてしまうために、人間の目には1フレーム期間を通して画素がずっと点灯の状態、または非点灯の状態であったかのように見え、あたかも境界部が揺れ動いているように表示妨害が視認されてしまう。

【0028】

【課題を解決するための手段】

本発明者らは、偽輪郭の視認を防止するために、期間が長い表示期間を一定の規則により複数の表示期間(分割表示期間)に分割した。そしてなおかつ、該複数の分割表示期間が連続して出現しないように、該複数の分割表示期間を1フレーム期間内に分散させることを考えた。

【0029】

分割する表示期間は1つでも複数でも良い。ただし上位ビットに対応する表示期間、言いかえると長さの長い表示期間から一定の規則により順に分割することが好ましい。

【0030】

また、表示期間の分割数は設計者が適宜選択可能であるが、どこまで分割するかは、表示装置の駆動速度と、要求される画像の表示品質とのバランスによって決めるのが好ましい。

【0031】

また同じビットのデジタルビデオ信号に対応した分割表示期間の長さは同じであることが望ましいが、本発明はこれに限定されない。分割表示期間の長さは必ずしも同じである必要はない。

【0032】

上記構成によって、二進コード法による時間分割駆動において顕著な、偽輪郭などの表示妨害が視認されるのを防ぐことができる。

【0033】

以下に本発明の構成について述べる。

【0034】

本発明によって、

第1のTFT、第2のTFT、第3のTFT及び有機EL素子をそれぞれ有する画素が、複数設けられたEL表示装置の駆動方法であって、

1フレーム期間にn+m個(n、mは共に自然数)の表示期間が出現し、

前記n+m個の表示期間は、nビットのデジタルビデオ信号のうち、いずれか1ビットのデジタルビデオ信号にそれぞれ対応しており、

前記n+m個の表示期間のいずれか複数の表示期間は、前記デジタルビデオ信号の同じビットに対応しており、

前記複数の表示期間の間に、前記n+m個の表示期間のうちの、前記デジタルビデオ信号の他のビットに対応する表示期間が出現し、

前記n+m個の表示期間のそれぞれは、前記第1のTFTがオンになることで、対応するビットの前記デジタルビデオ信号が前記第2のTFTのゲート電極に入力され、なおかつ前記第3のTFTがオフでになることで開始され、

前記n+m個の表示期間のそれぞれは、開始された後に、前記n+m個の表示期間のうちの、他の表示期間が開始されるか、もしくは第3のTFTがオンになることで終了し、

前記第2のTFTがオンになると前記有機EL素子が発光し、オフになると発光しないことを特徴とするEL表示装置の駆動方法が提供される。

【0035】

本発明によって、

第1のTFT、第2のTFT、第3のTFT及び有機EL素子をそれぞれ有する画素が、複数設けられたEL表示装置の駆動方法であって、

1フレーム期間にn+m個(n、mは共に自然数)の表示期間が出現し、

前記n+m個の表示期間は、nビットのデジタルビデオ信号のうち、いずれか1ビットのデジタルビデオ信号にそれぞれ対応しており、

前記n+m個の表示期間のいずれか複数の表示期間は、前記デジタルビデオ信号の最上位ビットに対応しており、

前記複数の表示期間の間に、前記n+m個の表示期間のうちの、前記デジタルビデオ信号の他のビットに対応する表示期間が出現し、

前記n+m個の表示期間のそれぞれは、前記第1のTFTがオンになることで、対応するビットの前記デジタルビデオ信号が前記第2のTFTのゲート電極に入力され、なおかつ前記第3のTFTがオフでになることで開始され、

前記n+m個の表示期間のそれぞれは、開始された後に、前記n+m個の表示期間のうちの、他の表示期間が開始されるか、もしくは第3のTFTがオンになることで終了し、

前記第2のTFTがオンになると前記有機EL素子が発光し、オフになると発光しないことを特徴とするEL表示装置の駆動方法が提供される。

【0036】

本発明によって、

第1のTFT、第2のTFT、第3のTFT及び有機EL素子をそれぞれ有する画素が、複数設けられたEL表示装置の駆動方法であって、

1フレーム期間にn+m個(n、mは共に自然数)の表示期間が出現し、

前記n+m個の表示期間は、nビットのデジタルビデオ信号のうち、いずれか1ビットのデジタルビデオ信号にそれぞれ対応しており、

前記デジタルビデオ信号の上位ビットは、それぞれ前記n+m個の表示期間のいずれか複数の表示期間に対応しており、

前記複数の表示期間の間に、前記n+m個の表示期間のうちの、前記デジタルビデオ信号の他のビットに対応する表示期間が出現し、

前記n+m個の表示期間のそれぞれは、前記第1のTFTがオンになることで、対応するビットの前記デジタルビデオ信号が前記第2のTFTのゲート電極に入力され、なおかつ前記第3のTFTがオフでになることで開始され、

前記n+m個の表示期間のそれぞれは、開始された後に、前記n+m個の表示期間のうちの他の表示期間が開始されるか、もしくは第3のTFTがオンになることで終了し、

前記第2のTFTがオンになると前記有機EL素子が発光し、オフになると発光しないことを特徴とするEL表示装置の駆動方法が提供される。

【0037】

本発明は、

前記第1のTFTと前記第2のTFTが、極性が同じであることを特徴としていても良い。

【0038】

本発明は、

前記n+m個の表示期間のうち、各ビットのデジタルビデオ信号に対応する表示期間の長さをT1、T2、T3、…、Tn-1、Tnとすると、

T1、T2、T3、…、Tn-1=20、21、22、2n-2、2n-1であることを特徴としていても良い。

【0039】

【発明の実施の形態】

(実施の形態1)

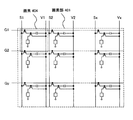

以下に、本発明の時間分割駆動法で中間階調を表示した場合について、図1を用いて詳しく説明する。

【0040】

図1(A)に表示装置の画素部を示し、図1(B)に、該画素部において、1フレーム期間(F)中に出現する表示期間Trの長さの比を示す。

【0041】

図1では、1〜2n階調の表示が可能なnビットのデジタルビデオ信号を用いて、画像を表示している。画素部の右半分が2n-1+1階調の表示を行っており、左半分が2n-1階調の表示を行っている。

【0042】

nビットのデジタルビデオ信号を用いる場合、単純な二進コード法によれば、1フレーム期間中にn個の表示期間(表示期間Tr1〜表示期間Trn)が出現する。そしてデジタルビデオ信号の1ビット目〜nビット目のデジタルビデオ信号は、それぞれ表示期間Tr1〜表示期間Trnに対応している。

【0043】

表示期間Tr1〜表示期間Trnの長さの比は、20:21:22:…:2n-2:2n-1となる。最上位ビット(この場合nビット目)のデジタルビデオ信号に対応する表示期間Trnの長さが一番長く、最下位ビット(1ビット目)のデジタルビデオ信号に対応する表示期間Tr1の長さが一番短い。

【0044】

2n-1階調の表示を行う場合、表示期間Tr1〜表示期間Tr(n−1)において画素を点灯の状態にし、表示期間Trnにおいて画素を非点灯の状態にする。また2n-1+1階調の表示を行う場合、表示期間Tr1〜表示期間Tr(n−1)において画素を非点灯の状態にし、表示期間Trnにおいて画素を点灯の状態にする。

【0045】

そして本実施の形態においては、一番期間の長い表示期間である表示期間Trnを2つの分割表示期間(S1TrnとS2Trn)に分割している。なお本実施の形態において、表示期間Trnを2つの分割表示期間に分割しているが、本発明はこれに限定されない。2つ以上であれば分割表示期間は、駆動回路や画素のTFTの動作速度が追いつく限り、いくつ設けても良い。

【0046】

分割表示期間は連続して出現せず、必ず間に他のビットのデジタルビデオ信号に対応する表示期間が出現するようにする。

【0047】

なお分割表示期間の長さは全て同じでなくとも良い。また、分割しない表示期間の並び順は、必ずしも制限を設けない。上位ビットに対応した表示期間から、下位ビットに対応した表示期間の順に並べるとは限らない。

【0048】

次に図2を用いて、本発明の駆動方法において偽輪郭などの表示妨害が視認されずらい理由について述べる。

【0049】

図2(A)に本発明の駆動方法で表示を行う表示装置の画素部を示し、図2(B)に、該画素部において、1フレーム期間中に出現する表示期間や分割表示期間を、画素が点灯する期間と点灯しない(非点灯の)期間とに分けて、それぞれの期間の長さを示す。

【0050】

図2(A)では、画素部の右半分が2n-1+1階調の表示を行っており、左半分が2n-1階調の表示を行っている。

【0051】

画素部の2n-1階調の表示を行っている部分では、1フレーム期間中の2n-1−1/2nの期間において画素が点灯の状態であり、1フレーム期間中の2n-1/2nの期間において画素が非点灯の状態である。そして画素が点灯の状態の期間と、非点灯の状態の期間とが交互に出現している。

【0052】

また、画素部の2n-1+1階調の表示を行っている部分では、1フレーム期間中の2n-1/2nの期間において画素が点灯の状態であり、1フレーム期間中の2n-1−1/2nの期間において画素が非点灯の状態である。そして画素が点灯の状態の期間と、非点灯の状態の期間とが交互に出現している。

【0053】

1フレーム期間中に点灯期間と非点灯期間とが分割されて交互に出現するので、人間の視点が左右上下に微妙に動いており、たまたま別の表示期間または分割表示期間にまたがっていたりすることも十分起こりうる。こういった場合に、人間の視点が非点灯の画素のみを連続して凝視したり、逆に点灯している画素のみを連続して凝視してしまったとしても、連続する点灯期間もしくは非点灯期間の長さが、従来の単純な二進コード法による駆動に比べて短いため、偽輪郭の視認を防止することができる。

【0054】

例えば、破線で示したように、視点が2n-1階調を表示している部分から、2n-1+1階調を表示している部分に移動したとする。そして本発明の駆動方法では、視点が2n-1階調を表示している部分に置かれたときに画素が非点灯の状態であり、なおかつ視点が2n-1+1階調を表示している部分に移動したときに画素が点灯の状態であったとしても、連続して出現する2つの非点灯期間の和が従来に比べて短くなる。そのため、人間の目には1フレーム期間を通して、画素がずっと非点灯の状態であったかのように視認されてしまうのを防ぐことができる。

【0055】

逆に例えば、実線で示したように、視点が2n-1+1階調を表示している部分から、2n-1階調を表示している部分に移動したとする。そして本発明の駆動方法では、視点が2n-1+1階調を表示している部分に置かれたときに画素が点灯の状態であり、なおかつ視点が2n-1階調を表示している部分に移動したときに画素が点灯の状態であったとしても、連続して出現する2つの点灯期間の和が従来に比べて短くなる。そのため、人間の目には1フレーム期間を通して、画素がずっと点灯の状態であったかのように視認されてしまうのを防ぐことができる。

【0056】

上記構成によって、二進コード法による時間分割駆動において顕著な、偽輪郭などの表示妨害が視認されるのを防ぐことができる。

【0057】

(実施の形態2)

実施の形態1では、最上位ビットのデジタルビデオ信号に対応する表示期間のみ、分割表示期間に分割していた。本実施の形態では、最上位ビットから連続して順に選ばれた、複数の上位ビットのデジタルビデオ信号に対応する表示期間を、それぞれ複数の分割表示期間に分割する例について説明する。なお本明細書において、上位ビットは分割表示期間に分割された表示期間に対応しており、下位ビットは分割表示期間に分割されない表示期間に対応している。

【0058】

図3を用いて本実施の形態の駆動方法について説明する。図3は、nビットのデジタルビデオ信号を用いて時分割階調表示を行った際に、画素部において1フレーム期間(F)中に出現する表示期間Trと分割表示期間STrの長さの比を示す。

【0059】

本実施の形態では、表示期間Trnと表示期間Tr(n−1)を、上位ビットのデジタルビデオ信号に対応する表示期間とする。なお本実施の形態では、nビットと、(nー1)ビットの2つのビットを上位ビットとする駆動方法について説明するが、本発明はこれに限定されない。上位ビットの数は1つでも良く、もちろん2以上であっても良い。ただし全ての上位ビットは、最上位ビットから順に連続していることが必要である。例えば上位ビットが3つの場合、nビット目と、(n−1)ビット目と、(n−2)ビット目のデジタルビデオ信号が上位ビットに相当する。

【0060】

表示期間Tr1〜表示期間Trnの長さの比は、20:21:22:…:2n-2:2n-1となる。

【0061】

2n-1階調の表示を行う場合、表示期間Tr1〜表示期間Tr(n−1)において画素を点灯の状態にし、表示期間Trnにおいて画素を非点灯の状態にする。また2n-1+1階調の表示を行う場合、表示期間Tr1〜表示期間Tr(n−1)において画素を非点灯の状態にし、表示期間Trnにおいて画素を点灯の状態にする。

【0062】

そして本実施の形態においては、上位ビットに対応する表示期間、本実施の形態では表示期間Trnを3つの分割表示期間(S1Trn、S2Trn、S3Trn)に、表示期間Tr(n−1)を2つの分割表示期間(S1Tr(n−1)、S2Tr(n−1))にそれぞれ分割している。なお本実施の形態では、表示期間Trnの分割数が3、表示期間Tr(n−1)の分割数が2となるように分割表示期間を形成したが、本発明はこれに限定されない。上位ビットに対応する表示期間の分割数はこの数値に限定されず、2以上であれば、駆動回路や画素のTFTの動作速度が追いつく限りいくつでも設けることが可能である。

【0063】

同じビットのデジタルビデオ信号に対応する分割表示期間は連続して出現せず、必ず間に他のビットのデジタルビデオ信号に対応するサブフレーム期間または表示期間が出現するようにする。

【0064】

なお同じビットのデジタルビデオ信号に対応する分割表示期間の長さは、全て同じでなくとも良い。

【0065】

上記構成によって、二進コード法による時間分割駆動において顕著な、偽輪郭などの表示妨害が視認されるのを防ぐことができる。

【0066】

(実施の形態3)

本実施の形態では、表示期間を一定の規則に基づいて、複数の分割表示期間に分割する駆動方法について説明する。説明を容易にするために、本実施の形態では8ビットのデジタルビデオ信号を用いて階調表示を行う場合について説明する。

【0067】

nビット(n=1〜8)のデジタルビデオ信号に対応する表示期間の長さを、それぞれLnとし、該表示期間の分割数をmnとする。このとき、mn=1、2、3、4、…のそれぞれの場合について、Ln/mn 3の値を求めると、以下の表1のようになる。

【0068】

【表1】

【0069】

ここで本実施の形態では、1フレーム期間中に設ける表示期間と分割表示期間の総数を13とする。全ての表示期間及び分割表示期間の長さは、なるべく等しいことが好ましい。全ての表示期間及び分割表示期間の長さが等しければ、偽輪郭などの表示妨害が視認されるのをより効果的に防ぐことができる。よって表1に示したLn/mn 3の値がなるべく等しくなるように、なおかつ1フレーム期間中に設ける表示期間と分割表示期間の総数が13になるように、各表示期間の分割数を選択する。また上位ビットに対応する表示期間、言いかえると長さの長い表示期間から順に分割することが好ましい。本実施の形態では表2に丸印で示すように分割する。

【0070】

【表2】

【0071】

つまり、表示期間Tr1〜4が分割なし、表示期間Tr5〜7が2分割、表示期間Tr8が3分割となるようにする。また1フレーム期間において、同じビットのデジタルビデオ信号に対応する表示期間は、連続して出現しないように駆動する。

【0072】

表示期間の分割数は設計者が適宜選択可能であるが、どこまで分割するかは、表示装置の駆動速度と、要求される画像の表示品質とのバランスによって決めるのが好ましい。

【0073】

また同じビットのデジタルビデオ信号に対応した分割表示期間の長さは同じであることが望ましいが、本発明はこれに限定されない。分割表示期間の長さは必ずしも同じである必要はない。

【0074】

なお、条件によっては、上述のLn/mn 3に代わり、Ln/mn 2を用いたほうがより効果的に偽輪郭の視認を防ぐことが可能な場合もある。どちらの値を基準に駆動方法を決定するかは、設計者が適宜選択することが可能である。

【0075】

上記構成によって、二進コード法による時間分割駆動において顕著な、偽輪郭などの表示妨害が視認されるのを防ぐことができる。

【0076】

【実施例】

以下に、本発明の実施例について説明する。

【0077】

(実施例1)

本実施例では、各画素に設けられた2つの薄膜トランジスタ(TFT)を用いて、有機EL素子の発光を制御するELディスプレイの画素部の構成と、駆動方法について説明する。

【0078】

本実施例のELディスプレイの画素部401の拡大図を図4に示す。ソース信号線(S1〜Sx)、電源供給線(V1〜Vx)、ゲート信号線(G1〜Gy)が画素部401に設けられている。

【0079】

本実例の場合、ソース信号線(S1〜Sx)のいずれか1つと、電源供給線(V1〜Vx)のいずれか1つと、ゲート信号線(G1〜Gy)のいずれか1つとを備えた領域が画素404である。画素部401にはマトリクス状に複数の画素404が配置されることになる。

【0080】

画素404の拡大図を図5に示す。図5において、405はスイッチング用TFTである。スイッチング用TFT405のゲート電極は、ゲート信号線G(G1〜Gyのいずれか1つ)に接続されている。スイッチング用TFT405のソース領域とドレイン領域は、一方がソース信号線S(S1〜Sxのいずれか1つ)に、もう一方がEL駆動用TFT406のゲート電極、各画素が有するコンデンサ408にそれぞれ接続されている。

【0081】

コンデンサ408はスイッチング用TFT405が非選択状態(オフ状態)にある時、EL駆動用TFT406のゲート電圧(ゲート電極とソース領域間の電位差)を保持するために設けられている。なお本実施例ではコンデンサ408を設ける構成を示したが、本発明はこの構成に限定されず、コンデンサ408を設けない構成にしても良い。

【0082】

また、EL駆動用TFT406のソース領域とドレイン領域は、一方が電源供給線V(V1〜Vxのいずれか1つ)に接続され、もう一方は有機EL素子407に接続される。電源供給線Vはコンデンサ408に接続されている。

【0083】

有機EL素子407は陽極と陰極と、陽極と陰極との間に設けられたEL層とからなる。陽極がEL駆動用TFT406のソース領域またはドレイン領域と接続している場合、陽極が画素電極、陰極が対向電極となる。逆に陰極がEL駆動用TFT406のソース領域またはドレイン領域と接続している場合、陰極が画素電極、陽極が対向電極となる。

【0084】

有機EL素子407の対向電極には対向電位が与えられている。また電源供給線Vは電源電位が与えられている。電源電位と対向電位は、本発明の駆動方法を用いたELディスプレイに、外付けのIC等により設けられた電源によって与えられる。電源供給線の電源電位は、電源電位が有機EL素子の画素電極に与えられたときに有機EL素子が発光する程度に、対向電極との間に電位差を有する電位に保たれている。

【0085】

現在の典型的な有機ELディスプレイには、画素の発光する面積あたりの発光量が200cd/m2の場合、画素部の面積あたりの電流が数mA/cm2程度必要となる。そのため特に画面サイズが大きくなると、ICに設けられた電源から与えられる電位の高さをスイッチで制御することが難しくなっていく。本実施例においては、電源電位と対向電位は常に一定に保たれており、ICに設けられた電源から与えられる電位の高さをスイッチで制御する必要がないので、より大きな画面サイズのパネルの実現に有用である。

【0086】

スイッチング用TFT405、EL駆動用TFT406は、nチャネル型TFTでもpチャネル型TFTでもどちらでも用いることができる。ただしEL駆動用TFT406のソース領域またはドレイン領域が有機EL素子407の陽極と接続されている場合、EL駆動用TFT406はpチャネル型TFTであることが望ましい。また、EL駆動用TFT406のソース領域またはドレイン領域が有機EL素子407の陰極と接続されている場合、EL駆動用TFT406はnチャネル型TFTであることが望ましい。

【0087】

またスイッチング用TFT405、EL駆動用TFT406は、シングルゲート構造ではなく、ダブルゲート構造、やトリプルゲート構造などのマルチゲート構造を有していても良い。

【0088】

次に上述した構成を有する本発明のELディスプレイの駆動方法について、図6を用いて説明する。図6において、横軸は時間を示しており。縦軸は選択されているゲート信号線の位置を示している。

【0089】

まず、ゲート信号線駆動回路からゲート信号線G1に入力されるゲート信号によって、ゲート信号線G1が選択される。なお本明細書においてゲート信号線が選択されるとは、該ゲート信号線に接続されている全てのスイッチング用TFT405が全てオンの状態になることを意味する。つまりここでは、ゲート信号線G1に接続されている全ての画素(1ライン目の画素)のスイッチング用TFT405がオンの状態になることを意味する。

【0090】

そして同時に、ソース信号線(S1〜Sx)にソース信号線駆動回路から、1ビット目のデジタルビデオ信号が入力される。デジタルビデオ信号はスイッチング用TFT405を介してEL駆動用TFT406のゲート電極に入力される。

【0091】

そして本実施例では、デジタルビデオ信号が「0」の情報を有していた場合、EL駆動用TFT406はオフの状態になる。よって有機EL素子407の画素電極には電源電位は与えられない。その結果、「0」の情報を有するデジタルビデオ信号が入力された画素が有する有機EL素子407は発光しない。

【0092】

なお本明細書においてデジタルビデオ信号が画素に入力されるとは、該画素が有するEL駆動用TFTのゲート電極に、デジタルビデオ信号が入力されることを意味する。

【0093】

逆に、「1」の情報を有していた場合、EL駆動用TFT406はオンの状態になる。よって有機EL素子407の画素電極には電源電位が与えられる。その結果、「1」の情報を有するデジタルビデオ信号が入力された画素が有する有機EL素子407は発光する。

【0094】

このように有機EL素子407が発光、または非発光の状態になり、1ライン目の画素は表示を行う。

【0095】

次にゲート信号線G1の選択が終了すると同時に、ゲート信号線G2がゲート信号によって選択される。そしてゲート信号線G2に接続されている全ての画素のスイッチング用TFT405がオンの状態になり、2ライン目の画素にソース信号線(S1〜Sx)から1ビット目のデジタルビデオ信号が入力される。

【0096】

そして順に、全てのゲート信号線(G1〜Gy)がゲート信号によって選択される。全てのゲート信号線(G1〜Gy)が選択され、全てのラインの画素に1ビット目のデジタルビデオ信号が入力されるまでの期間が書き込み期間Ta1である。

【0097】

なお書き込み期間Ta1が開始されてから、次に出現する書き込み期間(この場合Ta2)が開始されるまでの期間を、表示期間Tr1と呼ぶ。

【0098】

表示期間Tr1が終了すると書込期間Ta2となり、書込期間Ta1の場合と同様に順に全てのゲート信号線が順に選択され、2ビット目のデジタルビデオ信号が全ての画素に入力される。全てのラインの画素に2ビット目のデジタルビデオ信号が入力し終わるまでの期間を、書き込み期間Ta2と呼ぶ。

【0099】

書き込み期間Ta2が開始されてから次に出現する書き込み期間が開始されるまでの期間(この場合書き込み期間Tan)を表示期間Tr2と呼ぶ。

【0100】

表示期間Tr2が終了すると、書き込み期間Tanが開始される。書込期間Ta1の場合と同様に順に全てのゲート信号線が順に選択され、nビット目のデジタルビデオ信号が全ての画素に入力される。全てのラインの画素にnビット目のデジタルビデオ信号が入力し終わるまでの期間を、書き込み期間Tanと呼ぶ。

【0101】

書き込み期間Tanが開始されてから次に出現する書き込み期間が開始されるまでの期間(この場合書き込み期間Ta3)を分割表示期間S1Trnと呼ぶ。

【0102】

そして分割表示期間S1Trnが終了すると、順に表示期間Tr3、Tr4、…、Tr(n−1)が出現し、それぞれの期間において同様に、対応するビットのデジタルビデオ信号が画素に入力される。

【0103】

Tr(n−1)が終了すると、書き込み期間Tanが開始される。書込期間Ta1の場合と同様に順に全てのゲート信号線が順に選択され、nビット目のデジタルビデオ信号が全ての画素に入力される。全てのラインの画素にnビット目のデジタルビデオ信号が入力し終わるまでの期間を、書き込み期間Tanと呼ぶ。

【0104】

書き込み期間Tanが開始されてから次に出現する書き込み期間が開始されるまでの期間(この場合、次のフレーム期間における書き込み期間Ta1)を分割表示期間S2Trnと呼ぶ。

【0105】

なお分割表示期間S1Trnと分割表示期間S2Trnとを合わせて、表示期間Trnと呼ぶ。

【0106】

全ての表示期間(Tr1〜Trn)が終了すると1つの画像を表示することができる。本発明の駆動方法において、1つの画像を表示する期間を1フレーム期間(F)と呼ぶ。1フレーム期間が終了すると次のフレーム期間が開始される。そして再び書込期間Ta1が出現し、上述した動作を繰り返す。

【0107】

本実施例では、全ての書き込み期間の長さの和が1フレーム期間よりも短く、なおかつ表示期間の長さの比は、Tr1:Tr2:Tr3:…:Tr(n−1):Trn=20:21:22:…:2(n-2):2(n-1)となるようにすることが必要である。この表示期間の組み合わせで1〜2n階調のうち所望の階調表示を行うことができる。

【0108】

1フレーム期間中に有機EL素子が発光した表示期間の長さの総和を求めることによって、当該フレーム期間におけるその画素の表示した階調がきまる。例えば、n=8のとき、全ての表示期間で画素が発光した場合の輝度を100%とすると、Tr1とTr2において画素が発光した場合には1%の輝度が表現でき、Tr3とTr5とTr8を選択した場合には60%の輝度が表現できる。

【0109】

また表示期間Tr1〜Trnは、どのような順序で出現させても良い。例えば1フレーム期間中において、Tr1の次にTr3、Tr5、Tr2、…という順序で表示期間を出現させることも可能である。ただし、同じnビット目のデジタルビデオ信号に対応する、分割表示期間S1Trnと分割表示期間S2Trnは、連続して出現しないようにすることが肝要である。

【0110】

なお本実施例では、電源電位と対向電位の高さを常に一定にしていたが、本発明はこれに限定されない。書き込み期間において電源電位と対向電位の高さを同じに保ち、書き込み期間が終了すると同時に、電源電位が有機EL素子の画素電極に与えられたときに有機EL素子が発光する程度の電位差を、電源電位と対向電極の電位とが常に有するようにしても良い。

【0111】

この場合、表示期間内に書き込み期間は含まれない。表示期間は書き込み期間が終了してから、次に出現する書き込み期間が開始されるまでの期間に相当する。例えば表示期間Tr1は、書き込み期間Ta1が終了してから、書き込み期間Ta1の次に出現する書き込み期間(例えばTa2)が開始されるまでの期間である。

【0112】

上記構成によって、二進コード法による時間分割駆動において顕著な、偽輪郭などの表示妨害が視認されるのを防ぐことができる。

【0113】

なお本実施例では、表示期間Trnを2つの分割表示期間S1TrnとS2Trnとに分割しているが、本実施例はこの構成に限定されない。分割する表示期間は1つでも複数でも良い。ただし上位ビットに対応する表示期間、言いかえると長さの長い表示期間から順に分割することが好ましい。また、表示期間の分割数は設計者が適宜選択可能であるが、どこまで分割するかは、表示装置の駆動速度と、要求される画像の表示品質とのバランスによって決めるのが好ましい。

【0114】

また同じビットのデジタルビデオ信号に対応した分割表示期間の長さは同じであることが望ましいが、本発明はこれに限定されない。分割表示期間の長さは必ずしも同じである必要はない。

【0115】

(実施例2)

本実施例では、各画素に設けられた3つの薄膜トランジスタ(TFT)を用いて、有機EL素子の発光を制御するELディスプレイの画素部の構成と、駆動方法について説明する。

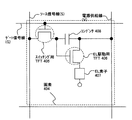

【0116】

本実施例のELディスプレイの画素部501の拡大図を図7に示す。ソース信号線(S1〜Sx)、電源供給線(V1〜Vx)、書き込み用ゲート信号線(第1のゲート信号線)(Ga1〜Gay)、消去用ゲート信号線(第2のゲート信号線)(Ge1〜Gey)が画素部501に設けられている。

【0117】

ソース信号線(S1〜Sx)の1つと、電源供給線(V1〜Vx)の1つと、書き込み用ゲート信号線(Ga1〜Gay)の1つと、消去用ゲート信号線(Ge1〜Gey)の1つとを備えた領域が画素505である。画素部501にはマトリクス状に複数の画素505が配列されることになる。

【0118】

画素505の拡大図を図8に示す。図8において、507はスイッチング用TFTである。スイッチング用TFT507のゲート電極は、書き込み用ゲート信号線Ga(Ga1〜Gayのいずれか1つ)に接続されている。スイッチング用TFT507のソース領域とドレイン領域は、一方がソース信号線S(S1〜Sxのいずれか1つ)に、もう一方がEL駆動用TFT508のゲート電極、各画素が有するコンデンサ512及び消去用TFT509のソース領域又はドレイン領域にそれぞれ接続されている。

【0119】

コンデンサ512はスイッチング用TFT505が非選択状態(オフ状態)にある時、EL駆動用TFT508のゲート電圧を保持するために設けられている。なお本実施例ではコンデンサ512を設ける構成を示したが、本発明はこの構成に限定されず、コンデンサ512を設けない構成にしても良い。

【0120】

また、EL駆動用TFT508のソース領域とドレイン領域は、一方が電源供給線V(V1〜Vxのいずれか1つ)に接続され、もう一方は有機EL素子510に接続される。電源供給線Vはコンデンサ512に接続されている。

【0121】

また消去用TFT509のソース領域とドレイン領域のうち、スイッチング用TFT507のソース領域またはドレイン領域に接続されていない方は、電源供給線Vに接続されている。そして消去用TFT509のゲート電極は、消去用ゲート信号線Ge(Ge1〜Gexのいずれか1つ)に接続されている。

【0122】

有機EL素子510は陽極と陰極と、陽極と陰極との間に設けられたEL層とからなる。陽極がEL駆動用TFT508のソース領域またはドレイン領域と接続している場合、陽極が画素電極、陰極が対向電極となる。逆に陰極がEL駆動用TFT508のソース領域またはドレイン領域と接続している場合、陰極が画素電極、陽極が対向電極となる。

【0123】

有機EL素子510の対向電極には対向電位が与えられている。また電源供給線Vは電源電位が与えられている。そして対向電位と電源電位の電位差は、電源電位が画素電極に与えられたときに有機EL素子が発光する程度の電位差に常に保たれている。電源電位と対向電位は、本発明の駆動方法を用いたELディスプレイに、外付けのIC等により設けられた電源によって与えられる。なお対向電位を与える電源を、本明細書では特に対向電源511と呼ぶ。

【0124】

現在の典型的なELディスプレイには、画素の発光する面積あたりの発光量が200cd/m2の場合、画素部の面積あたりの電流が数mA/cm2程度必要となる。そのため特に画面サイズが大きくなると、ICに設けられた電源から与えられる電位の高さをスイッチで制御することが難しくなっていく。本実施例においては、電源電位と対向電位は常に一定に保たれており、ICに設けられた電源から与えられる電位の高さをスイッチで制御する必要がないので、より大きな画面サイズのパネルの実現に有用である。

【0125】

スイッチング用TFT507、EL駆動用TFT508、消去用TFT509は、nチャネル型TFTでもpチャネル型TFTでもどちらでも用いることができる。またスイッチング用TFT507、EL駆動用TFT508、消去用TFT509は、シングルゲート構造ではなく、ダブルゲート構造、やトリプルゲート構造などのマルチゲート構造を有していても良い。

【0126】

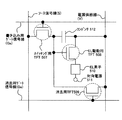

次に図7〜図8で示した本発明のELディスプレイの駆動方法について、図9を用いて説明する。図9において、横軸は時間を示しており。縦軸は選択されているゲート信号線の位置を示している。

【0127】

はじめに、1ライン目の画素において表示期間Tr1が開始され、、書き込み用ゲート信号線駆動回路(図示せず)から書き込み用ゲート信号線Ga1に入力される書き込み用ゲート信号(第1のゲート信号)によって、書き込み用ゲート信号線Ga1が選択される。そして書き込み用ゲート信号線Ga1に接続されている全ての画素(1ライン目の画素)のスイッチング用TFT507がオンの状態になる。

【0128】

そして同時に、ソース信号線駆動回路502からソース信号線S1〜Sxに入力される1ビット目のデジタルビデオ信号が、スイッチング用TFT507を介してEL駆動用TFT508のゲート電極に入力される。

【0129】

デジタルビデオ信号は「0」または「1」の情報を有しており、「0」と「1」のデジタルビデオ信号は、一方がHi、一方がLoの電圧を有する信号である。

【0130】

本実施例では、デジタルビデオ信号が「0」の情報を有していた場合、EL駆動用TFT508はオフの状態となる。よって有機EL素子510の画素電極に電源電位が与えられない。その結果、「0」の情報を有するデジタルビデオ信号が入力された画素が有する有機EL素子510は発光しない。

【0131】

逆に、デジタルビデオ信号が「1」の情報を有していた場合、EL駆動用TFT508はオンの状態となる。よって有機EL素子510の画素電極に電源電位が与えられる。その結果、「1」の情報を有するデジタルビデオ信号が入力された画素が有する有機EL素子510は発光する。

【0132】

なお本実施例ではデジタルビデオ信号が「0」の情報を有していた場合、EL駆動用TFT508はオフの状態となり、「1」の情報を有していた場合EL駆動用TFT508はオンの状態となるが、本発明はこの構成に限定されない。デジタルビデオ信号が「0」の情報を有していた場合、EL駆動用TFT508がオンの状態となり、「1」の情報を有していた場合EL駆動用TFT508オフの状態となっても良い。

【0133】

このように、1ライン目の画素にデジタルビデオ信号が入力されると同時に、有機EL素子510が発光、または非発光の状態になり、1ライン目の画素は表示を行う。

【0134】

次に書き込み用ゲート信号線Ga1の選択が終了すると、書き込み用ゲート信号線Ga2が書き込み用ゲート信号によって選択される。そして書き込み用ゲート信号線Ga2に接続されている全ての画素のスイッチング用TFT507がオンの状態になり、2ライン目の画素にソース信号線S1〜Sxから1ビット目のデジタルビデオ信号が入力される。

【0135】

そして順に、全ての書き込み用ゲート信号線Ga1〜Gayが選択され、全ての画素に1ビット目のデジタルビデオ信号が入力される。全ての画素に1ビット目のデジタルビデオ信号が入力されるまでの期間が、書き込み期間Ta1である。各ラインの画素において書き込み期間Taが開始されるタイミングはそれぞれ時間差を有している。

【0136】

なお、画素が表示を行っている期間を表示期間Trと呼ぶ。例えば1ライン目の画素だと、書き込み用ゲート信号線Ga1が選択されると同時に表示期間Tr1が開始される。各ラインの表示期間が開始されるタイミングはそれぞれ異なっている。

【0137】

一方、全ての画素に1ビット目のデジタルビデオ信号が入力される前、言い換えると書き込み期間Ta1が終了する前に、画素への1ビット目のデジタルビデオ信号の入力と並行して、消去用ゲート信号線駆動回路(図示せず)から消去用ゲート信号線Ge1入力される消去用ゲート信号(第2のゲート信号)によって、消去用ゲート信号線Ge1が選択される。そして、消去用ゲート信号線Ge1に接続されている全ての画素(1ライン目の画素)の消去用TFT509がオンの状態になる。そして電源供給線V1〜Vxの電源電位が消去用TFT509を介してEL駆動用TFT508のゲート電極に与えられる。

【0138】

電源電位がEL駆動用TFT508のゲート電極に与えられると、EL駆動用TFT508のゲート電極とソース領域の電位が同じになり、ゲート電圧が0Vになる。よってEL駆動用TFT508はオフの状態となる。つまり、書き込み用ゲート信号線Ga1が書き込み用ゲート信号によって選択されたときからEL駆動用TFT508のゲート電極が保持していたデジタルビデオ信号は、EL駆動用TFT508のゲート電極に電源電位が与えられることで消去される。よって電源電位は有機EL素子510の画素電極に与えられなくなり、1ライン目の画素が有する有機EL素子510は全て非発光の状態になり、1ライン目の画素が表示を行わなくなる。

【0139】

そして消去用ゲート信号線Ge1の選択が終了すると、消去用ゲート信号線Ge2が選択され、消去用ゲート信号線Ge2に接続されている全ての画素(2ライン目の画素)の消去用TFT509がオンの状態になる。そして電源供給線V1〜Vxの電源電位が消去用TFT509を介してEL駆動用TFT508のゲート電極に与えられる。電源電位がEL駆動用TFT508のゲート電極に与えられると、EL駆動用TFT508はオフの状態となる。よって電源電位は有機EL素子510の画素電極に与えられなくなる。その結果2ライン目の画素が有する有機EL素子510は全て非発光の状態になり、2ライン目の画素が表示を行わない非表示の状態となる。

【0140】

そして順に、全ての消去用ゲート信号線に消去用ゲート信号が入力されていく。全ての消去用ゲート信号線Ge1〜Geyが選択され、全ての画素が保持している1ビット目のデジタルビデオ信号が消去されるまでの期間が消去期間Te1である。各ラインにおいて書き込み期間Teが開始されるタイミングはそれぞれ時間差を有している。

【0141】

なお、画素が表示を行わない期間を非表示期間Tdと呼ぶ。例えば1ライン目の画素だと、消去用ゲート信号線Ge1が選択されると同時に表示期間Tr1が終了し、非表示期間Td1が開始される。表示期間と同様に、各ラインの非表示期間が開始されるタイミングは異なっている。

【0142】

一方、全ての画素が保持している1ビット目のデジタルビデオ信号が消去される前、言い換えると消去期間Te1が終了する前に、画素が保持している1ビット目のデジタルビデオ信号の消去と並行して、再び書き込み用ゲート信号による書き込み用ゲート信号線Ga1の選択が行われる。そして1ライン目の画素に、2ビット目のデジタルビデオ信号が入力される。その結果、1ライン目の画素は再び表示を行うので、非表示期間Td1が終了する。

【0143】

書き込み期間Ta1が開始されてから、次に出現する書き込み期間(この場合書き込み期間Ta2)が開始されるまでの期間が表示期間Tr1である。

【0144】

次に表示期間Tr2が開始され、書き込み期間Ta2となる。そして同様に、順に全ての書き込み用ゲート信号線が選択され、2ビット目のデジタルビデオ信号が全ての画素に入力される。

【0145】

一方、全ての画素に2ビット目のデジタルビデオ信号が入力される前、言い換えると書き込み期間Ta2が終了する前に、画素への2ビット目のデジタルビデオ信号の入力と並行して、消去用ゲート信号による消去用ゲート信号線Ge1の選択が行われる。よって1ライン目の画素が有する有機EL素子は全て非発光の状態になり、1ライン目の画素が表示を行わなくなる。よって1ライン目の画素において表示期間Tr2は終了し、非表示期間Td2となる。

【0146】

そして順に、全ての消去用ゲート信号線Ge2〜Geyが選択され、全ての画素が保持している2ビット目のデジタルビデオ信号が消去される。全ての画素が保持している2ビット目のデジタルビデオ信号が消去されるまでの期間が消去期間Te2である。

【0147】

次に、表示期間Tr2が終了し、表示期間Tr3が開始される。そして同様に、順に全ての書き込み用ゲート信号線が選択され、3ビット目のデジタルビデオ信号が全ての画素に入力される。

【0148】

一方、全ての画素に3ビット目のデジタルビデオ信号が入力される前、言い換えると書き込み期間Ta3が終了する前に、画素への3ビット目のデジタルビデオ信号の入力と並行して、消去用ゲート信号による消去用ゲート信号線Ge1の選択が行われる。よって1ライン目の画素が有する有機EL素子は全て非発光の状態になり、1ライン目の画素が表示を行わなくなる。よって1ライン目の画素において表示期間Tr3は終了し、非表示期間Td3となる。

【0149】

そして順に、全ての消去用ゲート信号線Ge2〜Geyが選択され、全ての画素が保持している3ビット目のデジタルビデオ信号が消去される。全ての画素が保持している3ビット目のデジタルビデオ信号が消去されるまでの期間が消去期間Te3である。

【0150】

次に、表示期間Tr3が終了し、分割表示期間S1Trnが開始される。そして同様に、順に全ての書き込み用ゲート信号線が選択され、nビット目のデジタルビデオ信号が全ての画素に入力される。

【0151】

一方、全ての画素にnビット目のデジタルビデオ信号が入力される前、言い換えると書き込み期間Tanが終了する前に、画素へのnビット目のデジタルビデオ信号の入力と並行して、消去用ゲート信号による消去用ゲート信号線Ge1の選択が行われる。よって1ライン目の画素が有する有機EL素子は全て非発光の状態になり、1ライン目の画素が表示を行わなくなる。よって1ライン目の画素において表示期間Trnは終了し、非表示期間Td3となる。

【0152】

そして順に、全ての消去用ゲート信号線Ge2〜Geyが選択され、全ての画素が保持しているnビット目のデジタルビデオ信号が消去される。全ての画素が保持しているnビット目のデジタルビデオ信号が消去されるまでの期間が消去期間Tenである。

【0153】

上述した動作はmビット目のデジタルビデオ信号が画素に入力されるまで繰り返し行われ、表示期間Trと、分割表示期間STrと、非表示期間Tdとが繰り返し出現する。表示期間Tr1は、書き込み期間Ta1が開始されてから消去期間Te1が開始されるまでの期間である。また非表示期間Td1は、消去期間Te1が開始されてから次に出現する書き込み期間(この場合書き込み期間Ta2)が開始されるまでの期間である。そして表示期間Tr2、Tr3、…、Tr(m−1)と非表示期間Td2、Td3、…、Td(m−1)も、表示期間Tr1と非表示期間Td1と同様に、それぞれ書き込み期間Ta1、Ta2、…、Tamと消去期間Te1、Te2、…、Te(m−1)とによって、その期間が定められる。

【0154】

説明を簡便にするために、図9ではm=n−2の場合を例にとって示すが、本発明はこれに限定されないのは言うまでもない。本発明においてmは、1からnまでの値を任意に選択することが可能である。

【0155】

次に表示期間Trm〔n−2(以下、括弧内はm=n−2の場合を示す)〕が開始されると、m〔n−2〕ビット目のデジタルビデオ信号が1ライン目の画素に入力され、1ライン目の画素は表示期間Trm〔n−2〕となり表示を行う。そして次のビットのデジタルビデオ信号が入力されるまで、m〔n−2〕ビット目のデジタルビデオ信号は画素に保持される。

【0156】

そして次に表示期間Tr(m+1)〔n−1〕が開始され、(m+1)〔n−1〕ビット目のデジタルビデオ信号が1ライン目の画素に入力されると、画素に保持されていたm〔n−2〕ビット目のデジタルビデオ信号は、(m+1)〔n−1〕ビット目のデジタルビデオ信号に書き換えられる。そして1ライン目の画素は表示期間Tr(m+1)〔n−1〕となり、表示を行う。(m+1)〔n−1〕ビット目のデジタルビデオ信号は、次のビットのデジタルビデオ信号が入力されるまで画素に保持される。

【0157】

そして次に分割表示期間S1Trnが開始され、nビット目のデジタルビデオ信号が1ライン目の画素に入力されると、画素に保持されていた(m+1)〔n−1〕ビット目のデジタルビデオ信号は、nビット目のデジタルビデオ信号に書き換えられる。そして1ライン目の画素は表示期間Trnとなり、表示を行う。nビット目のデジタルビデオ信号は、次のフレーム期間のデジタルビデオ信号が入力されるまで画素に保持される。

【0158】

表示期間Trm〔n−2〕、…、Trnは、書き込み期間Tam〔n−2〕、…、Tanが開始されてから、その次に出現する書き込み期間が開始されるまでの期間である。

【0159】

全ての表示期間Tr1〜Trnが終了すると、1つの画像を表示することができる。本発明において、1つの画像が表示される期間を1フレーム期間(F)と呼ぶ。

【0160】

そして1フレーム期間終了後は、再び書き込み用ゲート信号線Ga1が書き込み用ゲート信号によって選択される。そして、次のフレーム期間の1ビット目のデジタルビデオ信号が画素に入力され、1ライン目の画素が再び表示期間Tr1となる。そして再び上述した動作を繰り返す。

【0161】

本実施例の駆動方法では、全ての書き込み期間の長さの和が1フレーム期間よりも短いことが重要である。また本実施例の駆動方法では、表示期間Trnが2つの分割表示期間S1TrnとS2Trnとに分けられている。よって表示期間の長さをTr1:Tr2:Tr3:…:Tr(n−1):2×Trn=20:21:22:…:2(n-2):2(n-1)とすることが必要である。この表示期間の組み合わせで1〜2n階調のうち所望の階調表示を行うことができる。

【0162】

1フレーム期間中に有機EL素子が発光した表示期間の長さの総和を求めることによって、当該フレーム期間におけるその画素の表示した階調がきまる。例えば、n=8のとき、全部の表示期間で画素が発光した場合の輝度を100%とすると、Tr1とTr2において画素が発光した場合には1%の輝度が表現でき、Tr3とTr5とTr8を選択した場合には60%の輝度が表現できる。

【0163】

mビット目のデジタルビデオ信号が画素に書き込まれる書き込み期間Tamは、表示期間Trmの長さよりも短いことが肝要である。よってビット数mの値は、1〜nのうち、書き込み期間Tamが表示期間Trmの長さよりも短くなるような値であることが必要である。

【0164】

また表示期間Tr1〜Trnは、どのような順序で出現させても良い。例えば1フレーム期間中において、Tr1の次にTr3、Tr5、Tr2、…という順序で表示期間を出現させることも可能である。ただし、表示期間Tr1〜Trnが互いに重ならない順序の方がより好ましい。また消去期間Te1〜Tenも、互いに重ならない順序の方がより好ましい。

【0165】

上記構成によって、二進コード法による時間分割駆動において顕著な、偽輪郭などの表示妨害が視認されるのを防ぐことができる。

【0166】

なお本実施例では、表示期間Trnを2つの分割表示期間S1TrnとS2Trnとに分割しているが、本実施例はこの構成に限定されない。分割する表示期間は1つでも複数でも良い。ただし上位ビットに対応する表示期間、言いかえると長さの長い表示期間から順に分割することが好ましい。また、表示期間の分割数は設計者が適宜選択可能であるが、どこまで分割するかは、表示装置の駆動速度と、要求される画像の表示品質とのバランスによって決めるのが好ましい。

【0167】

また同じビットのデジタルビデオ信号に対応した分割表示期間の長さは同じであることが望ましいが、本発明はこれに限定されない。分割表示期間の長さは必ずしも同じである必要はない。

【0168】

なお本実施例では、実施例1で示した駆動方法と異なり、有機EL素子が発光する期間を、書き込み期間より短くすることが可能である。そのため、1フレーム期間における表示期間の長さの総和の割合(デューティー比)が、書き込み期間の長さによってのみ決定されない。

【0169】

なお本実施例では、EL駆動用TFTのゲート電極にかかる電圧を保持するためにコンデンサを設ける構造としているが、コンデンサを省略することも可能である。EL駆動用TFTが、ゲート絶縁膜を介してゲート電極に重なるように設けられたLDD領域を有している場合、この重なり合った領域には一般的にゲート容量と呼ばれる寄生容量が形成される。このゲート容量をEL駆動用TFTのゲート電極にかかる電圧を保持するためのコンデンサとして積極的に用いても良い。

【0170】

このゲート容量の容量値は、上記ゲート電極とLDD領域とが重なり合った面積によって変化するため、その重なり合った領域に含まれるLDD領域の長さによって決まる。

【0171】

(実施例3)

本実施例では、図4に示した画素部を駆動させるために用いるソース信号線駆動回路と、ゲート信号線駆動回路の詳しい構成について説明する。

【0172】

図10に本実施例のELディスプレイの駆動回路のブロック図を示す。図10(A)はソース信号線駆動回路601であり、シフトレジスタ602、ラッチ(A)603、ラッチ(B)604を有している。

【0173】

ソース信号線駆動回路601において、シフトレジスタ602にクロック信号(CLK)およびスタートパルス(SP)が入力される。シフトレジスタ602は、これらのクロック信号(CLK)およびスタートパルス(SP)に基づきタイミング信号を順に発生させ、バッファ等(図示せず)を通して後段の回路へタイミング信号を順次供給する。

【0174】

シフトレジスタ602からのタイミング信号は、バッファ等によって緩衝増幅される。タイミング信号が供給される配線には、多くの回路あるいは素子が接続されているために負荷容量(寄生容量)が大きい。この負荷容量が大きいために生ずるタイミング信号の立ち上がりまたは立ち下がりの”鈍り”を防ぐために、このバッファが設けられる。なおバッファは必ずしも設ける必要はない。

【0175】

バッファによって緩衝増幅されたタイミング信号は、ラッチ(A)603に供給される。ラッチ(A)603は、nビットデジタルビデオ信号を処理する複数のステージのラッチを有している。ラッチ(A)603は、前記タイミング信号が入力されると、ソース信号線駆動回路601の外部から供給されるnビットのデジタルビデオ信号を順次取り込み、保持する。

【0176】

なお、ラッチ(A)603にデジタルビデオ信号を取り込む際に、ラッチ(A)603が有する複数のステージのラッチに、順にデジタルビデオ信号を入力しても良い。しかし本発明はこの構成に限定されない。ラッチ(A)603が有する複数のステージのラッチをいくつかのグループに分け、各グループごとに並行して同時にデジタルビデオ信号を入力する、いわゆる分割駆動を行っても良い。なおこのときのグループの数を分割数と呼ぶ。例えば4つのステージごとにラッチをグループに分けた場合、4分割で分割駆動すると言う。

【0177】

ラッチ(A)603の全てのステージのラッチにデジタルビデオ信号の書き込みが一通り終了するまでの時間を、ライン期間と呼ぶ。実際には、上記ライン期間に水平帰線期間が加えられた期間をライン期間に含むことがある。

【0178】

1ライン期間が終了すると、ラッチ(B)604にラッチシグナル(Latch Signal)が供給される。この瞬間、ラッチ(A)603に書き込まれ保持されているデジタルビデオ信号は、ラッチ(B)604に一斉に送出され、ラッチ(B)604の全ステージのラッチに書き込まれ、保持される。

【0179】

デジタルビデオ信号をラッチ(B)604に送出し終えたラッチ(A)603には、シフトレジスタ602からのタイミング信号に基づき、デジタルビデオ信号の書き込みが順次行われる。

【0180】

この2順目の1ライン期間中には、ラッチ(B)604に書き込まれ、保持されているデジタルビデオ信号がソース信号線に入力される。

【0181】

図10(B)はゲート信号線駆動回路の構成を示すブロック図である。

【0182】

ゲート信号線駆動回路605は、それぞれシフトレジスタ606、バッファ607を有している。また場合によってはレベルシフトを有していても良い。

【0183】

ゲート信号線駆動回路605において、シフトレジスタ606からのタイミング信号がバッファ607に供給され、対応するゲート信号線に供給される。ゲート信号線には、1ライン分の画素のスイッチング用TFTのゲート電極が接続されている。そして、1ライン分の画素のスイッチング用TFTを一斉にONにしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

【0184】

(実施例4)

本実施例では、本発明の駆動方法を用いるELディスプレイを作製した例について、図11、図12を用いて説明する。

【0185】

図11(A)は本発明の駆動方法を用いたELディスプレイのTFT基板の上面図を示している。なお本明細書においてTFT基板とは、画素部が設けられている基板を意味する。

【0186】

基板4001上に、画素部4002と、ソース信号線駆動回路4003と、第1のゲート信号線駆動回路4004aと、第2のゲート信号線駆動回路4004bとが設けられている。なお本発明においてソース信号線駆動回路とゲート信号線駆動回路の数は図11(A)に示した数に限定されない。ソース信号線駆動回路とゲート信号線駆動回路の数は、設計者が適宜設定することが可能である。また、本実施例ではソース信号線駆動回路とゲート信号線駆動回路とをTFT基板上に設けているが、本発明はこの構成に限定されない。TFT基板とは別の基板上に設けたソース信号線駆動回路とゲート信号線駆動回路とを、FPC等により画素部と電気的に接続するようにしても良い。

【0187】

4005は引き回し配線である。引き回し配線4005は、基板4001の外部に設けられたIC等にFPC4006を介して接続されている。

【0188】

引き回し配線4005の拡大図を図11(B)に示す。4100はR用引き回し配線、4101はG用引き回し配線、4102はB用引き回し配線である。

【0189】

図12(A)は、図11(A)に示したTFT基板をシーリング材によって封止することによって形成されたELディスプレイの上面図であり、図12(B)は、図12(A)のA−A’における断面図、図12(C)は図12(A)のB−B’における断面図である。なお図11において既に示したものは、同じ符号を用いて示す。

【0190】

基板4001上に設けられた画素部4002と、ソース信号線駆動回路4003と、第1及び第2のゲート信号線駆動回路4004a、bとを囲むようにして、シール材4009が設けられている。また画素部4002と、ソース信号線駆動回路4003と、第1及び第2のゲート信号線駆動回路4004a、bとの上にシーリング材4008が設けられている。よって画素部4002と、ソース信号線駆動回路4003と、第1及び第2のゲート信号線駆動回路4004a、bとは、基板4001とシール材4009とシーリング材4008とによって、充填材4210で密封されている。

【0191】

また基板4001上に設けられた画素部4002と、ソース信号線駆動回路4003と、第1及び第2のゲート信号線駆動回路4004a、bとは、複数のTFTを有している。図12(B)では代表的に、下地膜4010上に形成された、ソース信号線駆動回路4003に含まれる駆動TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを図示する)4201及び画素部4002に含まれるEL駆動用TFT(有機EL素子への電流を制御するTFT)4202を図示した。

【0192】

本実施例では、駆動TFT4201には公知の方法で作製されたpチャネル型TFTまたはnチャネル型TFTが用いられ、EL駆動用TFT4202には公知の方法で作製されたpチャネル型TFTが用いられる。また、画素部4002にはEL駆動用TFT4202のゲートに接続された保持容量(図示せず)が設けられる。

【0193】

駆動TFT4201及びEL駆動用TFT4202上には層間絶縁膜(平坦化膜)4304が形成され、その上にEL駆動用TFT4202のドレインと電気的に接続する画素電極(陽極)4203が形成される。画素電極4203としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したものを用いても良い。

【0194】

そして、画素電極4203の上には絶縁膜4302が形成され、絶縁膜4302は画素電極4203の上に開口部が形成されている。この開口部において、画素電極4203の上にはEL(エレクトロルミネッセンス)層4204が形成される。EL層4204は公知の有機EL材料を用いることができる。また、有機EL材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

【0195】

EL層4204の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また、EL層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

【0196】

EL層4204の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極4205が形成される。また、陰極4205とEL層4204の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、EL層4204を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極4205を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。そして陰極4205は所定の電圧が与えられている。

【0197】

以上のようにして、画素電極(陽極)4203、EL層4204及び陰極4205からなる有機EL素子4303が形成される。そして有機EL素子4303を覆うように、絶縁膜4302上に保護膜4303が形成されている。保護膜4303は、有機EL素子4303に酸素や水分等が入り込むのを防ぐのに効果的である。

【0198】

4005aは電源供給線に接続された引き回し配線であり、EL駆動用TFT4202のソース領域に電気的に接続されている。引き回し配線4005aはシール材4009と基板4001との間を通り、異方導電性フィルム4300を介してFPC4006が有するFPC用配線4301に電気的に接続される。

【0199】

シーリング材4008としては、ガラス材、金属材(代表的にはステンレス材)、セラミックス材、プラスチック材(プラスチックフィルムも含む)を用いることができる。プラスチック材としては、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

【0200】

但し、有機EL素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

【0201】

また、充填材4210としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施例では充填材として窒素を用いた。

【0202】

また充填材4103を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておくために、シーリング材4008の基板4001側の面に凹部4007を設けて吸湿性物質または酸素を吸着しうる物質4207を配置する。そして、吸湿性物質または酸素を吸着しうる物質4207が飛び散らないように、凹部カバー材4208によって吸湿性物質または酸素を吸着しうる物質4207は凹部4007に保持されている。なお凹部カバー材4208は目の細かいメッシュ状になっており、空気や水分は通し、吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207を設けることで、有機EL素子4303の劣化を抑制できる。

【0203】

図12(C)に示すように、画素電極4203が形成されると同時に、引き回し配線4005a上に接するように導電性膜4203aが形成される。

【0204】

また、異方導電性フィルム4300は導電性フィラー4300aを有している。基板4001とFPC4006とを熱圧着することで、基板4001上の導電性膜4203aとFPC4006上のFPC用配線4301とが、導電性フィラー4300aによって電気的に接続される。

【0205】

なお、本実施例は、実施例1〜3と自由に組み合わせて実施することが可能である。

【0206】

(実施例5)

本実施例では、本発明のEL表示装置において、同一基板上に画素部と、画素部の周辺に設ける駆動回路のTFT(nチャネル型TFT及びpチャネル型TFT)を同時に作製する方法について詳細に図13〜図16を用いて説明する。

【0207】

まず、本実施例ではコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスからなる基板300を用いる。なお、基板300としては、透光性を有する基板であれば限定されず、石英基板を用いても良い。また、本実施例の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。

【0208】

次いで、基板300上に酸化珪素膜、窒化珪素膜または酸化窒化珪素膜などの絶縁膜から成る下地膜301を形成する。本実施例では下地膜301として2層構造を用いるが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。下地膜301の一層目としては、プラズマCVD法を用い、SiH4、NH3、及びN2Oを反応ガスとして成膜される酸化窒化珪素膜301aを10〜200nm(好ましくは50〜100nm)形成する。本実施例では、膜厚50nmの酸化窒化珪素膜301a(組成比Si=32%、O=27%、N=24%、H=17%)を形成した。次いで、下地膜301のニ層目としては、プラズマCVD法を用い、SiH4、及びN2Oを反応ガスとして成膜される酸化窒化珪素膜301bを50〜200nm(好ましくは100〜150nm)の厚さに積層形成する。本実施例では、膜厚100nmの酸化窒化珪素膜301b(組成比Si=32%、O=59%、N=7%、H=2%)を形成した。

【0209】

次いで、下地膜上に半導体層302〜305を形成する。半導体層302〜305は、非晶質構造を有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜した後、公知の結晶化処理(レーザー結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜を所望の形状にパターニングして形成する。この半導体層302〜305の厚さは25〜80nm(好ましくは30〜60nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくは珪素(シリコン)またはシリコンゲルマニウム(SiXGe1-X(X=0.0001〜0.02))合金などで形成すると良い。本実施例では、プラズマCVD法を用い、55nmの非晶質珪素膜を成膜した後、ニッケルを含む溶液を非晶質珪素膜上に保持させた。この非晶質珪素膜に脱水素化(500℃、1時間)を行った後、熱結晶化(550℃、4時間)を行い、さらに結晶化を改善するためのレーザーアニ―ル処理を行って結晶質珪素膜を形成した。そして、この結晶質珪素膜をフォトリソグラフィ法を用いたパターニング処理によって、半導体層302〜305を形成した。

【0210】

また、半導体層302〜305を形成した後、TFTのしきい値を制御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。

【0211】

また、レーザー結晶化法で結晶質半導体膜を作製する場合には、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO4レーザーを用いることができる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宣選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数300Hzとし、レーザーエネルギー密度を100〜400mJ/cm2(代表的には200〜300mJ/cm2)とする。また、YAGレーザーを用いる場合にはその第2高調波を用いパルス発振周波数30〜300kHzとし、レーザーエネルギー密度を300〜600mJ/cm2(代表的には350〜500mJ/cm2)とすると良い。そして幅100〜1000μm、例えば400μmで線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を50〜90%として行えばよい。

【0212】

次いで、半導体層302〜305を覆うゲート絶縁膜306を形成する。ゲート絶縁膜306はプラズマCVD法またはスパッタ法を用い、厚さを40〜150nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により110nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成した。勿論、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

【0213】

また、酸化珪素膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製される酸化珪素膜は、その後400〜500℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0214】

次いで、図13(A)に示すように、ゲート絶縁膜306上に膜厚20〜100nmの第1の導電膜307と、膜厚100〜400nmの第2の導電膜308とを積層形成する。本実施例では、膜厚30nmのTaN膜からなる第1の導電膜307と、膜厚370nmのW膜からなる第2の導電膜308を積層形成した。TaN膜はスパッタ法で形成し、Taのターゲットを用い、窒素を含む雰囲気内でスパッタした。また、W膜は、Wのターゲットを用いたスパッタ法で形成した。その他に6フッ化タングステン(WF6)を用いる熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従って、本実施例では、高純度のW(純度99.9999%)のターゲットを用いたスパッタ法で、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9〜20μΩcmを実現することができた。

【0215】

なお、本実施例では、第1の導電膜307をTaN、第2の導電膜308をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶珪素膜に代表される半導体膜を用いてもよい。また、Ag、Pd、Cuからなる合金を用いてもよい。また、第1の導電膜をタンタル(Ta)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化チタン(TiN)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をAl膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をCu膜とする組み合わせとしてもよい。

【0216】

次に、図13(B)に示すようにフォトリソグラフィ法を用いてレジストからなるマスク309〜312を形成し、電極及び配線を形成するための第1のエッチング処理を行う。第1のエッチング処理では第1及び第2のエッチング条件で行う。本実施例では第1のエッチング条件として、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を25/25/10(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行った。ここでは、松下電器産業(株)製のICPを用いたドライエッチング装置(Model E645−□ICP)を用いた。基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパー形状とする。第1のエッチング条件でのWに対するエッチング速度は200.39nm/min、TaNに対するエッチング速度は80.32nm/minであり、TaNに対するWの選択比は約2.5である。また、この第1のエッチング条件によって、Wのテーパー角は、約26°となる。

【0217】

この後、図13(B)に示すようにレジストからなるマスク309〜312を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF4とCl2とを用い、それぞれのガス流量比を30/30(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した第2のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。第2のエッチング条件でのWに対するエッチング速度は58.97nm/min、TaNに対するエッチング速度は66.43nm/minである。なお、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。

【0218】

上記第1のエッチング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15〜45°とすればよい。こうして、第1のエッチング処理により第1の導電層と第2の導電層から成る第1の形状の導電層314〜317(第1の導電層314a〜317aと第2の導電層314b〜317b)を形成する。319はゲート絶縁膜であり、第1の形状の導電層314〜317で覆われない領域は20〜50nm程度エッチングされ薄くなった領域が形成される。

【0219】

そして、レジストからなるマスクを除去せずに第1のドーピング処理を行い、半導体層にn型を付与する不純物元素を添加する。(図13(B))ドーピング処理はイオンドープ法、若しくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を1×1013〜5×1015atoms/cm2とし、加速電圧を60〜100keVとして行う。本実施例ではドーズ量を1.5×1015atoms/cm2とし、加速電圧を80keVとして行った。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いた。この場合、導電層314〜317がn型を付与する不純物元素に対するマスクとなり、自己整合的に高濃度不純物領域118〜121が形成される。高濃度不純物領域320〜323には1×1020〜1×1021atoms/cm3の濃度範囲でn型を付与する不純物元素を添加する。

【0220】

次いで、図13(C)に示すようにレジストからなるマスクを除去せずに第2のエッチング処理を行う。ここでは、エッチング用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を20/20/20(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。第2のエッチング処理でのWに対するエッチング速度は124.62nm/min、TaNに対するエッチング速度は20.67nm/minであり、TaNに対するWの選択比は6.05である。従って、W膜が選択的にエッチングされる。この第2のエッチングによりWのテーパー角は70°となった。この第2のエッチング処理により第2の導電層324b〜327bを形成する。一方、第1の導電層314a〜317aは、ほとんどエッチングされず、第1の導電層324a〜327aを形成する。

【0221】

次いで、第2のドーピング処理を行う。ドーピングは第2の導電層324b〜327bを不純物元素に対するマスクとして用い、第1の導電層のテーパー部下方の半導体層に不純物元素が添加されるようにドーピングする。本実施例では、不純物元素としてP(リン)を用い、ドーズ量1.5×1014、電流密度0.5μA、加速電圧90keVにてプラズマドーピングを行った。こうして、第1の導電層と重なる低濃度不純物領域329〜332を自己整合的に形成する。この低濃度不純物領域329〜332へ添加されたリン(P)の濃度は、1×1017〜5×1018atoms/cm3であり、且つ、第1の導電層のテーパー部の膜厚に従って緩やかな濃度勾配を有している。なお、第1の導電層のテーパー部と重なる半導体層において、第1の導電層のテーパー部の端部から内側に向かって若干、不純物濃度が低くなっているものの、ほぼ同程度の濃度である。また、高濃度の不純物元素が添加された高濃度不純物領域333〜336を形成する。

【0222】

次いで、図14(B)に示すようにレジストからなるマスクを除去してからフォトリソグラフィー法を用いて、第3のエッチング処理を行う。この第3のエッチング処理では第1の導電層のテーパー部を部分的にエッチングして、第2の導電層と重なる形状にするために行われる。ただし、第3のエッチングを行わない領域には、図14(B)に示すようにレジストからなるマスク338を形成する。

【0223】

第3のエッチング処理におけるエッチング条件は、エッチングガスとしてCl2とSF6とを用い、それぞれのガス流量比を10/50(sccm)として第1及び第2のエッチングと同様にICPエッチング法を用いて行う。なお、第3のエッチング処理でのTaNに対するエッチング速度は、111.2nm/minであり、ゲート絶縁膜に対するエッチング速度は、12.8nm/minである。

【0224】

本実施例では、1.3Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行った。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。以上により、第1の導電層340a〜342aが形成される。

【0225】

上記第3のエッチングによって、第1の導電層340a〜342aと重ならない不純物領域(LDD領域)343〜345が形成される。なお、不純物領域(GOLD領域)346は、第1の導電層324aと重なったままである。

【0226】

また、第1の導電層324aと第2の導電層324bとで形成された電極は、最終的に駆動回路のnチャネル型TFTのゲート電極となり、また、第1の導電層340aと第2の導電層340bとで形成された電極は、最終的に駆動回路のpチャネル型TFTのゲート電極となる。

【0227】

同様に、第1の導電層341aと第2の導電層341bとで形成された電極は、最終的に画素部のnチャネル型TFTのゲート電極となり、第1の導電層342aと第2の導電層342bとで形成された電極は、最終的に画素部のpチャネル型TFTのゲート電極となる。

【0228】

このようにして、本実施例は、第1の導電層340a〜342aと重ならない不純物領域(LDD領域)343〜345と、第1の導電層324aと重なる不純物領域(GOLD領域)346を同時に形成することができ、TFT特性に応じた作り分けが可能となる。

【0229】

次にゲート絶縁膜319をエッチング処理する。ここでのエッチング処理は、エッチングガスにCHF3を用い、反応性イオンエッチング法(RIE法)を用いて行う。本実施例では、チャンバー圧力6.7Pa、RF電力800W、CHF3ガス流量35sccmで第3のエッチング処理を行った。

【0230】

これにより、高濃度不純物領域333〜336の一部は露呈し、絶縁膜356a〜356dが形成される。

【0231】

次いで、レジストからなるマスクを除去した後、新たにレジストからなるマスク348、349を形成して第3のドーピング処理を行う。この第3のドーピング処理により、pチャネル型TFTの活性層となる半導体層に前記一導電型(n型)とは逆の導電型(p型)を付与する不純物元素が添加された不純物領域350〜353を形成する。(図14(C))第1の導電層340aおよび342aを不純物元素に対するマスクとして用い、p型を付与する不純物元素を添加して自己整合的に不純物領域を形成する。

【0232】

本実施例では、不純物領域350〜353はジボラン(B2H6)を用いたイオンドープ法で形成する。なお、この第3のドーピング処理の際には、nチャネル型TFTを形成する半導体層はレジストからなるマスク348、349で覆われている。第1のドーピング処理及び第2のドーピング処理によって、不純物領域350〜353にはそれぞれ異なる濃度でリンが添加されているが、そのいずれの領域においてもp型を付与する不純物元素の濃度が2×1020〜2×1021atoms/cm3となるようにドーピング処理することにより、pチャネル型TFTのソース領域およびドレイン領域として機能するために何ら問題は生じない。

【0233】

以上までの工程でそれぞれの半導体層に不純物領域が形成される。

【0234】

次いで、レジストからなるマスク348、349を除去して第1の層間絶縁膜357を形成する。この第1の層間絶縁膜357としては、プラズマCVD法またはスパッタ法を用い、厚さを100〜200nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚150nmの酸化窒化珪素膜を形成した。勿論、第1の層間絶縁膜357は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

【0235】

次いで、図15(A)に示すように、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程はファーネスアニール炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜550℃で行えばよく、本実施例では550℃、4時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

【0236】

なお、本実施例では、上記活性化処理と同時に、結晶化の際に触媒として使用したニッケルが高濃度のリンを含む不純物領域(334〜336、350、351)にゲッタリングされ、主にチャネル形成領域となる半導体層中のニッケル濃度が低減される。このようにして作製したチャネル形成領域を有するTFTはオフ電流値が下がり、結晶性が良いことから高い電界効果移動度が得られ、良好な特性を達成することができる。

【0237】

また、第1の層間絶縁膜を形成する前に活性化処理を行っても良い。ただし、用いた配線材料が熱に弱い場合には、本実施例のように配線等を保護するため層間絶縁膜(シリコンを主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で活性化処理を行うことが好ましい。

【0238】

その他、活性化処理を行った後でドーピング処理を行い、第1の層間絶縁膜を形成させても良い。

【0239】

さらに、3〜100%の水素を含む雰囲気中で、300〜550℃で1〜12時間の熱処理を行い、半導体層を水素化する工程を行う。本実施例では水素を約3%の含む窒素雰囲気中で410℃、1時間の熱処理を行った。この工程は層間絶縁膜に含まれる水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

【0240】

また、活性化処理としてレーザーアニール法を用いる場合には、上記水素化を行った後、エキシマレーザーやYAGレーザー等のレーザー光を照射することが望ましい。

【0241】

次いで、図15(B)に示すように第1の層間絶縁膜357上に有機絶縁物材料から成る第2の層間絶縁膜358を形成する。本実施例では膜厚1.6μmのアクリル樹脂膜を形成した。次いで、各不純物領域333、335、350、351に達するコンタクトホールを形成するためのパターニングを行う。

【0242】

第2の層間絶縁膜358としては、珪素を含む絶縁材料や有機樹脂からなる膜を用いる。珪素を含む絶縁材料としては、酸化珪素、窒化珪素、酸化窒化珪素を用いることができ、また有機樹脂としては、ポリイミド、ポリアミド、アクリル、BCB(ベンゾシクロブテン)などを用いることができる。

【0243】

本実施例では、プラズマCVD法により形成された酸化窒化珪素膜を形成した。なお、酸化窒化珪素膜の膜厚として好ましくは1〜5μm(さらに好ましくは2〜4μm)とすればよい。酸化窒化珪素膜は、膜自身に含まれる水分が少ないために有機EL素子の劣化を抑える上で有効である。

【0244】

また、コンタクトホールの形成には、ドライエッチングまたはウエットエッチングを用いることができるが、エッチング時における静電破壊の問題を考えると、ウエットエッチング法を用いるのが望ましい。

【0245】

さらに、ここでのコンタクトホールの形成において、第1層間絶縁膜及び第2層間絶縁膜を同時にエッチングするため、コンタクトホールの形状を考えると第2層間絶縁膜を形成する材料は、第1層間絶縁膜を形成する材料よりもエッチング速度の速いものを用いるのが好ましい。

【0246】

そして、各不純物領域333、335、350、351とそれぞれ電気的に接続する配線359〜366を形成する。そして、膜厚50nmのTi膜と、膜厚500nmの合金膜(AlとTiとの合金膜)との積層膜をパターニングして形成するが、他の導電膜を用いても良い。

【0247】

次いで、その上に透明導電膜を80〜120nmの厚さで形成し、パターニングすることによって透明電極367を形成する。(図15(B))

【0248】

なお、本実施例では、透明電極として酸化インジウム・スズ(ITO)膜や酸化インジウムに2〜20[%]の酸化亜鉛(ZnO)を混合した透明導電膜を用いる。

【0249】

また、透明電極367は、ドレイン配線365と接して重ねて形成することによってEL駆動用TFTのドレイン領域と電気的な接続が形成される。

【0250】

次に、図16に示すように、珪素を含む絶縁膜(本実施例では酸化珪素膜)を500[nm]の厚さに形成し、透明電極367に対応する位置に開口部を形成して、バンクとして機能する第3の層間絶縁膜368を形成する。開口部を形成する際、ウエットエッチング法を用いることで容易にテーパー形状の側壁とすることが出来る。開口部の側壁が十分になだらかでないと段差に起因するEL層の劣化が顕著な問題となってしまうため、注意が必要である。

【0251】

なお、本実施例においては、第3の層間絶縁膜368として酸化珪素でなる膜を用いているが、場合によっては、ポリイミド、ポリアミド、アクリル、BCB(ベンゾシクロブテン)といった有機樹脂膜を用いることもできる。

【0252】

次に、図16で示すようにEL層369を蒸着法により形成し、更に蒸着法により陰極(MgAg電極)370および保護電極371を形成する。このときEL層369及び陰極370を形成するに先立って透明電極367に対して熱処理を施し、水分を完全に除去しておくことが望ましい。なお、本実施例では有機EL素子の陰極としてMgAg電極を用いるが、公知の他の材料であっても良い。

【0253】

なお、EL層369としては、公知の材料を用いることができる。本実施例では正孔輸送層(Hole transporting layer)及び発光層(Emitting layer)でなる2層構造をEL層とするが、正孔注入層、電子注入層若しくは電子輸送層のいずれかを設ける場合もある。このように組み合わせは既に様々な例が報告されており、そのいずれの構成を用いても構わない。

【0254】

本実施例では正孔輸送層としてポリフェニレンビニレンを蒸着法により形成する。また、発光層としては、ポリビニルカルバゾールに1,3,4−オキサジアゾール誘導体のPBDを30〜40%分子分散させたものを蒸着法により形成し、緑色の発光中心としてクマリン6を約1%添加している。

【0255】

また、保護電極371でもEL層369を水分や酸素から保護することは可能であるが、さらに好ましくはパッシベーション膜372を設けると良い。本実施例ではパッシベーション膜372として300nm厚の窒化珪素膜を設ける。このパッシベーション膜も保護電極371の後に大気解放しないで連続的に形成しても構わない。

【0256】

また、保護電極371は陰極370の劣化を防ぐために設けられ、アルミニウムを主成分とする金属膜が代表的である。勿論、他の材料でも良い。また、EL層369、陰極370は非常に水分に弱いので、保護電極371までを大気解放しないで連続的に形成し、外気からEL層を保護することが望ましい。

【0257】

なお、EL層369の膜厚は10〜400[nm](典型的には60〜150[nm])、陰極370の厚さは80〜200[nm](典型的には100〜150[nm])とすれば良い。

【0258】

こうして図16に示すような構造のEL表示装置が完成する。なお、本実施例におけるEL表示装置の作成工程においては、回路の構成および工程の関係上、ゲート電極を形成している材料であるTa、Wによってソース信号線を形成し、ソース、ドレイン電極を形成している配線材料であるAlによってゲート信号線を形成しているが、異なる材料を用いても良い。

【0259】

また、nチャネル型TFT701及びpチャネル型TFT702を有する駆動回路706と、スイッチング用TFT703及びEL駆動用TFT704を有する画素部707を同一基板上に形成することができる。

【0260】

駆動回路706のnチャネル型TFT701はチャネル形成領域333、ゲート電極の一部を構成する第1の導電層324aと重なる低濃度不純物領域329(GOLD領域)とソース領域またはドレイン領域として機能する高濃度不純物領域333を有している。pチャネル型TFT702にはチャネル形成領域373、ゲート電極の一部を構成する第1の導電層340aと重ならない不純物領域343、ソース領域またはドレイン領域として機能する不純物領域350および352を有している。

【0261】

画素部707のスイッチング用TFT703にはチャネル形成領域374、ゲート電極を形成する第1の導電層341aと重ならず、ゲート電極の外側に形成される低濃度不純物領域344(LDD領域)とソース領域またはドレイン領域として機能する高濃度不純物領域335を有している。

【0262】

画素部707のEL駆動用TFT704にはチャネル形成領域375、ソース領域またはドレイン領域として機能する高濃度不純物領域351および353を有している。

【0263】

なお、本実施例は、実施例1〜4と自由に組み合わせて実施することが可能である。

【0264】

(実施例6)

本発明を用いて駆動するELディスプレイは、自発光型であるため液晶表示装置に比べて明るい場所での視認性に優れ、しかも視野角が広い。従って、様々な電子機器の表示部に用いることができる。例えば、TV放送等を大画面で鑑賞するには対角30インチ以上(典型的には40インチ以上)のEL表示装置(ELディスプレイを筐体に組み込んだ電気光学装置)の表示部として本発明の駆動方法を用いたELディスプレイを用いるとよい。

【0265】

なお、ELディスプレイには、パソコン用ディスプレイ、TV放送受信用ディスプレイ、広告表示用ディスプレイ等の全ての情報表示用ディスプレイが含まれる。また、その他にも様々な電子機器の表示部として本発明の駆動方法を用いたELディスプレイを用いることができる。

【0266】

その様な本発明を用いた電子機器としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。特に、斜め方向から見ることの多い携帯情報端末は視野角の広さが重要視されるため、ELディスプレイを用いることが望ましい。それら電子機器の具体例を図17、図18に示す。

【0267】

図17(A)はEL表示装置であり、筐体2001、支持台2002、表示部2003等を含む。本発明の駆動方法を用いたELディスプレイは表示部2003に用いることができる。ELディスプレイは自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることができる。

【0268】

図17(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。本発明の駆動方法を用いたELディスプレイは表示部2102に用いることができる。

【0269】

図17(C)は頭部取り付け型の電気光学装置の一部(右片側)であり、本体2201、信号ケーブル2202、頭部固定バンド2203、スクリーン部2204、光学系2205、表示部2206等を含む。本発明の駆動方法を用いたELディスプレイは表示部2206に用いることができる。

【0270】

図17(D)は記録媒体を備えた画像再生装置(具体的にはDVD再生装置)であり、本体2301、記録媒体(DVD等)2302、操作スイッチ2303、表示部(a)2304、表示部(b)2305等を含む。表示部(a)2304は主として画像情報を表示し、表示部(b)2305は主として文字情報を表示するが、本発明の駆動方法を用いたELディスプレイはこれら表示部(a)、(b)2304、2305に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

【0271】

図17(E)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2401、表示部2402、アーム部2403を含む。本発明の駆動方法を用いたELディスプレイは表示部2402に用いることができる。

【0272】