JP4034122B2 - 発光装置及び素子基板 - Google Patents

発光装置及び素子基板 Download PDFInfo

- Publication number

- JP4034122B2 JP4034122B2 JP2002160318A JP2002160318A JP4034122B2 JP 4034122 B2 JP4034122 B2 JP 4034122B2 JP 2002160318 A JP2002160318 A JP 2002160318A JP 2002160318 A JP2002160318 A JP 2002160318A JP 4034122 B2 JP4034122 B2 JP 4034122B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- transistor

- wiring

- drain

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000000758 substrate Substances 0.000 title claims description 30

- 239000003990 capacitor Substances 0.000 claims description 80

- 239000012535 impurity Substances 0.000 description 72

- 239000010408 film Substances 0.000 description 59

- 238000003860 storage Methods 0.000 description 40

- 239000010410 layer Substances 0.000 description 39

- 238000010586 diagram Methods 0.000 description 28

- 230000015572 biosynthetic process Effects 0.000 description 26

- 239000000463 material Substances 0.000 description 16

- 238000005070 sampling Methods 0.000 description 13

- 238000000034 method Methods 0.000 description 12

- 239000000126 substance Substances 0.000 description 12

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- 229910052760 oxygen Inorganic materials 0.000 description 9

- 230000005540 biological transmission Effects 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 5

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 239000000945 filler Substances 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 239000003566 sealing material Substances 0.000 description 4

- 206010047571 Visual impairment Diseases 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 239000004973 liquid crystal related substance Substances 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- 229920002799 BoPET Polymers 0.000 description 2

- 239000005041 Mylar™ Substances 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 239000011231 conductive filler Substances 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 230000005283 ground state Effects 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 238000004020 luminiscence type Methods 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920006267 polyester film Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 239000000178 monomer Substances 0.000 description 1

- 239000002985 plastic film Substances 0.000 description 1

- 229920006255 plastic film Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3283—Details of drivers for data electrodes in which the data driver supplies a variable data current for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0417—Special arrangements specific to the use of low carrier mobility technology

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

Description

【発明の属する技術分野】

本発明は、電流を発光素子に供給するための手段と発光素子とが、複数の各画素に備えられた発光装置及び該発光装置の駆動方法に関する。なお発光装置とは、発光素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに本発明は、該発光装置を作製する過程における、発光素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、電流を発光素子に供給するための手段を複数の各画素に備える。

【0002】

【従来の技術】

発光素子は自ら発光するため視認性が高く、液晶表示装置(LCD)で必要なバックライトが要らず薄型化に最適であると共に、視野角にも制限が無い。そのため近年、発光素子を用いた発光装置は、CRTやLCDに代わる表示装置として注目されている。

【0003】

なお、本明細書において発光素子は、電流または電圧によって輝度が制御される素子を意味しており、OLED(Organic Light Emitting Diode)や、FED(Field Emission Display)に用いられているMIM型の電子源素子(電子放出素子)等を含んでいる。

【0004】

発光素子の1つであるOLED(Organic Light Emitting Diode)は、電場を加えることで発生するルミネッセンス(Electroluminescence)が得られる電界発光材料を含む層(以下、電界発光層と記す)と、陽極層と、陰極層とを有している。電界発光層は陽極と陰極の間に設けられており、単層または複数の層で構成されている。これらの層の中に無機化合物を含んでいる場合もある。電界発光層におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)とが含まれる。

【0005】

次に、一般的な発光装置の画素の構成とその駆動について簡単に説明する。図19に示した画素は、TFT80、81と、保持容量82と、発光素子83とを有している。

【0006】

TFT80は、ゲートが走査線85に接続されており、ソースとドレインが一方は信号線84に、もう一方はTFT81のゲートに接続されている。TFT81は、ソースが端子86に接続されており、ドレインが発光素子83の陽極に接続されている。発光素子83の陰極は端子87に接続されている。保持容量82はTFT81のゲートとソース間の電圧を保持するように設けられている。また、端子86、87には、電源からそれぞれ所定の電圧が印加されており、互いに電圧差を有している。

【0007】

なお本明細書において電圧とは、特に記載のない限りグラウンドとの電位差を意味する。

【0008】

走査線85の電圧によりTFT80がオンになると、信号線84に入力されたビデオ信号の電圧がTFT81のゲートに入力される。この入力されたビデオ信号の電圧に従って、TFT81のゲート電圧(ゲートとソース間の電圧差)が定まる。そして、該ゲート電圧によって流れるTFT81のドレイン電流は、発光素子83に供給され、発光素子83は供給された電流によって発光する。

【0009】

ところで、ポリシリコンで形成されたTFTは、アモルファスシリコンで形成されたTFTよりも電界効果移動度が高く、オン電流が大きいので、発光装置のトランジスタとしてより適している。しかし、ポリシリコンを用いてTFTを形成しても、その電気的特性は所詮単結晶シリコン基板に形成されるMOSトランジスタの特性に匹敵するものではない。例えば、電界効果移動度は単結晶シリコンの1/10以下である。また、ポリシリコンを用いたTFTは、結晶粒界に形成される欠陥に起因して、その特性にばらつきが生じやすいといった問題点を有している。

【0010】

図19に示した画素において、TFT81の閾値やオン電流等の特性が画素毎にばらつくと、ビデオ信号の電圧が同じであってもTFT81のドレイン電流の大きさが画素間で異なり、結果的に発光素子83の輝度がばらついてしまうこととなる。

【0011】

そこで、上述した問題を回避するために、TFTの特性のばらつきによって発光素子に流れる電流のばらつきを抑えることができる、様々な種類の画素の構成が考案されている。以下に、その代表的な画素として、電流入力型の画素と、閾値補正型の電圧入力型の画素の構成を例示し、その駆動について説明する。

【0012】

まず、特開2001−147659号に記載の電流入力型の画素の構成について、図20(A)を用いて説明する。

【0013】

図20(A)に記載の画素は、TFT11、12、13、14と、保持容量15と、発光素子16とを有している。

【0014】

TFT11は、ゲートが端子18に接続され、ソースとドレインが一方は電流源17に、他方はTFT13のドレインに接続されている。TFT12は、ゲートが端子19に、ソースとドレインが一方はTFT13のドレインに、他方はTFT13のゲートに接続されている。TFT13とTFT14は、ゲートが互いに接続されており、ソースが共に端子20に接続されている。TFT14のドレインは発光素子16の陽極に接続されており、発光素子16の陰極は端子21に接続されている。保持容量15はTFT13及び14のゲートとソース間の電圧を保持するように設けられている。端子20、21には、電源からそれぞれ所定の電圧が印加されており、互いに電圧差を有している。

【0015】

端子18、19に与えられる電圧によりTFT11、12がオンになった後、電流源17によってTFT13のドレイン電流が制御される。ここで、TFT13はゲートとドレインが接続されるため飽和領域で動作しており、そのドレイン電流は以下の式1で表される。なお、VGSはゲート電圧、μを移動度、C0を単位面積あたりのゲート容量、W/Lをチャネル形成領域のチャネル幅Wとチャネル長Lの比、VTHを閾値、ドレイン電流をIDとする。

【0016】

【式1】

ID=μC0W/L(VGS−VTH)2/2

【0017】

式1においてμ、C0、W/L、VTHは全て個々のトランジスタによって決まる固定の値である。式1から、TFT13のドレイン電流はゲート電圧VGSによって変化することがわかる。よって、式1に従うと、ドレイン電流に見合った値のゲート電圧VGSが、TFT13において発生する。

【0018】

このとき、TFT13とTFT14はそのゲートとソースが互いに接続されているため、TFT14のゲート電圧がTFT13のゲート電圧と同じ大きさに保たれる。よって、TFT13とTFT14はドレイン電流が比例関係にある。特に、μ、C0、W/L、VTHの値が同じであれば、TFT13とTFT14はドレイン電流が同じになる。TFT14に流れるドレイン電流は発光素子16に供給され、該ドレイン電流の大きさに見合った輝度で発光素子16は発光する。

【0019】

特に、TFT13に対するTFT14のオン電流の比を大きくすることで、短い書き込み時間で、所望の大きさの電流を発光素子に供給することができる。

【0020】

そして、端子18、19に与えられる電圧によりTFT11、12がオフになった後も、TFT14のゲート電圧VGSが保持容量15によって保持されている限り、発光素子16は発光し続ける。

【0021】

次に、Tech. Digest IEDM 98, 875. R. M. A. Dawson etc.に記載の電流入力型の画素の構成について、図20(B)を用いて説明する。図20(B)に記載の画素は、TFT31、32、33、34と、保持容量35と、発光素子36とを有している。

【0022】

TFT31はゲートが端子38に接続され、ソースとドレインが一方は電流源37に、他方はTFT33のソースに接続されている。また、TFT34はゲートが端子38に接続され、ソースとドレインが一方はTFT33のゲートに、他方はTFT33のドレインに接続されている。TFT32は、ゲートが端子39に、ソースとドレインが、一方は端子40に、他方はTFT33のソースに接続されている。TFT33のドレインは発光素子36の陽極に接続されており、発光素子36の陰極は端子41に接続されている。保持容量35はTFT33のゲートとソース間の電圧を保持するように設けられている。端子40、41には、電源からそれぞれ所定の電圧が印加されており、互いに電圧差を有している。

【0023】

端子38に与えられる電圧によりTFT31及び34がオンになり、かつ端子39に与えられる電圧によりTFT32がオフなった後、電流源37によってTFT33のドレイン電流が制御される。ここで、TFT33はゲートとドレインが接続されているため飽和領域で動作しており、そのドレイン電流は上述の式1で表される。式1から、TFT33のドレイン電流はゲート電圧VGSによって変化することがわかる。よって、式1に従うと、ドレイン電流に見合った値のゲート電圧VGSが、TFT33において発生する。該ゲート電圧VGSは、保持容量35において保持される。

【0024】

TFT33に流れるドレイン電流は発光素子36に供給され、該ドレイン電流の大きさに見合った輝度で発光素子36は発光する。

【0025】

そして、端子38に与えられる電圧によりTFT31、34がオフになった後、端子39に与えられる電圧によりTFT32がオンになる。このとき、TFT33のゲート電圧が保持容量35によって保持されている限り、TFT31、34がオンであったときと同じ輝度で発光素子36は発光する。

【0026】

上述した図20(A)、(B)に示す電流入力型の画素は、TFTの閾値やオン電流等の特性が画素毎にばらついていても、電流源により発光素子に供給される電流の大きさを制御するので、画素間で発光素子の輝度にばらつきが生じるのを防ぐことができる。

【0027】

次に、US6,229,506に記載の、閾値補正型の電圧入力型画素の構成について、図21を用いて説明する。図21に記載の画素は、TFT51、52、53、54と、保持容量55、56と、発光素子57とを有している。

【0028】

TFT51は、ゲートが端子59に接続され、ソースとドレインが一方は端子58に、他方は保持容量55の一方の電極に接続されている。保持容量55のもう一方の電極はTFT53のゲートに接続されている。TFT52は、ゲートが端子61に接続されており、ソースがTFT53のゲートに、ドレインがTFT53のドレイン及びTFT54のソースに接続されている。TFT53のソースは端子60に接続されており、保持容量56はTFT53のゲートとソース間の電圧を保持するように設けられている。TFT54はゲートが端子62に接続されており、ドレインが発光素子57の陽極に接続されている。発光素子57の陰極は端子63に接続されている。端子60、63には、電源からそれぞれ所定の電圧が印加されており、互いに電圧差を有している。ここでは端子60にかかる電圧を、端子63にかかる電圧よりも高くしている。

【0029】

まず、端子58に印加される電圧を、端子60に印加される電圧と同じ高さにする。そして端子59に印加する電圧を制御してTFT51をオンにした後に、端子61、62に印加する電圧を制御することでTFT52、54をオンにすると、保持容量55、56に電荷が貯まり始める。そして、保持容量56に保持される電圧が、TFT53のしきい値(VTH)を上回ったところで、TFT53がオンする。

【0030】

次にTFT54をオフすると、保持容量55、56に貯まっていた電荷が、オンの状態にあるTFT53を介して放出される。このとき、TFT52はオンなので、TFT53のゲートとドレインが接続されており、よって、TFT53は飽和領域で動作する。したがって、電荷が放出されているときのドレイン電流は、上記の式1で表される。

【0031】

この電荷の放出は、ID=0、つまりTFT53がオフになるまで続く。式1においてμ、C0、W/L、VTHは全て個々のトランジスタによって決まる固定の値であるので、ID=0のとき、式1より、VGS=VTHとなる。つまり、電荷の放出によりTFT53がオフになると、保持容量56にTFT53の閾値分の電圧VTHが保持されることになる。

【0032】

次に、TFT52をオフにし、端子58にビデオ信号の電圧VDataを印加する。このビデオ信号の入力により、保持容量56には、電荷保存則に従い、閾値電圧VTHに電圧VDataを加算した電圧が保持される。

【0033】

次に、TFT51をオフにした後、TFT54をオンにすることで、TFT53のドレイン電流が発光素子57に供給される。このときTFT53のドレイン電流は、保持容量56に保持されている、閾値電圧VTHに電圧VDataを加算した電圧によって制御される。よって、TFT53の閾値VTHに関わらず、必ず電圧VDataに見合った値の電流が発光素子57に供給されることになり、閾値のばらつきに起因する輝度むらを抑えることができる。

【0034】

【発明が解決しようとする課題】

このように、図19に示した画素に比べ、図20に示した電流入力型の画素及び図21に示した閾値補正型の電圧入力型の画素は、TFTの特性のばらつきによって発光素子に流れる電流のばらつきを抑えることができる。しかし、上述した構成の画素もそれぞれ課題を有している。

【0035】

図20(A)に代表されるような、画素に供給された電流を電圧に変換して保持する手段(TFT13)と、該保持された電圧に応じた大きさの電流を発光素子に流す手段(TFT14)の2つの手段を有する画素の場合、いずれか一方の手段の特性がずれることにより、2つの手段における特性のバランスが画素間でばらつくことがある。すると、駆動部から発光素子に供給される電流の大きさが所望の値に保たれなくなり、画素間で発光素子の輝度にばらつきが生じてしまう。

【0036】

具体的に図20(A)では、TFT13またはTFT14において、TFTに固有の特性であるμ、C0、VTHや、W/Lがずれてしまった場合、TFT13のドレイン電流に対するTFT14のドレイン電流の比が画素間で異なってしまい、画素間において発光素子の輝度のばらつきが生じてしまう。

【0037】

一方、図20(B)に代表されるような、画素に供給された電流を電圧に変換して保持し、かつ該保持された電圧に応じた大きさの電流を発光素子に流す手段(TFT33)を有する画素の場合、画素に供給された電流を電圧に変換する際に、発光素子に電流が流れる。発光素子は比較的大きな容量を有している。そのため、例えば低い階調から高い階調へ表示が変化する場合、発光素子の有する容量に電荷がたまるまで、電流から変換される電圧の値が安定しない。よって、低い階調から高い階調へ表示が変化するのに時間がかかってしまう。また逆に、高い階調から低い階調へ表示が変化する場合、発光素子の有する容量が有する余分な電荷が放出されるまで、電流から変換される電圧の値が安定しない。よって、高い階調から低い階調へ表示が変化するのに時間がかかってしまう。

【0038】

具体的に図20(B)では、電流源37から供給される電流の値が変わったときに、TFT33のゲート電圧が安定するのに時間がかかり、電流を書き込む時間が長くなる。その結果、例えば、動画表示において残像が視認されてしまうことがあり、高速応答で動画表示に向いているという発光素子の特徴を生かしきれない。

【0039】

図21に代表されるような、発光素子に供給する電流を制御するTFT(TFT53)の閾値分の電圧を、予め保持容量に書き込む画素の場合、該保持容量に閾値分の電圧を書き込む際に、発光素子に電流は流れないので、図20(B)のように発光素子の容量によって書き込み時間が左右されるということはない。

【0040】

しかし、TFT53がオンになる程度の電荷を保持容量に貯めた後、保持容量に保持される電圧が閾値分の電圧VTHとなるまでTFT53を介して電荷を放電する必要があり、よってこの電荷の放電に要する時間により、書き込み時間を抑えることができない。よって図21に代表されるような画素は、デジタルの信号を用いた時間階調表示など、更なる書き込み時間の短縮化が要求される場合に対応することができない。その結果、例えば、動画表示において残像が視認されたり、高速応答で動画表示に向いているという発光素子の特徴を生かしきれない。

【0041】

本発明は上述したことに鑑み、TFTの特性の違いに起因する、画素間における発光素子の輝度のばらつきを抑えることができ、なおかつ残像が視認されにくい発光装置、発光装置の駆動方法及び素子基板の提供を課題とする。

【0042】

【課題を解決するための手段】

本発明は、発光素子に供給する電流を制御する素子として、4つの端子(ノード)の短絡または開放、言い換えると接続、を制御することができるトランジスタ(以下、マルチ端子トランジスタ)を用いて駆動する、電流入力型発光装置及び閾値補正型の電圧入力型発光装置を考案した。なお本明細書において接続とは、特に記載のない限り電気的な接続を意味する。

【0043】

すなわち、本発明の電流入力型発光装置は、ビデオ信号に相当する電流をマルチ端子トランジスタが有する4つのノードのうちの2つのノード間に流すことで電圧に変換し、次に前記2つのノードと異なる2つのノードを短絡させて、該電圧を再び電流に変換し、発光素子に供給する。

【0044】

具体的に本発明の電流入力型発光装置の画素には、

▲1▼ ゲートの電圧を制御することで4つのノードを短絡または開放する手段

▲2▼ 前記ゲートの電圧を保持する手段

▲3▼ 第1のノードと前記ゲートの接続を制御する手段

▲4▼ 前記第1のノードと第2のノードの間に流れる電流を制御する手段

▲5▼ 第3のノードと第4のノードの間に流れる電流を制御する手段

▲6▼ 前記第3のノードと第4のノードの間に流れる電流が供給される発光素子が備えられている。

【0045】

また本発明の素子基板は、上記電流入力型発光装置を作製する過程における、発光素子が完成する前の一形態に相当する。具体的には、

▲1▼ ゲートの電圧を制御することで4つのノードを短絡または開放する手段

▲2▼ 前記ゲートの電圧を保持する手段

▲3▼ 第1のノードと前記ゲートの接続を制御する手段

▲4▼ 前記第1のノードと第2のノードの間に流れる電流を制御する手段

▲5▼ 第3のノードと第4のノードの間に流れる電流を制御する手段し、なおかつ、第3のノードと第4のノードの間に流れる電流を発光素子に供給するための手段

が備えられている。

【0046】

上記構成により、発光素子に電流を流さずに、電流を電圧に変換することができるので、図20(B)に示した画素よりも書き込み時間を抑えることができる。また、1つのマルチ端子トランジスタで、画素に供給された電流を電圧に変換して保持し、かつ該保持された電圧に応じた大きさの電流を発光素子に流すことができるので、図20(A)に示した画素のように、画素間において発光素子の輝度のばらつきが生じてしまうのを防ぐことができる。

【0047】

また、ビデオ信号に相当する電流を電圧に変換するときの2つのノード(第1と第2のノード)間のチャネル長とチャネル幅の比(L/W)を、該電圧を再び電流に変換して発光素子に供給する時における2つのノード(第3と第4のノード)間のL/Wよりも、小さくする。言い換えると、ビデオ信号に相当する電流を電圧に変換するときの2つのノード間のチャネル長を、該電圧を再び電流に変換して発光素子に供給する時における2つのノード間のチャネル長よりも、短くする。

【0048】

チャネル幅が長くなるとオン電流を大きくすることができ、チャネル長を長くすると、飽和領域の線形性を高めることができる。

【0049】

よって、上記構成により、書き込み時間を抑えつつ、所望の大きさの電流を発光素子に供給することができ、また発光素子を発光させるときの飽和領域の線形性を高め、画素間の輝度のばらつきをより抑えることができる。

【0050】

また、本発明の閾値補正型の電圧入力型発光装置は、マルチ端子トランジスタが有する4つのノードのうちの2つのノードを短絡することで、閾値分の電圧の保持容量への書き込みと、ビデオ信号に相当する電圧の保持容量への書き込みとを行なう。次に、前記2つのノードと異なる2つのノードを短絡させて、該2つの電圧を電流に変換し、発光素子に供給する。

【0051】

具体的に本発明の閾値補正型の電圧入力型発光装置の画素には、

▲1▼ ゲートの電圧を制御することで4つのノードを短絡または開放する手段

▲2▼ 前記ゲートの電圧を保持する手段

▲3▼ 第2のノードと前記ゲートの接続を制御する手段

▲4▼ ▲3▼の手段により前記第2のノードと前記ゲートとが接続されているときに、前記▲2▼の手段において保持される電圧の大きさを制御する手段

▲5▼ 第3のノードと第4のノードの間に流れる電流を制御する手段

▲6▼ 前記第3のノードと第4のノードの間に流れる電流が供給される発光素子が備えられている。

【0052】

また本発明の素子基板は、上記電圧入力型発光装置を作製する過程における、発光素子が完成する前の一形態に相当する。具体的には、

(1) ゲートの電圧を制御することで4つのノードを短絡または開放する手段

(2) 前記ゲートの電圧を保持する手段

(3) 第2のノードと前記ゲートの接続を制御する手段

(4) (3)の手段により前記第2のノードと前記ゲートとが接続されているときに、前記(2)の手段において保持される電圧の大きさを制御する手段

(5) 第3のノードと第4のノードの間に流れる電流を制御し、なおかつ、第3のノードと第4のノードの間に流れる電流を発光素子に供給するための手段

が備えられている。

【0053】

そして、マルチ端子トランジスタの閾値分の電圧の保持容量への書き込み時と、ビデオ信号に相当する電圧の保持容量への書き込み時における、2つのノード間のチャネル長とチャネル幅の比(L/W)を、該電圧を電流に変換して発光素子に供給する時における2つのノード間のL/Wよりも、小さくする。言い換えると、マルチ端子トランジスタの閾値分の電圧の保持容量への書き込み時と、ビデオ信号に相当する電圧の保持容量への書き込み時における、2つのノード間のチャネル長を、該電圧を電流に変換して発光素子に供給する時における2つのノード間のチャネル長よりも、小さくする。

【0054】

上記構成により、電荷を保持容量に貯め、保持容量に保持される電圧が閾値分の電圧VTHとなるまで電荷を放電し、ビデオ信号に相当する電圧を保持容量へ書き込むという、一連の動作の速度を向上させつつ、所望の大きさの電流を発光素子に供給することができる。また、発光素子を発光させるときに飽和領域の線形性を高め、画素間の輝度のばらつきをより抑えることができる。

【0055】

なお、具体的にマルチ端子トランジスタは、活性層と、前記活性層に接する絶縁膜と、前記絶縁膜に接するゲート電極とを有している。そして、前記活性層は、少なくとも1つのチャネル形成領域と、少なくとも4つの不純物領域とを有している。そして4つの不純物領域が、マルチ端子トランジスタと他の素子との間の、電圧または電流の出入り口となるノードに相当する。

【0056】

ノードとなる4つの各不純物領域は、チャネル形成領域のいずれか1つとのみ接している。つまり、ノードとなる4つの不純物領域は、任意の2つの不純物領域の間に、ノードとなる他の不純物領域を挟んでいない。

【0057】

なお、任意の不純物領域が、不純物濃度の低い領域(低濃度不純物領域)を含んでおり、該低濃度不純物領域がチャネル形成領域と接していても良い。この構成により不純物領域近傍の電界集中を緩和することができる。

【0058】

ゲート電極は絶縁膜を間に挟んでチャネル形成領域と重なっている。そして、ゲート電極に印加する電圧を制御することで、各ノード間の抵抗を制御し、短絡または開放することができる。

【0059】

なお、本発明のマルチ端子トランジスタは、基板と活性層の間にゲート電極が設けられていても良いし、ゲート電極と基板の間に活性層が設けられていても良い。

【0060】

なお、本発明の発光装置において、画素に用いるトランジスタ(マルチ端子トランジスタを含む)は、多結晶シリコンを用いて形成されたトランジスタであっても良いし、アモルファスシリコンを用いた薄膜トランジスタであっても良い。また、有機半導体を用いたトランジスタであっても良い。

【0061】

なお本発明の発光装置の画素に設けられたトランジスタは、シングルゲート構造を有していても良いし、ダブルゲート構造やそれ以上のゲート電極を有するマルチゲート構造であっても良い。

【0062】

【発明の実施の形態】

(実施の形態1)

以下に、本発明の電流入力型の発光装置の構成について説明する。本発明の電流入力型発光装置が有する画素部には、複数の画素がマトリクス状に配置されている。また画素部には信号線、電源線、走査線など、各種配線が配置されている。

【0063】

図1(A)に本発明の電流入力型の発光装置における、画素の回路図を示す。図1(A)では、各画素に6つトランジスタ(Tr1〜Tr6)と、発光素子101と、保持容量102とが設けられている。Tr1〜Tr5が、2つのノード(ソースとドレイン)の短絡と開放を制御するトランジスタに相当し、Tr6が4つのノードの短絡と開放を制御するトランジスタに相当する。

【0064】

Tr6は、▲1▼ゲートの電圧を制御することで4つのノードを短絡または開放する手段に相当する。保持容量102は、▲2▼前記ゲートの電圧を保持する手段に相当する。Tr2は、▲3▼第1のノードと前記ゲートの接続を制御する手段に相当する。Tr1及びTr3は、▲4▼第1のノードと第2のノードの間に流れる電流を制御する手段に相当する。Tr4及びTr5は、▲5▼第3のノードと第4のノードの間に流れる電流を制御する手段に相当する。発光素子101は、▲6▼前記第3のノードと第4のノードの間に流れる電流が供給される発光素子に相当する。

【0065】

なお、発光素子が完成する前の形態に相当する素子基板は、▲6▼の発光素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、パターニングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

【0066】

Tr1のゲートは第1の走査線Gj(j=1〜y)に接続されており、ソースとドレインは、一方が信号線Si(i=1〜x)に、もう一方がTr6の第1のノードNd1に接続されている。

【0067】

Tr2のゲートは第2の走査線Pj(j=1〜y)に接続されており、ソースとドレインは、一方がTr6のゲートに、もう一方がTr6の第1のノードNd1に接続されている。

【0068】

Tr3のゲートは第1の走査線Gj(j=1〜y)に接続されており、ソースとドレインは、一方が電源線Vi(i=1〜x)に、もう一方がTr6の第2のノードNd2に接続されている。

【0069】

Tr4のゲートは第3の走査線Qj(j=1〜y)に接続されており、ソースとドレインは、一方が電源線Vi(i=1〜x)に、もう一方がTr6の第3のノードNd3に接続されている。

【0070】

Tr5のゲートは第4の走査線Rj(j=1〜y)に接続されており、ソースとドレインは、一方がTr6の第4のノードNd4に、もう一方が発光素子101の画素電極に接続されている。

【0071】

発光素子101は陽極と陰極を有しており、本明細書では、陽極を画素電極として用いる場合は陰極を対向電極と呼び、陰極を画素電極として用いる場合は陽極を対向電極と呼ぶ。

【0072】

また、保持容量102はトランジスタTr6のゲートと電源線Viの間の電圧を保持するために設けられている。

【0073】

電源線V1〜Vxと対向電極には、それぞれ電源から所定の電圧が与えられており、電源線V1〜Vxと対向電極とは、発光素子に順バイアスの電流を流すことができる程度の電圧差を有している。なお、電源線V1〜Vxの電圧は全て同じ高さに保たなくても良く、例えばカラーの画像を表示する発光装置の場合、対応する色毎に変えるようにしても良い。

【0074】

なお、Tr1〜Tr6の極性はnチャネル型であってもpチャネル型であっても、どちらでも良い。ただし、Tr1とTr3の極性は同じである。そして、陽極を画素電極として用い、陰極を対向電極として用いる場合、Tr6はpチャネル型トランジスタであることが望ましい。逆に、陽極を対向電極として用い、陰極を画素電極として用いる場合、Tr6はnチャネル型トランジスタであることが望ましい。

【0075】

また、信号線と電源線の数は必ずしも同じであるとは限らない。また、第1走査線と、第2走査線と、第3走査線と、第4走査線の数は必ずしも同じであるとは限らない。

【0076】

なお、図1(A)ではTr1とTr3のゲートが、共に第1の走査線Gjに接続されているが、別途走査線を設け、互いに異なる走査線に接続するようにしても良い。この場合、Tr1とTr3の極性は同じでなくとも良い。

【0077】

またTr4とTr5のゲートを共に第3の走査線Qjに接続するようにしても良い。図1(B)に、Tr4とTr5のゲートを共に第3の走査線Qjに接続した場合の、画素の回路図を示す。図1(B)ではTr4とTr5の極性は同じである。図1(B)に示す画素は、図1(A)に示す画素に比べて走査線の数が少なくて済む。

【0078】

次に、Tr6の詳しい構成について説明する。Tr6は、4つのノードを短絡または開放することができるマルチ端子トランジスタである。4つのノードの短絡または開放は、ゲートに与えられる電圧で制御することができる。

【0079】

図2(A)は、Tr6の上面図であり、図2(B)は、図2(A)の破線A−A’における断面図に相当し、図2(C)は、図2(A)の破線B−B’における断面図に相当する。

【0080】

Tr6は、活性層201と、該活性層に接するゲート絶縁膜202と、ゲート絶縁膜202に接するゲート電極(ゲート)203とを有している。活性層201は、チャネル形成領域204と、導電型を付与する不純物が添加された不純物領域205〜208を有している。ゲート電極203とチャネル形成領域204は、ゲート絶縁膜202を間に挟んで重なっている。

【0081】

不純物領域205〜208はそれぞれチャネル形成領域204に接している。なお、不純物領域内に、不純物濃度の低い低濃度不純物領域(LDD領域)が設けられていても良い。この場合、低濃度不純物領域がチャネル形成領域204に接するようにする。また、ゲート電極と重ならない不純物の添加されていない領域(オフセット領域)が、チャネル形成領域と不純物領域との間に設けられていても良い。

【0082】

そしてTr6は、第1のノードNd1と第2のノードNd2の間に流れるオン電流が、第3のノードNd1と第4のノードNd2の間に流れるオン電流より大きくなるように、そのチャネル形成領域204のレイアウトを設定する。具体的に例えば、不純物領域205と206の間のチャネル形成領域204の長さと幅の比L1-2/W1-2を、不純物領域207と208の間のチャネル形成領域204の長さと幅の比L3-4/W3-4よりも小さく設定する。

【0083】

具体的には、L1-2=W3-4、L3-4=W1-2とすると、L1-2/L3-4を1/5以下1/20以上であるのが好ましい。例えばL1-2=5μm、L3-4=50μmの場合だと、第1のノードNd1と第2のノードNd2の間に流れるオン電流は、第3のノードNd1と第4のノードNd2の間に流れるオン電流の100倍程度とすることができる。

【0084】

活性層201を覆うように、ゲート絶縁膜202上に、層間絶縁膜209が形成されている。そして、層間絶縁膜209及びゲート絶縁膜202に形成されたコンタクトホールを介して、不純物領域205〜208にそれぞれ接続された配線210〜213が形成されている。なお、図2ではゲート絶縁膜202が不純物領域205〜208を覆っているが、本発明はこの構成に限定されない。不純物領域205〜208は必ずしもゲート絶縁膜202に覆われている必要はなく、露出していても良い。

【0085】

Tr6は、ゲート電極203に印加される電圧によって、各不純物領域205〜208間の抵抗、ひいては各配線210〜213間の抵抗が制御され、短絡と開放が制御される。

【0086】

なお、図2に示した構成はTr6の一実施例である。Tr6は各不純物領域間に2つ以上のチャネル形成領域が設けられた、所謂マルチゲート構造を有していても良い。

【0087】

次に、図1(A)に示した画素の駆動について説明する。

【0088】

本発明の電流入力型発光装置の画素の駆動は、書き込み期間Taと、保持期間Thと、表示期間Tdとに分けて説明することができる。図3(A)に、各期間におけるTr1〜Tr5のスイッチングのタイミングを示す。そして、図1(A)の画素のTr1〜Tr5が全てnチャネル型TFTの場合に、各期間において各走査線に入力される電圧のタイミングチャートを、図3(B)に示す。

【0089】

まず、各ラインの画素において書き込み期間Taが順に開始される。書き込み期間が開始されると、Tr1〜Tr3がオンになり、Tr4、Tr5がオフになる。書き込み期間における画素の構成の概略図を、図4(A)に示す。書き込み期間Taでは、駆動回路に設けられた電流源103から、ビデオ信号に相当する電流(信号電流)Idataが信号線Siに入力される。

【0090】

そして、信号電流Idataは、Tr6のノードNd1とNd2を介して、信号線Siと電源線Viの間を流れる。つまり、Tr6のノードNd1とNd2の間に流れるドレイン電流IDは、信号電流Idataとほぼ同じ値に保たれる。

【0091】

そして、書き込み期間TaにおいてTr6は、そのゲートとNd1が接続されているので、飽和領域で動作している。よって、Tr6のドレイン電流IDは、上述の式1で表される。式1においてμ、C0、W/L、VTHは全て個々のトランジスタによって決まる固定の値であるので、Tr6のゲート電圧VGSは信号電流Idataの値によって定まる。該ゲート電圧VGSは、保持容量102において保持される。

【0092】

各ラインの画素において書き込み期間Taが終了すると、保持期間Thが開始される。保持期間Thでは、Tr1〜Tr5が全てオフになる。保持期間における画素の構成の概略図を、図4(B)に示す。なお、Tr1及びTr3よりもTr2を先にオフするのが望ましい。Tr2を先にオフすることで、Tr2を介して保持容量102から電荷が放出されるのを防ぎ、確実に電圧を保持することができる。

【0093】

そして、各ラインの画素において保持期間Thが終了すると、表示期間Tdが開始される。表示期間Tdが開始されると、Tr1〜Tr3はオフ、Tr4、Tr5がオンになる。表示期間における画素の構成の概略図を、図4(C)に示す。

【0094】

Tr4とTr5がオンになることで、保持容量102によって保持されているゲート電圧VGSに見合った大きさのドレイン電流IDが、Tr6のノードNd3とNd4を介して発光素子101に供給される。発光素子101は供給された電流に見合った輝度で発光する。なお、ドレイン電流IDが発光素子101の閾値以下だと発光しない。

【0095】

ビデオ信号がアナログの場合、表示期間Tdが終了すると1フレーム期間が終了し、1つの画像が表示される。そして、次のフレーム期間が開始され、再び上述した動作が繰り返される。各画素の階調は、表示期間Tdにおいて発光素子101に流れる電流の大きさで決まる。

【0096】

また、ビデオ信号がデジタルで、時間階調表示を行なう場合、1フレーム期間が複数のサブフレーム期間からなる。各サブフレーム期間の長さの比は、20:21:…:2n-1を満たす。そして、各サブフレーム期間内に書き込み期間Ta、保持期間Th、表示期間Tdが出現する。そして、各サブフレーム期間ごとに発光を制御することで、1フレーム期間全体を通して階調を表示することができる。

【0097】

本発明の電流入力型の発光装置では、書き込み期間Taにおいて発光素子に電流を流さずに、電流を電圧に変換することができるので、図20(B)に示した画素よりも電流の書き込み時間を抑えることができる。また、1つのマルチ端子トランジスタで、画素に供給された電流を電圧に変換して保持し、かつ該保持された電圧に応じた大きさの電流を発光素子に流すことができるので、図20(A)に示した画素のように、画素間において発光素子の輝度のばらつきが生じてしまうのを防ぐことができる。

【0098】

また、チャネル幅が長くなるとオン電流を大きくすることができ、チャネル長を長くすると、飽和領域の線形性を高めることができる。よって、ビデオ信号に相当する電流を電圧に変換するときの2つのノードNd1とNd2間のチャネル長を、該電圧を再び電流に変換して発光素子に供給するときの2つのノードNd3とNd4間のチャネル長よりも短くすることで、書き込み期間Taの長さを抑えつつ所望の大きさの電流を発光素子に供給することができ、また表示期間TdのTr6の飽和領域の線形性を高め、画素間の輝度のばらつきをより抑えることができる。

【0099】

(実施の形態2)

以下に、本発明の閾値補正型の電圧入力型発光装置の構成について説明する。本発明の閾値補正型の電圧入力型発光装置が有する画素部には、複数の画素がマトリクス状に配置されている。また画素部には信号線、電源線、走査線など、各種配線が配置されている。

【0100】

図5(A)に本発明の閾値補正型の電圧入力型発光装置における、画素の回路図を示す。図5(A)では、各画素に6つトランジスタ(Tr1〜Tr6)と、発光素子301と、保持容量302とが設けられている。Tr1〜Tr5が、2つのノード(ソースとドレイン)の短絡と開放を制御するトランジスタに相当し、Tr6が4つのノードの短絡と開放を制御するトランジスタに相当する。

【0101】

Tr6は、(1)ゲートの電圧を制御することで4つのノードを短絡または開放する手段に相当する。保持容量302は、(2)前記ゲートの電圧を保持する手段に相当する。Tr5は、(3)第2のノードと前記ゲートの接続を制御する手段に相当する。Tr1及びTr3は、(4) (3)の手段により第2のノードと前記ゲートとが接続されているときに、前記(2)の手段において保持される電圧の大きさを制御する手段に相当する。Tr4及びTr2は、(5)第3のノードと第4のノードの間に流れる電流を制御する手段に相当する。発光素子301は、(6)前記第3のノードと第4のノードの間に流れる電流が供給される発光素子に相当する。

【0102】

なお、発光素子が完成する前の形態に相当する素子基板は、(6)の発光素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、パターニングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

【0103】

なお、Tr6の詳しい構成については、実施の形態1のTr6と同じであり、図2を参照することができるので、ここでは説明省略する。

【0104】

Tr1のゲートは第1の走査線Gj(j=1〜y)に接続されており、ソースとドレインは、一方が信号線Si(i=1〜x)に、もう一方がTr6の第1のノードNd1に接続されている。

【0105】

Tr2のゲートは第2の走査線Pj(j=1〜y)に接続されており、ソースとドレインは、一方がTr6の第3のノードNd3に、もう一方が電源線Vi(i=1〜x)に接続されている。

【0106】

Tr3のゲートは第3の走査線Qj(j=1〜y)に接続されており、ソースとドレインは、一方がTr6の第2のノードNd2に、もう一方が発光素子301が有する対向電極に接続されている。

【0107】

Tr4のゲートは第4の走査線Rj(j=1〜y)に接続されており、ソースとドレインは、一方が第4のノードNd4に、もう一方が発光素子301が有する画素電極に接続されている。

【0108】

Tr5のゲートは第5の走査線Wj(j=1〜y)に接続されており、ソースとドレインは、一方がTr6のゲートに、もう一方がTr6の第2のノードNd2に接続されている。

【0109】

また、保持容量302はトランジスタTr6のゲートと電源線Viの間の電圧を保持するために設けられている。

【0110】

電源線V1〜Vxと対向電極には、それぞれ電源から所定の電圧が与えられており、電源線V1〜Vxと対向電極とは、発光素子に順バイアスの電流を流すことができる程度の電圧差を有している。なお、電源線V1〜Vxの電圧は全て同じ高さに保たなくても良く、例えばカラーの画像を表示する発光装置の場合、対応する色毎に変えるようにしても良い。

【0111】

なお、Tr1〜Tr6の極性はnチャネル型であってもpチャネル型であっても、どちらでも良い。ただし、陽極を画素電極として用い、陰極を対向電極として用いる場合、Tr6はpチャネル型トランジスタであることが望ましい。逆に、陽極を対向電極として用い、陰極を画素電極として用いる場合、Tr6はnチャネル型トランジスタであることが望ましい。

【0112】

また、信号線と電源線の数は必ずしも同じであるとは限らない。また、第1〜第5走査線の数は必ずしも同じであるとは限らない。

【0113】

なお、Tr2とTr4のゲートを、共に第2の走査線Pjに接続するようにしても良い。図5(B)に、Tr2とTr4のゲートを共に第2の走査線Pjに接続した場合の、画素の回路図を示す。図5(B)ではTr2とTr4の極性は同じである。図5(B)に示す画素は、図5(A)に示す画素に比べて走査線の数が少なくて済む。

【0114】

また、Tr2、Tr4及びTr5のゲートを、共に第2の走査線Pjに接続するようにしても良い。図6に、Tr2、Tr4及びTr5のゲートを共に第2の走査線Pjに接続した場合の、画素の回路図を示す。図6ではTr2、Tr4の極性は同じであり、Tr5はTr2及びTr4の極性とは逆の極性を有する。図6に示す画素は、図5(A)、(B)に示す画素に比べて走査線の数が少なくて済む。

【0115】

次に、図5(A)に示した画素の駆動について説明する。

【0116】

本発明の閾値補正型の電圧入力型発光装置の画素の駆動は、初期化期間Tiと、書き込み期間Taと、表示期間Tdとに分けて説明することができる。図7(A)に、各期間におけるTr1〜Tr5のスイッチングのタイミングを示す。そして、図5(A)の画素のTr1〜Tr5が全てnチャネル型TFTの場合に、各期間において各走査線に入力される電圧のタイミングチャートを、図7(B)に示す。

【0117】

まず、各ラインの画素において初期化期間Tiが順に開始される。初期化期間Tiが開始されると、Tr3、Tr5がオンになり、Tr1、Tr2、Tr4がオフになる。初期化期間における画素の構成の概略図を、図8(A)に示す。Vcは対向電極の電圧である。初期化期間Tiでは、電源線Viの電圧と対向電極の電圧に見合った大きさの電荷が、保持容量302に蓄積される。電源線Viと対向電極に与えられる電圧はそれぞれ一定であるので、初期化期間Tiにおいて保持容量302に蓄積される電荷も常に一定になる。

【0118】

そして、次にTr3をオフにした後、各ラインの画素において初期化期間Tiが終了し、次に書き込み期間Taが開始される。書き込み期間Taが開始されると、まずTr1、Tr5がオンになり、Tr2、Tr3、Tr4がオフになる。そして、駆動回路から、ビデオ信号に相当する電圧(信号電圧)Vdataが信号線Siに入力される。信号電圧Vdataは、Tr6のノードNd1とNd2を介して、保持容量302に与えられる。

【0119】

なおVdataは、|Vdata+VTH|<|Vc|を必ず満たすような高さに設定する。よって、Tr6のNd1とNd2の間にドレイン電流IDが流れ、保持容量302に蓄積されている電荷が放出される。このとき、Tr5はオンなので、Tr6のゲートとNd2は接続されており、よって、Tr6は飽和領域で動作する。したがって、電荷が放出されているときのドレイン電流IDは、上記の式1で表される。

【0120】

この電荷の放出は、ID=0、つまりTr6がオフになるまで続く。式1においてμ、C0、W/L、VTHは全て個々のトランジスタによって決まる固定の値であるので、ID=0のとき、式1より、VGS=VTHとなる。つまり、電荷の放出によりTr6がオフになると、保持容量302には、信号電圧VDataにTr6の閾値分の電圧VTHを加算した電圧が保持されることになる。

【0121】

次に各ラインの画素において書き込み期間Taが終了すると、表示期間Tdが開始される。表示期間Tdが開始されると、Tr1、Tr3、Tr5はオフ、Tr2、Tr4がオンになる。表示期間における画素の構成の概略図を、図8(C)に示す。

【0122】

Tr2とTr4がオンになることで、Tr6のドレイン電流が発光素子301に供給される。このときTr6のドレイン電流は、保持容量302に保持されている、閾値電圧VTHに電圧VDataを加算した電圧によって制御される。よって、Tr6の閾値VTHに関わらず、必ず電圧VDataに見合った値の電流が発光素子301に供給される。発光素子301は供給された電流に見合った輝度で発光するので、結果的に閾値のばらつきに起因する輝度むらを抑えることができる。なお、ドレイン電流IDが発光素子301の閾値以下だと発光しない。

【0123】

ビデオ信号がアナログの場合、表示期間Tdが終了すると1フレーム期間が終了し、1つの画像が表示される。そして、次のフレーム期間が開始され、再び上述した動作が繰り返される。各画素の階調は、表示期間Tdにおいて発光素子301に流れる電流の大きさで決まる。

【0124】

また、ビデオ信号がデジタルで、時間階調表示を行なう場合、1フレーム期間が複数のサブフレーム期間からなる。そして、各サブフレーム期間内に初期化期間Ti、書き込み期間Ta、表示期間Tdが出現する。そして、各サブフレーム期間ごとに発光を制御することで、1フレーム期間全体を通して階調を表示することができる。

【0125】

チャネル幅が長くなるとオン電流を大きくすることができ、チャネル長を長くすると、飽和領域の線形性を高めることができる。よって、本発明の閾値補正型の電圧入力型発光装置では、保持容量に保持される電圧が閾値分の電圧VTHとなるまで電荷を放電し、またビデオ信号に相当する電圧を保持容量へ書き込むときの、2つのノードNd1とNd2間のチャネル長を、発光素子に電流を供給するときの2つのノードNd3とNd4間のチャネル長よりも短くすることで、初期化期間Ti及び書き込み期間Taの長さを抑えつつ、所望の大きさの電流を発光素子に供給することができ、また表示期間TdのTr6の飽和領域の線形性を高め、画素間の輝度のばらつきをより抑えることができる。

【0126】

【実施例】

以下、本発明の実施例について説明する。

【0127】

(実施例1)

本実施例では、基板と活性層の間にゲート電極が形成されている、マルチ端子トランジスタの構成について説明する。

【0128】

本実施例のマルチ端子トランジスタ(以下、単にトランジスタ)の構成について、図9を用いて説明する。図9(A)は、本実施例のトランジスタの上面図であり、図9(B)は、図9(A)の破線A−A’における断面図に相当し、図9(C)は、図9(A)の破線B−B’における断面図に相当する。

【0129】

本実施例のトランジスタは、ゲート電極701と、該ゲート電極701に接するゲート絶縁膜702と、該ゲート絶縁膜702に接する活性層703とを有している。活性層703は、チャネル形成領域704と、導電型を付与する不純物が添加された不純物領域705〜708を有している。ゲート電極701とチャネル形成領域704は、ゲート絶縁膜702を間に挟んで重なっている。なお、720はチャネル形成領域を形成する際に用いるマスクであり、絶縁膜で形成されている。

【0130】

不純物領域705〜708はそれぞれチャネル形成領域704に接している。なお、不純物領域の一部に低濃度不純物領域(LDD領域)が設けられていても良い。この場合、該低濃度不純物領域がチャネル形成領域704に接する。また、不純物領域とチャネル形成領域704の間に、ゲート電極と重ならない不純物の添加されていない領域(オフセット領域)が、設けられていても良い。

【0131】

活性層703の不純物領域705〜708を覆うように層間絶縁膜709が形成されている。そして、層間絶縁膜709に形成されたコンタクトホールを介して、不純物領域705〜708にそれぞれ接続された配線710〜713が形成されている。

【0132】

図9のトランジスタは、ゲート電極701に印加される電圧によって、各不純物領域710〜713間の抵抗、ひいては各配線710〜713間の抵抗が制御され、短絡と開放が制御される。

【0133】

そして図9のトランジスタは、第1のノードNd1に相当する不純物領域705と、第2のノードNd2に相当する不純物領域706の間に流れるオン電流が、第3のノードNd1に相当する不純物領域707と、第4のノードNd2に相当する不純物領域708の間に流れるオン電流より大きくなるように、そのチャネル形成領域704のレイアウトを設定する。具体的に例えば、不純物領域705と706の間のチャネル形成領域704の長さL1-2を、不純物領域707と708の間のチャネル形成領域704の長さL3-4よりも短く設定する。

【0134】

活性層703を覆うように、ゲート絶縁膜702上に、層間絶縁膜709が形成されている。そして、層間絶縁膜709及びゲート絶縁膜702に形成されたコンタクトホールを介して、不純物領域705〜708にそれぞれ接続された配線710〜713が形成されている。なお、図9ではゲート絶縁膜702が不純物領域705〜708を覆っているが、本発明はこの構成に限定されない。不純物領域705〜708は必ずしもゲート絶縁膜702に覆われている必要はなく、露出していても良い。

【0135】

なお、図9に示した構成はTr6の一実施例である。Tr6は各不純物領域間に2つ以上のチャネル形成領域が設けられた、所謂マルチゲート構造を有していても良い。

【0136】

(実施例2)

本実施例では、図1(A)に示した回路図に相当するマスク図面について説明する。

【0137】

図10に本実施例の画素の上面図を示す。図1(A)で既に示したものについては同じ符号を付す。なおトランジスタの配置を明確にするため、図10では発光素子の画素電極のみ示しているが、実際には画素電極上に電界発光層と、対向電極とが順に積層されている。また、図10のA−A’における断面図を図11(A)に、B−B’における断面図を図11(B)に、C−C’における断面図を図11(C)に示す。

【0138】

Tr1のゲート電極131は、第1の走査線Gjの一部である。またTr1のソースとドレインとなる2つの不純物領域132は、一方は信号線Siに、もう一方は配線133を介して、Tr2の不純物領域134及びTr6の第1の不純物領域(Nd1)に接続されている。

【0139】

Tr2のゲート電極135は、配線136の一部であり、配線136は配線137を介して第2の走査線Pjに接続されている。Tr2のソースとドレインとなる2つの不純物領域のうち、134に示した一方の不純物領域は上記したように配線133に接続されており、もう一方は配線138を介してTr6のゲート電極139に接続されている。

【0140】

Tr3のゲート電極140は、第1の走査線Gjの一部である。また、Tr3のソースとドレインとなる2つの不純物領域は、一方は電源線Viに、もう一方は配線141を介してTr6の第2の不純物領域(Nd2)に接続されている。

【0141】

Tr4のゲート電極142は、配線143の一部であり、配線143は配線144を介して第3の走査線Qjに接続されている。Tr4のソースとドレインとなる2つの不純物領域は、一方は電源線Viに、もう一方は配線145を介してTr6の第3の不純物領域(Nd3)に接続されている。

【0142】

Tr5のゲート電極146は、第4の走査線Rjの一部である。また、Tr5のソースとドレインとなる2つの不純物領域147は、一方は配線148を介してTr6の第4の不純物領域(Nd4)に、もう一方は発光素子101の画素電極130に接続されている。なお、本実施例では陽極を画素電極130として用いており、発光素子101から発せられる光が矢印に示すとおり基板150側に向いている。なお、陰極を画素電極130として用いても良い。その場合、発光素子から発せられる光が基板150とは逆の方向に向く。

発光素子101は、画素電極130と対向電極151との間に電界発光層152を挟んだ構造になっている。

【0143】

また、半導体膜153に含まれる不純物領域154は、電源線Viと接続されている。また容量用の電極155は、Tr6のゲート電極139と電気的に接続されている。そして、容量用の電極155と半導体膜153は、ゲート絶縁膜156を間に挟んで重なり合うことで、保持容量102を形成している。

【0144】

なお、本発明の電流入力型発光装置の画素の構成は、図10及び図11に示したものに限定されない。

【0145】

(実施例3)

本実施例では、図5(A)に示した回路図に相当するマスク図面について説明する。

【0146】

図12に本実施例の画素の上面図を示す。図5(A)で既に示したものについては同じ符号を付す。なおトランジスタの配置を明確にするため、図12では発光素子の画素電極のみ示しているが、実際には画素電極上に電界発光層と、対向電極とが順に積層されている。また、図12のA−A’における断面図を図13(A)に、B−B’における断面図を図13(B)に、C−C’における断面図を図13(C)に示す。

【0147】

Tr1のゲート電極331は、第1の走査線Gjの一部である。またTr1のソースとドレインとなる2つの不純物領域は、一方は信号線Siに、もう一方は配線333を介して、Tr6の第1の不純物領域(Nd1)に接続されている。

【0148】

Tr2のゲート電極335は、配線336の一部であり、配線336は配線337を介して第2の走査線Pjに接続されている。Tr2のソースとドレインとなる2つの不純物領域のうち、334に示した一方の不純物領域は配線361を介してTr6の第3の不純物領域(Nd3)に接続されており、もう一方は電源線Viに接続されている。

【0149】

Tr3のゲート電極340は、第3の走査線Qjの一部である。また、Tr3のソースとドレインとなる2つの不純物領域は、一方は配線329を介してTr6の第2の不純物領域Nd2に、もう一方は配線341を介して配線360に接続されている。配線360には発光素子の対向電極に印加される電圧と同じ高さの電圧が印加されている。

【0150】

Tr4のゲート電極342は、配線343の一部であり、配線343は配線344を介して第4の走査線Rjに接続されている。Tr4のソースとドレインとなる2つの不純物領域332は、一方は配線345を介してTr6の第4の不純物領域(Nd4)に、もう一方は画素電極330に接続されている。

【0151】

Tr5のゲート電極346は、配線362の一部であり、配線362は配線363を間に介して第5の走査線Wjに接続されている。また、Tr5のソースとドレインとなる2つの不純物領域は、一方は配線329を介してTr6の第2の不純物領域(Nd2)に、もう一方は配線365に接続されている。配線365はTr6のゲート電極366と電気的に接続されている。

【0152】

なお、本実施例では陽極を画素電極330として用いており、発光素子301から発せられる光が矢印に示すとおり基板350側に向いている。なお、陰極を画素電極330として用いても良い。その場合、発光素子から発せられる光が基板350とは逆の方向に向く。発光素子301は、画素電極330と対向電極351との間に電界発光層352を挟んだ構造になっている。

【0153】

また、半導体膜353に含まれる不純物領域354は、電源線Viと接続されている。また容量用の電極355は、Tr6のゲート電極366と電気的に接続されている。そして、容量用の電極355と半導体膜353は、ゲート絶縁膜356を間に挟んで重なり合うことで、保持容量302を形成している。

【0154】

なお、本発明の閾値補正型の電圧入力型発光装置の画素の構成は、図12及び図13に示したものに限定されない。

【0155】

(実施例4)

本実施例では、電流入力型発光装置において、信号線へのビデオ信号の供給を制御する信号線駆動回路と、走査線の電圧を制御する走査線駆動回路の構成について説明する。なお本実施例では、アナログのビデオ信号を用いた場合の駆動回路の構成について説明する。

【0156】

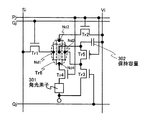

図14(A)に、本実施例の信号線駆動回路401のブロック図を示す。402はシフトレジスタ、403はバッファ、404はサンプリング回路、405は電流変換回路を示している。

【0157】

シフトレジスタ402には、クロック信号(CLK)、スタートパルス信号(SP)が入力されている。シフトレジスタ402にクロック信号(CLK)とスタートパルス信号(SP)が入力されると、タイミング信号が生成される。生成されたタイミング信号は、バッファ403において増幅または緩衝増幅されて、サンプリング回路404に入力される。なお、バッファの代わりにレベルシフタを設けて、タイミング信号を増幅しても良い。また、バッファとレベルシフタを両方設けていても良い。

【0158】

サンプリング回路404では、ビデオ信号線430から入力されたアナログのビデオ信号を、タイミング信号に同期して後段の電流変換回路405に入力する。電流変換回路405では、入力されたアナログのビデオ信号の電圧に見合った大きさの信号電流Idataを生成し、対応する各信号線(S1〜Sx)に供給する。

【0159】

図14(B)にサンプリング回路404と、電流変換回路405が有する電流設定回路(C1〜Cx)の具体的な構成を示す。なおサンプリング回路404は、端子410においてバッファ403と接続されている。

【0160】

サンプリング回路404には、複数のスイッチ411が設けられている。そしてサンプリング回路404には、ビデオ信号線430からアナログのビデオ信号が入力されており、スイッチ411はタイミング信号に同期して、該アナログのビデオ信号をサンプリングし、後段の電流設定回路C1に入力する。なお図14(B)では、電流設定回路C1〜Cxのうち、サンプリング回路404が有するスイッチ411の1つに接続されている電流設定回路C1だけを示しているが、各スイッチ411の後段に、図14(B)に示したような電流設定回路C1が接続されているものとする。

【0161】

なお本実施例では、スイッチ411にトランジスタを1つだけ用いているが、スイッチ411はタイミング信号に同期してアナログのビデオ信号をサンプリングできるスイッチであれば良く、本実施例の構成に限定されない。

【0162】

サンプリングされたアナログのビデオ信号は、電流設定回路C1が有する電流出力回路412に入力される。電流出力回路412は、入力されたビデオ信号の電圧に見合った値の電流(信号電流)を出力する。なお図14(B)ではアンプ及びトランジスタを用いて電流出力回路412を形成しているが、本発明はこの構成に限定されず、電流出力回路は入力された信号の電圧に見合った値の電流を出力することができる回路であれば良い。

【0163】

該信号電流は、同じく電流設定回路C1が有するリセット回路417に入力される。リセット回路417は、2つのトランスミッションゲート413、414と、インバーター416と、を有している。

【0164】

トランスミッションゲート414にはリセット信号(Res)が入力されており、トランスミッションゲート413には、インバーター416によって反転されたリセット信号(Res)が入力されている。そしてトランスミッションゲート413とトランスミッションゲート414は、反転したリセット信号とリセット信号にそれぞれ同期して動作しており、一方がオンのとき片一方がオフになっている。

【0165】

そして、トランスミッションゲート413がオンのときに信号電流は対応する信号線に入力される。逆に、トランスミッションゲート414がオンのときに電源415の電圧が対応する信号線に与えられる。なお信号線は、帰線期間中にリセットするのが望ましい。しかし、画像を表示している期間以外であるならば、必要に応じて帰線期間以外の期間にリセットすることも可能である。

【0166】

次に、走査線駆動回路の構成について説明する。

【0167】

図15は走査線駆動回路641の構成を示すブロック図である。走査線駆動回路641は、それぞれシフトレジスタ642、バッファ643を有している。また場合によってはレベルシフタを有していても良い。

【0168】

走査線駆動回路641において、シフトレジスタ642にクロックCLK及びスタートパルス信号SPが入力されることによって、タイミング信号が生成される。生成されたタイミング信号はバッファ643において緩衝増幅され、対応する走査線に供給される。

【0169】

走査線には、1ライン分の画素のトランジスタのゲートが接続されている。そして、1ライン分の画素のトランジスタを一斉にオンにしなくてはならないので、バッファ643は大きな電流を流すことが可能なものが用いられる。

【0170】

なお、本発明の発光装置が有する信号線駆動回路と走査線駆動回路は、図14、図15に示した構成に限定されない。

【0171】

なお、シフトレジスタの代わりに、例えばデコーダ回路のような信号線の選択ができる別の回路を用いても良い。

【0172】

本実施例の構成は、実施例1〜3と自由に組み合わせて実施することが可能である。

【0173】

(実施例5)

本実施例では、閾値補正型の電圧入力型発光装置において、信号線へのビデオ信号の供給を制御する信号線駆動回路の構成について説明する。なお本実施例では、アナログのビデオ信号を用いた場合の駆動回路の構成について説明する。

【0174】

図16に本実施例の信号線駆動回路611の回路図を示す。612はシフトレジスタ、613はレベルシフタ、614はサンプリング回路を示している。

【0175】

クロック信号(CLK)、スタートパルス信号(SP)が、シフトレジスタ612に入力される。画像情報を有するアナログの信号(アナログのビデオ信号)はサンプリング回路614に入力される。

【0176】

シフトレジスタ612にクロック信号(CLK)とスタートパルス信号(SP)が入力されると、タイミング信号が生成されてレベルシフタ613に入力される。レベルシフタ613に入力されたタイミング信号は、その振幅が増幅されて、サンプリング回路614に入力される。

【0177】

サンプリング回路614に入力されたタイミング信号によって、同じくサンプリング回路614に入力されたアナログのビデオ信号がサンプリングされ、対応する信号線に入力される。

【0178】

なお、走査線駆動回路の構成は、電流入力型発光装置の走査線駆動回路と同じ構成を用いることができるので、ここでは説明を省略する。

【0179】

本実施例の構成は、実施例1〜4と自由に組み合わせて実施することが可能である。

【0180】

(実施例6)

本実施例では、本発明の発光装置の外観について、図17を用いて説明する。

【0181】

図17は、トランジスタが形成された素子基板をシーリング材によって封止することによって形成された発光装置の上面図であり、図17(B)は、図17(A)のA−A’における断面図、図17(C)は図17(A)のB−B’における断面図である。

【0182】

基板4001上に設けられた画素部4002と、信号線駆動回路4003と、走査線駆動回路4004a、bとを囲むようにして、シール材4009が設けられている。また画素部4002と、信号線駆動回路4003と、走査線駆動回路4004a、bとの上にシーリング材4008が設けられている。よって画素部4002と、信号線駆動回路4003と、走査線駆動回路4004a、bとは、基板4001とシール材4009とシーリング材4008とによって、充填材4210で密封されている。

【0183】

なお本実施例では、2つの走査線駆動回路で各走査線の電圧を制御しているが、走査線駆動回路の数はこれに限定されない。例えば図1(A)に示した画素を有する発光装置において、第1〜第4の各走査線に対応する走査線駆動回路をそれぞれ設けるようにしても良い。

【0184】

また基板4001上に設けられた画素部4002と、信号線駆動回路4003と、走査線駆動回路4004a、bとは、複数のTFTを有している。図17(B)では代表的に、下地膜4010上に形成された、信号線駆動回路4003に含まれる駆動TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを図示する)4201及び画素部4002に含まれるトランジスタ4202を図示した。

【0185】

本実施例では、駆動TFT4201には公知の方法で作製されたpチャネル型TFTまたはnチャネル型TFTが用いられ、トランジスタ4202には公知の方法で作製されたnチャネル型TFTが用いられる。

【0186】

駆動TFT4201及びトランジスタ4202上には層間絶縁膜(平坦化膜)4301が形成され、その上にトランジスタ4202のドレインと電気的に接続する画素電極(陽極)4203が形成される。画素電極4203としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したものを用いても良い。

【0187】

そして、画素電極4203の上には絶縁膜4302が形成され、絶縁膜4302は画素電極4203の上に開口部が形成されている。この開口部において、画素電極4203の上には電界発光層4204が形成される。電界発光層4204は公知の有機の電界発光材料または無機の電界発光材料を用いることができる。また、有機の電界発光材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

【0188】

電界発光層4204の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また、電界発光層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

【0189】

電界発光層4204の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極4205が形成される。また、陰極4205と電界発光層4204の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、電界発光層4204を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極4205を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。そして陰極4205は所定の電圧が与えられている。

【0190】

以上のようにして、画素電極(陽極)4203、電界発光層4204及び陰極4205からなる発光素子4303が形成される。そして発光素子4303を覆うように、絶縁膜4302上に保護膜4209が形成されている。保護膜4209は、発光素子4303に酸素や水分等が入り込むのを防ぐのに効果的である。

【0191】

4005aは電源線に接続された引き回し配線であり、トランジスタ4202のソースに電気的に接続されている。引き回し配線4005aはシール材4009と基板4001との間を通り、異方導電性フィルム4300を介してFPC4006が有するFPC用配線4301に電気的に接続される。

【0192】

シーリング材4008としては、ガラス材、金属材(代表的にはステンレス材)、セラミックス材、プラスチック材(プラスチックフィルムも含む)を用いることができる。プラスチック材としては、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

【0193】

但し、発光素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

【0194】

また、充填材4210としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施例では充填材として窒素を用いた。

【0195】

また充填材4210を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておくために、シーリング材4008の基板4001側の面に凹部4007を設けて吸湿性物質または酸素を吸着しうる物質4207を配置する。そして、吸湿性物質または酸素を吸着しうる物質4207が飛び散らないように、凹部カバー材4208によって吸湿性物質または酸素を吸着しうる物質4207は凹部4007に保持されている。なお凹部カバー材4208は目の細かいメッシュ状になっており、空気や水分は通し、吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207を設けることで、発光素子4303の劣化を抑制できる。

【0196】

図17(C)に示すように、画素電極4203が形成されると同時に、引き回し配線4005a上に接するように導電性膜4203aが形成される。

【0197】

また、異方導電性フィルム4300は導電性フィラー4300aを有している。基板4001とFPC4006とを熱圧着することで、基板4001上の導電性膜4203aとFPC4006上のFPC用配線4301とが、導電性フィラー4300aによって電気的に接続される。

【0198】

本実施例の構成は、実施例1〜実施例5に示した構成と自由に組み合わせて実施することが可能である。

【0199】

(実施例7)

発光素子を用いた発光装置は自発光型であるため、液晶ディスプレイに比べ、明るい場所での視認性に優れ、視野角が広い。従って、様々な電子機器の表示部に用いることができる。

【0200】

本発明の発光装置を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDVD:Digital Versatile Disc)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。特に、斜め方向から画面を見る機会が多い携帯情報端末は、視野角の広さが重要視されるため、発光装置を用いることが望ましい。それら電子機器の具体例を図18に示す。

【0201】

図18(A)は表示装置であり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。本発明の発光装置を表示部2003に用いることで、本発明の表示装置が完成する。発光装置は自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることができる。なお、発光素子表示装置は、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

【0202】

図18(B)はデジタルスチルカメラであり、本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含む。本発明の発光装置を表示部2102に用いることで、本発明のデジタルスチルカメラが完成する。

【0203】

図18(C)はノート型パーソナルコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。本発明の発光装置を表示部2203に用いることで、本発明のノート型パーソナルコンピュータが完成する。

【0204】

図18(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。本発明の発光装置を表示部2302に用いることで、本発明のモバイルコンピュータが完成する。

【0205】

図18(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(DVD等)読み込み部2405、操作キー2406、スピーカー部2407等を含む。表示部A2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示する。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明の発光装置を表示部A2403、B2404に用いることで、本発明の画像再生装置が完成する。

【0206】

図18(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2501、表示部2502、アーム部2503を含む。本発明の発光装置を表示部2502に用いることで、本発明のゴーグル型ディスプレイが完成する。

【0207】

図18(G)はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609等を含む。本発明の発光装置を表示部2602に用いることで、本発明のビデオカメラが完成する。

【0208】

ここで図18(H)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。なお、表示部2703は黒色の背景に白色の文字を表示することで携帯電話の消費電流を抑えることができる。本発明の発光装置を表示部2703に用いることで、本発明の携帯電話が完成する。

【0209】

なお、将来的に有機の電界発光材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる。

【0210】

また、上記電子機器はインターネットやCATV(ケーブルテレビ)などの電子通信回線を通じて配信された情報を表示することが多くなり、特に動画情報を表示する機会が増してきている。有機の電界発光材料の応答速度は非常に高いため、発光装置は動画表示に好ましい。

【0211】

また、発光装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話や音響再生装置のような文字情報を主とする表示部に発光装置を用いる場合には、非発光部分を背景として文字情報を発光部分で形成するように駆動することが望ましい。

【0212】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、本実施例の電子機器は実施例1〜6に示したいずれの構成の発光装置を用いても良い。

【0213】

【発明の効果】

本発明の電流入力型発光装置は、発光素子に電流を流さずに、電流を電圧に変換することができるので、図20(B)に示した画素よりも書き込み時間を抑えることができる。また、1つのマルチ端子トランジスタで、画素に供給された電流を電圧に変換して保持し、かつ該保持された電圧に応じた大きさの電流を発光素子に流すことができるので、図20(A)に示した画素のように、画素間において発光素子の輝度のばらつきが生じてしまうのを防ぐことができる。

【0214】

また、ビデオ信号に相当する電流を電圧に変換するときの2つのノード間のチャネル長とチャネル幅の比(L/W)を、該電圧を再び電流に変換して発光素子に供給する時における2つのノード間のL/Wよりも、小さくする。言い換えると、ビデオ信号に相当する電流を電圧に変換するときの2つのノード間のチャネル長を、該電圧を再び電流に変換して発光素子に供給する時における2つのノード間のチャネル長よりも、短くする。

【0215】

チャネル幅が長くなるとオン電流を大きくすることができ、チャネル長を長くすると、飽和領域の線形性を高めることができる。

【0216】

よって、上記構成により、書き込み時間を抑えつつ、所望の大きさの電流を発光素子に供給することができ、また発光素子を発光させるときの飽和領域の線形性を高め、画素間の輝度のばらつきをより抑えることができる。

【0217】

また本発明の閾値補正型の電圧入力型発光装置は、電荷を保持容量に貯め、保持容量に保持される電圧が閾値分の電圧VTHとなるまで電荷を放電し、ビデオ信号に相当する電圧を保持容量へ書き込むという、一連の動作の速度を向上させつつ、所望の大きさの電流を発光素子に供給することができる。また、発光素子を発光させるときに飽和領域の線形性を高め、画素間の輝度のばらつきをより抑えることができる。

【図面の簡単な説明】

【図1】 本発明の発光装置の画素の回路図。

【図2】 マルチ端子トランジスタの構成を示す図。

【図3】 各トランジスタの動作及び各走査線のタイミングチャート。

【図4】 駆動における画素の概略図。

【図5】 本発明の発光装置の画素の回路図。

【図6】 本発明の発光装置の画素の回路図。

【図7】 各トランジスタの動作及び各走査線のタイミングチャート。

【図8】 駆動における画素の概略図。

【図9】 マルチ端子トランジスタの構成を示す図。

【図10】 本発明の発光装置の画素の上面図。

【図11】 本発明の発光装置の画素の断面図。

【図12】 本発明の発光装置の画素の上面図。

【図13】 本発明の発光装置の画素の断面図。

【図14】 アナログ駆動法における信号線駆動回路の詳細図。

【図15】 走査線駆動回路のブロック図。

【図16】 アナログ駆動法における信号線駆動回路の詳細図。

【図17】 本発明の発光装置の外観図及び断面図。

【図18】 本発明の発光装置を用いた電子機器の図。

【図19】 従来の発光装置の画素の回路図。

【図20】 従来の発光装置の画素の回路図。

【図21】 従来の発光装置の画素の回路図。

Claims (12)

- 第1乃至第5の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

発光素子と、を有し、

前記コンデンサーは、電極の一方が前記第6のトランジスタのゲートに接続され、他方が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第3の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第1のノードに接続され、ゲートが前記第5の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第4の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記発光素子に接続され、ゲートが前記第4の配線に接続されていることを特徴とする発光装置。 - 第1乃至第6の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

発光素子と、を有し、

前記コンデンサーは、電極の一方が前記第6のトランジスタのゲートに接続され、他方が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第3の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第1のノードに接続され、ゲートが前記第5の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第4の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記発光素子に接続され、ゲートが前記第6の配線に接続されていることを特徴とする発光装置。 - 第1乃至第6の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

発光素子と、を有し、

前記コンデンサーは、一方の電極が前記第6のトランジスタのゲートに接続され、他方の電極が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第4の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードと前記第5のトランジスタのソース又はドレインの他方に接続され、他方が前記発光素子の一方の電極に接続され、ゲートが前記第5の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記発光素子の他方の電極に接続され、ゲートが前記第3の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第2のノードに接続され、ゲートが前記第6の配線に接続されていることを特徴とする発光装置。 - 第1乃至第7の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

発光素子と、を有し、

前記コンデンサーは、一方の電極が前記第6のトランジスタのゲートに接続され、他方の電極が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第4の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードと前記第5のトランジスタのソース又はドレインの他方に接続され、他方が前記発光素子の一方の電極に接続され、ゲートが前記第5の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記発光素子の他方の電極に接続され、ゲートが前記第7の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第2のノードに接続され、ゲートが前記第6の配線に接続されていることを特徴とする発光装置。 - 第1乃至第5の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

発光素子と、を有し、

前記コンデンサーは、一方の電極が前記第6のトランジスタのゲートに接続され、他方の電極が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第4の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードと前記第5のトランジスタのソース又はドレインの他方に接続され、他方が前記発光素子の一方の電極に接続され、ゲートが前記第5の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記発光素子の他方の電極に接続され、ゲートが前記第3の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第2のノードに接続され、ゲートが前記第3の配線に接続さ れていることを特徴とする発光装置。 - 第1乃至第5の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

画素電極と、を有し、

前記コンデンサーは、一方の電極が前記第6のトランジスタのゲートに接続され、他方の電極が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第3の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第1のノードに接続され、ゲートが前記第5の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第4の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記画素電極に接続され、ゲートが前記第4の配線に接続されていることを特徴とする素子基板。 - 第1乃至第6の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

画素電極と、を有し、

前記コンデンサーは、一方の電極が前記第6のトランジスタのゲートに接続され、他方の電極が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線が接続され、ゲートが前記第3の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第1のノードに接続され、ゲートが前記第5の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第4の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記画素電極に接続され、ゲートが前記第6の配線に接続されていることを特徴とする素子基板。 - 請求項6または請求項7において、

前記第2の配線が、前記コンデンサーの他方の電極に用いられていることを特徴とする素子基板。 - 第1乃至第6の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

画素電極と、

対向電極と、を有し、

前記コンデンサーは、一方の電極が前記第6のトランジスタのゲートに接続され、他方の電極が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第4の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードと前記第5のトランジスタのソース又はドレインの他方に接続され、他方が前記対向電極に接続され、ゲートが前記第5の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記画素電極に接続され、ゲートが前記第3の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第2のノードに接続され、ゲートが前記第6の配線に接続されていることを特徴とする素子基板。 - 第1乃至第7の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

画素電極と、

対向電極と、を有し、

前記コンデンサーは、一方の電極が前記第6のトランジスタのゲートに接続され、他方の電極が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第4の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードと前記第5のトランジスタのソース又はドレインの他方に接続され、他方が前記対向電極に接続され、ゲートが前記第5の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記画素電極に接続され、ゲートが前記第7の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第2のノードに接続され、ゲートが前記第6の配線に接続されていることを特徴とする素子基板。 - 第1乃至第5の配線と、

ゲート、ソースおよびドレインを有する第1乃至第5のトランジスタと、

ゲート、第1乃至第4のノードを有する第6のトランジスタと、

コンデンサーと、

画素電極と、

対向電極と、を有し、

前記コンデンサーは、一方の電極が前記第6のトランジスタのゲートに接続され、他方の電極が前記第2の配線に接続され、

前記第1のトランジスタは、ソース又はドレインの一方が前記第1のノードに接続され、他方が前記第1の配線に接続され、ゲートが前記第4の配線に接続され、

前記第2のトランジスタは、ソース又はドレインの一方が前記第3のノードに接続され、他方が前記第2の配線に接続され、ゲートが前記第3の配線に接続され、

前記第3のトランジスタは、ソース又はドレインの一方が前記第2のノードと前記第5のトランジスタのソース又はドレインの他方に接続され、他方が前記対向電極に接続され、ゲートが前記第5の配線に接続され、

前記第4のトランジスタは、ソース又はドレインの一方が前記第4のノードに接続され、他方が前記画素電極に接続され、ゲートが前記第3の配線に接続され、

前記第5のトランジスタは、ソース又はドレインの一方が前記第6のトランジスタのゲートに接続され、他方が前記第2のノードに接続され、ゲートが前記第3の配線に接続されていることを特徴とする素子基板。 - 請求項9乃至請求項11のいずれか一項において、

前記第2の配線が、前記コンデンサーの他方の電極に用いられていることを特徴とする素子基板。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002160318A JP4034122B2 (ja) | 2002-05-31 | 2002-05-31 | 発光装置及び素子基板 |

| US10/447,268 US7005675B2 (en) | 2002-05-31 | 2003-05-29 | Light-emitting device, method for driving light-emitting device and element board |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002160318A JP4034122B2 (ja) | 2002-05-31 | 2002-05-31 | 発光装置及び素子基板 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004004348A JP2004004348A (ja) | 2004-01-08 |

| JP2004004348A5 JP2004004348A5 (ja) | 2005-09-02 |

| JP4034122B2 true JP4034122B2 (ja) | 2008-01-16 |

Family

ID=30429770

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002160318A Expired - Fee Related JP4034122B2 (ja) | 2002-05-31 | 2002-05-31 | 発光装置及び素子基板 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7005675B2 (ja) |

| JP (1) | JP4034122B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW577179B (en) | 2001-10-09 | 2004-02-21 | Semiconductor Energy Lab | Switching element, display device, light emitting device using the switching element, and semiconductor device |

| JP4202012B2 (ja) | 2001-11-09 | 2008-12-24 | 株式会社半導体エネルギー研究所 | 発光装置及び電流記憶回路 |

| JP4046267B2 (ja) * | 2002-03-26 | 2008-02-13 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP4034122B2 (ja) | 2002-05-31 | 2008-01-16 | 株式会社半導体エネルギー研究所 | 発光装置及び素子基板 |

| GB0227356D0 (en) * | 2002-11-23 | 2002-12-31 | Koninkl Philips Electronics Nv | Colour active matrix electroluminescent display devices |

| KR100653846B1 (ko) * | 2005-04-11 | 2006-12-05 | 실리콘 디스플레이 (주) | 유기 발광 다이오드의 구동 회로 및 구동 방법 |

| KR100547515B1 (ko) * | 2005-07-27 | 2006-01-31 | 실리콘 디스플레이 (주) | 유기발광다이오드 표시장치 및 그 구동방법 |

| KR101324756B1 (ko) | 2005-10-18 | 2013-11-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 그의 구동방법 |

| JP5013697B2 (ja) * | 2005-10-19 | 2012-08-29 | 三洋電機株式会社 | 表示装置 |

| JP4939045B2 (ja) * | 2005-11-30 | 2012-05-23 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| US9792866B2 (en) * | 2005-12-02 | 2017-10-17 | Flextronics Computing Mauritus Ltd. | Detecting and eliminating method for ghosting effect of LCD |

| US8786793B2 (en) * | 2007-07-27 | 2014-07-22 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| JP2010160526A (ja) * | 2010-04-23 | 2010-07-22 | Seiko Epson Corp | 発光装置および電子機器 |

| JP5141812B2 (ja) * | 2011-11-09 | 2013-02-13 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| KR102276118B1 (ko) * | 2014-11-28 | 2021-07-13 | 삼성디스플레이 주식회사 | 박막 트랜지스터 및 이를 포함하는 유기 발광 표시 장치 |

| KR102514412B1 (ko) * | 2016-05-02 | 2023-03-28 | 삼성디스플레이 주식회사 | 반도체소자 및 이를 채용하는 표시장치 |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3898480A (en) * | 1974-04-04 | 1975-08-05 | Rockwell International Corp | Multiphase logic circuit |

| JPS60241266A (ja) | 1984-05-16 | 1985-11-30 | Nippon Telegr & Teleph Corp <Ntt> | 半導体装置及びその製造方法 |

| US4917467A (en) * | 1988-06-16 | 1990-04-17 | Industrial Technology Research Institute | Active matrix addressing arrangement for liquid crystal display |

| JPH0492475A (ja) | 1990-08-08 | 1992-03-25 | Nippon Telegr & Teleph Corp <Ntt> | 相補型薄膜トランジスタ |

| US5258325A (en) * | 1990-12-31 | 1993-11-02 | Kopin Corporation | Method for manufacturing a semiconductor device using a circuit transfer film |

| US5376561A (en) | 1990-12-31 | 1994-12-27 | Kopin Corporation | High density electronic circuit modules |

| JPH04267551A (ja) | 1991-02-22 | 1992-09-24 | Casio Comput Co Ltd | 薄膜トランジスタ |

| JPH10144928A (ja) * | 1996-11-08 | 1998-05-29 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| US6229506B1 (en) * | 1997-04-23 | 2001-05-08 | Sarnoff Corporation | Active matrix light emitting diode pixel structure and concomitant method |

| JP2953465B1 (ja) | 1998-08-14 | 1999-09-27 | 日本電気株式会社 | 定電流駆動回路 |

| JP3686769B2 (ja) * | 1999-01-29 | 2005-08-24 | 日本電気株式会社 | 有機el素子駆動装置と駆動方法 |

| JP3353731B2 (ja) | 1999-02-16 | 2002-12-03 | 日本電気株式会社 | 有機エレクトロルミネッセンス素子駆動装置 |

| JP3259774B2 (ja) | 1999-06-09 | 2002-02-25 | 日本電気株式会社 | 画像表示方法および装置 |

| JP4092857B2 (ja) * | 1999-06-17 | 2008-05-28 | ソニー株式会社 | 画像表示装置 |

| JP2001147659A (ja) | 1999-11-18 | 2001-05-29 | Sony Corp | 表示装置 |

| JP4593740B2 (ja) * | 2000-07-28 | 2010-12-08 | ルネサスエレクトロニクス株式会社 | 表示装置 |

| JP4014831B2 (ja) * | 2000-09-04 | 2007-11-28 | 株式会社半導体エネルギー研究所 | El表示装置及びその駆動方法 |

| SG115435A1 (en) * | 2000-12-28 | 2005-10-28 | Semiconductor Energy Lab | Luminescent device |

| US7199515B2 (en) * | 2001-06-01 | 2007-04-03 | Semiconductor Energy Laboratory Co., Ltd. | Organic light emitting element and light emitting device using the element |

| TW577179B (en) * | 2001-10-09 | 2004-02-21 | Semiconductor Energy Lab | Switching element, display device, light emitting device using the switching element, and semiconductor device |

| JP4202012B2 (ja) * | 2001-11-09 | 2008-12-24 | 株式会社半導体エネルギー研究所 | 発光装置及び電流記憶回路 |

| JP4046267B2 (ja) * | 2002-03-26 | 2008-02-13 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP4034122B2 (ja) | 2002-05-31 | 2008-01-16 | 株式会社半導体エネルギー研究所 | 発光装置及び素子基板 |

-

2002

- 2002-05-31 JP JP2002160318A patent/JP4034122B2/ja not_active Expired - Fee Related

-

2003

- 2003-05-29 US US10/447,268 patent/US7005675B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004004348A (ja) | 2004-01-08 |

| US7005675B2 (en) | 2006-02-28 |

| US20040056257A1 (en) | 2004-03-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11121203B2 (en) | Semiconductor device and method of driving the semiconductor device | |

| US8570256B2 (en) | Device substrate, light emitting device and driving method of light emitting device | |

| JP5106506B2 (ja) | 発光装置 | |

| US7460095B2 (en) | Display device and manufacturing method thereof | |

| US8866714B2 (en) | Semiconductor device and display device utilizing the same | |

| JP3706107B2 (ja) | 発光装置及び電子機器 | |

| JP4034122B2 (ja) | 発光装置及び素子基板 | |

| JPWO2003038796A1 (ja) | 信号線駆動回路及び発光装置 | |

| US7038674B2 (en) | Display device and method for driving the same | |

| JP3939666B2 (ja) | 発光装置及び電子機器 | |

| JP4790070B2 (ja) | 発光装置及び発光装置の駆動方法 | |

| JP4490403B2 (ja) | 発光装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050301 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050301 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070725 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070807 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070928 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071023 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071024 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101102 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101102 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101102 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111102 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111102 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121102 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121102 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131102 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |