JP4053433B2 - 電流出力daコンバータ回路、表示装置及び電子機器 - Google Patents

電流出力daコンバータ回路、表示装置及び電子機器 Download PDFInfo

- Publication number

- JP4053433B2 JP4053433B2 JP2003001495A JP2003001495A JP4053433B2 JP 4053433 B2 JP4053433 B2 JP 4053433B2 JP 2003001495 A JP2003001495 A JP 2003001495A JP 2003001495 A JP2003001495 A JP 2003001495A JP 4053433 B2 JP4053433 B2 JP 4053433B2

- Authority

- JP

- Japan

- Prior art keywords

- current

- transistors

- circuit

- source

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3283—Details of drivers for data electrodes in which the data driver supplies a variable data current for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0248—Precharge or discharge of column electrodes before or after applying exact column voltages

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

Description

【発明の属する技術分野】

本発明は、電流出力回路、DAコンバータ回路の技術に関する。さらには、前記電流出力回路、DAコンバータ回路を搭載した表示装置、電子機器に関する。

【0002】

【従来の技術】

近年、画像の表示を行う薄型表示装置の重要性が増している。薄型表示装置としては、液晶素子を用いて画像の表示を行う液晶表示装置が、薄型、高画質、軽量などの利点を活かして、携帯電話やパソコンをはじめとする種々の用途の表示装置(ディスプレイ装置)として幅広く用いられている。

【0003】

他方で、発光素子を用いた薄型表示装置、発光装置の開発も進められている。この発光素子には、有機材料、無機材料、薄膜材料、バルク材料、分散材料等、広汎にわたる様々な材料を利用した多様な素子が存在する。

【0004】

薄型表示装置向けに特に有望視されている代表的な発光素子は、有機発光ダイオード(OLED)素子である。OLED素子を用いたOLED表示装置は、既存の液晶表示装置以上に薄型、軽量である特長に加え、動画表示に適した高応答速度、高視野角、低電圧駆動などの特長を有しているため、携帯電話や携帯情報端末(PDA)をはじめテレビ、モニターなど、幅広い用途が見込まれ、次世代ディスプレイとして注目されている。

【0005】

中でもアクティブマトリクス(AM)型のOLED表示装置は、パッシブマトリクス(PM)型では困難な、高精細、大画面の表示も可能であるうえ、PM型を上回る低消費電力動作で高信頼性を有し、実用化への期待は大変強い。AM型の他の利点として、駆動回路をパネル上に集積することができれば、パネルの狭額縁化が図れ、高付加価値品となるという点もある。

【0006】

OLED素子は一般に、陽極と、陰極と、該陽極と該陰極との間に有機化合物を含む層とを有する構造をしている、電流駆動型の発光素子である。電流駆動型というのは、OLED素子に流れる電流量と発光輝度が概ね比例するためである。

【0007】

AM型OLED表示装置において画像を表示する駆動方式には、電圧入力方式と電流入力方式がある。前者の電圧入力方式は、画素に入力するビデオ信号として、電圧値形式データのビデオ信号を入力する。他方、後者の電流入力方式は、画素に入力するビデオ信号として、電流値形式データのビデオ信号を入力する。AM型OLED表示装置においては、一般論としては、電流入力方式の方がより好ましい傾向にある。

【0008】

電流入力方式の方が好ましい理由は、表示品位上の問題である。AM型OLED表示装置の画素では、電圧入力方式にしても電流入力方式にしても、該画素のOLED素子の発光輝度を制御する画素駆動トランジスタを、OLED素子に直列に接続している。電圧入力方式では通常、画素駆動トランジスタのゲート電極にビデオ信号の電圧が直接印加される。そのためOLED素子を定電流発光させる場合、画素駆動トランジスタの電気的特性が各々の画素間で均一でなくバラつきを有していると、各画素のOLED素子駆動電流にバラつきが生じる。OLED素子駆動電流のバラつきは、OLED素子の発光輝度のバラつきとなり、画面全体でみると砂嵐状あるいは絨毯模様のムラとして表示画像の品位を低下させる。

【0009】

特に現在通常は、画素駆動トランジスタとして、多結晶(ポリ)シリコンTFTが用いられる。画素駆動トランジスタとして非晶質(アモルファス)シリコン薄膜トランジスタ(TFT)を用いると、高輝度の発光に十分な電流が得られないためである。しかし、ポリシリコンTFTでは、結晶粒界における欠陥等に起因して電気的特性にバラつきが生じやすい。

【0010】

電流入力方式はAM型OLED表示装置において、電圧入力方式よりも一般的には好ましいにもかかわらず、課題もある。その一つが、電流入力方式では電圧入力方式よりも駆動回路がやや複雑で、パネル上に集積しにくいことである。

【0011】

【発明が解決しようとする課題】

代表的な電流入力方式AM型表示装置のパネル構成を、図7〜図9及び図4を用いて説明する。

【0012】

図9がパネル全体の構成図である。画素がマトリクス状に配置された画素部931が存在するだけでなく、ゲート駆動回路921やデータ駆動回路911がパネル上に一体形成されていることが多い。データ駆動回路911内の一点鎖線部913はセレクタ回路である。図9の点線部912a、912bは電流データ出力回路であり、図8の点線部842のような構成をとる。

【0013】

図8の電流データ出力回路は大別すると、シフトレジスタ部、ディジタルデータラッチ部、電流源(電流出力回路)、DAスイッチの4部よりなる。電流源(電流出力回路)とDAスイッチは、合わせて電流出力DAコンバータ回路を構成している。

【0014】

シフトレジスタ部に相当するのが801〜803であり、803は正と反のクロック信号線、チェッカ部801〜802は図4の403に示す回路である。シフトレジスタ部はタイミング信号を順次出力発生させ、ディジタルデータラッチ部がこのタイミング信号に合わせて画像データ(ディジタルデータ)をデータ信号線から読込む。

【0015】

ディジタルデータラッチ部に相当するのが811〜818であり、817は各ビットのデータ信号線、818はラッチ信号線、チェッカ部815〜816は図4の403に示す回路である。図8では画像データ(ディジタルデータ)は3ビットを想定しているため、データ信号線は3本にしてある。また812と813のチェッカ部815〜816は図上では省略してある。ディジタルデータラッチ部からのタイミング信号に合わせて読込まれた画像データ(ディジタルデータ)は、ラッチ信号に同期してDAスイッチ821〜823へ伝達される。

【0016】

電流源(電流出力回路)に相当するのはドット部824であり、具体的な回路構成は図7のドット部791に示す。各ビットに対応する電流源が独立に設けられている。従って例えば701、711、721、731、741よりなる電流源回路は、702、712、722、732、742よりなる電流源回路とは全く独立である。

【0017】

DAスイッチに相当する821〜823は、図7では761〜763としてある。各DAスイッチは並列に設置されているので、DAスイッチがオン状態にある全ビットの電流源の合計電流が、結果的に電流データ出力回路から出力される。

【0018】

パネル外における画像データの処理はディジタル電圧データとして行うのが最も便利であるから、図8の電流データ出力回路における、電流出力DAコンバータ回路は重要である。しかし該DAコンバータでは全ビットについて、別々に電流値を設定する必要があり動作が煩雑となる。またビット数が大きな場合には、電流設定用の入力線数の増加、レイアウトの複雑化、大面積化につながってしまう。

【0019】

本発明は、ディジタル電圧値形式のデータを読込み、アナログ電流値形式のデータを出力する、簡素なDAコンバータ回路を提供することを課題とする。本発明は、電流入力方式のAM型OLED表示装置に使用するデータ駆動回路として用いることができる。

【0020】

【課題を解決するための手段】

まず本発明は、複数の駆動トランジスタを有し、該複数の駆動トランジスタは互いにゲート電極を電気的に接続し、該ゲート電極と前記複数の駆動トランジスタの各ドレインとの間にスイッチを備えたことを特徴とする電流出力回路を含むものである。

【0021】

また本発明は、前記電流出力回路を有し、該電流出力回路が有する複数の駆動トランジスタの各ドレインに、ビットデータに対応してオンオフ制御されるスイッチが備えられていることを特徴とする電流出力DAコンバータ回路を含むものである。

【0022】

さらに本発明は、前記電流出力回路あるいは前記電流出力DAコンバータ回路を使用する表示装置、電子機器を含むものである。

【0023】

【発明の実施の形態】

(実施の形態1)

本発明の実施の一例を図10、図12、図4、図1を用いて説明する。この例は本発明のDAコンバータ回路を、AM型OLED表示装置のデータ駆動回路に使用する場合である。この例では、3ビットのディジタル電圧値形式のデータを画像データとして読込むが、本発明のDAコンバータ回路にビット数の制限がないことは勿論である。

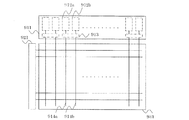

【0024】

図10がパネル全体の構成図である。画素がマトリクス状に配置された画素部1931と、ゲート駆動回路1921と、データ駆動回路1911がパネル上に一体形成されている。データ駆動回路1911内の一点鎖線部1913はセレクタ回路である。図10の点線部1912a、1912bは電流データ出力回路であり、図12の1842のような構成をとる。

【0025】

以下、まず電流データ出力回路1912a、1912bに相当する1842(図12)につき説明し、それからセレクタ回路1913の説明をする。

【0026】

図12の電流データ出力回路1842は大別すると、シフトレジスタ部、ディジタルデータラッチ部、電流源(電流出力回路)、DAスイッチの4部分よりなる。電流源(電流出力回路)とDAスイッチは、合わせて電流出力DAコンバータ回路を構成している。

【0027】

シフトレジスタ部に相当するのが1801〜1803であり、1803は正と反のクロック信号線、チェッカ部1801〜1802は、例えば図4の403に示す回路で構成される。もっともチェッカ部1801〜1802の構成は、403に示す回路に限定はされない。同等の機能を実現するいかなる回路でもよい。

【0028】

シフトレジスタ部1801〜1803はタイミング信号を順次出力発生させ、ディジタルデータラッチ部がこのタイミング信号に合わせて画像データ(ディジタルデータ)をデータ信号線から読込む。

【0029】

ディジタルデータラッチ部に相当するのが1811〜1818であり、1817は各ビットのデータ信号線、1818はラッチ信号線、チェッカ部1815〜1816は図4の403に示す回路を用いることができる。図12では画像データ(ディジタルデータ)は3ビットを想定しているため、データ信号線は3本にしてある。また1812と1813のチェッカ部1815〜1816は図上では省略してある。ディジタルデータラッチ部からのタイミング信号に合わせて読込まれた画像データ(ディジタルデータ)は、ラッチ信号に同期してDAスイッチ1821〜1823へ伝達される。

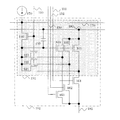

【0030】

電流源(電流出力回路)に相当するのはドット部1824であり、具体的な回路構成は図1のドット部191に示す。トランジスタ101〜103は駆動トランジスタである。またDAスイッチに相当するのが、トランジスタ161〜163(図1)である。このDAスイッチトランジスタは、図12では1821〜1823に相当する。

【0031】

図1では各ビットに対応する駆動トランジスタは、独立に設けられている。例えば第1ビット(MSB)は101、第2ビットは102、第3ビット(LSB)は103であり、各トランジスタのL/Wサイズは、概ね1:2:4としておく。しかし駆動トランジスタ101〜103はゲート電極が電気的に接続されているので、同時に基準電流を設定することが可能である。この点で図1の回路は、図7の回路と異なる。また図1の回路は、図7の回路よりもトランジスタや配線が少ないため、小面積化が果たせる。

【0032】

図1の電流源(電流出力回路)に基準電流を設定する際の動作を説明する。

【0033】

基準電流を設定するときは、まずディジタル信号入力線151〜153からトランジスタ161〜163がオフとなるような信号を入力する。トランジスタ161〜163がnチャネル型の場合は、ロウ(低電圧)信号である。ただし182の先が電気的に開放(ハイインピーダンス)状態となっているなど、出力部182から電流が洩れる心配がない場合には、トランジスタ161〜163をオフにする必要はない。

【0034】

次に電流設定信号入力線110からトランジスタ121〜123、140がオンとなるような信号を入力する。これらのトランジスタがnチャネル型の場合は、ハイ(高電圧)信号である。すると基準電流源170から定電圧源181へと基準電流が流れる。このとき駆動トランジスタ101〜103はゲートとドレインが短絡されている。そのため電流が定常値となった後で、電流設定信号入力線110からトランジスタ121〜123、140がオフとなるような信号を入力すると、駆動トランジスタ101〜103のゲート電圧として基準電流が記憶される。

【0035】

基準電流の設定はこれで終了する。もっとも駆動トランジスタ101〜103のゲートノードからの洩れ電流が微少であるが存在するので、定期的(或いは不定期)に基準電流の設定は反復する必要がある。

【0036】

基準電流設定後、ディジタル信号入力線151〜153から画像信号に対応するディジタル電圧信号を入力する。ディジタル信号入力線151〜153は、電流出力DAコンバータ回路192のデータ入力部に相当する。DAスイッチトランジスタ161〜163は並列に設置されているので、DAスイッチがオン状態にある全ビットの電流源の合計電流が、結果的に出力部182から出力される。こうして、ディジタル電圧データがアナログの電流に変換される。

【0037】

図1の電流出力DAコンバータ回路192において、駆動トランジスタ101〜103のしきい電圧値、電界効果移動度等の電気的特性にバラつきがあると、中間階調の表示が不正確となる可能性がある。しかし、先述の基準電流設定により、最大階調での正確な表示は保証される。

【0038】

また図1の電流出力DAコンバータ回路192においては、基準電流設定は全ビット同時に行われるので、各ビット別々に設定を要する図7の場合と比較し、煩雑さが解消される。

【0039】

図1の例は、3ビットのディジタル電圧値形式のデータを読込み、アナログ電流値形式のデータを出力するDAコンバータ回路であるが、Nビット(Nは2以上の任意の整数)のディジタル電圧値形式のデータを読込む場合についても、同様の構成を用いることができる。

【0040】

また図1の例では、駆動トランジスタ101〜103がnチャネル型であり181が低電圧源であるが、駆動トランジスタ101〜103がpチャネル型であり181が高電圧源であっても同様の構成を用いることができる。さらに他の構成であっても、複数の駆動トランジスタを有し、前記複数の駆動トランジスタは互いにゲート電極を電気的に接続し、該ゲート電極と前記複数の駆動トランジスタの各ドレインとの間にスイッチを備えた電流出力回路を含むものであればよい。

【0041】

パネル外における画像データの処理はディジタル電圧データとして行うのが最も便利であるから、図3の電流データ出力回路における、電流出力DAコンバータ回路192(図1)又は1835(図12)は重要である。

【0042】

しかし例えば出力すべきアナログ電流がゼロ又は極めて微小である場合、長い設定時間を要することとなり、図2の電流出力DAコンバータ回路のみでは不都合である。そのような不都合を回避するために、電流データ出力回路1842にはプリチャージ回路などが付加されていてもよい。

【0043】

以上、電流データ出力回路1912a、1912bに相当する1842につき説明した。次にセレクタ回路1913の説明をする。セレクタ回路1913の具体例の一つとして図11(1955)に回路構成を示すが、これに限定されるものではない。

【0044】

図10のセレクタ回路1913は、電流データ出力回路1912aまたは1912bの出力をデータ線1914aまたは1914bに切替える。図10では、セレクタ回路1個につき電流データ出力回路の個数とデータ線の本数の比は2:2あるが、一般にはこれ以外の比も可能である。ここで本質的なことは、セレクタ回路1個につき電流データ出力回路が複数個設けられる点である。

【0045】

セレクタ回路1個につき電流データ出力回路が複数個設けられることにより、一つの電流データ出力回路がデータ出力している間にも、他の電流データ出力回路の電流源(図1のドット部191)に基準電流設定をすること可能となる。したがって時間の有効活用ができる。

【0046】

例えば、奇数フレーム目では電流データ出力回路1912aに基準電流設定をしつつ1912bでデータ出力し、偶数フレーム目では電流データ出力回路1912bに基準電流設定をしつつ1912aでデータ出力することが可能である。そうすると、データ出力のための期間と別個に基準電流設定のための期間を設ける必要がなくなり、時間の有効活用ができる。

【0047】

図10のセレクタ回路1913は、以上の利点をもたらすことから有用であるが、本発明に必須の要素ではない。よって、図10に代えて他の構成を採用しても構わない。

【0048】

(実施の形態2)

本発明の実施の他の一例を図5、図12、図4、図2を用いて説明する。この例は本発明のDAコンバータ回路を、AM型OLED表示装置のデータ駆動回路に使用する場合である。この例では、3ビットのディジタル電圧値形式のデータを画像データとして読込むが、本発明のDAコンバータ回路にビット数の制限がないことは勿論である。

【0049】

図5がパネル全体の構成図である。画素がマトリクス状に配置された画素部531と、ゲート駆動回路521と、データ駆動回路511がパネル上に一体形成されている。図5の点線部512は電流データ出力回路であり、図12の点線部1842のような構成をとる。なお本例においても、図5に代えて図10のようなセレクタ回路を有するデータ駆動回路を使用してもよいが、説明を簡単にするためパネル全体の構成は図5のとおりとする。

【0050】

以下、電流データ出力回路512に相当する1842につき説明する。

【0051】

図12の電流データ出力回路1842は大別すると、シフトレジスタ部、ディジタルデータラッチ部、電流源(電流出力回路)、DAスイッチの4部分よりなる。電流源(電流出力回路)とDAスイッチは、合わせて電流出力DAコンバータ回路を構成している。

【0052】

シフトレジスタ部に相当するのが1801〜1803であり、1803は正と反のクロック信号線、チェッカ部1801〜1802は、例えば図4の403に示す回路で構成される。もっともチェッカ部1801〜1802の構成は、403に示す回路に限定はされない。同等の機能を実現するいかなる回路でもよい。

【0053】

シフトレジスタ部1801〜1803はタイミング信号を順次出力発生させ、ディジタルデータラッチ部がこのタイミング信号に合わせて画像データ(ディジタルデータ)をデータ信号線から読込む。

【0054】

ディジタルデータラッチ部に相当するのが1811〜1818であり、1817は各ビットのデータ信号線、1818はラッチ信号線、チェッカ部1815〜1816は図4の403に示す回路を用いることができる。図12では画像データ(ディジタルデータ)は3ビットを想定しているため、データ信号線は3本にしてある。また1812と1813のチェッカ部1815〜1816は図上では省略してある。ディジタルデータラッチ部からのタイミング信号に合わせて読込まれた画像データ(ディジタルデータ)は、ラッチ信号に同期してDAスイッチ1821〜1823へ伝達される。

【0055】

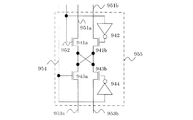

電流源(電流出力回路)に相当するのはドット部1824であり、具体的な回路構成を図2のドット部291に示す。

【0056】

トランジスタ201〜203は駆動トランジスタであり、トランジスタ261〜263はDAスイッチトランジスタであり、図12の1821〜1823に相当する。

【0057】

図2では各ビットに対応する駆動トランジスタは、独立に設けられている。例えば第1ビット(MSB)は201、第2ビットは202、第3ビット(LSB)は203であり、各トランジスタのL/Wサイズは、概ね1:2:4としておくのが望ましい。より一般的に言うと、各トランジスタのL/Wサイズは、概ね20:21:・・・:2N-1(Nは2以上の任意の整数)というように、バイナリの重み付けをするのが望ましい訳である。

【0058】

駆動トランジスタ202〜203はゲート電極が電気的に接続されているので、同時に基準電流を設定することが可能である。この点で図2の回路は、図7の回路と異なる。図2の回路は、図7の回路よりもトランジスタや配線が少ないため、小面積化が果たせる。

【0059】

さらに駆動トランジスタ201のゲート電極は、202〜203のゲート電極と電気的に接続されていない。この点で図2の回路は、図1の回路とも異なる。図2の回路は、第1ビット(MSB)の駆動トランジスタ201については、他のビットとは独立に基準電流を設定するため、MSBデータの電流値の正確性を期することができる。

【0060】

図2の電流源(電流出力回路)に基準電流を設定する際の動作を説明する。

【0061】

基準電流を設定するときは、まずディジタル信号入力線251〜253からトランジスタ261〜263がオフとなるような信号を入力する。トランジスタ261〜263がnチャネル型の場合は、ロウ(低電圧)信号である。ただし282の先が電気的に開放(ハイインピーダンス)状態となっているなど、出力部282から電流が洩れる心配がない場合には、トランジスタ261〜263をオフにする必要はない。

【0062】

次に電流設定信号入力線210からトランジスタ222〜223、240がオンとなるような信号を入力する。これらのトランジスタがnチャネル型の場合は、ハイ(高電圧)信号である。すると基準電流源270から定電圧源281へと基準電流が流れる。このとき駆動トランジスタ202〜203はゲートとドレインが短絡されている。そのため電流が定常値となった後で、電流設定信号入力線210からトランジスタ222〜223、240がオフとなるような信号を入力すると、駆動トランジスタ202〜203のゲート電圧として第2、第3ビットの基準電流が記憶される。

【0063】

これと同時に、或いは別のタイミングで、電流設定信号入力線211からトランジスタ221、241がオンとなるような信号を入力する。これらのトランジスタがnチャネル型の場合は、ハイ(高電圧)信号である。すると基準電流源271から定電圧源281へと基準電流が流れる。このとき駆動トランジスタ201はゲートとドレインが短絡されている。そのため電流が定常値となった後で、電流設定信号入力線211からトランジスタ221、241がオフとなるような信号を入力すると、駆動トランジスタ201のゲート電圧として第1ビット(MSB)の基準電流が記憶される。

【0064】

基準電流の設定はこれで終了する。もっとも駆動トランジスタ201〜203のゲートノードからの洩れ電流が微少であるが存在するので、定期的(或いは不定期)に基準電流の設定は反復する必要がある。

【0065】

基準電流設定後、ディジタル信号入力線251〜253から画像信号に対応するディジタル電圧信号を入力する。ディジタル信号入力線251〜253は、電流出力DAコンバータ回路192のデータ入力部に相当する。DAスイッチトランジスタ261〜263は並列に設置されているので、DAスイッチがオン状態にある全ビットの電流源の合計電流が、結果的に出力部282から出力される。こうして、ディジタル電圧データがアナログの電流に変換される。

【0066】

図2の電流出力DAコンバータ回路292において、駆動トランジスタ202〜203のしきい電圧値、電界効果移動度等の電気的特性にバラつきがあると、中間階調の表示が不正確となる可能性がある。しかし、先述の基準電流設定により、最大階調およびMSBの中間階調での正確な表示は保証される。

【0067】

また図2の電流出力DAコンバータ回路292においては、基準電流設定は第2ビットと第3ビットで同時に行われるので、各ビット別々に設定を要する図7の場合と比較し、煩雑さが解消される。

【0068】

図2の例は、3ビットのディジタル電圧値形式のデータを読込み、アナログ電流値形式のデータを出力するDAコンバータ回路であるが、Nビット(Nは2以上の任意の整数)のディジタル電圧値形式のデータを読込む場合についても、同様の構成を用いることができる。

【0069】

また図2の例では、駆動トランジスタ201〜203がnチャネル型であり281が低電圧源であるが、駆動トランジスタ201〜203がpチャネル型であり281が高電圧源であっても同様の構成を用いることができる。さらに他の構成であっても、複数の駆動トランジスタを有し、前記複数の駆動トランジスタは互いにゲート電極を電気的に接続し、該ゲート電極と前記複数の駆動トランジスタの各ドレインとの間にスイッチを備えた電流出力回路を含むものであればよい。

【0070】

さらにトランジスタ240の位置や容量230の接続ノードは、図2の例に制限されるわけではない。例えば、図1の例と同様にすることも可能である。基準電流設定時における、駆動トランジスタ202〜203のソースゲート間電圧を記憶できるようになっていればよい。

【0071】

加えて図2の例は、2ビット分については図1の例と同じ構成で、他の1ビット分については独立に基準電流を設定する構成であるが、pビット分については図1の例と同じ構成、qビット分については独立に基準電流を設定する構成でもよい(p、qは2以上の任意の整数)。さらにxビット分については図1の例と同じ構成、yビット分についてはそれと独立の図1の例と同じ構成でもよい(x、yは2以上の任意の整数)。

【0072】

パネル外における画像データの処理はディジタル電圧データとして行うのが最も便利であるから、図12の電流データ出力回路における、電流出力DAコンバータ回路292(図2)又は1835(図12)は重要である。

【0073】

しかし例えば出力すべきアナログ電流がゼロ又は極めて微小である場合、長い設定時間を要することとなり、図2の電流出力DAコンバータ回路のみでは不都合である。そのような不都合を回避するために、電流データ出力回路1842にはプリチャージ回路などが付加されていてもよい。

【0074】

以上、電流データ出力回路512に相当する1842につき説明した。

【0075】

(実施の形態3)

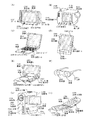

実施の形態3では、本発明の表示装置、電子機器を、いくつか例示する。

【0076】

本発明の電子機器、表示装置としては、モニター、ビデオカメラ、ディジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(オーディオコンポ、カーオーディオ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などと、これらに搭載されている表示装置が挙げられる。これら電子機器の具体例を図6に示す。

【0077】

図6(A)はモニターである。この例は筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含んでいる。本発明の表示装置は表示部2003に用いることができる。なおモニターには、パソコン用、TV放送受信用、広告表示用などのすべての情報表示装置が含まれる。

【0078】

図6(B)はディジタルスチルカメラである。この例は本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含んでいる。本発明の表示装置は表示部2102に用いることができる。

【0079】

図6(C)はノート型パーソナルコンピュータである。この例は本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含んでいる。本発明の表示装置は表示部2203に用いることができる。

【0080】

図6(D)はモバイルコンピュータである。この例は本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含んでいる。本発明の表示装置は表示部2302に用いることができる。

【0081】

図6(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)である。この例は本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(DVD等)読込み部2405、操作キー2406、スピーカー部2407等を含んでいる。本発明の表示装置は、表示部A2403、表示部B2404に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

【0082】

図6(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)である。この例は本体2501、表示部2502、アーム部2503等を含んでいる。本発明の表示装置は表示部2502に用いることができる。

【0083】

図6(G)はビデオカメラである。この例は本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609等を含んでいる。本発明の表示装置は表示部2602に用いることができる。

【0084】

図6(H)は携帯電話である。この例は本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含んでいる。本発明の表示装置は表示部2703に用いることができる。なお、表示部2703は黒色背景に白色文字を表示することで、携帯電話の消費電力を抑制することができる。

【0085】

このように、本発明の適用範囲は極めて広く、あらゆる分野の電子機器等に使用することが可能である。

【0086】

【発明の効果】

本発明は、複数の駆動トランジスタを有し、前記複数の駆動トランジスタは互いにゲート電極を電気的に接続し、該ゲート電極と前記複数の駆動トランジスタの各ドレインとの間にスイッチを備えたことを特徴とする、電流出力回路を含むものである。

該電流出力回路を用いることにより、ディジタル電圧値形式のデータを読込み、アナログ電流値形式のデータを出力する、簡素なDAコンバータ回路を提供することができる。

本発明は、電流入力方式のAM型OLED表示装置に使用するデータ駆動回路などに用いることができる。

【図面の簡単な説明】

【図1】 本発明の電流出力回路、DAコンバータ回路の例を示す図。

【図2】 本発明の電流出力回路、DAコンバータ回路の例を示す図。

【図3】 セレクタ回路の例を示す図。

【図4】 ラッチ回路の構成例を示す図。

【図5】 表示装置のパネル構成例を示す図。

【図6】 本発明の表示装置、電子機器の例を示す図。

【図7】 公知の電流出力回路、DAコンバータ回路を示す図。

【図8】 DAコンバータ回路を用いたデータドライバの構成例を示す図。

【図9】 表示装置のパネル構成例を示す図。

【図10】 本発明の表示装置のパネル構成例を示す図。

【図11】 本発明のセレクタ回路の例を示す図。

【図12】 本発明のDAコンバータ回路を用いたデータドライバの構成例を示す図。

Claims (5)

- 第1乃至第3の駆動トランジスタ、第1乃至第8のトランジスタ、第1及び第2の電流源、及び定電圧源を有し、

前記第1の駆動トランジスタは、ゲートは前記第1のトランジスタのソース又はドレインの一方に、ソース又はドレインの一方は前記第2及び前記第3のトランジスタの各々のソース又はドレインの一方に、ソース又はドレインの他方は前記定電圧源に電気的に接続され、

前記第2の駆動トランジスタは、ゲートは前記第4のトランジスタのソース又はドレインの一方に、ソース又はドレインの一方は前記第5及び前記第6のトランジスタの各々のソース又はドレインの一方に、ソース又はドレインの他方は前記定電圧源に電気的に接続され、

前記第3の駆動トランジスタは、ゲートは前記第4のトランジスタのソース又はドレインの一方に、ソース又はドレインの一方は前記第7及び前記第8のトランジスタの各々のソース又はドレインの一方に、ソース又はドレインの他方は前記定電圧源に電気的に接続され、

前記第1及び前記第2のトランジスタの各々のゲートは、第1の電流設定信号入力線に電気的に接続され、

前記第4、前記第5及び前記第7のトランジスタの各々のゲートは、第2の電流設定信号入力線に電気的に接続され、

前記第1及び前記第2のトランジスタの各々のソース又はドレインの他方は、前記第1の電流源に電気的に接続され、

前記第4、前記第5及び前記第7のトランジスタの各々のソース又はドレインの他方は、前記第2の電流源に電気的に接続され、

前記第3のトランジスタのゲートは、第1のデジタル信号入力線に電気的に接続され、

前記第6のトランジスタのゲートは、第2のデジタル信号入力線に電気的に接続され、

前記第8のトランジスタのゲートは、第3のデジタル信号入力線に電気的に接続され、

前記第3、前記第6及び前記第8のトランジスタの各々のソース又はドレインの他方は、出力部に電気的に接続され、

前記第1のデジタル信号入力線を介して前記第3のトランジスタのゲートに入力されるデジタル信号は最上位ビットの信号であることを特徴とする電流出力DAコンバータ回路。 - 請求項1において、

前記第1、前記第2及び前記第3の駆動トランジスタのチャネル長/チャネル幅は、1:2:4であることを特徴とする電流出力DAコンバータ回路。 - 請求項1に記載の前記電流出力DAコンバータ回路を有することを特徴とする表示装置。

- 請求項1に記載の前記電流出力DAコンバータ回路を有することを特徴とする電子機器。

- 請求項3に記載の前記表示装置を有することを特徴とする電子機器。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003001495A JP4053433B2 (ja) | 2003-01-07 | 2003-01-07 | 電流出力daコンバータ回路、表示装置及び電子機器 |

| TW092135622A TWI354957B (en) | 2003-01-07 | 2003-12-16 | Current output circuit, current output da converte |

| US10/745,497 US7348947B2 (en) | 2003-01-07 | 2003-12-29 | Circuit, display device, and electronic apparatus |

| CN200410001385.XA CN1518232B (zh) | 2003-01-07 | 2004-01-07 | 电路,显示设备以及电子装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003001495A JP4053433B2 (ja) | 2003-01-07 | 2003-01-07 | 電流出力daコンバータ回路、表示装置及び電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004215109A JP2004215109A (ja) | 2004-07-29 |

| JP2004215109A5 JP2004215109A5 (ja) | 2006-02-09 |

| JP4053433B2 true JP4053433B2 (ja) | 2008-02-27 |

Family

ID=32708817

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003001495A Expired - Fee Related JP4053433B2 (ja) | 2003-01-07 | 2003-01-07 | 電流出力daコンバータ回路、表示装置及び電子機器 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7348947B2 (ja) |

| JP (1) | JP4053433B2 (ja) |

| CN (1) | CN1518232B (ja) |

| TW (1) | TWI354957B (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4566528B2 (ja) * | 2002-12-05 | 2010-10-20 | シャープ株式会社 | 表示装置 |

| US7928937B2 (en) * | 2004-04-28 | 2011-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| KR100600314B1 (ko) * | 2004-11-17 | 2006-07-18 | 삼성에스디아이 주식회사 | 발광 표시 장치 및 그것의 데이터 구동 칩 |

| US7570233B2 (en) * | 2004-11-24 | 2009-08-04 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| JP4438069B2 (ja) * | 2004-12-03 | 2010-03-24 | キヤノン株式会社 | 電流プログラミング装置、アクティブマトリクス型表示装置およびこれらの電流プログラミング方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| NL8500086A (nl) * | 1985-01-16 | 1986-08-18 | Philips Nv | Digitaal-analoog omzetter. |

| JP2799712B2 (ja) | 1988-08-20 | 1998-09-21 | 株式会社日立製作所 | Da変換器 |

| JP3062035B2 (ja) * | 1995-03-31 | 2000-07-10 | インターナショナル・ビジネス・マシーンズ・コーポレ−ション | D/aコンバータ |

| JP3169884B2 (ja) * | 1998-02-26 | 2001-05-28 | 日本電気アイシーマイコンシステム株式会社 | ディジタル・アナログ変換器及びそのテスト方法 |

| JP3252897B2 (ja) | 1998-03-31 | 2002-02-04 | 日本電気株式会社 | 素子駆動装置および方法、画像表示装置 |

| US6545514B2 (en) * | 1999-04-26 | 2003-04-08 | Stmicroelectronics N.V. | Drive circuit for inductive loads |

| JP2000347159A (ja) * | 1999-06-09 | 2000-12-15 | Hitachi Ltd | 液晶表示装置 |

| JP2001147659A (ja) | 1999-11-18 | 2001-05-29 | Sony Corp | 表示装置 |

| JP2002215095A (ja) * | 2001-01-22 | 2002-07-31 | Pioneer Electronic Corp | 発光ディスプレイの画素駆動回路 |

| JP4982014B2 (ja) * | 2001-06-21 | 2012-07-25 | 株式会社日立製作所 | 画像表示装置 |

| CN100365688C (zh) * | 2001-08-29 | 2008-01-30 | 日本电气株式会社 | 用于驱动电流负载器件的半导体器件及提供的电流负载器件 |

| US7576734B2 (en) * | 2001-10-30 | 2009-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Signal line driving circuit, light emitting device, and method for driving the same |

| JP4498669B2 (ja) * | 2001-10-30 | 2010-07-07 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置、及びそれらを具備する電子機器 |

| JP4451057B2 (ja) * | 2002-12-27 | 2010-04-14 | シャープ株式会社 | 表示装置の駆動方法、表示装置、および、そのプログラム |

| TWI405156B (zh) * | 2003-01-06 | 2013-08-11 | Semiconductor Energy Lab | 電路、顯示裝置及電子機器 |

-

2003

- 2003-01-07 JP JP2003001495A patent/JP4053433B2/ja not_active Expired - Fee Related

- 2003-12-16 TW TW092135622A patent/TWI354957B/zh not_active IP Right Cessation

- 2003-12-29 US US10/745,497 patent/US7348947B2/en active Active

-

2004

- 2004-01-07 CN CN200410001385.XA patent/CN1518232B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7348947B2 (en) | 2008-03-25 |

| US20040135779A1 (en) | 2004-07-15 |

| CN1518232B (zh) | 2011-08-17 |

| TW200419493A (en) | 2004-10-01 |

| TWI354957B (en) | 2011-12-21 |

| CN1518232A (zh) | 2004-08-04 |

| JP2004215109A (ja) | 2004-07-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6909243B2 (en) | Light-emitting device and method of driving the same | |

| JP5487254B2 (ja) | 半導体装置 | |

| US7271784B2 (en) | Display device and driving method thereof | |

| US9620060B2 (en) | Semiconductor device including transistors, switches and capacitor, and electronic device utilizing the same | |

| EP1388842B1 (en) | Multi-window display device and method of driving the same | |

| US9626913B2 (en) | Current source circuit, a signal line driver circuit and a driving method thereof and a light emitting device | |

| KR20060010791A (ko) | 반도체 장치 | |

| JP2003323153A (ja) | 発光装置 | |

| US7049991B2 (en) | Semiconductor device, digital-analog converter and display device thereof | |

| US7961160B2 (en) | Display device, a driving method of a display device, and a semiconductor integrated circuit incorporated in a display device | |

| JP2005031598A (ja) | 表示装置及びその駆動方法 | |

| JP4397811B2 (ja) | 半導体装置、el表示装置、及び電子機器 | |

| JP4034086B2 (ja) | 発光装置及び電子機器 | |

| JP4053433B2 (ja) | 電流出力daコンバータ回路、表示装置及び電子機器 | |

| US6919834B2 (en) | Circuit, display device, and electronic device | |

| JP4339132B2 (ja) | 回路、表示装置及び電子機器 | |

| JP2004198683A (ja) | 表示装置 | |

| JP4574128B2 (ja) | 発光装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051220 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051220 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070906 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070911 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071106 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071205 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101214 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101214 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101214 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111214 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111214 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121214 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121214 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131214 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |