KR20140013931A - 액정 표시 장치 - Google Patents

액정 표시 장치 Download PDFInfo

- Publication number

- KR20140013931A KR20140013931A KR1020130082985A KR20130082985A KR20140013931A KR 20140013931 A KR20140013931 A KR 20140013931A KR 1020130082985 A KR1020130082985 A KR 1020130082985A KR 20130082985 A KR20130082985 A KR 20130082985A KR 20140013931 A KR20140013931 A KR 20140013931A

- Authority

- KR

- South Korea

- Prior art keywords

- liquid crystal

- signal

- pixel

- video signal

- potential

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0245—Clearing or presetting the whole screen independently of waveforms, e.g. on power-on

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0261—Improving the quality of display appearance in the context of movement of objects on the screen or movement of the observer relative to the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

- G09G2320/046—Dealing with screen burn-in prevention or compensation of the effects thereof

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0626—Adjustment of display parameters for control of overall brightness

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/027—Arrangements or methods related to powering off a display

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/3406—Control of illumination source

Abstract

본 발명은 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 액정 표시 장치를 제공한다. 특히 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 데다가 액정 소자의 열화를 억제할 수 있는 액정 표시 장치를 제공한다.

트랜지스터 및 액정 소자를 포함하는 복수의 화소와, 복수의 화소에 적어도 비디오 신호와 리셋 신호를 입력하는 구동 회로를 갖고, 구동 회로는 비디오 신호의 극성을 m프레임(m은 2 이상의 자연수)마다 반전시키면서 화소에 입력하고, 비디오 신호의 비입력 기간에 리셋 신호를 화소에 입력한다.

트랜지스터 및 액정 소자를 포함하는 복수의 화소와, 복수의 화소에 적어도 비디오 신호와 리셋 신호를 입력하는 구동 회로를 갖고, 구동 회로는 비디오 신호의 극성을 m프레임(m은 2 이상의 자연수)마다 반전시키면서 화소에 입력하고, 비디오 신호의 비입력 기간에 리셋 신호를 화소에 입력한다.

Description

본 발명은 액정 표시 장치 및 액정 표시 장치의 구동 방법에 관한 것이다.

절연 표면을 갖는 기판 위에 형성된 반도체 박막을 사용하여 박막 트랜지스터(TFT)를 구성하는 기술이 주목을 받고 있다. 박막 트랜지스터는 집적 회로(IC)나 화상 표시 장치(표시 장치)와 같은 전자 디바이스에 널리 응용되고 있다.

박막 트랜지스터를 사용한 표시 장치로서는 각 화소에 스위칭 소자로서 박막 트랜지스터를 제공한 액티브 매트릭스형 액정 표시 장치를 들 수 있다. 액정 표시 장치는 휴대 전화나 노트북 퍼스널 컴퓨터 등 휴대 기기로부터 텔레비전 등 대형 기기까지 폭넓게 사용되고 있다. 이와 같은 액정 표시 장치를 사용한 전자 기기에서는 소비 전력의 저감이 큰 과제이다. 예를 들어, 휴대 기기에서는 소비 전력의 절감이 더 긴 연속 동작 시간으로 이어지며, 대형 텔레비전 등에서는 소비 전력의 절감이 전기 요금의 절감으로 이어진다.

여기서, 액정 표시 장치에서는 정지 화상을 표시하는 동안에도 비디오 신호의 재기록이 계속되며, 재기록에 따라 전력이 소비된다. 이와 같은 소비 전력을 절감하기 위한 방법으로서, 예를 들어 정지 화상 표시에서, 화면을 한 번 주사하여 비디오 신호를 기록한 후에 비(非)주사 기간으로서 주사 기간보다 긴 휴지 기간을 설정하는 기술이 보고되어 있다(예를 들어, 특허문헌 1 및 비특허문헌 1 참조).

K.Tsuda 등. IDW' 02 Proc., pp.295-298

그러나, 상기 액정 표시 장치는 정지 화상을 표시하는 데 기능하는 것이며, 동영상을 표시할 때는 휴지 기간을 설정할 수 없기 때문에 소비 전력을 저감하지 못한다.

상술한 문제를 감안하여, 본 발명의 일 형태에서는, 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 액정 표시 장치를 제공하는 것을 목적 중 하나로 한다. 특히 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 데다가 액정 소자의 열화를 억제할 수 있는 액정 표시 장치를 제공하는 것을 목적 중 하나로 한다.

본 발명의 일 형태는 트랜지스터 및 트랜지스터와 전기적으로 접속된 액정 소자를 포함하는 복수의 화소와, 복수의 화소에 적어도 비디오 신호와 리셋 신호를 입력하는 구동 회로를 가지며, 구동 회로는 비디오 신호의 극성을 m프레임(m은 2 이상의 자연수)마다 반전시키면서 화소에 입력하고, 비디오 신호의 비입력 기간에 리셋 신호를 화소에 입력하는 액정 표시 장치이다.

상기에 있어서, 구동 회로는 전위가 공통 전위보다 높은 기간과, 전위가 공통 전위보다 낮은 기간을 적어도 한 번 이상 반복한 후에, 전위가 공통 전위와 대략 같은 전위가 되는 리셋 신호를 화소에 입력하는 것이 바람직하다. 또한, 액정 소자는 한 쌍의 전극을 가지며, 리셋 신호를 입력하여 화소의 액정 소자의 한 쌍의 전극 사이의 전위차를 대략 0V로 한 후, 이 화소의 트랜지스터를 오프 상태로 하는 것이 바람직하다. 또한, 구동 회로가 복수의 화소 모두에 리셋 신호를 입력한 후에 전원의 공급이 차단되는 것이 바람직하다.

또한, 상기에 있어서, 복수의 화소에 광을 조사하는 백 라이트가 추가적으로 제공되고, 백 라이트가 비점등 상태일 때, 구동 회로가 리셋 신호를 화소에 입력하는 것이 바람직하다. 또한, 구동 회로는 화소 전체가 재기록되는 타이밍에 리셋 신호를 화소에 입력하는 것이 바람직하다. 또한, 설정한 시간에 액정 표시 장치를 기동시키는 타이머가 제공되고, 액정 표시 장치가 전원 오프 상태로부터 타이머로 기동하였을 때, 구동 회로가 리셋 신호를 화소에 입력하여도 좋다.

또한 트랜지스터로서, 산화물 반도체를 포함하는 트랜지스터를 사용하는 것이 바람직하다.

또한, 본 명세서 등에 있어서, '대략 같은 전위'라고 기재한 경우에는 엄밀하게 같은 전위의 경우뿐만 아니라, 차이를 충분히 무시할 수 있을 정도로 전위가 다른 경우도 포함한다. 또한, 본 명세서 등에 있어서, '전위차를 대략 0V로 한다'라고 기재한 경우에는 엄밀하게 전위차를 0V로 하는 경우뿐만 아니라, 충분히 무시할 수 있을 정도의 전위차가 생기는 경우도 포함한다.

또한, 본 명세서 등에서 '위'나 '아래'라는 용어는 구성 요소의 위치 관계가 '바로 위' 또는 '바로 아래'인 것으로 한정하는 것이 아니다. 예를 들어, '게이트 절연층 위의 게이트 전극'이라는 표현은 게이트 절연층과 게이트 전극 사이에 다른 구성 요소를 포함하는 것을 제외하지 않는다.

또한, 본 명세서 등에 있어서, '전극'이나 '배선'이라는 용어는 이들 구성 요소를 기능적으로 한정하는 것이 아니다. 예를 들어, '전극'은 '배선'의 일부분으로서 사용될 수 있고, 그 반대도 역시 마찬가지이다. 또한, '전극'이나 '배선'이라는 용어는 복수의 '전극'이나 '배선'이 일체로 되어 형성되는 경우 등도 포함한다.

또한, '소스'나 '드레인'의 기능은 상이한 극성의 트랜지스터를 채용하는 경우나, 회로 동작에서 전류의 방향이 변화하는 경우 등에는 서로 바뀔 수 있다. 따라서, 본 명세서 등에 있어서는, '소스'나 '드레인'의 용어는 서로 바꾸어 사용할 수 있다.

또한, 본 명세서 등에서 '전기적으로 접속된다'라는 표현에는 '어떤 전기적 작용을 갖는 것'을 통하여 접속되는 경우가 포함된다. 여기서, '어떤 전기적 작용을 갖는 것'은 접속 대상 사이에서 전기 신호를 주고받고 할 수 있는 것이면 특별한 제한은 없다.

예를 들어, '어떤 전기적 작용을 갖는 것'에는 전극이나 배선을 비롯하여 트랜지스터 등 스위칭 소자, 저항 소자, 인덕터, 커패시터, 기타 각종 기능을 갖는 소자 등이 포함된다.

본 발명의 일 형태는 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 액정 표시 장치를 제공할 수 있다. 특히 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 데다가 액정의 열화를 억제할 수 있는 액정 표시 장치를 제공할 수 있다.

도 1은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 흐름도.

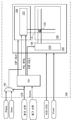

도 2는 본 발명의 일 형태에 따른 액정 표시 장치를 설명하기 위한 블록도.

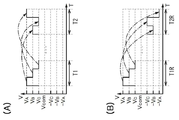

도 3은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 타이밍 차트.

도 4는 본 발명의 일 형태에 따른 액정 표시 장치를 설명하기 위한 블록도.

도 5는 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 모식도.

도 6은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 타이밍 차트.

도 7은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 타이밍 차트.

도 8은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 타이밍 차트.

도 9는 본 발명의 일 형태에 따른 액정 표시 장치의 상면도 및 단면도.

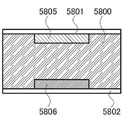

도 10은 본 발명의 일 형태에 따른 액정 표시 장치의 액정 소자를 설명하기 위한 단면도.

도 11은 본 발명의 일 형태에 따른 액정 표시 장치의 액정 소자를 설명하기 위한 단면도.

도 12는 본 발명의 일 형태에 따른 액정 표시 장치의 액정 소자를 설명하기 위한 단면도.

도 13은 본 발명의 일 형태에 따른 액정 표시 장치를 사용한 전자 기기를 도시한 도면.

도 14는 본 발명의 일 형태에 따른 액정 표시 장치를 사용한 전자 기기를 도시한 도면.

도 15는 본 발명의 일 형태에 따른 액정 표시 장치를 사용한 전자 기기를 도시한 도면.

도 2는 본 발명의 일 형태에 따른 액정 표시 장치를 설명하기 위한 블록도.

도 3은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 타이밍 차트.

도 4는 본 발명의 일 형태에 따른 액정 표시 장치를 설명하기 위한 블록도.

도 5는 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 모식도.

도 6은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 타이밍 차트.

도 7은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 타이밍 차트.

도 8은 본 발명의 일 형태에 따른 액정 표시 장치의 동작을 설명하기 위한 타이밍 차트.

도 9는 본 발명의 일 형태에 따른 액정 표시 장치의 상면도 및 단면도.

도 10은 본 발명의 일 형태에 따른 액정 표시 장치의 액정 소자를 설명하기 위한 단면도.

도 11은 본 발명의 일 형태에 따른 액정 표시 장치의 액정 소자를 설명하기 위한 단면도.

도 12는 본 발명의 일 형태에 따른 액정 표시 장치의 액정 소자를 설명하기 위한 단면도.

도 13은 본 발명의 일 형태에 따른 액정 표시 장치를 사용한 전자 기기를 도시한 도면.

도 14는 본 발명의 일 형태에 따른 액정 표시 장치를 사용한 전자 기기를 도시한 도면.

도 15는 본 발명의 일 형태에 따른 액정 표시 장치를 사용한 전자 기기를 도시한 도면.

이하에서는 본 발명의 실시형태에 대해서 도면을 사용하여 자세히 설명한다. 다만, 본 발명은 이하의 설명에 한정되지 않으며, 그 형태 및 자세한 사항을 다양하게 변경할 수 있다는 것은 당업자라면 용이하게 이해할 수 있다. 또한, 본 발명은 이하에 기재된 실시형태의 내용에 한정하여 해석되는 것이 아니다.

또한, 각 실시형태의 도면 등에 도시한 각 구성의 크기, 층의 두께, 신호 파형, 또는 영역은 명료화를 위하여 과장되어 표기되는 경우가 있다. 따라서 반드시 그 스케일에 한정되지 않는다.

또한 본 명세서에서 사용한 제 1, 제 2, 제 3, 내지 제 N(N은 자연수)이라는 서수사는 구성 요소의 혼동을 피하기 위하여 붙인 것이며, 수(數)적으로 한정하는 것이 아님을 부기한다.

(실시형태 1)

본 실시형태에서는 본 발명의 일 형태에 따른 액정 표시 장치 및 액정 표시 장치의 구동 방법에 대하여 도 1 내지 도 8을 이용하여 설명한다.

우선, 본 실시형태에 제시되는 액정 표시 장치의 구동 방법에 대해서, 도 1에 도시한 흐름도를 참조하여 설명한다.

도 1에 도시한 바와 같이, 본 실시형태에 제시되는 액정 표시 장치는 전원 공급이 시작되면, 구동 회로로부터 각 화소에 비디오 신호를 입력한다. 입력되는 비디오 신호의 극성은 m프레임(m은 2 이상의 자연수) 동안 유지된다. 바꿔 말하면, 본 실시형태에 제시되는 액정 표시 장치에서는 m프레임마다 비디오 신호의 극성이 반전된다. 여기서, m프레임 기간으로서는 액정의 열화를 억제하기 위해서, 예를 들어 1초 정도 이하로 하는 것이 바람직하다. 다만, m프레임 기간은 이것에 한정되는 것이 아니며, 액정 소자에 인가하는 전압이나 액정 재료 등에 맞추어 적절히 설정하면 좋다. 또한, 비디오 신호의 극성은 예를 들어, 대향 전극의 전위(이하에서는 공통 전위라고도 부름)를 기준으로 결정할 수 있다.

다음에, 극성이 반전된 비디오 신호가 구동 회로로부터 각 화소에 입력되고, m프레임 기간 후에 비디오 신호의 극성이 다시 반전된다. 이하에서, m프레임마다 극성을 반전시키면서, 구동 회로로부터 각 화소에 비디오 신호가 반복적으로 입력되어 화상이 표시된다.

종래 수행되어 온 1프레임마다 반전 구동에서는 화소에 인가되는 전압 레벨이 큰 경우에, 프레임 간의 전압 레벨의 크기가 변화하지 않아도, 신호의 반전에 의해 비디오 신호의 변화량이 커져 소비 전력이 커졌다. 한편, 본 실시형태에 제시되는 액정 표시 장치의 구동 방법에서는 같은 극성의 비디오 신호를 m프레임 기간 이상 연속적으로 기록할 수 있기 때문에, 비디오 신호의 변화량을 저감하여 소비 전력을 절감할 수 있다. 또한, 상기 액정 표시 장치의 구동 방법은 표시 화상이 정지 화상이든 동영상이든 어느 쪽이라도 가능하기 때문에, 동영상을 표시하는 경우에도 소비 전력을 저감할 수 있다.

상술한 바와 같이 구동 회로가 각 화소에 비디오 신호를 입력함으로써, 본 실시형태에 제시되는 액정 표시 장치는 화상을 표시할 수 있다. 한편, 액정 표시 장치를 비표시 상태로 할 때는 구동 회로에 정지 신호가 입력되어, 상기 비디오 신호의 입력 사이클이 종료된다. 도 1에 도시한 바와 같이, 정지 신호가 구동 회로에 입력되면, 구동 회로로부터 각 화소에 비디오 신호가 이니라 리셋 신호가 입력된다. 모든 회로에 리셋 신호가 입력되면, 액정 표시 장치에 대한 전원의 공급이 차단된다.

여기서, 정지 신호란, 액정 표시 장치의 화상 표시 상태를 종료시키고, 화상 비표시 상태로 이행시키는 신호이다. 예를 들어, 리모트 컨트롤러나 버튼 조작 등에 의해 직접 제어하여 발신할 수 있는 신호로 하여도 좋고, 비디오 신호의 기초가 되는 데이터 신호 등을 측정하여 발신할 수 있는 신호로 하여도 좋고, 액정 표시 장치에 제공되는 백 라이트의 광량 등을 측정하여 발신할 수 있는 신호로 하여도 좋다.

또한, 리셋 신호란, 각 화소에 입력하여 액정의 열화를 억제하기 위한 신호이다. 여기서, 액정 소자에 양 또는 음의 극성으로 유지된 전계를 장시간 동안 인가시키면, 액정이 열화되어 상기 액정 소자의 전기 특성에 이상이 발생한다. 이와 같이 본 실시형태에 제시되는 액정 표시 장치의 구동 방법에서는 같은 극성의 비디오 신호를 m프레임 기간 이상 연속적으로 기록하기 때문에, 1프레임마다 비디오 신호의 극성을 반전시키는 종래의 구동 방법과 비교하면, 같은 극성으로 유지된 전계가 액정 소자에 장시간 인가된다.

그래서, 본 실시형태에 제시되는 구동 방법에서는 정지 신호를 입력한 후, 화소에 리셋 신호를 입력함으로써 액정의 열화를 억제한다. 리셋 신호로서는 예를 들어, 양의 극성과 음의 극성으로 적어도 한 번 이상 반전되는 전위를 입력하는 것이 바람직하다. 이 때, 양의 극성의 전위 및 음의 극성의 전위의 절대값은 가능한 한 큰 값으로 하는 것이 바람직하다. 또한, 리셋 신호의 극성도 비디오 신호의 극성과 마찬가지로, 예를 들어 공통 전위를 기준으로 결정할 수 있다. 즉, 리셋 신호는 전위가 공통 전위보다 높은 기간과, 전위가 공통 전위보다 낮은 기간을 적어도 한 번 이상 반복한다.

또한, 이와 같이 리셋 신호로서 적어도 한 번 이상 극성이 반전시키면서 전위를 입력한 후, 리셋 신호의 전위를 공통 전위와 대략 같은 전위로 하는 것이 바람직하다. 또한, 이와 같이 하여 액정 소자의 전극 간의 전위차를 대략 0V로 한 후, 화소에 제공된 액정 소자와 전기적으로 접속된 트랜지스터를 오프 상태로 하는 것이 바람직하다.

또한, 리셋 신호를 입력할 때는 백 라이트를 비점등 상태로 하는 것이 바람직하다. 백 라이트를 비점등 상태로 하여 리셋 신호를 입력함으로써, 리셋 신호의 입력으로 인한 화상 왜곡의 표시를 방지할 수 있다. 상술한 바와 같이, 정시 신호를 백 라이트의 점등과 연동시키면, 백 라이트가 비점등 상태일 때의 리셋 신호의 입력을 용이하게 수행할 수 있다.

또한, 도 1에서는 액정 표시 장치에 대한 전원 공급 차단 전에 리셋 신호를 입력하지만, 본 발명은 이것에 한정되지 않는다. 액정 표시 장치의 화소 전체가 재기록되는 타이밍, 예를 들어 액정 표시 장치의 화면을 암전시킬 때 등에 상기 리셋 신호를 입력할 수도 있다. 또한, 예를 들어, 상기 액정 표시 장치가 텔레비전 수신기로서 사용되는 경우에는, 채널이나 입력 장치를 전환할 때, 프로그램이 CF로 전환될 때 등에 상기 리셋 신호를 입력할 수도 있다.

또한, 액정 표시 장치가 화상 비표시 상태일 때, 타이머로 설정한 시간에 상기 리셋 신호를 입력하여 액정의 열화를 억제하는 구성으로 할 수도 있다. 액정 표시 장치가 사용되지 않는 특정한 시간(예를 들어, 심야 등 일반적으로 사용자가 액정 표시 장치를 사용하지 않는 시간 등)으로 설정하여 타이머로 액정 표시 장치를 기동시켜, 상기 리셋 신호를 입력시키면 좋다. 이 때, 화상 왜곡의 표시를 방지하기 위해서, 백 라이트를 비점등 상태로 하는 것이 바람직하다.

이와 같이 리셋 신호의 입력을 수행함으로써, 극성이 반전된 전계가 액정 소자에 적어도 한 번 이상 짧은 시간으로 인가되기 때문에, 상술한 바와 같이, 같은 극성의 비디오 신호를 m프레임 기간 이상 연속적으로 기록하여도 액정의 열화를 억제할 수 있다.

상술한 바와 같이 함으로써, 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 액정 표시 장치를 제공할 수 있다. 특히 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 데다가 액정의 열화를 억제할 수 있는 액정 표시 장치를 제공할 수 있다.

이하에서, 본 실시형태에 제시되는 액정 표시 장치의 구성과 구동 방법의 일례에 대해서 도 2 내지 도 8을 사용하여 설명한다.

도 2에 본 발명의 일 형태에 따른 액정 표시 장치(100)의 블록도를 도시하였다. 액정 표시 장치(100)는 표시 제어 신호 생성 회로(101)와, 선택 회로(102)와, 표시 패널(103)을 갖는다.

표시 패널(103)은 게이트 라인 구동 회로(104), 소스 라인 구동 회로(105), 및 화소부(106)를 갖는다. 화소부(106)는 복수의 화소(108)를 가지며, 화소(108)에 적어도 한 쌍의 전극을 갖는 액정 소자가 제공되어 있다. 게이트 라인 구동 회로(104)로부터 게이트 라인(109)에 공급되는 주사선 신호에 의해, 소스 라인(110)에 공급되는 비디오 신호의 화소(108)에 대한 기록이 제어된다. 또한, 소스 라인 구동 회로(105)는 디지털/아날로그 변환 회로(107)를 갖는 것이 바람직하다. 또한, 본 명세서 등에 있어서, 구동 회로라고 기재하는 경우에는 게이트 라인 구동 회로(104)와 소스 라인 구동 회로(105)를 포함하며, 더구나 표시 제어 신호 생성 회로(101), 선택 회로(102) 등도 포함하는 경우가 있다.

표시 패널(103)에는 고전원 전위 VDD 및 저전원 전위 VSS를 기초로 하는 전원 전압, 공통 전위 Vcom이 공급된다.

표시 제어 신호 생성 회로(101)는 외부로부터 입력되는 동기 신호에 기초하여 게이트 라인 구동 회로(104) 및 소스 라인 구동 회로(105)를 동작시키기 위한 신호를 출력하는 회로이다.

동기 신호의 일례로서는 수평 동기 신호(Hsync.), 수직 동기 신호(Vsync.), 기준 클럭 신호(CLK)가 있다.

게이트 라인 구동 회로(104)를 동작시키기 위한 신호로서는 게이트 라인 측 스타트 펄스 GSP, 게이트 라인 측 클럭 신호 GCLK 등이 있다. 또한, 게이트 라인 측 클럭 신호 GCLK는 위상이 시프트됨으로써 복수의 게이트 라인 측 클럭 신호가 된 것을 포함한다.

소스 라인 구동 회로(105)를 동작시키기 위한 신호로서는 소스 라인 측 스타트 펄스 SSP, 소스 라인 측 클럭 신호 SCLK 등이 있다. 또한, 소스 라인 측 클럭 신호 SCLK는 위상이 시프트됨으로써 복수의 소스 라인 측 클럭 신호가 된 것을 포함한다.

또한, 소스 라인 구동 회로(105)가 갖는 디지털/아날로그 변환 회로(107)는 외부로부터 입력되는 데이터 신호 Data, 및 표시 제어 신호 생성 회로(101)로부터 입력되는 극성 반전 신호 POL이 공급된다. 디지털/아날로그 변환 회로(107)는 데이터 신호 Data를 극성 반전 신호 POL에 기초하여 아날로그 값의 비디오 신호로 변환한다. 이 데이터 신호를 아날로그 값의 비디오 신호로 변환할 때는 래더(ladder) 저항과 스위치를 조합한 회로로 수행하면 좋고, 동시에 감마 보정 등을 수행하는 구성으로 하면 좋다.

또한, 소스 라인 구동 회로(105)가 갖는 디지털/아날로그 변환 회로(107)는 입력되는 극성 반전 신호 POL에 따라, 화소에 출력하는 비디오 신호의 극성을 전환시킬 수 있는 회로이면 좋고, 다른 회로로 할 수도 있다. 예를 들어, 극성 반전 신호 POL에 따라, 화소에 출력하는 비디오 신호의 극성을 전환시키는 반전 증폭기(inverting amplifier)를 사용하여도 좋다.

외부로부터 입력되는 데이터 신호 Data는 디지털 데이터이다. 데이터 신호 Data가 아날로그 데이터인 경우에는 디지털 데이터로 변환한다.

극성 반전 신호 POL은 데이터 신호 Data를 아날로그 신호인 비디오 신호(Vdata라고도 함)로 변환할 때, 상기 비디오 신호를 공통 전위에 대해 높은 전위(양의 극성) 및 낮은 전위(음의 극성) 중 어느 하나로 전환하는 신호이다.

비디오 신호 Vdata는 데이터 신호 Data에 기초한 전압이다. 비디오 신호 Vdata는 소스 라인(110)을 통하여 각 화소(108)의 액정 소자의 전극 중 하나에 인가되는 전압이다. 액정 소자에 대한 비디오 신호의 인가는 화소(108)에 대한 비디오 신호의 기록이라고도 한다. 극성이 상이한 비디오 신호 Vdata이어도 비디오 신호의 전위와 공통 전위의 차이의 절대값이 같으면, 액정 표시 장치에 입력되는 데이터 신호 Data는 같은 값이 된다. 또한, 비디오 신호는 비디오 신호의 전위가 공통 전위보다 높은 경우에는 액정 소자에 양의 극성의 전압이 인가된다. 한편, 비디오 신호의 전위가 공통 전위보다 낮은 경우에는 액정 소자에 음의 극성의 전압이 인가된다.

또한, 화소에 기록되는 비디오 신호는 기록되는 비디오 신호의 전압 레벨로부터, 더 보정된 전압 레벨로 변경함으로써, 액정 소자의 응답을 빠르게 할 수 있다. 예를 들어, 비디오 신호의 전압 레벨을 더 큰 전압 레벨의 비디오 신호로 보정함으로써, 액정 소자의 응답 시간을 짧게 하여, 화상 표시를 신속하게 수행할 수 있다. 이와 같은 보정 신호를 인가하는 구동 방법은 오버드라이브 구동이라고도 불린다.

또한, 표시 제어 신호 생성 회로(101)에 있어서, 출력되는 극성 반전 신호 POL의 신호의 반전을 m프레임 기간마다 수행하기 위해서는, 예를 들어 동기 신호인 수직 동기 신호(Vsync.)의 주기를 m주기 카운트하여 극성 반전 신호 POL의 신호를 반전하는 구성으로 하면 좋다. 구체적으로는 수직 동기 신호의 주기를 카운트하여 얻어지는 카운트 값을 표시 제어 신호 생성 회로(101)에 출력하는 카운터 회로를 제공하면 좋다. 카운터 회로가 수직 동기 신호의 카운트 값을 m주기로 리셋하여, 표시 제어 신호 생성 회로(101)가 상기 리셋에 따라 극성 반전 신호 POL의 전위의 H 레벨과 L 레벨을 전환하는 구성으로 하면 좋다.

또한, 표시 제어 신호 생성 회로(101)는 액정 표시 장치(100)를 비표시 상태로 할 때는 외부로부터 입력되는 정지 신호(STP)에 따라 극성 반전 신호 RPOL을 출력한다. 여기서, 정지 신호 STP가 표시 제어 신호 생성 회로(101)에 입력되면, 극성 반전 신호 POL의 출력이 정지되고, 이 대신에 극성 반전 신호 RPOL이 출력된다.

또한, 선택 회로(102)는 정지 신호 STP에 따라 데이터 신호 Data 또는 리셋 데이터 신호 Rdata를 선택하여 디지털/아날로그 변환 회로(107)에 출력한다. 정지 신호 STP가 입력되지 않을 때는 선택 회로(102)는 데이터 신호 Data를 출력하고, 정지 신호 STP가 입력되면 선택 회로(102)는 리셋 데이터 신호 Rdata를 출력한다. 여기서, 리셋 데이터 신호 Rdata는 데이터 신호 Data와 마찬가지로 디지털 데이터이다.

디지털/아날로그 변환 회로(107)에 출력된 리셋 데이터 신호 Rdata는 극성 반전 신호 RPOL에 따라 아날로그 값의 리셋 신호(Vres라고도 부름)로 변환된다. 즉 극성 반전 신호 RPOL은 리셋 데이터 신호 Rdata를 아날로그 신호인 리셋 신호 Vres로 변환할 때, 상기 리셋 신호를 공통 전위보다 높은 전위(양의 극성) 및 낮은 전위(음의 극성) 중 어느 하나로 전환하는 신호이다.

화상을 표시할 때는 수직 동기 신호(Vsync.)에 따라 표시 제어 신호 생성 회로(101)로부터 극성 반전 신호 POL이 출력되고, 선택 회로(102)로부터 출력된 데이터 신호 Data는 디지털/아날로그 변환 회로(107)에서 극성 반전 신호 POL에 따라 비디오 신호 Vdata로 변화된다. 한편, 화상을 비표시 상태로 할 때는 정지 신호 STP에 따라 표시 제어 신호 생성 회로(101)로부터 극성 반전 신호 RPOL이 출력되고, 선택 회로(102)로부터 출력된 리셋 데이터 신호 Rdata는 디지털/아날로그 변환 회로(107)에서 극성 반전 신호 RPOL에 따라 리셋 신호 Vres로 변화된다.

도 3의 (A)는 액정 표시 장치(100)의 화상을 표시할 때, 표시 제어 신호 생성 회로(101), 선택 회로(102), 및 표시 패널(103)에 입출력되는 신호를 모식적으로 도시한 타이밍 차트이다.

도 3의 (A)의 타이밍 차트는 수직 동기 신호(Vsync.), 데이터 신호(data), 극성 반전 신호 POL의 파형을 모식적으로 도시한 것이다. 또한, 도 3의 (A)에 도시한 타이밍 차트에서는 가로축은 시간을 나타내고, 세로축은 화소의 액정 소자에 인가하는 비디오 신호 Vdata의 전압 레벨을 나타낸다.

도 3의 (A)에 도시한 타이밍 차트에서는 수직 동기 신호의 H 레벨의 주기에 동기하여, 데이터 신호가 첫 번째 프레임 내지 m 번째(m은 2 이상의 자연수) 프레임에서 연속하여 공급된다. 극성 반전 신호 POL은 수직 동기 신호의 H 레벨을 카운트하여 m번마다 신호를 반전한다. 그래서, 극성 반전 신호 POL을 m프레임마다 반전한 신호를 할 수 있다.

극성 반전 신호 POL의 반전에 따라 양의 극성 또는 음의 극성으로 반전되는 비디오 신호는 공통 전위에 대한 전압 레벨로서 각 화소에 기록된다. 도 3의 (A)에 도시한 바와 같이, 본 실시형태의 구성에서는 m프레임 기간 연속적으로 같은 극성의 반전 상태를 유지하여 동작시킬 수 있다.

일반적으로 표시 소자에 액정 소자를 사용하는 표시 장치에서는 게이트 라인 반전 구동, 소스 라인 반전 구동, 프레임 반전 구동, 도트 반전 구동이라는, 1프레임 기간마다 양 또는 음의 극성을 교대로 표시 소자에 공급하는 반전 구동을 수행한다. 그러나, 액정 소자에 인가하는 비디오 신호의 전압 레벨이 큰 경우에 반전 구동을 수행하면, 표시 소자에 인가하는 전압 레벨의 크기가 변하지 않아도 신호의 반전에 의해 비디오 신호의 변화량이 커져, 소비 전력이 커진다. 소비 전력의 증대는 구동 주파수가 큰 구동이 수행되는 경우에 특히 현저하게 된다.

한편, 도 3의 (A)에 도시한 예에서는 같은 극성의 비디오 신호를 m프레임 기간 이상 연속적으로 인가함으로써 기록할 수 있다. 그러므로, 1프레임 기간마다 반전 구동을 수행한 경우에 반전 구동에 따른 비디오 신호의 변화량이 커진다는 문제를 저감할 수 있어, 소비 전력을 절감할 수 있다.

또한, 도 3의 (A)에 도시한 바와 같이, 본 실시형태에서 제시한 구성에서는 m프레임 기간마다 반전 구동한다. 그러므로, m 번째 프레임부터 (m+1) 번째 프레임간, 및 2m 번째 프레임부터 (2m+1) 번째 프레임간에서는 비디오 신호의 변화가 커진다. 한편, m 번째 프레임부터 (m+1) 번째 프레임, 및 2m 번째 프레임부터 (2m+1) 번째 프레임에서는 비디오 신호를 공통 전위 Vcom과 대략 같은 전위로 하는 블랭크 기간을 설정하는 구성으로 함으로써, 비디오 신호의 변화를 작게 할 수 있다. 이로써, 소비 전력을 더 저감할 수 있다.

또한, 도 3의 (B)는 액정 표시 장치(100)의 화상을 비표시 상태로 할 때의 표시 제어 신호 생성 회로(101), 선택 회로(102), 및 표시 패널(103)에 입출력되는 신호를 모식적으로 도시한 타이밍 차트이다.

도 3의 (B)에 도시한 타이밍 차트에 정지 신호(STP), 리셋 데이터 신호(Rdata), 극성 반전 신호 RPOL의 파형을 모식적으로 도시하였다. 또한, 도 3의 (B)에 도시한 타이밍 차트에서는 가로축은 시간을 나타내고, 세로축은 화소의 액정 소자에 인가하는 리셋 신호 Vres의 전압 레벨을 나타낸다.

도 3의 (B)에 도시한 타이밍 차트에서는 정지 신호 STP의 H 레벨이 입력되면, 리셋 데이터 신호가 R1 번째 프레임 및 R2 번째 프레임에 입력된다. 여기서 R1 번째 프레임이란, 정지 신호 STP가 입력되고 나서 첫 번째 프레임을 뜻하고, R2 번째 프레임이란, 정지 신호 STP가 입력되고 나서 2 번째 프레임을 뜻한다. 극성 반전 신호 RPOL은 R1 번째 프레임과 R2 번째 프레임에서 반전되며, 도 3의 (B)에서는 극성 반전 신호 RPOL은 R1 번째 프레임에서 양의 극성이 되고 R2 번째 프레임에서 음의 극성이 된다.

극성 반전 신호 RPOL에 따라 양의 극성 또는 음의 극성으로 반전되는 리셋 신호 Vres는 공통 전위 Vcom에 대한 전압 레벨로서 각 화소에 기록된다. 도 3의 (B)에서는 리셋 신호 Vres는 R1 번째 프레임에서 양의 극성이 되고 R2 번째 프레임에서 음의 극성이 된다. 이 때, 전압 레벨의 절대값은 최대한 크게, 예를 들어 비디오 신호의 전압 레벨의 절대값의 최대값과 같은 정도로 하는 것이 바람직하다. 또한, R1 번째 프레임의 리셋 신호 Vres의 극성은 정지 신호 STP가 입력되었을 때의 비디오 신호 Vdata의 극성을 반전시킨 극성으로 하는 것이 바람직하다. 이와 같이 리셋 신호 Vres를 모든 화소에 입력한 후, 고전원 전위 VDD의 공급을 차단하면 좋다.

이와 같이 리셋 신호 Vres를 입력함으로써, 상술한 바와 같이 m프레임 기간 이상 연속적으로 같은 극성의 비디오 신호를 기록하여도 액정의 열화를 억제할 수 있다. 따라서, 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 데다가 액정의 열화를 억제할 수 있는 액정 표시 장치를 제공할 수 있다.

또한, 도 3의 (B)에서는 리셋 신호로서 R1 번째 프레임과 R2 번째 프레임의 2프레임에 양의 극성과 음의 극성의 전위를 각각 인가하지만, 이것에 한정되지 않으며, 3프레임 이상 전위의 극성을 반전시키면서 리셋 신호를 입력시키는 구성으로 하여도 좋다. 또한, 정지 신호 STP가 입력되었을 때의 비디오 신호 Vdata의 전위의 극성을 반전시킨 극성을 갖는 전위의 리셋 신호를 1프레임만 입력시키는 구성으로 할 수도 있다.

또한, 도 3의 (B)에서는 R1 번째 프레임의 길이, R2 번째 프레임의 길이는 도 3의 (A)에 도시한 1프레임 기간과 같은 정도이지만, 본 실시형태에 제시되는 액정 표시 장치는 이것에 한정되지 않으며, R1 번째 프레임, R2 번째 프레임, 또는 R3 번째 프레임 이후의 프레임의 길이를 1프레임 기간 이상의 길이로 하여도 좋다.

또한, 이와 같이 리셋 신호 Vres로서 적어도 한 번 이상 극성을 반전시키면서 전위를 입력한 후, 리셋 신호 Vres의 전위를 공통 전위 Vcom과 대략 같은 전위로 하는 것이 바람직하다. 예를 들어, 도 3의 (B)에 있어서, R2 번째 프레임 다음에 리셋 신호의 전압 레벨이 공통 전위 Vcom이 되는 R3 번째 프레임을 제공하는 구성으로 하면 좋다. 또한, 이와 같이 하여 액정 소자의 전극 간의 전위차를 대략 0V로 한 후, 화소에 제공된 액정 소자와 전기적으로 접속된 트랜지스터를 오프 상태로 하는 것이 바람직하다.

다음에, 도 2에 도시한 표시 패널(103)의 구성에 대해서, 구체적인 구성예를 제시하며, 본 실시형태의 효과에 대해서 자세히 설명한다.

도 4는 도 2에 도시한 표시 패널(103)이 갖는 게이트 라인 구동 회로(104), 소스 라인 구동 회로(105), 및 화소부(106)의 구성을 구체적으로 도시한 것이다.

게이트 라인 구동 회로(104)는 시프트 레지스터 회로(201)를 갖는다. 소스 라인 구동 회로(105)는 시프트 레지스터 회로(202), 디지털/아날로그 변환 회로(107), 및 아날로그 스위치(203)를 갖는다.

도 4에서는 일례로서 화소부(106)가 3행 3열의 화소(108)를 갖는 구성을 도시하였다. 화소(108)는 각각 트랜지스터(204), 용량 소자(205), 및 액정 소자(206)를 갖는다. 트랜지스터(204)는 게이트가 게이트 라인(109)에 접속되고, 소스 및 드레인 중 하나가 소스 라인(110)에 접속된다.

트랜지스터(204)로서는 오프 상태에서의 전류(오프 전류)가 낮은 트랜지스터를 사용하는 것이 바람직하며, 예를 들어 산화물 반도체를 사용한 트랜지스터를 사용하는 것이 바람직하다. 이와 같은 트랜지스터를 트랜지스터(204)로서 사용함으로써, 용량 소자(205) 및 액정 소자(206)로부터 트랜지스터(204)를 통하여 전하가 누설되기 어려워지기 때문에, 액정 소자(206)에 인가하는 전압을 장시간 유지할 수 있다. 이로써, 액정 표시 장치(100)의 표시 화상의 유지 특성을 높일 수 있다.

한편, 이와 같이 트랜지스터(204)로서 오프 전류가 낮은 트랜지스터를 사용하면, 액정 표시 장치(100)의 전원을 오프 상태로 한 후에도, 트랜지스터(204)와 접속되는 액정 소자(206)의 전압이 유지되고, 극성이 유지된 전계가 액정에 장시간 인가되어 액정이 열화될 우려가 있다. 한편, 상술한 바와 같이 리셋 신호를 입력할 때, 적어도 한 번 이상 극성을 반전시키면서 전위를 입력한 후, 리셋 신호 Vres의 전위를 공통 전위 Vcom과 대략 같은 전위로 하여 트랜지스터(204)를 오프 상태로 함으로써, 극성이 유지된 전계가 액정에 장시간 인가되는 것을 억제할 수 있다.

또한, 상술한 바와 같이 액정 표시 장치(100)의 전원이 오프 상태일 때, 타이머로 설정한 시간에 액정 표시 장치(100)를 기동시켜 상기 리셋 신호를 입력하는 구성으로 하는 것이 바람직하다. 이로써, 액정 표시 장치(100)의 전원을 오프 상태로 하였을 때, 액정 소자(206)의 전압이 유지되어 있어도, 타이머로 설정한 시각에 액정의 상태를 전계가 인가되지 않는 상태로 할 수 있다.

도 4에 있어서, 게이트 라인 구동 회로(104)가 갖는 시프트 레지스터 회로(201)는 게이트 라인 측 스타트 펄스 GSP, 게이트 라인 측 클럭 신호 GCLK가 입력된다. 시프트 레지스터 회로(201)는 첫 번째 행 내지 3 번째 행에 있는 게이트 라인(109)에 대해 선택 신호 Gout1 내지 선택 신호 Gout3을 사용하여 순차적으로 H 레벨의 신호를 출력하여, 트랜지스터(204)의 도통 상태를 제어할 수 있다.

도 4에 있어서, 소스 라인 구동 회로(105)가 갖는 디지털/아날로그 변환 회로(107)는 화상을 표시할 때는 데이터 신호 Data, 및 극성 반전 신호 POL에 따라 생성되는 비디오 신호 Vdata를 출력한다. 또한, 화상을 비표시 상태로 할 때는 리셋 데이터 신호 Rdata, 및 극성 반전 신호 RPOL에 따라 생성되는 리셋 신호 Vres를 출력한다. 비디오 신호 Vdata 및 리셋 신호 Vres는 아날로그 스위치(203)가 도통 상태가 됨으로써, 소스 라인(110)을 통하여 화소(108)의 용량 소자(205) 및 액정 소자(206)에 기록된다.

도 4에 있어서, 소스 라인 구동 회로(105)가 갖는 시프트 레지스터 회로(202)는 소스 라인 측 스타트 펄스 SSP, 소스 라인 측 클럭 신호 SCLK가 입력된다. 시프트 레지스터 회로(202)는 첫 번째 열 내지 3 번째 열에 있는 아날로그 스위치(203)에 대해 선택 신호 Sout1 내지 선택 신호 Sout3을 사용하여 순차적으로 H 레벨의 신호를 출력하여, 아날로그 스위치(203)의 도통 상태를 제어할 수 있다.

다음에, 도 5의 (A)에 도시한 화소부의 모식도, 및 도 5의 (B)에 도시한, 데이터 신호에 기초하는 양 또는 음의 극성을 갖는 비디오 신호의 도면을 사용하여, 복수의 프레임 기간에 걸친 본 발명의 구동 방법의 구체적인 동작의 일례에 대해서 설명한다.

도 5의 (A)에 도시한 도면은 화상을 표시할 때의 첫 번째 프레임, 2 번째 프레임, m 번째 프레임, 및 (m+1) 번째 프레임, 화상을 비표시로 할 때의 R1 번째 프레임, R2 번째 프레임, 및 R3 번째 프레임에, 3행 3열의 화소부에 입력되는 데이터 신호의 모식도이다. 여기서, R1 번째 프레임이란, 정지 신호 STP가 입력되고 나서 첫 번째 프레임을 뜻하고, R2 번째 프레임이란, 2 번째 프레임을 뜻하고, R3 번째 프레임이란, 3 번째 프레임을 뜻한다.

도 5의 (A)에 도시한 첫 번째 프레임은 1행 1열째의 화소(211), 2행 1열째의 화소(221), 및 3행 1열째의 화소(231)에는 데이터 신호로서 'VA'를 입력하고, 1행 2열째의 화소(212), 2행 2열째의 화소(222), 및 3행 2열째의 화소(232)에는 데이터 신호로서 'VB'를 입력하고, 1행 3열째의 화소(213), 2행 3열째의 화소(223), 및 3행 3열째의 화소(233)에는 데이터 신호로서 'VC'를 입력하는 예이다.

또한, 도 5의 (A)에 도시한 데이터 신호 'VA', 'VB', 및 'VC'를 비디오 신호의 전압 레벨의 크기로 표현하려면, |VA|, |VB|, |VC|로 표현할 수 있다. 또한, 설명을 위해 |VA|, |VB|, |VC|의 대소 관계를 일례로서 나타내면, |VC|<|VB|<|VA|가 된다. 극성 반전 신호 POL이 H 레벨(POL_H)인 경우에는, 도 5의 (B)에 도시한 바와 같이 비디오 신호는 'VA', 'VB', 및 'VC'로 표기할 수 있고, '양의 극성의 비디오 신호를 기록한다'라고 설명할 수 있다. 또한, 극성 반전 신호 POL이 L 레벨(POL_L)인 경우에, 도 5의 (B)에 도시한 바와 같이 비디오 신호는 '-VA', '-VB', 및 '-VC'로 표기할 수 있고, '음의 극성의 비디오 신호를 기록한다'라고 설명할 수 있다. 또한, 도 5의 (B)에 도시한 바와 같이, 'VA', 'VB', 및 'VC'와, '-VA', '-VB', 및 '-VC'의 비디오 신호는 공통 전위 Vcom을 사이에 두고 대칭이 되고, 크기가 같은 신호이다.

또한, 도 5의 (A)에 있어서, 2 번째 프레임에서는 화소(211), 화소(221), 및 화소(231)에 'VB'를 입력하고, 화소(212), 화소(222), 및 화소(232)에 'VC'를 입력하고, 화소(213), 화소(223), 및 화소(233)에 'VA'를 데이터 신호로서 입력한다.

또한, 도 5의 (A)에 있어서, m 번째 프레임에서는 화소(211), 화소(221), 및 화소(231)에 'VC'를 입력하고, 화소(212), 화소(222), 및 화소(232)에 'VA'를 입력하고, 화소(213), 화소(223), 및 화소(233)에 'VB'를 데이터 신호로서 입력한다.

또한, 도 5의 (A)에 있어서, (m+1) 번째 프레임에서는 화소(211), 화소(221), 및 화소(231)에 'VB'를 입력하고, 화소(212), 화소(222), 및 화소(232)에 'VC'를 입력하고, 화소(213), 화소(223), 및 화소(233)에 'VA'를 데이터 신호로서 입력한다.

또한, 도 5의 (A)에 있어서, R1 번째 프레임에서는 모든 화소에 'VA'를 데이터 신호로서 입력하고, R2 번째 프레임에서도 마찬가지로 모든 화소에 'VA'를 데이터 신호로서 입력한다. 또한, 도 5의 (A)에 있어서, R3 번째 프레임에서는 모든 화소에 공통 전위 Vcom에 대응하는 'Vcom'를 데이터 신호로서 입력한다.

도 6은 도 5의 (A)에 도시한, 화상을 표시할 때의 화소부로의 데이터 신호의 입력에 기초하여 도시한 타이밍 차트이다. 도 6에 도시한 타이밍 차트에서는 첫 번째 프레임, 2 번째 프레임, m 번째 프레임, 및 (m+1) 번째 프레임에서의 선택 신호 Gout1 내지 선택 신호 Gout3, 선택 신호 Sout1 내지 선택 신호 Sout3, 데이터 신호 Data, 극성 반전 신호 POL, 및 비디오 신호 Vdata를 도시하였다. 또한, 도 6에 도시한 타이밍 차트에서는 점순차 구동으로 한 경우에 대해서 설명하지만, 선순차 구동으로 하는 구성이어도 좋다.

도 6에 도시한 타이밍 차트에서는 도 3의 (A)에서 설명한 바와 같이, 극성 반전 신호 POL의 신호를 m프레임 기간마다 반전시키는 구성으로 할 수 있다. 따라서, 본 실시형태에서의 비디오 신호 Vdata를 m프레임 기간 연속적으로, 같은 극성의 비디오 신호로 하여 동작시킬 수 있다. 그러므로, 1프레임 기간마다 반전 구동을 수행한 경우에, 반전 구동에 따른 비디오 신호의 변화량이 커진다는 문제를 저감할 수 있어, 소비 전력을 절감할 수 있다.

다음에 도 7에서는 도 6에 도시한 타이밍 차트에서 화소부에서의 첫 번째 열의 비디오 신호의 변화를 발췌해서 설명한다.

도 7의 (A)에 도시한 도면은 도 6에 도시한 기간 T1 및 기간 T2에서의 비디오 신호의 변화를 발췌해서 도시한 모식도이다. 또한, 도 7의 (B)에 도시한 도면은 도 6에 도시한 타이밍 차트에 대해 1프레임마다 극성 반전 신호 POL을 반전시키는 구성으로 한 경우의, 도 6의 기간 T1 및 기간 T2에 대응하는 기간 T1R 및 기간 T2R에서의 비디오 신호의 변화를 발췌해서 도시한 모식도이다. 즉, 도 7의 (B)에서는 기간 T1R 및 기간 T2R에서 비디오 신호의 극성이 반전되어 있다.

도 7의 (A)에 도시한 기간 T1은 첫 번째 프레임의 첫 번째 행의 각 열에서의 비디오 신호를 나타낸다. 도 7의 (A)에 도시한 기간 T2는 2 번째 프레임의 첫 번째 행의 각 열에서의 비디오 신호를 나타낸다. 도 7의 (B)에 도시한 기간 T1R는 첫 번째 프레임의 첫 번째 행의 각 열에서의 비디오 신호를 나타낸다. 도 7의 (B)에 도시한 기간 T2R는 2 번째 프레임의 첫 번째 행의 각 열에서의 비디오 신호를 나타낸다. 또한, 도 7의 (A) 및 (B)에서는 기간 T1과 기간 T2와, 기간 T1R과 기간 T2R에 있어서, 같은 열에서의 비디오 신호에 착안하여, 이들의 변화에 대해서 화살표로 가리켰다.

도 7의 (A)에 있어서, 1행의 각 열의 첫 번째 프레임과 2번째 프레임 사이의 비디오 신호의 차이를 열거하면, 첫 번째 열에서는 |VA-VB|이고, 2 번째 열에서는 |VB-VC|이고, 3 번째 열에서는 |VC-VA|이다. 또한, 도 7의 (B)에 있어서, 1행의 각 열의 첫 번째 프레임과 2번째 프레임 사이의 비디오 신호의 차이를 열거하면, 첫 번째 열에서는 |VA+VB|이고, 2 번째 열에서는 |VB+VC|이고, 3 번째 열에서는 |VC+VA|이다.

도 7의 (A)와 (B)에 있어서, 같은 열에서의 비디오 신호에 착안하면, 전압의 변화가 큰 것은 도 7의 (B)에 도시한 1프레임마다 극성 반전 신호 POL을 반전시키는 프레임 반전 구동으로 한 경우이다. 한편, 도 7의 (A)에 도시한 극성 반전 신호 POL의 신호의 반전을 m프레임 기간마다 수행하는 구성으로 한 경우에는 같은 열에서의 비디오 신호의 변화가 작다. 따라서, 도 7의 (A)의 경우에는, 화소에 기록하는 비디오 신호의 충방전에 필요한 소비 전력을 작게 할 수 있다.

따라서, 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 액정 표시 장치를 제공할 수 있다.

도 8은 도 5의 (A)에 도시한 화상을 비표시 상태로 할 때의 화소부에 대한 데이터 신호의 입력에 기초하여 도시한 타이밍 차트이다. 도 8에 도시한 타이밍 차트에서는 R1 번째 프레임, R2 번째 프레임, 및 R3 번째 프레임에서의 선택 신호 Gout1 내지 선택 신호 Gout3, 선택 신호 Sout1 내지 선택 신호 Sout3, 리셋 데이터 신호 Rdata, 극성 반전 신호 RPOL, 및 리셋 신호 Vres를 도시하였다. 또한, 도 8에 도시한 타이밍 차트에서는 점순차 구동으로 한 경우에 대해서 설명하지만, 선순차 구동으로 하는 구성이어도 좋다.

도 8에 도시한 타이밍 차트에서는 도 3의 (B)에서 설명한 바와 같이, 극성 반전 신호 RPOL의 전위를 R1 번째 프레임과 R2 번째 프레임 간에서 반전시킨다. 이로써, R1 번째 프레임에서는 리셋 신호 Vres로서 전위 VA가 입력되고, R2 번째 프레임에서는 리셋 신호 Vres로서 전위 -VA가 입력된다. 이와 같이 리셋 신호 Vres를 입력함으로써, 도 6에 도시한 바와 같이 같은 극성의 비디오 신호를 m프레임 기간 이상 연속적으로 기록하여도, 액정의 열화를 억제할 수 있다. 또한, 리셋 신호 Vres의 전위를, 이와 같이 비디오 신호 Vdata의 전압 레벨의 절대값의 최대값과 같은 정도로 함으로써, 강한 전계를 반전하여 액정 소자에 인가할 수 있기 때문에 액정 소자의 열화를 더 억제할 수 있다.

또한, R3 번째 프레임에서, 리셋 신호 Vres로서, 'Vcom'의 데이터 신호에 대응하는 공통 전위 Vcom을 입력한다. 이와 같이 하여 액정 소자의 전극 사이의 전위차를 대략 0V로 한 후, 화소에 제공된 액정 소자(206)와 전기적으로 접속된 트랜지스터(204)를 오프 상태로 함으로써, 극성이 유지된 전계가 액정에 장시간 인가되는 것을 억제할 수 있다.

상술한 바와 같이 하여, 동영상을 표시하는 경우에도 소비 전력의 저감이 도모된 데다가 액정의 열화를 억제할 수 있는 액정 표시 장치를 제공할 수 있다.

또한, 본 실시형태에서는 프레임 반전 구동을 수행하는 액정 표시 장치를 예로 들어 설명하였지만, 다른 구성으로 하여도 좋다. 예를 들어, 게이트 라인 반전 구동, 소스 라인 반전 구동, 또는 도트 반전 구동 등을 수행하는 액정 표시 장치로 하여도 좋다.

본 실시형태에 기재된 구성이나 방법 등은 다른 실시형태에 기재되는 구성이나 방법 등과 적절히 조합하여 사용할 수 있다.

(실시형태 2)

본 실시형태에서는, 액정 표시 장치의 외관 및 단면 등을 제시하며, 그 구성에 대해 설명한다. 본 실시형태에서는 표시 소자로서 액정 소자를 사용한 예를 들어 설명한다.

또한, 액정 표시 장치란, 커넥터, 예를 들어 FPC(Flexible printed circuit) 또는 TCP(Tape Carrier Package)가 장착된 모듈, TCP의 끝에 프린트 배선판이 제공된 모듈, 또는 표시 소자에 COG(Chip On Glass) 방식에 의해 IC(집적 회로)가 직접 실장된 모듈도 모두 그 범주에 포함하는 것으로 한다.

액정 표시 장치의 외관 및 단면에 대해, 도 9의 (A1), (A2), (B)를 사용하여 설명한다. 도 9의 (A1), (A2)는 제 1 기판(4001)과 제 2 기판(4006) 사이에 트랜지스터(4010, 4011), 및 액정 소자(4013)를 실재(4005)에 의해 밀봉한 패널의 평면도이며, 도 9의 (B)는 도 9의 (A1), (A2)의 M-N 부분의 단면도에 상당한다.

제 1 기판(4001) 위에 제공된 화소부(4002)와, 게이트 라인 구동 회로(4004)를 둘러싸도록 실재(4005)가 제공되어 있다. 또한 화소부(4002)와 게이트 라인 구동 회로(4004) 위에 제 2 기판(4006)이 제공되어 있다. 따라서, 화소부(4002)와 게이트 라인 구동 회로(4004)는 제 1 기판(4001)과 실재(4005)와 제 2 기판(4006)에 의해, 액정층(4008)과 함께 밀봉되어 있다. 또한 제 1 기판(4001) 위의 실재(4005)로 둘러싸여 있는 영역과는 다른 영역에, 별도 준비된 기판 위에 단결정 반도체막 또는 다결정 반도체막으로 형성된 소스 라인 구동 회로(4003)가 실장되어 있다.

또한, 도 9에서는 도시하지 않았지만, 광원으로서 화소에 광을 조사하는 백 라이트를 적절히 제공할 수 있다. 여기서, 백 라이트는 상기 리셋 신호를 입력할 때, 비점등 상태인 것이 바람직하다. 이로써, 리셋 신호 입력에 따른 화상 왜곡의 표시를 방지할 수 있다. 또한, 도 9에서는 도시하지 않았지만, 설정한 시간에 상기 액정 표시 장치를 기동시키는 타이머를 적절히 제공할 수 있다. 여기서, 이 타이머는 액정 표시 장치가 사용되지 않는 특정한 시간(예를 들어, 심야 등 일반적으로 사용자가 액정 표시 장치를 사용하지 않는 시간 등)으로 설정하여 타이머로 액정 표시 장치를 기동시켜, 상기 리셋 신호를 입력시키면 좋다. 또한, 위상차판, 반사 방지막 등 광학 필름 등은 적절히 제공할 수 있다. 또한, 컬러 필터층으로서 기능하는 착색층을 제공할 수 있다.

또한, 별도로 형성한 구동 회로의 접속 방식에 대해서는 특별한 한정은 없으며, COG 방식, 와이어 본딩 방식, 또는 TAB 방식 등을 이용할 수 있다. 도 9의 (A1)는 COG 방식에 의해 소스 라인 구동 회로(4003)를 실장하는 예이며, 도 9의 (A2)는 TAB 방식에 의해 소스 라인 구동 회로(4003)를 실장하는 예이다.

또한, 제 1 기판(4001) 위에 제공된 화소부(4002)와, 게이트 라인 구동 회로(4004)는 복수의 트랜지스터를 가지며, 도 9의 (B)에서는 화소부(4002)에 포함되는 트랜지스터(4010)와 게이트 라인 구동 회로(4004)에 포함되는 트랜지스터(4011)를 예시하였다. 트랜지스터(4010, 4011) 위에는 절연층(4020, 4021)이 제공되어 있다.

트랜지스터(4010, 4011)는 비정질, 미결정, 다결정, 또는 단결정인, 실리콘 또는 게르마늄 등 박막 반도체를 반도체층에 적용할 수 있다. 또는, 트랜지스터(4010, 4011)는 산화물 반도체를 반도체층에 적용할 수 있다. 본 실시형태에서, 트랜지스터(4010, 4011)는 n채널형 트랜지스터이다. 산화물 반도체를 반도체층에 적용함으로써, 오프 전류가 매우 낮은 트랜지스터를 화소의 스위칭 소자에 사용할 수 있다. 이 경우에는, 한 번 화소에 기록한 비디오 전압의 변동이 작기 때문에, 표시 품위의 향상을 도모할 수 있다.

여기서, 전자 공여체(도너)가 되는 수분 또는 수소 등 불순물이 저감되고, 또 산소 결손이 저감됨으로써 고순도화된 산화물 반도체(purified OS)는 i형(진성 반도체)이거나, 또는 i형에 매우 가깝다. 그러므로, 고순도화된 산화물 반도체를 반도체층에 갖는 트랜지스터는 오프 전류가 매우 작고, 신뢰성이 높다.

구체적으로는, 고순도화된 산화물 반도체막에 채널 형성 영역을 갖는 트랜지스터의 오프 전류가 작다는 것은 여러 가지 실험에 의하여 증명할 수 있다. 예를 들어, 채널 폭이 1×106μm이고 채널 길이가 10μm인 소자의 경우에도, 소스 전극과 드레인 전극간의 전압(드레인 전압)이 1V 내지 10V인 범위에서 오프 전류가 반도체 파라미터 애널라이저의 측정 한계 이하, 즉 1×10-13A 이하라는 특성을 얻을 수 있다. 이 경우에, 오프 전류를 트랜지스터의 채널 폭으로 규격화한 오프 전류는 100zA/μm 이하인 것을 알 수 있다. 또한, 용량 소자와 트랜지스터를 접속시켜, 용량 소자에 유입 또는 용량 소자로부터 유출하는 전하를 상기 트랜지스터로 제어하는 회로를 사용하여, 오프 전류를 측정하였다. 상기 측정에서는 상기 트랜지스터에 고순도화된 산화물 반도체막을 채널 형성 영역에 사용하여, 용량 소자의 단위 시간당 전하량의 추이로부터 상기 트랜지스터의 오프 전류를 측정하였다. 이 결과로, 트랜지스터의 소스 전극과 드레인 전극간의 전압이 3V인 경우에, 수십 yA/μm라는, 더 작은 오프 전류가 얻어지는 것을 알았다. 따라서, 고순도화된 산화물 반도체막을 채널 형성 영역에 사용한 트랜지스터는 결정성을 갖는 실리콘을 사용한 트랜지스터에 비하여 오프 전류가 현저히 작다.

또한, 트랜지스터(4010, 4011)의 반도체층으로서 산화물 반도체막을 사용하는 경우, 산화물 반도체로서는 적어도 인듐(In) 또는 아연(Zn)을 포함하는 것이 바람직하다. 또한, 상기 산화물 반도체를 사용한 트랜지스터의 전기적 특성의 편차를 감소시키기 위한 스테빌라이저로서, 상술한 것에 추가하여 갈륨(Ga)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 주석(Sn)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 하프늄(Hf)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 알루미늄(Al)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 지르코늄(Zr)을 갖는 것이 바람직하다.

산화물 반도체 중에서도 In-Ga-Zn계 산화물, In-Sn-Zn계 산화물 등은 탄화 실리콘, 질화 갈륨, 또는 산화 갈륨과 달리, 스퍼터링법이나 습식법에 의해 전기적 특성이 우수한 트랜지스터를 제작할 수 있으며, 양산성이 우수하다는 이점이 있다. 또한, 탄화 실리콘, 질화 갈륨, 또는 산화 갈륨과 달리, 상기 In-Ga-Zn계 산화물은 유리 기판 위에 전기적 특성이 우수한 트랜지스터를 제작할 수 있다. 또한, 기판의 대형화에도 대응할 수 있다.

또한, 다른 스테빌라이저로서 란타노이드인, 란탄(La), 세륨(Ce), 프라세오디뮴(Pr), 네오디뮴(Nd), 사마륨(Sm), 유로퓸(Eu), 가돌리늄(Gd), 테르븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 에르븀(Er), 툴륨(Tm), 이테르븀(Yb), 루테튬(Lu) 중 어느 한 종류 또는 복수 종류를 포함하여도 좋다.

예를 들어, 산화물 반도체로서, 산화 인듐, 산화 갈륨, 산화 주석, 산화 아연, 2원계 금속의 산화물인 In-Zn계 산화물, Sn-Zn계 산화물, Al-Zn계 산화물, Zn-Mg계 산화물, Sn-Mg계 산화물, In-Mg계 산화물, In-Ga계 산화물, 3원계 금속의 산화물인 In-Ga-Zn계 산화물(IGZO라고도 표기함), In-Al-Zn계 산화물, In-Sn-Zn계 산화물, Sn-Ga-Zn계 산화물, Al-Ga-Zn계 산화물, Sn-Al-Zn계 산화물, In-Hf-Zn계 산화물, In-La-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물, In-Lu-Zn계 산화물, 4원계 금속의 산화물인 In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Sn-Hf-Zn계 산화물, In-Hf-Al-Zn계 산화물을 사용할 수 있다.

또한, 예를 들어, In-Ga-Zn계 산화물이란, In과 Ga와 Zn을 함유한 산화물을 뜻하며, In과 Ga와 Zn의 비율은 특별히 제한되지 않는다. 또한, In와 Ga와 Zn 이외의 금속 원소를 포함하여도 좋다. In-Ga-Zn계 산화물은 무(無)전계시의 저항이 충분히 높아 오프 전류를 충분히 작게 할 수 있으며, 또한 이동도도 높다.

예를 들어, 원자수비가 In:Ga:Zn=1:1:1(=1/3:1/3:1/3) 또는 In:Ga:Zn=2:2:1(=2/5:2/5:1/5)인 In-Ga-Zn계 산화물이나 이것과 근방의 조성을 갖는 산화물을 사용할 수 있다. 또는, 원자수비가 In:Sn:Zn=1:1:1(=1/3:1/3:1/3), In:Sn:Zn=2:1:3(=1/3:1/6:1/2) 또는 In:Sn:Zn=2:1:5(=1/4:1/8:5/8)인 In-Sn-Zn계 산화물이나 이것과 근방의 조성을 갖는 산화물을 사용하면 좋다.

예를 들어, In-Sn-Zn계 산화물은 비교적 용이하게 높은 이동도를 얻을 수 있다. 그러나, In-Ga-Zn계 산화물의 경우에도 벌크 내의 결함 밀도를 저감함으로써 이동도를 향상할 수 있다.

또한, 단결정, 다결정(폴리크리스탈이라고도 함), 또는 비정질 등의 상태를 갖는 산화물 반도체막을 트랜지스터에 사용할 수 있다. 바람직하게는, 산화물 반도체막은 CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)막으로 한다.

아래에서, 산화물 반도체막의 구조에 대해서 설명한다.

산화물 반도체막은 단결정 산화물 반도체막과, 비단결정 산화물 반도체막으로 대별된다. 비단결정 산화물 반도체막이란, 비정질 산화물 반도체막, 미결정 산화물 반도체막, 다결정 산화물 반도체막, CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)막 등을 말한다.

비정질 산화물 반도체막은 막 내의 원자 배열이 불규칙하며, 결정 성분을 갖지 않는 산화물 반도체막이다. 미소 영역에도 결정부를 갖지 않고, 막 전체가 완전한 비정질 구조인 산화물 반도체막이 그 전형이다.

미결정 산화물 반도체막은 예를 들어, 크기가 1nm 이상 10nm 미만인 미결정(나노 결정이라고도 함)을 포함한다. 따라서, 미결정 산화물 반도체막은 비정질 산화물 반도체막보다 원자 배열의 규칙성이 높다. 그러므로, 미결정 산화물 반도체막은 비정질 산화물 반도체막보다 결함 준위 밀도가 낮다는 특징을 갖는다.

CAAC-OS막은 복수의 결정부를 갖는 산화물 반도체막의 하나이며, 결정부의 대부분은 하나의 변이 100nm 미만인 입방체 내에 들어가는 크기이다. 따라서, CAAC-OS막에 포함되는 결정부는 하나의 변이 10nm 미만, 5nm 미만, 또는 3nm 미만인 입방체 내에 들어가는 크기인 경우도 포함된다. CAAC-OS막은 미결정 산화물 반도체막보다 결함 준위 밀도가 낮다는 특징을 갖는다. 아래에서 CAAC-OS막에 대하여 자세히 설명한다.

CAAC-OS막을 투과형 전자 현미경(TEM: Transmission Electron Microscope)에 의하여 관찰하면, 결정부와 결정부 간의 명확한 경계, 즉 결정 입계(그레인 바운더리라고도 함)는 확인되지 않는다. 따라서, CAAC-OS막은 결정 입계에 기인하는 전자 이동도의 저하가 일어나기 어렵다고 할 수 있다.

CAAC-OS막을 시료면에 대략 평행한 방향으로부터 TEM에 의해 관찰(단면 TEM 관찰)하면, 결정부에서 금속 원자가 층상으로 배열되어 있는 것을 확인할 수 있다. 금속 원자의 각 층은 CAAC-OS막이 형성되는 면(피형성면이라고도 함) 또는 CAAC-OS막의 상면의 요철을 반영한 형상이며, CAAC-OS막의 피형성면 또는 상면에 평행하게 배열된다.

한편, CAAC-OS막을 시료면에 대략 수직인 방향으로부터 TEM에 의해 관찰(평면 TEM 관찰)하면, 결정부에서 금속 원자가 삼각형 또는 육각형으로 배열되어 있는 것을 확인할 수 있다. 그러나, 상이한 결정부 간에서 금속 원자의 배열에는 규칙성이 보이지 않는다.

본 명세서에 있어서, '평행'이란, 2개의 직선이 -10° 이상 10° 이하의 각도로 배치된 상태를 말한다. 따라서, -5° 이상 5° 이하의 경우도 그 범주에 포함된다. 또한 '수직'이란, 2개의 직선이 80° 이상 100° 이하의 각도로 배치된 상태를 말한다. 따라서, 85° 이상 95° 이하의 경우도 그 범주에 포함된다.

단면 TEM 관찰 및 평면 TEM 관찰에 의거하여, CAAC-OS막의 결정부는 배향성을 갖는 것을 알 수 있다.

X선 회절(XRD: X-Ray Diffraction) 장치를 사용하여 CAAC-OS막의 구조 해석을 수행하면, 예를 들어 InGaZnO4의 결정을 갖는 CAAC-OS막의 out-of-plane법에 의한 해석에서는, 회절각(2θ)의 피크가 31° 근방에 나타나는 경우가 있다. 이 피크는 InGaZnO4의 결정의 (009)면에 귀속되기 때문에, CAAC-OS막의 결정이 c축 배향성을 갖고, c축이 피형성면 또는 상면에 대략 수직인 방향으로 배향하는 것을 확인할 수 있다.

한편, c축에 대략 수직인 방향으로부터 X선을 입사시키는 in-plane법에 의하여 CAAC-OS막을 해석하면, 2θ가 56° 근방일 때 피크가 나타나는 경우가 있다. 이 피크는 InGaZnO4의 결정의 (110)면에 귀속된다. InGaZnO4의 단결정 산화물 반도체막의 경우에는, 2θ를 56° 근방에 고정하여, 시료면의 법선 벡터를 축(φ축)으로 하여 시료를 회전시키면서 분석(φ 스캔)을 수행하면, (110)면과 등가인 결정면에 귀속되는 6개의 피크가 관찰된다. 한편, CAAC-OS막의 경우에는, 2θ를 56° 근방에 고정하여 φ 스캔을 수행하여도 명료한 피크가 나타나지 않는다.

따라서, CAAC-OS막에서는, 상이한 결정부 간에서 a축 및 b축의 배향이 불규칙하지만, c축 배향성을 갖고, 또 c축이 피형성면 또는 상면의 법선 벡터에 평행한 방향으로 배향하는 것을 알 수 있다. 따라서, 상술한 단면 TEM 관찰로 확인된 층상으로 배열된 금속 원자의 각층은 결정의 ab면에 평행한 면이다.

또한, 결정부는 CAAC-OS막을 형성하였을 때 또는 열처리 등의 결정화 처리를 수행하였을 때에 형성된다. 상술한 바와 같이, 결정의 c축은 CAAC-OS막의 피형성면 또는 상면의 법선 벡터에 평행한 방향으로 배향한다. 따라서, 예를 들어 CAAC-OS막의 형상을 에칭 등에 의해 변화시킨 경우에는 결정의 c축이 CAAC-OS막의 피형성면 또는 상면의 법선 벡터에 평행하게 배향하지 않을 수도 있다.

또한, CAAC-OS막 내의 결정화도가 균일하지 않아도 좋다. 예를 들어, CAAC-OS막의 결정부가 CAAC-OS막의 상면 근방으로부터의 결정 성장에 의하여 형성되는 경우에는, 상면 근방의 영역은 피형성면 근방의 영역보다 결정화도가 높게 되는 경우가 있다. 또한, CAAC-OS막에 불순물을 첨가하는 경우에는, 불순물이 첨가된 영역의 결정화도가 변화되어, 부분적으로 결정화도가 다른 영역이 형성될 수도 있다.

또한, out-of-plane법에 의하여 InGaZnO4의 결정을 갖는 CAAC-OS막을 해석하면, 2θ의 피크가 31° 근방 외에 36° 근방에도 나타나는 경우가 있다. 2θ의 피크가 36° 근방에 나타나는 것은 CAAC-OS막 내의 일부에 c축 배향성을 갖지 않는 결정이 포함되는 것을 시사한다. CAAC-OS막은 2θ의 피크가 31° 근방에 나타나고, 36° 근방에 나타나지 않는 것이 바람직하다.

CAAC-OS막을 사용한 트랜지스터는 가시광이나 자외광의 조사에 기인한 전기 특성의 변동이 작다. 따라서, 상기 트랜지스터는 신뢰성이 높다.

또한, 산화물 반도체막은 예를 들어, 비정질 산화물 반도체막, 미결정 산화물 반도체막, CAAC-OS막 중 2종류 이상을 갖는 적층막이라도 좋다.

또한, 액정 소자(4013)가 갖는 화소 전극층(4030)은 박막 트랜지스터(4010)와 접속된다. 그리고, 액정 소자(4013)의 대향 전극층(4031)은 제 2 기판(4006) 위에 형성된다. 화소 전극층(4030)과 대향 전극층(4031)과 액정층(4008)이 중첩되는 부분이 액정 소자(4013)에 상당한다. 또한, 화소 전극층(4030), 대향 전극층(4031)은 각각 배향막으로서 기능하는 절연층(4032), 절연층(4033)이 제공되고, 절연층(4032), 절연층(4033)을 개재(介在)하여 액정층(4008)을 협지(挾持)한다.

또한, 제 1 기판(4001), 제 2 기판(4006)으로서는, 투광성 기판을 사용할 수 있으며, 유리, 세라믹스, 플라스틱을 사용할 수 있다. 플라스틱으로서는, FRP(Fiberglass-Reinforced Plastics)판, PVF(폴리비닐플루오라이드) 필름, 폴리에스테르 필름, 또는 아크릴 수지 필름을 사용할 수 있다.

또한, 구조체(4035)는 절연막이 선택적으로 에칭되어 얻어지는 기둥 형상 스페이서이며, 화소 전극층(4030)과 대향 전극층(4031) 사이의 거리(셀 갭)를 제어하기 위해 제공된다. 또한, 구 형상의 스페이서를 사용하여도 좋다. 또한, 대향 전극층(4031)은 트랜지스터(4010)와 동일 기판 위에 제공되는 공통 전위선에 접속된다. 공통 접속부를 사용하여, 한 쌍의 기판간에 배치되는 도전성 입자를 통하여 대향 전극층(4031)과 공통 전위선을 접속할 수 있다. 한편, 도전성 입자는 실재(4005)에 함유시킬 수 있다.

또한, 액정 소자의 전극의 구조는 액정 소자의 표시 모드에 의해 적절히 변경할 수 있다.

또한, 액정 표시 장치에서는 기판의 외측(시인측)에 편광판을 제공하고, 내측에 착색층, 표시 소자에 이용하는 전극층의 순서로 제공하는 예를 나타내지만, 편광판은 기판의 내측에 제공하여도 좋다. 또한, 편광판과 착색층의 적층 구조도 본 실시형태에 한정되지 않으며, 편광판 및 착색층의 재료나 제작 공정 조건에 따라 적절히 설정하면 좋다. 또한, 표시부 이외에 블랙 매트릭스로서 기능하는 차광막을 제공하여도 좋다.

트랜지스터(4010) 및 트랜지스터(4011)는 반도체층 이외에, 게이트 절연층, 게이트 전극층, 및 배선층(소스 배선층이나 용량 배선층 등)으로 구성된다.

또한, 트랜지스터(4010) 및 트랜지스터(4011) 위에 절연층(4020)이 형성된다. 절연층(4020)으로서는 일례로 RF 스퍼터링법에 의해 형성한 질화 실리콘막을 사용한다.

또한, 평탄화 절연막으로서 절연층(4021)을 형성한다. 절연층(4021)으로서는 폴리이미드, 아크릴, 벤조사이클로부텐계 수지, 폴리아미드, 에폭시 등 내열성을 갖는 유기 재료를 사용할 수 있다. 또한, 상기 유기 재료 이외에, 저유전율 재료(low-k 재료), 실록산계 수지, PSG(인 유리), BPSG(인붕소 유리) 등을 사용할 수 있다. 이때, 이들 재료로 형성되는 복수의 절연막을 적층시킴으로써, 절연층(4021)을 형성하여도 좋다.

화소 전극층(4030), 대향 전극층(4031)에는 산화 텅스텐을 함유한 인듐 산화물, 산화 텅스텐을 함유한 인듐 아연 산화물, 산화 티타늄을 함유한 인듐 산화물, 산화 티타늄을 함유한 인듐 주석 산화물, 산화 인듐 주석, 인듐 아연 산화물, 산화 실리콘이 첨가된 인듐 주석 산화물 등 투광성을 갖는 도전성 재료를 사용할 수 있다.

도전성 고분자로서는, 소위 π전자 공액계 도전성 고분자를 사용할 수 있다. 예를 들어, 폴리아닐린 또는 그 유도체, 폴리피롤 또는 그 유도체, 폴리티오펜 또는 그 유도체, 또는 아닐린, 피롤, 및 티오펜 중의 2종 이상으로 이루어진 공중합체 또는 그 유도체 등을 들 수 있다.

또한, 별도로 형성된 소스 라인 구동 회로(4003)와, 게이트 라인 구동 회로(4004) 또는 화소부(4002)에 공급되는 각종 신호 및 전위는 FPC(4018)로부터 공급된다.

접속 단자 전극(4015)은 액정 소자(4013)에 포함된 화소 전극층(4030)과 같은 도전막으로 형성되고, 단자 전극(4016)은 박막 트랜지스터(4010), 트랜지스터(4011)의 소스 전극층 및 드레인 전극층과 같은 도전막으로 형성된다.

접속 단자 전극(4015)은 이방성 도전막(4019)을 개재하여 FPC(4018)가 갖는 단자와 전기적으로 접속된다.

또한, 도 9에서는 소스 라인 구동 회로(4003)를 별도로 형성하여 제 1 기판(4001)에 실장한 예를 도시하였지만, 본 실시형태는 이 구성에 한정되지 않는다. 게이트 라인 구동 회로를 별도 형성하여 실장하여도 좋고, 소스 라인 구동 회로의 일부 또는 게이트 라인 구동 회로의 일부만을 별도 형성하여 실장하여도 좋다.

본 실시형태는 다른 실시형태에 기재된 구성과 적절히 조합하여 실시할 수 있다.

(실시형태 3)

본 실시형태에서는 실시형태 2에서 설명한 액정 소자의 표시 모드에 대해서 설명한다. 또한, 실시형태 2에서는 TN(Twisted Nematic) 모드의 단면이 되는 액정 소자의 일례를 도시하였지만, 다른 표시 모드로 할 수도 있다. 이하에서는, 각 표시 모드에서의 액정을 동작시키는 전극 및 기판에 대해서 모식도를 사용하여 설명한다.

도 10은 TN 모드의 단면이 되는 액정 소자의 모식도이다.

서로 대향하도록 배치된 제 1 기판(5801) 및 제 2 기판(5802) 사이에 액정층(5800)이 협지된다. 제 1 기판(5801)에 제 1 전극(5805)이 형성된다. 제 2 기판(5802)에 제 2 전극(5806)이 형성된다.

도 11의 (A)는 VA(Vertical Alignment) 모드의 액정 표시 장치의 단면의 모식도이다. VA 모드는 무전계일 때, 액정 분자가 기판에 수직이 되도록 배향되는 모드이다.

서로 대향하도록 배치된 제 1 기판(5811) 및 제 2 기판(5812) 사이에 액정층(5810)이 협지된다. 제 1 기판(5811)에 제 1 전극(5815)이 형성된다. 제 2 기판(5812)에 제 2 전극(5816)이 형성된다.

도 11의 (B)는 MVA(Multi-domain Vertical Alignment) 모드의 액정 표시 장치의 단면의 모식도이다. MVA 모드는 돌기물을 제공함으로써, 복수 방향으로 액정 분자의 배향이 제어되어 시야각 의존성을 보상(補償)하는 방법이다.

서로 대향하도록 배치된 제 1 기판(5821) 및 제 2 기판(5822) 사이에 액정층(5820)이 협지된다. 제 1 기판(5821)에 제 1 전극(5825)이 형성된다. 제 2 기판(5822)에 제 2 전극(5826)이 형성된다. 제 1 전극(5825) 위에는 배향 제어용으로 제 1 돌기물(5827)이 형성된다. 제 2 전극(5826) 위에는 배향 제어용으로 제 2 돌기물(5828)이 형성된다.

도 12의 (A)는 IPS(In-Plane-Switching) 모드의 액정 표시 장치의 단면의 모식도이다. IPS 모드는 액정 분자를 기판에 대해 평행한 면 내에서 항상 회전시키는 모드이며, 화면을 보는 각도에 따른 액정층의 굴절률의 차이가 작기 때문에, 시야각 의존이 적다. IPS 모드는 전극을 한쪽 기판 측에만 제공한 수평 전계 방식을 채용한다.

서로 대향하도록 배치된 제 1 기판(5851) 및 제 2 기판(5852) 사이에 액정층(5850)이 협지된다. 제 2 기판(5852)에 제 1 전극(5855) 및 제 2 전극(5856)이 형성된다.

또한, IPS 모드 등의 수평 전계 방식의 전극 구조에서는 배향막을 사용하지 않는, 블루상을 나타내는 액정을 사용하여도 좋다.

도 12의 (B)는 FFS(Fringe Field Switching) 모드의 단면의 모식도이다. FFS 모드는 액정 분자를 기판에 대해 평행한 면 내에서 항상 회전시키는 모드이며, 화면을 보는 각도에 따른 액정층의 굴절률의 차이가 작기 때문에, 시야각 의존이 적다. FFS 모드는 전극을 한쪽 기판 측에만 제공한 수평 전계 방식을 채용한다.

서로 대향하도록 배치된 제 1 기판(5861) 및 제 2 기판(5862) 사이에 액정층(5860)이 협지된다. 제 2 기판(5862)에 제 2 전극(5866)이 형성된다. 제 2 전극(5866)에 절연막(5867)이 형성된다. 절연막(5867) 위에 제 1 전극(5865)이 형성된다.

본 실시형태는 다른 실시형태에 기재된 구성과 적절히 조합하여 실시하는 것이 가능하다.

(실시형태 4)

본 실시형태에서는, 상술한 실시형태에서 설명한 액정 표시 장치를 구비하는 전자 기기에 대해서 설명한다. 전자 기기로서는, 텔레비전 수상기, 비디오 카메라, 디지털 카메라 등의 카메라, 고글형 디스플레이, 내비게이션 시스템, 음향 재생 장치(카오디오, 오디오 콤포넌트 등), 컴퓨터, 게임 기기, 휴대 정보 단말(모바일 컴퓨터, 휴대 전화, 스마트폰, 휴대형 오락기, 전자 서적, 또는 태블릿 단말 등), 기록 매체를 구비한 화상 재생 장치(구체적으로는 Digital Versatile Disc(DVD) 등의 기록 매체를 재생하고, 그 화상을 표시할 수 있는 표시 장치를 구비한 장치) 등을 들 수 있다. 이들 전자 기기의 구체적인 예에 대하여, 도 13 내지 도 15를 사용하여 설명한다.

도 13의 (A)는 휴대형 오락기이며, 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 접속 단자(9636), 기록 매체 판독부(9672) 등을 구비할 수 있다. 도 13의 (A)의 휴대용 오락기는 기록 매체에 기록된 프로그램 또는 데이터를 판독하여 표시부에 표시하는 기능, 무선 통신에 의해 다른 휴대용 오락기와 정보를 공유하는 기능 등을 가질 수 있다. 도 13의 (A)에 도시된 휴대형 오락기의 기능은 이것에 한정되지 않으며, 다양한 기능을 가질 수 있다.

도 13의 (B)는 디지털 카메라이며, 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 접속 단자(9636), 셔터 버튼(9676), 및 수상부(9677) 등을 구비할 수 있다. 도 13의 (B)의 디지털 카메라는 정지 화상을 촬영하는 기능, 동영상을 촬영하는 기능, 촬영된 화상을 자동적으로 또는 수동적으로 보정하는 기능, 촬영된 화상 등의 정보를 저장하는 기능, 촬영된 화상 등의 정보를 표시부에 표시하는 기능 등을 가질 수 있다. 도 13의 (B)에 도시된 디지털 카메라는 이것에 한정되지 않으며 다양한 기능을 가질 수 있다.

도 13의 (C)는 텔레비전 수상기이며, 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 접속 단자(9636) 등을 구비할 수 있다. 도 13의 (C)의 텔레비전 수상기는 텔레비전용 전파를 화상 신호로 변환하는 기능, 화상 신호를 처리하여, 표시하는 데 적합한 신호로 변환하는 기능, 화상 신호의 프레임 주파수를 변환하는 기능 등을 가질 수 있다. 또한, 도 13의 (C)에 도시한 텔레비전 수상기가 갖는 기능은 이것에 한정되지 않으며, 다양한 기능을 가질 수 있다.

또한, 상술한 실시형태에서 설명한 바와 같이, 표시부(9631)의 화면 전체가 재기록되는 타이밍에 리셋 신호를 입력하는 구성으로 하는 경우에는, 채널이나 입력 장치를 전환할 때, 프로그램이 CF로 전환될 때 등에 리셋 신호를 입력하면 좋다.

도 14의 (A)는 컴퓨터이며, 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 접속 단자(9636), 포인팅 디바이스(9681), 외부 접속 포트(9680) 등을 구비할 수 있다. 도 14의 (A)에 도시된 컴퓨터는 다양한 정보(정지 화상, 동영상, 및 텍스트 화상 등)를 표시부에 표시하는 기능, 다양한 소프트웨어(프로그램)에 의해 처리를 제어하는 기능, 무선 통신 또는 유선 통신 등의 통신 기능, 통신 기능을 이용하여 다양한 컴퓨터 네트워크에 접속하는 기능, 통신 기능을 이용하여 다양한 데이터를 송신 또는 수신하는 기능 등을 가질 수 있다. 또한, 도 14의 (A)의 컴퓨터가 갖는 기능은 이것에 한정되지 않으며, 다양한 기능을 가질 수 있다.

다음에, 도 14의 (B)는 휴대 전화이며, 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 마이크로폰(9638), 외부 접속 포트(9680) 등을 구비할 수 있다. 도 14의 (B)에 도시된 휴대 전화는 다양한 정보(정지 화상, 동영상, 텍스트 화상 등)를 표시부에 표시하는 기능, 달력, 날짜, 또는 시간 등을 표시부에 표시하는 기능, 표시부에 표시된 정보를 조작하거나 편집하는 기능, 다양한 소프트웨어(프로그램)에 의해 처리를 제어하는 기능 등을 가질 수 있다. 또한, 도 14의 (B)에 도시된 휴대 전화가 갖는 기능은 이것에 한정되지 않으며, 다양한 기능을 가질 수 있다.

다음에, 도 14의 (C)는 전자 종이(E-book이라고도 함)이며, 하우징(9630), 표시부(9631), 조작 키(9635) 등을 구비할 수 있다. 도 14의 (C)에 도시된 전자 종이는 다양한 정보(정지 화상, 동영상, 텍스트 화상 등)를 표시부에 표시하는 기능, 달력, 날짜, 시간 등을 표시부에 표시하는 기능, 표시부에 표시된 정보를 조작하거나 편집하는 기능, 다양한 소프트웨어(프로그램)에 의해 처리를 제어하는 기능 등을 가질 수 있다. 또한, 도 14의 (C)에 도시된 전자 종이가 갖는 기능은 이것에 한정되지 않으며, 다양한 기능을 가질 수 있다.

도 15의 (A) 및 도 15의 (B)는 폴더형 태블릿 단말이다. 도 15의 (A)는 태블릿 단말을 펼친 상태이며, 하우징(9630), 표시부(9631a), 표시부(9631b), 표시 모드 전환 스위치(9624), 전원 스위치(9625), 전력 절약 모드 전환 스위치(9626), 후크(9623), 조작 스위치(9628)를 갖는다.

표시부(9631a)는 일부를 터치 패널의 영역(9642a)으로 할 수 있고, 표시된 조작 키(9648)를 터치함으로써 데이터 입력을 할 수 있다. 또한, 도면에서는 일례로서 표시부(9631a)에 있어서 영역의 반이 표시만 하는 기능을 갖는 구성이고 영역의 나머지 반이 터치 패널 기능을 갖는 구성을 도시하였지만, 이 구성에 한정되지 않는다. 표시부(9631a)의 모든 영역이 터치 패널의 기능을 갖는 구성으로 하여도 좋다. 예를 들어, 표시부(9631a)의 전체 면에 키보드 버튼을 표시시켜 터치 패널로 하고, 표시부(9631b)를 표시 화면으로서 사용할 수 있다.

또한, 표시부(9631b)에서도 표시부(9631a)와 마찬가지로, 표시부(9631b)의 일부를 터치 패널의 영역(9642b)으로 할 수 있다. 또한, 터치 패널의 키보드 표시 전환 버튼(9649)이 표시되어 있는 위치를 손가락이나 스타일러스 등으로 터치함으로써 표시부(9631b)에 키보드 버튼을 표시할 수 있다.

또한, 터치 패널의 영역(9642a)과 터치 패널의 영역(9642b)에 대해 동시적으로 터치 입력을 수행할 수도 있다.

또한, 표시 모드 전환 스위치(9624)는 세로 표시 또는 가로 표시 등의 표시 방향을 전환하거나, 흑백 표시나 컬러 표시의 전환 등을 선택할 수 있다. 전력 절약 모드 전환 스위치(9626)는 태블릿 단말에 내장되어 있는 광 센서로 검출되는 사용시의 외광의 광량에 따라 표시의 휘도를 최적의 것으로 할 수 있다. 태블릿 단말은 광 센서뿐만 아니라, 자이로, 가속도 센서 등 기울기를 검출하는 센서와 같은 다른 검출 장치를 내장하여도 좋다.

또한, 도 15의 (A)에서는 표시부(9631b)와 표시부(9631a)의 표시 면적이 같은 예를 도시하였지만, 이것에 특별히 한정되지 않으며, 크기가 서로 달라도 좋고 표시 품질도 달라도 좋다. 예를 들어, 한쪽이 다른 쪽보다 고정세한 표시가 가능한 표시 패널로 하여도 좋다.

도 15의 (B)는 태블릿 단말을 닫은 상태를 도시한 것이며, 하우징(9630), 태양 전지(9643), 충방전 제어 회로(9644), 배터리(9645), DCDC 컨버터(9646)를 구비한다. 또한, 도 15의 (B)에서는 충방전 제어 회로(9644)의 일례로서 배터리(9645), DCDC 컨버터(9646)를 구비하는 구성을 도시하였다.

또한, 태블릿 단말은 접을 수 있기 때문에, 사용하지 않을 때는 하우징(9630)을 닫은 상태로 할 수 있다. 따라서, 표시부(9631a), 표시부(9631b)를 보호할 수 있기 때문에, 내구성이 우수하며 장기 사용의 관점에서 보아도 신뢰성이 우수한 태블릿 단말을 제공할 수 있다.

또한, 이 외에도 도 15의 (A) 및 (B)에 도시된 태블릿 단말은 다양한 정보(정지 화상, 동영상, 텍스트 화상 등)를 표시하는 기능, 달력, 날짜, 또는 시각 등을 표시부에 표시하는 기능, 표시부에 표시한 정보를 터치 입력 조작하거나 또는 편집하는 터치 입력 기능, 각종 소프트웨어(프로그램)에 의하여 처리를 제어하는 기능 등을 가질 수 있다.

태블릿 단말의 표면에 장착된 태양 전지(9643)에 의하여, 터치 패널, 표시부, 또는 영상 신호 처리부 등에 전력을 공급할 수 있다. 또한, 태양 전지(9643)를 하우징(9630)의 한쪽 면 또는 양쪽 면에 제공할 수 있으며, 배터리(9645)를 효율적으로 충전할 수 있는 구성으로 할 수 있다. 또한 배터리(9645)로서 리튬 이온 전지를 사용하면, 소형화를 도모할 수 있는 등의 이점이 있다.

또한, 도 15의 (B)에 도시된 충방전 제어 회로(9644)의 구성 및 동작에 대하여 도 15의 (C)에 블록도를 도시하여 설명한다. 도 15의 (C)는 태양 전지(9643), 배터리(9645), DCDC 컨버터(9646), 컨버터(9647), 스위치(SW1) 내지 스위치(SW3), 표시부(9631)를 도시한 것이며, 배터리(9645), DCDC 컨버터(9646), 컨버터(9647), 스위치(SW1) 내지 스위치(SW3)가 도 15의 (B)에 도시한 충방전 제어 회로(9644)에 대응하는 부분이다.

먼저, 외광을 이용하여 태양 전지(9643)에 의해 발전되는 경우의 동작 예에 대해서 설명한다. 태양 전지(9643)로 발전한 전력은 배터리(9645)를 충전하기 위한 전압이 되도록 DCDC 컨버터(9646)로 승압 또는 강압이 수행된다. 그리고, 표시부(9631)의 동작에 태양 전지(9643)로부터의 전력이 사용될 때는 스위치(SW1)를 온 상태로 하여, 컨버터(9647)에 의해 표시부(9631)에 필요한 전압으로 승압 또는 강압을 수행한다. 또한, 표시부(9631)에서의 표시를 실시하지 않을 때는 스위치(SW1)를 오프 상태로 하고 스위치(SW2)를 온 상태로 하여 배터리(9645)를 충전하는 구성으로 하면 좋다.

또한, 태양 전지(9643)에 대해서는 발전 수단의 일례로서 도시하였지만, 특별히 한정되지 않고 압전 소자(피에조 소자)나 열전 변환 소자(펠티어 소자) 등 다른 발전 수단에 의해 배터리(9645)를 충전하는 구성이라도 좋다. 예를 들어, 무선(비접촉)으로 전력을 송수신하여 충전하는 무접점 전력 전송 모듈이나, 다른 충전 수단을 조합하여 수행하는 구성으로 하여도 좋다.

본 실시형태에 기재된 전자 기기는 상술한 실시형태에서 설명한 액정 표시 장치를 구비함으로써, 저소비 전력화를 도모할 수 있다.

본 실시형태는 다른 실시형태에 기재된 구성과 적절히 조합하여 실시할 수 있다.

100: 액정 표시 장치

101: 표시 제어 신호 생성 회로

102: 선택 회로

103: 표시 패널

104: 게이트 라인 구동 회로

105: 소스 라인 구동 회로

106: 화소부

107: 디지털/아날로그 변환 회로

108: 화소

109: 게이트 라인

110: 소스 라인

201: 시프트 레지스터 회로

202: 시프트 레지스터 회로

203: 아날로그 스위치

204: 트랜지스터

205: 용량 소자

206: 액정 소자

211: 화소

212: 화소

213: 화소

221: 화소

222: 화소

223: 화소

231: 화소

232: 화소

233: 화소

4001: 기판

4002: 화소부

4003: 소스 라인 구동 회로

4004: 게이트 라인 구동 회로

4005: 실재

4006: 기판

4008: 액정층

4010: 트랜지스터

4011: 트랜지스터

4013: 액정 소자

4015: 접속 단자 전극

4016: 단자 전극

4018: FPC

4019: 이방성 도전막

4020: 절연층

4021: 절연층

4030: 화소 전극층

4031: 대향 전극층

4032: 절연층

4033: 절연층

4035: 구조체

5800: 액정층

5801: 기판

5802: 기판

5805: 전극

5806: 전극

5810: 액정층

5811: 기판

5812: 기판

5815: 전극

5816: 전극

5820: 액정층

5821: 기판

5822: 기판

5825: 전극

5826: 전극

5827: 돌기물

5828: 돌기물

5850: 액정층

5851: 기판

5852: 기판

5855: 전극

5856: 전극

5860: 액정층

5861: 기판

5862: 기판

5865: 전극

5866: 전극

5867: 절연막

9623: 후크

9624: 스위치

9625: 전원 스위치

9626: 스위치

9628: 조작 스위치

9630: 하우징

9631: 표시부

9631a: 표시부

9631b: 표시부

9633: 스피커

9635: 조작 키

9636: 접속 단자

9638: 마이크로폰

9642a: 영역

9642b: 영역

9643: 태양 전지

9644: 충방전 제어 회로

9645: 배터리

9646: DCDC 컨버터

9647: 컨버터

9648: 조작 키

9649: 버튼

9672: 기록 매체 판독부

9676: 셔터 버튼

9677: 수상부

9680: 외부 접속 포트

9681: 포인팅 디바이스

101: 표시 제어 신호 생성 회로

102: 선택 회로

103: 표시 패널

104: 게이트 라인 구동 회로

105: 소스 라인 구동 회로

106: 화소부

107: 디지털/아날로그 변환 회로

108: 화소

109: 게이트 라인

110: 소스 라인

201: 시프트 레지스터 회로

202: 시프트 레지스터 회로

203: 아날로그 스위치

204: 트랜지스터

205: 용량 소자

206: 액정 소자

211: 화소

212: 화소

213: 화소

221: 화소

222: 화소

223: 화소

231: 화소

232: 화소

233: 화소

4001: 기판

4002: 화소부

4003: 소스 라인 구동 회로

4004: 게이트 라인 구동 회로

4005: 실재

4006: 기판

4008: 액정층

4010: 트랜지스터

4011: 트랜지스터

4013: 액정 소자

4015: 접속 단자 전극

4016: 단자 전극

4018: FPC

4019: 이방성 도전막

4020: 절연층

4021: 절연층

4030: 화소 전극층

4031: 대향 전극층

4032: 절연층

4033: 절연층

4035: 구조체

5800: 액정층

5801: 기판

5802: 기판

5805: 전극

5806: 전극

5810: 액정층

5811: 기판

5812: 기판

5815: 전극

5816: 전극

5820: 액정층

5821: 기판

5822: 기판

5825: 전극

5826: 전극

5827: 돌기물

5828: 돌기물

5850: 액정층

5851: 기판

5852: 기판

5855: 전극

5856: 전극

5860: 액정층

5861: 기판

5862: 기판

5865: 전극

5866: 전극

5867: 절연막

9623: 후크

9624: 스위치

9625: 전원 스위치

9626: 스위치

9628: 조작 스위치

9630: 하우징

9631: 표시부

9631a: 표시부

9631b: 표시부

9633: 스피커

9635: 조작 키

9636: 접속 단자

9638: 마이크로폰

9642a: 영역

9642b: 영역

9643: 태양 전지

9644: 충방전 제어 회로

9645: 배터리

9646: DCDC 컨버터

9647: 컨버터

9648: 조작 키

9649: 버튼

9672: 기록 매체 판독부

9676: 셔터 버튼

9677: 수상부

9680: 외부 접속 포트

9681: 포인팅 디바이스

Claims (16)

- 액정 표시 장치에 있어서,

액정 소자를 포함하는 화소와;

비디오 신호의 극성을 m프레임(m은 2 이상의 자연수)마다 반전시키면서 상기 비디오 신호를 상기 화소에 입력하고, 상기 비디오 신호가 상기 화소에 입력되지 않을 때에 리셋 신호를 상기 화소에 입력하는 구동 회로를 포함하는, 액정 표시 장치. - 제 1 항에 있어서,

상기 리셋 신호의 전위는 제 1 기간에는 공통 전위보다 높고, 제 2 기간에는 상기 공통 전위보다 낮은, 액정 표시 장치. - 제 2 항에 있어서,

상기 리셋 신호의 상기 전위는 상기 제 1 기간 및 상기 제 2 기간 후에는 상기 공통 전위와 대략 같은 전위인, 액정 표시 장치. - 제 1 항에 있어서,

상기 화소에 대해 광을 발광할 수 있는 백 라이트를 더 포함하고,

상기 구동 회로는 상기 백 라이트가 발광하지 않을 때에 상기 리셋 신호를 상기 화소에 입력하는, 액정 표시 장치. - 액정 표시 장치에 있어서,

액정 소자 및 상기 액정 소자에 전기적으로 접속된 트랜지스터를 포함하는 화소와;

비디오 신호의 극성을 m프레임(m은 2 이상의 자연수)마다 반전시키면서 상기 비디오 신호를 상기 화소에 입력하고, 상기 비디오 신호가 상기 화소에 입력되지 않을 때에 리셋 신호를 상기 화소에 입력하는 구동 회로를 포함하고,

상기 트랜지스터는 채널 형성 영역을 포함하는 산화물 반도체층을 포함하는, 액정 표시 장치. - 제 5 항에 있어서,

상기 리셋 신호의 전위는 제 1 기간에는 공통 전위보다 높고, 제 2 기간에는 상기 공통 전위보다 낮은, 액정 표시 장치. - 제 6 항에 있어서,

상기 리셋 신호의 상기 전위는 상기 제 1 기간 및 상기 제 2 기간 후에는 상기 공통 전위와 대략 같은 전위인, 액정 표시 장치. - 제 5 항에 있어서,

상기 화소에 대해 광을 발광할 수 있는 백 라이트를 더 포함하고,

상기 구동 회로는 상기 백 라이트가 발광하지 않을 때에 상기 리셋 신호를 상기 화소에 입력하는, 액정 표시 장치. - 액정 표시 장치에 있어서,

트랜지스터 및 상기 트랜지스터에 전기적으로 접속된 액정 소자를 각각 포함하는 복수의 화소와;

상기 복수의 화소 각각에 비디오 신호 및 리셋 신호를 입력하는 구동 회로를 포함하고,

상기 구동 회로는 상기 비디오 신호의 극성을 m프레임(m은 2 이상의 자연수)마다 반전시키면서 상기 비디오 신호를 상기 복수의 화소 각각에 입력하고,

상기 구동 회로는 상기 비디오 신호가 입력되지 않는 기간에 상기 리셋 신호를 상기 복수의 화소 각각에 입력하는, 액정 표시 장치. - 제 9 항에 있어서,

상기 구동 회로는 상기 리셋 신호를 상기 복수의 화소 각각에 입력하고, 상기 리셋 신호의 전위는 상기 전위가 공통 전위보다 높은 기간 및 상기 전위가 상기 공통 전위보다 낮은 기간이 적어도 한 번 반복된 후에, 상기 공통 전위와 대략 같은 전위인, 액정 표시 장치. - 제 9 항에 있어서,

상기 액정 소자는 한 쌍의 전극을 포함하고,

상기 리셋 신호를 입력함으로써 상기 액정 소자의 상기 한 쌍의 전극 사이의 전위차를 대략 0V로 한 후, 상기 트랜지스터가 오프 상태가 되는, 액정 표시 장치. - 제 9 항에 있어서,

상기 구동 회로가 상기 리셋 신호를 상기 복수의 화소 모두에 입력한 후, 전원 공급이 차단되는, 액정 표시 장치. - 제 9 항에 있어서,

상기 복수의 화소에 대해 광을 발광할 수 있는 백 라이트를 더 포함하고,

상기 구동 회로는 상기 백 라이트가 발광하지 않을 때에 상기 리셋 신호를 상기 복수의 화소 각각에 입력하는, 액정 표시 장치. - 제 9 항에 있어서,

상기 구동 회로는 상기 화소 모두에서 데이터가 재기록됨과 동시에 상기 리셋 신호를 상기 복수의 화소 각각에 입력하는, 액정 표시 장치. - 제 9 항에 있어서,

설정 시간에 상기 액정 표시 장치를 기동시키는 타이머를 더 포함하고,

상기 구동 회로는 상기 액정 표시 장치가 상기 타이머에 의해 전원 오프 상태로부터 기동되었을 때, 상기 리셋 신호를 상기 복수의 화소 각각에 입력하는, 액정 표시 장치. - 제 9 항에 있어서,

상기 트랜지스터는 산화물 반도체를 포함하는, 액정 표시 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012165630 | 2012-07-26 | ||

| JPJP-P-2012-165630 | 2012-07-26 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20140013931A true KR20140013931A (ko) | 2014-02-05 |

Family

ID=49994414

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020130082985A KR20140013931A (ko) | 2012-07-26 | 2013-07-15 | 액정 표시 장치 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9390664B2 (ko) |

| JP (2) | JP2014041348A (ko) |

| KR (1) | KR20140013931A (ko) |

| CN (1) | CN103578442B (ko) |

| TW (1) | TWI588808B (ko) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014032399A (ja) | 2012-07-13 | 2014-02-20 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| US9984644B2 (en) | 2012-08-08 | 2018-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and method for driving the same |

| WO2014185122A1 (ja) * | 2013-05-15 | 2014-11-20 | シャープ株式会社 | 液晶表示装置 |

| JP2018013765A (ja) | 2016-04-28 | 2018-01-25 | 株式会社半導体エネルギー研究所 | 電子デバイス |

| JP2018040963A (ja) * | 2016-09-08 | 2018-03-15 | ラピスセミコンダクタ株式会社 | 表示ドライバ及び表示装置 |

| JP7191818B2 (ja) * | 2017-04-27 | 2022-12-19 | 株式会社半導体エネルギー研究所 | 表示ユニット |

| JP6798470B2 (ja) * | 2017-11-08 | 2020-12-09 | カシオ計算機株式会社 | 電子時計、表示制御方法、及びプログラム |

Family Cites Families (165)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JPH08179728A (ja) * | 1994-12-21 | 1996-07-12 | Sharp Corp | 液晶表示装置 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| US5821910A (en) | 1995-05-26 | 1998-10-13 | National Semiconductor Corporation | Clock generation circuit for a display controller having a fine tuneable frame rate |

| US5900886A (en) | 1995-05-26 | 1999-05-04 | National Semiconductor Corporation | Display controller capable of accessing an external memory for gray scale modulation data |

| KR100394896B1 (ko) | 1995-08-03 | 2003-11-28 | 코닌클리케 필립스 일렉트로닉스 엔.브이. | 투명스위칭소자를포함하는반도체장치 |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| TW375696B (en) | 1996-06-06 | 1999-12-01 | Toshiba Corp | Display device |

| JPH10111491A (ja) * | 1996-10-08 | 1998-04-28 | Fujitsu Ltd | 液晶表示装置 |

| JPH10293286A (ja) | 1997-02-21 | 1998-11-04 | Toshiba Corp | 液晶表示装置の駆動方法 |

| KR100266212B1 (ko) | 1997-05-17 | 2000-09-15 | 구본준; 론 위라하디락사 | 잔상제거기능을가지는액정표시장치 |

| JPH1124041A (ja) * | 1997-06-30 | 1999-01-29 | Toshiba Corp | 液晶表示装置 |

| US6496172B1 (en) | 1998-03-27 | 2002-12-17 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device, active matrix type liquid crystal display device, and method of driving the same |

| JP2000081606A (ja) | 1998-06-29 | 2000-03-21 | Sanyo Electric Co Ltd | 液晶表示素子の駆動方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| JP3589395B2 (ja) | 1999-03-29 | 2004-11-17 | シャープ株式会社 | 液晶表示装置 |

| JP3466951B2 (ja) * | 1999-03-30 | 2003-11-17 | 株式会社東芝 | 液晶表示装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4519251B2 (ja) * | 1999-10-13 | 2010-08-04 | シャープ株式会社 | 液晶表示装置およびその制御方法 |

| TW494382B (en) | 2000-03-22 | 2002-07-11 | Toshiba Corp | Display apparatus and driving method of display apparatus |

| CN1220098C (zh) | 2000-04-28 | 2005-09-21 | 夏普株式会社 | 显示器件、显示器件驱动方法和装有显示器件的电子设备 |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| JP2002107769A (ja) * | 2000-09-29 | 2002-04-10 | Toshiba Corp | 液晶表示素子および液晶配向方法 |

| JP3842030B2 (ja) | 2000-10-06 | 2006-11-08 | シャープ株式会社 | アクティブマトリクス型表示装置およびその駆動方法 |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP2002229532A (ja) | 2000-11-30 | 2002-08-16 | Toshiba Corp | 液晶表示装置及び液晶表示装置の駆動方法 |

| JP3607197B2 (ja) | 2000-12-26 | 2005-01-05 | シャープ株式会社 | 表示駆動装置および表示装置モジュール |

| JP3730159B2 (ja) | 2001-01-12 | 2005-12-21 | シャープ株式会社 | 表示装置の駆動方法および表示装置 |

| JP4879427B2 (ja) | 2001-02-21 | 2012-02-22 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3916986B2 (ja) * | 2001-05-18 | 2007-05-23 | シャープ株式会社 | 信号処理回路、低電圧信号発生器およびそれを備えた画像表示装置 |

| JP2002351430A (ja) | 2001-05-30 | 2002-12-06 | Mitsubishi Electric Corp | 表示装置 |

| GB2378343B (en) | 2001-08-03 | 2004-05-19 | Sendo Int Ltd | Image refresh in a display |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| EP1443130B1 (en) | 2001-11-05 | 2011-09-28 | Japan Science and Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP3627710B2 (ja) | 2002-02-14 | 2005-03-09 | セイコーエプソン株式会社 | 表示駆動回路、表示パネル、表示装置及び表示駆動方法 |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7023141B2 (en) * | 2002-03-01 | 2006-04-04 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and drive method thereof |

| CN1445821A (zh) | 2002-03-15 | 2003-10-01 | 三洋电机株式会社 | ZnO膜和ZnO半导体层的形成方法、半导体元件及其制造方法 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| EP1582911A4 (en) * | 2003-01-08 | 2007-08-08 | Toshiba Matsushita Display Tec | LIQUID CRYSTAL DISPLAY |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| TWI293750B (en) | 2003-10-02 | 2008-02-21 | Sanyo Electric Co | Method for driving a liquid crystal display device, a liquid crystal display device, and a driving device for such liquid crystal device |

| JP2005157157A (ja) * | 2003-11-28 | 2005-06-16 | Toppoly Optoelectronics Corp | 残留映像除去電気回路 |

| JP4016942B2 (ja) | 2003-12-10 | 2007-12-05 | セイコーエプソン株式会社 | Pwm信号生成回路及び表示ドライバ |

| EP2413366B1 (en) | 2004-03-12 | 2017-01-11 | Japan Science And Technology Agency | A switching element of LCDs or organic EL displays |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| CN101057339B (zh) | 2004-11-10 | 2012-12-26 | 佳能株式会社 | 无定形氧化物和场效应晶体管 |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| KR100953596B1 (ko) | 2004-11-10 | 2010-04-21 | 캐논 가부시끼가이샤 | 발광장치 |

| CN101057338B (zh) | 2004-11-10 | 2011-03-16 | 佳能株式会社 | 采用无定形氧化物的场效应晶体管 |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| JP2006154545A (ja) | 2004-11-30 | 2006-06-15 | Sanyo Electric Co Ltd | 液晶表示装置 |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| JP4433405B2 (ja) | 2005-01-21 | 2010-03-17 | セイコーエプソン株式会社 | 半導体装置の製造方法 |

| TWI569441B (zh) | 2005-01-28 | 2017-02-01 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI472037B (zh) | 2005-01-28 | 2015-02-01 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| WO2006123551A1 (ja) | 2005-05-16 | 2006-11-23 | Tpo Hong Kong Holding Limited | マトリクス駆動方法及び回路並びにこれを用いた表示装置 |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP2007065134A (ja) * | 2005-08-30 | 2007-03-15 | Sanyo Epson Imaging Devices Corp | 液晶表示装置 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| EP3614442A3 (en) | 2005-09-29 | 2020-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having oxide semiconductor layer and manufactoring method thereof |

| KR101142281B1 (ko) | 2005-10-11 | 2012-05-07 | 엘지디스플레이 주식회사 | 유기전계발광소자 및 그 구동방법 |

| EP1777689B1 (en) | 2005-10-18 | 2016-08-10 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device and electronic equipment each having the same |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR20090115222A (ko) | 2005-11-15 | 2009-11-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 제조방법 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| TWI349259B (en) | 2006-05-23 | 2011-09-21 | Au Optronics Corp | A panel module and power saving method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| US8289246B2 (en) * | 2006-06-15 | 2012-10-16 | Sharp Kabushiki Kaisha | Electric current driving type display device and pixel circuit |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP2008046458A (ja) * | 2006-08-18 | 2008-02-28 | Citizen Miyota Co Ltd | 液晶表示装置及び液晶表示装置の駆動方法及びそれを用いたプロジェクション装置 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7777712B2 (en) * | 2006-10-17 | 2010-08-17 | Himax Technologies Limited | Level shift circuit and display using same |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7596201B2 (en) | 2007-03-15 | 2009-09-29 | Epson Imaging Devices Corporation | Gray code counter and display device therewith |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| CN101663762B (zh) | 2007-04-25 | 2011-09-21 | 佳能株式会社 | 氧氮化物半导体 |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| KR100968720B1 (ko) | 2007-06-29 | 2010-07-08 | 소니 주식회사 | 액정 장치, 및 전자기기 |

| TWI383371B (zh) | 2007-08-31 | 2013-01-21 | Chunghwa Picture Tubes Ltd | 時序控制器,顯示裝置與調整迦瑪電壓方法 |

| KR100907255B1 (ko) | 2007-09-18 | 2009-07-10 | 한국전자통신연구원 | 유기 박막 트랜지스터를 구비하는 표시 장치 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| KR101301422B1 (ko) * | 2008-04-30 | 2013-08-28 | 엘지디스플레이 주식회사 | 액정표시장치와 그 구동방법 |

| KR101303424B1 (ko) | 2008-06-12 | 2013-09-05 | 엘지디스플레이 주식회사 | 액정표시장치와 그 구동방법 |

| US8400387B2 (en) * | 2008-07-09 | 2013-03-19 | Citizen Holdings Co., Ltd. | Liquid crystal display device |

| KR101492564B1 (ko) | 2008-08-06 | 2015-03-06 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그것의 공통전압 조절 방법 |

| KR101533741B1 (ko) | 2008-09-17 | 2015-07-03 | 삼성디스플레이 주식회사 | 표시패널의 구동방법 및 이를 이용한 표시장치 |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| JP2010107732A (ja) * | 2008-10-30 | 2010-05-13 | Toshiba Mobile Display Co Ltd | 液晶表示装置 |

| JP2010122493A (ja) | 2008-11-20 | 2010-06-03 | Eastman Kodak Co | 表示装置 |

| WO2010106713A1 (ja) * | 2009-03-18 | 2010-09-23 | シャープ株式会社 | 液晶表示装置およびその駆動方法 |

| US8970460B2 (en) * | 2009-04-01 | 2015-03-03 | Rohm Co., Ltd. | Liquid crystal driving apparatus |

| US20100315396A1 (en) | 2009-06-10 | 2010-12-16 | Himax Technologies Limited | Timing controller, display and charge sharing function controlling method thereof |

| WO2011046010A1 (en) | 2009-10-16 | 2011-04-21 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic device including the liquid crystal display device |

| KR101765849B1 (ko) * | 2009-12-18 | 2017-08-08 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 표시 장치 및 전자 기기 |

| WO2011074379A1 (en) * | 2009-12-18 | 2011-06-23 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and driving method thereof |

| WO2011077925A1 (en) | 2009-12-25 | 2011-06-30 | Semiconductor Energy Laboratory Co., Ltd. | Method for driving liquid crystal display device |

| KR101814222B1 (ko) | 2010-02-12 | 2018-01-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 표시 장치 및 전자 장치 |

| KR101733765B1 (ko) | 2010-02-26 | 2017-05-08 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 표시장치의 구동 방법 |

| KR101698570B1 (ko) * | 2010-03-25 | 2017-01-23 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| US8605059B2 (en) * | 2010-07-02 | 2013-12-10 | Semiconductor Energy Laboratory Co., Ltd. | Input/output device and driving method thereof |

| KR101839953B1 (ko) * | 2011-01-21 | 2018-03-20 | 삼성디스플레이 주식회사 | 구동 장치 및 이를 이용한 표시 장치 |

| JP2014032396A (ja) | 2012-07-13 | 2014-02-20 | Semiconductor Energy Lab Co Ltd | 表示装置の駆動方法、及び表示装置 |

| JP2014032399A (ja) | 2012-07-13 | 2014-02-20 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

-

2013

- 2013-07-15 KR KR1020130082985A patent/KR20140013931A/ko not_active Application Discontinuation

- 2013-07-17 TW TW102125560A patent/TWI588808B/zh not_active IP Right Cessation

- 2013-07-25 CN CN201310316646.6A patent/CN103578442B/zh active Active

- 2013-07-25 US US13/950,951 patent/US9390664B2/en active Active

- 2013-07-26 JP JP2013155166A patent/JP2014041348A/ja not_active Withdrawn

-

2017

- 2017-12-01 JP JP2017231375A patent/JP2018067002A/ja not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| US9390664B2 (en) | 2016-07-12 |

| JP2018067002A (ja) | 2018-04-26 |

| CN103578442B (zh) | 2017-09-29 |

| CN103578442A (zh) | 2014-02-12 |

| US20140028645A1 (en) | 2014-01-30 |

| JP2014041348A (ja) | 2014-03-06 |

| TW201413694A (zh) | 2014-04-01 |

| TWI588808B (zh) | 2017-06-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7411839B2 (ja) | 半導体装置 | |

| JP2020197725A (ja) | 表示パネル | |

| US9390664B2 (en) | Liquid crystal display device | |

| KR101841908B1 (ko) | 표시 장치 | |

| JP5952435B2 (ja) | 液晶表示装置 | |

| JP2020126269A (ja) | 液晶表示装置 | |

| US20140015819A1 (en) | Method for Driving Display Device and Display Device | |

| US9508276B2 (en) | Method of driving display device including comparator circuit, and display device including comparator circuit | |

| JP6290576B2 (ja) | 液晶表示装置及びその駆動方法 | |

| KR20130031820A (ko) | 액정 표시 장치 및 전자 장치 | |

| KR20140020191A (ko) | 액정 표시 장치 및 그 구동 방법 | |

| JP7411837B2 (ja) | 出力回路 | |

| US11587521B2 (en) | Gate driver on array (GOA) circuit and display device solving problem of electrical stress easily biasing threshold voltage of thin film transistor (TFT) | |

| WO2013179787A1 (ja) | 液晶表示装置の駆動方法、液晶表示装置およびそれを備えた携帯機器 | |

| WO2014208130A1 (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |