KR20100065145A - 반도체 장치 및 전자 기기 - Google Patents

반도체 장치 및 전자 기기 Download PDFInfo

- Publication number

- KR20100065145A KR20100065145A KR1020107002910A KR20107002910A KR20100065145A KR 20100065145 A KR20100065145 A KR 20100065145A KR 1020107002910 A KR1020107002910 A KR 1020107002910A KR 20107002910 A KR20107002910 A KR 20107002910A KR 20100065145 A KR20100065145 A KR 20100065145A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- substrate

- semiconductor layer

- single crystal

- semiconductor

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 365

- 239000000758 substrate Substances 0.000 claims abstract description 406

- 239000013078 crystal Substances 0.000 claims abstract description 59

- 238000000034 method Methods 0.000 claims description 163

- 239000011521 glass Substances 0.000 claims description 62

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 56

- 229910052710 silicon Inorganic materials 0.000 claims description 56

- 239000010703 silicon Substances 0.000 claims description 56

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 39

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 39

- 239000005407 aluminoborosilicate glass Substances 0.000 claims description 5

- 239000005354 aluminosilicate glass Substances 0.000 claims description 5

- 229910052788 barium Inorganic materials 0.000 claims description 5

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 claims description 5

- 239000005388 borosilicate glass Substances 0.000 claims description 5

- 238000005498 polishing Methods 0.000 abstract description 5

- 239000000126 substance Substances 0.000 abstract description 2

- 239000010410 layer Substances 0.000 description 470

- 239000010408 film Substances 0.000 description 141

- 230000008569 process Effects 0.000 description 101

- 239000002585 base Substances 0.000 description 77

- 150000002500 ions Chemical class 0.000 description 53

- 239000007789 gas Substances 0.000 description 45

- 238000004519 manufacturing process Methods 0.000 description 36

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 35

- 238000010438 heat treatment Methods 0.000 description 25

- 239000012535 impurity Substances 0.000 description 25

- 238000000926 separation method Methods 0.000 description 25

- 238000005530 etching Methods 0.000 description 24

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 21

- 238000012545 processing Methods 0.000 description 21

- 239000010409 thin film Substances 0.000 description 20

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 19

- 229910052814 silicon oxide Inorganic materials 0.000 description 18

- 230000007547 defect Effects 0.000 description 16

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 15

- 230000015572 biosynthetic process Effects 0.000 description 15

- 230000006870 function Effects 0.000 description 15

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 14

- 239000001257 hydrogen Substances 0.000 description 14

- 229910052739 hydrogen Inorganic materials 0.000 description 14

- 239000011229 interlayer Substances 0.000 description 14

- 239000004973 liquid crystal related substance Substances 0.000 description 14

- 239000001301 oxygen Substances 0.000 description 14

- 229910052760 oxygen Inorganic materials 0.000 description 14

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 14

- 239000012298 atmosphere Substances 0.000 description 12

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 12

- 239000003990 capacitor Substances 0.000 description 11

- 238000004891 communication Methods 0.000 description 11

- 230000001678 irradiating effect Effects 0.000 description 10

- 238000005259 measurement Methods 0.000 description 10

- 229910052757 nitrogen Inorganic materials 0.000 description 10

- 230000001681 protective effect Effects 0.000 description 10

- 230000005669 field effect Effects 0.000 description 9

- 238000010884 ion-beam technique Methods 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 230000010355 oscillation Effects 0.000 description 9

- 230000004888 barrier function Effects 0.000 description 8

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 8

- 235000012431 wafers Nutrition 0.000 description 8

- 238000005468 ion implantation Methods 0.000 description 7

- 239000000463 material Substances 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- 230000015556 catabolic process Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 229910052732 germanium Inorganic materials 0.000 description 6

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 6

- 230000008018 melting Effects 0.000 description 6

- 238000002844 melting Methods 0.000 description 6

- 230000009467 reduction Effects 0.000 description 6

- 125000006850 spacer group Chemical group 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 150000004767 nitrides Chemical class 0.000 description 5

- 238000002161 passivation Methods 0.000 description 5

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- -1 hydrogen ions Chemical class 0.000 description 4

- 150000001282 organosilanes Chemical class 0.000 description 4

- 230000004044 response Effects 0.000 description 4

- 229910000077 silane Inorganic materials 0.000 description 4

- 239000002356 single layer Substances 0.000 description 4

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 3

- 239000003513 alkali Substances 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 238000009835 boiling Methods 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- BIXHRBFZLLFBFL-UHFFFAOYSA-N germanium nitride Chemical compound N#[Ge]N([Ge]#N)[Ge]#N BIXHRBFZLLFBFL-UHFFFAOYSA-N 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 238000009832 plasma treatment Methods 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 230000003746 surface roughness Effects 0.000 description 3

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- 238000001237 Raman spectrum Methods 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000001678 elastic recoil detection analysis Methods 0.000 description 2

- 238000001887 electron backscatter diffraction Methods 0.000 description 2

- 238000011156 evaluation Methods 0.000 description 2

- 230000001747 exhibiting effect Effects 0.000 description 2

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 2

- 229910000449 hafnium oxide Inorganic materials 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002366 halogen compounds Chemical class 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 230000035515 penetration Effects 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 239000010979 ruby Substances 0.000 description 2

- 229910001750 ruby Inorganic materials 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- 238000004506 ultrasonic cleaning Methods 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 238000006124 Pilkington process Methods 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 238000001069 Raman spectroscopy Methods 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- MXSJNBRAMXILSE-UHFFFAOYSA-N [Si].[P].[B] Chemical compound [Si].[P].[B] MXSJNBRAMXILSE-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052789 astatine Inorganic materials 0.000 description 1

- 238000007664 blowing Methods 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- UIZLQMLDSWKZGC-UHFFFAOYSA-N cadmium helium Chemical compound [He].[Cd] UIZLQMLDSWKZGC-UHFFFAOYSA-N 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000003985 ceramic capacitor Substances 0.000 description 1

- 239000000460 chlorine Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 150000002222 fluorine compounds Chemical class 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 1

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 1

- 230000005660 hydrophilic surface Effects 0.000 description 1

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000011835 investigation Methods 0.000 description 1

- 239000007791 liquid phase Substances 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- 229960001730 nitrous oxide Drugs 0.000 description 1

- 235000013842 nitrous oxide Nutrition 0.000 description 1

- 230000006911 nucleation Effects 0.000 description 1

- 238000010899 nucleation Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000007500 overflow downdraw method Methods 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000003014 reinforcing effect Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 230000008054 signal transmission Effects 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- CZDYPVPMEAXLPK-UHFFFAOYSA-N tetramethylsilane Chemical compound C[Si](C)(C)C CZDYPVPMEAXLPK-UHFFFAOYSA-N 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/78654—Monocrystalline silicon transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1262—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate

- H01L27/1266—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate the substrate on which the devices are formed not being the final device substrate, e.g. using a temporary substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

- H01L21/2003—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy characterised by the substrate

- H01L21/2007—Bonding of semiconductor wafers to insulating substrates or to semiconducting substrates using an intermediate insulating layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/30—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by physical imperfections; having polished or roughened surface

- H01L29/34—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by physical imperfections; having polished or roughened surface the imperfections being on the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/66772—Monocristalline silicon transistors on insulating substrates, e.g. quartz substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Element Separation (AREA)

- Recrystallisation Techniques (AREA)

Abstract

내열성이 낮은 기판을 베이스 기판으로 사용하는 SOI 기판을 이용한 고성능 반도체 장치를 제공하는 것을 목적으로 한다. 나아가, 화학적 연마를 사용하지 않고 고성능 반도체 장치를 제조하는 것을 목적으로 한다. 또한, 전자 기기는 상기 반도체 장치를 사용한다. 절연 기판 위의 절연층, 상기 절연층 위의 접합층 및 상기 접합층 위의 단결정 반도체층을 포함하고, 상기 단결정 반도체층의 상부 표면의 요철 형상의 산술 평균 거칠기는 1 nm 이상 7 nm 이하이다. 또는 상기 요철 형상의 제곱평균평방근 거칠기는 1 nm 이상 10 nm 이하이다. 또는 상기 요철 형상의 높이에 있어서 최대 차이가 5 nm 이상 250 nm 이하이다.

Description

본 발명은 반도체 장치 및 전자 기기에 관한 것이다.

본 명세서에서의 반도체 장치는 반도체 특성들을 이용하여 기능하는 모든 장치들을 의미하며, 전기 광학 장치, 반도체 회로 및 전자 기기는 모두 상기 반도체 장치의 범주에 포함된다.

최근에 벌크 실리콘 웨이퍼 대신 SOI(silicon on insulator) 기판을 사용하는 집적 회로가 발전하고 있다. 절연층 위에 형성된 박막 단결정 실리콘막의 특성들을 이용하여 집적 회로에 형성된 트랜지스터들은 각각으로부터 완전하게 전자적으로 분리될 수 있다. 나아가 각 트랜지스터는 완전 공핍 트랜지스터로서 형성될 수 있으므로 고집적, 고속 드라이빙 및 저전력 소비와 같은 높은 부가가치를 갖는 반도체 집적 회로가 실현될 수 있다.

SOI 기판을 제조하는 방법으로서 수소 이온 주입 및 분리를 조합하는 수소-이온-주입 분리법이 알려져 있다. 수소-이온-주입 분리법의 전형적인 절차는 이하 서술하는 바와 같다.

우선, 수소 이온을 실리콘 웨이퍼에 주입하여 표면으로부터 미리 결정된 높이로 이온 주입층을 형성한다. 다음으로, 베이스 기판으로 사용되는 다른 실리콘 웨이퍼를 산화함으로써 산화 실리콘막을 형성한다. 그 다음으로 수소 이온이 주입된 실리콘 웨이퍼를 다른 실리콘 웨이퍼의 산화 실리콘막에 결합시키고 상기 두 개의 실리콘 웨이퍼들을 서로 접합시킨다. 그리고나서 가열 처리를 행하여 웨이퍼를 분리면과 이온 주입층으로 분리시킨다. 가열 처리는 상기 접합에서 결합력을 개선시키기 위하여 행해진다는 것을 주의해야 한다.

단결정 실리콘층을 수소-이온-주입 분리법을 이용하여 유리 기판 위에 형성하는 방법은 공지 기술이다(예로는 특허문헌 1: 일본공개특허공보 특개평11-097379호 참조). 특허문헌 1에서, 이온 주입 또는 분리판에서 높이가 수 나노미터 내지 수십 나노미터인 단차를 제거하기 위하여 분리판을 기계적으로 연마한다.

유리 기판은 실리콘 웨이퍼보다 면적이 더 크고 단가가 낮으며 액정 표시 장치와 같은 표시 장치를 제조하는 데 주로 이용된다. 베이스 기판으로 유리 기판을 이용하면 저렴한 대면적의 SOI 기판을 제조할 수 있다.

그러나 유리 기판의 변형점이 700 ℃ 이하이므로 열 저항이 낮다. 그러므로 유리 기판의 내열 온도 이상으로 가열할 수 없으며 프로세스 온도가 700 ℃ 이하로 한정된다. 즉, 분리판에서 결정 훼손이나 표면 요철을 제거하는 프로세스 온도에 한계가 있다. 나아가 유리 기판에 접합된 단결정 실리콘판을 이용하여 트랜지스터를 제조하는 프로세스 온도에 한계가 있다.

게다가 유리 기판의 크기가 커서 사용가능한 장치 또는 프로세스 방법에 제한이 있다. 예를 들면, 특허문헌 1에 기재된 분리판의 기계적 연마는 큰 면적의 기판에 적용되어야 하는데 프로세싱 정확성, 장치의 비용 등의 관점에서 비현실적이다. 그러나 반도체 소자의 특성을 끌어내기 위해서는, 분리판의 표면 요철을 일정 정도로 억제해야하는 것이 필요하다.

전술한 바와 같이, 유리 기판과 같이 면적이 넓고 내열성(耐熱性)이 낮은 기판이 베이스 기판으로 사용되는 경우에는 반도체층의 표면 요철을 억제하고 원하는 특성을 획득하기가 어렵다.

상술한 문제점들을 해결하고자, 본 발명은 열 저항이 낮은 기판을 베이스 기판으로 사용하는 SOI 기판을 이용하는 고성능 반도체 장치를 제공하는 것을 목적으로 한다. 나아가, 본 발명은 기계적 연마(예를 들어, CMP)를 행하지 않는 고성능 반도체 장치를 제공하는 것을 목적으로 한다. 더 나아가, 본 발명은 상기의 반도체 장치를 이용하는 전자 기기를 제공하는 것을 목적으로 한다.

본 발명의 한 측면에 따른 반도체 장치는 절연 기판 위의 절연층, 상기 절연층 위의 접합층 및 상기 접합층 위에 단결정 반도체층을 포함하고, 상기 단결정 반도체층의 상부 표면에 있는 요철 형상의 산술 평균 거칠기는 1 nm 이상 7 nm 이하인 것을 특징으로 한다.

본 발명의 또 다른 측면에 따른 반도체 장치는 절연 기판 위의 절연층, 상기 절연층 위의 접합층 및 상기 접합층 위의 단결정 반도체층을 포함하고, 상기 단결정 반도체층의 상부 표면에 있는 요철 형상의 제곱평균평방근 거칠기는 1 nm 이상10 nm 이하인 것을 특징으로 한다.

본 발명의 또 다른 측면에 따른 반도체 장치는 절연 기판 위의 절연층, 상기 절연층 위의 접합층 및 상기 접합층 위의 단결정 반도체층을 포함하며, 상기 단결정 반도체층의 상부 표면에 있는 요철 형상의 높이에 있어서 최대 차이가 5nm 이상 250nm 이하인 것을 특징으로 한다.

본 발명의 또 다른 측면에 따른 반도체 장치는 내열 온도가 700 ℃ 이하인 기판, 상기 기판 위의 절연층, 상기 절연층 위의 접합층 및 상기 접합층 위의 단결정 반도체층을 포함하고, 상기 단결정 반도체층의 상부 표면에 있는 요철 형상의 산술 평균 거칠기는 1 nm 이상 7 nm 이하인 것을 특징으로 한다.

본 발명의 또 다른 측면에 따른 반도체 장치는 내열 온도가 700 ℃ 이하인 기판, 상기 기판 위의 절연층, 상기 절연층 위의 접합층, 상기 접합층 위의 단결정 반도체층을 포함하고, 상기 단결정 반도체의 상부 표면에 있는 요철 형상의 제곱평균평방근 거칠기는 1 nm 이상 10 nm 이하인 것을 특징으로 한다.

본 발명의 또 다른 측면에 따른 반도체 장치는 내열 온도가 700 ℃ 이하인 기판, 상기 기판 위의 절연층, 상기 절연층 위의 접합층 및 상기 접합층 위의 단결정 반도체층을 포함하고, 상기 단결정 반도체층의 상부 표면에 있는 요철 형상의 높이에 있어서 최대 차이가 5 nm 이상 250 nm 이하인 것을 특징으로 한다.

전술한 구성에서, 상기 기판은 알루미노실리게이트 유리(alluminosilicate glass), 알루미노보로실리게이트 유리(alluminoborosilicate glass), 또는 바륨보로실리게이트 유리(bariumborosilicate glass) 중 하나를 포함하는 유리 기판이다. 기판의 크기는 CMP 공정의 적용이 어려울 정도, 예를 들면 각 면이 300 ㎜를 초과할 정도로 크지 않는 한 특별히 제한하지 않는다.

나아가, 전술한 구성에서, 상기 접합층은 유기실란 가스(organosilane gas)를 이용한 화학 기상 성장법에 의해 형성된 산화 실리콘막(silicon oxide film)을 포함할 수 있다. 나아가 상기 절연층은 산화질화 실리콘막(silicon oxynitride film) 또는 질화산화 실리콘막(silicon nitride oxide film)을 포함할 수 있다.

나아가, 전술한 구성에서, 상기 단결정 반도체층은 주표면(집적 회로가 형성되는 표면)으로 (100)면을 가질 수 있다. 또는 상기 단결정 반도체층은 주표면으로 (110)면을 가질 수 있다.

상기 단결정 반도체층의 상부 표면은 레이저 광을 조사하여 평탄한 요철 형상을 가지고 있다는 점을 주의해야 한다. 즉, 상부 표면의 볼록형상은 날카롭게 뾰족한 것이 아니라 일정한 반경의 굴곡으로 이루어져 평탄하다.

상기 단결정 반도체층의 두께를 조절하거나 표면 요철을 감소시키기 위하여 박막 또는 평탄화 처리를 실시한다는 점을 주의해야 한다. 전술한 처리에는 건식 에칭(dry etching), 습식 에칭(wet etching) 또는 건식 에칭과 습식 에칭을 조합한 에칭 중 하나를 사용할 수 있다. 에치-백 처리(etch-back treatment)를 실시할 수도 있다. 상기 처리는 레이저 광 조사 전이나 후에 적용할 수 있다.

나아가, 전술한 구성에서는, 전술한 요철 형상에서 각각의 오목부 또는 볼록부의 평균 폭이 바람직하게는 60 nm 이상 120 nm 이하이다. 상기 오목부 또는 볼록부각각의 폭이 평균 높이로 측정된다는 점도 주목할 만하다.

전술한 반도체 장치를 이용하여 다양한 전자 기기들을 제공할 수 있다.

본 발명의 반도체 장치에는 내열 온도가 낮은 기판이 사용되고 단결정 반도체층의 표면 요철 형상은 기계적 연마 없이도 일정한 정도 이하로 억제된다. 따라서 내열성이 낮은 기판을 베이스 기판으로 사용한 SOI 기판을 이용하여 고성능 반도체 장치를 제공할 수 있다. 나아가 상기 반도체 장치를 이용하여 다양한 전자 기기들을 제공할 수 있다.

도 1a 내지 도 1h는 SOI 기판을 제조하는 방법을 나타내는 단면도.

도 2a 내지 도 2c는 SOI 기판을 제조하는 방법을 나타내는 단면도이며 도 1h에 후속하는 공정을 설명한 단면도.

도 3a 내지 도 3g는 SOI 기판을 제조하는 방법을 나타내는 단면도.

도 4a 내지 도 4c는 SOI 기판을 제조하는 방법을 나타내는 단면도이며 도 3g에 후속하는 공정을 설명한 단면도.

도 5a 내지 도 5h는 SOI 기판을 제조하는 방법을 나타내는 단면도.

도 6a 내지 도 6c는 SOI 기판을 제조하는 방법을 나타내는 단면도이며 도 5h에 후속하는 공정을 설명한 단면도.

도 7a 내지 도 7d는 SOI 기판을 이용한 반도체 장치를 제조하는 방법을 나타내는 단면도.

도 8a 및 도 8b는 SOI 기판을 이용한 반도체 장치를 제조하는 방법을 나타내는 단면도이며 도 7d에 후속하는 공정을 설명한 단면도.

도 9는 SOI 기판을 이용하여 형성된 마이크로프로세서의 구성의 블록도.

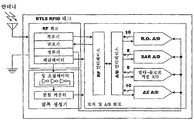

도 10은 SOI 기판을 이용하여 형성된 RFCPU 구성의 블록도.

도 11은 베이스 기판으로 마더 유리(mother glass)를 이용한 SOI 기판의 정면도.

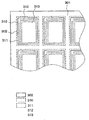

도 12a는 액정 표시 장치의 화소의 평면도이고, 도 12b는 도 12a에서 선 J-K를 따라 절단한 단면의 단면도.

도 13a는 전계발광(electroluminescence) 표시 장치의 화소의 평면도이고, 도 13b는 도 13a에서 선 J-K를 따라 절단한 단면의 단면도.

도 14a는 휴대 전화의 외관도이고, 도 14b는 디지털 플레이어의 외관도이고, 도 14c는 전자 서적의 외관도.

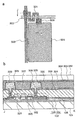

도 15는 SOI 기판을 이용하여 제조된 TFT의 단면 사진.

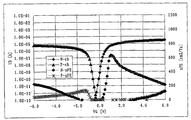

도 16은 TFT의 특성을 나타내는 그래프.

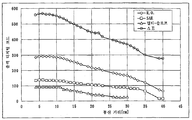

도 17은 정류 전압을 비교하여 나타내는 그래프.

도 18은 RTLS-RFID 태그의 사진.

도 19는 RTLS-RFID 태그의 블록도.

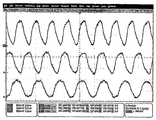

도 20은 RTLS-RFID 태그의 응답 신호 파형을 나타내는 도면.

도 21은 RTLS-RFID 태그의 통신 거리 대 출력 디지털 코드의 관계를 나타낸 그래프.

도 22는 SOI 기판의 결정 방위의 분석 결과를 나타내는 도면.

도 23은 SOI 기판과 벌크 실리콘의 라만 스펙트럼.

도 24는 SOI 기판을 이용하여 제조된 TFT의 단면사진.

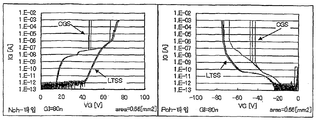

도 25a 및 도 25b는 TFT의 특성을 나타내는 그래프.

도 26은 TFT를 각각 포함하는 용량 TEG의 게이트 내압 특성을 나타내는 그래프.

도 27은 TFT를 포함하는 9 단계 링 오실레이터의 파형을 나타내는 그래프.

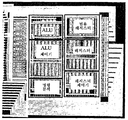

도 28은 CPU의 사진.

도 29a 및 도 29b는 각각 CPU의 쉬무 플롯(shmoo plot).

도 30a 및 도 30b는 SOI 기판의 AFM 사진.

도 2a 내지 도 2c는 SOI 기판을 제조하는 방법을 나타내는 단면도이며 도 1h에 후속하는 공정을 설명한 단면도.

도 3a 내지 도 3g는 SOI 기판을 제조하는 방법을 나타내는 단면도.

도 4a 내지 도 4c는 SOI 기판을 제조하는 방법을 나타내는 단면도이며 도 3g에 후속하는 공정을 설명한 단면도.

도 5a 내지 도 5h는 SOI 기판을 제조하는 방법을 나타내는 단면도.

도 6a 내지 도 6c는 SOI 기판을 제조하는 방법을 나타내는 단면도이며 도 5h에 후속하는 공정을 설명한 단면도.

도 7a 내지 도 7d는 SOI 기판을 이용한 반도체 장치를 제조하는 방법을 나타내는 단면도.

도 8a 및 도 8b는 SOI 기판을 이용한 반도체 장치를 제조하는 방법을 나타내는 단면도이며 도 7d에 후속하는 공정을 설명한 단면도.

도 9는 SOI 기판을 이용하여 형성된 마이크로프로세서의 구성의 블록도.

도 10은 SOI 기판을 이용하여 형성된 RFCPU 구성의 블록도.

도 11은 베이스 기판으로 마더 유리(mother glass)를 이용한 SOI 기판의 정면도.

도 12a는 액정 표시 장치의 화소의 평면도이고, 도 12b는 도 12a에서 선 J-K를 따라 절단한 단면의 단면도.

도 13a는 전계발광(electroluminescence) 표시 장치의 화소의 평면도이고, 도 13b는 도 13a에서 선 J-K를 따라 절단한 단면의 단면도.

도 14a는 휴대 전화의 외관도이고, 도 14b는 디지털 플레이어의 외관도이고, 도 14c는 전자 서적의 외관도.

도 15는 SOI 기판을 이용하여 제조된 TFT의 단면 사진.

도 16은 TFT의 특성을 나타내는 그래프.

도 17은 정류 전압을 비교하여 나타내는 그래프.

도 18은 RTLS-RFID 태그의 사진.

도 19는 RTLS-RFID 태그의 블록도.

도 20은 RTLS-RFID 태그의 응답 신호 파형을 나타내는 도면.

도 21은 RTLS-RFID 태그의 통신 거리 대 출력 디지털 코드의 관계를 나타낸 그래프.

도 22는 SOI 기판의 결정 방위의 분석 결과를 나타내는 도면.

도 23은 SOI 기판과 벌크 실리콘의 라만 스펙트럼.

도 24는 SOI 기판을 이용하여 제조된 TFT의 단면사진.

도 25a 및 도 25b는 TFT의 특성을 나타내는 그래프.

도 26은 TFT를 각각 포함하는 용량 TEG의 게이트 내압 특성을 나타내는 그래프.

도 27은 TFT를 포함하는 9 단계 링 오실레이터의 파형을 나타내는 그래프.

도 28은 CPU의 사진.

도 29a 및 도 29b는 각각 CPU의 쉬무 플롯(shmoo plot).

도 30a 및 도 30b는 SOI 기판의 AFM 사진.

본 발명에 따른 실시 형태 및 실시예는 이하 동반하는 도면을 사용하여 서술된다. 여기서 기재된 형태와 상세한 설명은 발명의 취지와 범위로부터 벗어나지 않고 다양한 양태로 변경할 수 있다는 점을 당업자라면 용이하게 이해할 수 있다. 그러므로 본 발명은 후술할 실시 형태 및 실시예의 기재 내용에 한정한다고 해석될 수 없다. 이하 설명할 본 발명의 구성에서 동일한 요소들은 도면 전체에 걸쳐 동일한 부호로 표시했다.

(실시 형태 1)

도 1a 내지 도 1h 및 도 2a 내지 도 2c는 본 발명의 반도체에 사용되는 SOI 기판을 제조하는 방법의 일예를 보여주는 단면도이다. SOI 기판를 제조하는 방법의 일예는 도 1a 내지 도 1h 및 도 2a 내지 도 2c를 이용하여 이하 기술하기로 한다.

우선, 베이스 기판(101)을 준비한다(도 1a 참조). 상기 베이스 기판(101)에는 액정 표시 장치와 같은 전자 공업용으로 사용되는 광 투과성을 갖는 유리 기판을 사용할 수 있다. 상기 유리 기판으로는 열 팽창 계수가 2.5×10-6/℃ 이상 5.0×10-6/℃ 이하(바람직하게는 3.0×10-6/℃ 이상 4.0×10-6/℃ 이하)이고 비등점이 580 ℃ 이상 680 ℃ 이하(바람직하게는 600℃ 이상 680℃ 이하)인 기판을 사용하는 것이 내열성, 비용 등의 면에서 바람직하다. 나아가, 상기 유리 기판은 무알칼리 유리 기판인 것이 바람직하다. 무알칼리 유리 기판의 소재로는, 예를 들어, 알루미노실리케이트 유리(alluminosilicate glass), 알루미노보로실리케이트 유리(alluminoborosilicate glass) 또는 바륨 보로실리케이트 유리(barium borosilicate glass)와 같은 유리 소재를 사용한다.

상기 유리 기판은 퓨젼법(fusion method) 또는 플로팅법(float method)을 이용하여 제조될 수 있다. 플로팅법에 의해 제조된 유리 기판에 관하여는 표면이 연마될 수 있으며 연마 후 연마재를 제거하는 화학적 용액 처리를 할 수 있다.

상기 베이스 기판(101)으로는 상기 유리 기판뿐 아니라 세라믹 기판, 쿼츠 기판 또는 사파이어 기판과 같은 절연체로 이루어진 절연성 기판; 금속 또는 스테인레스 스틸과 같은 전도체로 이루어진 전도성 기판; 실리콘 또는 갈륨비소(gallium arsenide)로 이루어진 반도체 기판 등을 이용할 수 있다는 점을 주목하기 바란다.

다음으로, 상기 베이스 기판(101)을 세정하고 10 nm 이상 400 nm 이하의 두께를 갖는 절연층(102)을 그 위에 형성한다(도 1b 참조). 상기 절연층(102)은 단층 구조 또는 2층 이상의 다층 구조를 적용할 수 있다.

상기 절연층(102)을 구성하는 막으로는, 산화 실리콘막(silicon oxide film), 질화 실리콘막(silicon nitride film), 산화질화 실리콘막(silicon oxynitride film), 질화산화 실리콘막(silicon nitride oxide film), 산화 게르마늄막(germanium oxide film), 질화 게르마늄막(germanium nitride film), 산화질화 게르마늄막(germanium oxynitride film), 또는 질화산화 게르마늄막(germanium nitirde oxide film)과 같은 실리콘 또는 게르마늄을 조성으로 함유하는 절연막을 사용할 수 있다. 나아가, 산화 알루미늄, 산화 탄탈륨, 산화 하프늄과 같은 금속 산화물을 함유하는 절연막; 질화 알루미늄과 같은 금속 질화물을 함유하는 절연막; 산화질화 알루미늄막과 같은 금속 산화질화물을 함유하는 절연막; 또는 질화산화 알루미늄막과 같은 금속 질화산화물을 함유하는 절연막 등을 사용할 수 있다.

본 명세서에서는, 산화질화물은 질소보다 산소를 더 많이 함유한 물질을 말하며, 질화산화물은 산소보다 질소를 더 많이 함유한 물질을 말한다는 점을 주의해야 한다. 예를 들어, 산화질화 실리콘은 질소보다 산소를 더 함유하고 있으며, 예를 들어, 산소가 50 at.% 이상 70 at.% 이하, 질소가 0.5 at.% 이상 15 at.% 이하, 실리콘이 25 at.% 이상 35 at.% 이하, 그리고 수소가 0.1 at.% 이상 10 at.% 이하의 농도 범위를 포함한다. 나아가, 질화산화 실리콘은 산소보다 질소를 더 함유하며, 예를 들어, 산소가 5 at.% 이상 30 at.% 이하, 질소가 20 at.% 이상 55 at.% 이하, 실리콘이 25 at.% 이상 35 at.% 이하, 그리고 수소가 10 at.% 이상 30 at.% 이하의 농도 범위를 포함한다. 전술한 범위는 러더포드 후방 산란 분광법(Rutherford backscattering spectrometry: RBS) 또는 수소 전방 산란법(hydregen forward scattering: HFS)을 이용하여 측정되는 범위이다. 나아가 구성 원소의 함유 비율의 합계는 100 at.%을 초과하지 않는다.

상기 베이스 기판(101)으로 반도체 장치의 신뢰성을 감소시키는 알카리 금속 또는 알카리 토 금속(alkaline earth metal)과 같은 불순물을 함유하는 기판을 사용하는 경우에는, 불순물이 상기 베이스 기판(101)으로부터 반도체층으로 확산되는 것을 방지할 수 있는 최소 1층 이상의 막을 설치하는 것이 바람직하다. 이러한 막의 예로는, 질화 실리콘막, 질화산화 실리콘막, 질화 알루미늄막, 질화산화 알루미늄막과 같은 것이 있다. 이러한 막을 포함하는 경우에는 상기 절연층(102)이 배리어층으로 기능할 수 있다.

예를 들어, 상기 절연층(102)을 단층 구조를 갖는 배리어층(barrier layer)으로 형성하는 경우에는, 두께가 10nm 이상 200nm 이하인 질화 실리콘막, 질화산화 실리콘막, 질화 알루미늄막, 또는 질화산화 알루미늄막을 형성할 수 있다.

상기 절연층(102)이 배리어층으로 기능하고 2층 구조를 갖는 경우에는 다음의 구조를 적용할 수 있다: 질화 실리콘막과 산화 실리콘막의 적층막; 질화 실리콘막과 산화질화 실리콘막의 적층막; 질화산화 실리콘막과 산화 실리콘막의 적층막; 질화산화 실리콘막과 산화질화 실리콘막의 적층막 등. 전술한 2층 구조 각각에서 앞에 기재된 막을 상기 베이스 기판(101)의 상면에 형성되는 막으로 하는 것이 바람직하다. 나아가 높은 블로킹 효과를 갖는 하층의 내부 응력이 반도체층에 영향을 미치지 않도록 하기 위하여 응력을 완화시킬 수 있는 소재로 형성된 막을 상층으로 선택하는 것이 바람직하다. 나아가, 상기 상층의 두께는 10 nm 이상 200 nm 이하일 수 있으며, 상기 하층의 두께는 10 nm 이상 200 nm 이하일 수 있다.

본 실시 형태에서, 상기 하층이 프로세스 가스로 SiH4와 NH3를 이용하는 플라즈마 CVD법으로 형성된 질화산화 실리콘막(103)이며 상기 상층이 프로세스 가스로 SiH4와 N2O를 이용하는 플라즈마 CVD법으로 형성된 산화질화 실리콘막(104)인 2층 구조를 상기 절연층(102)에 채용한다.

도 1a 및 도 1b에 도시된 공정을 따라 반도체 기판이 가공된다. 우선, 반도체 기판(111)을 준비한다(도 1c 참조). SOI 기판을 제조하기 위하여 상기 반도체 기판(111)을 박막화한 반도체층을 베이스 기판(101)에 붙인다. 단결정 반도체 기판을 반도체 기판(111)으로 사용하는 것이 바람직하지만, 다결정 반도체 기판을 사용하여도 무방하다. 또한, 예를 들어, 실리콘, 게르마늄, 실리콘-게르마늄, 또는 실리콘 카바이드 등과 같은 주기율표의 4족에 속한 원소로 이루어진 기판을 사용할 수 있다. 갈륨비소 또는 인듐인(indium phosphide)과 같은 화합물 반도체로 이루어진 반도체 기판을 사용할 수 있다.

다음으로, 상기 반도체 기판(111)을 세정한다. 그리고나서, 상기 반도체 기판(111)의 표면에 보호막(112)을 형성한다(도 1d 참조). 상기 보호막(112)에는 이온 조사시에 상기 반도체 기판(111)이 불순물에 의해 오염되는 것을 방지하는 효과, 조사된 이온의 거동에 의해 반도체 기판(111)이 훼손되는 것을 방지하는 효과 등이 있다. CVD법에 의해 산화 실리콘, 질화 실리콘, 질화산화 실리콘, 산화질화 실리콘 등을 증착하여 보호막(112)을 형성할 수 있다. 나아가 상기 반도체 기판(111)을 산화하거나 질화하여 보호막(112)을 형성할 수도 있다.

다음으로, 상기 보호막(112)을 통하여 전계에 의해 가속화되는 이온으로 이루어진 이온 빔(121)을 상기 반도체 기판(111)에 조사하여, 상기 반도체 기판(111)의 표면으로부터 소정의 깊이에 있는 영역에 취화층(113)을 형성한다(도 1e 참조). 상기 취화층(113)이 형성된 영역의 깊이는 상기 이온 빔(121)의 가속 에너지와 입사각에 의하여 조절될 수 있다. 이온의 평균 침입(侵入) 깊이나 동일한 정도의 깊이의 영역에 취화층(113)이 형성될 수 있다.

상기 취화층(113)이 형성된 깊이에 따라 상기 반도체 기판(111)으로부터 분리된 상기 반도체층의 두께가 결정된다. 상기 취화층(113)이 형성된 깊이는 50 nm 이상 500 nm 이하이고 상기 반도체 기판(111)으로부터 분리된 상기 반도체층의 바람직한 두께는 50 nm 이상 200 nm 이하이다.

상기 반도체 기판(111)을 이온으로 조사하기 위하여는 이온 주입 장치나 이온 도핑 장치가 사용될 수 있다. 이온 주입 장치에서는, 소스 가스를 여기(勵起)시켜서 이온 종(種)을 생성하고, 생성된 이온 종을 질량 분리하여 소정의 질량을 각각 갖는 이온을 피처리물에 주입한다. 이온 도핑 장치에서는, 프로세스 가스를 여기(勵起)시켜서 이온 종을 생성하고, 생성된 이온 종을 질량 분리하지 않고 피처리물에 주입한다. 질량 분리 장치를 구비한 이온 도핑 장치에서는 이온 주입 장치에서와 마찬가지로 질량 분리를 동반한 이온 조사를 행할 수 있다.

예를 들어, 이온 도핑 장치를 사용하는 이온 조사 단계 공정은 다음의 조건에서 행해질 수 있다:

ㆍ 가속 전압은 10 kV 이상 100 kV 이하(바람직하게는 20 kV 이상 80 kV 이하)

ㆍ 도스량(dose)은 1×1016 ions/㎠ 이상 4×1016 ions/㎠ 이하

ㆍ 빔 전류 농도는 2 ㎂/㎠ 이상(바람직하게는 5 ㎂/㎠ 이상, 그리고 더욱 바람직하게는 10 ㎂/㎠ 이상)

이온 조사 공정에서 소스 가스로는 수소를 이용할 수 있다. 수소 가스(H2 가스)를 이용함으로써, H+, H2 +, H3 + 이온을 이온 종으로 생성할 수 있다. 수소 가스를 소스 가스로 사용하는 경우에는 대량의 H3 + 이온으로 조사를 행하는 것이 바람직하다. 대량의 H3 + 이온으로 조사함으로써, H+ 이온 및/또는 H2 + 이온을 조사하는 경우에 비하여 이온 조사 효율이 향상된다. 즉, 조사 시간이 단축될 수 있다. 나아가, 취화층(113)으로부터의 박리가 더욱 용이해질 수 있다. 나아가, H3 + 이온을 이용함으로써 이온의 평균 침입 깊이가 얕아질 있으므로, 취화층(113)이 반도체 기판(111)의 표면으로부터 좀 더 얕은 깊이에 있는 영역에 형성될 수 있다.

이온 주입 장치를 사용하는 경우에는, 질량 분리를 통하여 H3 + 이온을 주입하는 것이 바람직하다. 물론, H2 + 이온을 주입할 수도 있다.

상기 이온 도핑 장치를 사용하는 경우에는, H3 + 이온을 이온 빔(121)의 H+, H2 + 및 H3 + 이온의 총량의 적어도 70 % 이상을 함유하는 것이 바람직하다. H3 + 이온의 비율이 80 % 이상일 것이 더욱 바람직하다. 이러한 방법에서 H3 + 이온의 비율을 높임으로써 상기 취화층(113)은 1×1020 atoms/㎤ 이상의 농도인 수소를 함유할 수 있다. 상기 취화층(113)이 적어도 5×1020 atoms/㎤ 이상의 수소를 함유하는 경우에 반도체층의 박리가 용이할 수 있다는 점을 주의하여야 한다.

상기 이온 조사 공정에서 상기 소스 가스로, 수소 가스 대신, 헬륨 가스 또는 아르곤 가스 같은 희소 가스, 불소 가스 또는 염소 가스로 대표되는 할로겐 가스, 및 불소 화합물 가스(예를 들어 BF3)와 같은 할로겐 화합물 가스로부터 선택된 다양한 가스를 사용할 수 있다. 헬륨을 상기 소스 가스로 사용하는 경우에는, 질량 분리를 행하지 않고 He+ 이온의 비율이 높은 상기 이온 빔(121)을 형성할 수 있다. 상기 이온 빔(121)으로 이러한 이온 빔을 이용함으로써, 상기 취화층(113)을 효율적으로 형성할 수 있다.

나아가, 이온 조사 공정을 복수회 행하여 상기 취화층(113)을 형성할 수도 있다. 이 경우에는, 다른 소스 가스 또는 동일한 소스 가스를 상기 이온 조사 공정에 사용할 수 있다. 예를 들어, 상기 소스 가스로 희소 가스를 사용하여 행할 수도 있고, 그리고나서 소스 가스로 수소 가스를 사용하여 이온 조사를 행할 수도 있다. 예를 들어, 할로겐 가스 또는 할로겐 화합물 가스를 사용하여 이온 조사를 행할 수 있고, 수소 가스를 사용하여 이온 조사를 행할 수도 있다.

상기 취화층(113)을 형성한 후에는, 에칭하여 상기 보호막(112)을 제거한다. 그리고나서, 상기 반도체 기판(111)의 상면에 접합층(114)을 형성한다(도 1f 참조). 상기 접합층(114)을 제거하지 않고 상기 보호막(112) 상에 상기 접합층(114)을 형성할 수도 있다.

상기 접합층(114)은 매끄러운 친수성 표면을 갖는 층이다. 상기 접합층(114)으로는 화학 반응에 의해 형성된 절연막, 특히 산화 실리콘막을 사용하는 것이 바람직하다. 상기 접합층(114)의 두께는 10 nm 이상 200 nm 이하일 수 있다. 바람직한 두께는 10 nm 이상 100 nm 이하이고 더욱 바람직한 두께는 20 nm 이상 50 nm 이하이다. 상기 반도체 기판(111)의 가열 온도는 상기 접합층(114)을 형성하는 공정에서 상기 취화층(113)에 도입된 원자 또는 분자가 이탈하지 않도록 하는 온도일 필요가 있다는 점을 주의하여야 한다. 구체적으로는, 상기 가열 온도는 350 ℃ 이하인 것이 바람직하다.

상기 접합층(114)의 산화 실리콘막을 플라즈마 CVD법에 의해 형성한 경우에는 유기실란 가스를 실리콘 소스 가스로 사용하는 것이 바람직하다. 산소(O2) 가스를 수소 소스 가스로 사용할 수 있다. 상기 유기실란 가스로는 다음 중 하나를 사용할 수 있다: 규산에틸(TESO)(화학식: Si(OC2H5)4); 테트라메틸실란(TMS)(화학식: Si(CH3)4); 테트라메틸사이클로테트라실록산(TMCTS); 옥타메틸사이클로테트라실록산(OMCTS); 헥사메틸디실라잔(HMDS); 트리에톡시실란(화학식: SiH(OC2H5)3); 트리디메틸아미노실란(화학식: SiH(N(CH3)2)3) 등. 나아가, 상기 실리콘 소스 가스로는, 상기 유기실란 가스 대신에, 실란(SiH4), 디실란(Si2H6) 등을 사용할 수 있다.

플라즈마 CVD법 대신에 열 CVD법을 이용하여 상기 산화 실리콘막을 형성할 수도 있다. 이러한 경우에는, 상기 실리콘 소스 가스로 실란(SiH4), 디실란(Si2H6) 등을 사용할 수 있으며, 상기 산소 소스 가스로는 산소(O2) 가스, 일산화이질소(N2O) 가스 등을 사용할 수 있다. 가열 온도는 200 ℃ 이상 500 ℃ 이하가 바람직하다. 상기 접합층(114)은 절연성 재료를 사용하여 형성하는 경우가 많으며, 이러한 의미로 절연층의 범주에 상기 접합층(114)을 포함시킬 수 있다.

다음으로, 상기 베이스 기판(101) 및 상기 반도체 기판(111)을 서로 접합시킨다(도 1g 참조). 이러한 접합 공정을 이하와 같이 행한다: 우선, 상기 절연층(102)이 형성된 상기 베이스 기판(102)과 상기 접합층(114)이 형성된 상기 반도체 기판(111)을 초음파 세정 등의 방법으로 세정한다; 그리고 다음으로 상기 절연층(102)과 상기 접합층(114)을 서로 밀착하여 상기 절연층(102)과 상기 접합층(114)을 서로 접합시킨다. 결합 메카니즘으로는 반 데르 발스력이 연관된 메카니즘, 수소 결합력과 연관된 메카니즘 등을 고려할 수 있다.

전술한 바와 같이 상기 접합층(114)으로는 유기실란을 이용한 플라즈마 CVD법에 의해 형성된 산화 실리콘막, 열 CVD법에 의해 형성된 산화 실리콘막 등을 사용할 수 있으며, 상기 절연층(102)과 상기 접합층(114)은 실온에서 접합할 수 있다. 그러므로, 유리 기판과 같은 내열성이 낮은 기판을 상기 베이스 기판(101)으로 사용할 수 있다.

상기 절연층(102)의 형성은 생략될 수 있는 점을 주목하여야 한다; 그러나, 이러한 경우는 본 실시 형태에서 기재되어 있지 않다. 이러한 경우에는, 상기 접합층(114)을 상기 베이스 기판(101)에 접합하게 된다. 상기 베이스 기판(101)이 유리 기판인 경우에는, 유리실란을 사용하는 CVD법에 의해 형성된 산화 실리콘막, 열 CVD법에 의해 형성된 산화 실리콘막, 소스 재료로 실록산을 사용하여 형성된 산화 실리콘막 등의 상기 접합층(114)을 형성함으로써 상기 유리 기판과 상기 접합층(114)을 실온에서 접합할 수 있다.

상기 결합력을 더욱 증가시키키 위하여, 상기 절연층(102)의 표면에 N2, O2, Ar 및 NH3로부터 선택된 가스 또는 혼합 가스를 사용한 플라즈마 처리, 산소 플라즈마 처리 또는 오존 처리 등을 행하여 표면을 친수성으로 만드는 방법이 있다. 이러한 처리에 의해, 상기 절연층(102)의 표면에 수산기(hydroxyl)을 부가하여, 상기 절연층(102)과 상기 접합층(114) 사이의 결합 계면에 수소 결합을 형성할 수 있다. 상기 절연층(102)을 형성하지 않는 경우에는, 상기 베이스 기판(101)의 표면을 친수성으로 만드는 처리를 행할 수 있다.

상기 베이스 기판(101)과 상기 반도체 기판(111)을 서로 밀착시킨 후, 가열 처리 또는 가압 처리를 행하는 것이 바람직하다. 이는 가열 처리 또는 가압 처리를 행함으로써 상기 절연층(102)과 상기 접합층(114) 간의 결합력을 개선시킬 수 있기 때문이다. 상기 가열 처리의 온도는 상기 베이스 기판(101)의 내열 온도 이하가 바람직하며, 상기 가열 온도는 400 ℃ 이상 700 ℃ 이하일 수 있다. 예를 들어, 유리 기판을 상기 베이스 기판(101)으로 사용하는 경우, 상기 비등점을 내열 온도로 고려해도 좋다. 상기 가압 처리는 상기 결합 계면에 수직 방향으로 힘을 가하기 위하여 행하는 것이며, 상기 베이스 기판(101)과 상기 반도체 기판(111)의 강도를 고려하여 가해지는 압력을 결정한다.

다음으로, 상기 반도체 기판(111)을 반도체 기판(111')과 반도체층(115)으로 분리한다(도 1h 참조). 상기 베이스 기판(101)과 상기 반도체 기판(111)을 서로 접합시킨 후 상기 반도체 기판(111)을 가열하여 상기 반도체 기판(111)의 분리를 행한다. 상기 반도체 기판(111)의 상기 가열 온도는 상기 베이스 기판의 내열 온도에 의존하는데, 예를 들어, 400 ℃ 이상 700 ℃ 이하이다.

전술한 바와 같이 400 ℃ 이상 700 ℃ 이하의 온도에서 가열 처리를 행함으로써, 상기 취화층(113)에 형성된 미소한 공공(空孔)의 체적 변화가 일어나 상기 취화층(113)에 틈을 생성하게 된다. 그 결과, 상기 반도체 기판(111)은 상기 취화층(113)과 분리된다. 상기 접합층(114)을 상기 베이스 기판(101)에 결합시키기 때문에, 상기 반도체 기판(111)으로부터 분리된 상기 반도체층(115)은 상기 베이스 기판(101)에 잔존한다. 나아가, 이러한 가열 처리에 의해 상기 베이스 기판(101)과 상기 접합층(114) 사이의 결합 계면을 가열하기 때문에, 상기 결합 계면에 공유 결합을 형성하여 상기 결합 계면에서의 결합력이 개선된다.

전술한 공정을 통하여, 상기 반도체층(115)을 상기 베이스 기판(101)에 설치시킨 SOI 기판(131)이 제조된다. 상기 SOI 기판(131)은 상기 베이스 기판(101) 위에 상기 절연층(102), 상기 접합층(114) 및 상기 반도체층(115)이 순서대로 적층되고, 상기 절연층(102) 및 상기 접합층(114) 간의 상기 계면에 접합이 형성된 다층 구조를 갖는 기판이다. 상기 절연층(102)을 형성하지 않는 경우에는 상기 베이스 기판(101)과 상기 접합층(114) 사이의 계면에 접합이 형성된다는 점을 주의해야 한다.

나아가, 상기 반도체 기판(111)을 분리하여 상기 SOI 기판(131)을 형성한 후 400 ℃ 이상 700 ℃ 이하의 온도로 가열 처리도 행할 수 있다. 이러한 가열 처리에 의하여, 상기 SOI 기판(131)의 상기 접합층(114)과 상기 절연층(102)의 결합력을 더욱 개선시킬 수 있다. 당연히 상기 베이스 기판(101)의 내열 온도를 초과하지 않도록 상기 가열 온도의 상한을 설정한다.

상기 반도체층(115)의 표면에는 상기 분리 공정 또는 상기 이온 조사 공정에 의한 결함이 존재하고, 상기 표면의 평탄성이 훼손된다. 요철이 있는 상기 반도체층(115)의 표면상에 높은 내압을 갖는 박막 게이트 절연층을 형성하는 것은 어렵다. 그러므로 평탄화 작업이 상기 반도체층(115)에 행해진다. 나아가, 상기 반도체층(115)의 결함은, 예를 들어, 상기 반도체층(115)과 게이트 절연층 간 계면의 국소화된 상태 밀도(localized state density)의 증가와 같은, 트랜지스터의 성능과 신뢰성에 악영향을 미치므로, 상기 반도체층(115)의 상기 결함을 감소시키기 위한 처리를 행한다.

상기 반도체층(115)의 평탄화 및 결함의 감소는 레이저 빔(122)으로 상기 반도체층(115)을 조사함으로써 실현된다(도 2a 참조). 상기 레이저 빔(122)을 상기 반도체층(115)의 상기 상면측으로부터 조사함으로써 상기 반도체층(115)의 상면을 용융(熔融)한다. 상기 반도체층(115)을 상기 용융 후 냉각하고 고체화하고 이로 인하여 상편의 평탄성이 개선된 반도체층(115A)을 얻을 수 있다(도 2b 참조). 상기 평탄화 처리에서 상기 레이저 빔(122)을 사용하기 때문에, 상기 베이스 기판(101)을 가열할 필요가 없어서 상기 베이스 기판(101)의 온도 상승을 억제할 수 있다. 그러므로, 유리 기판과 같은 저내열성 기판을 상기 베이스 기판(101)으로 사용할 수 있다.

상기 반도체층(115)을 상기 레이저 빔(122)의 조사로 부분적으로 용융하는 것이 바람직하다는 것을 주목해야 한다. 이는 상기 반도체층(115)을 완전하게 용융하는 경우에는, 액체상에서 상기 반도체층(115)의 무질서한 핵발생(disorderd nucleation)때문에 상기 반도체층(115)이 재결정화되어 상기 반도체층(115A)의 결정성이 낮아진다. 부분 용융에 의하여, 용융되지 않은 상기 반도체층(115)의 고체 부분으로터 결정 성장이 진행된다. 따라서, 상기 반도체층(115)의 결함을 감소시키고 결정성을 회복한다. 완전 용융은 상기 반도체층(115)이 상기 반도체층(115)와 상기 접합층(114) 사이의 계면으로 용융되어 액체 상태로 되는 것을 말한다. 한편, 부분 용융은 상기 상층이 용융되어 액체 상태로 되는 반면 하층은 용융없이 고체 상태를 유지하는 것을 말한다.

상기 레이저 광 조사에는, 연속 발진 레이저(CW 레이저) 또는 펄스 발진 레이저(10 내지 100 Hz의 정도의 반복 레이트에 있는 것이 바람직하다)를 사용할 수 있다. 구체적으로는, 연속 발진 레이저로서 다음을 사용할 수 있다: Ar 레이저, Kr 레이저, CO2 레이저, YAG 레이저, YVO4 레이저, YLF 레이저, YAlO3 레이저, GdVO4 레이저, Y2O3 레이저, 루비 레이저, 알렉산드라이트 레이저, Ti:사파이어 레이저, 헬륨-카드뮴 레이저 등. 펄스 발진 레이저로는 다음을 사용할 수 있다: Ar 레이저, Kr 레이저, 엑시머(ArF, KrF, XeCl 등) 레이저, CO2 레이저, YAG 레이저, YVO4 레이저, YLF 레이저, YAlO3 레이저, GdVO4 레이저, Y2O3 레이저, 루비 레이저, 알렉산드라이트 레이저, Ti:사파이어 레이저, 구리 증기 레이저, 금 증기 레이저 등. 이러한 펄스 발진 레이저는 상기 반복 레이트가 증가하는 경우에는 연속 발진 레이저와 같은 방법으로 처리될 수 있다. 펄스 발진 레이저 빔은 부분 용융을 위해 사용하는 것이 바람직하나, 본 발명은 이에 한정하지 않는다.

상기 레이저 빔(122)은 상기 반도체층(115)에 의해 흡수될 수 있는 파장으로 설정할 필요가 있다. 상기 파장은 상기 레이저 광의 표피 깊이를 고려하여 결정하는 것이 좋다. 예를 들어, 250 nm 내지 700 nm 정도로 상기 파장을 설정할 수 있다. 나아가, 상기 레이저 빔(122)의 조사 에너지 밀도는 상기 레이저 빔(122)의 상기 파장, 상기 레이저 광의 표피 깊이, 상기 반도체층(115)의 두께 등을 고려하여 결정할 수 있다. 예를 들어, 상기 레이저 빔(122)의 조사 에너지 밀도는 300 내지 800 mJ/㎠ 정도로 설정하는 것이 좋다.

상기 반도체층(115)의 두께가 상기 이온 조사 공정에서 도입되는 이온의 깊이를 제어함으로써 50 nm 이상으로 증가되는 경우에, 상기 레이저 빔(122)의 상기 조사 에너지 밀도의 제어가 용이해진다. 따라서, 상기 레이저 빔(122)으로 조사함으로써 상기 반도체층(115)의 표면 평탄화와 결정성의 개선이 효율적으로 이루어질 수 있다. 상기 레이저 빔(122)의 상기 조사 에너지 밀도는 상기 반도체층(115)의 두께가 증가됨에 따라 높아질 필요가 있기 때문에, 상기 반도체층(115)의 두께는 200 nm 이하가 바람직하다.

상기 레이저 빔(122)의 조사는 대기 분위기로서 산소를 함유하는 분위기나 질소 분위기와 같은 불활성 분위기에서 행해질 수 있다. 불활성 분위기에서 상기 레이저 빔(122)으로 조사를 행하기 위하여, 밀폐된 챔버 내에서 상기 레이저 빔(122)을 조사하되, 상기 챔버 내의 분위기는 제어되는 것이 좋다. 상기 챔버를 사용하지 않는 경우에는, 상기 레이저 빔(122)이 조시되는 표면에 질소 가스와 같은 불활성 가스를 불어넣어 질소 분위기를 형성할 수 있다.

질소와 같은 불활성 분위기는 대기 분위기보다 상기 반도체층(115)의 평탄성을 개선하는 효과를 더 높일 수 있다. 게다가, 상기 불활성 분위기는 상기 대기 분위기보다 크랙(crack)이나 릿지(ridge)의 생성을 억제하는 데 더 높은 효과를 갖는다. 상술한 불활성 분위기에서는, 산소의 농도가 0.1 % 이하이고, 바람직하게는 0.01 % 이하이고, 더욱 바람직하게는 0.001 % 이하라는 것을 주의하여야 한다.

상기 레이저 빔(122)을 조사하여 도 2b에 도시된 상기 반도체층(115A)을 포함하는 SOI 기판(131A)을 형성한 후, 상기 반도체층(115A)의 두께를 감소시키기 위하여 박막 공정을 행한다(도 2c 참조).

상기 반도체층(115A)을 박막화하기 위하여, 건식 에칭, 습식 에칭 또는 상기 양 에칭의 조합 중 하나를 행할 수 있다. 예를 들어, 상기 반도체 기판(111)이 실리콘 기판인 경우에, 프로세스 가스로 SF6 및 O2를 사용하여 건식 에칭을 하여 반도체층(115A)을 박막화할 수 있다. 나아가, Cl2를 프로세스 가스로 사용하여도 좋다.

상기 에칭 처리에 의하여, 박막 반도체층(115B)을 포함하는 SOI 기판(131B)을 제조할 수 있다(도 2c 참조). 상기 레이저 빔(122)을 조사하여 상기 반도체층(115A)의 표면을 미리 평탄화하기 때문에, 이러한 박막 공정은 에치-백 처리에 의하지 않고, 에칭 처리에 의해 행할 수 있다. 당연히 에치-백 처리를 적용할 수도 있다. 이러한 박막 공정에서, 상기 반도체층(115B)의 두께는 바람직하게는 100 nm 이하 5 nm 이상으로, 더욱 바람직하게는 50 nm 이하 5 nm 이상으로 감소시킨다.

본 실시 형태에서는 레이저 광 조사에 의하여 표면을 평탄화한 후 상기 에칭 처리 또는 에치-백 처리를 행하고 있지만, 본 발명은 이에 한정되지 않는다. 예를 들어, 에칭 처리 또는 에치-백 처리를 레이저 광 조사 전에 행할 수도 있다. 이러한 경우에는, 상기 반도체층의 표면에의 요철이나 결함을 상기 에칭 처리 또는 에치-백 처리에 의하여 감소시킬 수 있다. 또는 에칭 또는 에치-백 처리를 상기 레이저 광 조사 전 및 후에 행할 수도 있다. 나아가, 상기 레이저 광 조사와 에칭 처리 또는 에치-백 처리를 상호 교대로 반복할 수도 있다. 레이저 광 조사 또는 에칭 처리(또는 에치-백 처리) 중 하나를 이용한 경우와 비교하여, 전술한 바와 같은 레이저 광 조사 및 에칭 처리(또는 에치-백 처리)의 조합을 이용함으로써 상기 반도체층의 표면의 요철, 결함 등을 현저하게 감소시킬 수 있다.

상술한 공정을 통하여, SOI 기판을 제조할 수 있다. SOI 기판의 영역을 증가시키기 위하여, 복수의 상기 반도체층(115B)을 한 장의 상기베이스 기판(101)에 붙인다. 예를 들어, 도 1c 내지 도 1f를 이용하여 기재된 공정을 여러 번 반복하고 복수의 상기 반도체 기판(111)을 상기 한 장의 베이스 기판(101)에 고정시킨다. 그리고 나서, 도 1h의 가열 공정을 행하여 상기 반도체 기판(111)을 분리하고 이로써 복수의 반도체층(115)을 상기 베이스 기판(101)에 고정시킨 상기 SOI 기판(131)을 제조한다. 그 후에, 상기 도 2a 내지 도 2c를 통하여 복수의 반도체층(115B)을 상기 베이스 기판(101)에 붙인 상기 SOI 기판(131B)을 제조할 수 있다.

본 실시 형태에서 설명된 바와 같이, 레이저 광 조사에 의한 상기 반도체층의 상기 평탄화 공정 및 에칭 처리(또는 에치-백 처리)를 조합함으로써, 두께가 100 nm 이하이고, 평탄성이 높고, 훼손이 적은 상기 반도체층(115B)을 형성할 수 있다. 즉, 상기 베이스 기판(101)으로 유리 기판을 사용하고 상기 취화층(113)의 형성을 위하여 이온 도핑 장치를 사용하더라도 상술한 특성을 갖는 상기 반도체층(115B)이 접합된 상기 SOI 기판(131B)을 형성할 수 있다.

상기 SOI 기판(131B)을 이용한 트랜지스터를 제조함으로써, 게이트 절연층의 박막 및 상기 SOI 기판과 상기 게이트 절연층 사이의 국소화된 계면 상태 밀도의 감소가 실현될 수 있다. 게다가, 상기 반도체층(115B)을 박막화함으로써, 유리 기판 위의 단결정 반도체층을 이용하여 완전 공핍형의 트랜지스터를 제조할 수 있다. 따라서, 높은 성능, 예를 들어 빠른 속도로 동작할 수 있는 높은 신뢰성, 높은 전계 효과 이동도, 및 낮은 전압 소비를 갖는 트랜지스터를 베이스 기판 위에 제조할 수 있다.

대면적에 적합하지 않은 CMP 처리가 필요하지 않으므로, 고성능 반도체 장치의 대면적화를 실현할 수 있다. 본 실시 형태에 따르면, 대면적 기판을 사용하는 경우뿐 아니라 소형 기판을 사용하는 경우에도 물론 양호한 반도체 장치를 제공할 수 있다. 본 실시 형태에서의 공정을 통하여 얻을 수 있는 반도체층의 표면 특성은 이하 기술할 것이며, 여기서 Ra는 산술 평균 거칠기를 의미하며, RMS는 제곱평균평방근 거칠기, 그리고 P-V는 최대 높이차를 의미한다. P-V 값은 어떤 경우에는 미세한 결함에 의하여 크게 영향을 받을 수 있다; 그러므로 Ra 또는 RMS를 평가 파라미터로 사용하는 것이 더욱 바람직하다.

ㆍ Ra: 7 nm 이하

ㆍ RMS: 10 nm 이하

ㆍ P-V: 250 nm 이하

CMP를 사용하는 경우에는 상술한 파라미터가 다음과 같다:

ㆍ Ra: 1 nm 미만

ㆍ RMS: 1 nm 미만

ㆍ P-V: 5 nm 미만

이상으로부터, CMP를 이용하지 않고 형성된 본 발명의 상기 반도체 기판의 표면의 파라미터들이 다음의 범위 내에 있다는 것을 염두에 두어야 한다.

ㆍ Ra: 1 nm 이상 7 nm 이하(바람직하게는 1 nm 이상 3 nm 이하)

ㆍ RMS: 1 nm 이상 10 nm 이하(바람직하게는 1 nm 이상 4 nm 이하)

ㆍ P-V: 5 nm 이상 250 nm 이하(바람직하게는 5 nm 이상 50 nm 이하)

본 실시 형태에서 사용되는 상기 반도체 기판의 주표면은 (100) 면, (110) 면 또는 (111) 면인 것이 양호하다. (100) 면을 사용하는 경우에는 계면 상태 밀도를 감소시킬 수 있고, 전계 효과형 트랜지스터의 제조에 적합하다. (110) 면을 사용하는 경우에는 접합층에 포함된 원소와 반도체 포함된 원소(예를 들면, 실리콘 원소) 사이에 밀접한 접합을 형성하며, 절연층과 반도체층 간의 밀착성을 개선시킨다. 즉, 상기 반도체층의 분리를 억제할 수 있다. 게다가, 원자가 (110) 면에 조밀하게 배열되므로 다른 면을 사용하는 경우와 비교하여 SOI 기판의 단결정 실리콘층의 평탄성이 개선된다. 즉, 이러한 반도체층을 사용하여 제조된 트랜지스터는 탁월한 특성을 갖는다. (110) 면도 또한 영률(young's modulus)이 (100) 면의 영률보다 크고, 분리도 쉬운 이점을 갖는다는 것을 염두에 두도록 한다.

(실시 형태 2)

도 3a 내지 도 3g 및 도 4a 내지 도 4c는 본 발명의 반도체 기판용 SOI 기판을 제조하는 방법의 다른 실시예를 도시하는 단면도이다. SOI 기판을 제조하는 방법의 다른 실시예를 도 3a 내지 도 3g 및 도 4a 내지 도 4c를 이용하여 이하 기재한다.

도 1a를 이용하여 실시 형태 1에서 설명한 바와 같이, SOI 기판의 베이스 기판으로 기능하는 상기 베이스 기판(101)을 준비한다(도 3a 참조). 도 3a는 상기 베이스 기판(101)의 단면도이다. 나아가, 도 1c를 이용하여 설명한 바와 같이 상기 반도체 기판(111)을 준비한다(도 3b 참조). 도 3b는 상기 반도체 기판(111)의 단면도이다.

다음으로, 상기 반도체 기판(111)을 세정한다. 그리고나서, 절연층을 상기 반도체 기판(111)의 표면에 형성한다(도 3c 참조). 상기 절연층(116)은 단층 구조이거나 2 층 이상의 다층 구조일 수 있다. 상기 절연층(116)의 두께는 10 nm 이상 400 nm 이하일 수 있다.

상기 절연층(116)에 포함된 막으로는, 산화 실리콘막, 질화 실리콘막, 산화질화 실리콘막, 질화산화 실리콘막, 산화 게르마늄막, 질화 게르마늄막, 산화질화 게르마늄막, 또는 질화산화 게르마늄과 같은 실리콘 또는 게르마늄을 조성으로 함유하는 절연막을 사용할 수 있다. 나아가, 산화 알루미늄, 산화 탄탈륨, 산화 하프늄과 같은 금속 산화물을 함유하는 절연막; 질화 알루미늄과 같은 금속 질화물을 함유하는 절연막; 산화질화 알루미늄막과 같은 금속 산화질화물을 함유하는 절연막; 또는 질화산화 알루미늄막과 같은 금속 질화산화물을 함유하는 절연막 등을 사용할 수 있다.

상기 절연층(116)에 포함된 절연막을 형성하는 방법으로는, CVD 법, 스퍼터링 법(sputtering method), 상기 반도체 기판(111)을 산화(또는 질화)하는 방법 등이 있다.

베이스 기판(101)으로 반도체 장치의 신뢰성을 감소시키는 알카리 금속 또는 알카리 토 금속(alkaline earth metal)과 같은 불순물을 함유하는 기판을 사용하는 경우에는, 불순물이 베이스 기판(101)으로부터 SOI 기판의 반도체층으로 확산되는 것을 방지할 수 있는 최소 1층 이상의 막을 설치하는 것이 바람직하다. 이러한 막의 예로는, 질화 실리콘막, 질화산화 실리콘막, 질화 알루미늄막, 질화산화 알루미늄막 등과 같은 것이 있다. 이러한 막을 포함하는 경우에는 상기 절연층(102)이 배리어층으로 기능할 수 있다.

예를 들어, 상기 절연층(116)을 단층 구조를 갖는 배리어층으로 형성하는 경우에는, 두께가 10 nm 이상 200 nm 이하인 질화 실리콘막, 질화산화 실리콘막, 질화 알루미늄막, 또는 질화산화 알루미늄막을 형성할 수 있다.

상기 절연층(116)이 배리어층으로 기능하고 2층 구조를 갖는 경우에는 다음의 구조를 적용할 수 있다: 질화 실리콘막과 산화 실리콘막의 적층막; 질화 실리콘막과 산화질화 실리콘막의 적층막; 질화산화 실리콘막과 산화 실리콘막의 적층막; 질화산화 실리콘막과 산화질화 실리콘막의 적층막 등. 전술한 상기 2층 구조 각각에서 앞에 기재된 막을 상기 반도체 기판(111) 측(하층) 상에 형성하는 것이 바람직하다. 나아가 높은 블로킹 효과를 갖는 상층의 내부 응력이 상기 반도체층에 영향을 미치지 않도록 하기 위하여 응력을 완화시킬 수 있는 소재로 이루어진 막을 하층으로 선택하는 것이 바람직하다. 나아가, 상기 상층의 두께는 10 nm 이상 200 nm 이하일 수 있으며, 상기 하층의 두께는 10 nm 이상 200 nm 이하일 수 있다.

본 실시 형태에서, 상기 절연층(116)은 상기 하층이 프로세스 가스로 SiH4와 N2O를 사용하는 플라즈마 CVD법으로 형성된 산화질화 실리콘막(117)이며 상기 상층이 프로세스 가스로 SiH4와 NH3를 사용하는 플라즈마 CVD법으로 형성된 질화산화 실리콘막(118)인 2층 구조를 적용한다.

다음으로, 전계에 의해 가속화되는 이온을 포함하는 이온 빔(121)을 상기 절연층(116)을 통하여 상기 반도체 기판(111)에 조사하여, 상기 반도체 기판(111)의 표면으로부터 소정의 깊이의 영역에 취화층(113)을 형성한다(도 3d 참조). 이 공정은 도 1e를 이용하여 설명한 상기 취화층(113)의 형성과 같은 방법으로 행할 수 있다. 상기 절연층(116)은 이온 조사시에 상기 반도체 기판(111)이 불순물에 의하여 오염되는 것을 방지하는 효과, 상기 반도체 기판(111)이 조사된 이온의 거동에 의하여 훼손되는 것을 방지하는 효과 등이 있다.

상기 취화층(113)을 형성한 후 상기 절연층(116) 상에 상기 접합층(114)을 형성한다(도 3e 참조).

상기 접합층(114)은 본 실시 형태에서 이온 조사 공정 후에 형성되지만, 상기 이온 조사 공정 전에 상기 접합층(114)을 형성할 수도 있다. 이러한 경우, 도 3c의 상기 절연층의 형성 후에, 상기 접합층(114)을 상기 절연층(116) 상에 형성하고, 도 3d의 공정에서의 상기 이온 빔(121)을 상기 접합층(114)과 상기 절연층(116)을 통하여 상기 반도체 기판(111)에 조사한다.

나아가, 실시 형태 1에서 설명한 바와 같이, 상기 이온 조사는 상기 보호막(112)의 형성 후에 행할 수도 있다. 이러한 경우, 도 1c 내지 도 1e의 공정 후에 상기 보호막(112)을 제거하고, 상기 절연층(116)과 상기 접합층(114)을 상기 반도체 기판(111) 위에 형성하는 것이 좋다.

다음으로, 상기 베이스 기판(101)과 상기 반도체 기판(111)을 서로 붙인다(도 3f 참조). 상기 붙임 공정은 다음과 같이 행해진다: 우선, 접합 계면을 형성하는 상기 베이스 기판(101)과 상기 접합층(114)의 각 표면을 초음파 세정과 같은 방법으로 세정한다; 그리고 다음으로 상기 베이스 기판(101)과 상기 접합층(114)을 도 1g를 이용하여 설명한 접합 공정과 유사한 공정으로 각각 밀착되게 해서, 상기 베이스 기판(101)과 상기 접합층(114)을 서로 접합시킨다.

상기 베이스 기판(101)과 상기 접합층(114)을 접합하기 전에, 상기 베이스 기판(101)의 표면을 산소 플라즈사 처리 또는 오존 처리를 실행하여 친수성으로 만드는 것이 좋다. 그 결과, 상기 베이스 기판(101)과 상기 접합층(114) 간의 결합력을 강력하게 할 수 있다. 나아가, 상기 결합력을 향상시키기 위하여, 상기 베이스 기판(101)과 상기 접합층(114)을 서로 밀착되게 한 후, 실시 형태 1에서 설명한 가열 처리 또는 가압 처리를 행할 수도 있다.

다음으로, 반도체 기판(111)을 반도체 기판(111')과 반도체층(115)으로 분리한다(도 3g 참조). 본 실시 형태에 설명되는 상기 분리 공정은 도 1h를 이용하여 설명된 상기 분리 공정과 유사한 방법으로 행해질 수 있다. 상기 반도체 기판(111)의 분리는 상기 베이스 기판(101)과 상기 반도체 기판(111)을 서로 붙인 후에 상기 반도체 기판(111)을 가열하여 실행된다. 상기 반도체 기판(111)의 가열 온도는 상기 베이스 기판의 내열 온도에 의존하며, 예를 들어, 400 ℃ 이상 700 ℃이다.

상술한 공정을 통하여, 상기 베이스 기판(101) 위에 상기 반도체층(115)을 설치한 SOI 기판(132)을 제조한다. 상기 SOI 기판(132)은 상기 베이스 기판(101) 위에 상기 접합층(114), 상기 절연층(116) 및 상기 반도체층(115)이 순서대로 적층되고, 상기 베이스 기판(101)과 상기 접합층(114) 간의 계면에 접합이 형성된 다층 구조를 갖는 기판이다.

이 후에, 상기 레이저 빔(122)으로 상기 SOI 기판(132)을 조사하는 평탄화 공정을 행한다(도 4a 참조). 이러한 평탄화 공정은 도 2a에 도시된 경우와 동일한 방법으로 행해질 수 있다. 도 4a에 도시된 바와 같이, 상기 레이저 빔(122)의 조사는 상기 반도체층(115)의 상면측에 행하여 상기 반도체층(115)을 부분적으로 용융하고, 이로 인하여 평탄성이 개선되고 결함이 감소된 상기 반도체층(115A)을 형성한다(도 4b 참조).

상기 반도체층(115A)을 포함하는 SOI 기판(132A)을 상기 레이저 빔(122)의 조사에 의하여 형성한 후, 상기 반도체층(115A)을 박막화하는 상기 반도체층의 박막화 공정을 행한다(도 4c 참조). 이러한 박막화 공정은 도 2c의 박막화 공정과 동일한 방법으로 행해질 수 있으며, 상기 반도체층(115A)을 에칭(또는 에치-백)하여 상기 반도체층(115A)의 두께를 감소시킨다. 이러한 박막화 공정에서, 상기 반도체층(115B)의 두께를 바람직하게는 100 nm 이하 5 nm 이상으로, 더욱 바람직하게는 50 nm 이하 5 nm 이상으로 제어한다.

본 실시 형태에서는 레이저 광 조사에 의하여 표면을 평탄화한 후 상기 에칭 처리 또는 에치-백 처리를 행하고 있지만, 본 발명은 이에 한정되지 않는다. 예를 들어, 에칭 처리 또는 에치-백 처리를 레이저 광 조사 전에 행할 수도 있다. 이러한 경우에는, 상기 반도체층의 표면에 요철이나 결함을 상기 에칭 처리 또는 에치-백 처리에 의하여 감소시킬 수 있다. 또는 에칭 또는 에치-백 처리를 상기 레이저 광 조사 전 및 후에 행할 수도 있다. 나아가, 상기 레이저 광 조사와 에칭 처리 또는 에치-백 처리를 상호 교대로 반복할 수도 있다. 레이저 광 조사 또는 에칭 처리(또는 에치-백 처리) 중 하나를 이용한 경우와 비교하여, 전술한 바와 같은 레이저 광 조사 및 에칭 처리(또는 에치-백 처리)의 조합을 이용함으로써 상기 반도체층의 표면의 요철, 결함 등을 현저하게 감소시킬 수 있다.

도 3a 내지 도 3g 및 도 4a 내지 도 4c에 도시된 이상의 공정을 통하여 상기 반도체층(115B)을 포함하는 SOI 기판(132B)을 형성할 수 있다.

실시 형태 1에서과 같이, 본 실시 형태에 설명된 공정을 통하여 한 장의 베이스 기판(101)에 복수의 상기 반도체층(115B)을 붙인 상기 SOI 기판(132B)을 제조할 수 있다. 예를 들면, 도 3b 내지 도 3e를 참조하여 설명된 공정을 여러번 반복하여 상기 취화층(113)이 각각 형성된 복수의 상기 반도체 기판(111)을 준비한다. 다음으로, 도 3f의 접합 공정을 여러번 반복하여 상기 복수의 반도체 기판(111)을 상기 한 장의 베이스 기판(101)에 고정시킨다. 그리고나서, 도 3g의 가열 공정을 행하여 상기 반도체 기판(111)을 분리하여, 상기 복수의 반도체층(115)을 상기 베이스 기판(101)에 고정시킨 상기 SOI 기판(132)을 제조한다. 그 후, 상기 도 4a 내지 도 4c의 공정을 통하여 상기 복수의 반도체층(115B)을 상기 베이스 기판(101)에 붙인 상기 SOI 기판(132B)을 형성할 수 있다.

본 실시 형태에서 설명된 바와 같이, 레이저 광 조사에 의한 상기 반도체층의 상기 평탄화 공정 및 에칭 처리(또는 에치-백 처리)를 조합함으로써, 두께가 100 nm 이하이고, 평탄성이 높고, 결함이 적은 상기 반도체층(115B)을 형성할 수 있다. 즉, 상기 베이스 기판(101)으로 유리 기판을 사용하고 상기 취화층(113)의 형성을 위하여 이온 도핑 장치를 사용하더라도 상술한 특성을 갖는 상기 반도체층(115B)이 접합된 상기 SOI 기판(132B)을 형성할 수 있다.

상기 SOI 기판(132B)을 이용한 트랜지스터를 제조함으로써, 게이트 절연층의 박막 및 상기 SOI 기판과 상기 게이트 절연층 사이의 국소화된 계면 상태 밀도의 감소가 실현될 수 있다. 게다가, 상기 반도체층(115B)을 박막화함으로써, 유리 기판 위의 단결정 반도체층을 이용하여 완전 공핍형의 트랜지스터를 제조할 수 있다. 따라서, 높은 성능, 예를 들어 빠른 속도로 동작할 수 있는 높은 신뢰성, 높은 전계 효과 이동도, 및 낮은 전압 소비를 갖는 트랜지스터를 베이스 기판 위에 제조할 수 있다.

대면적에 적합하지 않은 CMP 처리가 필요하지 않으므로, 고성능 반도체 장치의 대면적화를 실현할 수 있다. 본 실시 형태에 따르면, 대면적 기판을 사용하는 경우뿐 아니라 소형 기판을 사용하는 경우에도 물론 양호한 반도체 장치를 제공할 수 있다. 본 실시 형태의 공정을 통하여 얻은 상기 반도체층의 표면 특성은 실시 형태 1에서의 특성과 같다.

본 실시 형태에서 사용되는 상기 반도체 기판의 주표면은 (100) 면, (110) 면 또는 (111) 면에 있는 것이 양호하다. (100) 면을 사용하는 경우에는 계면 상태 밀도를 감소시킬 수 있고, 전계 효과형 트랜지스터의 제조에 적합하다. (110) 면을 사용하는 경우에는 접합층에 포함된 원소와 반도체 포함된 원소(예를 들면, 실리콘 원소) 사이에 밀접한 접합을 형성하며, 절연층과 반도체층 간의 밀착성을 개선시킨다. 즉, 상기 반도체층의 분리를 억제할 수 있다. 게다가, 원자가 (110) 면에 조밀하게 배열되므로 다른 면을 사용하는 경우와 비교하여 SOI 기판의 단결정 실리콘층의 평탄성이 개선된다. 즉, 이러한 반도체층을 사용하여 제조된 트랜지스터는 탁월한 특성을 갖는다. (110) 면도 또한 영률(young's modulus)이 (100) 면의 영률보다 크고, 분리도 쉬운 이점을 갖는다는 것을 염두에 두도록 한다.

본 실시 형태는 실시 형태 1과 적절하게 조합될 수 있다.

(실시 형태 3)

도 5a 내지 도 5h 및 도 6a 내지 도 6c는 본 발명의 반도체 기판용 SOI 기판을 제조하는 방법의 다른 실시예를 도시하는 단면도이다. SOI 기판을 제조하는 방법의 다른 실시예를 도 5a 내지 도 5h 및 도 6a 내지 도 6c를 이용하여 이하 설명한다.

도 1a를 이용하여 실시 형태 1에서 설명한 바와 같이, SOI 기판의 베이스 기판으로 기능하는 상기 베이스 기판(101)을 준비하고(도 5a 참조), 상기 절연층(102)을 상기 베이스 기판(101) 위에 형성한다. 본 실시 형태에서는 또한, 상기 절연층은 상기 질화산화 실리콘막(103) 및 상기 산화질화 실리콘막(104)로 이루어진 2층막이다. 다음으로, 상기 절연층(102) 위에 접합층(105)을 형성한다(도 5b 참조). 이러한 접합층(105)은 실시 형태 1 또는 2에서 설명된 상기 반도체 기판(111) 위에 형성된 상기 접합층(114)과 동일한 방법으로 형성될 수 있다.

도 5c 내지 도 5e는 도 1c 내지 도 1e에 도시된 동일한 공정을 나타내고 있다. 실시 형태 1에서 설명한 바와 같이, 상기 반도체 기판(111) 위에 상기 보호막(112)을 형성하고, 상기 반도체 기판(111) 위에 상기 취화층(113)을 형성한다. 상기 취화층(113)을 형성한 후, 도 5f에 도시된 바와 같이, 상기 보호막(112)을 제거한다. 상기 보호막(112)을 제거한 후, 도 1f와 같이 상기 접합층(114)을 또한 형성할 수 있다. 또는, 상기 보호막(112)을 잔재시킨 상태에서 후속 접합 단계를 행할 수도 있다. 또는, 상기 보호막(112)을 잔재시킨 상태에서 상기 보호막(112) 위에 상기 접합층(114)을 형성할 수 있다.

다음으로, 상기 베이스 기판(101)과 상기 반도체 기판(111)을 서로 붙인다(도 5g 참조). 이러한 붙임 단계는 도 1g를 이용하여 설명된 상기 접합 공정과 동일한 방법으로 행해질 수 있으며, 여기서 상기 반도체 기판(111)과 상기 접합층(105)을 서로 밀접하게 하여서 상기 반도체 기판(111)과 상기 접합층(105)을 서로 접합시킨다.

상기 반도체 기판(111)과 상기 접합층(105)을 접합시키기 전에, 상기 반도체 기판(111)의 표면을 산소 플라즈마 처리 또는 오존 처리를 행하여 친수성으로 만들 수 있다. 나아가, 결합력을 향상시키기 위하여, 상기 반도체 기판(111)과 상기 접합층(105)을 서로 접합시킨 후, 실시 형태 1에 설명된 가열 처리 또는 가압 처리를 행할 수 있다.

다음으로, 상기 반도체 기판(111)을 상기 반도체 기판(111')과 상기 반도체층(115)으로 분리한다(도 5h 참조). 본 실시 형태에 설명된 상기 분리 공정은 도 1h를 이용하여 설명된 상기 분리 공정과 같은 방법으로 행해질 수 있다. 즉, 상기 반도체 기판(111)과 상기 접합층(105)을 서로 접합시킨 후, 상기 반도체 기판(111)을 400 ℃ 이상 700 ℃ 이하의 온도로 가열시킨다. 상기 가열 온도의 상한은 상기 베이스 기판(101)의 비등점을 초과하지 않도록 설정한다.

전술한 공정을 통하여, 상기 베이스 기판(101) 위에 상기 반도체층(115)을 설치한 SOI 기판(133)을 제조한다. 상기 SOI 기판(133)은 상기 절연층(102), 상기 접합층(105) 및 상기 반도체층(115)가 순서대로 적층되고, 상기 반도체층(115)과 상기 접합층(105) 사이의 계면에 결합이 형성된 다층 구조의 기판이다.

이 후에, 상기 레이저 빔(122)으로 상기 SOI 기판(133)을 조사하는 평탄화 공정을 행한다(도 6a 참조). 이러한 평탄화 공정은 도 2a에 도시된 방법과 동일한 방법으로 행해질 수 있다. 도 6a에 도시된 바와 같이, 상기 레이저 빔(122)의 조사는 상기 반도체층(115)의 상면측에 행하여 상기 반도체층(115)을 부분적으로 용융하고, 이로 인하여 평탄성이 개선되고 결함이 감소된 상기 반도체층(115A)을 형성한다(도 6b 참조).

상기 반도체층(115A)을 포함하는 SOI 기판(133A)을 상기 레이저 빔(122)의 조사에 의하여 형성한 후, 상기 반도체층(115A)을 박막화하는 상기 반도체층의 박막화 공정을 행한다(도 6c 참조). 이러한 박막화 공정은 도 2c의 박막화 공정과 동일한 방법으로 행해질 수 있으며, 상기 반도체층(115A)을 에칭(또는 에치-백)하여 상기 반도체층(115A)의 두께를 감소시킨다. 이러한 박막화 공정에서, 상기 반도체층(115B)의 두께를 바람직하게는 100 nm 이하 5 nm 이상으로, 더욱 바람직하게는 50 nm 이하 5 nm 이상으로 제어한다.

도 5a 내지 도 5h 및 도 6a 내지 도 6c에 도시된 이상의 공정을 통하여 상기 반도체층(115B)을 포함하는 SOI 기판(133B)을 형성할 수 있다.

실시 형태 1에서과 같이, 본 실시 형태에 설명된 공정을 통하여 한 장의 베이스 기판(101)에 복수의 상기 반도체층(115B)을 붙인 상기 SOI 기판(133B)을 제조할 수 있다. 예를 들면, 도 5c 내지 도 5f를 이용하여 설명된 공정을 여러번 반복하여 상기 취화층(113)에 각각 설치된 복수의 상기 반도체 기판(111)을 준비한다. 다음으로, 도 5g의 접합 공정을 여러번 반복하여 상기 복수의 반도체 기판(111)을 상기 한 장의 베이스 기판(101)에 고정시킨다. 그리고나서, 도 5h의 가열 공정을 행하여 상기 반도체 기판(111)을 분리하여, 상기 복수의 반도체층(115)을 상기 베이스 기판(101)에 고정시킨 상기 SOI 기판(133)을 제조한다. 그 후, 상기 도 6a 내지 도 6c의 공정을 통하여 상기 복수의 반도체층(115B)을 상기 베이스 기판(101)에 붙인 상기 SOI 기판(133B)을 형성할 수 있다.

본 실시 형태에서 설명된 바와 같이, 레이저 광 조사에 의한 상기 반도체층의 상기 평탄화 공정 및 에칭 처리(또는 에치-백 처리)를 조합함으로써, 두께가 100 nm 이하이고, 평탄성이 높고, 결함이 적은 상기 반도체층(115B)을 형성할 수 있다. 즉, 상기 베이스 기판(101)으로 유리 기판을 사용하고 상기 취화층(113)의 형성을 위하여 이온 도핑 장치를 사용하더라도 상술한 특성을 갖는 상기 반도체층(115B)이 접합된 상기 SOI 기판(133B)을 형성할 수 있다.

상기 SOI 기판(133B)을 이용한 트랜지스터를 제조함으로써, 게이트 절연층의 박막 및 상기 SOI 기판과 상기 게이트 절연층 사이의 국소화된 계면 상태 밀도의 감소가 실현될 수 있다. 게다가, 상기 반도체층(115B)을 박막화함으로써, 유리 기판 위의 단결정 반도체층을 이용하여 완전 공핍형의 트랜지스터를 제조할 수 있다. 따라서, 높은 성능, 예를 들어 빠른 속도로 동작할 수 있는 높은 신뢰성, 높은 전계 효과 이동도, 및 낮은 전압 소비를 갖는 트랜지스터를 베이스 기판 위에 제조할 수 있다.

대면적에 적합하지 않은 CMP 처리가 필요하지 않으므로, 고성능 반도체 장치의 대면적화를 실현할 수 있다. 본 실시 형태에 따르면, 대면적 기판을 사용하는 경우뿐 아니라 소형 기판을 사용하는 경우에도 물론 양호한 반도체 장치를 제공할 수 있다. 본 실시 형태의 공정을 통하여 얻은 상기 반도체층의 표면 특성은 실시 형태 1에서의 특성과 같다.

본 실시 형태에서 사용되는 상기 반도체 기판의 주표면은 (100) 면, (110) 면 또는 (111) 면인 것이 양호하다. (100) 면을 사용하는 경우에는 계면 상태 밀도를 감소시킬 수 있고, 전계 효과형 트랜지스터의 제조에 적합하다. (110) 면을 사용하는 경우에는 접합층에 포함된 원소와 반도체 포함된 원소(예를 들면, 실리콘 원소) 사이에 밀접한 접합을 형성하며, 절연층과 반도체층 간의 밀착성을 개선시킨다. 즉, 상기 반도체층의 분리를 억제할 수 있다. 게다가, 원자가 (110) 면에 조밀하게 배열되므로 다른 면을 사용하는 경우와 비교하여 SOI 기판의 단결정 실리콘층의 평탄성이 개선된다. 즉, 이러한 반도체층을 사용하여 제조된 트랜지스터는 탁월한 특성을 갖는다. (110) 면도 또한 영률(young's modulus)이 (100) 면의 영률보다 크고, 분리도 쉬운 이점을 갖는다는 것을 염두에 두도록 한다.

본 실시 형태는 실시 형태 1 또는 2와 적절하게 조합될 수 있다.

(실시 형태 4)

실시 형태 1 내지 3 각각에서는 상기 레이저 빔(122)으로 상기 반도체층(115)을 조사하기 전에 에칭 처리(또는 에치-백 처리)에 의하여 상기 반도체층(115)을 박막화하는 박막 공정을 행할 수 있다. 상기 취화층(113)의 형성에 이온 도핑 장치를 사용하는 경우에는, 상기 반도체층(115)의 두께를 100 nm 이하로 조절하는 것이 어렵다. 그러므로, 분리 직후의 상기 반도체층(115)은 비교적 두껍다. 상기 반도체층(115)이 두꺼울 경우에는 상기 레이저 빔(122)의 조사 에너지 밀도가 높아야하며, 따라서 상기 조사 에너지 밀도의 적용 범위가 더 좁아지게 되어 상기 레이저 빔(122)의 조사에 의하여 높은 수율로 상기 반도체층(115)을 평탄화하고 상기 반도체층(115)의 결정을 회복하는 것이 어려워진다.

그러므로, 상기 반도체층(115)의 두께가 200 nm를 초과하는 경우에는, 상기 반도체층(115)의 두께를 200 nm 이하로 감소시켜서 상기 레이저 빔(122)으로 조사하는 것이 바람직하다. 전술한 박막 처리는 상기 반도체층(115)의 두께를 60 nm 이상 150 nm 이하로 바람직하게 감소시킨다.

구체적으로, 상기 반도체층의 박막은 다음과 같이 실현될 수 있다:

우선, 상기 반도체층(115)을 에칭 처리 또는 에치-백 처리하여 박막화하고 나서 상기 레이저 빔(122)을 조사한다; 그리고나서, 상기 반도체층 상에 다시 에칭 처리 또는 에치-백 처리를 행하여서 상기 반도체층의 두께를 더욱 소망하는 두께로 감소시킨다. 상기 레이저 빔(122)의 조사 전에 박막에 의하여 상기 반도체층(115)을 소망하는 두께로 박막화할 수 있는 경우에는, 상기 레이저 빔(122)으로 조사한 후의 상기 박막을 생략할 수 있다.

본 실시 형태는 실시 형태 1 내지 3 중 하나와 적절하게 조합할 수 있다.

(실시 형태 5)

도 1a 내지 도 1h, 도 2a 내지 도 2c, 도 3a 내지 도 3g, 도 4a 내지 도 4c, 도 5a 내지 도 5h 및 도 6a 내지 도 6c를 이용하여 설명된 SOI 기판을 제조하는 방법 각각에 의하면, 무알칼리 유리 기판과 같은 다양한 종류의 유리 기판을 상기 베이스 기판(101)으로 적용할 수 있다. 그러므로, 상기 베이스 기판(101)으로 유리 기판을 사용함으로써, 각 면이 1 미터 이상인 대면적 SOI 기판을 제조할 수 있다. 이와 같은 반도체 제조에 제공되는 대면적 기판 위에 복수의 반도체 소자를 형성하게 되면, 액정 표시 장치, 전자발광 표시 장치 등을 제조할 수 있다. 이러한 표시 장치뿐 아니라 SOI 기판을 이용하여 태양 전지, 포토 IC 및 반도체 메모리 장치와 같은 다양한 종류의 반도체 장치를 제조할 수 있다.

이하, 도 7a 내지 도 7d 및 도 8a 및 도 8b를 참조하여 SOI 기판을 이용한 박막 트랜지스터를 제조하는 방법을 설명한다. 본 실시 형태에 설명된 트랜지스터 각각과 같은 복수의 박막 트랜지스터를 조합하여 다양한 종류의 반도체 장치를 형성한다.

도 7a는 SOI 기판의 단면도이다. 본 실시 형태에서는, 실시 형태 2의 제조 방법에 의해 제조된 상기 SOI 기판(132B)을 이용한다. 물론, 다른 구조를 갖는 SOI 기판도 사용할 수 있다.

TFT의 임계 전압을 제어하기 위하여는, 상기 반도체층(115B)에 붕소, 알루미늄, 갈륨과 같은 p형 불순물 또는 인 또는 비소와 같은 n형 불순물을 첨가하는 것이 바람직하다. 상기 불순물을 첨가하는 영역과 첨가하는 불순물의 종류는 n 채널형 TFT 또는 p 채널형 TFT 중 어느 것을 형성할 것인지, TFT을 어디에 형성할 것인지 등에 따라 적절하게 변경할 수 있다. 예를 들면, p형 불순물은 n 채널형 TFT의 형성 영역에 첨가할 수 있고, n형 불순물은 p 채널형 TFT의 형성 영역에 첨가할 수 있다. 상술한 불순물의 첨가는 도스량(dose amount)이 1×1012 ions/㎠ 이상 1×1017 ions/㎠ 이하 정도가 되도록 행하는 것이 바람직하다.

다음으로, 상기 SOI 기판의 상기 반도체층(115B)을 에칭하여 섬형상(island shape)으로 분리하여, 반도체층들(151, 152)을 형성한다(도 7b 참조). 본 실시 형태에서는, 상기 반도체층(151)을 이용하여 n 채널형 TFT를 형성하고 상기 반도체층(152)을 이용하여 p 채널형 TFT를 형성한다.

그리고나서, 상기 반도체층들(151, 152) 각각의 위에 게이트 절연층(153), 게이트 전극(154), 사이드월(sidewall) 절연층(155) 및 질화 실리콘층(156)을 형성한다(도 7c 참조). 상기 질화 실리콘층(156)은 에칭에 의하여 상기 게이트 전극(154)의 형상을 가공하는 마스크로 이용한다. 게이트 전극은 본 실시 형태에서 2층 구조를 갖는다.

다음으로, 상기 게이트 전극(154)을 마스크로 이용한 불순물 첨가와 상기 게이트 전극(154)과 상기 사이드월 절연층(155)을 마스크로 이용한 불순물 첨가는 상기 반도체층들(151, 152) 상에 행하여, 상기 반도체층(151)에 고농도 n형 불순물 영역(157)과 저농도 n형 불순물 영역(158)을 형성하고 상기 반도체(152)에 고농도 p형 불순물 영역(160)을 형성한다. 상기 반도체층들(151, 152)에 게이트 전극(154)과 중첩된 각 영역은 채널 형성 영역들(159, 161)이 된다. 상기 고농도 n형 불순물 영역들(157, 160)은 소스 및 드레인 영역으로 기능한다. 상기 n 채널형 TFT의 상기 저농도 n형 불순물 영역(158)은 LDD 영역으로 기능한다. 상기 불순물을 첨가한 후, 상기 반도체층들(151, 152)에 첨가되는 상기 불순물을 활성화하기 위하여 가열 처리를 행한다.

다음으로, 수소를 함유하는 절연층(163)을 형성한다(도 7d 참조). 상기 절연층(163)의 형성 후에, 350 ℃ 이상 450 ℃ 이하의 온도로 가열 처리를 행하여, 상기 절연층(163)에 함유된 수소를 반도체층들(151, 152)로 확산시킨다. 상기 절연층(163)은 프로세스 온도를 350 ℃ 이하로 하는 플라즈마 CVD법에 의하여 질화 실리콘 또는 질화산화 실리콘을 적층하여 형성할 수 있다. 상기 반도체층들(151, 152)에 수소를 공급함으로써 상기 반도체층(151)과 상기 게이트 절연층(153) 사이의 계면 및 상기 반도체층(152)과 상기 게이트 절연층(152) 사이의 계면의 결함을 효과적으로 감소시킬 수 있다.

그 후, 층간 절연층(164)을 형성한다(도 8a 참조). 상기 층간 절연층(164)로는, BPSG(boron phosphorus silicon glass)로 형성된 막, 또는 전형적인 폴리이미드와 같은 유기 수지막을 사용할 수 있다. 콘택트 홀(165)을 상기 층간 절연층(164)에 형성한다.

다음으로, 배선과 같은 것을 형성한다(도 8b 참조). 콘택트 플러그(166)는 상기 콘택트 홀(165)에 형성한다. WF6 가스 또는 SiH4 가스를 이용하는 화학기상성장법에 의해 텅스텐 실리사이드(tungsten silicide)를 형성하여 상기 콘택트 홀(165)을 채워서 상기 콘택트 플러그(166)를 형성한다. 또는, WF6 가스의 수소를 환원하는 텅스텐을 형성하여 상기 콘택트 홀(165)을 채워도 좋다. 그 후, 상기 콘택트 플러그(166)에 따라 배선(167)을 형성한다. 배선(167) 각각은 3층 구조인데, 알루미늄 또는 알루미늄 합금으로 형성된 전도막을 배리어 금속으로 기능하는 몰리브덴, 크로뮴, 티타늄 등의 금속막들 사이에 끼워넣어 형성한다. 상기 배선(167) 위에 층간 절연막(168)을 형성한다. 상기 배선(167)은 적절히 설치될 수 있고 다른 배선층을 그 위에 형성하여 다층 배선 구조를 형성한다. 이러한 경우, 싱글-다마신(single-damascence) 또는 듀얼-다마신(dual-damascence)와 같은 다마신 프로세스를 적용한다.

이상의 방법으로, SOI를 이용하는 각 박막 트랜지스터를 제조할 수 있다. SOI 기판의 반도체층은 결정 결함이 거의 없고 상기 반도체층과 상기 게이트 절연층(153) 사이의 계면 상태 밀도가 저감된 단결정 반도체층이다. 나아가, 상기 반도체층이 표면은 평탄화되고 그 두께는 100 nm 이하로 감소되었다. 따라서, 낮은 구동 전압, 높은 전계 효과 이동도, 서브문턱값과 같은 우수한 특성을 갖는 박막 트랜지스터를 상기 베이스 기판(101) 위에 형성할 수 있다. 나아가, 동일한 기판 위에 특성의 차이가 적은 높은 성능의 트랜지스터를 형성할 수 있다. 즉, 실시 형태 1 내지 3 각각에 설명된 상기 SOI 기판을 사용하여, 임계 전압 또는 이동도와 같은 트랜지스터 특성으로서 중요한 특성의 차이를 억제할 수 있고 상기 특성을 개선시킬 수 있다.

전술한 실시 형태 1 내지 3의 방법 중 하나에 따른 상기 SOI 기판을 이용한 반도체 소자를 형성함으로써, 높은 부가가치를 갖는 반도체 장치를 저가에 제조할 수 있다. 이하, 반도체 장치의 구체적인 모드를 도면을 참조하여 설명한다.

우선, 상기 반도체 장치의 예로서, 마이크로프로세서를 설명한다. 도 9는 마이크로프로세서(200)의 구성 예를 도시한 블록도이다.

이 마이크로프로세서(200)는 연산논리부(arithmetic logic unit: ALU)(201), ALU 제어부(ALU controller)(202), 명령 디코더(instruction decoder)(203), 인터럽트 제어부(interrupt controller)(204), 타이밍 제어부(timing controller)(205), 레지스터(register)(206), 레지스터 제어부(register controller)(207), 버스 인터페이스(bus interface: Bus I/F)(208), 읽기 전용 메모리(read-only memory: ROM)(209), 메모리 인터페이스(memory interface: ROM I/F)(210)를 갖는다.

상기 버스 인터페이스(208)을 통하여 상기 마이크로프로세서(200)에 입력되는 명령은 상기 명령 디코더(203)로 입력되어 디코딩되고, 그리고 나서 상기 ALU 제어부(202), 상기 인터럽트 제어부(204), 상기 레지스터 제어부(207) 및 상기 타이밍 제어부(205)에 입력된다. 상기 ALU 제어부(202), 상기 인터럽트 제어부(204), 상기 레지스터 제어부(207) 및 상기 타이밍 제어부(205)는 상기 디코딩된 명령을 기초로 다양한 제어를 수행한다.

구체적으로, 상기 ALU 제어부(202)는 상기 ALU(201)의 동작을 제어하는 신호를 생성한다. 나아가, 상기 마이크로프로세서(200)가 프로그램을 실행하는 동안, 인터럽트 제어부(204)는 외부 입력/출력 장치 또는 주변 회로로부터의 인터럽트 요구를그 우선도나 마스크 상태에 기초하여 처리한다. 상기 레지스터 제어부(207)는 상기 레지스터(206)의 어드레스를 생성하고 상기 마이크로프로세서(200)의 상태에 대응하여 상기 레지스터(206)로부터 그리고 상기 레지스터(206)로 데이터를 읽고 쓴다. 상기 타이밍 제어부(205)는 상기 ALU(201), 상기 ALU 제어부(202), 상기 명령 디코더(203), 상기 인터럽트 제어부(204) 및 상기 레지스터 제어부(207)의 동작 타이밍을 제어하는 신호를 생성한다.

예를 들면, 상기 타이밍 제어부(205)는 기준 클록 신호 CLK1에 기초하여 내부 클록 신호 CLK2를 생성하는 내부 클록 생성기를 구비하고 있어 상술한 다양한 회로로 상기 내부 클록 신호 CLK2를 제공한다. 도 9에 도시된 상기 마이크로프로세서(200)는 구성을 단순화한 예에 불과하며, 실제로 마이크로프로세서는 용도에 따라 다양한 구성을 갖는다.

상기 마이크로프로세서(200)는, 절연 표면 또는 절연 기판을 갖는 기판에 접합된 일정한 결정 방위를 갖는 단결정 반도체층(SOI 층)을 이용하여 집적 회로를 형성하기 때문에, 처리 속도의 고속화뿐 아니라 전력 소비에 있어서의 감소도 성취할 수 있다.

다음으로, 무선 데이터 송수신 기능 및 연산 기능을 구비한 반도체 장치의 예를 설명한다. 도 10은 이와 같은 반도체 장치의 구성예를 도시한 블록도이다. 도 10에 도시된 상기 반도체 장치는 무선 통신에 의해 외부 장치로/로부터 신호 전송 및 수신을 수행하여 동작하는 컴퓨터(이하 'RFCPU'라 한다)로 볼 수 있다.

RFCPU(211)는 도 10에 도시된 바와 같이 아날로그 회로부(212) 및 디지털 회로부(213)를 포함한다. 상기 아날로그 회로부(212)는 공진 용량을 갖는 공진 회로(214), 정류 회로(215), 정전압 회로(216), 리셋 회로(217), 발진 회로(218) 및 복조 회로(219) 및 변조 회로(220)를 포함한다. 상기 디지털 회로부(213)는 RF 인터페이스(221), 제어 레지스터(222), 클록 콘트롤러(223), CPU 인터페이스(224), 중앙 처리 유닛(225), 랜덤-액세스 메모리(226) 및 읽기 전용 메모리(227)를 포함한다.

상기 RFCPU(211)의 동작을 대략적으로 설명한다. 상기 공진 회로(214)는 안테나(228)에 의해 수신된 신호에 기초하여 유도 기전력을 생성한다. 상기 유도 기전력은 상기 정류 회로(215)를 통하여 용량부(229)에 충전된다. 상기 용량부(229)는 세라믹 커패시터 또는 전기 이중층 커패시터와 같은 커패시터를 형성하는 것이 바람직하다. 상기 용량부(229)는 상기 RFCPU(211)와 동일한 기판 위에 형성될 필요는 없고, 상기 용량부(229)는 상기 RFCPU(211)에 포함된 절연면을 갖는 기판에 별도의 부품으로 부착될 수 있다.

상기 리셋 회로(217)는 상기 디지털 회로부(213)를 리셋하기 위하여 초기화하는 신호를 생성한다. 예를 들면, 전원 전압의 상승 후 발생하는 신호를 상기 리셋 신호로 생성한다. 발진 회로(218)는 상기 정전압 회로(216)에 의해 생성된 제어 신호에 응답하여 클록 신호의 주파수 및 듀티비를 변경한다. 상기 복조 회로(219)는 수신 신호를 복조하는 회로이고, 상기 변조 회로(220)는 전송될 데이터를 변조하는 회로이다.

예를 들면, 상기 복조 회로(219)는 저역 필터를 포함하고 상기 신호의 진폭 변조(ASK) 방식의 수신 신호를 상기 신호의 진폭의 변동에 기초하여 이진화한다. 상기 변조 회로(220)는 진폭 변조(ASK) 방식의 송신 신호의 진폭을 변경함으로써 전송 데이터를 전송한다. 따라서, 상기 변조 회로(220)는 상기 공진 회로(214)의 공진점을 변화시켜서 통신 신호의 진폭을 변화시킨다.

상기 클록 콘트롤러(223)는 전원 전압 또는 상기 중앙 처리 유닛(225)의 소비 전류에 따라 클록 신호의 주파수 및 듀티비를 변경하는 제어 신호를 생성한다. 상기 전원 전압은 상기 전원 전압 제어 회로(230)에 의해 감시된다.

상기 안테나(228)로부터 상기 RFCPU(211)로 입력된 신호를 상기 복조 회로(219)에서 복조한 후, RF 인터페이스(221)에서 제어 코맨드, 데이터 등을 분해한다. 상기 제어 코맨드는 상기 제어 레지스터(222)에 저장한다. 상기 제어 코맨드는 상기 읽기 전용 메모리(227)에 저장된 데이터 읽기, 상기 랜덤-액세스 메모리(226)에 데이터 쓰기, 상기 중앙 처리 유닛(225)으로의 연산 명령 등을 포함한다.

상기 중앙 처리 유닛(225)은 상기 CPU 인터페이스(224)를 통해 상기 읽기 전용 메모리(227), 상기 랜덤-액세스 메모리(226) 및 상기 제어 레지스터(222)에 액세스한다. 상기 인터페이스(224)는 상기 중앙 처리 유닛(225)이 요구하는 어드레스에 기초하는 상기 읽기 전용 메모리(227), 상기 랜덤-액세스 메모리(226) 및 상기 제어 레지스터(222) 중 하나를 위해 액세스 신호를 생성하는 기능을 갖는다.

상기 중앙 처리 유닛(225)의 연산 방식은, 상기 읽기 전용 메모리(227)가 미리 운영 시스템(OS)을 저장하고, 시작 동작시에 프로그램을 읽어 실행하는 방식을 적용한다. 또는, 연산 전용 회로로 연산 회로를 형성하고 연산 처리를 하드웨어를 이용하여 실행하는 방식을 채택할 수도 있다. 하드웨어와 소프트웨어를 병용하는 방식에서는, 연산 전용 회로에 의해 일부 처리를 실행하고, 프로그램을 이용하여 연산 프로세싱의 나머지 부분을 상기 중앙 처리 유닛(225)에서 실행하는 방식을 적용할 수 있다.

상기 RFCPU(211)는 절연 표면 또는 절연 기판을 갖는 기판에 접합된 결정 방위가 일정한 단결정 반도체층(SOI층)을 이용하여 집적 회로를 형성하기 때문에, 처리 속도의 고속화뿐 아니라 전력 소비의 저감을 성취할 수 있다. 따라서, 전력을 제공하는 상기 용량부(229)를 소형화하더라도 장시간의 동작을 보장할 수 있다.

다음으로, 본 발명의 상기 반도체 장치로, 도 11, 도 12a 및 도 12b, 그리고 도 13a 및 도 13b를 참조하여 표시 장치를 설명한다.

SOI 기판의 베이스 기판으로 표시 패널을 제조하는 마더 유리라 불리는 대면적 유리 기판을 사용할 수 있다. 도 11은 마더 유리를 상기 베이스 기판(101)으로 사용하는 SOI 기판의 정면도이다.