JP6421570B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6421570B2 JP6421570B2 JP2014248139A JP2014248139A JP6421570B2 JP 6421570 B2 JP6421570 B2 JP 6421570B2 JP 2014248139 A JP2014248139 A JP 2014248139A JP 2014248139 A JP2014248139 A JP 2014248139A JP 6421570 B2 JP6421570 B2 JP 6421570B2

- Authority

- JP

- Japan

- Prior art keywords

- igbt

- region

- layer

- diode

- conductivity type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 42

- 239000010410 layer Substances 0.000 claims description 127

- 238000002347 injection Methods 0.000 claims description 76

- 239000007924 injection Substances 0.000 claims description 76

- 239000012535 impurity Substances 0.000 claims description 67

- 239000002344 surface layer Substances 0.000 claims description 11

- 239000000758 substrate Substances 0.000 description 24

- 238000009792 diffusion process Methods 0.000 description 14

- 230000015572 biosynthetic process Effects 0.000 description 12

- 238000005468 ion implantation Methods 0.000 description 12

- 239000000969 carrier Substances 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 7

- 238000000034 method Methods 0.000 description 6

- 239000011295 pitch Substances 0.000 description 6

- 238000000137 annealing Methods 0.000 description 5

- 238000009826 distribution Methods 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- 238000010586 diagram Methods 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 239000007772 electrode material Substances 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 230000007423 decrease Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/07—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common

- H01L27/0705—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common comprising components of the field effect type

- H01L27/0711—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common comprising components of the field effect type in combination with bipolar transistors and diodes, or capacitors, or resistors

- H01L27/0716—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common comprising components of the field effect type in combination with bipolar transistors and diodes, or capacitors, or resistors in combination with vertical bipolar transistors and diodes, or capacitors, or resistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/07—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common

- H01L27/0705—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common comprising components of the field effect type

- H01L27/0727—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common comprising components of the field effect type in combination with diodes, or capacitors or resistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/083—Anode or cathode regions of thyristors or gated bipolar-mode devices

- H01L29/0834—Anode regions of thyristors or gated bipolar-mode devices, e.g. supplementary regions surrounding anode regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/107—Substrate region of field-effect devices

- H01L29/1075—Substrate region of field-effect devices of field-effect transistors

- H01L29/1079—Substrate region of field-effect devices of field-effect transistors with insulated gate

- H01L29/1087—Substrate region of field-effect devices of field-effect transistors with insulated gate characterised by the contact structure of the substrate region, e.g. for controlling or preventing bipolar effect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/30—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by physical imperfections; having polished or roughened surface

- H01L29/32—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by physical imperfections; having polished or roughened surface the imperfections being within the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/36—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the concentration or distribution of impurities in the bulk material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/8613—Mesa PN junction diodes

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

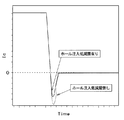

本発明の第1実施形態について説明する。図1に示すように、本実施形態にかかる半導体装置は、基板厚み方向に電流を流す縦型のIGBTとダイオードとが1つの基板に備えられることにより構成されている。具体的には、本実施形態にかかる半導体装置は以下のように構成されている。

本発明の第2実施形態について説明する。本実施形態は、第1実施形態に対してIGBT部100の構成を変更したものであり、その他については第1実施形態と同様であるため、第1実施形態と異なる部分についてのみ説明する。

本発明の第3実施形態について説明する。本実施形態は、第1、第2実施形態に対してホール注入低減層20の形成位置を増加させたものであり、その他については第1、第2実施形態と同様であるため、第1、第2実施形態と異なる部分についてのみ説明する。なお、ここでは第2実施形態に対してホール注入低減層20の形成位置を増加させた場合について説明するが、第1実施形態に対しても同様の構成を適用できる。

本発明の第4実施形態について説明する。本実施形態は、第2、第3実施形態に対してホールストッパ層を備えたものであり、その他については第2、第3実施形態と同様であるため、第2、第3実施形態と異なる部分についてのみ説明する。なお、ここでは第3実施形態に対してホールストッパ層を形成した場合について説明するが、第2実施形態に対しても同様の構成を適用できる。

本発明の第5実施形態について説明する。本実施形態は、第1〜第4実施形態に対してIGBT部100側にはみ出させたホール注入低減層20の形成位置を具体的に特定したものであり、その他については第1〜4実施形態と同様であるため、第1〜第4実施形態と異なる部分についてのみ説明する。なお、ここでは第1実施形態に対してホール注入低減層20の形成位置を増加させた場合について説明するが、第2〜第4実施形態に対しても同様の構成を適用できる。

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

3 コレクタ領域

4 カソード領域

5a チャネルp型領域

5b アノード領域

6 トレンチ

7 エミッタ領域

9 ゲート電極

20 ホール注入低減層

30 ホールストッパ層

100 IGBT部

200 ダイオード部

Claims (5)

- 縦型のIGBTが形成されたIGBT部(100)と、前記IGBT部に沿って備えられ、ダイオードが形成されたダイオード部(200)と、を有する半導体装置であって、

第1導電型のドリフト層(1)と、

前記IGBT部において、前記ドリフト層の裏面側に形成された第2導電型のコレクタ領域(3)と、

前記ダイオード部において、前記ドリフト層の裏面側に形成された第1導電型のカソード領域(4)と、

前記ドリフト層の表面側の表層部において、前記IGBT部および前記ダイオード部の双方に形成された第2導電型領域(5)と、

前記IGBT部において、複数本並べられ、前記第2導電型領域よりも深く形成されて前記第2導電型領域を複数に分けることで、前記第2導電型領域の少なくとも一部によってチャネル領域(5a)を構成するトレンチ(6)と、

前記IGBT部において、前記チャネル領域の表層部に前記トレンチの側面に沿って形成された第1導電型のエミッタ領域(7)と、

前記ダイオード部において、前記ドリフト層の上層部に、該ダイオード部における前記第2導電型領域により構成されるアノード領域(5b)よりも深くて低不純物濃度とされ、かつ、前記ドリフト層よりも高不純物濃度とされた第1導電型のホール注入低減層(20)と、

前記トレンチの表面に形成されたゲート絶縁膜(8)と、

前記ゲート絶縁膜の表面に形成されたゲート電極(9)と、

前記IGBT部において前記第2導電型領域に電気的に接続されると共に、前記アノード領域に電気的に接続された上部電極(11)と、

前記IGBT部において前記コレクタ領域に電気的に接続されると共に、前記ダイオード部において前記カソード領域と電気的に接続された下部電極(12)と、を備え、

前記IGBT部のうち前記ダイオード部に隣接している部分にも、前記ホール注入低減層が形成され、

該ホール注入低減層は、前記ダイオード部から前記IGBT部の一部にのみはみ出して形成されていることを特徴とする半導体装置。 - 前記IGBT部には、前記トレンチにて複数に分けられた前記第2導電型領域のうち前記チャネル領域ではない部分によって前記エミッタ領域が形成されていない間引き部が構成されていることを特徴とする請求項1に記載の半導体装置。

- 前記間引き部において、前記トレンチの深さ方向において前記第2導電型領域を上下に分割する第1導電型のホールストッパ層(30)が形成されていることを特徴とする請求項2に記載の半導体装置。

- 前記IGBT部には、前記トレンチにて複数に分けられた前記第2導電型領域のうち前記チャネル領域ではない部分によって前記エミッタ領域が形成されていない間引き部が構成されていると共に、該間引き部において、前記トレンチの深さ方向において前記第2導電型領域を上下に分割する第1導電型のホールストッパ層(30)が形成されており、

前記ホールストッパ層は、前記間引き部のうち前記ホール注入低減層が形成されている部分には形成されておらず、前記ホール注入低減層が形成されていない部分に形成されていることを特徴とする請求項1に記載の半導体装置。 - 前記ホール注入低減層は、前記トレンチの底部よりも浅く形成されていることを特徴とする請求項1ないし4のいずれか1つに記載の半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014248139A JP6421570B2 (ja) | 2013-12-20 | 2014-12-08 | 半導体装置 |

| US15/105,664 US9721945B2 (en) | 2013-12-20 | 2014-12-16 | Semiconductor device with IGBT and diode |

| PCT/JP2014/006244 WO2015093038A1 (ja) | 2013-12-20 | 2014-12-16 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013264294 | 2013-12-20 | ||

| JP2013264294 | 2013-12-20 | ||

| JP2014248139A JP6421570B2 (ja) | 2013-12-20 | 2014-12-08 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015135954A JP2015135954A (ja) | 2015-07-27 |

| JP2015135954A5 JP2015135954A5 (ja) | 2017-04-13 |

| JP6421570B2 true JP6421570B2 (ja) | 2018-11-14 |

Family

ID=53402406

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014248139A Active JP6421570B2 (ja) | 2013-12-20 | 2014-12-08 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9721945B2 (ja) |

| JP (1) | JP6421570B2 (ja) |

| WO (1) | WO2015093038A1 (ja) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6185511B2 (ja) * | 2015-05-26 | 2017-08-23 | トヨタ自動車株式会社 | 半導体装置 |

| DE102015111371B4 (de) * | 2015-07-14 | 2017-07-20 | Infineon Technologies Ag | Halbleiterbauelement mit einem schaltbaren und einem nicht schaltbaren Diodengebiet |

| JP6582762B2 (ja) * | 2015-09-03 | 2019-10-02 | 株式会社デンソー | 半導体装置 |

| JP6531589B2 (ja) * | 2015-09-17 | 2019-06-19 | 株式会社デンソー | 半導体装置 |

| JP6299789B2 (ja) * | 2016-03-09 | 2018-03-28 | トヨタ自動車株式会社 | スイッチング素子 |

| DE112017000079T5 (de) | 2016-03-10 | 2018-05-17 | Fuji Electric Co., Ltd. | Halbleitervorrichtung |

| US9768285B1 (en) * | 2016-03-16 | 2017-09-19 | Semiconductor Components Industries, Llc | Semiconductor device and method of manufacture |

| CN108604594B (zh) | 2016-08-12 | 2021-10-08 | 富士电机株式会社 | 半导体装置及半导体装置的制造方法 |

| JP6724993B2 (ja) | 2016-08-12 | 2020-07-15 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| CN106206679B (zh) * | 2016-08-31 | 2019-08-23 | 电子科技大学 | 一种逆导型igbt |

| DE112017000727T5 (de) | 2016-09-14 | 2018-10-31 | Fuji Electric Co., Ltd. | RC-IGBT und Herstellungsverfahren dafür |

| US10559663B2 (en) | 2016-10-14 | 2020-02-11 | Fuji Electric Co., Ltd. | Semiconductor device with improved current flow distribution |

| WO2018074434A1 (ja) * | 2016-10-17 | 2018-04-26 | 富士電機株式会社 | 半導体装置 |

| JP6624300B2 (ja) * | 2016-10-17 | 2019-12-25 | 富士電機株式会社 | 半導体装置 |

| CN109075202B (zh) | 2016-11-17 | 2021-08-31 | 富士电机株式会社 | 半导体装置 |

| EP3324443B1 (en) | 2016-11-17 | 2019-09-11 | Fuji Electric Co., Ltd. | Semiconductor device |

| JP6939300B2 (ja) * | 2016-11-17 | 2021-09-22 | 富士電機株式会社 | 半導体装置 |

| CN109314141B (zh) | 2016-12-08 | 2021-09-14 | 富士电机株式会社 | 半导体装置 |

| CN109219888B (zh) | 2016-12-08 | 2022-03-29 | 富士电机株式会社 | 半导体装置 |

| CN109891595B (zh) | 2017-05-31 | 2022-05-24 | 富士电机株式会社 | 半导体装置 |

| US10847617B2 (en) | 2017-12-14 | 2020-11-24 | Fuji Electric Co., Ltd. | Semiconductor device |

| JP6973510B2 (ja) | 2018-01-17 | 2021-12-01 | 富士電機株式会社 | 半導体装置 |

| JP6862381B2 (ja) | 2018-03-02 | 2021-04-21 | 株式会社東芝 | 半導体装置 |

| JP2019160877A (ja) * | 2018-03-08 | 2019-09-19 | トヨタ自動車株式会社 | 半導体装置 |

| JP7091204B2 (ja) * | 2018-09-19 | 2022-06-27 | 株式会社東芝 | 半導体装置 |

| DE102019106087B3 (de) * | 2019-03-11 | 2020-06-18 | Infineon Technologies Ag | Halbleitervorrichtung mit einem halbleiterkörper aus siliziumcarbid und verfahren |

| CN113287201A (zh) | 2019-07-12 | 2021-08-20 | 富士电机株式会社 | 半导体装置 |

| DE102019133030B4 (de) * | 2019-12-04 | 2023-05-04 | Infineon Technologies Austria Ag | Bipolartransistor mit isoliertem gate enthaltende halbleitervorrichtung und herstellungsverfahren |

| JP7231065B2 (ja) * | 2020-01-17 | 2023-03-01 | 富士電機株式会社 | 半導体装置 |

| US11296213B2 (en) * | 2020-03-20 | 2022-04-05 | Infineon Technologies Austria Ag | Reverse-conducting igbt having a reduced forward recovery voltage |

| CN114902426A (zh) | 2020-07-15 | 2022-08-12 | 富士电机株式会社 | 半导体装置 |

| JP7475251B2 (ja) * | 2020-10-01 | 2024-04-26 | 三菱電機株式会社 | 半導体装置 |

| JP7494745B2 (ja) * | 2021-01-26 | 2024-06-04 | 三菱電機株式会社 | 半導体装置および半導体装置の製造方法 |

| JP7016437B2 (ja) * | 2021-02-25 | 2022-02-04 | 三菱電機株式会社 | 半導体スイッチング素子及びその製造方法 |

| WO2023106152A1 (ja) * | 2021-12-08 | 2023-06-15 | ローム株式会社 | 半導体装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007134625A (ja) | 2005-11-14 | 2007-05-31 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP4857948B2 (ja) | 2006-06-26 | 2012-01-18 | 株式会社デンソー | 半導体装置の製造方法 |

| JP5103830B2 (ja) * | 2006-08-28 | 2012-12-19 | 三菱電機株式会社 | 絶縁ゲート型半導体装置 |

| JP2008192737A (ja) * | 2007-02-02 | 2008-08-21 | Denso Corp | 半導体装置 |

| JP4840482B2 (ja) * | 2008-10-14 | 2011-12-21 | 株式会社デンソー | 半導体装置 |

| JP4957840B2 (ja) * | 2010-02-05 | 2012-06-20 | 株式会社デンソー | 絶縁ゲート型半導体装置 |

| JP5190485B2 (ja) * | 2010-04-02 | 2013-04-24 | 株式会社豊田中央研究所 | 半導体装置 |

| US8716746B2 (en) * | 2010-08-17 | 2014-05-06 | Denso Corporation | Semiconductor device |

| JP5321669B2 (ja) | 2010-11-25 | 2013-10-23 | 株式会社デンソー | 半導体装置 |

| JP5594276B2 (ja) | 2010-12-08 | 2014-09-24 | 株式会社デンソー | 絶縁ゲート型半導体装置 |

| JP5937413B2 (ja) * | 2011-06-15 | 2016-06-22 | 株式会社デンソー | 半導体装置 |

| JP5821320B2 (ja) | 2011-06-23 | 2015-11-24 | トヨタ自動車株式会社 | ダイオード |

| JP6127421B2 (ja) | 2012-09-24 | 2017-05-17 | 株式会社デンソー | 半導体装置 |

-

2014

- 2014-12-08 JP JP2014248139A patent/JP6421570B2/ja active Active

- 2014-12-16 WO PCT/JP2014/006244 patent/WO2015093038A1/ja active Application Filing

- 2014-12-16 US US15/105,664 patent/US9721945B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20170025410A1 (en) | 2017-01-26 |

| WO2015093038A1 (ja) | 2015-06-25 |

| US9721945B2 (en) | 2017-08-01 |

| JP2015135954A (ja) | 2015-07-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6421570B2 (ja) | 半導体装置 | |

| US8981470B2 (en) | Semiconductor device and manufacturing method of the same | |

| JP6365165B2 (ja) | 半導体装置の製造方法 | |

| JP4456013B2 (ja) | 半導体装置 | |

| JP5348276B2 (ja) | 半導体装置 | |

| JP6226786B2 (ja) | 半導体装置およびその製造方法 | |

| US20140203356A1 (en) | Semiconductor device including vertical semiconductor element | |

| JP5102411B2 (ja) | 半導体装置およびその製造方法 | |

| CN101375402B (zh) | 横向soi半导体器件及其制造方法 | |

| JP2012169386A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP2009289904A (ja) | 半導体装置 | |

| US8242537B2 (en) | IGBT with fast reverse recovery time rectifier and manufacturing method thereof | |

| JP2013062344A (ja) | 半導体装置およびその製造方法 | |

| JP6127421B2 (ja) | 半導体装置 | |

| US20170047316A1 (en) | Semiconductor device | |

| CN102208439B (zh) | 半导体装置及其制造方法 | |

| JP2013058575A (ja) | 半導体装置及びその製造方法 | |

| JP2010135677A (ja) | 半導体装置 | |

| US20160149029A1 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| JP2011243919A (ja) | 半導体装置およびその製造方法 | |

| WO2020075248A1 (ja) | 半導体装置及びその製造方法 | |

| JP6582762B2 (ja) | 半導体装置 | |

| JP2006294968A (ja) | 半導体装置およびその製造方法 | |

| JP2012049466A (ja) | 半導体装置およびその製造方法 | |

| JP7392613B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170308 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170428 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180404 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180918 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20181001 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6421570 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |