JP6149277B2 - 電子部品実装方法、電子部品実装システムおよび基板 - Google Patents

電子部品実装方法、電子部品実装システムおよび基板 Download PDFInfo

- Publication number

- JP6149277B2 JP6149277B2 JP2013507779A JP2013507779A JP6149277B2 JP 6149277 B2 JP6149277 B2 JP 6149277B2 JP 2013507779 A JP2013507779 A JP 2013507779A JP 2013507779 A JP2013507779 A JP 2013507779A JP 6149277 B2 JP6149277 B2 JP 6149277B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- layer

- electronic components

- chip

- predetermined

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000758 substrate Substances 0.000 title claims description 911

- 238000000034 method Methods 0.000 title claims description 230

- 229920005989 resin Polymers 0.000 claims description 266

- 239000011347 resin Substances 0.000 claims description 266

- 230000008569 process Effects 0.000 claims description 120

- 229910000679 solder Inorganic materials 0.000 claims description 93

- 238000005304 joining Methods 0.000 claims description 48

- 238000010438 heat treatment Methods 0.000 claims description 47

- 238000012545 processing Methods 0.000 claims description 45

- 238000003384 imaging method Methods 0.000 claims description 44

- 230000002950 deficient Effects 0.000 claims description 41

- 238000007689 inspection Methods 0.000 claims description 37

- 238000007517 polishing process Methods 0.000 claims description 21

- 239000011521 glass Substances 0.000 claims description 12

- 229920005992 thermoplastic resin Polymers 0.000 claims description 10

- 238000005498 polishing Methods 0.000 claims description 8

- 230000001678 irradiating effect Effects 0.000 claims description 7

- FGUUSXIOTUKUDN-IBGZPJMESA-N C1(=CC=CC=C1)N1C2=C(NC([C@H](C1)NC=1OC(=NN=1)C1=CC=CC=C1)=O)C=CC=C2 Chemical compound C1(=CC=CC=C1)N1C2=C(NC([C@H](C1)NC=1OC(=NN=1)C1=CC=CC=C1)=O)C=CC=C2 FGUUSXIOTUKUDN-IBGZPJMESA-N 0.000 claims description 6

- 230000006837 decompression Effects 0.000 claims description 4

- 238000010030 laminating Methods 0.000 claims description 4

- 238000000608 laser ablation Methods 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 632

- 239000013256 coordination polymer Substances 0.000 description 146

- 239000010949 copper Substances 0.000 description 64

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 51

- 229910052802 copper Inorganic materials 0.000 description 51

- 238000001994 activation Methods 0.000 description 41

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 28

- 238000012546 transfer Methods 0.000 description 25

- 230000004913 activation Effects 0.000 description 22

- 239000000126 substance Substances 0.000 description 17

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 16

- 239000007772 electrode material Substances 0.000 description 16

- 239000000463 material Substances 0.000 description 15

- 229910052786 argon Inorganic materials 0.000 description 14

- 102100031476 Cytochrome P450 1A1 Human genes 0.000 description 13

- 102100026533 Cytochrome P450 1A2 Human genes 0.000 description 13

- 101000941690 Homo sapiens Cytochrome P450 1A1 Proteins 0.000 description 13

- 101000855342 Homo sapiens Cytochrome P450 1A2 Proteins 0.000 description 13

- 238000002844 melting Methods 0.000 description 13

- 239000012298 atmosphere Substances 0.000 description 12

- 230000008018 melting Effects 0.000 description 12

- 230000032258 transport Effects 0.000 description 11

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 10

- 238000013459 approach Methods 0.000 description 9

- 238000010586 diagram Methods 0.000 description 9

- 230000003287 optical effect Effects 0.000 description 9

- 229910052710 silicon Inorganic materials 0.000 description 9

- 239000010703 silicon Substances 0.000 description 9

- 230000004907 flux Effects 0.000 description 8

- 229910052757 nitrogen Inorganic materials 0.000 description 8

- 239000012299 nitrogen atmosphere Substances 0.000 description 8

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 7

- 239000001301 oxygen Substances 0.000 description 7

- 229910052760 oxygen Inorganic materials 0.000 description 7

- 239000004065 semiconductor Substances 0.000 description 7

- 239000000853 adhesive Substances 0.000 description 6

- 230000001070 adhesive effect Effects 0.000 description 6

- 238000007796 conventional method Methods 0.000 description 6

- 239000007789 gas Substances 0.000 description 6

- 230000007246 mechanism Effects 0.000 description 6

- BDAGIHXWWSANSR-UHFFFAOYSA-N methanoic acid Natural products OC=O BDAGIHXWWSANSR-UHFFFAOYSA-N 0.000 description 6

- 230000035515 penetration Effects 0.000 description 6

- 238000000926 separation method Methods 0.000 description 6

- 239000002356 single layer Substances 0.000 description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 238000005286 illumination Methods 0.000 description 5

- 238000003475 lamination Methods 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 230000003647 oxidation Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- 239000007790 solid phase Substances 0.000 description 5

- 238000004140 cleaning Methods 0.000 description 4

- 238000001816 cooling Methods 0.000 description 4

- 230000007547 defect Effects 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 238000007747 plating Methods 0.000 description 4

- 238000004528 spin coating Methods 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- OSWFIVFLDKOXQC-UHFFFAOYSA-N 4-(3-methoxyphenyl)aniline Chemical compound COC1=CC=CC(C=2C=CC(N)=CC=2)=C1 OSWFIVFLDKOXQC-UHFFFAOYSA-N 0.000 description 3

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 101710201952 Photosystem II 22 kDa protein, chloroplastic Proteins 0.000 description 3

- 102100021941 Sorcin Human genes 0.000 description 3

- 101000741271 Sorghum bicolor Phosphoenolpyruvate carboxylase 1 Proteins 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000005520 cutting process Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 235000019253 formic acid Nutrition 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 238000010884 ion-beam technique Methods 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 238000003825 pressing Methods 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- 238000005476 soldering Methods 0.000 description 3

- 229920001187 thermosetting polymer Polymers 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- 230000008859 change Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 239000010432 diamond Substances 0.000 description 2

- 239000006185 dispersion Substances 0.000 description 2

- 238000006073 displacement reaction Methods 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 230000012447 hatching Effects 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- -1 oxygen ions Chemical class 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 229920001169 thermoplastic Polymers 0.000 description 2

- 239000004416 thermosoftening plastic Substances 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- 238000002679 ablation Methods 0.000 description 1

- 239000012190 activator Substances 0.000 description 1

- 229920006223 adhesive resin Polymers 0.000 description 1

- 238000005275 alloying Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- CUPFNGOKRMWUOO-UHFFFAOYSA-N hydron;difluoride Chemical compound F.F CUPFNGOKRMWUOO-UHFFFAOYSA-N 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 239000007791 liquid phase Substances 0.000 description 1

- 238000006386 neutralization reaction Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000003303 reheating Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 239000000523 sample Substances 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000002904 solvent Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/50—Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group H01L27/00 or H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67144—Apparatus for mounting on conductive members, e.g. leadframes or conductors on insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6835—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies

- H01L24/75—Apparatus for connecting with bump connectors or layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/94—Batch processes at wafer-level, i.e. with connecting carried out on a wafer comprising a plurality of undiced individual devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0652—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next and on each other, i.e. mixed assemblies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68354—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used to support diced chips prior to mounting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/68381—Details of chemical or physical process used for separating the auxiliary support from a device or wafer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05571—Disposition the external layer being disposed in a recess of the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05638—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05647—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/07—Structure, shape, material or disposition of the bonding areas after the connecting process

- H01L2224/08—Structure, shape, material or disposition of the bonding areas after the connecting process of an individual bonding area

- H01L2224/081—Disposition

- H01L2224/0812—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/08135—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding the bonding area connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/08145—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding the bonding area connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13023—Disposition the whole bump connector protruding from the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13025—Disposition the bump connector being disposed on a via connection of the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13147—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

- H01L2224/16146—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked the bump connector connecting to a via connection in the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/731—Location prior to the connecting process

- H01L2224/73101—Location prior to the connecting process on the same surface

- H01L2224/73103—Bump and layer connectors

- H01L2224/73104—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/7525—Means for applying energy, e.g. heating means

- H01L2224/753—Means for applying energy, e.g. heating means by means of pressure

- H01L2224/75301—Bonding head

- H01L2224/75314—Auxiliary members on the pressing surface

- H01L2224/75315—Elastomer inlay

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/757—Means for aligning

- H01L2224/75753—Means for optical alignment, e.g. sensors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/7598—Apparatus for connecting with bump connectors or layer connectors specially adapted for batch processes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/80009—Pre-treatment of the bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/80009—Pre-treatment of the bonding area

- H01L2224/8001—Cleaning the bonding area, e.g. oxide removal step, desmearing

- H01L2224/80013—Plasma cleaning

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/8034—Bonding interfaces of the bonding area

- H01L2224/80357—Bonding interfaces of the bonding area being flush with the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/808—Bonding techniques

- H01L2224/80894—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces

- H01L2224/80895—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces between electrically conductive surfaces, e.g. copper-copper direct bonding, surface activated bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/808—Bonding techniques

- H01L2224/80894—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces

- H01L2224/80896—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces between electrically insulating surfaces, e.g. oxide or nitride layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/8119—Arrangement of the bump connectors prior to mounting

- H01L2224/81191—Arrangement of the bump connectors prior to mounting wherein the bump connectors are disposed only on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/812—Applying energy for connecting

- H01L2224/81201—Compression bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81801—Soldering or alloying

- H01L2224/81815—Reflow soldering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81801—Soldering or alloying

- H01L2224/8182—Diffusion bonding

- H01L2224/8183—Solid-solid interdiffusion

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/94—Batch processes at wafer-level, i.e. with connecting carried out on a wafer comprising a plurality of undiced individual devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/95001—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips involving a temporary auxiliary member not forming part of the bonding apparatus, e.g. removable or sacrificial coating, film or substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/9512—Aligning the plurality of semiconductor or solid-state bodies

- H01L2224/95136—Aligning the plurality of semiconductor or solid-state bodies involving guiding structures, e.g. shape matching, spacers or supporting members

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06513—Bump or bump-like direct electrical connections between devices, e.g. flip-chip connection, solder bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00013—Fully indexed content

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15788—Glasses, e.g. amorphous oxides, nitrides or fluorides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

- H01L2924/3511—Warping

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Wire Bonding (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

- Die Bonding (AREA)

Description

本発明の第2の側面は、電子部品実装方法であって、a)仮基板である第iの基板(ただし、iは1以上の整数)上に第iの樹脂層を形成するステップと、b)第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で前記第iの樹脂層に平面配置して仮固定するステップと、c)所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合するステップと、d)前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離するステップと、f)ステップd)の後、前記第i層の複数の電子部品が前記所定の基板上に平面的に配置された後に、前記所定の基板上に配置された状態での前記第i層の複数の電子部品のそれぞれに関する第1の接合状態検査を行うステップと、を備え、前記ステップf)の後、値iをインクリメントして再び前記ステップa)〜前記ステップd)が実行され、前記値iのインクリメント後に再び実行される前記ステップb)においては、前記第1の接合状態検査にて不良であると判定された電子部品に対応する位置を除外して、前記第i層の複数の電子部品が第iの樹脂層に平面配置されることを特徴とする。

本発明の第3の側面は、電子部品実装方法であって、a)仮基板である第iの基板(ただし、iは1以上の整数)上に第iの樹脂層を形成するステップと、b)第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で前記第iの樹脂層に平面配置して仮固定するステップと、c)所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合するステップと、d)前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離するステップと、e)値iをインクリメントして前記ステップa)と前記ステップb)と前記ステップc)と前記ステップd)とを繰り返し実行し、前記所定の基板上の複数の平面位置において電子部品を複数層に積層するステップと、をさらに備え、前記値iのインクリメント前の前記ステップd)は、前記第i層の複数の電子部品から前記第iの基板が分離された後において、前記第i層の複数の電子部品における露出面に対して、平坦化研磨処理を実行するステップ、を有し、前記値iのインクリメント後の前記ステップc)は、前記第iの基板に配置された前記第i層の複数の電子部品と前記所定の基板に配置された第(i−1)層の複数の電子部品とを対向させた状態で前記第iの基板と前記所定の基板とを相対的に接近させることによって、前記第i層の複数の電子部品と前記第(i−1)層の複数の電子部品とを相対的に接近させ、前記第i層の複数の電子部品と前記平坦化研磨処理が施された前記第(i−1)層の複数の電子部品とをそれぞれ接合するステップ、を有することを特徴とする。

本発明の第5の側面は、電子部品実装システムであって、仮基板である第iの基板(ただし、iは1以上の整数)上に形成された第iの樹脂層に、第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で載置し、第i層の複数の電子部品を前記第iの樹脂層に平面配置して仮固定する第1のボンディング手段と、所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する第2のボンディング手段と、前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離する分離手段と、前記第i層の複数の電子部品が前記所定の基板上に平面的に配置された後に、前記所定の基板上に配置された状態での前記第i層の複数の電子部品のそれぞれに関する第1の接合状態検査を行う検査手段と、を備え、前記第2のボンディング手段は、前記所定の基板と前記第1のボンディング手段によって前記第iの樹脂層に仮固定された前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する動作を、値iをインクリメントしつつ繰り返し行うことによって、前記所定の基板上の複数の平面位置のそれぞれにおいて複数の電子部品を積層し、前記値iのインクリメント後に前記第i層の複数の電子部品が前記第iの樹脂層に平面配置して仮固定される際には、前記第(i−1)層の複数の電子部品のうち前記第1の接合状態検査にて不良であると判定された電子部品に対応する位置を除外して、前記第i層の複数の電子部品が第iの樹脂層に平面配置されることを特徴とする。

本発明の第6の側面は、電子部品実装システムであって、仮基板である第iの基板(ただし、iは1以上の整数)上に形成された第iの樹脂層に、第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で載置し、第i層の複数の電子部品を前記第iの樹脂層に平面配置して仮固定する第1のボンディング手段と、所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する第2のボンディング手段と、前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離する分離手段と、前記第i層の複数の電子部品から前記第iの基板が分離された後において、前記第i層の複数の電子部品における露出面に対して、平坦化研磨処理を実行する研磨手段と、を備え、前記第2のボンディング手段は、前記所定の基板と前記第1のボンディング手段によって前記第iの樹脂層に仮固定された前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する動作を、値iをインクリメントしつつ繰り返し行うことによって、前記所定の基板上の複数の平面位置のそれぞれにおいて複数の電子部品を積層し、前記値iのインクリメント後において、前記第iの基板に配置された前記第i層の複数の電子部品と前記所定の基板に配置された第(i−1)層の複数の電子部品とを対向させた状態で前記第iの基板と前記所定の基板とを相対的に接近させることによって、前記第i層の複数の電子部品と前記第(i−1)層の複数の電子部品とを相対的に接近させ、前記第i層の複数の電子部品と前記平坦化研磨処理が施された前記第(i−1)層の複数の電子部品とをそれぞれ接合することを特徴とする。

図1〜図3は、本実施形態に係る電子部品実装動作を示すフローチャートである。これらの図に示すような各工程が行われることにより、基板WA上の複数の平面位置において複数層の電子部品(ここでは半導体チップ(単にチップとも称する))が積層される。図26では、3層の複数のチップが積層される状態が例示されている。なお、ここでは、各チップ(詳細にはシリコン(Si)チップ)CPに貫通電極VAが設けられている場合を想定する(図33参照)。ただし、各図においては、便宜上、貫通電極VAの図示を適宜省略する。また、本発明は、各チップCPに貫通電極VAが設けられない場合にも適用可能である。

まず、チップ実装システム1の構成について説明する。

後述するように、この実施形態(ステップS12,S22参照)では、アライメントマークMC1,MC2(図8等参照)を用いて、各チップCP(CPi)が水平方向において位置決めされて仮基板WTi上に載置される。

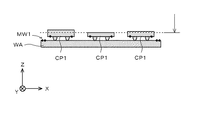

また、後述するように、この実施形態(ステップS13,S23参照)では、アライメントマークMW1,MW2を用いて、両基板WA,WTiが水平方向において位置決めされる。アライメントマークMW1,MW2は、基板WA,WTiの相対位置を調整するためのマークであり、基板位置調整用マークとも称される。

次に、図1〜図3のフローチャート等を参照しつつ、この実施形態におけるチップ実装動作(電子部品実装動作)について詳細に説明する。ここでは、複数のチップが3層に積層される場合を例示する。なお、これに限定されず、2層に積層されるようにしてもよく、あるいは4層以上に積層されるようにしてもよい。あるいは、基板WA上に1層のチップ層のみが設けられるようにしてもよい。

最初に、第1層のチップの積層動作(ステップS10)(図1および図2参照)が次のようにして行われる。

詳細には、まずステップS11(図2)において、仮基板である基板WT1(図6)上に樹脂層RS1が形成される(図7)。なお、仮基板WT1には、マークMC2,MW2が樹脂層RS1の形成前に予め付されている。この樹脂層RSiは、光(赤外光等)を透過する。

次に、ステップS12において、第1層の複数のチップCP1がフェイスアップ状態で樹脂層RS1に平面配置されて仮固定される(図8〜図12等参照)。ここで、各チップCPの「フェイスアップ状態」は、当該各チップCPの接合面(例えば、ハンダバンプBUが付された側の面)が上側を向いた状態である。

その後、ステップS13の処理が実行される。

つぎに、ステップS14において、「デボンド処理」が実行される。具体的には、複数のチップCP1が基板WAの所定位置にそれぞれ載置(接合)された状態を維持しつつ、複数のチップCP1から基板WT1が分離される。

つぎに、第2層のチップの積層動作(ステップS20)(図1および図3参照)が次のようにして行われる。上述したように、第2層に関するステップS21〜S24の対応処理は、第1層に関するステップS11〜S14の各処理とそれぞれ同様の処理である。ただし、ステップS13,S14では第1層のチップCPiが基板WA上に直接的に載置等されるのに対して、第i層(ここではi=2)に関するステップS23,S24においては既に積層済みの第(i−1)層のチップCP(i−1)に対して第i層のチップCPiが載置等される。

ところで、上述のような従来技術(先行技術文献1)を利用することによれば、基板(ウエハ)上に単一層の複数の半導体チップ(以下単にチップとも称する)を平面的に配置してボンディングする技術(単層COW(Chip On Wafer)実装技術とも称する)として、次のような技術が考えられる。

上述したように、ステップS12,S22においては、次のようなレベリング工程が実行されることが好ましい。

また、この発明は上述の内容に限定されるものではなく、様々な改変が可能である。

たとえば、上記実施形態等においては、樹脂層RSが熱可塑性樹脂で形成される場合を例示したが、これに限定されず、樹脂層RSが光硬化性樹脂(紫外線硬化樹脂等)で形成されるようにしてもよい。

また、上記実施形態等においては、ステップS24(S14)のデボンド処理として、樹脂層RSを温度T4に加熱して溶融させ、仮基板WTiをチップCPから剥離する技術を例示したがこれに限定されない。

上記実施形態等においては、ステップS13,S23において、下ステージ51側のヒータにより基板WAが加熱され且つ上ステージ53側のヒータにより仮基板WTiが加熱されることによって、各チップCPiのハンダバンプBUが溶融され、基板WA上に複数のチップCPiが接合される場合が例示されているが、これに限定されない。

また、上記実施形態等においては、ステップS14の後にそのままステップS21が実行される場合が例示されているが、これに限定されない。たとえば、第1層に関するステップS14と第2層に関するステップS21との間(あるいは、第i層に関するステップS24とその次の第(i+1)層に関するステップS21との間)にアンダーフィル工程が設けられるようにしてもよい。すなわち、デボンド処理後にアンダーフィル工程を設けるようにしてもよい。

また、上記実施形態等においては、赤外光を用いて位置認識用の画像が取得される場合が例示されているが、これに限定されない。たとえば、可視光を用いて位置認識用の画像が取得されるようにしてもよい。

また、上記実施形態等におけるハンダ接合(ステップS13,S23)は、次のようにして実現されるようにしてもよい。なお、ここでは、上記実施形態と同様に、各チップCPには貫通電極(例えば銅(Cu)などで構成される)VAが設けられ、且つ、当該貫通電極VAの表面にハンダバンプBUが設けられる場合を想定する(図33参照)。また、ここでは、ハンダバンプBUが貫通電極VAの上側表面にのみ設けられる場合を例示するが、これに限定されず、ハンダバンプBUが貫通電極VAの下側表面にも(すなわち上下両側に)設けられるようにしてもよい。あるいは、ハンダバンプBUが貫通電極VAの下側表面にのみ設けられるようにしてもよい。

上記実施形態等においては、ハンダ接合を例示したが、これに限定されず、その他の接合にも本発明を適用することが可能である。たとえば、ハンダ(ハンダバンプ)を介さずに、電極材料(例えば銅(Cu))同士を直接的に接合(直接接合)する場合にも本発明を適用することもできる。ここでは、各チップCPには貫通電極(例えば銅(Cu)などで構成される)VAが設けられ、当該貫通電極VAの表面に銅(Cu)ポストPSがさらに突出して設けられる場合を例示する(図36参照)。

ここで、原子ビーム照射処理においては、イオン化された特定物質(アルゴン等)が電界で加速された後に、ビーム照射部内で供給された電荷と直ちに結合して、その電気特性が中和される。そして、電気的に中和された特定物質が高速で被接合物へと向かう。

また、上記においては、ビーム照射(アルゴンボンバードメント等)による表面活性化処理を伴って接合処理が行われる場合を例示したが、これに限定されない。たとえば、親水化処理による表面活性化処理を伴って接合処理が行われる場合にも本発明を適用することができる。以下では、このような改変例について説明する。

また、上記において、チップ供給装置10からCOWボンディング装置30へと供給される各チップCPは、良品であることが予め確認されることが好ましい。具体的には、チップ供給装置10において複数のチップCPのそれぞれについて良品チップであるか不良品チップであるかが判定され(良否判定がなされ)、良品であると判定されたチップ(すなわち良品チップ)のみがCOWボンディング装置30へと供給されることが好ましい。

また、上記実施形態等においては、鉛直方向(上下方向)におけるチップ位置を調整することなどによるレベリング処理(ステップS12,S22)を例示したが、これに限定されない。たとえば、各層のチップから電極部分が突出して設けられる場合には、次のような手法を用いて、複数のチップの相互間において、各電極部分の先端部の上下方向の位置を揃えるようにしてもよい。ここでは、各チップCPの上側表面に銅(Cu)ポストPSがさらに突出して設けられる場合を例示する(図52参照)。また、図52においては、チップ相互間においてチップの厚みのバラツキおよびバンプ高さのバラツキが存在する状況が示されている。なお、銅ポストPSは、チップCPに設けられた貫通電極の上側に配置されてもよく、あるいは、貫通電極以外の部分の上側に配置されてもよい。

また、上記実施形態においては、最終的なチップサイズSZ(基板からの切り出し後の完成品チップのサイズ(次述))とは異なるサイズ(平面サイズ)のチップCPiが、基板WA上に配置されている。詳細には、最終的なチップサイズSZよりも小さなサイズ(平面サイズ)のチップCPiが載置されている。

また、上記実施形態等においては、電極材料として、銅(Cu)が主に例示されているが、これに限定されず、電極材料として、その他の金属材料(金(Au)、銀(Ag)等)が用いられてもよい。

10 チップ供給装置

30 ボンディング装置

31 ステージ

33 ボンディング部

33H ヘッド部

35,35a,35b,55,55a,55b 撮像部

36,56 位置認識部

39 チップ搬送部

50 ボンディング装置

51 下ステージ

53 上ステージ

70 搬送部

71 搬送ロボット

90 搬出入部

CPi チップ

MC1,MC2 チップ位置調整用マーク(部品位置調整用マーク)

MW1,MW2 基板位置調整用マーク

PL 平面部材

RSi 樹脂層

RU アンダーフィル樹脂

WA 基板

WTi 仮基板

Claims (30)

- 電子部品実装方法であって、

a)仮基板である第iの基板(ただし、iは1以上の整数)上に第iの樹脂層を形成するステップと、

b)第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で前記第iの樹脂層に平面配置して仮固定するステップと、

c)所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合するステップと、

d)前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離するステップと、

e)値iをインクリメントして前記ステップa)と前記ステップb)と前記ステップc)と前記ステップd)とを繰り返し実行し、前記所定の基板上の複数の平面位置において電子部品を複数層に積層するステップと、

を備え、

前記第i層の複数の電子部品は、それぞれ、第1の種類の部品位置調整用マークを有しており、

前記第iの基板は、前記第i層の複数の電子部品のそれぞれに対応して、第2の種類の部品位置調整用マークを有しており、

前記ステップb)においては、

前記第i層の複数の電子部品のそれぞれにおける前記第1の種類の部品位置調整用マークと前記第i層の複数の電子部品のそれぞれに対応して前記第iの基板に設けられた前記第2の種類の部品位置調整用マークとを用いて前記第i層の複数の電子部品のそれぞれが前記第iの基板平面に平行な方向において位置決めされ、前記第i層の複数の電子部品のそれぞれが前記第iの基板上の前記第iの樹脂層に載置され、

前記所定の基板は、第1の種類の基板位置調整用マークを有しており、

前記第iの基板は、第2の種類の基板位置調整用マークを有しており、

前記ステップc)において、前記所定の基板における前記第1の種類の基板位置調整用マークと前記第iの基板における前記第2の種類の基板位置調整用マークとを用いて前記所定の基板と前記第iの基板とが前記第iの基板平面に平行な方向において位置決めされることによって、前記所定の基板に保持された前記の複数の電子部品のそれぞれと前記第iの基板に保持された前記第i層の複数の電子部品のそれぞれとの位置関係が調整されることを特徴とする電子部品実装方法。 - 請求項1に記載の電子部品実装方法において、

前記第2の種類の基板位置調整用マークは、前記第1の種類の基板位置調整用マークとは異なる形状のマークとして設けられることを特徴とする電子部品実装方法。 - 請求項1または請求項2に記載の電子部品実装方法において、

前記第2の種類の基板位置調整用マークは、前記第1の種類の基板位置調整用マークの基準位置から所定量オフセットされた位置に設けられることを特徴とする電子部品実装方法。 - 請求項1〜請求項3のいずれかに記載の電子部品実装方法において、

前記第2の種類の部品位置調整用マークは、前記第1の種類の部品位置調整用マークとは異なる形状のマークとして設けられることを特徴とする電子部品実装方法。 - 請求項1〜請求項4のいずれかに記載の電子部品実装方法において、

前記第2の種類の部品位置調整用マークは、前記第1の種類の部品位置調整用マークの基準位置から所定量オフセットされた位置に設けられることを特徴とする電子部品実装方法。 - 請求項1〜請求項5のいずれかに記載の電子部品実装方法において、

前記第i層の複数の電子部品は、それぞれ、前記第1の種類の部品位置調整用マークを当該電子部品内における同じ位置に有していることを特徴とする電子部品実装方法。 - 請求項1〜請求項6のいずれかに記載の電子部品実装方法において、

前記第iの基板は、ガラス基板であり、

前記第1の種類の部品位置調整用マークは、前記第i層の複数の電子部品のそれぞれにおいて前記第iの基板側の面に設けられ、

前記ステップb)においては、

前記第i層の複数の電子部品のそれぞれにおける前記第1の種類の部品位置調整用マークと前記第i層の複数の電子部品のそれぞれに対応して前記第iの基板に設けられた前記第2の種類の部品位置調整用マークとを可視光により撮像した画像を用いて、前記第i層の複数の電子部品のそれぞれが前記第iの基板平面に平行な方向において位置決めされ、前記第i層の複数の電子部品のそれぞれが前記第iの基板上の前記第iの樹脂層に載置されることを特徴とする電子部品実装方法。 - 請求項1〜請求項6のいずれかに記載の電子部品実装方法において、

前記ステップb)においては、

前記第i層の複数の電子部品のそれぞれにおける前記第1の種類の部品位置調整用マークと前記第i層の複数の電子部品のそれぞれに対応して前記第iの基板に設けられた前記第2の種類の部品位置調整用マークとを赤外光により撮像した画像を用いて、前記第i層の複数の電子部品のそれぞれが前記第iの基板平面に平行な方向において位置決めされ、前記第i層の複数の電子部品のそれぞれが前記第iの基板上の前記第iの樹脂層に載置されることを特徴とする電子部品実装方法。 - 電子部品実装方法であって、

a)仮基板である第iの基板(ただし、iは1以上の整数)上に第iの樹脂層を形成するステップと、

b)第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で前記第iの樹脂層に平面配置して仮固定するステップと、

c)所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合するステップと、

d)前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離するステップと、

f)ステップd)の後、前記第i層の複数の電子部品が前記所定の基板上に平面的に配置された後に、前記所定の基板上に配置された状態での前記第i層の複数の電子部品のそれぞれに関する第1の接合状態検査を行うステップと、

を備え、

前記ステップf)の後、値iをインクリメントして再び前記ステップa)〜前記ステップd)が実行され、

前記値iのインクリメント後に再び実行される前記ステップb)においては、前記第1の接合状態検査にて不良であると判定された電子部品に対応する位置を除外して、前記第i層の複数の電子部品が第iの樹脂層に平面配置されることを特徴とする電子部品実装方法。 - 請求項9に記載の電子部品実装方法において、

前記ステップf)においては、前記第i層の複数の電子部品であって良品判定済みの複数の電子部品が前記所定の基板上に平面的に配置された後に、前記所定の基板上に配置された状態での前記第i層の複数の電子部品のそれぞれに関する前記第1の接合状態検査が行われ、

前記値iのインクリメント後に再び実行される前記ステップb)においては、前記第1の接合状態検査にて不良であると判定された電子部品に対応する位置を除外して、前記第i層の複数の電子部品であって良品判定済みの複数の電子部品が前記第iの樹脂層に平面配置されることを特徴とする電子部品実装方法。 - 請求項9または請求項10に記載の電子部品実装方法において、

前記ステップf)の後、値iをインクリメントして前記ステップa)〜前記ステップd)および前記ステップf)が再び実行され、

前記値iのインクリメント後に再び実行される前記ステップf)においては、前記所定の基板上に配置された状態での前記第i層の複数の電子部品のそれぞれに関する第2の接合状態検査が実行され、

前記値iのインクリメント後に再び実行される前記ステップd)の後、値iを再インクリメントして前記ステップa)〜前記ステップd)が再び実行され、

前記値iの再インクリメント後に再び実行される前記ステップb)においては、前記第2の接合状態検査にて不良であると判定された電子部品に対応する位置をも除外して、前記第i層の複数の電子部品が前記第iの樹脂層に平面配置されることを特徴とする電子部品実装方法。 - 請求項11に記載の電子部品実装方法において、

前記値iの再インクリメント後に再び実行される前記ステップb)においては、前記第2の接合状態検査にて不良であると判定された電子部品に対応する位置をも除外して、前記第i層の複数の電子部品であって良品判定済みの複数の電子部品が前記第iの樹脂層に平面配置されることを特徴とする電子部品実装方法。 - 電子部品実装方法であって、

a)仮基板である第iの基板(ただし、iは1以上の整数)上に第iの樹脂層を形成するステップと、

b)第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で前記第iの樹脂層に平面配置して仮固定するステップと、

c)所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合するステップと、

d)前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離するステップと、

e)値iをインクリメントして前記ステップa)と前記ステップb)と前記ステップc)と前記ステップd)とを繰り返し実行し、前記所定の基板上の複数の平面位置において電子部品を複数層に積層するステップと、

をさらに備え、

前記値iのインクリメント前の前記ステップd)は、

前記第i層の複数の電子部品から前記第iの基板が分離された後において、前記第i層の複数の電子部品における露出面に対して、平坦化研磨処理を実行するステップ、

を有し、

前記値iのインクリメント後の前記ステップc)は、

前記第iの基板に配置された前記第i層の複数の電子部品と前記所定の基板に配置された第(i−1)層の複数の電子部品とを対向させた状態で前記第iの基板と前記所定の基板とを相対的に接近させることによって、前記第i層の複数の電子部品と前記第(i−1)層の複数の電子部品とを相対的に接近させ、前記第i層の複数の電子部品と前記平坦化研磨処理が施された前記第(i−1)層の複数の電子部品とをそれぞれ接合するステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項13のいずれかに記載の電子部品実装方法において、

前記ステップc)は、値i=1のとき、

前記所定の基板と前記第1の基板に配置された前記第1層の複数の電子部品とを対向させた状態で前記所定の基板と前記第1の基板とを相対的に接近させることによって、前記所定の基板と前記第1層の複数の電子部品とを相対的に接近させ、前記第1層の複数の電子部品を前記所定の基板上の所定の位置にそれぞれ載置し、前記所定の基板と前記第1層の複数の電子部品とを接合するステップ、

を有し、

前記ステップd)は、値i=1のとき、

前記第1層の複数の電子部品が前記所定の基板に接合された状態を維持しつつ、前記第1層の複数の電子部品から前記第1の基板を分離するステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項14のいずれかに記載の電子部品実装方法において、

前記ステップc)は、値iが2以上の整数のとき、

前記所定の基板に配置された第(i−1)層の複数の電子部品と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記第(i−1)層の複数の電子部品と前記第i層の複数の電子部品とを相対的に接近させ、前記第(i−1)層の複数の電子部品と前記第i層の複数の電子部品とをそれぞれ接合するステップ、

を有し、

前記ステップd)は、値iが2以上の整数のとき、

前記第i層の複数の電子部品が前記第(i−1)層の複数の電子部品にそれぞれ接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離するステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項15のいずれかに記載の電子部品実装方法において、

前記ステップd)は、

d−1)光硬化性樹脂で形成された前記第iの樹脂層に対してレーザアブレーション処理を施すことによって、前記第i層の複数の電子部品から前記第iの基板を分離するステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項15のいずれかに記載の電子部品実装方法において、

前記ステップd)は、

d−2)熱可塑性樹脂で形成された前記第iの樹脂層を加熱することによって、前記第i層の複数の電子部品から前記第iの基板を分離するステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項15のいずれかに記載の電子部品実装方法において、

前記ステップd)は、

d−3)熱可塑性樹脂で形成された前記第iの樹脂層に紫外線を照射した後に前記第iの樹脂層を加熱することによって、前記第i層の複数の電子部品から前記第iの基板を分離するステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項18のいずれかに記載の電子部品実装方法において、

前記ステップa)は、

a−1)スピンコータによって前記第iの基板上に樹脂を塗布するステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項18のいずれかに記載の電子部品実装方法において、

前記ステップa)は、

a−2)前記第iの基板上に樹脂シートを貼付するステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項20のいずれかに記載の電子部品実装方法において、

前記ステップc)においては、前記所定の基板および前記第iの基板のいずれか一方の上下を反転して、前記所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とが対向した状態で、前記所定の基板と前記第iの基板とが相対的に接近されることを特徴とする電子部品実装方法。 - 請求項1〜請求項13のいずれかに記載の電子部品実装方法において、

前記ステップc)においては、前記所定の基板に対する前記第i層の複数の電子部品の接合がハンダ接合処理を伴って行われるとともに、前記ハンダ接合処理が所定の温度プロファイルで実行されることを特徴とする電子部品実装方法。 - 請求項1〜請求項13のいずれかに記載の電子部品実装方法において、

前記ステップc)においては、前記所定の基板に対する前記第i層の複数の電子部品の接合がハンダ接合処理を伴って行われ、当該ハンダ接合処理は、前記第i層の複数の電子部品が収容される処理空間において、所定期間にわたる減圧処理を伴って実行されることを特徴とする電子部品実装方法。 - 請求項1〜請求項23のいずれかに記載の電子部品実装方法において、

前記ステップc)は、

前記所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させ、且つ、前記第i層の複数の電子部品を加熱した状態で、前記所定の基板と前記第iの基板とのアライメント動作を行って前記第i層の複数の電子部品のそれぞれを前記第iの基板平面に平行な方向において位置決めするステップ、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項13のいずれかに記載の電子部品実装方法において、

前記ステップc)は、

前記所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させるとともに前記第i層の複数の電子部品を加熱して接合用のハンダバンプを溶融させ、且つ、前記所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを接触させた状態で、前記所定の基板と前記第iの基板とのアライメント動作を行って前記第i層の複数の電子部品のそれぞれを前記第iの基板平面に平行な方向において位置決めするステップと、

を有することを特徴とする電子部品実装方法。 - 請求項1〜請求項13のいずれかに記載の電子部品実装方法において、

前記ステップc)は、値iが2以上の整数のとき、

前記所定の基板に配置された第(i−1)層の複数の電子部品と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させるとともに前記第i層の複数の電子部品を加熱して接合用のハンダバンプを溶融させ、且つ、前記第(i−1)層の複数の電子部品と前記第i層の複数の電子部品とを接触させた状態で、前記所定の基板と前記第iの基板とのアライメント動作を行って前記第i層の複数の電子部品のそれぞれを前記第iの基板平面に平行な方向において位置決めするステップと、

を有することを特徴とする電子部品実装方法。 - 電子部品実装システムであって、

仮基板である第iの基板(ただし、iは1以上の整数)上に形成された第iの樹脂層に、第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で載置し、第i層の複数の電子部品を前記第iの樹脂層に平面配置して仮固定する第1のボンディング手段と、

所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する第2のボンディング手段と、

前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離する分離手段と、

を備え、

前記第2のボンディング手段は、前記所定の基板と前記第1のボンディング手段によって前記第iの樹脂層に仮固定された前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する動作を、値iをインクリメントしつつ繰り返し行うことによって、前記所定の基板上の複数の平面位置のそれぞれにおいて複数の電子部品を積層し、

前記第i層の複数の電子部品は、それぞれ、第1の種類の部品位置調整用マークを有しており、

前記第iの基板は、前記第i層の複数の電子部品のそれぞれに対応して、第2の種類の部品位置調整用マークを有しており、

前記第1のボンディング手段は、

前記第i層の複数の電子部品を構成する各電子部品における前記第1の種類の部品位置調整用マークと前記各電子部品に対応して前記第iの基板に設けられた前記第2の種類の部品位置調整用マークとを用いて、前記第iの基板平面に平行な方向における前記各電子部品の位置を認識する第1の位置認識手段と、

前記第1の位置認識手段によって認識された前記各電子部品の前記位置に基づいて前記第iの基板と前記各電子部品とを相対的に駆動し、前記第iの基板上における前記各電子部品の位置を調整する第1の駆動手段と、

を有し、

前記所定の基板は、第1の種類の基板位置調整用マークを有しており、

前記第iの基板は、前記第1の種類の基板位置調整用マークとは異なる形状の第2の種類の基板位置調整用マークを有しており、

前記第2のボンディング手段は、

前記所定の基板における前記第1の種類の基板位置調整用マークと前記第iの基板における前記第2の種類の基板位置調整用マークとを用いて、前記第iの基板平面に平行な方向における前記所定の基板と前記第iの基板との相対位置関係を求める第2の位置認識手段と、

第2の位置認識手段によって求められた前記相対位置関係に基づいて前記所定の基板と前記第iの基板とを相対的に駆動し、前記所定の基板と前記第iの基板との位置関係を調整する第2の駆動手段と、

を有することを特徴とする電子部品実装システム。 - 電子部品実装システムであって、

仮基板である第iの基板(ただし、iは1以上の整数)上に形成された第iの樹脂層に、第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で載置し、第i層の複数の電子部品を前記第iの樹脂層に平面配置して仮固定する第1のボンディング手段と、

所定の基板と前記第iの基板に仮固定された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する第2のボンディング手段と、

前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離する分離手段と、

前記第i層の複数の電子部品が前記所定の基板上に平面的に配置された後に、前記所定の基板上に配置された状態での前記第i層の複数の電子部品のそれぞれに関する第1の接合状態検査を行う検査手段と、

を備え、

前記第2のボンディング手段は、

前記所定の基板と前記第1のボンディング手段によって前記第iの樹脂層に仮固定された前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する動作を、値iをインクリメントしつつ繰り返し行うことによって、前記所定の基板上の複数の平面位置のそれぞれにおいて複数の電子部品を積層し、

前記値iのインクリメント後に前記第i層の複数の電子部品が前記第iの樹脂層に平面配置して仮固定される際には、前記第(i−1)層の複数の電子部品のうち前記第1の接合状態検査にて不良であると判定された電子部品に対応する位置を除外して、前記第i層の複数の電子部品が第iの樹脂層に平面配置されることを特徴とする電子部品実装システム。 - 電子部品実装システムであって、

仮基板である第iの基板(ただし、iは1以上の整数)上に形成された第iの樹脂層に、第i層の複数の電子部品をその接合面を上側に向けたフェイスアップ状態で載置し、第i層の複数の電子部品を前記第iの樹脂層に平面配置して仮固定する第1のボンディング手段と、

所定の基板と前記第iの基板に配置された前記第i層の複数の電子部品とを対向させた状態で前記所定の基板と前記第iの基板とを相対的に接近させることによって、前記所定の基板と前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する第2のボンディング手段と、

前記第i層の複数の電子部品が前記所定の基板に対して接合された状態を維持しつつ、前記第i層の複数の電子部品から前記第iの基板を分離する分離手段と、

前記第i層の複数の電子部品から前記第iの基板が分離された後において、前記第i層の複数の電子部品における露出面に対して、平坦化研磨処理を実行する研磨手段と、

を備え、

前記第2のボンディング手段は、

前記所定の基板と前記第1のボンディング手段によって前記第iの樹脂層に仮固定された前記第i層の複数の電子部品とを相対的に接近させ、前記所定の基板と前記第i層の複数の電子部品とを接合する動作を、値iをインクリメントしつつ繰り返し行うことによって、前記所定の基板上の複数の平面位置のそれぞれにおいて複数の電子部品を積層し、

前記値iのインクリメント後において、前記第iの基板に配置された前記第i層の複数の電子部品と前記所定の基板に配置された第(i−1)層の複数の電子部品とを対向させた状態で前記第iの基板と前記所定の基板とを相対的に接近させることによって、前記第i層の複数の電子部品と前記第(i−1)層の複数の電子部品とを相対的に接近させ、前記第i層の複数の電子部品と前記平坦化研磨処理が施された前記第(i−1)層の複数の電子部品とをそれぞれ接合することを特徴とする電子部品実装システム。 - 請求項1に記載の電子部品実装方法における前記第iの基板として用いられる基板であって、

前記第2の種類の部品位置調整用マークと、

前記第2の種類の基板位置調整用マークと、

を有することを特徴とする基板。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011076616 | 2011-03-30 | ||

| JP2011076616 | 2011-03-30 | ||

| JP2011159429 | 2011-07-20 | ||

| JP2011159429 | 2011-07-20 | ||

| PCT/JP2012/058567 WO2012133760A1 (ja) | 2011-03-30 | 2012-03-30 | 電子部品実装方法、電子部品実装システムおよび基板 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017050510A Division JP6383449B2 (ja) | 2011-03-30 | 2017-03-15 | 電子部品実装方法および電子部品実装システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2012133760A1 JPWO2012133760A1 (ja) | 2014-07-28 |

| JP6149277B2 true JP6149277B2 (ja) | 2017-06-21 |

Family

ID=46931457

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013507779A Active JP6149277B2 (ja) | 2011-03-30 | 2012-03-30 | 電子部品実装方法、電子部品実装システムおよび基板 |