JP4950051B2 - 遠隔でテストチャンネルをバッファリングする装置 - Google Patents

遠隔でテストチャンネルをバッファリングする装置 Download PDFInfo

- Publication number

- JP4950051B2 JP4950051B2 JP2007531379A JP2007531379A JP4950051B2 JP 4950051 B2 JP4950051 B2 JP 4950051B2 JP 2007531379 A JP2007531379 A JP 2007531379A JP 2007531379 A JP2007531379 A JP 2007531379A JP 4950051 B2 JP4950051 B2 JP 4950051B2

- Authority

- JP

- Japan

- Prior art keywords

- buffer

- test

- isolation

- delay

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/30—Marginal testing, e.g. by varying supply voltage

- G01R31/3004—Current or voltage test

- G01R31/3008—Quiescent current [IDDQ] test or leakage current test

Description

Claims (19)

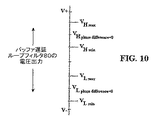

- 電子デバイスをテストするためのテストシステムのテストチャネルにおいて提供された分離バッファと、

該テストチャネルにおいて、該分離バッファの信号入力と出力との間に提供されたバッファバイパス素子と、

該電子デバイスに接触するように構成されたテストプローブと

を含み、

該テストチャネルは、該電子デバイスのテストを制御するためにテスタの1つの端部において電気的に接続しており、該テストプローブの別の端部において終端するように構成され、

前記バッファバイパス素子が伝送ゲートを含み、

信号が、トライステートバッファが動作可能にされるときには前記伝送ゲートを動作不能にするために、該トライステートバッファが動作不能にされるときには該伝送ゲートを動作可能にするために提供される、装置。 - 前記バッファバイパス素子がトランジスタを含む、請求項1に記載の装置。

- 前記トランジスタが、前記分離バッファの入力と出力との間に接続されたソースドレイン経路を有するCMOS装置である、請求項2に記載の装置。

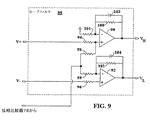

- 電子デバイスをテストするためのテストチャネルにおいて提供された分離バッファと、

該分離バッファと並列に提供されたバッファバイパス素子と、

該電子デバイスのテストを制御するために該テストチャネルをテスタに電気的に接続するように構成された電気的インターフェースと、

該電子デバイスに接触するように構成されたテストプローブと

を含み、

該電気的インターフェースは、該テストプローブに電気的に接続され、

前記バッファバイパス素子が伝送ゲートを含み、

信号が、トライステートバッファが動作可能にされるときには前記伝送ゲートを動作不能にするために、該トライステートバッファが動作不能にされるときには該伝送ゲートを動作可能にするために提供される、装置。 - 前記テストチャネルはそれぞれ、前記テストプローブのうちの1つにおいて終端している、請求項4に記載の装置。

- 前記プローブ接触点は弾力性のばねを含む、請求項5に記載の装置。

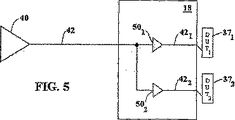

- 電子デバイスをテストするためのテスタに電気的に接続するように構成された信号ラインと、

該電子デバイスのうちの1つに接触するように構成された、該信号ラインから複数のテストプローブまでの複数の分岐と、

分離バッファであって、該分離バッファのそれぞれは該分岐のうちの一つにおいて提供される、分離バッファと、

バッファバイパス素子であって、該バッファバイパス素子それぞれは該分離バッファのうちの1つと電気的に並列に接続されている、バッファバイパス素子と

を含み、

前記バッファバイパス素子は伝送ゲートを含み、

前記信号ラインにおいて提供されるさらなるバッファであって、前記分離バッファの入力に接続される出力を有するさらなるバッファをさらに含み、前記バッファバイパス素子は該さらなるバッファの入力と該分離バッファのうちの1つの出力とに電気的に接続され、

前記さらなるバッファはトライステートバッファを含み、

信号が、前記トライステートバッファが動作可能にされるときには前記伝送ゲートを動作不能にするため、該トライステートバッファが動作不能とされるときには該伝送ゲートを動作可能とするために提供される、装置。 - 前記分離バッファに可変遅延制御入力を提供する出力を有する遅延制御回路をさらに含む、請求項7に記載の装置。

- それぞれのバッファバイパス素子は、前記分離バッファのうちの1つの入力および出力に電気的に接続されている、請求項7に記載の装置。

- 前記テストプローブは、弾力性のばね構造を含んでいる、請求項7に記載の装置。

- 前記テストプローブは、弾力性のばね構造を含んでいる、請求項4に記載の装置。

- 前記テストチャネルのうちの少なくとも1つは、複数の分岐信号ラインに電気的に接続された共通の信号ラインを含んでおり、それぞれの分岐信号ラインは、前記プローブのうちの1つにおいて終端している、請求項4に記載の装置。

- 前記テストチャネルのうちの前記少なくとも1つにおいて、前記分離バッファのうちの1つが前記分岐ラインのそれぞれに提供される、請求項12に記載の装置。

- 前記テストチャネルのうちの前記少なくとも1つにおいて、それぞれのバイパス素子は、前記分離バッファのうちの1つの入力および出力に接続されている、請求項13に記載の装置。

- 前記テストチャネルのうちの前記少なくとも1つの前記共通の信号ラインにおいて提供されたさらなる分離バッファをさらに含んでいる、請求項13に記載の装置。

- 前記テストチャネルのうちの前記少なくとも1つにおいて、

前記さらなる分離バッファの出力は、前記分離バッファの入力に接続されており、

それぞれのバイパス素子は、該さらなる分離バッファの入力と該分離バッファのうちの1つの出力とに接続されている、請求項15に記載の装置。 - 前記テストチャネルは、複数の分岐信号ラインに電気的に接続された共通の信号ラインを含んでおり、前記装置は、

テストされるべき複数の電子デバイスに接触するように構成された複数のテストプローブであって、それぞれの分岐は、該複数のテストプローブのうちの1つにおいて終端している、複数のテストプローブと、

該分岐のうちのそれぞれの分岐において提供されている複数の分離バッファと、

複数のバッファバイパス素子であって、それぞれのバッファバイパス素子は、該分離バッファのうちの1つと電気的に並列に接続されている、バッファバイパス素子と

をさらに含んでいる、請求項1に記載の装置。 - テスタをさらに含んでおり、該テスタは、前記テストチャネルを介して前記電子デバイスにテスト信号を提供することによって、該電子デバイスのテストを制御するように構成されている、請求項17に記載の装置。

- 前記テストプローブは、弾力性のばね構造を含んでいる、請求項17に記載の装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/937,470 | 2004-09-09 | ||

| US10/937,470 US7453258B2 (en) | 2004-09-09 | 2004-09-09 | Method and apparatus for remotely buffering test channels |

| PCT/US2005/032202 WO2006029340A2 (en) | 2004-09-09 | 2005-09-08 | Method and apparatus for remotely buffering test channels |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008512682A JP2008512682A (ja) | 2008-04-24 |

| JP2008512682A5 JP2008512682A5 (ja) | 2008-10-23 |

| JP4950051B2 true JP4950051B2 (ja) | 2012-06-13 |

Family

ID=35995565

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007531379A Expired - Fee Related JP4950051B2 (ja) | 2004-09-09 | 2005-09-08 | 遠隔でテストチャンネルをバッファリングする装置 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US7453258B2 (ja) |

| EP (1) | EP1794607A2 (ja) |

| JP (1) | JP4950051B2 (ja) |

| KR (1) | KR101207090B1 (ja) |

| CN (2) | CN101115998B (ja) |

| TW (1) | TWI401447B (ja) |

| WO (1) | WO2006029340A2 (ja) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7262611B2 (en) * | 2000-03-17 | 2007-08-28 | Formfactor, Inc. | Apparatuses and methods for planarizing a semiconductor contactor |

| US7365556B2 (en) * | 2004-09-02 | 2008-04-29 | Texas Instruments Incorporated | Semiconductor device testing |

| US7453258B2 (en) | 2004-09-09 | 2008-11-18 | Formfactor, Inc. | Method and apparatus for remotely buffering test channels |

| US7262624B2 (en) * | 2004-12-21 | 2007-08-28 | Formfactor, Inc. | Bi-directional buffer for interfacing test system channel |

| US7653356B2 (en) * | 2005-09-15 | 2010-01-26 | Silicon Laboratories Inc. | System and method for reducing spurious emissions in a wireless communication device including a testing apparatus |

| US7890822B2 (en) * | 2006-09-29 | 2011-02-15 | Teradyne, Inc. | Tester input/output sharing |

| US7852094B2 (en) * | 2006-12-06 | 2010-12-14 | Formfactor, Inc. | Sharing resources in a system for testing semiconductor devices |

| JP2009071533A (ja) * | 2007-09-12 | 2009-04-02 | Advantest Corp | 差動信号伝送装置および試験装置 |

| US20090085598A1 (en) * | 2007-09-28 | 2009-04-02 | Qimonda Ag | Integrated circuit test system and method with test driver sharing |

| JP2011226854A (ja) * | 2010-04-16 | 2011-11-10 | Advantest Corp | 電圧を供給する装置 |

| KR101133030B1 (ko) * | 2010-12-08 | 2012-04-04 | 인텔릭스(주) | 디스크리트 자가 진단 시스템 |

| JP2014520905A (ja) | 2011-06-29 | 2014-08-25 | ダウ グローバル テクノロジーズ エルエルシー | 難燃性組成物、難燃性組成物を含む繊維強化ポリウレタン系複合材物品およびその使用 |

| US8680888B2 (en) * | 2011-12-15 | 2014-03-25 | Micron Technologies, Inc. | Methods and systems for routing in a state machine |

| US8928383B2 (en) * | 2013-03-15 | 2015-01-06 | Analog Devices, Inc. | Integrated delayed clock for high speed isolated SPI communication |

| TWI467195B (zh) * | 2013-06-17 | 2015-01-01 | Ardentek Corp | 測試系統之接觸界面檢測法 |

| CN104931759B (zh) * | 2014-03-21 | 2018-07-06 | 中芯国际集成电路制造(上海)有限公司 | 一种标准单元漏电流的测试电路及测试方法 |

| US9696376B2 (en) * | 2015-03-12 | 2017-07-04 | Globalfoundries Inc. | Leakage testing of integrated circuits using a logarithmic transducer and a voltmeter |

| US10302677B2 (en) * | 2015-04-29 | 2019-05-28 | Kla-Tencor Corporation | Multiple pin probes with support for performing parallel measurements |

| KR102576210B1 (ko) | 2016-07-05 | 2023-09-08 | 삼성전자주식회사 | 반도체 장치 |

| JP6782134B2 (ja) * | 2016-09-26 | 2020-11-11 | ラピスセミコンダクタ株式会社 | スキャン回路、集合スキャン回路、半導体装置、および半導体装置の検査方法 |

| KR102336181B1 (ko) | 2017-06-07 | 2021-12-07 | 삼성전자주식회사 | 누설 전류 측정 회로, 이를 포함하는 집적 회로 및 시스템 |

| US20190250208A1 (en) * | 2018-02-09 | 2019-08-15 | Qualcomm Incorporated | Apparatus and method for detecting damage to an integrated circuit |

| KR102549004B1 (ko) * | 2018-06-22 | 2023-06-29 | 삼성디스플레이 주식회사 | 점등 검사 장치, 점등 검사 방법 및 점등 검사 시스템 |

| US11313903B2 (en) * | 2020-09-30 | 2022-04-26 | Analog Devices, Inc. | Pin driver and test equipment calibration |

| CN113866589A (zh) * | 2021-09-03 | 2021-12-31 | 长江存储科技有限责任公司 | 芯片测试装置及芯片测试方法 |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0812529B2 (ja) * | 1989-06-07 | 1996-02-07 | キヤノン株式会社 | 定着装置 |

| JP3005250B2 (ja) * | 1989-06-30 | 2000-01-31 | テキサス インスツルメンツ インコーポレイテツド | バスモニター集積回路 |

| JPH05172900A (ja) * | 1991-12-20 | 1993-07-13 | Yokogawa Electric Corp | パルス伝送路 |

| JPH0720206A (ja) * | 1993-06-23 | 1995-01-24 | Kawasaki Steel Corp | 発振回路用出力回路 |

| JP3080847B2 (ja) * | 1994-10-05 | 2000-08-28 | 日本電気株式会社 | 半導体記憶装置 |

| US5594694A (en) | 1995-07-28 | 1997-01-14 | Micron Quantum Devices, Inc. | Memory circuit with switch for selectively connecting an input/output pad directly to a nonvolatile memory cell |

| US5790459A (en) | 1995-08-04 | 1998-08-04 | Micron Quantum Devices, Inc. | Memory circuit for performing threshold voltage tests on cells of a memory array |

| WO1997024806A1 (en) * | 1995-12-28 | 1997-07-10 | Advantest Corporation | Semiconductor integrated circuit device with delay error correcting circuit |

| US6239604B1 (en) * | 1996-10-04 | 2001-05-29 | U.S. Philips Corporation | Method for inspecting an integrated circuit by measuring a voltage drop in a supply line of sub-circuit thereof |

| US5966318A (en) * | 1996-12-17 | 1999-10-12 | Raytheon Company | Nondestructive readout memory utilizing ferroelectric capacitors isolated from bitlines by buffer amplifiers |

| JPH11231022A (ja) * | 1998-02-13 | 1999-08-27 | Matsushita Electric Ind Co Ltd | 半導体装置の検査方法および検査装置 |

| JPH11326441A (ja) * | 1998-05-20 | 1999-11-26 | Advantest Corp | 半導体試験装置 |

| US6055287A (en) * | 1998-05-26 | 2000-04-25 | Mcewan; Thomas E. | Phase-comparator-less delay locked loop |

| US6442674B1 (en) * | 1998-12-30 | 2002-08-27 | Intel Corporation | Method and system for bypassing a fill buffer located along a first instruction path |

| US6157231A (en) * | 1999-03-19 | 2000-12-05 | Credence System Corporation | Delay stabilization system for an integrated circuit |

| US6534826B2 (en) * | 1999-04-30 | 2003-03-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US6377067B1 (en) * | 2000-02-01 | 2002-04-23 | Winbond Electronics Corporation | Testing method for buried strap and deep trench leakage current |

| US6603323B1 (en) * | 2000-07-10 | 2003-08-05 | Formfactor, Inc. | Closed-grid bus architecture for wafer interconnect structure |

| JP4717295B2 (ja) * | 2000-10-04 | 2011-07-06 | 株式会社半導体エネルギー研究所 | ドライエッチング装置及びエッチング方法 |

| US6445228B1 (en) * | 2001-08-28 | 2002-09-03 | Xilinx, Inc. | Programmable even-number clock divider circuit with duty cycle correction and optional phase shift |

| JP2003279625A (ja) * | 2002-03-27 | 2003-10-02 | Toshiba Microelectronics Corp | 半導体集積回路 |

| JP3703794B2 (ja) * | 2002-11-05 | 2005-10-05 | 日本電子材料株式会社 | プローブおよびプローブカード |

| JP2004170079A (ja) * | 2002-11-15 | 2004-06-17 | Hitachi Electronics Eng Co Ltd | 試験波形供給方法、半導体試験方法、ドライバ、及び半導体試験装置 |

| US7250772B2 (en) * | 2002-11-19 | 2007-07-31 | University Of Utah Research Foundation | Method and apparatus for characterizing a signal path carrying an operational signal |

| JP2004198269A (ja) * | 2002-12-19 | 2004-07-15 | Hitachi Ltd | 半導体集積回路装置 |

| US7154259B2 (en) | 2003-10-23 | 2006-12-26 | Formfactor, Inc. | Isolation buffers with controlled equal time delays |

| US7453258B2 (en) | 2004-09-09 | 2008-11-18 | Formfactor, Inc. | Method and apparatus for remotely buffering test channels |

-

2004

- 2004-09-09 US US10/937,470 patent/US7453258B2/en not_active Expired - Fee Related

-

2005

- 2005-09-08 WO PCT/US2005/032202 patent/WO2006029340A2/en active Application Filing

- 2005-09-08 CN CN2005800297017A patent/CN101115998B/zh not_active Expired - Fee Related

- 2005-09-08 EP EP05795133A patent/EP1794607A2/en not_active Withdrawn

- 2005-09-08 JP JP2007531379A patent/JP4950051B2/ja not_active Expired - Fee Related

- 2005-09-08 KR KR1020077008051A patent/KR101207090B1/ko not_active IP Right Cessation

- 2005-09-08 CN CN201010536273XA patent/CN102053221A/zh active Pending

- 2005-09-09 TW TW094131190A patent/TWI401447B/zh not_active IP Right Cessation

-

2008

- 2008-11-18 US US12/273,408 patent/US7825652B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR101207090B1 (ko) | 2012-11-30 |

| WO2006029340A2 (en) | 2006-03-16 |

| CN101115998B (zh) | 2011-01-05 |

| KR20070100695A (ko) | 2007-10-11 |

| TW200624841A (en) | 2006-07-16 |

| CN101115998A (zh) | 2008-01-30 |

| US7453258B2 (en) | 2008-11-18 |

| TWI401447B (zh) | 2013-07-11 |

| JP2008512682A (ja) | 2008-04-24 |

| US20060049820A1 (en) | 2006-03-09 |

| US20090132190A1 (en) | 2009-05-21 |

| CN102053221A (zh) | 2011-05-11 |

| EP1794607A2 (en) | 2007-06-13 |

| US7825652B2 (en) | 2010-11-02 |

| WO2006029340A3 (en) | 2007-07-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4950051B2 (ja) | 遠隔でテストチャンネルをバッファリングする装置 | |

| US7362092B2 (en) | Isolation buffers with controlled equal time delays | |

| US6586921B1 (en) | Method and circuit for testing DC parameters of circuit input and output nodes | |

| US5617035A (en) | Method for testing integrated devices | |

| US7109736B2 (en) | System for measuring signal path resistance for an integrated circuit tester interconnect structure | |

| JP4255284B2 (ja) | 差動動作のためのシングル・エンド・チャネルの較正 | |

| KR100731344B1 (ko) | 자동화된 테스트 장비에서 테스트 및 교정하기 위한 회로및 그 방법 | |

| US9551741B2 (en) | Current tests for I/O interface connectors | |

| US10481204B2 (en) | Methods and systems to measure a signal on an integrated circuit die | |

| US6262585B1 (en) | Apparatus for I/O leakage self-test in an integrated circuit | |

| US11567121B2 (en) | Integrated circuit with embedded testing circuitry | |

| JP3558425B2 (ja) | 信号切換装置およびスイッチ回路 | |

| WO2008056206A1 (en) | Method for testing noise immunity of an integrated circuit and a device having noise immunity testing capabilities | |

| Muhtaroglu et al. | I/O self-leakage test | |

| Lanzoni et al. | An experimental study of testing techniques for bridging faults in CMOS ICs | |

| Rajinita et al. | Improving testability and fault analysis in low level design |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080903 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080903 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100527 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110204 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110914 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110920 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20111220 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20111228 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120119 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120209 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120308 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150316 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |