JP4813743B2 - 画像表示装置の製造方法 - Google Patents

画像表示装置の製造方法 Download PDFInfo

- Publication number

- JP4813743B2 JP4813743B2 JP2002215239A JP2002215239A JP4813743B2 JP 4813743 B2 JP4813743 B2 JP 4813743B2 JP 2002215239 A JP2002215239 A JP 2002215239A JP 2002215239 A JP2002215239 A JP 2002215239A JP 4813743 B2 JP4813743 B2 JP 4813743B2

- Authority

- JP

- Japan

- Prior art keywords

- image display

- active matrix

- display device

- silicon film

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 41

- 239000010408 film Substances 0.000 claims description 194

- 239000000758 substrate Substances 0.000 claims description 137

- 239000011159 matrix material Substances 0.000 claims description 76

- 239000010409 thin film Substances 0.000 claims description 72

- 238000000034 method Methods 0.000 claims description 64

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 55

- 229910021419 crystalline silicon Inorganic materials 0.000 claims description 41

- 239000004973 liquid crystal related substance Substances 0.000 claims description 27

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 26

- 238000002407 reforming Methods 0.000 claims description 20

- 239000010410 layer Substances 0.000 claims description 17

- 230000001678 irradiating effect Effects 0.000 claims description 12

- 238000000206 photolithography Methods 0.000 claims description 7

- 230000001681 protective effect Effects 0.000 claims description 3

- 230000002093 peripheral effect Effects 0.000 claims 2

- 229920005591 polysilicon Polymers 0.000 description 43

- 229910052710 silicon Inorganic materials 0.000 description 43

- 239000010703 silicon Substances 0.000 description 43

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 42

- 239000013078 crystal Substances 0.000 description 40

- 102100036464 Activated RNA polymerase II transcriptional coactivator p15 Human genes 0.000 description 36

- 101000713904 Homo sapiens Activated RNA polymerase II transcriptional coactivator p15 Proteins 0.000 description 36

- 229910004444 SUB1 Inorganic materials 0.000 description 36

- 238000010586 diagram Methods 0.000 description 34

- 238000005070 sampling Methods 0.000 description 23

- 230000008569 process Effects 0.000 description 22

- 108091006146 Channels Proteins 0.000 description 17

- 239000004065 semiconductor Substances 0.000 description 17

- 101150034590 DAR1 gene Proteins 0.000 description 12

- 101100393304 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) GPD1 gene Proteins 0.000 description 12

- 229910004438 SUB2 Inorganic materials 0.000 description 9

- 101100311330 Schizosaccharomyces pombe (strain 972 / ATCC 24843) uap56 gene Proteins 0.000 description 9

- 238000012986 modification Methods 0.000 description 9

- 230000004048 modification Effects 0.000 description 9

- 101150018444 sub2 gene Proteins 0.000 description 9

- 101100330724 Arabidopsis thaliana DAR3 gene Proteins 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 8

- 239000000463 material Substances 0.000 description 8

- 229910052751 metal Inorganic materials 0.000 description 8

- 239000002184 metal Substances 0.000 description 8

- 239000007787 solid Substances 0.000 description 8

- BWSIKGOGLDNQBZ-LURJTMIESA-N (2s)-2-(methoxymethyl)pyrrolidin-1-amine Chemical compound COC[C@@H]1CCCN1N BWSIKGOGLDNQBZ-LURJTMIESA-N 0.000 description 7

- 101100330723 Arabidopsis thaliana DAR2 gene Proteins 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 230000003287 optical effect Effects 0.000 description 7

- 229920002120 photoresistant polymer Polymers 0.000 description 7

- 238000002425 crystallisation Methods 0.000 description 6

- 230000008025 crystallization Effects 0.000 description 6

- 239000012535 impurity Substances 0.000 description 6

- 102100036725 Epithelial discoidin domain-containing receptor 1 Human genes 0.000 description 5

- 101710131668 Epithelial discoidin domain-containing receptor 1 Proteins 0.000 description 5

- 238000002513 implantation Methods 0.000 description 5

- 238000005530 etching Methods 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 238000007789 sealing Methods 0.000 description 4

- 239000011856 silicon-based particle Substances 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 210000002858 crystal cell Anatomy 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000001965 increasing effect Effects 0.000 description 3

- 238000005224 laser annealing Methods 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 3

- 102100038742 Cytochrome P450 2A13 Human genes 0.000 description 2

- 101100224481 Dictyostelium discoideum pole gene Proteins 0.000 description 2

- LFERELMXERXKKQ-KMXXXSRASA-N Fenugreekine Chemical compound NC(=O)C1=CC=CC([C@H]2[C@@H]([C@H](O)[C@@H](COP(O)(=O)OP(O)(=O)OC[C@@H]3[C@H]([C@@H](O)[C@@H](O3)N3C4=NC=NC(N)=C4N=C3)O)O2)O)=N1 LFERELMXERXKKQ-KMXXXSRASA-N 0.000 description 2

- 101000957389 Homo sapiens Cytochrome P450 2A13 Proteins 0.000 description 2

- 101150046160 POL1 gene Proteins 0.000 description 2

- 101150110488 POL2 gene Proteins 0.000 description 2

- 238000001069 Raman spectroscopy Methods 0.000 description 2

- 101100117436 Thermus aquaticus polA gene Proteins 0.000 description 2

- 229910009372 YVO4 Inorganic materials 0.000 description 2

- 238000012790 confirmation Methods 0.000 description 2

- 230000001276 controlling effect Effects 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000001887 electron backscatter diffraction Methods 0.000 description 2

- 238000004050 hot filament vapor deposition Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000000608 laser ablation Methods 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 150000003376 silicon Chemical class 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- LJSMMWFTVBPRDS-UHFFFAOYSA-N 5,6-diamino-3',6'-bis(diethylamino)spiro[2-benzofuran-3,9'-xanthene]-1-one Chemical compound O1C(=O)C2=CC(N)=C(N)C=C2C21C1=CC=C(N(CC)CC)C=C1OC1=CC(N(CC)CC)=CC=C21 LJSMMWFTVBPRDS-UHFFFAOYSA-N 0.000 description 1

- ALKWEXBKAHPJAQ-NAKRPEOUSA-N Asn-Leu-Asp-Asp Chemical compound NC(=O)C[C@H](N)C(=O)N[C@@H](CC(C)C)C(=O)N[C@@H](CC(O)=O)C(=O)N[C@@H](CC(O)=O)C(O)=O ALKWEXBKAHPJAQ-NAKRPEOUSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 238000004435 EPR spectroscopy Methods 0.000 description 1

- 108091006149 Electron carriers Proteins 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 108090000699 N-Type Calcium Channels Proteins 0.000 description 1

- 102000004129 N-Type Calcium Channels Human genes 0.000 description 1

- 108010075750 P-Type Calcium Channels Proteins 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 101710120101 Photosystem I reaction center subunit XI Proteins 0.000 description 1

- 101710127295 Photosystem I reaction center subunit XI, chloroplastic Proteins 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000003197 catalytic effect Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000002050 diffraction method Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 238000002003 electron diffraction Methods 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 230000031700 light absorption Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 238000002715 modification method Methods 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000011158 quantitative evaluation Methods 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 230000027756 respiratory electron transport chain Effects 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

- H01L21/02686—Pulsed laser beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02422—Non-crystalline insulating materials, e.g. glass, polymers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02488—Insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/02502—Layer structure consisting of two layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02587—Structure

- H01L21/0259—Microstructure

- H01L21/02595—Microstructure polycrystalline

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02609—Crystal orientation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

- H01L21/02683—Continuous wave laser beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02691—Scanning of a beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

- H01L27/1274—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor

- H01L27/1285—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor using control of the annealing or irradiation parameters, e.g. using different scanning direction or intensity for different transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13454—Drivers integrated on the active matrix substrate

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Optics & Photonics (AREA)

- Ceramic Engineering (AREA)

- Materials Engineering (AREA)

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

- Liquid Crystal (AREA)

Description

【発明の属する技術分野】

本発明は、画像表示装置に係り、特に絶縁基板上に形成された半導体膜の結晶構造をレーザ光で改質し、改質された半導体膜に駆動回路のアクティブ素子を形成した画像表示装置の製造方法に関する。

【0002】

【従来の技術】

マトリクス配列された画素の駆動素子として薄膜トランジスタ等のアクティブ素子を用いたアクティブ・マトリクス型表示装置(またはアクティブ・マトリクス型駆動方式の画像表示装置、あるいは単にディスプレイ装置とも称する)が広く使用されている。この種の画像表示装置の多くは、半導体膜としてシリコン膜を用いて形成された薄膜トランジスタ(TFT)等のアクティブ素子で構成された多数の画素回路と駆動回路とを絶縁基板上に配置することで良質の画像を表示することができる。ここでは、上記アクティブ素子として、その典型例である薄膜トランジスタを例として説明する。

【0003】

半導体膜としてこれまで一般的に用いられてきた非晶質シリコン半導体膜(アモルファスシリコン半導体膜)を用いた薄膜トランジスタでは、そのキャリア(電子またはホール)移動度に代表される薄膜トランジスタの性能に限界があるために、高速、高機能が要求される回路を構成することは困難であった。より優れた画像品質を提供するのに必要な高移動度の薄膜トランジスタの実現にはアモルファスシリコン膜(以下、非晶質シリコン膜とも称する)をあらかじめポリシリコン膜(以下、多結晶シリコン膜とも称する)に改質(結晶化)し、ポリシリコン膜を用いて薄膜トランジスタを形成するのが有効である。この改質のためにはエキシマレーザ光等のレーザ光を照射してアモルファスシリコン膜をアニールする手法が用いられている。

【0004】

この種のレーザアニールに関する手法については例えば、T.C.Angelis et al; Effect of Excimer Laser Annealing on the Structural and Electrical Properties of Polycrystalline Silicon Thin-Film Transistor, J. Appl. Phy., Vol.86, pp4600-4606,1999 あるいは H. Kuriyama et al; Lateral Grain Growth of Poly-Si Films with a Specific Orientation by an Eximer Laser Annealing Method, Jpn. J. Appl. Phy., Vol.32, pp6190-6195,1993 あるいは K.Suzuki et al; Correlation between Power Density Fluctuation and Grain Size Distribution of Laser annealed Poly-Crystalline Silicon, SPIE Conference, Vol.3618, pp310-319, 1999 などに詳細に述べられている。

【0005】

エキシマレーザ光照射を使用するアモルファスシリコン膜の結晶化による改質方法を図34で説明する。図34は最も一般的なエキシマパルスレーザ光照射を走査することによるアモルファスシリコン膜の結晶化方法の説明図であり、図34(a)は照射される半導体層を形成した絶縁基板の構成、同(b)はレーザ光の照射で改質される状態を示す。この絶縁基板にはガラスやセラミックスが用いられる。

【0006】

図34において、絶縁基板SUB上に下地膜(SiN等、図示せず)を介して堆積したアモルファスシリコン膜ASIに幅が数nm乃至数100nm程度の線状のエキシマレーザ光ELAを照射し、矢印で示したように一方向(x方向)に沿って1乃至数パルス毎に照射位置を移動する走査を行うことによりアモルファスシリコン膜ASIをアニールし、絶縁基板SUB全体のアモルファスシリコン膜ASIをポリシリコン膜PSIに改質する。この方法で改質したポリシリコン膜PSIにエッチング、配線形成、イオン打ち込み等の種々の加工を施して、各々の画素部あるいは駆動部に薄膜トランジスタ等のアクティブ素子を有する回路を形成する。この絶縁基板を用いて液晶表示装置や有機EL表示装置等のアクティブ・マトリクス方式の画像表示装置を製造する。

【0007】

図35は図34におけるレーザ光照射部の部分平面図と薄膜トランジスタ部の構成例を説明する要部平面図である。図35(a)に示したように、レーザ光照射部には0.05乃至0.5μm程度の結晶化した多数のシリコン粒子(多結晶シリコン)PSIが面内均一に成長する。各シリコン粒子(すなわちシリコン結晶)の粒界の殆どはそれぞれが自身で閉じている(全方向に隣接するシリコン粒子の間に粒界が存在する)。図35(a)に□で囲んだ部分を個々の薄膜トランジスタ等のアクティブ素子のための半導体膜となるトランジスタ部TRAとなる。従来のシリコン膜の改質はこのような結晶化を意味している。

【0008】

上記の改質されたシリコン膜(ポリシリコン膜PSI)を利用して画素回路を形成するには図35(b)に示すように結晶化したシリコンの一部をトランジスタ部として利用するために、図35(a)のトランジスタ部TRAとなる部分を除く不要部をエッチングで除去してシリコン膜の島(アイランド)を形成し、このアイランドPSI−L上にゲート絶縁膜(図示せず)、ゲート電極GT、ソース電極SD1、ドレイン電極SD2を配置して薄膜トランジスタを製造するのである。

【0009】

【発明が解決しようとする課題】

上記の従来技術においては、絶縁基板上に改質したポリシリコン膜で薄膜トランジスタを形成して動作性能のよい薄膜トランジスタ等のアクティブ素子を配置するものであるが、前記したように、ポリシリコン膜の結晶を用いた例えば薄膜トランジスタのチャネルにおけるキャリア移動度(電子移動度あるいはホール移動度、以下では単に電子移動度とも称する)には限界がある。すなわち、エキシマレーザ光の照射で結晶化したポリシリコン膜の結晶の粒界は前記図34に示したように粒状をなす個々の結晶毎に閉じており、ソース電極とドレイン電極の間のチャネルにおけるキャリアの更に大きな移動度を実現するには限界がある。近年の高精細化に伴って駆動回路の回路密度も稠密となっている。このような駆動回路における回路密度が極めて大きい薄膜トランジスタ等のアクティブ素子には、さらに大きなキャリア移動度が要求される。

【0010】

本発明の目的は、マトリクス状に配置された画素部を駆動するための駆動素子に高速の移動度で動作する高性能の薄膜トランジスタ回路等を有するアクティブ・マトリクス基板を備えた画像表示装置の製造方法を提供することにある。なお、本発明は、画像表示装置のための絶縁基板に形成されたポリシコン半導体膜の改質に限るものではなく、他の基板例えばシリコンウエハ上に形成された同様の半導体膜の改質等にも同様に適用できる。

【0011】

【課題を解決するための手段】

上記の課題を解決するための手段として、本発明は 絶縁基板の全域に形成されたアモルファスシリコン膜の全面にエキシマレーザ光を照射してポリシリコン膜に改質し、あるいはポリシリコン膜を形成した絶縁基板を作成し、この絶縁基板の画素領域の周辺に配置される駆動回路領域のポリシリコン膜に固体レーザを用いたパルス変調レーザ光あるいは擬似CWレーザ光を選択的に照射しながら所定の方向に走査して、当該走査方向に成長した結晶が連続した粒界を持つ如く結晶サイズが大きく改質された略帯状結晶シリコン膜の不連続改質領域を形成する。

【0012】

不連続改質領域は概して矩形状とし、この矩形状の不連続改質領域内に駆動回路等の所要の回路を作り込む際に、当該回路を構成する薄膜トランジスタ等のアクティブ素子のチャネル方向が前記略帯状結晶シリコン膜の粒界方向に略並行となるようにする。なお、本発明では、上記のパルス変調レーザ光の照射で略帯状結晶シリコン膜の不連続改質領域を作成する手法をSELAX(Selectively Enlarging Laser Crystallization)と称する。

【0013】

また、本発明による画像表示装置の製造では、好ましくは、往復動作を用いて駆動回路部のポリシリコン膜に選択的にレーザビーム(以下、レーザ光、あるいは単にレーザとも称する)を照射する上記SELAX処理により、上記略帯状結晶シリコン膜の不連続改質領域を形成する。この不連続改質領域は駆動回路領域の全領域に形成することもできるが、当該駆動回路の回路密度等を考慮した必要な領域に略矩形状に形成するのが推奨される。特に、略矩形状の不連続改質領域を駆動回路領域の上記必要な領域に主としてに配列して形成することにより、レーザ光照射処理の効率と個々の略帯状結晶シリコン膜の膜質を全ての不連続改質領域で均一化できる。

【0014】

本発明による略帯状結晶シリコン膜は、レーザ光の走査方向と直角方向を幅とし、上記走査方向を長さとしたとき、例えば、幅が0.1μm乃至10μm、長さが1μm乃至100μm程度の単結晶の集合体である。このような略帯状結晶シリコン膜を用いることで良好なキャリア移動度を確保できる。その値は、電子移動度としておよそ300cm2 /V・s以上、望ましくは500cm2 /V・s以上にもなる。

【0015】

一方、従来のエキシマレーザを用いたシリコン膜の改質では、レーザ光照射部には0.05μm乃至0.5μm程度の結晶化した多数のシリコン粒子(ポリシリコン)がランダムに成長する。このようなポリシリコン膜の電子移動度としてはおよそ200cm2 /V・s以下、平均的には120cm2 /V・s程度である。これは、アモルファスシリコン膜の電子移動度である1cm2 /V・s以下に比べれば性能は向上しているが、本発明の略帯状結晶シリコン膜からなる不連続改質領域は上記の電子移動度よりもさらに高速の電子移動度を有する。

【0016】

本発明による画像表示装置を構成する絶縁基板の画素領域に有するシリコン膜はCVD法あるいはスパッタ法で形成されたアモルファスシリコン膜をエキシマレーザ光の照射で改質したポリシリコン膜であり、駆動回路領域に有するシリコン膜はポリシリコン膜に固体レーザを用いたパルス変調レーザ光あるいは擬似CWレーザ光の照射でさらに結晶構造が改質された略帯状結晶シリコン膜である。なお、ここで言うパルス変調とは、パルスの幅あるいはパルスとパルスの間隔、もしくはこれら両者を変化させる変調方法を意味する。具体的には、CW(連続発振)レーザを電気光学変調(Electro−Optic変調:EO変調)することでこのような変調パルスを得ることができる。

【0017】

本発明では絶縁基板上の駆動回路領域のポリシリコン膜に選択的にパルス変調レーザ光を走査しながら照射することで、選択的に照射される領域、すなわち略帯状結晶シリコン膜に改質された領域が絶縁基板面に沿って略矩形状の配列に形成される。以下、この略矩形状の領域を仮想タイルとも称する。なお、上記の仮想タイルと当該仮想タイルを構成する個々の改質領域は、その後に形成される回路部分に対応させて複数個ごとにブロック化して配列される。このような仮想タイルを採用することで、前記した効果に加えて薄膜トランジスタ等を形成する過程でエッチングで除去される半導体膜の領域にはレーザ光を照射する必要がなくなり、不要な作業を大幅に低減できる。

【0018】

本発明でアモルファスシリコン膜をポリシリコン膜に改質する場合に使用するエキシマレーザ、または発振波長200nm乃至1200nmの連続発振固体レーザ、あるいは同周波数範囲の固体パルスレーザであることが好ましい。連続発振レーザ光はアニール対象であるアモルファスシリコンに対して吸収のある波長、即ち紫外波長から可視波長が望ましく、より具体的にはArレーザ、Nd:YAGレーザ、Nd:YVO4レーザ、Nd:YLFレーザの第二高調波及び第三高調波又は第四高調波などが適用可能である。しかし、出力の大きさ及び安定性を考慮すると、LD(レーザダイオード)励起Nd:YAGレーザの第二高調波(波長532nm)あるいはNd:YVO4レーザの第二高調波(波長532nm)が最も望ましい。かかる波長の上、下限はシリコン膜の光吸収が効率よく生じる範囲と経済的に入手できる安定なレーザ光源の兼ね合いから定まるものである。なおこのポリシリコン膜は、膜の成膜の段階で形成することもできる。例えば、cat−CVD(カタリティック ベーパー デポジッション)法で直に基板あるいは下地上に形成することができる。

【0019】

本発明の固体レーザはシリコン膜に吸収するレーザ光を安定に供給できるとともに、ガスレーザに特有なガス交換作業や発信部の劣化等の経済負担が少ないのが特徴であり、経済的にシリコン膜を改質する手段として好ましい。しかし、本発明では該レーザが波長150nm乃至400nmのエキシマレーザであることを積極的に排除するものではない。

【0020】

本発明でポリシリコン膜を略帯状結晶シリコン膜に改質するために使用するレーザは発振波長200nm乃至1200nmの連続発振固体レーザあるいはパルス変調固体レーザ、若しくは擬似CW固体レーザ(擬似連続発振固体レーザ)であることが好ましい。擬似CW固体レーザは、高い周波数のパルスレーザを擬似連続発振レーザと看做し、所謂モードロック技術を用いることで、波長がUV領域であっても、周波数100MHz以上のパルスレーザを得ることができる。照射レーザが短パルスであっても、シリコンの凝固時間(<100ns)以内に次のパルスが照射されると、シリコン膜は固化することなく溶解時間を延長することができるので擬似的なCWと見なすことができる。また、電気光学変調(Electro−Optic変調:EO変調)と組み合わせることで、高効率でレーザエネルギーを吸収させ、レーザ光の走査方向に長さを制御した多結晶シリコン膜(略帯状結晶シリコン膜)を得ることができる。

【0021】

本発明ではレーザ光を光学的に調整し、強度の空間分布を均一化したうえでレンズ系を用いて集光して照射するのが望ましい。本発明ではレーザ光を断続的走査で照射する時の照射幅は駆動回路領域に必要な領域の幅とそのピッチに占める割合の両者から経済性を勘案して定められる。前記仮想タイル形状を形成する照射部の幅と長さは適用回路のサイズ、集積度等を勘案して定める。本発明は、レーザ光を移動させて絶縁基板上を走査するものに限らず、絶縁基板をX−Yステージに載置し、このX−Yステージの移動に同期してレーザ光の照射を断続的に行うようにしてもよい。

【0022】

本発明では、連続パルスレーザ光照射を50mm/s乃至3000mm/sの速度で走査するのが望ましい。この走査速度の下限は絶縁基板内の駆動回路領域を走査するのに要する時間と経済負担の兼ね合いから定められる。なお、照射速度の上限は走査に用いる機械設備の能力から制限されるものである。

【0023】

本発明では該レーザ照射がレーザ光を光学系で収束したビームを用いて走査する。このとき、単一のレーザ光を単一のビームに収束する光学系を使用してもよい。しかし、単一のレーザ光を複数に分割して照射することにより、複数の画素部の列に同時走査で照射することで大形サイズの基板を短時間で処理する場合には等に好適であり、レーザ光の照射の効率を著しく向上させることが可能となる。また、本発明では該レーザ光照射が複数のレーザ発振機を並列動作させてもよく、この方法の採用も大形サイズの基板を短時間で処理する場合には特に好ましい。

【0024】

さらに本発明では、略帯状結晶に改質されたシリコン膜で形成されるアクティブ素子回路が一般的なトップゲート型薄膜トランジスタ回路に限定されることなく、ボトムゲート型薄膜トランジスタ回路とすることも可能である。NチャンネルMISもしくはPチャンネルMISのみの単チャンネル回路を必要とする場合には製造工程の簡略化からボトムゲート型がむしろ好ましい場合もある。このような場合には、ゲート配線上に絶縁膜を介したシリコン膜をレーザ照射で略帯状結晶シリコン膜に改質するので、ゲート配線材料には高融点金属の採用が好ましく、タングステン(W)もしくはモリブデン(Mo)を主成分とするゲート配線材料の使用が好ましい。

【0025】

本発明の駆動回路の薄膜トランジスタ等の半導体構造を有する絶縁基板をアクティブ・マトリクス基板として使用することで、優れた画質の液晶表示装置を安価に提供できる。また、本発明のアクティブ・マトリクス基板を使用することで優れた画質の有機EL表示装置をも安価に提供できる。さらに本発明では、液晶表示装置、有機EL表示装置にとどまることなく、同様の半導体構造を駆動回路に有する他の方式のアクティブ・マトリクス型画像表示装置、さらには半導体ウエハ上に作り込む各種の半導体装置にも適用可能である。

【0026】

【発明の実施の形態】

以下、本発明の実施の形態について、実施例の図面を参照して詳細に説明する。

【0027】

図1は本発明による製造方法を適用して製造した画像表示装置の一例としての液晶表示装置を模式的に説明するための平面図である。図1における参照符号SUB1はアクティブ・マトリクス基板、またSUB2はアクティブ・マトリクス基板SUB1に貼り合わせたカラーフィルタ基板であり、液晶層を介して貼り合わせた端部を仮想線で示す。なお、カラーフィルタ基板SUB2の内面にはカラーフィルタ、あるいは共通電極が形成されているが、図1では図示を省略してある。なお、以下では上記のようなカラーフィルタ基板を用いた液晶表示装置を例として説明するが、アクティブ・マトリクス基板側にカラーフィルタを形成した形式の液晶表示装置にも同様に適用できる。

【0028】

アクティブ・マトリクス基板SUB1は、その中央の大部分に画素領域PARを有し、画素領域PARの外側で画素領域PARに形成された多数の画素に駆動信号を供給する回路を形成した駆動回路領域DAR1、DAR2、DAR3を有する。本実施例では、アクティブ・マトリクス基板SUB1の一方の長辺(図1の上辺)に画素に対して表示データを供給するデータ駆動回路DDR1、DDR2、・・・・・DDRn−1、DDRnを形成した駆動回路領域DAR1が配置されている。また、駆動回路領域DAR1に隣接する両辺(図1の左右辺)には走査回路GDR1、GDR2を有する駆動回路領域DAR2がそれぞれ配置されている。また、アクティブ・マトリクス基板SUB1の他方の長辺(図1の下辺)には所謂プリチャージ回路を有する駆動回路領域DAR3が配置されている。

【0029】

アクティブ・マトリクス基板SUB1とカラーフィルタ基板SUB2とが重畳する四隅にはアクティブ・マトリクス基板SUB1側からカラーフィルタ基板SUB2の共通電極に共通電極電位を供給するためのパッドCPADを有する。このパッドCPADは必ずしも四隅に設ける必要はなく、何れかの一隅、または何れかの二隅あるいは三隅に設けてもよい。

【0030】

アクティブ・マトリクス基板SUB1の上記一方の長辺のカラーフィルタ基板SUB2と重畳しない端縁には、データ駆動回路DDR(DDR1、DDR2、・・・・・DDRn−1、DDRn)の入力端子DTM(DTM1、DTM2、・・・DTMn−1、DTMn)および走査回路GDR(GDR1、GDR2)の入力端子GTM(GTM1、GTM2)が形成されている。画素領域PARにマトリクス配列される画素は、データ駆動回路DDRか延びるデータ線DLと走査回路GDRから延びるゲート線GLの交差部に設けられる。この画素は薄膜トランジスタTFTと画素電極PXで構成される。

【0031】

このような構成において、走査回路GDR(GDR1、GDR2)で選択されたゲート線GLに接続した薄膜トランジスタTFTがオンとなり、データ駆動回路DDR(DDR1、DDR2、・・・・・DDRn−1、DDRn)から延びるデータ線DLを介して供給される表示データ電圧が画素電極PXに印加され、カラーフィルタ基板SUB2側に有する共通電極との間に電界が発生する。この電界によって当該画素部分の液晶層の液晶配向方向が変調されて画素を表示する。

【0032】

なお、図1に示した液晶表示装置では、走査回路GDRを二系統のGDR1とGDR2に分け、それらをアクティブ・マトリクス基板SUB1の左右に配置し、各走査回路GDR1とGDR2から延びるそれぞれのゲート線GLを交互に櫛歯状に配置してある。しかし、これに限らず、走査回路GDRを一個とし、アクティブ・マトリクス基板SUB1の左右何れかの一辺に配置することもできる。後述の説明中では、上記のように走査回路GDRを一個としたものを例として説明している。本発明は、上記した駆動回路領域DAR1、DAR2、DAR3の全てに適用できるが、回路構成が最も精細な駆動回路領域DAR1に主として適用される。

【0033】

図2は図1におけるデータ駆動回路部分の回路構成例を説明するブロック図である。図2において、参照符号PARは画素領域を示す。画素領域には前記した画素PXが水平(x)方向と垂直(y)方向とにマトリクス状に配列されている(画素を画素電極PXで示す)。また、参照符号DDRはデータ駆動回路である。データ駆動回路DDRは水平シフトレジスタHSR、ラッチ回路LTFからなる第1ラッチ回路LT1、ラッチ回路LTSからなる第2ラッチ回路LT2、デジタル−アナログ変換回路D/Aからなるデジタル−アナログ変換器DAC、バッファ回路BA、サンプリングスイッチSSWからなるサンプリング回路SAMP、垂直シフトレジスタVSRから構成される。

【0034】

図示しない信号源から入力端子DTMを介して入力する各種のクロック信号CLは水平シフトレジスタHSRに入り、データ駆動回路DDR(DDR1、DDR2、・・・・・DDRn−1、DDRn)を横断して順次転送される。また、表示データDATAはデータラインDATA−Lから第1ラッチ回路LT1にラッチされる。第1ラッチ回路LT1にラッチされた表示データはラッチコントロールラインに印加されるラッチコントロール信号で第2ラッチ回路LT2にラッチされる。第2ラッチ回路LT2にラッチされた表示データはデジタル−アナログ変換器DAC、バッファ回路BA、サンプリング回路SAMPを通って画素領域PARにおける垂直シフトレジスタVSRで選択されたゲート線に接続した画素PXに供給される。

【0035】

本実施例では、データ駆動回路DDRの部分にパルス変調レーザ光の走査による選択的な照射で当該走査方向に連続した粒界を持つ如く改質された略帯状結晶シリコン膜の不連続改質領域を適用するものである。この不連続改質領域を適用する範囲を参照符号SXで示す。範囲SXの全てに不連続改質領域を設けることが理想的である。しかし、スループット等の生産効率を考慮して、その一部の回路に不連続改質を施してもよい。この不連続改質領域を参照符号TLで示す。ここでは、不連続改質領域SX内のサンプリングスイッチSSWを構成する回路部分のシリコン膜を矩形状に改質する場合を例として説明する。以下、このような不連続改質を施した矩形状の領域を便宜上仮想タイルとも称する。仮想タイルの大きさは作り込む回路規模に対応した大きさ、あるいは複数の回路を作り込む大きさに設定される。

【0036】

図3は図2におけるサンプリング回路を構成するサンプリングスイッチ部分の構成図である。各サンプリングスイッチSSWは図2のx方向に一列に配列された仮想タイルTLのそれぞれの中に形成されている。サンプリングスイッチSSWはアナログスイッチで構成され、その回路構成はデータ駆動回路DDRの他の構成部分に比べて精細であり、密に並んでいる。このサンプリングスイッチSSWを構成する薄膜トランジスタは電子の移動度が大きい不連続改質領域に形成されるので、他の回路よりも高精細に形成できる。信号線R1,G1,B1,R2,G2,B2は、画素領域では画素ピッチで配列されるため、サンプリングスイッチSSWの出力端では、その出力線(信号線)の間隔が狭く、画素領域側で間隔が広い配線パターンとなる。

【0037】

なお、バッファ回路BFは水平シフトレジスタHSRから入力する表示データと、この信号を反転した信号を3本ずつ、さらに2画素分の計12本を出力する。ここでは、一段の水平シフトレジスタHSRで2画素ずつ処理する場合を示す。各画素の各色カラーデータ(ビデオ信号)が極性の反転したものが対になっている。サンプリングスイッチSSWは、各画素のどちらの極性の信号を送るかを決める。図2に示されたように、サンプリングスイッチSSWの構造上、隣接した画素の極性は常に反転する。図3におけるR1は画素1(赤)の信号線、G1は画素1(緑)の信号線、B1は画素1(青)の信号線、R2は画素2(赤)の信号線、G2は画素2(緑)の信号線、B2は画素2(青)の信号線である。

【0038】

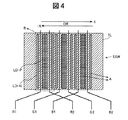

図4は図3に示した仮想タイル部分に形成されるサンプリングスイッチ回路の一つの構成を説明する拡大平面図、図5は図4の要部をさらに拡大して略帯状結晶シリコン膜の結晶方向を示す薄膜トランジスタ(TFT)のチャネル部の模式図である。仮想タイルTLはパルス変調レーザ光の走査方向x(あるいは−x)方向の走査で改質されている。仮想タイルTL中の参照符号LD−Pで示した部分はP型TFTが形成されるシリコンアイランド、LD−Nで示した部分はN型TFTが形成されるシリコンアイランドである。

【0039】

図5に示したように、シリコンアイランドLD−PおよびLD−Nの略帯状結晶シリコン膜の単結晶間に存在する粒界CBは結晶方向CGRに略同一方向となるように存在する。この結晶方向CGRと対向する位置にソース電極SD1とドレイン電極SD2がそれぞれ形成される。ソース電極SD1とドレイン電極SD2の間に流れる電流(チャネル電流)Ichの方向が結晶方向CGRと略平行する方向に設定される。このように、結晶方向CGRと電流Ichの方向を同一とすることにより、チャネルにおける電子の移動度を大きくすることができる。

【0040】

図6は図4に示した1つの仮想タイルにおけるB部分の拡大平面図、図7は図6のC−C'線に沿った断面図である。また、図8は図6の動作を説明するタイミング図である。図6と図7の構成と動作を図7および図2を参照して説明する。図6において、参照符号NT1とNT2はN型薄膜トランジスタ、PT1とPT2はP型薄膜トランジスタ、SR1+,SR1−,SR2+,SR2−はバッファBAを介して送られてきた水平シフトレジスタHSRからの信号線、VR+,VR−は赤のデータ信号(赤のビデオ信号)を示す。図7の参照符号SUB1はアクティブ・マトリクス基板、NCはN型チャネル、PCはP型チャネル、GIはゲート絶縁膜、L1は層間絶縁膜、PASSは絶縁保護膜を示す。

【0041】

図8の時刻1で信号線SR1+には“1”が、信号線SR1−には“−1”が出力され、時刻2で信号線SR2−には“−1”が、信号線SR2+には“1”が出力される。また、赤のデータ信号VR+は時刻1で画素1の信号(極性+)が、時刻2で画素2の信号(極性+)を出力する。同様に、赤のデータ信号VR−は時刻1で画素2の信号(極性−)が、時刻2で画素1の信号(極性−)を出力する。N型薄膜トランジスタNT1は時刻1にオンとなって赤のデータ信号VR+を信号線R1に出力する。P型薄膜トランジスタPT1は時刻2にオンとなって赤のデータ信号VR−を信号線R1に出力する。

【0042】

そして、N型薄膜トランジスタNT2は時刻2にオンとなって赤のデータ信号VR+を信号線R2に出力し、P型薄膜トランジスタPT2は時刻1にオンとなって赤のデータ信号VR−を信号線R2に出力する。これにより、信号線R1は時刻1に極性+のデータ(画素信号)を、時刻2に極性−のデータ(画素信号)を出力する。また、信号線R2は時刻1に極性−のデータ(画素信号)を、時刻1に極性+のデータ(画素信号)を出力する。

【0043】

以上説明した実施例では、略帯状結晶シリコン膜の仮想タイルTLをサンプリング回路SAMPを構成するサンプリングスイッチSSWの回路形成部分毎に設定した。前記したように、サンプリングスイッチSSWはアナログスイッチで構成され、回路構成が複雑で特に精細度が要求される部分である。この回路部分に仮想タイルTLで示される略帯状結晶シリコン膜を設けて薄膜トランジスタを形成することで、電子移動度が大で精細度を向上させた回路を実現することが可能となる。その結果、高速の画像表示を実現できる。なお、仮想タイルを設定する箇所は上記したサンプリング回路SAMPのみに限らず、図2に示した範囲SXの適宜の回路形成部分にも適用することができる。

【0044】

図9は本発明による画像表示装置を液晶表示装置に適用した他の実施例を模式的に説明するための図2と同様のブロック図である。本実施例は、仮想タイルTLを第1のラッチ回路LT1と第2のラッチ回路LT2の部分、デジタル−アナログ変換器DACとバッファ回路BAの部分に形成した。このように、本実施例では、仮想タイルTLをx方向に平行な2列以上に形成したものである。他の構成は図2と同様なので重複する説明は省略する。なお、ここでも、説明を容易にするため、仮想タイルTLのそれぞれを大まかな範囲で示してあるが、それぞれの仮想タイルTLは適用する回路規模に応じた適宜の大きさをもつ複数の仮想タイルをブロック化した集合体とする場合も含む。

【0045】

これらの回路部分に仮想タイルTLで示される略帯状結晶シリコン膜を設けることで、電子移動度が大で精細度を向上することが可能となる。その結果、高速で高精細の画像表示を実現できる。なお、仮想タイルを設定する箇所は上記の部分に限るものではなく、図2と同様にサンプリング回路SAMPも含めることもできる。また、仮想タイルTLを第1のラッチ回路LT1、第2のラッチ回路LT2、デジタル−アナログ変換器DAC、バッファ回路BAのそれぞれ、あるいは適宜に組合せた回路を含む種々のサイズに設定してもよい。

【0046】

上記した各実施例で説明した仮想タイルの大きさや配列、個々の改質領域の大きさや配列は、それぞれの適用回路の薄膜トランジスタの作り込みパターンを考慮して決定すればよく、例えば千鳥状の配列等も可能であり、また必ずしも規則的配列にこだわる必要はない。

【0047】

以上の実施例では、データ側の駆動回路を形成する駆動回路領域DAR1に略帯状結晶シリコン膜の不連続改質領域(仮想タイル)を適用しているが、本発明はこれに限らず、走査駆動回路領域DAR2、あるいはプリチャージ回路を有する駆動回路領域DAR3に対しても同様に適用可能である。

【0048】

このように、上記各実施例の構成によれば、マトリクス状に配置された画素部を駆動するための駆動回路に高速の移動度で動作する高性能の薄膜トランジスタ回路を有するアクティブ・マトリクス基板を備えた画像表示装置を製造することができ、高品質の画像表示装置を得ることができる。

【0049】

次に、本発明の画像表示装置の製造方法の実施例について図10乃至図15を参照して説明する。ここで説明する製造方法はCMOSの薄膜トランジスタの製造を例としており、N型薄膜トランジスタは自己整合GOLDD(Gate Overlapped Light Doped Drain)、P型薄膜トランジスタはカウンタードープによって形成する。

【0050】

図10乃至図15は一連の製造プロセスを示し、この一連の製造プロセスを図10の(A)から図15の(N)に従って説明する。先ず、アクティブ・マトリクス基板となる絶縁基板として、厚さが0.3mm乃至1.0mm程度で、好ましくは400°C乃至600°Cの熱処理で変形や収縮の少ない耐熱性のガラス基板SUB1を準備する。好ましくは、このガラス基板SUB1の上に熱的、化学的なバリア膜として機能するおよそ約50nm厚のSiN膜および約100nm厚のSiO膜をCVD法で連続かつ均一に堆積する。このガラス基板SUB1上にCVD等の手段でアモルファスシリコン膜ASIを形成する。 ・・・・・図10(A)

【0051】

次に、エキシマレーザ光ELAをx方向に走査し、アモルファスシリコン膜ASIを溶解し、結晶化してガラス基板SUB1上のアモルファスシリコン膜ASI全体を多結晶シリコン膜、すなわちポリシリコン膜PSIに改質する。 ・・・・・図10(B)

【0052】

なお、エキシマレーザ光ELAに替えて、他の方法、例えば固体パルスレーザアニールによる結晶化、シリコン膜の形成時にポリシリコン膜となるCat−CVD膜を採用することもできる。

【0053】

ホトリソグラフィー法あるいはドライエッチング法により、後述するパルス変調レーザ等のレーザ光SXL(なお、ここではパルス幅変調レーザを用いるものとして説明する)の照射位置決め等のターゲットとなる位置決めマークMKを形成する。 ・・・・・図10(C)

【0054】

マークMKを参照しながら、パルス変調レーザ光SXLをx方向に走査しながら所定の領域を選択しながら不連続で照射する。この選択的な照射でポリシリコン膜PSIを改質し、当該走査方向に連続した粒界を持つ略帯状結晶シリコン膜の不連続改質領域(仮想タイルのシリコン膜)SPSIを形成する。このとき、図1の駆動回路領域DAR1および/またはDAR2を走査するレーザ光を駆動回路領域DAR3までカバーさせることで、駆動回路領域DAR1、DAR2の隣接辺にある駆動回路領域DAR3にも同時に仮想タイルを形成することができる。 ・・・・・図11(D)

【0055】

ホトリソグラフィー法を用いて略帯状結晶シリコン膜の不連続改質領域(仮想タイルのシリコン膜)SPSIを加工し、薄膜トランジスタを作り込むアイランドSPSI−Lを形成する。 ・・・・・図11(E)

【0056】

不連続改質領域(仮想タイルのシリコン膜)SPSIのアイランドSPSI−Lを覆ってゲート絶縁膜GIを形成する。 ・・・・・図11(F)

【0057】

N型薄膜トランジスタを形成する領域に閾値を制御するためのインプランテーションNEを行う。このとき、P型薄膜トランジスタを形成する領域をホトレジストRNEで覆う。 ・・・・・図12(G)

【0058】

次に、P型薄膜トランジスタを形成する領域に閾値を制御するためのインプランテーションPEを行う。このとき、P型薄膜トランジスタを形成する領域をホトレジストRPEで覆う。 ・・・・・図12(H)

【0059】

この上に、スパッタリング法またはCVD法を用いて薄膜トランジスタのゲート電極となる二層の金属ゲート膜GT1,GT2を形成する。

・・・・・図12(I)

【0060】

金属ゲート膜GT1,GT2の形成領域をホトレジストRNで覆い、ホトリソグラフィー法により、金属ゲート膜GT1,GT2をパターニングする。このとき、LDD領域を形成するため、上層の金属ゲート膜GT2を所要量サイドエッチングし、下層の金属ゲート膜GT1より後退させる。この状態で、ホトレジストRNをマスクとしてN型の不純物Nをインプランテーションし、N型薄膜トランジスタのソース・ドレイン領域NSDを形成する。 ・・・・・図13(J)

【0061】

ホトレジストRNを剥離し、金属ゲート膜GT2をマスクとしてインプランテーションLDDを行い、N型薄膜トランジスタのLDD領域NLDDを形成する。 ・・・・・図13(K)

【0062】

N型薄膜トランジスタの形成領域をホトレジストRPで覆い、P型薄膜トランジスタのソース・ドレイン形成領域にP型の不純物Pをインプランテーションし、P型薄膜トランジスタのソース・ドレイン領域PSDを形成する。 ・・・・・図14(L)

【0063】

ホトレジストRPを剥離し、インプランテーションによる不純物を活性化した後、CVD法等で層間絶縁膜LIを形成する。 ・・・・・図14(M)

【0064】

ホトリソグラフィー法により層間絶縁膜LIとゲート絶縁膜GIにコンタクトホールを形成し、このコンタクトホールを介してN型薄膜トランジスタとP型薄膜トランジスタの各ソース・ドレインNSD、PSDに配線用の金属層を接続し、配線Lを形成する。この上に、層間絶縁膜L2を形成し、さらに保護絶縁膜PASSを形成する。 ・・・・・図14(N)

【0065】

以上の工程により、略帯状結晶シリコン膜の不連続改質領域(仮想タイルのシリコン膜)SPSIにCMOS薄膜トランジスタが形成される。なお一般に、N型薄膜トランジスタは劣化が激しい。チャネルとソース・ドレイン領域との間に低濃度不純物領域LDD(Light Doped Drain領域)を形成すると、この劣化が緩和される。GOLDDは低濃度不純物領域にゲート電極が被さった構造を有している。この場合、LDDで観測される性能低下が緩和される。P型薄膜トランジスタでは、その劣化がN型薄膜トランジスタほど深刻でなく、低濃度不純物領域LDDやGOLDDは通常は採用されない。

【0066】

次に、本発明の特徴である略帯状結晶シリコン膜の不連続改質領域(仮想タイルのシリコン膜)の形成について図16乃至図26を参照して説明する。図16は略帯状結晶シリコン膜の不連続改質領域(仮想タイルのシリコン膜)の形成プロセスの説明図であり、同図(a)はプロセスを説明する模式図、同図(b)はパルス変調レーザの波形例、同図(c)は擬似CWレーザの波形例を示す。

【0067】

略帯状結晶シリコン膜の不連続改質領域(仮想タイル)は、絶縁基板SUB1に有するバッファ層BFL上に形成されたポリシリコン膜PSIに図16の(b)又は(c)に示したレーザ光SXLを照射することで得られる。レーザ光SXLは(b)のパルス変調レーザ光、又は(c)に示したような擬似CWレーザ光を10ns乃至100msの周期で照射する。このレーザ光SXLを図16(a)に示したようにポリシリコン膜PSI上をx方向に走査し、y方向にシフトさせた後に−x方向に走査することで、当該走査方向x、−x方向に略帯状結晶を有するシリコン膜SPSIが得られる。絶縁基板SUNB1には位置決めのためのマークMKを有し、このマークMKを位置決めターゲットとしてレーザ光SXLの走査を行う。このように断続的にレーザを照射しながら基板を走査するので、略帯状結晶のシリコン膜SPSIを仮想タイル状に配列することができる。

【0068】

図17は略帯状結晶シリコン膜の結晶構造の説明図であり、同図(a)はレーザ光SXLの走査態様を説明する模式図、同図(b)はレーザ光SXLの走査により形成された略帯状結晶シリコン膜SPSIを非走査部分に残留するポリシリコン膜PSIとの結晶構造の違いを比較して示す模式図である。ポリシリコン膜PSIを同図(a)のようにレーザ光SXLの走査で改質することで、同図(b)に示したように、単結晶がレーザ光の走査方向に帯状に延在する略帯状結晶シリコン膜SPSIの結晶構造となる。参照符号CBは粒界を示す。

【0069】

略帯状結晶シリコン膜SPSIの平均粒サイズはレーザ光SXLの走査方向に約5μm程度、走査方向と直角方向(粒界CB間の幅)に0.5μm程度となる。なお、走査方向の粒サイズはレーザ光SXLのエネルギーや走査速度、パルス幅等の条件で可変である。これに対し、ポリシリコン膜PSIの平均粒径は0.6μm(0.3乃至1.2μm)程度である。このような結晶構造の相違によって、ポリシリコン膜PSIと略帯状結晶シリコン膜SPSIとを用いて薄膜トランジスタを構成した場合の電子移動度に大きな差をもたらす。

【0070】

上記の略帯状結晶シリコン膜SPSIは、下記の特徴を有する。すなわち、

(a)表面に対する主配向が{110}である。

【0071】

(b)キャリアの移動方向に略垂直な面の主配向が{100}である。

【0072】

上記(a)、(b)の2つの方位は、電子線回折法あるいはEBSP(Electron Backscatter Diffraction Pattern)法により評価できる。

【0073】

(c)膜の欠陥密度が1×1017cm-3より小さい。膜中の結晶欠陥数は、電気的特性、あるいは電子スピン共鳴(ESR)による不対電子の定量的評価から定義される値である。

【0074】

(d)膜のホール移動度が50cm2 /Vs以上、700cm2 /Vs以下である。

【0075】

(e)膜の熱伝導率は、温度依存性があり、ある温度で最大値を示す。熱伝導率は温度が上昇すると一端上昇し、最大値50W/mK以上、100W/mK以下の値を示す。高温領域では、熱伝導率は温度上昇に伴い低下する。熱伝導率は、3オメガ方法などから評価、定義される値である。

【0076】

(f)薄膜のラマン散乱分光から評価、定義されるラマンシフトは、512cm-1以上、518cm-1以下である。

【0077】

(g)膜の結晶粒界のΣ値の分布は、Σ11に最大値を有し、ガウス型に分布する。なお、Σ値は電子線回折法あるいはEBSP(Electron Backscatter Diffraction Pattern法から計測される値である。

【0078】

(h)膜の光学定数は、下記の条件を満たす領域であることを特徴とする。波長500nmにおける屈折率nは2.0以上、4.0以下であり、かつ減衰係数kは0.3以上、1以下であること。さらに、波長300nmにおける屈折率nは3.0以上、4.0以下であり、かつ減衰係数kは3.5以上、4以下であること。なお、光学定数は、分光エリプソメータによって計測された値である。

【0079】

図18はシリコン膜の結晶構造の相違に起因する薄膜トランジスタのチャネルにおける電子移動度の相違の説明図である。同図(a)は薄膜トランジスタのチャネル構造と当該チャネル部分のシリコン膜SIの粒界CBと電子移動の関係を示し、同図(b)はソースSD1とドレインSD2間に流れる電流が横断する粒界数と電子移動度の関係を示す。シリコン膜SIがポリシリコン膜PSIの場合はドレインSD2からソースSD1に電流が横断する粒界数が多く、シリコン膜SIが略帯状結晶シリコン膜SPSIの場合は大きな単結晶が成長方向に長く存在し、横断する粒界数が少ない。この関係を図18(b)に示した。

【0080】

平均横断粒界数Cは、電流方向でチャネルの幅をj分割し、電流が流れる方向で横断する粒界数をNiとしたとき、C=ΣNi/jで表される。図18(b)には、横軸に平均横断粒界数を、縦軸に電子移動度(cm2 /V・s)とその逆数(V・s/cm2 )を取って示してある。このように、薄膜トランジスタのチャネルを構成する略帯状結晶シリコン膜SPSIの結晶成長方向に電流が流れるようにソースSD1とドレインSD2を配置することにより、電子移動度は極端に大きくなる。すなわち、薄膜トランジスタの動作速度が大きくなる。したがって、薄膜トランジスタ自体を精細に作り込むことが可能となり、図3で説明したように、画素ピッチに対して配線R1,G1,B1,R2,G2,B2を狭いピッチで形成することができる。その結果、仮想タイルを用いて形成した回路間には大きなスペースが生じる。このスペースを他の配線等の形成スペースに利用することも可能である。

【0081】

図19はレーザ光の照射装置の一例を説明する構成図である。この照射装置ではポリシリコン膜PSIを形成したガラス基板SUB1をx−y方向の駆動ステージXYT上に設置し、基準位置測定用カメラCMを用いて位置合わせを行う。基準位置測定信号POSは制御装置CRLに入力され、駆動設備MDに入力された制御信号CSに基づいて照射位置の微調整を行い、所定の速度でステージXYTを移動させて一方向(図1のx方向)に走査する。かかる走査に同期して照射設備LUからレーザ光SXLをポリシリコン膜PSIに照射して、略帯状結晶シリコン膜SPSIに改質する。

【0082】

照射設備LU内には一例として連続発振(CW)固体レーザLS(レーザダイオード)励起の発振器、ホモジナイザ、パルス幅を変調するためのEOモジュレータ等の光学系HOS、反射ミラーML、集光レンズ系LZを配置することで所望の照射ビームを形成できる。レーザ光SXLの照射時間、照射強度などは制御装置CRLからのON−OFF信号SWS、制御信号LECで調整する。

【0083】

図20は仮想タイルのレイアウトの一例を説明する平面図である。この配置例では、仮想タイルTLは図1で説明した駆動回路領域DAR1に複数列で配置されている。仮想タイルTLは作り込む回路パルスに応じて、1列、2以上の多列、あるいは千鳥状等に配列することができる。本例では、3列(または、3段)としてある。各仮想タイルTLのサイズは、x方向の長さwが20μm以上で1mm以下、y方向の幅hが20μm以上で1mm以下、x方向に隣接する仮想タイルとの間隔dが3μm以上、y方向の間隔pが3μm以上となっている。この配置サイズはレーザのパワー、高品質な結晶を安定して成長させることができるサイズによって制約される。

【0084】

図21は図19の照射装置を用いたレーザ照射プロセス例の説明図である。図21では絶縁基板を単に基板と表記する。先ず、ポリシリコン膜を形成した絶縁基板にレーザ光SXLを照射するため、装置電源をONとし、レーザ発振器をONとする。駆動ステージXYT上に絶縁基板をセットし、真空チャックで固定する。絶縁基板の位置決めマークをターゲットとしてX軸、Y軸、およびθ軸(X−Y平面での回転方向)を規定値に調整し、絶縁基板の準備を完了する。

【0085】

一方、照射装置に各種条件を入力し、確認を行う。条件入力項目は、レーザ出力(NDフィルタの調整等)、結晶化位置(駆動ステージXYT上)のセット位置、結晶化距離(仮想タイルの結晶成長方向長さ)、間隔(仮想タイルの間隔)、個数(仮想タイルの作成個数)、レーザ光路上にあるスリット幅の調整、対物レンズのセット等である。結晶化距離、間隔、個数はEOモジュレータにセットする。また、確認事項は、レーザ光のビームプロファイラ、パワーモニタ、レーザ光照射位置等である。

【0086】

絶縁基板の準備が完了し、条件入力と確認が取られた後、絶縁基板の表面高さを測定し、オートフォーカス機構を作動させてレーザ光を照射する。レーザ光の照射でオートフォーカス機構を補正し、絶縁基板の表面高さを制御する。また、レーザ光の照射を継続中に絶縁基板の走査距離と照射位置を条件入力側にフィードバックする。

【0087】

所定の領域にレーザ光の照射処理を完了後、真空チャックをOFFとして駆動ステージXYTから絶縁基板を取り出す。以下、次の絶縁基板を駆動ステージXYTにセットし、上記操作を必要回数繰り返す。全ての必要な絶縁基板のレーザ照射処理を完了したとき、レーザ発振器をOFFとし、装置電源をOFFして終了する。

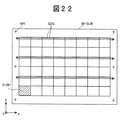

【0088】

図22は多面取りの大サイズ素材絶縁基板上における各個別の絶縁基板に対する略帯状結晶シリコン膜SPSIの仮想タイル形成操作の説明図である。図22中、参照符号M−SUBは大サイズ素材絶縁基板で、この大サイズ素材絶縁基板M−SUBに個々の画像表示装置のアクティブ・マトリクス基板SUB1が多数形成されている。ここでは、8×6=48枚取りとして示したが、これに限らないことは言うまでもない。この大サイズ素材絶縁基板M−SUBの駆動回路領域に対して、マークMKをターゲットとした位置合わせ後、レーザ光を図中に矢印SDSで示したように往復走査する。ここでは、3本のレーザ光を並列の走査することで、短時間に大サイズの素材絶縁基板M−SUBに所要の仮想タイルを形成できるようにしている。

【0089】

図23は図22で形成した仮想タイルの位置の一例を説明する一枚のアクティブ・マトリクス基板の平面図であり、同図(a)は全体図、同図(b)は同図(a)の矢印A部分の拡大図である。この例では、アクティブ・マトリクス基板SUB1のデータ信号の駆動回路領域DAR1を形成するx方向の一辺に複数の仮想タイルTLのブロックを一列に配置してある。この場合、仮想タイルは図2あるいは図9に参照符号SXで示した全域、または図2のサンプリング回路SAMP部分、図9の各ラッチ回路LT1、LT2の部分とデジタル−アナログ変換器DACやバッファ回路BAの部分に複数個設け、これをブロックに分けて配置する。仮想タイルを構成する個々の改質領域も同様に配置される。なお、同図(b)の仮想タイルのブロックや個々の改質領域の大きさや位置は本発明を分かり易く示したもので、実際の回路の大きさや位置とは異なる。

【0090】

図24は仮想タイルの他の配列を説明する図23(b)と同様の拡大図である。仮想タイルTLのブロックは同図(a)のようにx方向に平行な二列に配置され、あるいは同図(b)のようにx方向に平行で互いに千鳥状の三列に配置される。なお、各ブロックの大きさ、間隔は適用する回路構造に対応して可変とすることが可能である。なおブロックを構成する個々の改質領域の配列も複数配列、あるいは千鳥状の配列にすることができる。

【0091】

図25と図26は仮想タイルの位置の他例を説明する一枚のアクティブ・マトリクス基板の平面図である。図25では図1で説明した駆動回路領域DAR1とDAR3に仮想タイルを適用したものである。また、図26では図1で説明した駆動回路領域DAR1とDAR3およびアクティブ・マトリクス基板SUB1のy方向に延びる一辺に形成した走査駆動回路領域DAR2に仮想タイルを適用したものである。個々の仮想タイルやブロックの配列等は図23乃至図24で説明したものと同様である。

【0092】

次に、絶縁基板(アクティブ・マトリクス基板)に仮想タイルを形成するための位置決め用のマークについて説明する。図27はアクティブ・マトリクス基板SUB1への位置決め用のマーク付けとこのマークをターゲットとしたレーザの照射プロセスの第1例の説明図である。この例では、アクティブ・マトリクス基板SUB1に形成されているシリコン膜SIにホトリソグラフィー法で位置決め用のマークMKを形成し(P−1)、その後の連続パルスレーザSLXの照射時にこのマークMKを基準として位置決め(アライメント)を取る(P−2)。そして同様に、このマークMKを基準として連続パルスレーザSLXの照射で改質された略帯状結晶シリコン膜SPSIをアイランドSPSI−Lに加工する(P−3)。なお、このマークMKはアモルファスシリコン膜ASIの段階で形成してもよく、またポリシリコン膜の段階で形成してもよい。

【0093】

図28はアクティブ・マトリクス基板SUB1への位置決め用のマーク付けとこのマークをターゲットとしたレーザ光の照射プロセスの第2例の説明図である。この例では、アクティブ・マトリクスSUB1にポリシリコン膜PSIを形成後(P−1)、ポリシリコン膜PSIにレーザSLXを照射する際に、当該レーザSLXで位置決め用のマークMKを形成するようにしたものである(P−2)。その後のアイランドSPSI−Lの形成時にこのマークMKで位置決めを行う(P−3)。

【0094】

ポリシリコン膜PSIと略帯状結晶シリコン膜SPSIとは可視光の反射率に差がある。この差を位置決めターゲットとして利用することができる。また、ポリシリコン膜PSIと略帯状結晶シリコン膜SPSIとは、結晶の大きさに起因して高さに相違がでて来る。この略帯状結晶化したマークMKの部分の結晶粒界の段差をターゲットとして利用することもできる。なお、マークMK部分のポリシリコン膜をレーザアブレーションで除去してマークMKとすることもできる。このレーザアブレーションによるマークMKの形成方法は、マークMK形成のためのホトリソグラフィー工程を省略できる利点がある。

【0095】

図29はアクティブ・マトリクス基板SUB1への位置決め用のマーク付けとこのマークをターゲットとしたレーザ光の照射プロセスの第3例の説明図である。この例では、アクティブ・マトリクス基板SUB1にシリコン膜を形成する前に当該ガラス基板または下地膜に予めエッチング法あるいは機械的手段でマークMKを形成する(P−1)。アクティブ・マトリクス基板SUB1にポリシリコン膜PSIを形成し、このマークMKを基準としてレーザ光SLXを照射して略帯状結晶シリコン膜SPSIを形成する(P−2)。その後のアイランドSPSI−Lの形成時にこのマークMKで位置決めを行う(P−3)。

【0096】

上記したように、本実施例によれば、ポリシリコン膜をさらに大きな結晶に改質し、その結晶成長方向の配置により、ソースとドレイン間の電流が粒界を横切る確率を低減できる。その結果、薄膜トランジスタの動作速度を向上して最良の薄膜トランジスタ回路を得ることが可能となる。そして、画像表示装置の駆動回路部分に略帯状結晶シリコン膜の半導体膜を用いた薄膜トランジスタ回路を配置することができる。本実施例で得られる薄膜トランジスタの性能は、例えばNチャンネルMISトランジスタを作成する場合に、電界効果移動度が約300cm2 /V・s以上でかつ、閾値電圧のバラツキを±0.2V以下に抑制することができ、高性能、高信頼で動作し、デバイス間の均一性が優れたアクティブ・マトリクス基板を用いた表示装置を製造することができる。

【0097】

また本実施例では、電子キャリアを付与するリンのイオン打ち込みに代えてホールキャリアを付与するボロン打ち込みによりPチャンネルMISトランジスタを製造することもできる。また、上記したCMOS型の回路では周波数特性の向上が期待でき、高速動作に適している。

【0098】

図30は本発明の画像表示装置の第1例としての液晶表示装置の構成を説明する展開斜視図である。また、図31は図30のZ−Z線方向で切断した断面図である。この液晶表示装置は前記したアクティブ・マトリクス基板を用いて液晶表示装置を製造する。図30と図31において、参照符号PNLはアクティブ・マトリクス基板SUB1とカラーフィルタ基板SUB2の貼り合わせ間隙に液晶を封入した液晶セルで、その表裏に偏光板POL1,POL2が積層されている。また、参照符号OPSは拡散シートやプリズムシートからなる光学補償部材、GLBは導光板、CFLは冷陰極蛍光ランプ、RFSは反射シート、LFSはランプ反射シート、SHDはシールドフレーム、MDLはモールドケースである。

【0099】

前記した実施例の何れかの構成を有するアクティブ・マトリクス基板SUB1上に液晶配向膜層を形成し、これにラビング等の手法で配向規制力を付与する。画素領域ARの周辺にシール剤を形成した後、同様に配向膜層を形成したカラーフィルタ基板SUB2を所定のギャップで対向配置させ、このギャップ内に液晶を封入し、シール剤の封入口を封止材で閉鎖する。こうして構成した液晶セルPNLの表裏に偏光板POL1,POL2を積層し、導光板GLBと冷陰極蛍光ランプCFL等からなるバックライト等を光学補償部材OPSを介して実装することで液晶表示装置を製造する。なお、液晶セルの周辺に有する駆動回路にはフレキシブルプリント基板FPC1,FPC2を介してデータやタイミング信号が供給される。参照符号PCBは外部信号源と各フレキシブルプリント基板FPC1,FPC2の間において、当該外部信号源から入力する表示信号を液晶表示装置で表示する信号形式に変換するタイミングコンバータ等が搭載されている。

【0100】

本実施例のアクティブ・マトリクス基板を使用した液晶表示装置は、その画素回路に上記した優れたポリシリコン薄膜トランジスタ回路を配置することで、電流駆動能力に優れることから高速動作に適している。さらに、閾値電圧のバラツキが小さいために画質の均一性に優れ液晶表示装置を安価に提供できるのが特長である。

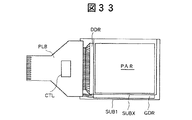

【0101】

また、本実施例のアクティブ・マトリクス基板を用いて有機EL表示装置を製造することができる。図32は本発明の画像表示装置の第2例としての有機EL表示装置の構成例を説明する展開斜視図である。また、図33は図32に示された構成要素を一体化した有機EL表示装置の平面図である。前記した各実施例の何れかのアクティブ・マトリクス基板SUB1に有する画素電極上に有機EL素子を形成する。有機EL素子は、画素電極表面から順次、ホール輸送層、発光層、電子輸送層、陰極金属層などを蒸着した積層体から構成される。このような積層層を形成したアクティブ・マトリクス基板SUB1の画素領域PARの周囲にシール材を配置し、封止基板SUBXまたは封止缶で封止する。

【0102】

この有機EL表示装置は、その駆動回路領域DDR、に外部信号源からの表示用信号をプリント基板PLBで供給する。このプリント基板PLBにはインターフェース回路チップCTLが搭載されている。そして、上側ケースであるシールドフレームSHDと下側ケースCASで一体化して有機EL表示装置とする。

【0103】

有機EL表示装置用のアクティブ・マトリクス駆動では、有機EL素子が電流駆動発光方式であるために高性能の画素回路の採用が良質な画像の提供には必須であり、CMOS型薄膜トランジスタの画素回路を用いるのが望ましい。また、駆動回路領域に形成する薄膜トランジスタ回路も高速、高精細化には必須である。本実施例のアクティブ・マトリクス基板SUB1は、このような要求を満たす高い性能を有している。本実施例の製造方法で製造したアクティブ・マトリクス基板を用いた有機EL表示装置は本実施例の特長を最大限に発揮する表示装置の1つである。

【0104】

本発明の製造方法は上記した画像表示装置のアクティブ・マトリクス基板に限るものではなく、また、本発明の製造方法は特許請求の範囲に記載の構成および実施例に記載の構成に限定されるものではなく、本発明の技術思想を逸脱することなく種々の変更が可能であり、例えば各種の半導体装置の製造にも適用することもできる。

【0105】

【発明の効果】

以上説明したように、本発明はアクティブ・マトリクス基板の画素領域の周辺に配置される駆動回路領域の回路を構成するシリコン膜にパルス変調レーザ光あるいは擬似CWレーザ光を照射して選択的に改質された略帯状結晶シリコン膜の不連続改質領域を形成し、この不連続改質領域に薄膜トランジスタ等のアクティブ素子からなる駆動回路を形成するという新規な方法を採用することにより、高速の移動度で動作する高性能の画像表示装置を得ることができる。

【図面の簡単な説明】

【図1】本発明による製造方法を適用して製造した画像表示装置の一例としての液晶表示装置を模式的に説明するための平面図である。

【図2】図1におけるデータ駆動回路部分の回路構成例を説明するブロック図である。

【図3】図2におけるサンプリング回路を構成するサンプリングスイッチ部分の構成図である。

【図4】図3に示した仮想タイルに形成されるサンプリングスイッチ回路の一つの構成を説明する拡大平面図である。

【図5】図4の要部をさらに拡大して略帯状結晶シリコン膜の結晶方向を示す薄膜トランジスタ(TFT)のチャネル部の模式図である。

【図6】図4に示した1つの仮想タイルにおけるB部分の拡大平面図である。

【図7】図6のC−C’線に沿った断面図である。

【図8】図6の動作を説明するタイミング図である。

【図9】本発明による画像表示装置を液晶表示装置に適用した他の実施例を模式的に説明するための図2と同様のブロック図である。

【図10】本発明の画像表示装置の製造方法の一実施例を説明するプロセスの説明図である。

【図11】本発明の画像表示装置の製造方法の一実施例を説明する図10に続くプロセスの説明図である。

【図12】本発明の画像表示装置の製造方法の一実施例を説明する図11に続くプロセスの説明図である。

【図13】本発明の画像表示装置の製造方法の一実施例を説明する図12に続くプロセスの説明図である。

【図14】本発明の画像表示装置の製造方法の一実施例を説明する図13に続くプロセスの説明図である。

【図15】本発明の画像表示装置の製造方法の一実施例を説明する図14に続くプロセスの説明図である。

【図16】略帯状結晶シリコン膜の不連続改質領域(仮想タイル)の形成プロセスの説明図である。

【図17】略帯状結晶シリコン膜の結晶構造の説明図である。

【図18】シリコン膜の結晶構造の相違に起因する薄膜トランジスタのチャネルにおける電子移動度の相違の説明図である。

【図19】レーザ光の照射装置の一例を説明する構成図である。

【図20】仮想タイルのレイアウトの一例を説明する平面図である。

【図21】図19の照射装置を用いたレーザ照射プロセス例の説明図である。

【図22】多面取りの大サイズ素材絶縁基板上における各個別の絶縁基板に対する略帯状結晶シリコン膜SPSIの仮想タイル形成操作の説明図である。

【図23】図22で形成した仮想タイルの位置の一例を説明する一個のアクティブ・マトリクス基板の平面図である。

【図24】仮想タイルの他の配列を説明する図23(b)と同様の拡大図である。

【図25】仮想タイルの位置の他例を説明する一個のアクティブ・マトリクス基板の平面図である。

【図26】仮想タイルの位置のさらに他例を説明する一個のアクティブ・マトリクス基板の平面図である。

【図27】アクティブ・マトリクス基板への位置決め用のマーク付けとこのマークをターゲットとした連続パルスレーザの照射プロセスの第1例の説明図である。

【図28】アクティブ・マトリクス基板SUB1への位置決め用のマーク付けとこのマークをターゲットとした連続パルスレーザの照射プロセスの第2例の説明図である。

【図29】アクティブ・マトリクス基板SUB1への位置決め用のマーク付けとこのマークをターゲットとした連続パルスレーザの照射プロセスの第3例の説明図である。

【図30】本発明の画像表示装置の第1例としての液晶表示装置の構成を説明する展開斜視図である。

【図31】図30のZ−Z線方向で切断した断面図である。

【図32】本発明の画像表示装置の第2例としての有機EL表示装置の構成例を説明する展開斜視図である。

【図33】図32に示された構成要素を一体化した有機EL表示装置の平面図である。

【図34】一般的なエキシマパルスレーザ光照射を走査することによるアモルファスシリコン膜の結晶化方法の説明図である。

【図35】図34におけるレーザ光照射部の部分平面図と薄膜トランジスタ部の構成例を説明する要部平面図である。

【符号の説明】

SUB1・・・・アクティブ・マトリクス基板、PAR・・・・画素領域、DAR1、DAR2、DAR3・・・・駆動回路領域、DDR1、DDR2、・・・・・DDRn−1、DDRn・・・・データ駆動回路、GDR1、GDR2・・・・走査回路、SUB2・・・・カラーフィルタ基板、CPADQ・・・・パッド、HSR・・・・水平シフトレジスタ、LT1・・・・第1ラッチ回路、LTS・・・・第2ラッチ回路、DAC・・・・デジタル−アナログ変換器、BA・・・・バッファ回路、SAMP・・・・サンプリング回路、VSR・・・・垂直シフトレジスタ、R1,G1,B1,R2,G2,B2・・・・信号線、TL・・・・仮想タイル、ELA・・・・エキシマレーザ光、SXL・・・・パルス変調レーザ光あるいは擬似CWレーザ光、SPSI・・・・略帯状結晶シリコン膜の不連続改質領域(仮想タイルのシリコン膜)、ASI・・・・アモルファスシリコン膜、PSI・・・・ポリシリコン膜。

Claims (17)

- 多数の画素をマトリクス状に形成した画素領域と、前記画素領域の外側で前記画素に駆動信号を供給するアクティブ回路を形成した駆動回路領域とを有するアクティブ・マトリクス基板を備えた画像表示装置の製造方法であって、

前記アクティブ・マトリクス基板の前記画素領域および前記駆動回路領域にアモルファスシリコン膜を形成する工程と、

前記アモルファスシリコン膜にエキシマレーザ光を照射して多結晶シリコン膜を形成する工程と、

前記多結晶シリコン膜の駆動回路領域部分にパルス幅および/またはパルス間隔が変調されたCWレーザ光を用い、該CWレーザ光または基板を走査して選択的な照射を行い、当該走査方向に連続した粒界を持つ如く改質された略帯状結晶シリコン膜の不連続改質領域を形成する工程と、

前記不連続改質領域の前記連続した粒界方向にキャリア移動方向を有する如く周辺回路を形成する工程とを含み、

前記パルス幅および/またはパルス間隔が変調されたCWレーザ光を用い、該CWレーザ光または基板を前記アクティブ・マトリクス基板の周辺の一辺に沿って、断続的に往復走査するように二列以上に分けて周辺回路を照射し、前記不連続改質領域を構成する個々の改質領域を前記駆動回路領域の延在方向に所定の間隔で略矩形状に形成し、配列させることを特徴とする画像表示装置の製造方法。 - 前記パルス幅および/またはパルス間隔が変調されたCWレーザ光を前記アクティブ・マトリクス基板の周辺の対向する二辺のそれぞれに沿って走査し、前記二辺に形成する前記不連続改質領域のそれぞれを構成する個々の改質領域を前記駆動回路領域のそれぞれの延在方向に所定の間隔で配列させることを特徴とする請求項1に記載の画像表示装置の製造方法。

- 前記パルス幅および/またはパルス間隔が変調されたCWレーザ光を前記アクティブ・マトリクス基板の周辺の一辺に沿って前記一辺の隣接辺を含んで走査し、前記不連続改質領域を構成する個々の改質領域を前記一辺の前記駆動回路領域の延在方向および前記隣接辺の前記駆動回路領域とに所定の間隔で配列させることを特徴とする請求項1に記載の画像表示装置の製造方法。

- 前記パルス幅および/またはパルス間隔が変調されたCWレーザ光を前記アクティブ・マトリクス基板の周辺の対向する二辺に沿って当該二辺の隣接辺を含んで走査し、前記不連続改質領域を構成する個々の改質領域を前記二辺および前記隣接辺における前記駆動回路領域のそれぞれの延在方向に所定の間隔で配列させることを特徴とする請求項1に記載の画像表示装置の製造方法。

- 少なくとも2個以上の前記不連続改質領域を配列した単位領域を形成し、前記駆動回路領域の延在方向に前記2個以上配列した単位領域を平行な2列以上に配列させることを特徴とする請求項1に記載の画像表示装置の製造方法。

- 前記2個以上配列した単位領域を構成する個々の改質領域を、前記駆動回路領域の延在方向と平行な2列以上に配列させることを特徴とする請求項5に記載の画像表示装置の製造方法。

- 前記不連続改質領域は前記駆動回路領域の延在方向に前記2個以上配列した単位領域を平行な2列以上で、かつ互いに千鳥状に配列させることを特徴とする請求項5に記載の画像表示装置の製造方法。

- 前記2個以上配列した単位領域を構成する個々の改質領域を、前記駆動回路領域の延在方向と平行な2列以上で、かつ互いに千鳥状に配列させることを特徴とする請求項7に記載の画像表示装置の製造方法。

- 前記アクティブ・マトリクス基板のアモルファスシリコン膜あるいは多結晶シリコン膜にホトリソグラフィー手法により位置決めマークを形成する工程を有することを特徴とする請求項1に記載の画像表示装置の製造方法。

- 前記アクティブ・マトリクス基板の位置決めマークは、あらかじめ前記アクティブ・マトリクス基板、あるいは当該アクティブ・マトリクス基板上のアモルファスシリコン膜または多結晶シリコン膜の下地に形成されていることを特徴とする請求項9に記載の画像表示装置の製造方法。

- 前記アクティブ・マトリクス基板上のアモルファスシリコン膜あるいは多結晶シリコン膜に前記パルス幅および/またはパルス間隔が変調されたレーザの照射で位置決めマークを形成する工程を有することを特徴とする請求項1に記載の画像表示装置の製造方法。

- 前記アクティブ回路に薄膜トランジスタを形成する工程を含むことを特徴とする請求項1に記載の画像表示装置の製造方法。

- 前記アクティブ・マトリクス基板に所定の間隔で対向配置されたカラーフィルタ基板を貼り合わせる工程と、

前記アクティブ・マトリクス基板と前記カラーフィルタ基板の間に液晶を封入する工程とを少なくとも含むことを特徴とする請求項1に記載の画像表示装置の製造方法。 - 前記アクティブ・マトリクス基板の前記画素領域を構成する画素毎に有機EL層を形成する工程と、

前記アクティブ・マトリクス基板の前記有機EL層側を覆って保護基板を貼り合わせる工程とを少なくとも含むことを特徴とする請求項1に記載の画像表示装置の製造方法。 - 前記CWレーザ光の波長が200nm乃至1200nmの固体レーザであることを特徴とする請求項1に記載の画像表示装置の製造方法。

- 前記CWレーザ光の照射幅が20μm乃至1000μmであることを特徴とする請求項1に記載の画像表示装置の製造方法。

- 前記CWレーザ光または基板の走査速度が50mm/s乃至3000mm/sであることを特徴とする請求項1に記載の画像表示装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002215239A JP4813743B2 (ja) | 2002-07-24 | 2002-07-24 | 画像表示装置の製造方法 |

| US10/602,738 US6949452B2 (en) | 2002-07-24 | 2003-06-25 | Method for fabricating image display device |

| US11/172,958 US7192852B2 (en) | 2002-07-24 | 2005-07-05 | Method for fabricating image display device |

| US11/702,576 US7666769B2 (en) | 2002-07-24 | 2007-02-06 | Method for fabricating image display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002215239A JP4813743B2 (ja) | 2002-07-24 | 2002-07-24 | 画像表示装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005208022A Division JP2005347764A (ja) | 2005-07-19 | 2005-07-19 | 画像表示装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004056058A JP2004056058A (ja) | 2004-02-19 |

| JP2004056058A5 JP2004056058A5 (ja) | 2005-10-27 |

| JP4813743B2 true JP4813743B2 (ja) | 2011-11-09 |

Family

ID=31937323

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002215239A Expired - Fee Related JP4813743B2 (ja) | 2002-07-24 | 2002-07-24 | 画像表示装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US6949452B2 (ja) |

| JP (1) | JP4813743B2 (ja) |

Families Citing this family (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3903761B2 (ja) * | 2001-10-10 | 2007-04-11 | 株式会社日立製作所 | レ−ザアニ−ル方法およびレ−ザアニ−ル装置 |

| US7504387B2 (en) * | 2002-10-16 | 2009-03-17 | Arthrodynamic Technologies, Animal Health Division, Inc. | Glycosaminoglycan composition and method for treatment and prevention of interstitial cystitis |

| JP4772261B2 (ja) * | 2002-10-31 | 2011-09-14 | シャープ株式会社 | 表示装置の基板の製造方法及び結晶化装置 |

| US7145229B2 (en) * | 2002-11-14 | 2006-12-05 | The Regents Of The University Of California | Silicone metalization |

| JP4503344B2 (ja) * | 2003-04-21 | 2010-07-14 | 株式会社半導体エネルギー研究所 | ビーム照射装置および半導体装置の作製方法 |

| US7220627B2 (en) * | 2003-04-21 | 2007-05-22 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device where the scanning direction changes between regions during crystallization and process |

| CN1595477A (zh) * | 2003-09-08 | 2005-03-16 | 三洋电机株式会社 | 显示装置 |

| JP5159021B2 (ja) * | 2003-12-02 | 2013-03-06 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2005217209A (ja) * | 2004-01-30 | 2005-08-11 | Hitachi Ltd | レーザアニール方法およびレーザアニール装置 |

| EP1728271B1 (en) | 2004-03-26 | 2016-06-08 | Semiconductor Energy Laboratory Co, Ltd. | Laser irradiation method and laser irradiation apparatus |

| US20050237895A1 (en) * | 2004-04-23 | 2005-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Laser irradiation apparatus and method for manufacturing semiconductor device |

| JP2005340788A (ja) * | 2004-04-28 | 2005-12-08 | Semiconductor Energy Lab Co Ltd | レーザ照射方法およびそれを用いた半導体装置の作製方法 |

| JP5250181B2 (ja) * | 2004-05-06 | 2013-07-31 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8525075B2 (en) | 2004-05-06 | 2013-09-03 | Semiconductor Energy Laboratory Co., Ltd. | Laser irradiation apparatus |

| JP5072197B2 (ja) * | 2004-06-18 | 2012-11-14 | 株式会社半導体エネルギー研究所 | レーザ照射装置およびレーザ照射方法 |

| US7820936B2 (en) * | 2004-07-02 | 2010-10-26 | Boston Scientific Scimed, Inc. | Method and apparatus for controlling and adjusting the intensity profile of a laser beam employed in a laser welder for welding polymeric and metallic components |

| JP2006019609A (ja) * | 2004-07-05 | 2006-01-19 | Hitachi Displays Ltd | 画像表示装置 |

| JP2006060191A (ja) * | 2004-07-23 | 2006-03-02 | Seiko Epson Corp | 薄膜半導体装置及びその製造方法、電気光学装置、電子機器 |

| JP4942959B2 (ja) * | 2004-07-30 | 2012-05-30 | 株式会社半導体エネルギー研究所 | レーザ照射装置およびレーザ照射方法 |

| JP5352040B2 (ja) * | 2004-08-23 | 2013-11-27 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8304313B2 (en) | 2004-08-23 | 2012-11-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and its manufacturing method |

| JP5030405B2 (ja) * | 2004-09-01 | 2012-09-19 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US7393764B2 (en) | 2004-11-29 | 2008-07-01 | Semiconductor Energy Laboratory Co., Ltd. | Laser treatment apparatus, laser treatment method, and manufacturing method of semiconductor device |

| JP5019739B2 (ja) * | 2004-11-29 | 2012-09-05 | 株式会社半導体エネルギー研究所 | レーザ処理装置 |

| US8395084B2 (en) * | 2005-05-02 | 2013-03-12 | Semiconductor Energy Laboratory Co., Ltd. | Laser irradiation apparatus and laser irradiation method |

| JP5085014B2 (ja) | 2005-05-26 | 2012-11-28 | 株式会社ジャパンディスプレイイースト | 半導体装置の製造方法及び半導体装置 |

| JP2005347764A (ja) * | 2005-07-19 | 2005-12-15 | Hitachi Ltd | 画像表示装置の製造方法 |

| JP2007088364A (ja) * | 2005-09-26 | 2007-04-05 | Hitachi Displays Ltd | 表示装置 |

| WO2007069516A1 (en) * | 2005-12-16 | 2007-06-21 | Semiconductor Energy Laboratory Co., Ltd. | Laser irradiation apparatus, laser irradiation method, and manufacturing method of semiconductor device |

| JP5130633B2 (ja) * | 2006-03-02 | 2013-01-30 | ソニー株式会社 | 画像表示デバイスおよび画像表示装置 |

| US20080045041A1 (en) * | 2006-08-17 | 2008-02-21 | Toshiba America Electronic Components, Inc. | Liquid Immersion Laser Spike Anneal |

| US20080090396A1 (en) * | 2006-10-06 | 2008-04-17 | Semiconductor Energy Laboratory Co., Ltd. | Light exposure apparatus and method for making semiconductor device formed using the same |

| JP5007192B2 (ja) * | 2006-10-06 | 2012-08-22 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TW200826055A (en) * | 2006-12-06 | 2008-06-16 | Gigno Technology Co Ltd | Display apparatus and manufacturing method thereof |

| TW200841474A (en) * | 2007-04-13 | 2008-10-16 | Chunghwa Picture Tubes Ltd | Method for fabricating thin film transistors |

| US7906316B2 (en) * | 2007-07-05 | 2011-03-15 | The Johns Hopkins University | Apparatus for detecting molecules |

| TWI464880B (zh) * | 2008-09-04 | 2014-12-11 | Au Optronics Corp | 薄膜電晶體陣列基板及其製作方法 |

| JP5517832B2 (ja) * | 2010-08-20 | 2014-06-11 | 住友重機械工業株式会社 | レーザアニール装置及びレーザアニール方法 |

| JP6439297B2 (ja) * | 2014-07-04 | 2018-12-19 | 富士電機株式会社 | 不純物導入方法、不純物導入装置及び半導体素子の製造方法 |

| CN105489487A (zh) | 2016-01-14 | 2016-04-13 | 京东方科技集团股份有限公司 | 低温多晶硅薄膜及晶体管的制备方法、激光晶化装置 |

| CN107863355B (zh) * | 2017-10-26 | 2022-01-25 | 上海中航光电子有限公司 | 一种显示基板、显示装置和显示基板的制造方法 |

| DE102018131023A1 (de) * | 2018-12-05 | 2020-06-25 | Osram Opto Semiconductors Gmbh | Optoelektronische leuchtvorrichtung mit einem pwm-transistor und verfahren zum herstellen oder steuern einer optoelektronischen leuchtvorrichtung |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS56145198A (en) * | 1980-04-04 | 1981-11-11 | Hitachi Ltd | Forming method of single crystal silicon membrane and device therefor |

| KR100299292B1 (ko) * | 1993-11-02 | 2001-12-01 | 이데이 노부유끼 | 다결정실리콘박막형성방법및그표면처리장치 |

| KR100321541B1 (ko) * | 1994-03-09 | 2002-06-20 | 야마자끼 순페이 | 능동 매트릭스 디스플레이 장치의 작동 방법 |

| JPH08264802A (ja) * | 1995-03-28 | 1996-10-11 | Semiconductor Energy Lab Co Ltd | 半導体作製方法、薄膜トランジスタ作製方法および薄膜トランジスタ |

| JP2000068520A (ja) * | 1997-12-17 | 2000-03-03 | Matsushita Electric Ind Co Ltd | 半導体薄膜、その製造方法、および製造装置、ならびに半導体素子、およびその製造方法 |

| JP4954359B2 (ja) * | 1999-02-12 | 2012-06-13 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2000275668A (ja) * | 1999-03-19 | 2000-10-06 | Fujitsu Ltd | レーザアニーリング装置、液晶表示装置及びその製造方法 |

| JP2000277450A (ja) * | 1999-03-24 | 2000-10-06 | Matsushita Electric Ind Co Ltd | レーザアニール装置及びこの装置を用いた薄膜トランジスタの製造方法 |

| JP2001023899A (ja) * | 1999-07-13 | 2001-01-26 | Hitachi Ltd | 半導体薄膜とその半導体膜を用いた液晶表示装置及びその製造方法 |

| JP3491571B2 (ja) * | 1999-07-13 | 2004-01-26 | 日本電気株式会社 | 半導体薄膜の形成方法 |

| JP2001127302A (ja) * | 1999-10-28 | 2001-05-11 | Hitachi Ltd | 半導体薄膜基板、半導体装置、半導体装置の製造方法および電子装置 |

| KR100303142B1 (ko) * | 1999-10-29 | 2001-11-02 | 구본준, 론 위라하디락사 | 액정표시패널의 제조방법 |

| JP2001189288A (ja) * | 1999-12-20 | 2001-07-10 | Ind Technol Res Inst | イオン注入利用の基板ダイシング法 |

| JP2001203168A (ja) * | 2000-01-21 | 2001-07-27 | Hitachi Ltd | 電子ビーム処理装置 |

| WO2001059823A1 (fr) * | 2000-02-08 | 2001-08-16 | Matsushita Electric Industrial Co., Ltd. | Dispositif de recuit pour lampe et substrat du dispositif d'affichage |

| US6368945B1 (en) * | 2000-03-16 | 2002-04-09 | The Trustees Of Columbia University In The City Of New York | Method and system for providing a continuous motion sequential lateral solidification |

| US6872607B2 (en) * | 2000-03-21 | 2005-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device |

| US6737672B2 (en) * | 2000-08-25 | 2004-05-18 | Fujitsu Limited | Semiconductor device, manufacturing method thereof, and semiconductor manufacturing apparatus |

| JP4925528B2 (ja) * | 2000-09-29 | 2012-04-25 | 三洋電機株式会社 | 表示装置 |

| JP2002151697A (ja) * | 2000-11-14 | 2002-05-24 | Sharp Corp | 半導体集積回路およびそれを用いた画像表示装置 |

| JP3859978B2 (ja) * | 2001-02-28 | 2006-12-20 | ザ トラスティーズ オブ コロンビア ユニヴァーシティ イン ザ シティ オブ ニューヨーク | 基板上の半導体材料膜に横方向に延在する結晶領域を形成する装置 |

| US6664147B2 (en) * | 2001-02-28 | 2003-12-16 | Sharp Laboratories Of America, Inc. | Method of forming thin film transistors on predominantly <100> polycrystalline silicon films |

| JP3842072B2 (ja) | 2001-05-25 | 2006-11-08 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタの作製方法 |

| JP4784955B2 (ja) * | 2001-07-18 | 2011-10-05 | 株式会社 液晶先端技術開発センター | 薄膜半導体装置の製造方法 |

| JP3857085B2 (ja) | 2001-08-03 | 2006-12-13 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ及びその作製方法 |

| JP3824898B2 (ja) * | 2001-09-14 | 2006-09-20 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| CN1216394C (zh) * | 2001-09-25 | 2005-08-24 | 松下电工株式会社 | 场致发射型电子源 |

| JP4135347B2 (ja) * | 2001-10-02 | 2008-08-20 | 株式会社日立製作所 | ポリシリコン膜生成方法 |

| JP3903761B2 (ja) * | 2001-10-10 | 2007-04-11 | 株式会社日立製作所 | レ−ザアニ−ル方法およびレ−ザアニ−ル装置 |

| US7078322B2 (en) * | 2001-11-29 | 2006-07-18 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a thin film transistor |

| JP2003179068A (ja) * | 2001-12-12 | 2003-06-27 | Hitachi Ltd | 画像表示装置およびその製造方法 |

| JP3992976B2 (ja) * | 2001-12-21 | 2007-10-17 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4011344B2 (ja) * | 2001-12-28 | 2007-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2003197526A (ja) * | 2001-12-28 | 2003-07-11 | Seiko Epson Corp | 半導体装置の製造方法、半導体装置、表示装置、および電子機器 |

| US7023500B2 (en) * | 2002-06-05 | 2006-04-04 | Hitachi, Ltd. | Display device with active-matrix transistor having silicon film modified by selective laser irradiation |

-

2002

- 2002-07-24 JP JP2002215239A patent/JP4813743B2/ja not_active Expired - Fee Related

-

2003

- 2003-06-25 US US10/602,738 patent/US6949452B2/en not_active Expired - Lifetime

-

2005

- 2005-07-05 US US11/172,958 patent/US7192852B2/en not_active Expired - Lifetime

-

2007

- 2007-02-06 US US11/702,576 patent/US7666769B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7666769B2 (en) | 2010-02-23 |

| US6949452B2 (en) | 2005-09-27 |

| US20050244996A1 (en) | 2005-11-03 |

| JP2004056058A (ja) | 2004-02-19 |

| US20070134893A1 (en) | 2007-06-14 |

| US20040082090A1 (en) | 2004-04-29 |

| US7192852B2 (en) | 2007-03-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4813743B2 (ja) | 画像表示装置の製造方法 | |

| US20210327986A1 (en) | Light emitting device | |

| US6797550B2 (en) | Semiconductor device and manufacturing method therefor | |

| JP2004054168A (ja) | 画像表示装置 | |

| US7253864B2 (en) | Active matrix display device with active element including a semiconductor film formed of an aggregate of single crystals each extending in the same direction | |

| US7557376B2 (en) | Display device using first and second semiconductor films of different crystallinity and boundary section therebetween | |

| US7033434B2 (en) | Mask for crystallizing, method of crystallizing amorphous silicon and method of manufacturing array substrate using the same | |

| US7132343B2 (en) | Method and apparatus for manufacturing display panel | |

| US20080166668A1 (en) | Laser mask and method of crystallization using the same | |

| US7700892B2 (en) | Sequential lateral solidification device and method of crystallizing silicon using the same | |

| JP2007183656A (ja) | アクティブマトリックス有機電界発光ディスプレイ装置及びその製造方法 | |

| EP1860699A1 (en) | Display having thin fim transistors with channel region of varying crystal state | |

| JP4336119B2 (ja) | アクティブマトリクス型led表示装置およびその要素 | |

| TW575866B (en) | Display device with active-matrix transistor and method for manufacturing the same | |

| JP5090690B2 (ja) | 半導体薄膜の製造方法、薄膜トランジスタの製造方法、及び半導体薄膜の製造装置 | |

| JP2005347764A (ja) | 画像表示装置の製造方法 | |

| KR20050078191A (ko) | 반도체 박막의 제조 방법 및 화상 표시 장치 | |

| JP4278013B2 (ja) | 薄膜素子の製造方法 | |

| JP2004165598A (ja) | アクティブ・マトリクス型表示装置とその製造方法 | |

| JP2006054223A (ja) | 半導体薄膜の結晶化方法、結晶化された半導体薄膜を有する基板、そして半導体薄膜の結晶化装置 | |

| JPH0566422A (ja) | 液晶表示装置の製造方法及びセンサの製造方法 | |

| JP2003209118A6 (ja) | アクティブマトリックス有機電界発光ディスプレイ装置及びその製造方法 | |

| JP2004138912A (ja) | ディスプレイ装置とその製造方法 | |

| JP2007141945A (ja) | 表示装置の製造方法及び表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050719 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050719 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080109 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080708 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080828 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20080912 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20081003 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20100824 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100824 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20110218 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20110218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110325 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110825 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4813743 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140902 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |