JP4675302B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4675302B2 JP4675302B2 JP2006258329A JP2006258329A JP4675302B2 JP 4675302 B2 JP4675302 B2 JP 4675302B2 JP 2006258329 A JP2006258329 A JP 2006258329A JP 2006258329 A JP2006258329 A JP 2006258329A JP 4675302 B2 JP4675302 B2 JP 4675302B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- switching element

- control signal

- semiconductor switching

- insulated gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 47

- 230000004044 response Effects 0.000 claims description 17

- 230000007704 transition Effects 0.000 claims description 16

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 claims description 14

- 101100484930 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) VPS41 gene Proteins 0.000 description 27

- 230000008859 change Effects 0.000 description 22

- 238000000034 method Methods 0.000 description 14

- 238000011084 recovery Methods 0.000 description 14

- 238000010586 diagram Methods 0.000 description 11

- 230000004048 modification Effects 0.000 description 10

- 238000012986 modification Methods 0.000 description 10

- 230000006378 damage Effects 0.000 description 3

- 230000008901 benefit Effects 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 230000020169 heat generation Effects 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/16—Modifications for eliminating interference voltages or currents

- H03K17/168—Modifications for eliminating interference voltages or currents in composite switches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0248—Particular design considerations for integrated circuits for electrical or thermal protection, e.g. electrostatic discharge [ESD] protection

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K17/081—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit

- H03K17/0814—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit by measures taken in the output circuit

- H03K17/08148—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit by measures taken in the output circuit in composite switches

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Conversion In General (AREA)

- Electronic Switches (AREA)

- Inverter Devices (AREA)

Description

図1は、本発明の実施の形態1に従うインバータ装置1の回路構成図である。

図3は、本発明の実施の形態1の変形例に従うインバータ装置10の回路構成図である。

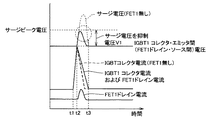

絶縁ゲート型バイポーラトランジスタが導通状態から非導通状態に遷移し始める際、上述したように絶縁ゲート型バイポーラトランジスタIGBT1のコレクタ・エミッタ間にはサージ電圧が生じる。このサージ電圧がツェナーダイオードZD1のツェナー電圧を越えて、抵抗R1,R2に電圧が印加されることになる。そして、抵抗R1,R2の抵抗分割に従う電圧が接続ノードに生成される。比較器COMPは、抵抗分割に従う接続ノードに生成された電圧と、基準電圧Vref1とを比較して、基準電圧Vref1以上の電圧が接続ノードに生成された場合に「H」レベルの比較結果をワンショットトリガパルス発生器15に出力する。

上記の実施の形態1においては、絶縁ゲート型バイポーラトランジスタIGBT1の導通状態から非導通状態に遷移する際に生じるサージ電圧すなわちターンオフサージ電圧を抑制する方式について説明したが、本実施の形態2においては、絶縁ゲート型バイポーラトランジスタIGBT1の非導通状態から導通状態に遷移する際に生じるサージ電圧すなわちターンオンサージ電圧を抑制する方式について説明する。

図4を参照して、本発明の実施の形態2に従うインバータ装置は、実施の形態1で説明したインバータ装置1と同様の回路構成図である。

図6は、本発明の実施の形態2の変形例に従うインバータ装置20の回路構成図である。

絶縁ゲート型バイポーラトランジスタIGBT1が非導通状態から導通状態に遷移し始める際、上述したようにダイオードD2あるいは絶縁ゲート型バイポーラトランジスタIGBT2のコレクタ・エミッタ間の電圧Vce2が変化し始め、リカバリ電流の電流変化率dI/dtに依存してサージ電圧が生じる。このサージ電圧がツェナーダイオードZD2のツェナー電圧を越えて、抵抗R3,R4に電圧が印加されることになる。そして、抵抗R3,R4の抵抗分割に従う電圧が接続ノードに生成される。比較器COMP#は、抵抗分割に従う接続ノードに生成された電圧と、基準電圧Vref2とを比較して、基準電圧Vref以上の電圧が接続ノードに生成された場合に「H」レベルの比較結果をワンショットトリガパルス発生器15#に出力する。

Claims (2)

- 第1の電圧と、出力ノードとの間に設けられ、第1の制御信号の入力に応答して駆動する第1の半導体スイッチング素子と、前記第1の半導体スイッチング素子と直列に前記出力ノードと第1の電圧よりも低い第2の電圧との間に接続され、第2の制御信号の入力に応答して駆動する第2の半導体スイッチング素子とを有するハーフブリッジ回路と、

前記第1の半導体スイッチング素子に対応して設けられ、前記第1の半導体スイッチング素子と並列に接続され、第3の制御信号の入力を受けて導通/非導通となる第1のMOSトランジスタと、

前記第1の制御信号の入力に応答して前記第1の半導体スイッチング素子が導通状態から非導通状態に移行する期間において生じる所定のサージ電圧を検知して、前記第3の制御信号を生成する信号生成回路とを備え、

前記信号生成回路は、

前記第1の電圧と前記第2の電圧との間に直列に接続された第1および第2の抵抗素子と、

前記第1および第2の抵抗素子と前記第1の電圧との間に設けられ、カソード側が前記第1の電圧と接続され、アノード側が前記第1および第2の抵抗素子と接続される定電圧ダイオードと、

前記第1および第2の抵抗素子の接続ノードに生成される電圧と基準電圧とを比較する比較器と、

前記比較器の比較結果に基づいて前記第3の制御信号であるワンショットトリガパルス信号を生成するワンショットトリガパルス信号生成回路とを含む、半導体装置。 - 第1の電圧と、出力ノードとの間に設けられ、第1の制御信号の入力に応答して駆動する第1の半導体スイッチング素子と、前記第1の半導体スイッチング素子と直列に前記出力ノードと第1の電圧よりも低い第2の電圧との間に接続され、第2の制御信号の入力に応答して駆動する第2の半導体スイッチング素子とを有するハーフブリッジ回路と、

前記第2の半導体スイッチング素子に対応して設けられ、前記第2の半導体スイッチング素子と並列に接続され、第3の制御信号の入力を受けて導通/非導通となる第1のMOSトランジスタと、

前記第1の制御信号の入力に応答して前記第1の半導体スイッチング素子が非導通状態から導通状態に移行する期間において生じる所定のサージ電圧を検知して、前記第3の制御信号を生成する信号生成回路とを備え、

前記信号生成回路は、

前記出力ノードと前記第2の電圧との間に直列に接続された第1および第2の抵抗素子と、

前記第1および第2の抵抗素子と前記出力ノードとの間に設けられ、カソード側が前記出力ノードと接続され、アノード側が前記第1および第2の抵抗素子と接続される定電圧ダイオードと、

前記第1および第2の抵抗素子の接続ノードに生成される電圧と基準電圧とを比較する比較器と、

前記比較器の比較結果に基づいて前記第3の制御信号であるワンショットトリガパルス信号を生成するワンショットトリガパルス信号生成回路とを含む、半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006258329A JP4675302B2 (ja) | 2006-09-25 | 2006-09-25 | 半導体装置 |

| US11/626,566 US7830196B2 (en) | 2006-09-25 | 2007-01-24 | Semiconductor device alleviating or preventing surge voltage |

| DE102007019524.0A DE102007019524B4 (de) | 2006-09-25 | 2007-04-25 | Halbleitervorrichtung, die einen Spannungsstoß verringert oder verhindert |

| CN2007101011037A CN101154880B (zh) | 2006-09-25 | 2007-04-26 | 抑制浪涌电压的半导体器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006258329A JP4675302B2 (ja) | 2006-09-25 | 2006-09-25 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008079475A JP2008079475A (ja) | 2008-04-03 |

| JP2008079475A5 JP2008079475A5 (ja) | 2009-04-02 |

| JP4675302B2 true JP4675302B2 (ja) | 2011-04-20 |

Family

ID=39154777

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006258329A Active JP4675302B2 (ja) | 2006-09-25 | 2006-09-25 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7830196B2 (ja) |

| JP (1) | JP4675302B2 (ja) |

| CN (1) | CN101154880B (ja) |

| DE (1) | DE102007019524B4 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10756718B2 (en) | 2018-10-19 | 2020-08-25 | Hyundai Motor Company | Gate driving apparatus for power semiconductor device |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102336059B (zh) * | 2010-07-22 | 2014-10-29 | 北京美科艺数码科技发展有限公司 | 一种压电喷头控制板 |

| JP5413472B2 (ja) * | 2011-06-15 | 2014-02-12 | 株式会社デンソー | 半導体装置 |

| US8717717B2 (en) | 2011-08-04 | 2014-05-06 | Futurewei Technologies, Inc. | High efficiency power regulator and method |

| WO2013150567A1 (ja) * | 2012-04-06 | 2013-10-10 | 三菱電機株式会社 | 複合半導体スイッチ装置 |

| JP5783997B2 (ja) * | 2012-12-28 | 2015-09-24 | 三菱電機株式会社 | 電力用半導体装置 |

| CN103368362A (zh) * | 2013-05-27 | 2013-10-23 | 苏州贝克微电子有限公司 | 在半桥配置下的双功率场效应管的驱动电路 |

| CN105474545B (zh) * | 2013-06-14 | 2019-04-26 | 通用电气技术有限公司 | 半导体开关串 |

| TWI543504B (zh) * | 2013-08-15 | 2016-07-21 | 天鈺科技股份有限公司 | 靜電放電防護電路 |

| US9722581B2 (en) | 2014-07-24 | 2017-08-01 | Eaton Corporation | Methods and systems for operating hybrid power devices using driver circuits that perform indirect instantaneous load current sensing |

| EP3065296A1 (en) * | 2015-03-05 | 2016-09-07 | General Electric Technology GmbH | Semiconductor switching string |

| JP6471550B2 (ja) * | 2015-03-17 | 2019-02-20 | サンケン電気株式会社 | スナバ回路 |

| US9819339B2 (en) * | 2015-05-13 | 2017-11-14 | Infineon Technologies Austria Ag | Method and circuit for reducing collector-emitter voltage overshoot in an insulated gate bipolar transistor |

| JP6601086B2 (ja) * | 2015-09-16 | 2019-11-06 | 富士電機株式会社 | 半導体装置及びその製造方法 |

| GB2542805A (en) * | 2015-09-30 | 2017-04-05 | General Electric Technology Gmbh | Semiconductor switching string |

| US10404188B2 (en) | 2015-11-16 | 2019-09-03 | Aisin Aw Co., Ltd. | Power conversion devices |

| JP6680102B2 (ja) * | 2016-06-16 | 2020-04-15 | 富士電機株式会社 | 半導体集積回路装置 |

| US10411689B2 (en) * | 2016-07-28 | 2019-09-10 | Infineon Technologies Ag | Increase robustness of devices to overvoltage transients |

| EP3429046A1 (de) | 2017-07-14 | 2019-01-16 | Siemens Aktiengesellschaft | Elektronischer schalter mit überspannungsbegrenzer |

| CN115632642B (zh) * | 2022-12-21 | 2023-03-10 | 杭州飞仕得科技股份有限公司 | 一种igbt关断电压尖峰抑制电路及相关设备 |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01280355A (ja) * | 1987-12-23 | 1989-11-10 | Asea Brown Boveri Ag | ターンオフ機構及び過電圧保護手段を備えたサイリスタ |

| JPH04354156A (ja) * | 1991-05-31 | 1992-12-08 | Fuji Electric Co Ltd | 半導体スイッチング装置 |

| JPH05304782A (ja) * | 1992-04-24 | 1993-11-16 | Toshiba Corp | 電力変換装置 |

| JPH0698554A (ja) * | 1992-09-14 | 1994-04-08 | Matsushita Electric Works Ltd | インバータ装置 |

| JPH07147726A (ja) * | 1993-11-26 | 1995-06-06 | Fuji Electric Co Ltd | 半導体装置の過電圧制限回路 |

| JPH07288456A (ja) * | 1994-02-23 | 1995-10-31 | Fuji Electric Co Ltd | 半導体装置の過電圧クランプ回路 |

| JP2000324797A (ja) * | 1999-05-14 | 2000-11-24 | Toshiba Corp | スナバ装置 |

| JP2002078104A (ja) * | 2000-08-24 | 2002-03-15 | Nippon Yusoki Co Ltd | 荷役車両の制御装置 |

| JP2002135973A (ja) * | 2000-10-20 | 2002-05-10 | Toshiba Corp | 過電圧保護回路 |

| JP2005295653A (ja) * | 2004-03-31 | 2005-10-20 | Densei Lambda Kk | スイッチング電源装置 |

| JP2006042410A (ja) * | 2004-07-22 | 2006-02-09 | Toshiba Corp | スナバ装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4366522A (en) * | 1979-12-10 | 1982-12-28 | Reliance Electric Company | Self-snubbing bipolar/field effect (biofet) switching circuits and method |

| JPH0646703B2 (ja) * | 1985-08-21 | 1994-06-15 | 日本電信電話株式会社 | スイツチング回路 |

| GB9104482D0 (en) * | 1991-03-04 | 1991-04-17 | Cooperheat Int Ltd | Solid state dc power supply |

| JPH05276650A (ja) * | 1992-03-19 | 1993-10-22 | Shin Kobe Electric Mach Co Ltd | 半導体スイッチング素子保護用スナバ回路 |

| US5666280A (en) * | 1993-05-07 | 1997-09-09 | Philips Electronics North America Corporation | High voltage integrated circuit driver for half-bridge circuit employing a jet to emulate a bootstrap diode |

| JPH10209832A (ja) * | 1997-01-27 | 1998-08-07 | Fuji Electric Co Ltd | 半導体スイッチ回路 |

| JP3290388B2 (ja) | 1997-09-10 | 2002-06-10 | 株式会社東芝 | インバータ装置 |

| JP2000012780A (ja) * | 1998-06-26 | 2000-01-14 | Toshiba Corp | 半導体スナバ装置及び半導体装置 |

| JP2000092817A (ja) * | 1998-09-16 | 2000-03-31 | Toshiba Corp | スナバ装置及び電力変換装置 |

| JP2001238348A (ja) * | 2000-02-21 | 2001-08-31 | Nissan Motor Co Ltd | 誘導負荷用電源装置の保護回路 |

| DE10219760A1 (de) * | 2002-05-02 | 2003-11-20 | Eupec Gmbh & Co Kg | Halbbrückenschaltung |

| US7176743B2 (en) * | 2005-03-18 | 2007-02-13 | Agere Systems Inc. | Driver circuit capable of providing rise and fall transitions that step smoothly in the transition regions |

-

2006

- 2006-09-25 JP JP2006258329A patent/JP4675302B2/ja active Active

-

2007

- 2007-01-24 US US11/626,566 patent/US7830196B2/en active Active

- 2007-04-25 DE DE102007019524.0A patent/DE102007019524B4/de active Active

- 2007-04-26 CN CN2007101011037A patent/CN101154880B/zh active Active

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01280355A (ja) * | 1987-12-23 | 1989-11-10 | Asea Brown Boveri Ag | ターンオフ機構及び過電圧保護手段を備えたサイリスタ |

| JPH04354156A (ja) * | 1991-05-31 | 1992-12-08 | Fuji Electric Co Ltd | 半導体スイッチング装置 |

| JPH05304782A (ja) * | 1992-04-24 | 1993-11-16 | Toshiba Corp | 電力変換装置 |

| JPH0698554A (ja) * | 1992-09-14 | 1994-04-08 | Matsushita Electric Works Ltd | インバータ装置 |

| JPH07147726A (ja) * | 1993-11-26 | 1995-06-06 | Fuji Electric Co Ltd | 半導体装置の過電圧制限回路 |

| JPH07288456A (ja) * | 1994-02-23 | 1995-10-31 | Fuji Electric Co Ltd | 半導体装置の過電圧クランプ回路 |

| JP2000324797A (ja) * | 1999-05-14 | 2000-11-24 | Toshiba Corp | スナバ装置 |

| JP2002078104A (ja) * | 2000-08-24 | 2002-03-15 | Nippon Yusoki Co Ltd | 荷役車両の制御装置 |

| JP2002135973A (ja) * | 2000-10-20 | 2002-05-10 | Toshiba Corp | 過電圧保護回路 |

| JP2005295653A (ja) * | 2004-03-31 | 2005-10-20 | Densei Lambda Kk | スイッチング電源装置 |

| JP2006042410A (ja) * | 2004-07-22 | 2006-02-09 | Toshiba Corp | スナバ装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10756718B2 (en) | 2018-10-19 | 2020-08-25 | Hyundai Motor Company | Gate driving apparatus for power semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101154880B (zh) | 2012-08-08 |

| JP2008079475A (ja) | 2008-04-03 |

| DE102007019524A1 (de) | 2008-04-10 |

| US7830196B2 (en) | 2010-11-09 |

| CN101154880A (zh) | 2008-04-02 |

| US20080074816A1 (en) | 2008-03-27 |

| DE102007019524B4 (de) | 2020-12-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4675302B2 (ja) | 半導体装置 | |

| US11139808B2 (en) | Semiconductor device and power conversion system | |

| CN105577153B (zh) | 半导体装置 | |

| JP3598933B2 (ja) | 電力変換装置 | |

| EP0431492B1 (en) | Bridge type power converter with improved efficiency | |

| JP3812353B2 (ja) | 半導体電力変換装置 | |

| WO2014123046A1 (ja) | ゲート駆動回路 | |

| JP5993749B2 (ja) | 半導体装置のゲート駆動回路およびそれを用いた電力変換装置 | |

| JP2019165542A (ja) | 半導体装置 | |

| JP5542719B2 (ja) | 電力用半導体素子の駆動保護回路 | |

| JP2017220861A (ja) | ゲート駆動回路 | |

| JP6714834B2 (ja) | 3レベル電力変換回路 | |

| WO2023062745A1 (ja) | 電力用半導体素子の駆動回路、電力用半導体モジュール、および電力変換装置 | |

| CN111869068B (zh) | 开关装置以及开关装置的控制方法 | |

| JP4321491B2 (ja) | 電圧駆動型半導体素子の駆動装置 | |

| JPH08322240A (ja) | 自己消弧形半導体素子のゲート制御方法 | |

| JP2006352931A (ja) | スイッチング素子保護回路 | |

| JPWO2020121419A1 (ja) | 電力用半導体素子の駆動回路、およびそれを用いた電力用半導体モジュール | |

| JP2011055616A (ja) | 電流制御型駆動回路 | |

| KR19990006822A (ko) | 충전발전기의 제어장치 | |

| JP2006129643A (ja) | スイッチング制御装置及び半導体集積回路装置 | |

| JP2003033044A (ja) | スナバ回路 | |

| JP6731885B2 (ja) | 半導体装置 | |

| CN113169662A (zh) | 电力转换装置 | |

| JP2002171746A (ja) | 半導体電力変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101014 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101217 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110118 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110125 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140204 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4675302 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |