JP4265788B2 - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP4265788B2 JP4265788B2 JP2004250982A JP2004250982A JP4265788B2 JP 4265788 B2 JP4265788 B2 JP 4265788B2 JP 2004250982 A JP2004250982 A JP 2004250982A JP 2004250982 A JP2004250982 A JP 2004250982A JP 4265788 B2 JP4265788 B2 JP 4265788B2

- Authority

- JP

- Japan

- Prior art keywords

- csbl

- auxiliary

- liquid crystal

- voltage

- pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3655—Details of drivers for counter electrodes, e.g. common electrodes for pixel capacitors or supplementary storage capacitors

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134345—Subdivided pixels, e.g. for grey scale or redundancy

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0443—Pixel structures with several sub-pixels for the same colour in a pixel, not specifically used to display gradations

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0443—Pixel structures with several sub-pixels for the same colour in a pixel, not specifically used to display gradations

- G09G2300/0447—Pixel structures with several sub-pixels for the same colour in a pixel, not specifically used to display gradations for multi-domain technique to improve the viewing angle in a liquid crystal display, such as multi-vertical alignment [MVA]

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0876—Supplementary capacities in pixels having special driving circuits and electrodes instead of being connected to common electrode or ground; Use of additional capacitively coupled compensation electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0223—Compensation for problems related to R-C delay and attenuation in electrodes of matrix panels, e.g. in gate electrodes or on-substrate video signal electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0247—Flicker reduction other than flicker reduction circuits used for single beam cathode-ray tubes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0271—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping

- G09G2320/0276—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping for the purpose of adaptation to the characteristics of a display device, i.e. gamma correction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/028—Improving the quality of display appearance by changing the viewing angle properties, e.g. widening the viewing angle, adapting the viewing angle to the view direction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2074—Display of intermediate tones using sub-pixels

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Liquid Crystal (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

Description

前記L本の電気的に独立な補助容量幹線に接続されるCSバスラインが、

CSBL_( p+2・(1−1) )B,( p+2・(1−1)+1 )A、

CSBL_( p+2・(2−1) )B,( p+2・(2−1)+1 )A、

CSBL_( p+2・(3−1) )B,( p+2・(3−1)+1 )A、

・

・

・

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A

と、

CSBL_( p+2・(1−1)+K・L+1 )B,( p+2・(1−1)+K・L+2 )A、

CSBL_( p+2・(2−1)+K・L+1 )B,( p+2・(2−1)+K・L+2 )A、

CSBL_( p+2・(3−1)+K・L+1 )B,( p+2・(3−1)+K・L+2 )A、

・

・

・

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(3−1)+K・L+2 )A

或いは

CSBL_( p+2・(1−1)+1 )B,( p+2・(1−1)+2 )A、

CSBL_( p+2・(2−1)+1 )B,( p+2・(2−1)+2 )A、

CSBL_( p+2・(3−1)+1 )B,( p+2・(3−1)+2 )A、

・

・

・

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(1−1)+K・L )B,( p+2・(1−1)+K・L+1 )A、

CSBL_( p+2・(2−1)+K・L )B,( p+2・(2−1)+K・L+1 )A、

CSBL_( p+2・(3−1)+K・L )B,( p+2・(3−1)+K・L+1 )A、

・

・

・

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

但し、p=1,3,5,・・・もしくはp=0,2,4,・・・

の関係を満足する。

Vlca=Vs−Vd

Vlcb=Vs−Vd

となる。また、このとき、それぞれの補助容量配線の電圧Vcsa、Vcsbは

Vcsa=Vcom−Vad

Vcsb=Vcom+Vad

である。

Vlca=Vs−Vd+2×K×Vad

Vlcb=Vs−Vd−2×K×Vad

へ変化する。但し、K=CCS/(CLC(V)+CCS)である。

Vlca=Vs−Vd+2×K×Vad

Vlcb=Vs−Vd−2×K×Vad

から、

Vlca=Vs−Vd

Vlcb=Vs−Vd

へ変化する。

Vlca=Vs−Vd

Vlcb=Vs−Vd

から、

Vlca=Vs−Vd+2×K×Vad

Vlcb=Vs−Vd−2×K×Vad

へ変化する。

Vlca=Vs−Vd+K×Vad

Vlcb=Vs−Vd−K×Vad

となる。

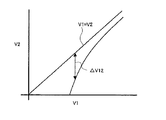

V1=Vlca−Vcom

V2=Vlcb−Vcom

すなわち、

V1=Vs−Vd+K×Vad−Vcom

V2=Vs−Vd−K×Vad−Vcom

となる。

CSBL_A_n+(L/2)・kが第1補助容量幹線に接続され、

CSBL_B_n+(L/2)・kが第2補助容量幹線に接続され、

CSBL_A_n+1+(L/2)・kが第3補助容量幹線に接続され、

CSBL_B_n+1+(L/2)・kが第4補助容量幹線に接続され、

CSBL_A_n+2+(L/2)・kが第5補助容量幹線に接続され、

CSBL_B_n+2+(L/2)・kが第6補助容量幹線に接続され、

・・・・・以下同様の接続関係を繰り返し、

CSBL_A_n+(L/2)−2+(L/2)・kが第L−3補助容量幹線に接続され、

CSBL_B_n+(L/2)−2+(L/2)・kが第L−2補助容量幹線に接続され、

CSBL_A_n+(L/2)−1+(L/2)・kが第L−1補助容量幹線に接続され、

CSBL_B_n+(L/2)−1+(L/2)・kが第L補助容量幹線に接続されるように構成すればよい。

CSBL_A_n+L・kおよびCSBL_B_n+(L/2)+L・kが第1補助容量幹線に接続され、

CSBL_B_n+L・kおよびCSBL_A_n+(L/2)+L・kが第2補助容量幹線に接続され、

CSBL_A_n+1+L・kおよびCSBL_B_n+(L/2)+1+L・kが第3補助容量幹線に接続され、

CSBL_B_n+1+L・kおよびCSBL_A_n+(L/2)+1+L・kが第4補助容量幹線に接続され、

CSBL_A_n+2+L・kおよびCSBL_B_n+(L/2)+2+L・kが第5補助容量幹線に接続され、

CSBL_B_n+2+L・kおよびCSBL_A_n+(L/2)+2+L・kが第6補助容量幹線に接続され、

CSBL_A_n+3+L・kおよびCSBL_B_n+(L/2)+3+L・kが第7補助容量幹線に接続されており、

CSBL_B_n+3+L・kおよびCSBL_A_n+(L/2)+3+L・kが第8補助容量幹線に接続され、

・・・・・以下同様の接続関係を繰り返し、

CSBL_A_n+(L/2)−2+L・kおよびCSBL_B_n+L−2+L・kが第L−3補助容量幹線に接続され、

CSBL_B_n+(L/2)−2+L・kおよびCSBL_A_n+L−2+L・kが第L−2補助容量幹線に接続され、

CSBL_A_n+(L/2)−1+L・kおよびCSBL_B_n+L−1+L・kが第L−1補助容量幹線に接続されており、

CSBL_B_n+(L/2)−1+L・kおよびCSBL_A_n+L−1+L・kが第L補助容量幹線に接続されればよい。

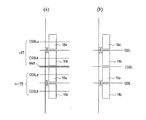

本実施形態の液晶表示装置のマトリックス構成(CSバスラインの接続形態)を図37に、この液晶表示装置の駆動に用いられる信号の波形を図38に示す。また、図37の接続形態を表7に示す。図37のマトリックス構成に対して、図38のタイミングでCSバスラインに振動電圧を印加することで、図35Aに示した駆動状態が実現される。

CSBL_( p )B, ( p+ 1 )A

と

CSBL_( p+ 5 )B, ( p+ 6 )A

との関係を満足するタイプ(α型)

或いは

CSBL_( p+ 1 )B, ( p+ 2 )A

と

CSBL_( p+ 4 )B, ( p+ 5 )A

との関係を満足するタイプ(β型)

の2種類が存在していることがわかる。すなわち、M1aおよびM3aのCS幹線に接続されているCSバスラインはα型であり、M2aおよびM4aのCS幹線に接続されているCSバスラインはβ型である。

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A

と

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(K−1)+K・L+2 )A

或いは、

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

の何れかで表されるCSバスラインの組を電気的に等価にすれば良ことがわかる。但しpはp=1,3,5,・・・もしくはp=,2,4,・・・である。この条件を導入する理由はα型とβ型との両方に属するCSバスラインは存在しないためである。

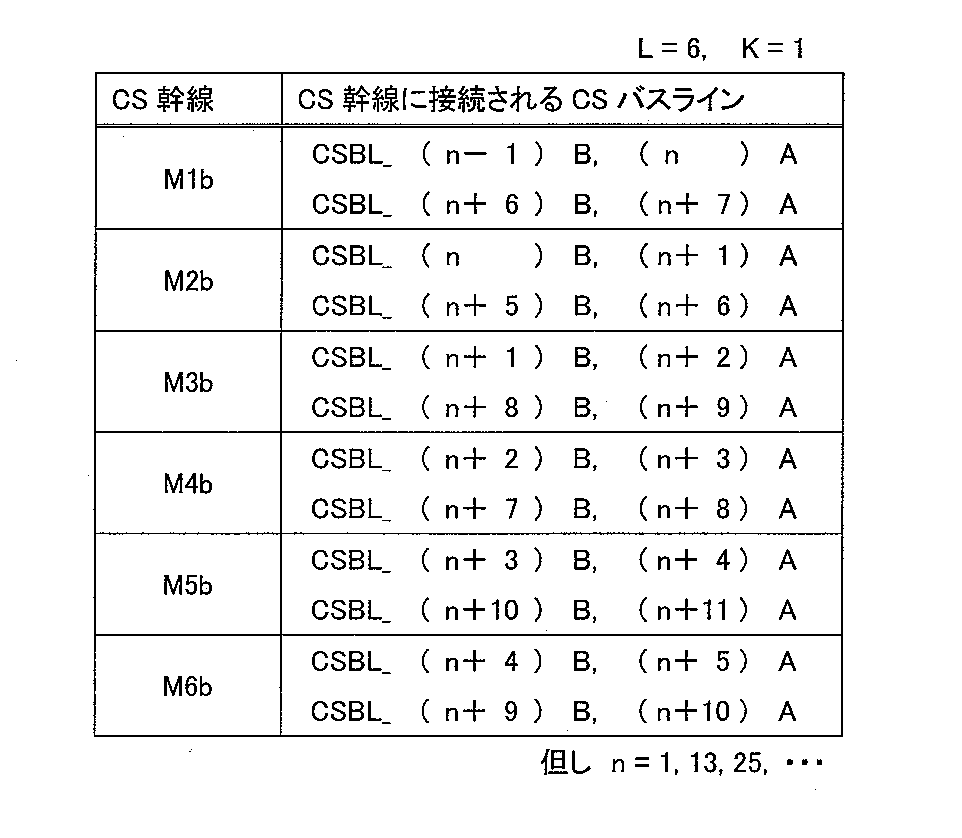

次に、電気的に独立なCS幹線の数が6本の場合の接続形態を図39に、そのときの駆動波形を図40に示す。また、図39の接続形態を表8に示す。

CSBL_( p )B,( p+ 1 )A

と

CSBL_( p+ 7 )B,( p+ 8 )A

或いは

CSBL_( p+ 1 )B,( p+ 2 )A

と

CSBL_( p+ 6 )B,( p+ 7 )A

但し、p=1,3,5,・・・もしくはp=,2,4,・・

の組が電気的に等しいCSバスラインとなっている事がわかる。

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A

と

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(K−1)+K・L+2 )A

或いは、

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

の何れかで表されるCSバスラインの組を電気的に等価にすれば良ことがわかる。但しpはp=1,3,5,・・・もしくはp=0,2,4,・・・である。

次に、電気的に独立なCSバスラインの数が8種類の場合の接続形態を図41に、そのときの駆動波形を図42に示す。また、図41の接続形態を表9に示す。

CSBL_( p )B,( p+ 1 )A

と

CSBL_( p+ 9 )B,( p+10 )A

或いは

CSBL_( p+ 1 )B,( p+ 2 )A

と

CSBL_( p+ 8 )B,( p+ 9 )A

但し、p=1,3,5,・・・もしくはp=0,2,4,・・・

の組が電気的に等しいCSバスラインとなっている事がわかる。

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A

と

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(K−1)+K・L+2 )A

或いは、

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

の何れかで表されるCSバスラインの組を電気的に等価にすれば良ことがわかる。但しpはp=1,3,5,・・・もしくはp=0,2,4,・・・である。

次に、電気的に独立なCSバスラインの数が10本の場合の接続形態を図43に、そのときの駆動波形を図44に示す。また、図43の接続形態を表10に示す。

CSBL_( p )B,( p+ 1 )A

と

CSBL_( p+ 11 )B,( p+12 )A

或いは

CSBL_( p+ 1 )B,( p+ 2 )A

と

CSBL_( p+10 )B,( p+11 )A

但し、p=1,3,5,・・・もしくはp=0,2,4,・・・

の組が電気的に等しいCSバスラインとなっている事がわかる。

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A

と

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(K−1)+K・L+2 )A

或いは、

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

の何れかで表されるCSバスラインの組を電気的に等価にすれば良ことがわかる。但しpはp=1,3,5,・・・もしくはp=0,2,4,・・・である。

次に、電気的に独立なCSバスラインの数が12種類の場合の接続形態を図45に、そのときの駆動波形を図46に示す。また、図45の接続形態を表11に示す。

CSBL_( p )B,( p+ 1 )A

と

CSBL_( p+ 13 )B,( p+14 )A

或いは

CSBL_( p+ 1 )B,( p+ 2 )A

と

CSBL_( p+12 )B,( p+13 )A

但し、p=1,3,5,・・・もしくはp=0,2,4,・・・

の組が電気的に等しいCSバスラインとなっている事がわかる。

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A

と

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(K−1)+K・L+2 )A

或いは、

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

の何れかで表されるCSバスラインの組を電気的に等価にすれば良ことがわかる。但しpはp=1,3,5,・・・もしくはp=0,2,4,・・・である。

パラメータKの値が2で、電気的に独立なCSバスラインの数が4種類の場合の接続形態を図47に、そのときの駆動波形を図48に示す。また、図47の接続形態を表12に示す。

CSBL_( p )B,( p+ 1 )A、

CSBL_( p + 2 )B,( p+ 3 )A

と

CSBL_( p + 9 )B,( p+ 10 )A、

CSBL_( p+ 11 )B,( p+12 )A

或いは

CSBL_( p+ 1 )B,( p+ 2 )A、

CSBL_( p + 3 )B,( p+ 4 )A

と

CSBL_( p+ 8 )B,( p+ 9 )A、

CSBL_( p+10 )B,( p+11 )A

但し、p=1,3,5,・・・もしくはp=0,2,4,・・・

の組が電気的に 等しいCSバスラインとなっている事がわかる。

CSBL_( p+2・(1−1) )B,( p+2・(1−1)+1 )A、

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A

と

CSBL_( p+2・(1−1)+K・L+1 )B,( p+2・(1−1)+K・L+2 )A、

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(K−1)+K・L+2 )A

或いは、

CSBL_( p+2・(1−1)+1 )B,( p+2・(1−1)+2 )A、

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(1−1)+K・L )B,( p+2・(1−1)+K・L+1 )A、

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

の何れかで表されるCSバスラインの組を電気的に等価にすれば良ことがわかる。但しpはp=1,3,5,・・・もしくはp=0,2,4,・・・である。

パラメータKの値が2で、電気的に独立なCSバスラインの数が6種類の場合の接続形態を図49に、そのときの駆動波形を図50に示す。また、図49の接続形態を表13に示す。

CSBL_( p )B,( p+ 1 )A、

CSBL_( p + 2 )B,( p+ 3 )A

と

CSBL_( p + 13 )B,( p+ 14 )A、

CSBL_( p+ 15 )B,( p+16 )A

或いは

CSBL_( p+ 1 )B,( p+ 2 )A、

CSBL_( p + 3 )B,( p+ 4 )A

と

CSBL_( p+ 12 )B,( p+ 13 )A、

CSBL_( p+14 )B,( p+15 )A

但し、p=1,3,5,・・・もしくはp=0,2,4,・・・

の組が電気的に等しいCSバスラインとなっている事がわかる。

CSBL_( p+2・(1−1) )B,( p+2・(1−1)+1 )A

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A、

と

CSBL_( p+2・(1−1)+K・L+1 )B,( p+2・(1−1)+K・L+2 )A、

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(K−1)+K・L+2 )A

或いは、

CSBL_( p+2・(1−1)+1 )B,( p+2・(1−1)+2 )A、

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(1−1)+K・L )B,( p+2・(1−1)+K・L+1 )A、

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

の何れかで表されるCSバスラインの組を電気的に等価にすれば良ことがわかる。但しpはp=1,3,5,・・・もしくはp=0,2,4,・・・である。

CSBL_( p+2・(1−1) )B,( p+2・(1−1)+1 )A、

CSBL_( p+2・(2−1) )B,( p+2・(2−1)+1 )A、

CSBL_( p+2・(3−1) )B,( p+2・(3−1)+1 )A、

・

・

・

CSBL_( p+2・(K−1) )B,( p+2・(K−1)+1 )A

と、

CSBL_( p+2・(1−1)+K・L+1 )B,( p+2・(2−1)+K・L+2 )A、

CSBL_( p+2・(2−1)+K・L+1 )B,( p+2・(2−1)+K・L+2 )A、

CSBL_( p+2・(3−1)+K・L+1 )B,( p+2・(3−1)+K・L+2 )A、

・

・

・

CSBL_( p+2・(K−1)+K・L+1 )B,( p+2・(3−1)+K・L+2 )A

或いは

CSBL_( p+2・(1−1)+1 )B,( p+2・(1−1)+2 )A、

CSBL_( p+2・(2−1)+1 )B,( p+2・(2−1)+2 )A、

CSBL_( p+2・(3−1)+1 )B,( p+2・(3−1)+2 )A、

・

・

・

CSBL_( p+2・(K−1)+1 )B,( p+2・(K−1)+2 )A

と

CSBL_( p+2・(1−1)+K・L )B,( p+2・(1−1)+K・L+1 )A、

CSBL_( p+2・(2−1)+K・L )B,( p+2・(2−1)+K・L+1 )A、

CSBL_( p+2・(3−1)+K・L )B,( p+2・(3−1)+K・L+1 )A、

・

・

・

CSBL_( p+2・(K−1)+K・L )B,( p+2・(K−1)+K・L+1 )A

とすれば良い。但しpはp=1,3,5,・・・もしくはp=0,2,4,・・・である。

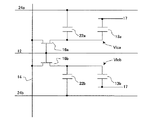

10a、10b 副画素

12 走査線

14a、14b 信号線

16a、16b TFT

18a、18b 副画素電極

100 液晶表示装置

Claims (30)

- それぞれが液晶層と前記液晶層に電圧を印加する複数の電極とを有し、行および列を有するマトリクス状に配列された複数の画素を備える液晶表示装置であって、

前記複数の画素のそれぞれは、それぞれの前記液晶層に互いに異なる電圧を印加することができる第1副画素および前記第2副画素であって、ある階調において前記第1副画素が前記第2副画素よりも高い輝度を呈する第1副画素および第2副画素を有し、

前記第1副画素および前記第2副画素のそれぞれは、

対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、前記副画素電極に電気的に接続された補助容量電極と、

絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量とを有し、

前記対向電極は、前記第1副画素および前記第2副画素に対して共通の単一の電極であり、前記補助容量対向電極は、前記第1副画素と前記第2副画素とで電気的に独立であって、かつ、

前記第1副画素および前記第2副画素のそれぞれに対応して設けられた2つのスイッチング素子を有し、前記2つのスイッチング素子は、共通の走査線を介して供給される走査信号電圧によってオン/オフ制御され、前記共通の走査線は前記第1副画素および前記第2副画素の何れの前記補助容量対向電極とも電気的に独立であり、

前記複数の画素の内の任意の画素の前記第1副画素の前記補助容量対向電極と、前記任意の画素に列方向に隣接する画素の前記第2副画素の前記補助容量対向電極とは、電気的に独立である、液晶表示装置。 - 前記任意の画素の前記第1副画素は、前記任意の画素に列方向に隣接する画素の第2副画素と隣接するように配置されている、請求項1に記載の液晶表示装置。

- 前記複数の画素のそれぞれにおいて、前記第1副画素は前記第2副画素と列方向に隣接するように配置されている、請求項1に記載の液晶表示装置。

- 互いに電気的に独立な複数の補助容量幹線を有し、前記補助容量幹線のそれぞれは、前記複数の画素の前記第1副画素および前記第2副画素が有する前記補助容量対向電極のいずれかに補助容量配線を介して電気的に接続されている、請求項1から3のいずれかに記載の液晶表示装置。

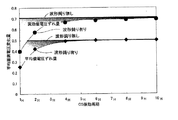

- 前記複数の補助容量幹線の内で電気的に独立な補助容量幹線はL本の補助容量幹線であって、前記補助容量幹線のそれぞれが供給する補助容量対向電圧は振動電圧であって、振動の周期は、水平走査期間のL倍である、請求項4に記載の液晶表示装置。

- 電気的に独立な前記複数の補助容量幹線は偶数本の補助容量幹線であって、互いに振動の位相が180度異なる補助容量対向電圧を供給する補助容量幹線の対で構成されている、請求項4または5のいずれかに記載の液晶表示装置。

- 電気的に独立な補助容量幹線の数は、1水平走査期間を前記補助容量配線の有する最大の負荷インピーダンスを近似したCR時定数で除した値の8倍よりも大きな数である、請求項4から6のいずれかに記載の液晶表示装置。

- 電気的に独立な補助容量幹線の数は、1水平走査期間を前記補助容量配線の有する最大の負荷インピーダンスを近似したCR時定数で除した値の8倍よりも大きく、且つ偶数である請求項4から6のいずれかに記載の液晶表示装置。

- 前記複数の補助容量幹線は、それぞれが電気的に独立な第1補助容量幹線および第2補助容量幹線を含み、

前記複数の画素が構成するある行をn行とし、任意の列のn行に属する画素が有する第1副画素の補助容量対向電極が接続された補助容量配線CSBL_A_n、第2副画素の補助容量対向電極が接続された補助容量配線をCSBL_B_nで表し、kを自然数(0を含む)とするとき、

CSBL_A_n+kが前記第1補助容量幹線に接続されており、

CSBL_B_n+kが前記第2補助容量幹線に接続されている、請求項1から8のいずれかに記載の液晶表示装置。 - 前記第1および第2補助容量幹線のそれぞれが供給する第1および第2補助容量対向電圧の振動の周期は、いずれも水平走査期間の2倍の時間である、請求項9に記載の液晶表示装置。

- 前記第2補助容量対向電圧は、前記第1補助容量対向電圧より水平走査期間の1倍の時間だけ位相が遅れている、請求項10に記載の液晶表示装置。

- 前記2つのスイッチング素子がオン状態にあるときに、前記第1副画素および前記第2副画素のそれぞれが有する前記副画素電極および前記補助容量電極に、共通の信号線を介して表示信号電圧が供給され、前記2つのスイッチング素子がオフ状態とされた後に、前記第1副画素および前記第2副画素のそれぞれの前記補助容量対向電極の電圧が変化し、

前記2つのスイッチングがオン状態からオフ状態とされた時刻の直後から、前記第1補助容量対向電圧が最初に変化するまでの時間をTdとするとき、Tdが、水平走査期間の0倍より大きく、かつ、水平走査期間の1倍よりも小さい時間である、請求項11に記載の液晶表示装置。 - 前記Tdが水平走査期間の0.5倍の時間に略等しい、請求項12に記載の液晶表示装置。

- 前記複数の補助容量幹線は、それぞれが電気的に独立な第1補助容量幹線、第2補助容量幹線、第3補助容量幹線、および第4補助容量幹線を含み、

前記複数の画素が構成するある行をn行とし、任意の列のn行に属する画素が有する第1副画素の補助容量対向電極が接続された補助容量配線CSBL_A_n、第2副画素の補助容量対向電極が接続された補助容量配線をCSBL_B_nで表し、kを自然数(0を含む)とするとき、

CSBL_A_n+4・kおよびCSBL_B_n+2+4・kが前記第1補助容量幹線に接続されており、

CSBL_B_n+4・kおよびCSBL_A_n+2+4・kが前記第2補助容量幹線に接続されており、

CSBL_A_n+1+4・kおよびCSBL_B_n+3+4・kが前記第3補助容量幹線に接続されており、

CSBL_B_n+1+4・kおよびCSBL_A_n+3+4・kが前記第4補助容量幹線に接続されている、請求項1から8のいずれかに記載の液晶表示装置。 - 前記第1から第4補助容量幹線のそれぞれが供給する第1から第4補助容量対向電圧の振動の周期は、いずれも水平走査期間の4倍の時間である、請求項14に記載の液晶表示装置。

- 前記第2補助容量対向電圧は、前記第1補助容量対向電圧より水平走査期間の2倍の時間だけ位相が遅れており、前記第3補助容量対向電圧は、前記第1補助容量対向電圧より水平走査期間の3倍の時間だけ位相が遅れており、前記第4補助容量対向電圧は、前記第1補助容量対向電圧より水平走査期間の1倍の時間だけ位相が遅れている、請求項15に記載の液晶表示装置。

- 前記第1副画素および前記第2副画素のそれぞれに対応して設けられた2つのスイッチング素子を有し、

前記2つのスイッチング素子は、共通の走査線を介して供給される走査信号電圧によってオン/オフ制御され、前記2つのスイッチング素子がオン状態にあるときに、前記第1副画素および前記第2副画素のそれぞれが有する前記副画素電極および前記補助容量電極に、共通の信号線を介して表示信号電圧が供給され、前記2つのスイッチング素子がオフ状態とされた後に、前記第1副画素および前記第2副画素のそれぞれの前記補助容量対向電極の電圧が変化し、

前記2つのスイッチングがオン状態からオフ状態とされた時刻の直後から、前記第1補助容量対向電圧が最初に変化するまでの時間をTdとするとき、Tdが、水平走査期間の0倍より大きく、かつ、水平走査期間の2倍よりも小さい時間である、請求項16に記載の液晶表示装置。 - 前記Tdが水平走査期間の1倍の時間に略等しい、請求項17に記載の液晶表示装置。

- 前記複数の補助容量幹線は、それぞれが電気的に独立な第1補助容量幹線、第2補助容量幹線、第3補助容量幹線、第4補助容量幹線、第5補助容量幹線および第6補助容量幹線を含み、

行方向、列方向にマトリックス状に配置された前記複数の画素が構成するある行をn行とし、任意の列のn行に属する画素が有する第1副画素の補助容量対向電極が接続された補助容量配線CSBL_A_n、第2副画素の補助容量対向電極が接続された補助容量配線をCSBL_B_nで表し、kを自然数(0を含む)とするとき、

CSBL_A_n+3・kが前記第1補助容量幹線に接続されており、

CSBL_B_n+3・kが前記第2補助容量幹線に接続されており、

CSBL_A_n+1+3・kが前記第3補助容量幹線に接続されており、

CSBL_B_n+1+3・kが前記第4補助容量幹線に接続されており、

CSBL_A_n+2+3・kが前記第5補助容量幹線に接続されており、

CSBL_B_n+2+3・kが前記第6補助容量幹線に接続されている、請求項1から8のいずれかに記載の液晶表示装置。 - 前記第1から第6補助容量幹線のそれぞれが供給する第1から第6補助容量対向電圧の振動の周期は、いずれも水平走査期間の6倍の時間である、請求項19に記載の液晶表示装置。

- 前記複数の補助容量幹線は、それぞれが電気的に独立なL本の補助容量幹線、第1補助容量幹線、第2補助容量幹線、第3補助容量幹線、第4補助容量幹線、第5補助容量幹線、第6補助容量幹線、・・・、第L−3補助容量幹線、第L−2補助容量幹線、第L−1補助容量幹線、および第L補助容量幹線を含み、

電気的に独立な補助容量幹線の数Lの1/2が奇数であるとき、即ちL=2,6,10,・・・であるとき、

前記複数の画素が構成するある行をn行とし、任意の列のn行に属する画素が有する第1副画素の補助容量対向電極が接続された補助容量配線CSBL_A_n、第2副画素の補助容量対向電極が接続された補助容量配線をCSBL_B_nで表し、kを自然数(0を含む)とするとき、

CSBL_A_n+(L/2)・kが前記第1補助容量幹線に接続されており、

CSBL_B_n+(L/2)・kが前記第2補助容量幹線に接続されており、

CSBL_A_n+1+(L/2)・kが前記第3補助容量幹線に接続されており、

CSBL_B_n+1+(L/2)・kが前記第4補助容量幹線に接続されており、

CSBL_A_n+2+(L/2)・kが前記第5補助容量幹線に接続されており、

CSBL_B_n+2+(L/2)・kが前記第6補助容量幹線に接続されており、

・・・

CSBL_A_n+(L/2)−2+(L/2)・kが前記第L−3補助容量幹線に接続されており、

CSBL_B_n+(L/2)−2+(L/2)・kが前記第L−2補助容量幹線に接続されており、

CSBL_A_n+(L/2)−1+(L/2)・kが前記第L−1補助容量幹線に接続されており、

CSBL_B_n+(L/2)−1+(L/2)・kが前記第L補助容量幹線に接続されている、請求項1から8のいずれかに記載の液晶表示装置。 - 前記第1から第L補助容量幹線のそれぞれが供給する第1から第L補助容量対向電圧の振動の周期は、いずれも水平走査期間のL倍の時間である、請求項21に記載の液晶表示装置。

- 前記複数の補助容量幹線は、それぞれが電気的に独立な第1補助容量幹線、第2補助容量幹線、第3補助容量幹線、第4補助容量幹線、第5補助容量幹線、第6補助容量幹線、第7補助容量幹線、および第8補助容量幹線を含み、

前記複数の画素が構成するある行をn行とし、任意の列のn行に属する画素が有する第1副画素の補助容量対向電極が接続された補助容量配線CSBL_A_n、第2副画素の補助容量対向電極が接続された補助容量配線をCSBL_B_nで表し、kを自然数(0を含む)とするとき、

CSBL_A_n+8・kおよびCSBL_B_n+4+8・kが前記第1補助容量幹線に接続されており、

CSBL_B_n+8・kおよびCSBL_A_n+4+8・kが前記第2補助容量幹線に接続されており、

CSBL_A_n+1+8・kおよびCSBL_B_n+5+8・kが前記第3補助容量幹線に接続されており、

CSBL_B_n+1+8・kおよびCSBL_A_n+5+8・kが前記第4補助容量幹線に接続されており、

CSBL_A_n+2+8・kおよびCSBL_B_n+6+8・kが前記第5補助容量幹線に接続されており、

CSBL_B_n+2+8・kおよびCSBL_A_n+6+8・kが前記第6補助容量幹線に接続されており、

CSBL_A_n+3+8・kおよびCSBL_B_n+7+8・kが前記第7補助容量幹線に接続されており、

CSBL_B_n+3+8・kおよびCSBL_A_n+7+8・kが前記第8補助容量幹線に接続されている、請求項1から8のいずれかに記載の液晶表示装置。 - 前記第1から第8補助容量幹線のそれぞれが供給する第1から第8補助容量対向電圧の振動の周期は、いずれも水平走査期間の8倍の時間である、請求項23に記載の液晶表示装置。

- 前記複数の補助容量幹線は、それぞれが電気的に独立なL本の補助容量幹線、第1補助容量幹線、第2補助容量幹線、第3補助容量幹線、第4補助容量幹線、第5補助容量幹線、第6補助容量幹線、第7補助容量幹線、第8補助容量幹線、・・・、第L−3補助容量幹線、第L−2補助容量幹線、第L−1補助容量幹線、及び第L補助容量幹線を含み、

電気的に独立な補助容量幹線の数Lの1/2が偶数であるとき、即ちL=4,8,12,・・・であるとき、

行方向、列方向にマトリックス状に配置された前記複数の画素が構成するある行をn行とし、任意の列のn行に属する画素が有する第1副画素の補助容量対向電極が接続された補助容量配線CSBL_A_n、第2副画素の補助容量対向電極が接続された補助容量配線をCSBL_B_nで表し、kを自然数(0を含む)とするとき、

CSBL_A_n+L・kおよびCSBL_B_n+(L/2)+L・kが前記第1補助容量幹線に接続されており、

CSBL_B_n+L・kおよびCSBL_A_n+(L/2)+L・kが前記第2補助容量幹線に接続されており、

CSBL_A_n+1+L・kおよびCSBL_B_n+(L/2)+1+L・kが前記第3補助容量幹線に接続されており、

CSBL_B_n+1+L・kおよびCSBL_A_n+(L/2)+1+L・kが前記第4補助容量幹線に接続されており、

CSBL_A_n+2+L・kおよびCSBL_B_n+(L/2)+2+L・kが前記第5補助容量幹線に接続されており、

CSBL_B_n+2+L・kおよびCSBL_A_n+(L/2)+2+L・kが前記第6補助容量幹線に接続されており、

CSBL_A_n+3+L・kおよびCSBL_B_n+(L/2)+3+L・kが前記第7補助容量幹線に接続されており、

CSBL_B_n+3+L・kおよびCSBL_A_n+(L/2)+3+L・kが前記第8補助容量幹線に接続されており、

・・・

CSBL_A_n+(L/2)−2+L・kおよびCSBL_B_n+L−2+L・kが前記第L−3補助容量幹線に接続されており、

CSBL_B_n+(L/2)−2+L・kおよびCSBL_A_n+L−2+L・kが前記第L−2補助容量幹線に接続されており、

CSBL_A_n+(L/2)−1+L・kおよびCSBL_B_n+L−1+L・kが前記第L−1補助容量幹線に接続されており、

CSBL_B_n+(L/2)−1+L・kおよびCSBL_A_n+L−1+L・kが前記第L補助容量幹線に接続されている、請求項1から8のいずれかに記載の液晶表示装置。 - 前記第1から第L補助容量幹線のそれぞれが供給する第1から第L補助容量対向電圧の振動の周期は、いずれも水平走査期間のL倍の時間である、請求項25に記載の液晶表示装置。

- 前記補助容量対向電圧のデューティ比は、いずれも1:1である、請求項9から26のいずれかに記載の液晶表示装置。

- 前記任意の画素の前記第1副画素は、前記任意の画素に列方向に隣接する画素の第2副画素と隣接するように配置されており、かつ、前記複数の画素のそれぞれにおいて、前記第1副画素は前記第2副画素と列方向に隣接するように配置されている請求項1から27のいずれかに記載の液晶表示装置。

- 前記第1副画素と前記第2副画素の面積は互いに略等しい、請求項1から28のいずれかに記載の液晶表示装置。

- 前記第2副画素の面積は前記第1副画素の面積よりも大きい、請求項1から28のいずれかに記載の液晶表示装置。

Priority Applications (10)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004250982A JP4265788B2 (ja) | 2003-12-05 | 2004-08-30 | 液晶表示装置 |

| EP10184895.0A EP2296140B1 (en) | 2003-12-05 | 2004-12-03 | Liquid crystal display |

| CN 200910126411 CN101510034B (zh) | 2003-12-05 | 2004-12-03 | 液晶显示器 |

| EP20100184908 EP2267692B1 (en) | 2003-12-05 | 2004-12-03 | Liquid crystal display |

| EP04257518.3A EP1538599B1 (en) | 2003-12-05 | 2004-12-03 | Liquid crystal display |

| TW093137490A TWI288380B (en) | 2003-12-05 | 2004-12-03 | Liquid crystal display |

| US11/002,424 US7429981B2 (en) | 2003-12-05 | 2004-12-03 | Liquid crystal display |

| KR1020040101483A KR100711230B1 (ko) | 2003-12-05 | 2004-12-04 | 액정표시장치 |

| US12/216,974 US8203520B2 (en) | 2003-12-05 | 2008-07-14 | Liquid crystal display |

| US13/465,446 US8487858B2 (en) | 2003-12-05 | 2012-05-07 | Liquid crystal display |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003408046 | 2003-12-05 | ||

| JP2004250982A JP4265788B2 (ja) | 2003-12-05 | 2004-08-30 | 液晶表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008104009A Division JP4738435B2 (ja) | 2003-12-05 | 2008-04-11 | 液晶表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005189804A JP2005189804A (ja) | 2005-07-14 |

| JP4265788B2 true JP4265788B2 (ja) | 2009-05-20 |

Family

ID=34467865

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004250982A Expired - Lifetime JP4265788B2 (ja) | 2003-12-05 | 2004-08-30 | 液晶表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (3) | US7429981B2 (ja) |

| EP (3) | EP2296140B1 (ja) |

| JP (1) | JP4265788B2 (ja) |

| KR (1) | KR100711230B1 (ja) |

| TW (1) | TWI288380B (ja) |

Families Citing this family (121)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4342200B2 (ja) * | 2002-06-06 | 2009-10-14 | シャープ株式会社 | 液晶表示装置 |

| JP4265788B2 (ja) * | 2003-12-05 | 2009-05-20 | シャープ株式会社 | 液晶表示装置 |

| JP4559091B2 (ja) * | 2004-01-29 | 2010-10-06 | ルネサスエレクトロニクス株式会社 | 表示装置用駆動回路 |

| JP4290680B2 (ja) | 2004-07-29 | 2009-07-08 | シャープ株式会社 | 容量性負荷充放電装置およびそれを備えた液晶表示装置 |

| WO2006035887A1 (ja) * | 2004-09-30 | 2006-04-06 | Sharp Kabushiki Kaisha | 液晶表示装置 |

| JP5000124B2 (ja) * | 2004-11-12 | 2012-08-15 | 三星電子株式会社 | 表示装置及びその駆動方法 |

| JP5090620B2 (ja) * | 2004-12-27 | 2012-12-05 | シャープ株式会社 | 液晶表示装置 |

| WO2006070829A1 (ja) * | 2004-12-28 | 2006-07-06 | Sharp Kabushiki Kaisha | 液晶表示装置およびその駆動方法 |

| WO2006093163A1 (ja) * | 2005-03-03 | 2006-09-08 | Sharp Kabushiki Kaisha | 表示装置、液晶モニター、液晶テレビジョン受像機および表示方法 |

| US7884890B2 (en) | 2005-03-18 | 2011-02-08 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| US7948463B2 (en) | 2005-03-18 | 2011-05-24 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| KR101188601B1 (ko) * | 2005-04-13 | 2012-10-08 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| US7936344B2 (en) | 2005-05-03 | 2011-05-03 | Hannstar Display Corporation | Pixel structure with improved viewing angle |

| KR101160831B1 (ko) * | 2005-06-01 | 2012-06-28 | 삼성전자주식회사 | 액정 표시 장치 |

| KR101152123B1 (ko) * | 2005-07-18 | 2012-06-15 | 삼성전자주식회사 | 액정 표시 장치 및 그 구동 방법 |

| KR101186878B1 (ko) * | 2005-08-26 | 2012-10-02 | 엘지디스플레이 주식회사 | 브이에이 모드 액정표시장치 및 그 구동방법 |

| WO2007034876A1 (ja) * | 2005-09-22 | 2007-03-29 | Sharp Kabushiki Kaisha | 液晶表示装置 |

| JP4405557B2 (ja) * | 2005-09-22 | 2010-01-27 | シャープ株式会社 | アクティブマトリクス基板、表示装置、テレビジョン装置、アクティブマトリクス基板の製造方法、及び表示装置の製造方法 |

| KR101182771B1 (ko) * | 2005-09-23 | 2012-09-14 | 삼성전자주식회사 | 액정 표시 패널과 그의 구동 방법 및 그를 이용한 액정표시 장치 |

| KR101189277B1 (ko) * | 2005-12-06 | 2012-10-09 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| CN100426369C (zh) * | 2005-12-21 | 2008-10-15 | 群康科技(深圳)有限公司 | 液晶显示器及其驱动方法 |

| WO2007102382A1 (ja) * | 2006-03-06 | 2007-09-13 | Sharp Kabushiki Kaisha | アクティブマトリクス基板、表示装置及びテレビジョン受像機 |

| KR101179215B1 (ko) * | 2006-04-17 | 2012-09-04 | 삼성전자주식회사 | 구동장치 및 이를 갖는 표시장치 |

| US7589703B2 (en) * | 2006-04-17 | 2009-09-15 | Au Optronics Corporation | Liquid crystal display with sub-pixel structure |

| TWI364734B (en) * | 2006-06-30 | 2012-05-21 | Chimei Innolux Corp | Liquid crystal display panel, driving method and liquid crystal displayer |

| TWI322401B (en) * | 2006-07-13 | 2010-03-21 | Au Optronics Corp | Liquid crystal display |

| US20100182345A1 (en) * | 2006-08-10 | 2010-07-22 | Fumikazu Shimoshikiryoh | Liquid crystal display |

| WO2008023602A1 (en) * | 2006-08-24 | 2008-02-28 | Sharp Kabushiki Kaisha | Liquid crystal display |

| EP2284828A1 (en) * | 2006-08-24 | 2011-02-16 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| TWI330746B (en) * | 2006-08-25 | 2010-09-21 | Au Optronics Corp | Liquid crystal display and operation method thereof |

| TWI336804B (en) * | 2006-08-25 | 2011-02-01 | Au Optronics Corp | Liquid crystal display and operation method thereof |

| TWI321771B (en) * | 2006-09-08 | 2010-03-11 | Au Optronics Corp | Liquid crystal display and driving method thereof |

| TWI336805B (en) * | 2006-12-07 | 2011-02-01 | Chimei Innolux Corp | Liquid crystal display device and driving method thereof |

| KR101332154B1 (ko) * | 2006-12-13 | 2014-01-08 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| TWI348065B (en) * | 2007-01-10 | 2011-09-01 | Au Optronics Corp | Liquid crystal display |

| TWI358050B (en) * | 2007-01-24 | 2012-02-11 | Au Optronics Corp | Pixel structure and method for generating drive vo |

| TWI350509B (en) * | 2007-01-25 | 2011-10-11 | Au Optronics Corp | A driving method for liquid crystal display |

| EP2136247B1 (en) * | 2007-03-15 | 2014-07-02 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| EP2149874A4 (en) | 2007-04-26 | 2011-11-30 | Sharp Kk | LIQUID CRYSTAL DISPLAY |

| TWI333113B (en) * | 2007-04-26 | 2010-11-11 | Au Optronics Corp | Liquid crystal display and driving method thereof |

| CN101669163B (zh) | 2007-04-27 | 2012-11-07 | 夏普株式会社 | 液晶显示装置 |

| JP5542297B2 (ja) | 2007-05-17 | 2014-07-09 | 株式会社半導体エネルギー研究所 | 液晶表示装置、表示モジュール及び電子機器 |

| JP5116359B2 (ja) | 2007-05-17 | 2013-01-09 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP5542296B2 (ja) | 2007-05-17 | 2014-07-09 | 株式会社半導体エネルギー研究所 | 液晶表示装置、表示モジュール及び電子機器 |

| KR101340054B1 (ko) * | 2007-06-05 | 2013-12-11 | 삼성디스플레이 주식회사 | 표시장치 및 이의 구동방법 |

| EP2161712A4 (en) * | 2007-06-12 | 2010-06-09 | Sharp Kk | LIQUID CRYSTAL PANEL CONTROL DEVICE, LIQUID CRYSTAL DISPLAY DEVICE, LIQUID CRYSTAL DISPLAY DEVICE CONTROL METHOD, CONTROL STATE CONTROL PROGRAM, AND TELEVISION RECEIVER |

| JP5214601B2 (ja) | 2007-06-12 | 2013-06-19 | シャープ株式会社 | 液晶表示装置、液晶表示装置の駆動方法、及びテレビジョン受像機 |

| WO2008152847A1 (ja) * | 2007-06-12 | 2008-12-18 | Sharp Kabushiki Kaisha | 液晶表示装置、液晶表示装置の駆動方法、およびテレビジョン受像機 |

| KR101487738B1 (ko) * | 2007-07-13 | 2015-01-29 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그의 구동 방법 |

| TW200905651A (en) * | 2007-07-26 | 2009-02-01 | Au Optronics Corp | Liquid crystal display with wide view angle |

| TWI339304B (en) * | 2007-10-16 | 2011-03-21 | Au Optronics Corp | Pixel structure, driving method thereof and pixel array structure |

| JP5009373B2 (ja) * | 2007-10-16 | 2012-08-22 | シャープ株式会社 | 液晶表示装置の駆動回路、液晶表示装置及び液晶表示装置の駆動方法 |

| KR100902214B1 (ko) * | 2007-11-08 | 2009-06-11 | 삼성모바일디스플레이주식회사 | 액정표시장치 및 그 구동방법 |

| CN101868819B (zh) * | 2007-11-21 | 2013-01-16 | 夏普株式会社 | 显示装置和扫描线驱动装置 |

| JP4522445B2 (ja) * | 2007-12-12 | 2010-08-11 | シャープ株式会社 | 表示装置 |

| US7719749B1 (en) * | 2007-11-29 | 2010-05-18 | Oasis Advanced Engineering, Inc. | Multi-purpose periscope with display and overlay capabilities |

| WO2009069359A1 (ja) * | 2007-11-30 | 2009-06-04 | Sharp Kabushiki Kaisha | 液晶表示装置、アクティブマトリクス基板、液晶パネル、液晶表示ユニット、テレビジョン受像機 |

| JP5512284B2 (ja) * | 2007-12-27 | 2014-06-04 | シャープ株式会社 | 液晶表示装置、液晶表示装置の駆動方法、テレビジョン受像機 |

| US8542228B2 (en) * | 2007-12-27 | 2013-09-24 | Sharp Kabushiki Kaisha | Liquid crystal display, liquid crystal display driving method, and television receiver utilizing a preliminary potential |

| EP2105915B1 (en) * | 2008-03-24 | 2012-11-21 | Sony Corporation | Liquid crystal display device and display control device |

| JP4807371B2 (ja) * | 2008-03-27 | 2011-11-02 | ソニー株式会社 | 液晶表示装置 |

| TWI397734B (zh) * | 2008-05-07 | 2013-06-01 | 瀚宇彩晶股份有限公司 | 液晶顯示器及其驅動方法 |

| KR101469028B1 (ko) | 2008-08-11 | 2014-12-04 | 삼성디스플레이 주식회사 | 표시 장치 |

| US8339534B2 (en) * | 2008-08-11 | 2012-12-25 | Samsung Display Co., Ltd. | Display device |

| US8212973B2 (en) * | 2008-09-15 | 2012-07-03 | Wintek Corporation | Color filter substrate and liquid crystal display |

| US8531443B2 (en) * | 2008-09-16 | 2013-09-10 | Sharp Kabushiki Kaisha | Display driving circuit, display device, and display driving method |

| KR101501497B1 (ko) | 2008-09-18 | 2015-03-12 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| WO2010038524A1 (ja) * | 2008-09-30 | 2010-04-08 | シャープ株式会社 | 表示装置および表示装置の駆動方法ならびに表示駆動の制御方法 |

| TWI375828B (en) * | 2008-09-30 | 2012-11-01 | Au Optronics Corp | Pixel array, driving method for the same and display panel |

| TWI399605B (zh) * | 2008-12-16 | 2013-06-21 | Century Display Shenxhen Co | Active matrix liquid crystal display panel |

| US8665195B2 (en) * | 2009-01-09 | 2014-03-04 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| WO2010092658A1 (ja) * | 2009-02-10 | 2010-08-19 | シャープ株式会社 | 液晶表示装置 |

| EP2413181A4 (en) * | 2009-03-24 | 2012-08-29 | Sharp Kk | TFT SUBSTRATE AND LIQUID CRYSTAL DISPLAY APPARATUS USING THE SAME |

| US8854562B2 (en) * | 2009-05-21 | 2014-10-07 | Sharp Kabushiki Kaisha | Liquid crystal panel |

| WO2010143348A1 (ja) | 2009-06-11 | 2010-12-16 | シャープ株式会社 | 液晶表示装置 |

| WO2011004538A1 (ja) * | 2009-07-10 | 2011-01-13 | シャープ株式会社 | 液晶駆動回路および液晶表示装置 |

| JP5290419B2 (ja) * | 2009-07-22 | 2013-09-18 | シャープ株式会社 | アクティブマトリクス基板、液晶パネル、液晶表示装置、液晶表示ユニット、テレビジョン受像機 |

| EP2477065A4 (en) | 2009-09-10 | 2013-05-29 | Sharp Kk | LIQUID CRYSTAL DISPLAY DEVICE |

| JP5179670B2 (ja) * | 2009-10-16 | 2013-04-10 | シャープ株式会社 | 液晶表示装置 |

| JP5412524B2 (ja) * | 2009-10-21 | 2014-02-12 | シャープ株式会社 | 液晶表示装置 |

| JP4925371B2 (ja) * | 2009-11-26 | 2012-04-25 | 東芝モバイルディスプレイ株式会社 | 液晶表示装置および液晶表示装置の駆動方法 |

| JP5226652B2 (ja) * | 2009-12-08 | 2013-07-03 | シャープ株式会社 | 液晶表示装置 |

| JP5619787B2 (ja) * | 2010-02-15 | 2014-11-05 | シャープ株式会社 | アクティブマトリクス基板、液晶パネル、液晶表示装置、テレビジョン受像機 |

| US8576156B2 (en) | 2010-02-25 | 2013-11-05 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| JP5631968B2 (ja) * | 2010-02-26 | 2014-11-26 | シャープ株式会社 | 液晶表示装置 |

| JP5450792B2 (ja) | 2010-03-19 | 2014-03-26 | シャープ株式会社 | 液晶表示装置 |

| CN101866590B (zh) * | 2010-04-26 | 2012-05-23 | 友达光电股份有限公司 | 显示器、显示器驱动方法以及源极驱动电路 |

| KR20120054890A (ko) * | 2010-11-22 | 2012-05-31 | 삼성모바일디스플레이주식회사 | 액정 표시 장치 및 그 구동 방법 |

| US9568794B2 (en) | 2010-12-20 | 2017-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| KR20120126223A (ko) * | 2011-05-11 | 2012-11-21 | 삼성디스플레이 주식회사 | 표시 기판 |

| WO2013018637A1 (ja) * | 2011-08-02 | 2013-02-07 | シャープ株式会社 | 液晶表示装置 |

| WO2013035676A1 (ja) * | 2011-09-06 | 2013-03-14 | シャープ株式会社 | 液晶表示装置、液晶パネルの駆動方法 |

| US9111505B2 (en) * | 2011-09-20 | 2015-08-18 | Sharp Kabushiki Kaisha | Liquid crystal display device and drive method for liquid crystal panel |

| KR101944482B1 (ko) * | 2012-01-18 | 2019-02-07 | 삼성디스플레이 주식회사 | 표시 패널 및 이의 구동 방법 |

| CN102592557B (zh) * | 2012-03-01 | 2014-07-09 | 深圳市华星光电技术有限公司 | 一种斜视角图像的模拟方法及装置 |

| US9245487B2 (en) | 2012-03-14 | 2016-01-26 | Apple Inc. | Systems and methods for reducing loss of transmittance due to column inversion |

| US9047826B2 (en) | 2012-03-14 | 2015-06-02 | Apple Inc. | Systems and methods for liquid crystal display column inversion using reordered image data |

| US9368077B2 (en) | 2012-03-14 | 2016-06-14 | Apple Inc. | Systems and methods for adjusting liquid crystal display white point using column inversion |

| US9047832B2 (en) | 2012-03-14 | 2015-06-02 | Apple Inc. | Systems and methods for liquid crystal display column inversion using 2-column demultiplexers |

| US9047838B2 (en) | 2012-03-14 | 2015-06-02 | Apple Inc. | Systems and methods for liquid crystal display column inversion using 3-column demultiplexers |

| KR101272338B1 (ko) * | 2012-06-29 | 2013-06-07 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| CN104620309B (zh) * | 2012-09-13 | 2017-09-22 | 夏普株式会社 | 液晶显示装置 |

| GB2516637A (en) * | 2013-07-26 | 2015-02-04 | Sharp Kk | Display device and method of driving same |

| US9812078B2 (en) * | 2013-09-20 | 2017-11-07 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| US20150118668A1 (en) | 2013-10-31 | 2015-04-30 | Dexcom, Inc. | Adaptive interface for continuous monitoring devices |

| KR102201109B1 (ko) | 2014-03-06 | 2021-01-11 | 삼성디스플레이 주식회사 | 표시 장치 |

| TWI526763B (zh) * | 2014-05-13 | 2016-03-21 | 友達光電股份有限公司 | 畫素結構、畫素陣列以及顯示面板 |

| CN114326211B (zh) | 2015-02-12 | 2025-03-28 | 株式会社半导体能源研究所 | 显示装置 |

| CN104599656B (zh) * | 2015-02-16 | 2017-04-05 | 深圳市华星光电技术有限公司 | 校正液晶面板的子像素的成像时灰阶的方法 |

| US9496299B1 (en) * | 2015-05-01 | 2016-11-15 | Sensors Unlimited, Inc. | Layout for routing common signals to integrating imaging pixels |

| CN108140353B (zh) | 2015-10-22 | 2020-09-01 | 夏普株式会社 | 液晶显示面板及其驱动方法 |

| CN108140354B (zh) | 2015-10-22 | 2020-09-11 | 夏普株式会社 | 液晶显示面板及其修正方法 |

| CN105182620B (zh) * | 2015-11-06 | 2018-05-08 | 京东方科技集团股份有限公司 | 像素结构及驱动方法、显示基板及显示装置 |

| CN107170419B (zh) * | 2017-06-29 | 2019-09-17 | 惠科股份有限公司 | 显示面板驱动方法、系统及显示装置 |

| CN107505744A (zh) * | 2017-08-25 | 2017-12-22 | 惠科股份有限公司 | 液晶显示装置 |

| KR102581313B1 (ko) * | 2018-10-01 | 2023-09-22 | 레이아 인코포레이티드 | 멀티뷰 픽셀들 및 멀티빔 방출기들의 오프셋된 행들을 갖는 멀티뷰 디스플레이 및 방법 |

| CN109188816B (zh) * | 2018-10-26 | 2021-06-22 | 昆山龙腾光电股份有限公司 | 阵列基板及其驱动方法和液晶显示装置及其驱动方法 |

| TWI691945B (zh) * | 2019-03-08 | 2020-04-21 | 凌巨科技股份有限公司 | 顯示裝置 |

| CN111856826A (zh) * | 2019-04-25 | 2020-10-30 | 堺显示器制品株式会社 | 液晶显示装置 |

| CN111091777B (zh) | 2020-03-22 | 2020-09-25 | 深圳市华星光电半导体显示技术有限公司 | 充电时间调试方法和装置 |

| CN115202118B (zh) * | 2022-07-29 | 2023-06-23 | 惠科股份有限公司 | 显示面板、显示面板的制作方法及显示装置 |

Family Cites Families (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5691277A (en) * | 1979-12-25 | 1981-07-24 | Citizen Watch Co Ltd | Liquiddcrystal display panel |

| FI74871B (fi) | 1986-06-26 | 1987-12-31 | Sinisalo Sport Oy | Skyddsklaede. |

| JPS6332009A (ja) | 1986-07-23 | 1988-02-10 | 三菱重工業株式会社 | 除雪装置 |

| JP3114347B2 (ja) | 1992-05-06 | 2000-12-04 | 日本電気株式会社 | 一次元ccd撮像装置 |

| US5338851A (en) | 1993-03-31 | 1994-08-16 | Eli Lilly And Company | Synthesis of cis-decahydroisoquinoline-3-carboxylic acids |

| JP3401049B2 (ja) * | 1993-05-26 | 2003-04-28 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 階調液晶表示パネル |

| JPH07152013A (ja) * | 1993-11-29 | 1995-06-16 | Nippondenso Co Ltd | 液晶表示素子 |

| JPH08146383A (ja) * | 1994-11-18 | 1996-06-07 | Matsushita Electric Ind Co Ltd | アクティブマトリックス型液晶表示素子 |

| JPH08179341A (ja) * | 1994-12-22 | 1996-07-12 | Matsushita Electric Ind Co Ltd | 液晶表示装置およびその駆動方法 |

| KR100234402B1 (ko) * | 1996-01-19 | 1999-12-15 | 윤종용 | 액정 표시 장치의 구동 방법 및 장치 |

| JPH1068931A (ja) * | 1996-08-28 | 1998-03-10 | Sharp Corp | アクティブマトリクス型液晶表示装置 |

| JP3395877B2 (ja) | 1996-12-20 | 2003-04-14 | シャープ株式会社 | 液晶表示装置及びその製造方法 |

| US6344883B2 (en) * | 1996-12-20 | 2002-02-05 | Sharp Kabushiki Kaisha | Liquid crystal display device and method for producing the same |

| JP3231261B2 (ja) | 1997-03-26 | 2001-11-19 | 株式会社アドバンスト・ディスプレイ | 液晶表示素子及びこれを用いた液晶表示装置 |

| JPH10274783A (ja) * | 1997-03-31 | 1998-10-13 | Sharp Corp | 液晶表示装置 |

| DE69841083D1 (de) | 1997-06-12 | 2009-10-01 | Sharp Kk | Anzeigevorrichtung mit vertikal ausgerichtetem Flüssigkristall |

| JPH1124225A (ja) | 1997-07-01 | 1999-01-29 | Fuji Photo Film Co Ltd | 液体噴射装置 |

| US6667783B2 (en) * | 2000-01-21 | 2003-12-23 | Rainbow Displays, Inc. | Construction of large, robust, monolithic and monolithic-like, AMLCD displays with wide view angle |

| TWI290252B (en) * | 2000-02-25 | 2007-11-21 | Sharp Kk | Liquid crystal display device |

| JP3600531B2 (ja) | 2000-02-25 | 2004-12-15 | シャープ株式会社 | 液晶表示装置 |

| JP2002333870A (ja) * | 2000-10-31 | 2002-11-22 | Matsushita Electric Ind Co Ltd | 液晶表示装置、el表示装置及びその駆動方法、並びに副画素の表示パターン評価方法 |

| US7019763B2 (en) * | 2001-01-09 | 2006-03-28 | Seiko Epson Corporation | Display device, driving method therefor, electro-optical device, driving method therefor, and electronic apparatus |

| GB0109015D0 (en) * | 2001-04-11 | 2001-05-30 | Koninkl Philips Electronics Nv | Bistable chiral nematic liquid crystal display and method of driving the same |

| US6956553B2 (en) * | 2001-04-27 | 2005-10-18 | Sanyo Electric Co., Ltd. | Active matrix display device |

| US7230597B2 (en) * | 2001-07-13 | 2007-06-12 | Tpo Hong Kong Holding Limited | Active matrix array devices |

| JP2003108098A (ja) * | 2001-09-29 | 2003-04-11 | Toshiba Corp | 平面表示装置 |

| JP3999081B2 (ja) * | 2002-01-30 | 2007-10-31 | シャープ株式会社 | 液晶表示装置 |

| AU2002336341A1 (en) * | 2002-02-20 | 2003-09-09 | Planar Systems, Inc. | Light sensitive display |

| JP3924485B2 (ja) * | 2002-03-25 | 2007-06-06 | シャープ株式会社 | 液晶表示装置の駆動方法及びその液晶表示装置 |

| JP4143323B2 (ja) * | 2002-04-15 | 2008-09-03 | Nec液晶テクノロジー株式会社 | 液晶表示装置 |

| JP4342200B2 (ja) * | 2002-06-06 | 2009-10-14 | シャープ株式会社 | 液晶表示装置 |

| TWI225232B (en) * | 2002-07-12 | 2004-12-11 | Toshiba Matsushita Display Tec | Display device |

| US20040012551A1 (en) * | 2002-07-16 | 2004-01-22 | Takatoshi Ishii | Adaptive overdrive and backlight control for TFT LCD pixel accelerator |

| KR100496297B1 (ko) * | 2003-03-06 | 2005-06-17 | 삼성에스디아이 주식회사 | 박막 트랜지스터를 구비한 평판표시장치 |

| KR200328406Y1 (ko) * | 2003-06-25 | 2003-09-29 | 최용범 | 가변형 조립식 문구용 꽃이통 |

| JP4265788B2 (ja) * | 2003-12-05 | 2009-05-20 | シャープ株式会社 | 液晶表示装置 |

-

2004

- 2004-08-30 JP JP2004250982A patent/JP4265788B2/ja not_active Expired - Lifetime

- 2004-12-03 EP EP10184895.0A patent/EP2296140B1/en not_active Expired - Lifetime

- 2004-12-03 EP EP20100184908 patent/EP2267692B1/en not_active Expired - Lifetime

- 2004-12-03 TW TW093137490A patent/TWI288380B/zh not_active IP Right Cessation

- 2004-12-03 EP EP04257518.3A patent/EP1538599B1/en not_active Expired - Lifetime

- 2004-12-03 US US11/002,424 patent/US7429981B2/en active Active

- 2004-12-04 KR KR1020040101483A patent/KR100711230B1/ko not_active Expired - Fee Related

-

2008

- 2008-07-14 US US12/216,974 patent/US8203520B2/en not_active Expired - Fee Related

-

2012

- 2012-05-07 US US13/465,446 patent/US8487858B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8487858B2 (en) | 2013-07-16 |

| KR20050054858A (ko) | 2005-06-10 |

| US8203520B2 (en) | 2012-06-19 |

| EP1538599A2 (en) | 2005-06-08 |

| EP2267692A2 (en) | 2010-12-29 |

| JP2005189804A (ja) | 2005-07-14 |

| US7429981B2 (en) | 2008-09-30 |

| EP2267692B1 (en) | 2015-04-29 |

| EP1538599A3 (en) | 2007-10-10 |

| TW200537403A (en) | 2005-11-16 |

| US20090046048A1 (en) | 2009-02-19 |

| EP2296140A3 (en) | 2012-05-30 |

| EP1538599B1 (en) | 2014-02-26 |

| KR100711230B1 (ko) | 2007-04-25 |

| US20120300164A1 (en) | 2012-11-29 |

| EP2296140B1 (en) | 2015-02-11 |

| EP2296140A2 (en) | 2011-03-16 |

| US20050122441A1 (en) | 2005-06-09 |

| EP2267692A3 (en) | 2012-05-23 |

| TWI288380B (en) | 2007-10-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4265788B2 (ja) | 液晶表示装置 | |

| JP4738435B2 (ja) | 液晶表示装置 | |

| JP4342200B2 (ja) | 液晶表示装置 | |

| JP4104639B2 (ja) | 液晶表示装置およびその駆動方法 | |

| US8208081B2 (en) | Liquid crystal display having pixel including multiple subpixels | |

| JP4393548B2 (ja) | 液晶表示装置 | |

| JP4393549B2 (ja) | 液晶表示装置 | |

| JP5042270B2 (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080411 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090210 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090210 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4265788 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120227 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120227 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130227 Year of fee payment: 4 |

|

| SG99 | Written request for registration of restore |

Free format text: JAPANESE INTERMEDIATE CODE: R316G99 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130227 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130227 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140227 Year of fee payment: 5 |

|

| SG99 | Written request for registration of restore |

Free format text: JAPANESE INTERMEDIATE CODE: R316G99 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |