JP4807371B2 - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP4807371B2 JP4807371B2 JP2008083169A JP2008083169A JP4807371B2 JP 4807371 B2 JP4807371 B2 JP 4807371B2 JP 2008083169 A JP2008083169 A JP 2008083169A JP 2008083169 A JP2008083169 A JP 2008083169A JP 4807371 B2 JP4807371 B2 JP 4807371B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- sub

- subpixel

- liquid crystal

- driving

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134345—Subdivided pixels, e.g. for grey scale or redundancy

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/137—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells characterised by the electro-optical or magneto-optical effect, e.g. field-induced phase transition, orientation effect, guest-host interaction or dynamic scattering

- G02F1/13712—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells characterised by the electro-optical or magneto-optical effect, e.g. field-induced phase transition, orientation effect, guest-host interaction or dynamic scattering the liquid crystal having negative dielectric anisotropy

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0443—Pixel structures with several sub-pixels for the same colour in a pixel, not specifically used to display gradations

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0252—Improving the response speed

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0271—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping

- G09G2320/0276—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping for the purpose of adaptation to the characteristics of a display device, i.e. gamma correction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/028—Improving the quality of display appearance by changing the viewing angle properties, e.g. widening the viewing angle, adapting the viewing angle to the view direction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/16—Determination of a pixel data signal depending on the signal applied in the previous frame

Description

Sa<Sb1<Sb2 ……(11)

Claims (11)

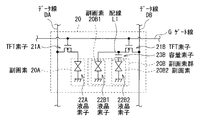

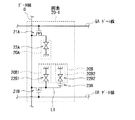

- 全体としてマトリクス状に配置され、各々が液晶素子を有する複数の画素と、

各画素の液晶素子に対して映像信号に基づく駆動電圧を印加することにより表示駆動を行う駆動手段と

を備え、

前記画素が、

低電圧階調の階調表現に用いられる第1副画素と、

前記低電圧階調よりも高電圧の階調である高電圧階調の階調表現に用いられる互いに異なる複数の第2副画素を有する副画素群と

により構成され、

前記第1副画素の面積(=Sa)が、前記副画素群の面積(=Sb)よりも小さくなるように設定され、

前記駆動手段は、前記映像信号に基づき前記第1副画素および前記複数の第2副画素の各々を個別に駆動する空間分割駆動によって、各画素に対する表示駆動を行うと共に、

前記空間分割駆動の際に、前記第1副画素と前記副画素群との間でオーバードライブ量が互いに異なることとなるように、前記第1副画素および前記複数の第2副画素の各々の駆動電圧に対してオーバードライブ処理を行う

液晶表示装置。 - 前記副画素群が、2つの第2副画素により構成され、

各画素が、前記第1副画素と前記2つの第2副画素とにより構成されている

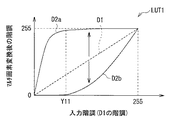

請求項1に記載の液晶表示装置。 - 前記駆動手段は、

第1の入力輝度位置から出力輝度が立ち上がるような第1の入出力輝度特性を、前記第1副画素に適用し、

前記第1の入力輝度位置よりも高い第2の入力輝度位置から出力輝度が立ち上がるような第2の入出力輝度特性を、前記2つの第2副画素のうちの一方に適用し、

前記第2の入力輝度位置よりも高い第3の入力輝度位置から出力輝度が立ち上がるような第3の入出力輝度特性を、前記2つの第2副画素のうちの他方に適用し、

これにより、前記第1副画素および前記2つの第2副画素の各々を個別に駆動する空間分割駆動を行う

請求項2に記載の液晶表示装置。 - 前記各画素は、

前記第1副画素を駆動するための第1のスイッチング素子と、

前記副画素群を駆動するための第2のスイッチング素子と、

前記第2のスイッチング素子と前記他方の第2副画素との間に設けられた容量素子と

を含み、

前記駆動手段は、前記映像信号における入力輝度レベルと前記第1副画素および前記副画素群にそれぞれ適用されるべき出力輝度レベルとを対応付けてなる第1のLUT(ルックアップテーブル)を用いることにより、前記第1副画素および前記2つの第2副画素に対する空間分割駆動を行う

請求項3に記載の液晶表示装置。 - 前記駆動手段は、各画素に対して線順次で表示駆動を行うものであり、

各画素に対応して、

駆動対象の画素を線順次で選択するための1本のゲート線と、

駆動対象の画素に前記駆動電圧を供給するための2本のデータ線と

が設けられている

請求項4に記載の液晶表示装置。 - 前記駆動手段は、各画素に対して線順次で表示駆動を行うものであり、

各画素に対応して、

駆動対象の画素を線順次で選択するための2本のゲート線と、

駆動対象の画素に前記駆動電圧を供給するための1本のデータ線と

が設けられている

請求項4に記載の液晶表示装置。 - 各画素は、前記第1副画素および前記2つの第2副画素をそれぞれ駆動するための3つのスイッチング素子を含み、

前記駆動手段は、前記映像信号における入力輝度レベルと前記第1副画素、前記一方の第2副画素および前記他方の第2副画素にそれぞれ適用されるべき出力輝度レベルとを対応付けてなる第2のLUT(ルックアップテーブル)を用いることにより、前記第1副画素および前記2つの第2副画素に対する空間分割駆動を行う

請求項3に記載の液晶表示装置。 - 前記第1副画素の面積Saが、前記画素全体の面積の1/3以下となるように設定されている

請求項2ないし請求項7のいずれか1項に記載の液晶表示装置。 - 前記第1副画素の面積Sa、前記一方の第2副画素の面積(=Sb1)および前記他方の第2副画素の面積(=Sb2)の間で、以下の(1)式を満たす

請求項8に記載の液晶表示装置。

Sa<Sb1<Sb2 ……(1) - 前記駆動手段は、前記空間分割駆動の際に、前記第1副画素に適用されるオーバードライブ量と比べて前記副画素群に適用されるオーバードライブ量のほうがより大きくなるように、前記オーバードライブ処理を行う

請求項1ないし請求項9のいずれか1項に記載の液晶表示装置。 - 前記液晶素子が、垂直配向(VA)モードの液晶を含んで構成されている

請求項1ないし請求項10のいずれか1項に記載の液晶表示装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008083169A JP4807371B2 (ja) | 2008-03-27 | 2008-03-27 | 液晶表示装置 |

| TW098108944A TWI410940B (zh) | 2008-03-27 | 2009-03-19 | 液晶顯示設備 |

| US12/383,731 US8334882B2 (en) | 2008-03-27 | 2009-03-26 | Liquid crystal display apparatus |

| CN2009101306704A CN101546543B (zh) | 2008-03-27 | 2009-03-27 | 液晶显示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008083169A JP4807371B2 (ja) | 2008-03-27 | 2008-03-27 | 液晶表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009237266A JP2009237266A (ja) | 2009-10-15 |

| JP2009237266A5 JP2009237266A5 (ja) | 2010-05-06 |

| JP4807371B2 true JP4807371B2 (ja) | 2011-11-02 |

Family

ID=41193637

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008083169A Expired - Fee Related JP4807371B2 (ja) | 2008-03-27 | 2008-03-27 | 液晶表示装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8334882B2 (ja) |

| JP (1) | JP4807371B2 (ja) |

| CN (1) | CN101546543B (ja) |

| TW (1) | TWI410940B (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011010417A1 (ja) * | 2009-07-22 | 2011-01-27 | シャープ株式会社 | アクティブマトリクス基板、液晶パネル、液晶表示装置、液晶表示ユニット、テレビジョン受像機 |

| KR101623582B1 (ko) * | 2009-07-31 | 2016-05-24 | 엘지디스플레이 주식회사 | 액정표시장치와 그 응답시간 보상방법 |

| KR101319354B1 (ko) * | 2009-12-21 | 2013-10-16 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그의 영상 처리 방법 |

| JP5421154B2 (ja) * | 2010-03-11 | 2014-02-19 | 株式会社ジャパンディスプレイ | 反射型液晶表示装置とその駆動方法と電子機器 |

| TWI494674B (zh) * | 2011-04-22 | 2015-08-01 | Chimei Innolux Corp | 顯示面板 |

| TWI477872B (zh) * | 2011-12-23 | 2015-03-21 | E Ink Holdings Inc | 可顯示多灰階之顯示裝置及其操作方法 |

| CN103185975B (zh) * | 2011-12-29 | 2016-02-03 | 上海天马微电子有限公司 | 液晶显示面板及驱动方法 |

| JP6140711B2 (ja) * | 2012-09-13 | 2017-05-31 | シャープ株式会社 | 液晶表示装置 |

| CN103529611B (zh) * | 2013-09-24 | 2017-01-25 | 深圳市华星光电技术有限公司 | 一种阵列基板及液晶显示面板 |

| US9852676B2 (en) * | 2014-01-30 | 2017-12-26 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| KR102183088B1 (ko) | 2014-02-10 | 2020-11-26 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| TWI526763B (zh) * | 2014-05-13 | 2016-03-21 | 友達光電股份有限公司 | 畫素結構、畫素陣列以及顯示面板 |

| CN104503180B (zh) * | 2015-01-08 | 2017-11-07 | 京东方科技集团股份有限公司 | 一种阵列基板、显示装置及其驱动方法 |

| KR102432472B1 (ko) * | 2015-10-22 | 2022-08-17 | 엘지디스플레이 주식회사 | 컨트롤러, 데이터 드라이버, 표시장치 및 그 구동방법 |

| CN105895042B (zh) * | 2016-06-07 | 2018-11-23 | 深圳市华星光电技术有限公司 | 液晶显示器以及改善液晶显示器的色偏的方法 |

| CN107238988A (zh) * | 2017-07-24 | 2017-10-10 | 武汉华星光电技术有限公司 | 阵列基板、显示面板和显示装置 |

| CN107564486A (zh) * | 2017-09-19 | 2018-01-09 | 惠科股份有限公司 | 显示装置的驱动方法及显示装置 |

| CN108172191B (zh) * | 2018-02-26 | 2020-12-15 | 海信视像科技股份有限公司 | 液晶显示器及其驱动方法、装置与计算机存储介质 |

| CN111833787B (zh) * | 2019-04-16 | 2022-10-11 | 咸阳彩虹光电科技有限公司 | 一种显示面板、装置及其驱动方法 |

| CN110570825A (zh) * | 2019-08-08 | 2019-12-13 | 深圳市华星光电技术有限公司 | 一种像素电路及液晶显示面板 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6512502B2 (en) * | 1998-05-27 | 2003-01-28 | International Business Machines Corporation | Lightvalve projection system in which red, green, and blue image subpixels are projected from two lightvalves and recombined using total reflection prisms |

| JP2002333870A (ja) * | 2000-10-31 | 2002-11-22 | Matsushita Electric Ind Co Ltd | 液晶表示装置、el表示装置及びその駆動方法、並びに副画素の表示パターン評価方法 |

| JP2003066433A (ja) * | 2001-08-28 | 2003-03-05 | Hitachi Ltd | 液晶表示装置 |

| US7755652B2 (en) * | 2002-01-07 | 2010-07-13 | Samsung Electronics Co., Ltd. | Color flat panel display sub-pixel rendering and driver configuration for sub-pixel arrangements with split sub-pixels |

| KR20040105934A (ko) * | 2003-06-10 | 2004-12-17 | 삼성전자주식회사 | 다중 도메인 액정 표시 장치 및 그에 사용되는 표시판 |

| US7206048B2 (en) * | 2003-08-13 | 2007-04-17 | Samsung Electronics Co., Ltd. | Liquid crystal display and panel therefor |

| US20050083353A1 (en) * | 2003-10-16 | 2005-04-21 | Junichi Maruyama | Display device |

| KR100689311B1 (ko) * | 2003-11-10 | 2007-03-08 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 및 그 구동방법 |

| JP4265788B2 (ja) * | 2003-12-05 | 2009-05-20 | シャープ株式会社 | 液晶表示装置 |

| WO2005059875A2 (en) * | 2003-12-16 | 2005-06-30 | Koninklijke Philips Electronics N.V. | A display panel comprising a plurality of pixels and a display device |

| EP1587049A1 (en) * | 2004-04-15 | 2005-10-19 | Barco N.V. | Method and device for improving conformance of a display panel to a display standard in the whole display area and for different viewing angles |

| JP4394512B2 (ja) * | 2004-04-30 | 2010-01-06 | 富士通株式会社 | 視角特性を改善した液晶表示装置 |

| KR100900115B1 (ko) * | 2004-10-06 | 2009-06-01 | 샤프 가부시키가이샤 | 액정 표시 장치 |

| KR101100882B1 (ko) * | 2004-11-05 | 2012-01-02 | 삼성전자주식회사 | 액정 표시 장치 및 그 구동 장치 |

| JP5090620B2 (ja) * | 2004-12-27 | 2012-12-05 | シャープ株式会社 | 液晶表示装置 |

| KR101153942B1 (ko) * | 2005-07-20 | 2012-06-08 | 삼성전자주식회사 | 액정 표시 장치 |

| KR101182771B1 (ko) | 2005-09-23 | 2012-09-14 | 삼성전자주식회사 | 액정 표시 패널과 그의 구동 방법 및 그를 이용한 액정표시 장치 |

| TWI345213B (en) * | 2006-03-09 | 2011-07-11 | Au Optronics Corp | Low color-shift liquid crystal display and its driving method |

| WO2007108436A1 (ja) * | 2006-03-20 | 2007-09-27 | Sharp Kabushiki Kaisha | 液晶表示装置 |

| JP2007310334A (ja) * | 2006-05-19 | 2007-11-29 | Mikuni Denshi Kk | ハーフトーン露光法を用いた液晶表示装置の製造法 |

| TWI356222B (en) * | 2006-09-18 | 2012-01-11 | Chimei Innolux Corp | Liquid crystal display panel and liquid crystal di |

| KR101388588B1 (ko) * | 2007-03-14 | 2014-04-23 | 삼성디스플레이 주식회사 | 액정표시장치 |

-

2008

- 2008-03-27 JP JP2008083169A patent/JP4807371B2/ja not_active Expired - Fee Related

-

2009

- 2009-03-19 TW TW098108944A patent/TWI410940B/zh active

- 2009-03-26 US US12/383,731 patent/US8334882B2/en active Active

- 2009-03-27 CN CN2009101306704A patent/CN101546543B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TWI410940B (zh) | 2013-10-01 |

| US8334882B2 (en) | 2012-12-18 |

| US20090262147A1 (en) | 2009-10-22 |

| CN101546543B (zh) | 2012-03-28 |

| JP2009237266A (ja) | 2009-10-15 |

| TW201003626A (en) | 2010-01-16 |

| CN101546543A (zh) | 2009-09-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4807371B2 (ja) | 液晶表示装置 | |

| JP4840412B2 (ja) | 液晶表示装置 | |

| KR101787238B1 (ko) | 표시 장치 | |

| JP5414974B2 (ja) | 液晶表示装置 | |

| JP5650422B2 (ja) | 液晶表示装置 | |

| US20190101796A1 (en) | Liquid crystal display device | |

| JP5124051B1 (ja) | 表示装置 | |

| JP2009265615A (ja) | 表示装置 | |

| US20100045685A1 (en) | Liquid Crystal Display Device | |

| JP5012327B2 (ja) | 液晶表示装置および液晶表示装置の駆動方法 | |

| WO2016098232A1 (ja) | 液晶表示装置及び液晶表示装置の駆動方法 | |

| JP2009237352A (ja) | 液晶表示装置 | |

| KR101494212B1 (ko) | 광원 구동 방법, 이를 수행하기 위한 광원 장치 및 이 광원장치를 갖는 표시 장치 | |

| JP2011242605A (ja) | 液晶表示装置 | |

| US20110234478A1 (en) | Liquid crystal display device | |

| JP2011242604A (ja) | 液晶表示装置 | |

| WO2007111012A1 (ja) | 液晶表示装置 | |

| US8159510B2 (en) | Liquid crystal display | |

| KR102062914B1 (ko) | 3원색 표시장치 및 그의 픽셀데이터 랜더링 방법 | |

| JP7222835B2 (ja) | 表示装置 | |

| KR100923497B1 (ko) | 액정표시장치 및 구동방법 | |

| JP2009037195A (ja) | 発光装置及びこれを利用した表示装置、発光装置の駆動方法及び表示装置の駆動方法 | |

| JP2009237323A (ja) | 液晶表示装置 | |

| KR20090103732A (ko) | 액정 표시 장치 | |

| WO2012005060A1 (ja) | 表示パネル、および、液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100317 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100317 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100712 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100804 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100906 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110719 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110801 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140826 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |