JP5414974B2 - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP5414974B2 JP5414974B2 JP2007005538A JP2007005538A JP5414974B2 JP 5414974 B2 JP5414974 B2 JP 5414974B2 JP 2007005538 A JP2007005538 A JP 2007005538A JP 2007005538 A JP2007005538 A JP 2007005538A JP 5414974 B2 JP5414974 B2 JP 5414974B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- gate

- row

- matrix

- pixels included

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 75

- 239000011159 matrix material Substances 0.000 claims description 47

- 239000000758 substrate Substances 0.000 claims description 32

- 238000000034 method Methods 0.000 claims description 13

- 239000003990 capacitor Substances 0.000 description 11

- 239000010408 film Substances 0.000 description 11

- 239000010409 thin film Substances 0.000 description 10

- 238000003860 storage Methods 0.000 description 8

- 238000010586 diagram Methods 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 239000003086 colorant Substances 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 230000010287 polarization Effects 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3659—Control of matrices with row and column drivers using an active matrix the addressing of the pixel involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependant on signal of two data electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3607—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals for displaying colours or for displaying grey scales with a specific pixel layout, e.g. using sub-pixels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0247—Flicker reduction other than flicker reduction circuits used for single beam cathode-ray tubes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Theoretical Computer Science (AREA)

- Computer Hardware Design (AREA)

- Nonlinear Science (AREA)

- Liquid Crystal (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

Description

反転駆動には更に次のような問題がある。画素マトリックスの行方向や列方向で隣接する画素間には一般に、電極間の電圧のキックバックや、電極間の結合容量に差がある。それらの差は、ライン反転駆動では画面上に縦縞状のムラを引き起こすおそれがあり、列反転駆動では画面上に横縞状のムラを引き起こすおそれがある。それらのムラにより、液晶表示装置の更なる高画質化が阻まれている。

そこで、本発明は、反転駆動に伴う縦縞状または横縞状のムラを低減して更なる高画質化を可能にし、かつ反転駆動に要する消費電力の更なる削減を可能にする液晶表示装置、の提供を目的とする。

基板、

その基板の上にマトリックス状に形成された複数の画素から成り、隣接する第1の画素行と第2の画素行とを含む画素マトリックス、

その基板の上で画素マトリックスの行方向に延び、第1の画素行に含まれる画素のいずれかに接続されている第1のゲート線、

その基板の上で画素マトリックスの行方向に延び、第1の画素行に含まれる画素のいずれかと、第2の画素行に含まれる画素のいずれかと、に接続されている第2のゲート線、及び、

その基板の上で画素マトリックスの行方向に延び、第2の画素行に含まれる画素のいずれかに接続されている第3のゲート線、を備えている。

基板の上で画素マトリックスの列方向に延び、各画素にデータ電圧を供給する第1のデータ線と第2のデータ線、を更に備えている。その上、第1の画素行に含まれる3つの隣接する画素のうち、少なくとも1つは第1のデータ線に接続され、残りは第2のデータ線に接続されている。一方、第2の画素行に含まれる3つの隣接する画素のうち、少なくとも1つは第2のデータ線に接続され、残りは第1のデータ線に接続されている。更に好ましくは、第1の画素行に含まれる3つの隣接する画素を、第1の画素、第2の画素、及び第3の画素、とし、第2の画素行に含まれる3つの隣接する画素であり、第1の画素、第2の画素、及び第3の画素、のそれぞれに画素マトリックスの列方向で隣接する3つの画素を、第4の画素、第5の画素、及び第6の画素、とするとき、第1の画素は第1のデータ線に接続され、第2の画素は第2のデータ線に接続され、第3の画素は第2のデータ線に接続され、第4の画素は第1のデータ線に接続され、第5の画素は第1のデータ線に接続され、第6の画素は第2のデータ線に接続されている。その他に、第1の画素は第2のデータ線に接続され、第2の画素は第1のデータ線に接続され、第3の画素は第2のデータ線に接続され、第4の画素は第1のデータ線に接続され、第5の画素は第2のデータ線に接続され、第6の画素は第1のデータ線に接続されていても良い。

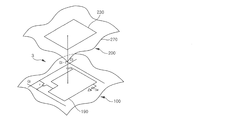

図1に示されているように、本発明の第1の実施形態による液晶表示装置は、液晶表示パネルアセンブリ300、ゲート駆動部400L、400R、データ駆動部500、階調電圧生成部800、及び、信号制御部600を備えている。

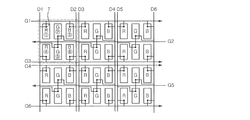

表示信号線は、ゲート信号(「走査信号」とも呼ばれる。)を供給する複数のゲート線G1〜Gnと、データ電圧を供給するデータ線D1〜Dmと、を含む。ゲート線G1〜Gnは、互いに平行に、画素マトリックスの行方向に延びている。データ線D1〜Dmは、互いに平行に、画素マトリックスの列方向に延びている。

維持キャパシタCstは、下部表示パネル100に設けられた別の信号線(維持電極線。図示せず)と画素電極190との重なり部分から形成されている。尚、維持電極線に対しては、共通電圧Vcomなどの所定の電圧が外部から印加される。

また、上部表示パネル200にはブラックマトリックスが形成され、画素間から漏れる光を遮っていても良い。それにより、画面の視認性が高められている。

データ駆動部500は、信号制御部600、液晶表示パネルアセンブリ300のデータ線D1〜Dm、及び階調電圧生成部800に接続されている。データ駆動部500は、信号制御部600からの映像データDATに基づいて階調電圧生成部800からの階調電圧のいずれかを選択し、選択された階調電圧をデータ電圧として、信号制御部600からのデータ制御信号CONT1の示すタイミングで、目標のデータ線D1〜Dmに対して印加する。

隣接する3本のゲート線の組G1〜G3、G4〜G6はそれぞれ、隣接する2つの画素行のそれぞれに対応づけられている。各ゲート線は各画素行の間に配置され、各画素のスイッチング素子(薄膜トランジスタ)Tに接続されている。一方、隣接する一対のデータ線D1とD2、D3とD4、D5とD6はそれぞれ、隣接する3つの画素列のそれぞれに対応づけられている。各データ線は各画素列の間に配置され、各画素の薄膜トランジスタTに接続されている。

下部表示パネル100は薄膜トランジスタ表示パネルである。下部表示パネル100では、透明なガラスなどの絶縁基板110の上にゲート線121a、121b、121cが形成されている。特に、図4に示されている3本のゲート線121a、121b、121cが上記の第1ないし第3のゲート線の組を構成している。尚、複数の維持電極線がゲート線と一緒に、絶縁基板110の上に形成されていても良い。各ゲート線121a、121b、121cの一部は各画素の付近で列方向に突出し、ゲート電極124を成す。

各画素を覆う保護膜180の上には画素電極190が一つずつ形成されている。画素電極190は好ましくは、インジウム錫酸化物(ITO)またはインジウム亜鉛酸化物(IZO)から成る。画素電極190はコンタクトホール181を介してドレイン電極175と物理的・電気的に接続されている。従って、薄膜トランジスタがターンオンするとき、画素電極190に対してドレイン電極175からデータ電圧が印加される。そのとき、画素電極190と図2に示されている共通電極270との間には電場が生成され、それにより、それら2つの電極190、270間に挟まれた液晶層3では液晶分子の配向方向が変化する。

画素電極190の上には更に配向膜(図示せず)が塗布されている。

まず、信号制御部600が、外部のグラフィックコントローラ(図示せず)から入力映像信号R、G、B及び入力制御信号を受信する。信号制御部600は入力映像信号R、G、Bを映像データDATに変換し、ゲート制御信号CONT1及びデータ制御信号CONT2を生成する。映像データDATとゲート制御信号CONT1とはゲート駆動部400L、400Rに送られ、データ制御信号CONT2はデータ駆動部500に送られる。

図6に示されているように、第1のデータ線と第2のデータ線との間ではデータ電圧の極性が反対である。従って、それら一対のデータ線の間に挟まれた画素群R、G、Bでは、外側の画素(第1の画素R、第3の画素B)に対するデータ電圧の極性が反対である。一方、列方向では、第1の画素Rに対するデータ電圧の極性が等しく、第3の画素Bに対するデータ電圧の極性が等しい。こうして、列反転駆動が実現する。更に、第1のゲート線G1と第3のゲート線G3とに挟まれた2つの画素群では、中央の画素(第2の画素)Gに対するデータ電圧の極性が反対である。すなわち、第2の画素から成る画素列では、データ電圧の極性が画素ごとに反転する。

その他に、図7とは異なり、第1ないし第3のゲート線に対するゲートオン電圧の印加期間を互いに重ねても良い(図示せず)。好ましくは、その重複期間の長さが1/3H〜1Hである。それにより、その重複期間中に各画素の液晶キャパシタ(及び維持キャパシタ)を予備充電できる。従って、ゲートオン電圧の印加期間中に画素電圧を目標のレベルまで確実に到達させることができる。その結果、キックバックの影響が弱められるので、列反転駆動では行方向に延びる縞状のムラが発生しない。

図8に示されているように、第2の実施形態による液晶表示装置では、第1の実施形態による液晶表示装置とは異なり、ゲート駆動部400が液晶表示パネルアセンブリ300の片側だけに設けられている。従って、全てのゲート線G1〜Gnが同じゲート駆動部400に接続されている。

図9では、第1のゲート線G1、G4は、直下の画素群の真ん中に位置する第2の画素G2と、右端に位置する第3の画素B3とに接続されている。第2のゲート線G2、G5は、直上の画素群の左端に位置する第1の画素R1と、直下の画素群の右端に位置する第6の画素B6とに接続されている。第3のゲート線G3、G6は、直下の画素群の左端に位置する第4の画素R4と、真ん中に位置する第5の画素G5とに接続されている。

一方、第1のデータ線D1は、第2の画素G2、第4の画素R4、及び第6の画素G6に接続されている。第2のデータ線D2は、第1の画素R1、第3の画素B3、及び第5の画素G5に接続されている。

第2の実施形態によるライン反転駆動では、列方向だけでなく行方向でも画素ごとにデータ電圧が反転し、実質的にはドット反転駆動と等価である。例えば図9に示されているように、画素とデータ線との間、及び画素とゲート線との間が接続されている場合は下記の通りである。第1のゲート線G1に対してゲートオン電圧が印加されると、第1のゲート線G1に接続された第2の画素G2に対しては第1のデータ線D1から正(+)のデータ電圧が印加され、第3の画素B3に対しては第2のデータ線D2から負(−)のデータ電圧が印加される。続いて、第2のゲート線G2に対してゲートオン電圧が印加されると、第2のゲート線G2に接続された第1の画素R1に対しては第2のデータ線D2から負(−)のデータ電圧が印加され、第6の画素B6に対しては第1のデータ線D1から正(+)のデータ電圧が印加される。更に、第3のゲート線G3に対してゲートオン電圧が印加されると、第3のゲート線G3に接続された第4の画素R4に対しては第1のデータ線D1から正(+)のデータ電圧が印加され、第5の画素G5に対しては第2のデータ線D2から負(−)のデータ電圧が印加される。

200:上部表示パネル

300:液晶表示パネルアセンブリ

400:ゲート駆動部

500:データ駆動部

600:信号制御部

800:階調電圧生成部

Claims (12)

- 基板、

前記基板の上にマトリックス状に形成された複数の画素から成り、隣接する第1の画素行と第2の画素行とを含む画素マトリックス、

前記基板の上で前記画素マトリックスの行方向に延び、前記第1の画素行に含まれる画素のいずれかに接続されている第1のゲート線、

前記基板の上で前記画素マトリックスの行方向に延び、前記第1の画素行に含まれる画素のいずれかと、前記第2の画素行に含まれる画素のいずれかと、に接続されている第2のゲート線、

前記基板の上で前記画素マトリックスの行方向に延び、前記第2の画素行に含まれる画素のいずれかに接続されている第3のゲート線、

前記第1のゲート線に接続される第1のゲート駆動部、

前記第2のゲート線に接続される第2のゲート駆動部、及び、

前記第3のゲート線に接続される第3のゲート駆動部、

を備え、

前記第1ないし第3のゲート駆動部が、水平周期の2倍に等しい期間中に、ゲートオン電圧を前記第1ないし第3のゲート線に順番に供給する、液晶表示装置。 - 前記第1ないし第3のゲート駆動部が前記基板に集積化されている、請求項1に記載の液晶表示装置。

- 前記第1のゲート駆動部と前記第2のゲート駆動部とが前記画素マトリックスの行方向で前記画素マトリックスを隔てて互いに対向している、請求項1に記載の液晶表示装置。

- 前記第1ないし第3のゲート線のそれぞれに対するゲートオン電圧の印加期間が水平周期の1/3倍〜1倍ずつ互いに重なっている、請求項1に記載の液晶表示装置。

- 基板、

前記基板の上にマトリックス状に形成された複数の画素から成り、隣接する第1の画素行と第2の画素行とを含む画素マトリックス、

前記基板の上で前記画素マトリックスの行方向に延び、前記第1の画素行に含まれる画素のいずれかに接続されている第1のゲート線、

前記基板の上で前記画素マトリックスの行方向に延び、前記第1の画素行に含まれる画素のいずれかと、前記第2の画素行に含まれる画素のいずれかと、に接続されている第2のゲート線、

前記基板の上で前記画素マトリックスの行方向に延び、前記第2の画素行に含まれる画素のいずれかに接続されている第3のゲート線、及び、

前記基板の上で前記画素マトリックスの列方向に延び、各画素にデータ電圧を供給する第1のデータ線と第2のデータ線、

を備え、

前記第1の画素行に含まれる3つの隣接する画素のうち、2つは前記第1のゲート線に接続され、残り1つは前記第2のゲート線に接続され、

前記第2の画素行に含まれる3つの隣接する画素のうち、1つは前記第2のゲート線に接続され、残り2つは前記第3のゲート線に接続され、

前記第1の画素行に含まれる3つの隣接する画素のうち、少なくとも1つは前記第1のデータ線に接続され、残りは前記第2のデータ線に接続されている、

液晶表示装置。 - 基板、

前記基板の上にマトリックス状に形成された複数の画素から成り、隣接する第1の画素行と第2の画素行とを含む画素マトリックス、

前記基板の上で前記画素マトリックスの行方向に延び、前記第1の画素行に含まれる画素のいずれかに接続されている第1のゲート線、

前記基板の上で前記画素マトリックスの行方向に延び、前記第1の画素行に含まれる画素のいずれかと、前記第2の画素行に含まれる画素のいずれかと、に接続されている第2のゲート線、

前記基板の上で前記画素マトリックスの行方向に延び、前記第2の画素行に含まれる画素のいずれかに接続されている第3のゲート線、及び、

前記基板の上で前記画素マトリックスの列方向に延び、各画素にデータ電圧を供給する第1のデータ線と第2のデータ線、

を備え、

前記第1の画素行に含まれる3つの隣接する画素のうち、少なくとも1つは前記第1のデータ線に接続され、残りは前記第2のデータ線に接続され、

前記第2の画素行に含まれる3つの隣接する画素のうち、少なくとも1つは前記第2のデータ線に接続され、残りは前記第1のデータ線に接続されている、

液晶表示装置。 - 前記第1の画素行に含まれる3つの隣接する画素を、第1の画素、第2の画素、及び第3の画素、とし、

前記第2の画素行に含まれる3つの隣接する画素であり、前記第1の画素、前記第2の画素、及び前記第3の画素、のそれぞれに前記画素マトリックスの列方向で隣接する3つの画素を、第4の画素、第5の画素、及び第6の画素、とするとき、

前記第1の画素は前記第1のデータ線に接続され、第2の画素は前記第2のデータ線に接続され、前記第3の画素は前記第2のデータ線に接続され、

前記第4の画素は前記第1のデータ線に接続され、前記第5の画素は前記第1のデータ線に接続され、前記第6の画素は前記第2のデータ線に接続されている、

請求項6に記載の液晶表示装置。 - 前記第1の画素行に含まれる3つの隣接する画素を、第1の画素、第2の画素、及び第3の画素、とし、

前記第2の画素行に含まれる3つの隣接する画素であり、前記第1の画素、前記第2の画素、及び前記第3の画素、のそれぞれに前記画素マトリックスの列方向で隣接する3つの画素を、第4の画素、第5の画素、及び第6の画素、とするとき、

前記第1の画素は前記第2のデータ線に接続され、前記第2の画素は前記第1のデータ線に接続され、前記第3の画素は前記第2のデータ線に接続され、

前記第4の画素は前記第1のデータ線に接続され、前記第5の画素は前記第2のデータ線に接続され、前記第6の画素は前記第1のデータ線に接続されている、

請求項6に記載の液晶表示装置。 - 前記第1の画素行と前記第2の画素行とのそれぞれに含まれる3つの隣接する画素が、赤色画素、緑色画素、及び青色画素からなる請求項5または6に記載の液晶表示装置。

- 基板、

前記基板の上にマトリックス状に形成された複数の画素からなり、隣接する第1の画素行と第2の画素行とを含む画素マトリックス、

前記基板の上で前記画素マトリックスの行方向に延び、前記第1の画素行に含まれる画素のいずれかに接続されている第1のゲート線、

前記基板の上で前記画素マトリックスの行方向に延び、前記第1の画素行に含まれる画素のいずれかと、前記第2の画素行に含まれる画素のいずれかとに接続されている第2のゲート線及び、

前記基板の上で前記画素マトリックスの行方向に延び、前記第2の画素行に含まれる画素のいずれかに接続されている第3のゲート線を備えている液晶表示装置を駆動する方法であり、

ゲートオン電圧を、水平周期の2倍に等しい期間中に、前記第1ないし第3のゲート線に対して順番に印加する段階を含む液晶表示装置の駆動方法。 - 前記第1ないし第3のゲート線のそれぞれに対し、短くとも水平周期の2/3倍に等しい時間ずつゲートオン電圧を印加する請求項10に記載の液晶表示装置の駆動方法。

- 前記第1ないし第3のゲート線のそれぞれに対するゲートオン電圧の印加期間を水平周期の1/3倍〜1倍ずつ互いに重ねる請求項10に記載の液晶表示装置の駆動方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060003996A KR101196860B1 (ko) | 2006-01-13 | 2006-01-13 | 액정 표시 장치 |

| KR10-2006-0003996 | 2006-01-13 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007188089A JP2007188089A (ja) | 2007-07-26 |

| JP2007188089A5 JP2007188089A5 (ja) | 2010-02-25 |

| JP5414974B2 true JP5414974B2 (ja) | 2014-02-12 |

Family

ID=38262702

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007005538A Expired - Fee Related JP5414974B2 (ja) | 2006-01-13 | 2007-01-15 | 液晶表示装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7796106B2 (ja) |

| JP (1) | JP5414974B2 (ja) |

| KR (1) | KR101196860B1 (ja) |

| CN (1) | CN101000414B (ja) |

Families Citing this family (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101407285B1 (ko) * | 2006-05-22 | 2014-06-13 | 엘지디스플레이 주식회사 | 액정표시장치 및 이의 구동방법 |

| KR101393628B1 (ko) * | 2007-02-14 | 2014-05-12 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| KR101627724B1 (ko) | 2007-12-03 | 2016-06-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 |

| TWI396912B (zh) * | 2008-01-31 | 2013-05-21 | Novatek Microelectronics Corp | 子畫素重新排列之液晶顯示器 |

| CN101533616B (zh) * | 2008-03-14 | 2011-05-18 | 胜华科技股份有限公司 | 一种用于液晶显示器的多工驱动电路 |

| TWI401658B (zh) * | 2008-07-18 | 2013-07-11 | Hannstar Display Corp | 液晶面板之閘極線驅動電路 |

| KR101595817B1 (ko) * | 2008-08-22 | 2016-02-22 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| KR101268963B1 (ko) * | 2008-10-30 | 2013-05-30 | 엘지디스플레이 주식회사 | 액정표시장치 |

| KR101535919B1 (ko) | 2008-12-12 | 2015-07-13 | 삼성디스플레이 주식회사 | 데이터 처리 방법, 이를 수행하기 위한 구동 장치 및 이 데이터 처리 장치를 구비한 표시 장치 |

| KR101542511B1 (ko) | 2008-12-24 | 2015-08-07 | 삼성디스플레이 주식회사 | 표시 장치 |

| TWI396026B (zh) * | 2009-07-22 | 2013-05-11 | Au Optronics Corp | 畫素陣列 |

| CN102023401B (zh) * | 2009-09-18 | 2014-04-16 | 北京京东方光电科技有限公司 | Tft-lcd阵列基板及其制造方法 |

| KR101604140B1 (ko) * | 2009-12-03 | 2016-03-17 | 엘지디스플레이 주식회사 | 액정표시장치 |

| KR101718499B1 (ko) * | 2010-02-01 | 2017-03-22 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| JP5620211B2 (ja) * | 2010-09-24 | 2014-11-05 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| CN102455552B (zh) * | 2010-10-19 | 2015-02-18 | 京东方科技集团股份有限公司 | 液晶显示器 |

| TWI471643B (zh) * | 2011-07-12 | 2015-02-01 | Innolux Corp | 影像顯示系統及其製造方法 |

| US20130076720A1 (en) * | 2011-09-23 | 2013-03-28 | Ahmad Al-Dahle | Pixel guard lines and multi-gate line configuration |

| TWI460518B (zh) | 2012-04-03 | 2014-11-11 | Au Optronics Corp | 顯示面板之陣列基板及畫素單元 |

| CN102955310B (zh) * | 2012-10-26 | 2015-04-15 | 京东方科技集团股份有限公司 | 一种像素驱动结构、驱动方法及显示装置 |

| TWI473057B (zh) | 2013-01-30 | 2015-02-11 | Au Optronics Corp | 畫素單元及畫素陣列 |

| KR102043165B1 (ko) | 2013-01-30 | 2019-11-12 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102020354B1 (ko) | 2013-03-12 | 2019-11-05 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| CN106019743B (zh) * | 2016-06-15 | 2023-08-22 | 京东方科技集团股份有限公司 | 一种阵列基板、其驱动方法及相关装置 |

| WO2017036430A2 (en) * | 2016-11-28 | 2017-03-09 | Viewtrix Technology Co., Ltd | Distributive-driving of display panel |

| EP3553154A4 (en) * | 2016-12-06 | 2020-06-24 | JNC Corporation | LIQUID CRYSTAL COMPOSITION AND LIQUID CRYSTAL DIMMER ELEMENT |

| US10504463B2 (en) * | 2017-03-13 | 2019-12-10 | Synaptics Incorporated | Display panel with reduced source lines |

| US10955695B2 (en) | 2017-05-18 | 2021-03-23 | Sharp Kabushiki Kaisha | Display device |

| WO2018221478A1 (ja) * | 2017-05-30 | 2018-12-06 | シャープ株式会社 | 液晶表示装置 |

| US20210132453A1 (en) * | 2017-05-30 | 2021-05-06 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| JP7187792B2 (ja) * | 2018-03-22 | 2022-12-13 | カシオ計算機株式会社 | 電子機器、電子時計、液晶制御方法およびプログラム |

| CN108538236A (zh) * | 2018-04-25 | 2018-09-14 | 京东方科技集团股份有限公司 | 阵列基板及其驱动方法、显示装置 |

| CN109032409B (zh) * | 2018-07-26 | 2021-11-02 | 京东方科技集团股份有限公司 | 一种显示面板的驱动方法、显示面板及显示装置 |

| KR102482983B1 (ko) * | 2018-08-02 | 2022-12-30 | 삼성디스플레이 주식회사 | 표시 패널 및 표시 장치 |

| CN109147654A (zh) * | 2018-10-30 | 2019-01-04 | 京东方科技集团股份有限公司 | 显示基板及显示装置 |

| CN109872697B (zh) * | 2019-03-26 | 2023-12-15 | 合肥鑫晟光电科技有限公司 | 一种阵列基板、显示面板、显示装置 |

| CN110136630B (zh) * | 2019-06-18 | 2022-10-04 | 京东方科技集团股份有限公司 | 一种显示面板及其驱动方法、显示装置 |

| TW202219929A (zh) * | 2020-10-06 | 2022-05-16 | 日商索尼半導體解決方案公司 | 顯示裝置 |

| CN113851072B (zh) * | 2020-10-12 | 2024-05-10 | 友达光电股份有限公司 | 驱动电路 |

| KR20220095854A (ko) | 2020-12-30 | 2022-07-07 | 엘지디스플레이 주식회사 | 표시장치 및 그 구동 방법 |

| JP7431793B2 (ja) | 2021-12-14 | 2024-02-15 | シャープディスプレイテクノロジー株式会社 | アクティブマトリクス基板、および表示パネル |

| CN114283759A (zh) * | 2021-12-30 | 2022-04-05 | 滁州惠科光电科技有限公司 | 像素结构、像素结构的驱动方法和显示面板 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0740102B2 (ja) * | 1986-03-10 | 1995-05-01 | 株式会社東芝 | アクテイブマトリクス型液晶表示装置 |

| US4901066A (en) * | 1986-12-16 | 1990-02-13 | Matsushita Electric Industrial Co., Ltd. | Method of driving an optical modulation device |

| JP2581796B2 (ja) * | 1988-04-25 | 1997-02-12 | 株式会社日立製作所 | 表示装置及び液晶表示装置 |

| JPH05134629A (ja) * | 1991-11-12 | 1993-05-28 | Fujitsu Ltd | アクテイブマトリクス型液晶表示パネル及びその駆動方法 |

| JP3300638B2 (ja) * | 1997-07-31 | 2002-07-08 | 株式会社東芝 | 液晶表示装置 |

| KR100277182B1 (ko) * | 1998-04-22 | 2001-01-15 | 김영환 | 액정표시소자 |

| JP3504496B2 (ja) * | 1998-05-11 | 2004-03-08 | アルプス電気株式会社 | 液晶表示装置の駆動方法および駆動回路 |

| KR100661826B1 (ko) * | 1999-12-31 | 2006-12-27 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 |

| KR100447233B1 (ko) * | 2001-12-28 | 2004-09-04 | 엘지.필립스 엘시디 주식회사 | 액정표시소자 |

| KR100951350B1 (ko) | 2003-04-17 | 2010-04-08 | 삼성전자주식회사 | 액정 표시 장치 |

| KR100945581B1 (ko) | 2003-06-23 | 2010-03-08 | 삼성전자주식회사 | 액정 표시 장치 및 그 구동 방법 |

| US7525526B2 (en) * | 2003-10-28 | 2009-04-28 | Samsung Electronics Co., Ltd. | System and method for performing image reconstruction and subpixel rendering to effect scaling for multi-mode display |

| US7358949B2 (en) * | 2004-02-25 | 2008-04-15 | Au Optronics Corp. | Liquid crystal display device pixel and drive circuit |

| KR101039023B1 (ko) | 2004-04-19 | 2011-06-03 | 삼성전자주식회사 | 액정 표시 장치 |

| KR20050113907A (ko) * | 2004-05-31 | 2005-12-05 | 삼성전자주식회사 | 액정 표시 장치 및 그의 구동 방법 |

| US7420550B2 (en) * | 2004-08-31 | 2008-09-02 | Vast View Technology, Inc. | Liquid crystal display driving device of matrix structure type and its driving method |

| KR101061854B1 (ko) * | 2004-10-01 | 2011-09-02 | 삼성전자주식회사 | 액정 표시 장치 및 그 구동 방법 |

| KR101171176B1 (ko) * | 2004-12-20 | 2012-08-06 | 삼성전자주식회사 | 박막 트랜지스터 표시판 및 표시 장치 |

| KR101160839B1 (ko) * | 2005-11-02 | 2012-07-02 | 삼성전자주식회사 | 액정 표시 장치 |

-

2006

- 2006-01-13 KR KR1020060003996A patent/KR101196860B1/ko active IP Right Grant

- 2006-12-14 US US11/610,816 patent/US7796106B2/en active Active

- 2006-12-21 CN CN2006101692541A patent/CN101000414B/zh not_active Expired - Fee Related

-

2007

- 2007-01-15 JP JP2007005538A patent/JP5414974B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007188089A (ja) | 2007-07-26 |

| US20070164964A1 (en) | 2007-07-19 |

| CN101000414B (zh) | 2010-09-01 |

| US7796106B2 (en) | 2010-09-14 |

| KR20070075584A (ko) | 2007-07-24 |

| CN101000414A (zh) | 2007-07-18 |

| KR101196860B1 (ko) | 2012-11-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5414974B2 (ja) | 液晶表示装置 | |

| KR101204365B1 (ko) | 액정 표시 패널 및 그 제조 방법 | |

| US8416231B2 (en) | Liquid crystal display | |

| KR101127593B1 (ko) | 액정 표시 장치 | |

| JP4331192B2 (ja) | 液晶表示装置およびその駆動方法 | |

| JP4277894B2 (ja) | 電気光学装置、駆動回路および電子機器 | |

| US20050190138A1 (en) | LCD and method of driving the same | |

| GB2464789A (en) | Liquid crystal display | |

| KR102020938B1 (ko) | 액정표시장치 | |

| US20070013631A1 (en) | Liquid crystal display driving methodology with improved power consumption | |

| JP4597950B2 (ja) | 液晶表示装置及びその駆動方法 | |

| KR20140126150A (ko) | 액정 표시 장치 및 그 구동 방법 | |

| JP2006085131A (ja) | 液晶表示装置 | |

| US20140375627A1 (en) | Display device and driving method thereof | |

| US20090195492A1 (en) | Liquid crystal display device | |

| KR101730552B1 (ko) | 횡전계 방식 액정표시장치 및 그 구동방법 | |

| US8054393B2 (en) | Liquid crystal display device | |

| KR20070008742A (ko) | 어레이 기판 및 이를 갖는 표시장치 | |

| EP2392963A1 (en) | Liquid crystal display device | |

| WO2020026954A1 (ja) | 表示装置及びその駆動方法 | |

| WO2011104947A1 (ja) | 液晶表示装置、テレビジョン受像機、液晶表示装置の表示方法 | |

| JP2011164236A (ja) | 表示装置 | |

| KR20040016185A (ko) | 액정표시패널 및 그 구동방법 | |

| TWI430001B (zh) | 顯示裝置 | |

| JP2010139776A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100112 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100112 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101220 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120828 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121105 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20121105 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20121213 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130325 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130409 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130522 |

|

| TRDD | Decision of grant or rejection written | ||

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131113 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5414974 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |