JP2014165210A - モジュール基板 - Google Patents

モジュール基板 Download PDFInfo

- Publication number

- JP2014165210A JP2014165210A JP2013032450A JP2013032450A JP2014165210A JP 2014165210 A JP2014165210 A JP 2014165210A JP 2013032450 A JP2013032450 A JP 2013032450A JP 2013032450 A JP2013032450 A JP 2013032450A JP 2014165210 A JP2014165210 A JP 2014165210A

- Authority

- JP

- Japan

- Prior art keywords

- board

- sub

- external electrode

- substrate

- module substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/14—Structural association of two or more printed circuits

- H05K1/144—Stacked arrangements of planar printed circuit boards

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49833—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers the chip support structure consisting of a plurality of insulating substrates

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/14—Structural association of two or more printed circuits

- H05K1/141—One or more single auxiliary printed circuits mounted on a main printed circuit, e.g. modules, adapters

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10227—Other objects, e.g. metallic pieces

- H05K2201/10378—Interposers

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Combinations Of Printed Boards (AREA)

Abstract

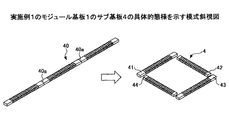

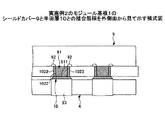

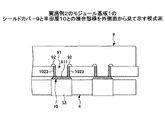

【解決手段】本発明によるモジュール基板1は、両面に電子部品2を実装されるメイン基板3と、メイン基板3の一方面側に配置されるサブ基板4と、サブ基板4の外部に形成される外部電極5と、外部電極5とメイン基板3の一方面側の端子部6とを接合する接合部材10とを含み、外部電極5はサブ基板4の他方面側に位置する他方面部51と一方面側に位置する一方面部52と一方面部52と他方面部51を接続する接続部53を含み、接合部材10の外部電極5との接合面101は他方面部51と接続部53の他方面側の一部とを少なくとも覆うことを特徴とする。

【選択図】図3

Description

2 電子部品

3 メイン基板

4 サブ基板

41〜4 サブ基板部分

5 外部電極

51 他方面部

52 一方面部

53 接続部

6 パッド(端子部:メイン基板3側)

7 マザーボード(接続対象基板)

8 パッド(端子部:マザーボード7側)

9 シールドカバー(遮蔽部材)

91 舌片部

911 端部

92 パンチ穴部

10 半田層(接合部材)

101 接合面(外部電極5側)

102 接合面(パッド6側)

1021 隙間部

1022 側面部

1023 舌辺側部

11 半田層(一方面側接合部材)

111 接合面(パッド8側)

Claims (8)

- 両面に電子部品を実装されるメイン基板と、当該メイン基板の一方面側に配置されるサブ基板と、当該サブ基板の外部に形成される外部電極と、前記外部電極と前記メイン基板の一方面側の端子部とを接合する接合部材とを含み、前記外部電極は前記サブ基板の他方面側に位置する他方面部と一方面側に位置する一方面部と当該一方面部と前記他方面部を接続する接続部を含み、前記接合部材の前記外部電極との接合面は前記他方面部と前記接続部の他方面側の一部とを少なくとも覆うことを特徴とするモジュール基板。

- 前記端子部は前記他方面部よりも外形が大きいことを特徴とする請求項1に記載のモジュール基板。

- 前記メイン基板の接続対象となる接続対象基板の側の端子部と前記外部電極とを接合する一方面側接合部材を含み、当該一方面側接合部材の前記外部電極との接合面は前記一方面部と前記接続部の一方面側の一部とを少なくとも覆うことを特徴とする請求項2に記載のモジュール基板。

- 前記接続対象基板の側の端子部よりも前記一方面部は外形が大きいことを特徴とする請求項3に記載のモジュール基板。

- 前記メイン基板を遮蔽する遮蔽部材を含み、当該遮蔽部材の一方面側に突出する端部は前記メイン基板の一方面と面直方向で一致させるとともに、前記接合部材の前記端子部との接合面は前記端部も覆うことを特徴とする請求項1〜4のいずれか一項に記載のモジュール基板。

- 前記サブ基板は前記メイン基板の有する複数の辺に沿って形成されるとともに、前記接続部は前記サブ基板の外縁側と内縁側の側面の少なくともいずれかに形成されることを特徴とする請求項1〜5のいずれか一項に記載のモジュール基板。

- 前記サブ基板は前記メイン基板の有する縁に個々に対応するサブ基板部分からなることを特徴とする請求項6に記載のモジュール基板。

- 前記サブ基板部分は一の棒状のサブ基板母材を切断して構成されることを特徴とする請求項7に記載のモジュール基板。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013032450A JP2014165210A (ja) | 2013-02-21 | 2013-02-21 | モジュール基板 |

| US14/184,958 US9468104B2 (en) | 2013-02-21 | 2014-02-20 | Module board |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013032450A JP2014165210A (ja) | 2013-02-21 | 2013-02-21 | モジュール基板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014165210A true JP2014165210A (ja) | 2014-09-08 |

| JP2014165210A5 JP2014165210A5 (ja) | 2016-04-07 |

Family

ID=51350999

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013032450A Pending JP2014165210A (ja) | 2013-02-21 | 2013-02-21 | モジュール基板 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9468104B2 (ja) |

| JP (1) | JP2014165210A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020512688A (ja) * | 2017-03-09 | 2020-04-23 | 華為技術有限公司Huawei Technologies Co.,Ltd. | 消費者向け電子製品のメインボードおよび端末 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9363892B2 (en) * | 2013-07-19 | 2016-06-07 | Google Technology Holdings LLC | Circuit assembly and corresponding methods |

| DE102015220676A1 (de) * | 2015-10-22 | 2017-04-27 | Zf Friedrichshafen Ag | Leiterplatte und Anordnung mit einer Leiterplatte |

| DE102017206099A1 (de) * | 2017-04-10 | 2018-10-11 | BSH Hausgeräte GmbH | Leiterplatten-Anordnung sowie Verfahren zur Herstellung einer Leiterplatten-Anordnung |

| US11553616B2 (en) * | 2018-12-07 | 2023-01-10 | Delta Electronics, Inc. | Module with power device |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06111869A (ja) * | 1992-09-29 | 1994-04-22 | Fujitsu Ltd | 表面実装用端子 |

| JP2007066936A (ja) * | 2005-08-29 | 2007-03-15 | Matsushita Electric Ind Co Ltd | 高周波モジュールとその製造方法 |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0732107A3 (en) * | 1995-03-16 | 1997-05-07 | Toshiba Kk | Screen device for circuit substrate |

| US6525414B2 (en) * | 1997-09-16 | 2003-02-25 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device including a wiring board and semiconductor elements mounted thereon |

| US6137164A (en) * | 1998-03-16 | 2000-10-24 | Texas Instruments Incorporated | Thin stacked integrated circuit device |

| SG111958A1 (en) * | 1998-03-18 | 2005-06-29 | Hitachi Cable | Semiconductor device |

| JP2001167969A (ja) * | 1999-12-06 | 2001-06-22 | Tdk Corp | 三次元搭載用多端子積層セラミックコンデンサ |

| US6528870B2 (en) * | 2000-01-28 | 2003-03-04 | Kabushiki Kaisha Toshiba | Semiconductor device having a plurality of stacked wiring boards |

| CN1207785C (zh) * | 2000-03-21 | 2005-06-22 | 三菱电机株式会社 | 半导体器件、电子装置的制造方法、电子装置和携带式信息终端 |

| US6528408B2 (en) * | 2001-05-21 | 2003-03-04 | Micron Technology, Inc. | Method for bumped die and wire bonded board-on-chip package |

| US7087988B2 (en) * | 2002-07-30 | 2006-08-08 | Kabushiki Kaisha Toshiba | Semiconductor packaging apparatus |

| JP2004303944A (ja) | 2003-03-31 | 2004-10-28 | Matsushita Electric Ind Co Ltd | モジュール基板及びその製造方法 |

| PL200759B1 (pl) * | 2003-04-25 | 2009-02-27 | Adb Polska Sp | Zestaw płytek z obwodami drukowanymi |

| JP2005277355A (ja) * | 2004-03-26 | 2005-10-06 | Sanyo Electric Co Ltd | 回路装置 |

| JP2005286057A (ja) * | 2004-03-29 | 2005-10-13 | Sanyo Electric Co Ltd | 回路装置およびその製造方法 |

| JP4421436B2 (ja) * | 2004-09-30 | 2010-02-24 | 太陽誘電株式会社 | 面実装コイル部品 |

| JP4864419B2 (ja) * | 2005-10-28 | 2012-02-01 | 株式会社東芝 | プリント回路板および電子機器 |

| JP4740765B2 (ja) * | 2006-02-24 | 2011-08-03 | エルピーダメモリ株式会社 | 半導体装置及びその製造方法 |

| JP2007281276A (ja) * | 2006-04-10 | 2007-10-25 | Nec Electronics Corp | 半導体装置 |

| US20070241441A1 (en) * | 2006-04-17 | 2007-10-18 | Stats Chippac Ltd. | Multichip package system |

| JP2007294560A (ja) * | 2006-04-24 | 2007-11-08 | Nec Electronics Corp | 半導体装置およびその製造方法 |

| JP5154262B2 (ja) * | 2008-02-26 | 2013-02-27 | 太陽誘電株式会社 | 電子部品 |

| TWI362732B (en) * | 2008-04-07 | 2012-04-21 | Nanya Technology Corp | Multi-chip stack package |

| KR20100046760A (ko) * | 2008-10-28 | 2010-05-07 | 삼성전자주식회사 | 반도체 패키지 |

| CN102369600B (zh) * | 2009-04-02 | 2014-09-10 | 株式会社村田制作所 | 电路基板 |

| JP5234521B2 (ja) * | 2009-08-21 | 2013-07-10 | Tdk株式会社 | 電子部品及びその製造方法 |

| JP2011171427A (ja) * | 2010-02-17 | 2011-09-01 | Canon Inc | 積層型半導体装置 |

| US8847376B2 (en) * | 2010-07-23 | 2014-09-30 | Tessera, Inc. | Microelectronic elements with post-assembly planarization |

| JP2012079876A (ja) * | 2010-09-30 | 2012-04-19 | Fujitsu Ltd | 電子装置の製造方法及び電子装置 |

| JP2012104790A (ja) * | 2010-10-12 | 2012-05-31 | Elpida Memory Inc | 半導体装置 |

| JP5788166B2 (ja) * | 2010-11-02 | 2015-09-30 | 新光電気工業株式会社 | 接続端子構造及びその製造方法、並びにソケット |

| JP5360158B2 (ja) * | 2011-08-05 | 2013-12-04 | 株式会社村田製作所 | チップ部品構造体 |

| US8436457B2 (en) * | 2011-10-03 | 2013-05-07 | Invensas Corporation | Stub minimization for multi-die wirebond assemblies with parallel windows |

| KR101894823B1 (ko) * | 2011-10-03 | 2018-09-04 | 인벤사스 코포레이션 | 평행한 윈도우를 갖는 다중-다이 와이어 본드 어셈블리를 위한 스터브 최소화 |

| US9462732B2 (en) * | 2013-03-13 | 2016-10-04 | Laird Technologies, Inc. | Electromagnetic interference shielding (EMI) apparatus including a frame with drawn latching features |

| JP6336714B2 (ja) * | 2013-05-27 | 2018-06-06 | 富士通コンポーネント株式会社 | 電子装置 |

| JP2015195263A (ja) * | 2014-03-31 | 2015-11-05 | マイクロン テクノロジー, インク. | 半導体装置及びその製造方法 |

-

2013

- 2013-02-21 JP JP2013032450A patent/JP2014165210A/ja active Pending

-

2014

- 2014-02-20 US US14/184,958 patent/US9468104B2/en not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06111869A (ja) * | 1992-09-29 | 1994-04-22 | Fujitsu Ltd | 表面実装用端子 |

| JP2007066936A (ja) * | 2005-08-29 | 2007-03-15 | Matsushita Electric Ind Co Ltd | 高周波モジュールとその製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020512688A (ja) * | 2017-03-09 | 2020-04-23 | 華為技術有限公司Huawei Technologies Co.,Ltd. | 消費者向け電子製品のメインボードおよび端末 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20140233191A1 (en) | 2014-08-21 |

| US9468104B2 (en) | 2016-10-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9552923B2 (en) | Electronic component | |

| JP2014165210A (ja) | モジュール基板 | |

| JP2007048976A (ja) | プリント回路板、およびプリント回路板を備えた電子機器 | |

| JP2011129708A (ja) | プリント配線板の接続構造 | |

| JP6318638B2 (ja) | プリント配線板および情報処理装置 | |

| JP4433058B2 (ja) | 電子装置及びその製造方法 | |

| JP2011100912A (ja) | パワー半導体モジュールのプリント配線板への実装構造 | |

| JP2021158225A (ja) | シールドケース及び電子回路モジュール | |

| JP5300994B2 (ja) | 電子機器 | |

| JP2013157565A (ja) | 電子機器 | |

| JP2008098398A (ja) | 回路装置及びその製造方法 | |

| JP2016082022A (ja) | 回路モジュール | |

| JP5300995B2 (ja) | 電子機器 | |

| JP2015159253A (ja) | プリント基板 | |

| KR101473478B1 (ko) | 인쇄회로 기판의 모듈 실장 구조 | |

| JP2015065208A (ja) | 補強用基板を用いたモジュール構造体 | |

| JP3185456U (ja) | 余剰はんだによる部品の実装不良を抑制するプリント配線板 | |

| JP6124258B2 (ja) | 電子回路ユニット及び電子回路ユニットの製造方法 | |

| JP6378906B2 (ja) | 電子回路モジュール用基板、電子回路モジュール用基板のための多面取り基板、及び電子回路モジュール用基板の製造方法 | |

| JP2018129464A (ja) | プリント回路基板及びプリント回路装置 | |

| JP6445220B1 (ja) | 電子装置およびその製造方法 | |

| JP2016054190A (ja) | 表面実装型パッケージ及び表面実装型パッケージとバイパスコンデンサの配線方法 | |

| JP2011103368A (ja) | 実装基板、電子機器および実装基板の製造方法 | |

| JPWO2020021743A1 (ja) | プリント回路板 | |

| JP2008124273A (ja) | シールド構造基板とその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161220 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20170620 |