JP2008166360A - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP2008166360A JP2008166360A JP2006351721A JP2006351721A JP2008166360A JP 2008166360 A JP2008166360 A JP 2008166360A JP 2006351721 A JP2006351721 A JP 2006351721A JP 2006351721 A JP2006351721 A JP 2006351721A JP 2008166360 A JP2008166360 A JP 2008166360A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- cap layer

- electrode

- layer insulating

- ruthenium

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/692—Electrodes

- H10D1/694—Electrodes comprising noble metals or noble metal oxides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

Abstract

【課題】 ルテニウム或いは酸化ルテニウムを上部電極、二酸化ハフニウム或いは酸化ジルコニウムを絶縁膜に用いたDRAMキャパシタにおいて、ルテニウム等の二酸化ハフニウム等中への拡散を抑制すること。

【解決手段】 ルテニウム或いは酸化ルテニウムの上部電極および二酸化ハフニウム或いは酸化ジルコニウムの絶縁膜の界面に、キャップ層絶縁膜として前記絶縁膜よりも誘電率の大きな五酸化タンタル或いは酸化ニオブを挿入し、ルテニウム等の二酸化ハフニウム等中への拡散を抑制する。

【選択図】 図31

【解決手段】 ルテニウム或いは酸化ルテニウムの上部電極および二酸化ハフニウム或いは酸化ジルコニウムの絶縁膜の界面に、キャップ層絶縁膜として前記絶縁膜よりも誘電率の大きな五酸化タンタル或いは酸化ニオブを挿入し、ルテニウム等の二酸化ハフニウム等中への拡散を抑制する。

【選択図】 図31

Description

本発明は、容量に電荷を蓄積して情報を記録するメモリであるDRAM(Dynamic Random Access Memory)の容量の構成に関するものである。

半導体デバイスは、高性能化を目的に微細化が進められている。DRAMのメモリセルは、微細化に伴いその占有面積が縮小する一方で、メモリセル内に作られるキャパシタは、読み出し不良防止のために、世代に関わらず一定の容量が要求される。そのため、次世代キャパシタの開発には、容量の高密度化が求められる。容量を高密度化するためには、電極面積の増大、絶縁膜の薄膜化が行なわれてきた。従来、電極構造は平板型であったが、一定面積のメモリセル内で電極面積を増大させるために、立体化の技術が用いられてきた。現在主流なのはスタック型、又はトレンチ型のキャパシタである。共にキャパシタ構造は円筒形であり、円筒の径に対する高さの比を示すアスペクト比は、20以上と非常に大きく、その加工は次第に困難となっている。又、下部電極にポリシリコンが用いられているMIS型のキャパシタが用いられる世代では、ポリシリコンの表面粗面化技術が用いられ、電極の実効的な面積を増大させていた。しかし、ポリシリコンの表面粗面化技術で増やせる面積の割合にも限界が存在する。そのため、同時に絶縁膜の薄膜化が進められている。

絶縁膜を薄膜化すると、絶縁膜を突き抜けて流れるリーク電流の増大が問題となる。DRAMでは情報を保持するために、キャパシタの電荷を蓄えなおすリフレッシュという動作が存在するが、リーク電流が大きいとリフレッシュ動作の頻度を増加しなくてはならず、その結果、消費電力が増大する。この消費電力の増大を抑制するために、リーク電流密度は世代に依らずおよそ1×10-7A/cm2以下に抑制する必要がある。従来、絶縁膜の材料には二酸化シリコンが用いられていたが、比誘電率を3.9と仮定して容量から換算した膜厚である酸化膜換算膜厚が6 nm以下となると、直接トンネルリーク電流が顕著となる。直接トンネルリーク電流は、絶縁膜の物理膜厚でリーク電流量がほぼ決まっており、膜厚が1nm薄くなると、リーク電流が桁で増大する。そのため、直接トンネルリーク電流が顕著である状態では、膜厚ばらつきに起因したリーク電流ばらつきによりメモリアレイのキャパシタ全てを、必要なリーク電流スペック内に収めることが難しい。つまり、直接トンネルリーク電流の抑制は必須である。

酸化膜換算膜厚の減少によるキャパシタ容量の増大および、物理膜厚増大による直接トンネルリーク電流の抑制を両立させる方法として考えられたのが、高誘電率絶縁膜の適用である。高誘電率絶縁膜材料の二酸化ハフニウムは、比誘電率が20程度であるため、酸化膜換算膜厚が2.0nmであっても物理膜厚を10nm以上にでき、直接トンネルリーク電流抑制には効果的である。又、二酸化ハフニウム高誘電率絶縁膜が用いられる世代では、空乏化容量が無く、薄膜化に有利なMIM型キャパシタの適用が有力である。その際、用いられる下部電極の材料は、DRAMプロセス親和性の高い窒化チタンが最有力である。二酸化ハフニウムは下部電極窒化チタンと良好な界面を形成することが知られており、有望な絶縁膜材料である。

ところで、こうした絶縁材料である二酸化ハフニウムと電極としての窒化チタンを用いたDRAM用キャパシタの報告が、IEEE、2004の“A Robust Alternative for the DRAM Capacitor of 50nm Generation”になされている。ここでは、Toxeqの確保することを前提として、キャパシタとして、Ru/Ta2O5/HfO2/TiNの検討がなされている(非特許文献1)。

2004 IEEE、三星電子、Nongseo-Lee等著、"A Robust Alternative for the DRAM Capacitor of 50nm Generation"、2004

しかし、前述の二酸化ハフニウムのように高い誘電率を有する絶縁膜を用いた場合、絶縁性能の低下によるリーク電流の増大が問題となる。材料物性の傾向として、高誘電率になるほど禁性帯幅は狭くなるため、バリアの高さに影響を受けるFowler-Nordheimリーク電流などの増大が懸念される。そこで、電極および絶縁膜のバリア高さを相対的に高める方法として考えられるのが、仕事関数の大きな電極の適用である。例えば、ルテニウムは仕事関数が4.8eV程度であり、現在広く用いられている電極材料である窒化チタンの仕事関数4.2eVに比べ大きく、バリア高さを増大させることが可能である。

しかし、現今のDRAM技術の水準においては、キャパシタ用の絶縁膜と電極との組み合わせを十分検討しないと、実用的な特性を得ることが出来ない。

DRAM用キャパシタの各構成要素に関して、本願発明の基礎となる検討結果を示し、次いで本願発明の骨子を明らかにする。

先ず、代表的な材料であるルテニウムを用いた上部電極および二酸化ハフニウム絶縁膜を用いたキャパシタの評価を行なった。同構造のキャパシタをDRAMの製品に適用するためには、まず、各材料の界面での元素の深さ方向のプロファイルが急峻で無くてはならない。電極である金属は含まれる不純物密度を低くし、電気伝導度を上げることで、電流の熱発生によるエネルギーロスを最小限にする必要がある。又、絶縁膜は、金属元素等の不純物等を最小限にし、リーク電流を増大させる原因となる禁性帯中の状態密度発生等を防ぐ必要がある。互いの材料に不純物が混入する可能性として最も考えられるのが、積層による相互拡散、又は一方の材料を構成する元素の他方の材料への拡散である。キャパシタの酸化膜換算膜厚、及びリーク電流、又、信頼性で要求される性能を得るための第一条件として、一般的に材料同士が拡散を起こさないことは必須である。本発明が解決しようとする課題は、これまで述べたような観点から、二酸化ハフニウム絶縁膜およびルテニウム上部電極を用いた構造において、拡散及び相互拡散等の無い、元素プロファイルが深さ方向に急峻な界面を有するキャパシタを形成することである。

本願発明の骨子は、半導体基板上に形成された複数のワード線と、複数のビット線と、前記複数のワード線と前記複数のビット線の所定の交点に設けられたメモリ選択用トランジスタと前期メモリセル選択用トランジスタに電気的に直列に接続され、前記半導体基板上に形成された情報蓄積用キャパシタとから構成されるメモリセルとを備えた半導体集積回路装置であって、前記情報蓄積用キャパシタは、第2の電極、及び前記第2の電極上に成膜された絶縁膜、及び前記絶縁膜上に成膜されたキャップ層絶縁膜、及び前記キャップ層絶縁膜上に成膜された第1の電極を有するものである。そして、前記第1の電極は、ルテニウム及び酸化ルテニウムから選ばれた少なくとも一者であり、前記絶縁膜は、酸化ハフニウム、イットリウムを添加した酸化ハフニウム、及び酸化ジルコニウムの群から選ばれた少なくとも一者であり、前記第2の電極は、窒化チタン、チタン、窒化タンタル、タンタル、窒化タングステン、タングステン、リンをドーピングしたポリシリコン、金、銀、銅、及びプラチナの群から選ばれた少なくとも一者である。

前記第2の電極は、通例半導体基板側に設けられ、下部電極と通称される。前記第1の電極は、通例キャパシタ用絶縁膜に対して前記半導体基板とは反対側に設けられ、上部電極と通称される。

更に、前記キャップ層絶縁膜は、前記キャップ層絶縁膜は前記絶縁膜よりも誘電率の高い、酸化タンタル及び酸化ニオブから選ばれた少なくとも一者であり、その厚さは、連続膜を構成する。実際的には、前記キャップ層絶縁膜の膜厚は、2nm以上、3nm以下で十分である。又、バンドギャップは、キャパシタ絶縁膜より小さい。前記キャップ層絶縁膜は、前記絶縁膜と前記上部電極の間に挿入することにより、アルミナをキャップ層絶縁膜として用いた場合に比べて、前記絶縁膜の伝導体オフセットの低下量が小さくなされる。

更に、半導体基板を基準として、通例、前記キャップ層絶縁膜は、前記キャパシタ用絶縁膜の上部に形成されるが、その逆の積層関係としても良い。

本願発明のよれば、DRAMメモリを有する半導体集積回路装置の低消費電力化、大容量化、高速化を実現することが可能である。特にDRAMを用いた、高密度集積メモリ回路、およびメモリ回路と論理回路が同一半導体基板に設けられたロジック混載型メモリ、を有する半導体集積回路装置において、有用である。

<実施例1>

前述のように、本発明に係るキャパシタの第1の電極(上部電極)としては、ルテニウム、酸化ルテニウムのいずれか一者、第2の電極(下部電極)としては、窒化チタン、チタン、窒化タンタル、タンタル、窒化タングステン、タングステン、リンをドーピングしたポリシリコン、金、銀、銅、プラチナの群から選ばれた少なくとも一者を用いる。又、こうした第1及び第2の電極材料の選択を前提として、キャパシタの絶縁膜及びこれ対するキャップ層絶縁膜の検討を行った。尚、前記第2の電極の材料群はこれまでにも知られた材料であるので、その詳細説明は省略する。尚、各部材の厚さは、次の通りである。第1の電極(上部電極)は、5nmから30nm、第2の電極(下部電極)は、5nmから30nm、及びキャパシタの絶縁膜は、3nmから10nmの範囲で選択される。

前述のように、本発明に係るキャパシタの第1の電極(上部電極)としては、ルテニウム、酸化ルテニウムのいずれか一者、第2の電極(下部電極)としては、窒化チタン、チタン、窒化タンタル、タンタル、窒化タングステン、タングステン、リンをドーピングしたポリシリコン、金、銀、銅、プラチナの群から選ばれた少なくとも一者を用いる。又、こうした第1及び第2の電極材料の選択を前提として、キャパシタの絶縁膜及びこれ対するキャップ層絶縁膜の検討を行った。尚、前記第2の電極の材料群はこれまでにも知られた材料であるので、その詳細説明は省略する。尚、各部材の厚さは、次の通りである。第1の電極(上部電極)は、5nmから30nm、第2の電極(下部電極)は、5nmから30nm、及びキャパシタの絶縁膜は、3nmから10nmの範囲で選択される。

本実施例では、先ず、ルテニウムを第1(上部)電極に、窒化チタンを第2(下部)電極に、酸化ハフニウム(より具体例は二酸化ハフニウムである、以下同様である)を絶縁膜に、及び酸化タンタルを第2の絶縁膜(キャップ絶縁膜)として用いた代表例を例示する。必要に応じて、その他の材料に言及する。

以下、具体的なデータを用いた本実施例に関する説明の骨子は、次の通りである。

(1)先ず、前提として、ルテニウムの第1の電極は、仕事関数が大きく、キャパシタにおけるFNトンネルリーク電流を抑制するに好ましい。尚、酸化ルテニウムも同様である。

(2)キャパシタ用絶縁膜は,直接トンネルリーク電流抑制のためには6nm以上の物理膜厚が必要である。しかし,世代が進むにつれ,膜厚低減によりキャパシタ容量値を増大させる必要がある。そこで,物理膜厚に対し小さい酸化膜換算膜厚を得ることができる高誘電率材料をキャパシタ絶縁膜に適用する必要がある。一方,誘電率の大きな材料は,禁性帯幅が低下する傾向にあり,リーク電流増大の原因となる。これら4つのファクターの、実際的な側面から、絶縁膜材料として、二酸化ハフニウムが最も好ましい。更には、同様の理由によって、絶縁膜材料として、イットリウムが添加された酸化ハフニウム、酸化ジルコニウムをあげることが出来る。

(3)しかし、ルテニウムと二酸化ハフニウムとの直接の接触は、製造工程中に、ルテニウムの二酸化ハフニウムへの拡散を招く。この拡散防止の為、第2の絶縁膜(以下、キャップ層絶縁膜と称する)を、両者の界面に挿入する必要性がある。

(4)キャップ層絶縁膜は、キャパシタ絶縁膜よりも誘電率の大きな材料の採用が好ましい。その理由は、キャパシタ絶縁膜及びキャップ層絶縁膜の両者の酸化膜換算膜厚の増大及び容量の損失が無いことである。こうした観点から、キャップ層絶縁膜は、酸化タンタル(より具体例は五酸化タンタルである、以下同様である)、酸化ニオブなどが好ましい。その厚さは、連続膜を構成し且つ3nm以下の厚さとなす。実際的には、キャップ層絶縁膜の膜厚は、2nm以上である。キャップ層絶縁膜は、前記絶縁膜と前記上部電極の間に挿入することにより、絶縁膜の伝導体オフセットの低下量が小さい為である。

(1)先ず、前提として、ルテニウムの第1の電極は、仕事関数が大きく、キャパシタにおけるFNトンネルリーク電流を抑制するに好ましい。尚、酸化ルテニウムも同様である。

(2)キャパシタ用絶縁膜は,直接トンネルリーク電流抑制のためには6nm以上の物理膜厚が必要である。しかし,世代が進むにつれ,膜厚低減によりキャパシタ容量値を増大させる必要がある。そこで,物理膜厚に対し小さい酸化膜換算膜厚を得ることができる高誘電率材料をキャパシタ絶縁膜に適用する必要がある。一方,誘電率の大きな材料は,禁性帯幅が低下する傾向にあり,リーク電流増大の原因となる。これら4つのファクターの、実際的な側面から、絶縁膜材料として、二酸化ハフニウムが最も好ましい。更には、同様の理由によって、絶縁膜材料として、イットリウムが添加された酸化ハフニウム、酸化ジルコニウムをあげることが出来る。

(3)しかし、ルテニウムと二酸化ハフニウムとの直接の接触は、製造工程中に、ルテニウムの二酸化ハフニウムへの拡散を招く。この拡散防止の為、第2の絶縁膜(以下、キャップ層絶縁膜と称する)を、両者の界面に挿入する必要性がある。

(4)キャップ層絶縁膜は、キャパシタ絶縁膜よりも誘電率の大きな材料の採用が好ましい。その理由は、キャパシタ絶縁膜及びキャップ層絶縁膜の両者の酸化膜換算膜厚の増大及び容量の損失が無いことである。こうした観点から、キャップ層絶縁膜は、酸化タンタル(より具体例は五酸化タンタルである、以下同様である)、酸化ニオブなどが好ましい。その厚さは、連続膜を構成し且つ3nm以下の厚さとなす。実際的には、キャップ層絶縁膜の膜厚は、2nm以上である。キャップ層絶縁膜は、前記絶縁膜と前記上部電極の間に挿入することにより、絶縁膜の伝導体オフセットの低下量が小さい為である。

以下、上記項目(2)より(4)の事実を説明するに、ルテニウムを第1(上部)電極に、窒化チタンを第2(下部)電極に、二酸化ハフニウムを絶縁膜に用いたキャパシタの問題点とその解決策を考察する。

<絶縁膜材料として二酸化ハフニウムが好ましい理由>

二酸化ハフニウムが、現在、DRAMのメモリの供するキャパシタ用絶縁膜に要求されている酸化膜換算膜厚と非誘電率を確保するに極めて有用であることを考察する。尚、二酸化ハフニウムは、上部電極および下部電極に窒化チタンを用いたMIMキャパシタでの適用に対し有望であることは知られているが、各電極が窒化チタンである。これに対して、本願発明では、一方の第1の電極はルテニウム或いは酸化ルテニウムを用いるものである。こうした諸条件から、二酸化ハフニウムが好ましいことを説明する。

二酸化ハフニウムが、現在、DRAMのメモリの供するキャパシタ用絶縁膜に要求されている酸化膜換算膜厚と非誘電率を確保するに極めて有用であることを考察する。尚、二酸化ハフニウムは、上部電極および下部電極に窒化チタンを用いたMIMキャパシタでの適用に対し有望であることは知られているが、各電極が窒化チタンである。これに対して、本願発明では、一方の第1の電極はルテニウム或いは酸化ルテニウムを用いるものである。こうした諸条件から、二酸化ハフニウムが好ましいことを説明する。

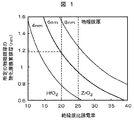

先ず、ある特定の誘電率の絶縁膜材料を用いて、得ることができる酸化膜換算膜厚を、図1を用いて説明する。図1は横軸が絶縁膜の比誘電率、縦軸が、各々の比誘電率の絶縁膜材料をある物理膜厚だけ成膜した場合に得られる酸化膜の換算膜厚の計算値を示す。パラメータは絶縁膜の物理膜厚である。絶縁膜材料として誘電率20の二酸化ハフニウムを、直接トンネルリーク電流を抑制可能な物理膜厚6nmに成膜した場合、図1より、薄膜化限界は約1.2nmである。図1での計算結果は、同構造で薄膜化を行なった場合、酸化膜換算膜厚1.2nm程度で直接トンネルリーク電流の増大に起因した薄膜化限界となることを示唆する。又、二酸化ハフニウムの物理膜厚を減少し、薄膜化を行なっていくと、絶縁膜のトンネル障壁の減少に起因した、Fowler-Nordheim (FN)トンネルリーク電流の増大も懸念される。特に、二酸化ハフニウムを、薄膜化限界である物理膜厚約6nm付近で使用する場合に問題が発生しやすいと考えられる。

一方、量産の生産ラインに備えられている絶縁膜の成膜装置に対する投資額を抑制し、コスト低減を行うためには、同じ材料をできるだけ長い世代に適用することが望ましい。そのためにも、上部電極および下部電極に窒化チタンを用いたMIM構造の二酸化ハフニウムキャパシタがFNトンネルリーク電流増大に起因した薄膜化限界に達した場合、上部電極を、窒化チタンよりも仕事関数が大きいルテニウムで置き換えることが望ましい。この構成によって、FNトンネルリーク電流を抑制し、さらに薄膜化を進めることが可能であると考えられる。ルテニウムで、上部電極および下部電極を置き換えることも有用である。

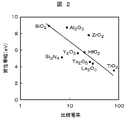

図2には、半導体向けの絶縁膜材料の候補が挙げられている。図2では、横軸と縦軸は、各々、比誘電率と禁性帯幅である。世代が進むにつれ高い誘電率が必要とされるが、リーク電流抑制のためには、大きな禁性帯幅も同時に必要である。しかし、図2から分かるように、比誘電率を増大すると禁性帯幅は減少する傾向があることが分かる。つまり、比誘電率が必要以上に大きな材料を用いると、禁性帯幅の狭さに起因したバリア高さの減少によりリーク電流抑制の観点から問題が生じる可能性がある。よって、各々の世代に用いる絶縁膜は、要求酸化膜換算膜厚の達成に必要な、適度な比誘電率を有する絶縁膜が望ましい。つまり、前述の酸化膜の換算膜厚1.2nm程度を得る場合、絶縁膜材料は二酸化ハフニウムが最も適した絶縁膜と言える。

<ルテニウムと二酸化ハフニウムとが直接接触する構造の問題点と、キャップ絶縁膜の必要性>

現在、DRAMに搭載するメモリセルキャパシタ向けには、リーク電流密度をおよそ10-7 A/cm2以下としなければならない。こうした条件に対して、上部電極にルテニウム、下部電極に窒化チタン、絶縁膜に二酸化ハフニウムを用いた構造のキャパシタが、どのようなリーク電流を有し、その原因は何かを検討した。そして、リーク電流の原因が、電極のルテニウムが絶縁膜の二酸化ハフニウム中に拡散していることであることを突きとめた。そこで、ルテニウムの拡散を抑制する方法として、ルテニウムと二酸化ハフニウムの界面に対して、キャップ層絶縁膜の挿入を検討した。

現在、DRAMに搭載するメモリセルキャパシタ向けには、リーク電流密度をおよそ10-7 A/cm2以下としなければならない。こうした条件に対して、上部電極にルテニウム、下部電極に窒化チタン、絶縁膜に二酸化ハフニウムを用いた構造のキャパシタが、どのようなリーク電流を有し、その原因は何かを検討した。そして、リーク電流の原因が、電極のルテニウムが絶縁膜の二酸化ハフニウム中に拡散していることであることを突きとめた。そこで、ルテニウムの拡散を抑制する方法として、ルテニウムと二酸化ハフニウムの界面に対して、キャップ層絶縁膜の挿入を検討した。

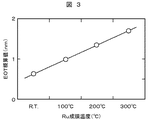

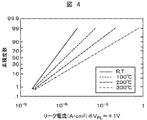

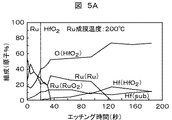

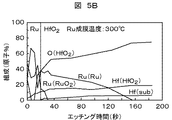

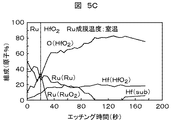

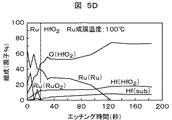

先ず、上部電極にルテニウム、下部電極に窒化チタン、絶縁膜に二酸化ハフニウムを用いた構造のキャパシタを試作し、電気特性および物理分析した結果を示す。図3は、ルテニウムの成膜温度とキャパシタの酸化膜の換算膜厚(ETO概算値)の関係を示す。成膜温度は、室温(R.T.)、100℃、200℃、300℃である。窒化チタンは化学気相成長法により30nm成膜し、二酸化ハフニウムは原子層成長法により10nm成膜、ルテニウムはスパッタ法により50nm成膜した。50%はおよそ、0.5nmと2.0nmの間に存在し、成膜温度の増大とともに増大する。又、リーク電流密度の累積度数分布の模式図を図4に示す。リーク電流密度の低いキャパシタは10-8A/cm -10-7A/cm2程度である、しかし、成膜温度の増大と共にばらつきは増大し、成膜温度300℃の場合は、リーク電流密度の大きなキャパシタは1 A/cm2程度である。前述したように、DRAMに搭載するメモリセルキャパシタ向けには、リーク電流密度をおよそ10-7 A/cm2以下としなければならない。この観点から、測定されたリーク電流は相当大きいと言わなければならない。

このリーク電流ばらつきの原因を究明するために、X線光電子分光法による分析と、アルゴンイオンによる試料のエッチングを交互に行い、各試料の深さ方向の元素分析を行った。図5(A)より図5(D)にこの結果を示す。各図は各々、Ruの成膜温度を、200℃、300℃、室温、100℃とした場合の結果である。又、縦軸は原子パーセントで示した各元素および各結合の占める割合、横軸がエッチング時間である。ここで、材料によりエッチングの速度が異なることに注意が必要である。ルテニウムは0.15nm/秒程度であり、二酸化ハフニウムは0.05nm/秒程度である。検出された元素および結合状態は、金属ルテニウムに起因したルテニウム、二酸化ルテニウムに起因したルテニウム、二酸化ハフニウム起因したハフニウム、ハフニウムのサブピーク、二酸化ハフニウムに起因した酸素の5つである。点線で示したアルゴンイオンエッチング時間が20秒より短い表面付近では、金属ルテニウムが支配的に存在する。しかし、点線より深い位置では、二酸化ハフニウムに起因するハフニウム、および酸素の量が支配的となる。この傾向は予想された通りである。しかし、ここで注目したいのは、界面付近での元素の量の変化の仕方である。相互拡散などの無い急峻な界面が形成されている場合、点線で示した時間付近で、界面よりも表面側にある元素は急激に減少すると考えられ、又、それよりも試料の深い位置に存在する元素は急激に増加すると考えられる。実際、二酸化ルテニウム起因のルテニウムは、アルゴンイオンエッチング時間の増大に対して急激に減少している。一方、二酸化ハフニウム起因のハフニウムおよび酸素は、アルゴンイオンエッチング時間の増大に対して比較的急峻に増大している。ところが、金属ルテニウムに起因するルテニウムは、アルゴンイオン時間の増大に対して、これまで見てきた元素と同等の傾きで減少することが予想される。しかし、実際は傾斜がなだらかになっている。ルテニウムの成膜温度が室温の試料では、金属ルテニウムに起因するルテニウムの原子パーセントが10%以下となるのが、約90秒である。これは、ルテニウムが二酸化ハフニウム中に拡散していることを示唆している。又、ルテニウムの成膜時間を増大させると、金属ルテニウムの起因のルテニウムが検出される二酸化ハフニウム中の深さは増大している。ルテニウムの成膜温度を100℃、200℃、300℃と上昇させていくと、金属ルテニウム起因のルテニウムの原子パーセントが10%となる時間は、110秒、110秒、140秒と増大している。温度の上昇は拡散速度を増加させるため、この結果も、ルテニウムが二酸化ハフニウム中に拡散していると考えられる。よって、図4で示したリーク電流密度のばらつきを抑制するためには、ルテニウムが二酸化ハフニウム中に拡散するのを抑制する必要があると考えた。そこで、ルテニウムの拡散を抑制する方法として、ルテニウムと二酸化ハフニウムの界面に対して、キャップ層絶縁膜の挿入を検討した。

<キャップ層絶縁膜として酸化タンタルが好ましい理由>

キャップ層絶縁膜の挿入により懸念されることとしては、酸化膜換算膜厚の増大、二酸化ハフニウムのバリアハイトの低下である。キャップ層絶縁膜を挿入するということは絶縁膜の膜厚増大につながるため、酸化膜換算膜厚が増大する。ルテニウムの二酸化ハフニウム中への拡散防止目的の場合、当材料同士が接触しないように、均一に成膜できる最小の膜厚だけのキャップ層絶縁膜を挿入すれば良い。

キャップ層絶縁膜の挿入により懸念されることとしては、酸化膜換算膜厚の増大、二酸化ハフニウムのバリアハイトの低下である。キャップ層絶縁膜を挿入するということは絶縁膜の膜厚増大につながるため、酸化膜換算膜厚が増大する。ルテニウムの二酸化ハフニウム中への拡散防止目的の場合、当材料同士が接触しないように、均一に成膜できる最小の膜厚だけのキャップ層絶縁膜を挿入すれば良い。

この時、その膜厚はおよそ2nmである。2nm以下では、いずれの成膜方法を用いても島状に成長し、均一な膜とならず、キャップ層の効果は無いと考えられる。同じ物理膜厚2nmだけ成膜するとしても、誘電率が大きな材料を用いた方が、酸化膜換算膜厚の増大は抑制できる。よって、キャップ層絶縁膜には、ルテニウムの二酸化ハフニウム中への拡散を抑制することに加え、キャパシタの酸化膜換算膜厚の増大を最小限とするために、誘電率の比較的大きな材料が好ましいと考えられる。又、本構造のキャパシタにおいて、2nmのキャップ層絶縁膜を挿入した場合であっても、Fowler-Nordheimトンネル電流や、直接トンネル電流に寄与する絶縁膜は、膜厚の厚い二酸化ハフニウムである。よって、これらリーク電流の抑制には、二酸化ハフニウムと電極間のバリア高さが重要となる。キャップ層絶縁膜を挿入した場合、キャップ層絶縁膜の材料に依存して二酸化ハフニウムのバリア高さが影響を受ける可能性があるが、キャップ層絶縁膜挿入により、二酸化ハフニウムのバリア高さがより高く保てるキャップ層絶縁膜材料が望ましい。よって、これらの観点からキャップ層絶縁膜の検討結果を示し、最適なキャップ層絶縁膜を例示す。

《キャップ層絶縁膜としての、五酸化タンタルとアルミナとの比較検討》

キャップ層絶縁膜として、候補と目される五酸化タンタルとアルミナとを比較検討した。両者はリーク電流のばらつきを抑制する効果は同等であるが、キャップ層絶縁膜がキャパシタ用絶縁膜の、二酸化ハフニウムのバリアの高さをより大きく取ることを可能にする。このことから、五酸化タンタルが最適の材用である。同様の観点で、酸化ニオブも好適である。こうしたバンド構造の問題は後に詳述する。

キャップ層絶縁膜として、候補と目される五酸化タンタルとアルミナとを比較検討した。両者はリーク電流のばらつきを抑制する効果は同等であるが、キャップ層絶縁膜がキャパシタ用絶縁膜の、二酸化ハフニウムのバリアの高さをより大きく取ることを可能にする。このことから、五酸化タンタルが最適の材用である。同様の観点で、酸化ニオブも好適である。こうしたバンド構造の問題は後に詳述する。

キャップ層絶縁膜の材料の候補として挙げるのは、五酸化タンタルとアルミナである。共に半導体プロセスとして広く検討され、用いられている材料である。これらの材料は、更に、高アスペクトのキャパシタにも成膜できる技術が確立しているため、DRAMキャパシタに適用可能な材料である。

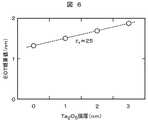

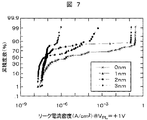

キャップ層絶縁膜に五酸化タンタルを用いたキャパシタの、酸化膜換算膜厚の概算値のキャップ層絶縁膜膜厚依存性を図6に示す。およそ、キャップ層絶縁膜の膜厚の増大に伴い、酸化膜換算膜厚が増大している。傾きより求めた比誘電率は約26である。次に、リーク電流密度の、キャップ層絶縁膜膜厚依存性を図7に示す。キャップ層絶縁膜膜厚を増大していくと、リーク電流密度ばらつきが劇的に減少していることが分かる。五酸化タンタルの膜厚が2nmでは、リーク電流密度のばらつきは約4桁、3nmの場合には約2桁である。つまり、五酸化タンタルキャップ層絶縁膜の挿入は、リーク電流密度のばらつき抑制には非常に効果的であることが判明した。

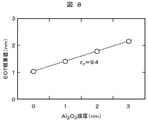

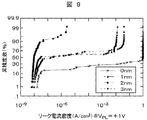

次にキャップ層絶縁膜にアルミナを用いた場合の、酸化膜換算膜厚概算値の、キャップ層絶縁膜膜厚依存性を図8に示す。酸化膜換算膜厚は、アルミナの膜厚を増大すると増大する傾向にある。傾きより、比誘電率を導出すると約9.4であった。五酸化タンタルをキャップ層絶縁膜に用いた場合と比較すると、比誘電率の差に起因して、挿入したキャップ層絶縁膜の物理膜厚に対する酸化膜換算膜厚の増加率が大きいことが分かる。アルミナをキャップ層絶縁膜に用いた場合、比誘電率の低さに起因した、酸化膜換算膜厚の増大が、実際に観察された。次に、リーク電流密度の、キャップ層絶縁膜膜厚依存性を図9に示す。アルミナ膜厚3nmの試料を除くと、キャップ層絶縁膜の膜厚を増大させると、リーク電流ばらつきが減少する傾向が確認された。キャップ層絶縁膜としてアルミナを挿入しない場合、8桁であったリーク電流密度のばらつきは、アルミナを2nm挿入することで3桁まで減少できた。つまり、五酸化タンタルを挿入した場合と同様に、アルミナをキャップ層絶縁膜に用いてもリーク電流密度のばらつきは同様に低減することが可能である。

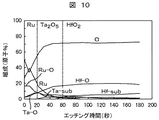

そこで、実際にキャップ層絶縁膜の挿入により、ルテニウムの二酸化ハフニウム中への拡散が抑制されていることを確認するために、キャップ層絶縁膜に五酸化タンタルを2nm挿入した試料を用いて、図5で示した、X線光電子分光法とアルゴンイオンエッチングを組み合わせた実験を行い、含有元素の深さプロファイルを取得した。その結果を図10に示す。アルゴンイオンエッチング時間が20秒までが電極ルテニウム、60秒までがキャップ層絶縁膜五酸化タンタル、60秒以降が二酸化ハフニウムをエッチングしていると考えられる。図10より、五酸化タンタルキャップ層絶縁膜2nmの挿入により、ルテニウムの二酸化ハフニウム中への拡散が劇的に減少していることが分かる。五酸化タンタルと二酸化ハフニウムの界面では、金属ルテニウム起因のルテニウムの原子パーセントは10%以下となっている。つまり、五酸化タンタルをキャップ層絶縁膜に用いると、ルテニウムの二酸化ハフニウム中への拡散が抑制され、リーク電流密度のばらつきが抑制されたと考えられる。

以上の結果より、五酸化タンタルをルテニウム上部電極と二酸化ハフニウム絶縁膜の間に挿入するキャップ層絶縁膜として用いると、ルテニウムの二酸化ハフニウム中への拡散が抑制されることが明らかとなった。

五酸化タンタルの比誘電率(26)は二酸化ハフニウムの比誘電率(20)よりも大きいことを考慮すると、絶縁膜を全て五酸化タンタルに置き換える方法も考えられるが、同方法は有効ではない。それは、五酸化タンタルはルテニウムとは急峻な界面を形成するが、窒化チタンと接触させると互いに反応し、急峻な界面が得られないからである。つまり、窒化チタンとの界面には二酸化ハフニウムが接していることが望ましい。下部電極をルテニウムとすれば、絶縁膜を五酸化タンタル単層とすることができるが、ルテニウムを下部電極に用いるためには、上部電極に用いるよりも高い技術が必要である。よって、技術的課題の少ない上部電極にルテニウムを適用する世代では、下部電極には広く用いられている窒化チタンを用いる必要がある。

このような観点から、キャップ層絶縁膜材料として考えられる他の材料は、酸化ニオブが挙げられる。当材料の比誘電率は30程度であり、同様のキャップ層の効果があると考えられる。

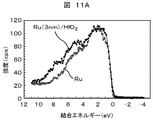

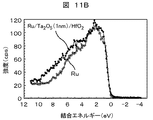

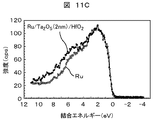

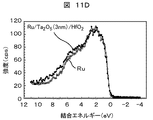

次に、ルテニウムが二酸化ハフニウム中に拡散することにより、リーク電流密度のばらつきを生じるメカニズムを説明する。五酸化タンタルを0nmから3nmまで1nmおきに増大させていった4つの試料をX線光電子分光法により分析し、得られた価電子帯波形を結果を図11Aより図11Dに示す。各々の図には、ルテニウムを50nm成膜した試料の分析から得られた、ルテニウムのみから得られた価電子帯波形を重ねて示す。価電子帯波形において、結合エネルギー0eVはフェルミエネルギーに対応し、結合エネルギーが増大すると、フェルミエネルギーよりも深いエネルギー準位を示す。また、価電子帯波形の強度は、その準位における電子の状態密度を示す。ルテニウムのみからの価電子帯波形と、二酸化ハフニウムとルテニウムを積層したときの波形の差分は、二酸化ハフニウムの状態密度を示す。図11(a)はキャップ層絶縁膜を挿入していない試料の結果であるが、結合エネルギーは約2.5eVから差分が生じている。この差分が生じ始めているエネルギーは価電子帯の上端に対応し、ルテニウムのフェルミエネルギーと二酸化ハフニウムの価電子帯オフセットが2.5eVであることを示す。このように考えると、どの試料においても、価電子帯上端のエネルギーよりも低いエネルギーではルテニウムのみに起因した波形と二酸化ハフニウムおよびキャップ層絶縁膜の五酸化タンタルを積層した試料の波形は重ならなくてはいけない。それは、このエネルギーは絶縁膜の禁性帯に対応するため、絶縁膜の状態密度は存在しないからである。しかし、図11A−図11Dを見ると、キャップ層絶縁膜が無い試料(図11A)および1nmの試料(図11B)については、結合エネルギー1eV−2eVの間に、同スペクトルの差分が発生している。一方、五酸化タンタルキャップ層絶縁膜を2nm以上挿入すると、同差分は消滅している。つまり、ルテニウムが二酸化ハフニウムに拡散していることが確認されている、キャップ層絶縁膜無しの試料では、二酸化ハフニウムの禁性帯中に何らかの状態密度が発生しており、一方、同拡散の抑制が確認されているキャップ層絶縁膜五酸化タンタルの膜厚が2nm以上の試料に関しては、同二酸化ハフニウムの禁性帯中の準位は消えていることが分かった。この結果は次のように考えることができる。

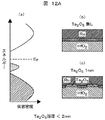

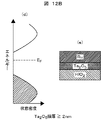

図12A及び図12Bには状態密度およびキャパシタの模式図を示した。キャップ層絶縁膜の五酸化タンタルの膜厚が1nm以下の場合、つまり五酸化タンタルが無い図12Aの(b)又は、1nmの膜のように均一な膜となっておらずルテニウムと二酸化ハフニウムが接している部分が存在する場合(図12Aの(c))は、ルテニウムが二酸化ハフニウム中に拡散し、二酸化ハフニウムの禁性帯中に状態密度を作ったと考えられる(図12Aの(a))。一方、キャップ層絶縁膜の五酸化タンタルの膜厚が2nm以上の場合(図12Bの(e))、つまり、均一な膜であるキャップ層絶縁膜の五酸化タンタルによりルテニウムと二酸化ハフニウムが完全に隔てられている場合、ルテニウムの二酸化ハフニウム中への拡散は抑制され、二酸化ハフニウムの禁性帯中には状態密度の発生は無いと考えられる(図12Bの(a))。

《キャップ層絶縁膜の二酸化ハフニウムのバリア高さに与える影響》

次に、キャップ層絶縁膜の挿入による、二酸化ハフニウムのバリア高さに与える影響を説明する。同評価のために、キャップ層絶縁膜に五酸化タンタル、またはアルミナを3nm挿入した場合のバンド構造を、物理分析により導出した。

次に、キャップ層絶縁膜の挿入による、二酸化ハフニウムのバリア高さに与える影響を説明する。同評価のために、キャップ層絶縁膜に五酸化タンタル、またはアルミナを3nm挿入した場合のバンド構造を、物理分析により導出した。

図13では、二酸化ハフニウムに起因したO1sピークの波形を示す。O1sのメインピークのエネルギーと、高エネルギー側に現れるロスピークの立ち上がりのエネルギーの差が、二酸化ハフニウムの禁性帯幅に一致することが知られている。同方法により求めた、二酸化ハフニウムの禁性帯幅は4.4eVであった。この値は、一般的に報告されている値よりも小さいが、これは、成膜方法等が最適化されていないためと考えられる。最適化を行なうと、二酸化ハフニウムの禁性帯幅は6.0eVとなる。

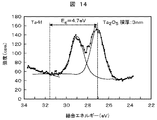

次に図14では五酸化タンタルに起因したTa4fピークの波形を示す。Ta4fのピークエネルギーとロスピークの立ち上がりのエネルギー差より、五酸化タンタルの禁性帯幅を導出すると、4.7eVであった。

次に図14では五酸化タンタルに起因したTa4fピークの波形を示す。Ta4fのピークエネルギーとロスピークの立ち上がりのエネルギー差より、五酸化タンタルの禁性帯幅を導出すると、4.7eVであった。

次に、図11に示したキャップ層絶縁膜に五酸化タンタルを挿入した試料およびアルミナを挿入した試料より得られた価電子帯波形から求めた、絶縁膜の価電子帯上端のエネルギーをまとめたのが図15である。五酸化タンタルおよびアルミナの膜厚を増大していくと、価電子帯オフセットの値は徐々に増大していく。これは、十分膜厚の厚い、ルテニウムと二酸化ハフニウムを積層したときの価電子帯オフセットが、ルテニウムと五酸化タンタルまたはアルミナを積層した時の価電子帯オフセットの値が変化している様子が見えていると考えられる。キャップ層絶縁膜の膜厚を3nm程度にすると、キャップ層絶縁膜材料のバルクの値に近いバンド構造が出来ると考えられる。また、特にアルミナを挿入すると価電子帯オフセットの増加量は大きい。これは、アルミナの禁性帯幅が6.6eVと比較的大きいため、アルミナの価電子帯オフセットも五酸化タンタルに比べて大きいためと考えられる。

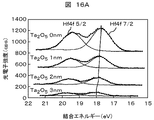

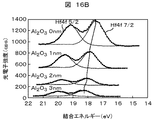

次に、キャップ層絶縁膜として五酸化タンタルとアルミナを、0nmから3nm挿入したときのHf4fピークの波形を、各々図16Aより図16Bに示す。これらの結果より分かるのは、いずれのキャップ層絶縁膜であっても、膜厚を増大していくと、Hf4fのピークエネルギーは高エネルギー側にシフトしていく点である。このピークエネルギーのシフト量をまとめたのが図17である。五酸化タンタルを挿入した場合もアルミナを挿入した場合も、キャップ層絶縁膜の物理膜厚増加に対してほぼ線形にHf4fのピークシフトが発生している。五酸化タンタルをキャップ層に3nm挿入した場合、約0.3eVの、アルミナをキャップ層絶縁膜に3nm挿入した場合、約0.6eVのシフトが観察された。このエネルギーシフトが意味するのは、ルテニウムに近い側の二酸化ハフニウムのバンドが、フェルミエネルギーに対してエネルギーシフトの分だけ下がっていることを示す。よって、キャップ層絶縁膜に五酸化タンタルを3nm挿入すると、アルミナを3nm挿入した場合に比べて、ルテニウム側の二酸化ハフニウムのバリア高さは0.3eV大きく取ることができることが判明した。

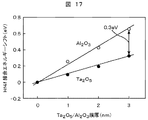

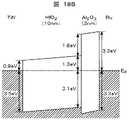

ルテニウムの仕事関数を4.8eV、窒化チタンの仕事関数を4.2eVと仮定すると、キャップ層絶縁膜として五酸化タンタルおよびアルミナを3nm挿入した場合のバンド構造は、各々図18A及び図18Bのように示すことができる。先に述べたように、二酸化ハフニウムのバリア高さはリーク電流への寄与が大きい。同バリア高さが大きいほど、リーク電流を低減することが可能である。このような観点からキャップ層絶縁膜を考えると、キャップ層絶縁膜にアルミナを用いた場合よりも五酸化タンタルを用いるほうが、二酸化ハフニウムのバリア高さを高くすることが可能であり、リーク電流低減に効果的であると考えられる。

図19には、キャップ層絶縁膜膜厚と、得られる酸化膜換算膜厚の関係を示した。横軸が比誘電率25を仮定した五酸化タンタルキャップ層絶縁膜の物理膜厚、縦軸が図中に記載の絶縁膜の物理膜厚を、五酸化タンタル絶縁膜の物理膜厚と併せて、直接トンネルリーク電流を抑制に最低限必要な6nmとしたときの酸化膜換算膜厚を示している。また、図中の黒点は、キャップ層絶縁膜および絶縁膜の膜厚を、最低それぞれ均一な膜となる2nm以上としたときの、実現可能な酸化膜換算膜厚を示している。絶縁膜に比誘電率20の二酸化ハフニウムを用いた場合、酸化膜換算膜厚は1.2nm以下で作成可能である。特に、キャップ層絶縁膜に五酸化タンタル2nmを適用しても、酸化膜換算膜厚1.2nm以下で、直接トンネルリーク電流を抑制したキャパシタの作成が可能であることが分かった。また、絶縁膜に比誘電率25の酸化ジルコニウムを用いた場合、同様に1.0nm以下の酸化膜換算膜厚のキャパシタを作成可能であり、キャップ層に五酸化タンタルを用いても、薄膜化限界はほぼ同等である。つまり、五酸化タンタルは二酸化ハフニウムや二酸化ジルコニウムよりも誘電率が高いため、キャップ層の挿入により、薄膜化限界が増大するようなことは無い。つまり、キャパシタ絶縁膜よりも誘電率の大きな材料からなるキャップ層の適用は、両者の物理膜厚の和が同じになるようにして積層しても、酸化膜換算膜厚の増大、もしくは容量の損失無くキャパシタ形成することができるため、非常に有効であることがわかった。

以上の結果より、キャップ層絶縁膜の材料は、従来材料のアルミナに比べ、五酸化タンタルが望ましいことが判明した。キャップ層絶縁膜の膜厚は拡散防止であるため、連続膜となっていなくてはならない。即ち、キャップ層絶縁膜は、連続膜となる最低の膜厚となして十分である。現実的には2nm以上である。また、絶縁膜の膜厚も同様に、連続膜となるためには2nm以上必要である。

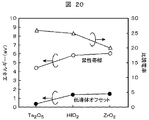

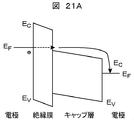

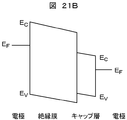

図20には、絶縁膜およびキャップ層絶縁膜の候補として挙げた材料の内一部の、禁性帯幅、伝導体オフセット量、および比誘電率の値を示した。一般的に、絶縁膜の絶縁性を示す指標をして用いられるのが、その絶縁膜材料の禁性帯幅である。五酸化タンタルの禁性帯幅は、二酸化ハフニウムや二酸化ジルコニウムに比べて小さい。しかし、キャパシタを作り、キャリアが電子と考えられる場合、各々のキャリアの絶縁膜中の伝導メカニズム(Fowler-Nordheimトンネル電流等)に関連しているのは、伝導帯オフセットである。これらの値はキャリアに対してバリアとして働くため、値が大きいほど、絶縁性能が高いと考えられる。図20より、キャップ層絶縁膜に用いる五酸化タンタルは、絶縁膜材料である二酸化ハフニウムや二酸化ジルコニウムに比べて伝導体オフセット量が小さいことがわかる。以上の事実および推測より、五酸化タンタルキャップ層絶縁膜と絶縁膜を積層したときFowler-Nordheimトンネル電流抑制に効果があるのは、絶縁膜である二酸化ハフニウム、または二酸化ジルコニウムである。ここで、電極および絶縁膜と、絶縁膜よりも伝導体オフセットの小さなキャップ層絶縁膜を積層したキャパシタの、キャップ層絶縁膜と接触している側の電極に正の電圧を印加した時のバンド構造を示したのが、図21A及び図21Bである。図21Aのように、もし、二酸化ハフニウムや二酸化ジルコニウム等の伝導体オフセット量の大きな絶縁膜材料の膜厚が薄いと、電極に電圧を印加した場合、電極中の電子が絶縁膜をトンネル効果により通り抜け、図21に示したように、伝導体オフセット量の小さなキャップ層絶縁膜の伝導体中を移動し、もう一方の電極に到達し、リーク電流を増大させる恐れがある。一方、図21Bのように伝導体オフセット量の大きな絶縁膜の物理膜厚が厚いと、電極より絶縁膜を通してキャップ層絶縁膜中に対して流れるF-Nトンネルリーク電流が抑制され、キャパシタのリーク電流も抑制されると考えられる。つまり、キャパシタ絶縁膜として異なる絶縁膜材料を積層する場合、価電子帯オフセット量の大きい絶縁膜の膜厚は、直接トンネルリーク電流が顕著な膜厚である6nm以下の範囲においては、厚くすべきである。先に、キャップ層絶縁膜の膜厚範囲は先に2nm以上3nm以下が望ましいと述べた。キャップ層絶縁膜材料の伝導体オフセット量が、絶縁膜材料の伝導体オフセット量よりも小さい場合は、キャップ層絶縁膜の膜厚は、絶縁膜の膜厚よりも薄くすると、リーク電流が抑制できるため、望ましい。

尚、ここで、非特許文献1に示されたRu/Ta2O5/HfO2/TiNの構造との比較に言及しておく。両者に積層形態に類似性はあるものの、明瞭に発明思想自体は相違する。非特許文献1ではキャパシタ絶縁物の誘電率を増大させるため、より誘電率の高いTa2O5を用い、Ta2O5の厚みを確保することを意図しています。即ち、非特許文献1はTa2O5/HfO2の二層誘電体(Ta2O5/HfO2 double dielectric)を意図しています。一方、本願発明は、TiN/HfO2/TiN構造の上部電極TiNをRuに変換することで、リーク電流の低減を図りました。この際、HfO2とRuとの界面の不安定さを見出し、その要因を分析し、そして、HfO2とRuの界面での元素拡散を阻止することを意図したものです。この結果、その他のファクタ、例えば、バンド構造における、伝導体のオフセット量の観点等よりTa2O5を選択したものであります。従って、上述したように、連続膜となる最低の膜厚にても十分なのであります。尚、例えば、原子層成長法で形成した膜は、おおよそ2nm相当以上のサイクル数で成膜を行った場合、連続膜となる。

以上、実施例1を詳細に説明したが、実施例1の概要を要約すれば以下の通りである。

即ち、上部電極ルテニウムを二酸化ハフニウム上に直接積層すると、ルテニウムが二酸化ハフニウム中へ拡散することが判明した。ルテニウムの二酸化ハフニウム中への拡散を抑制するために、界面に各々の材料と元素プロファイルが深さ方向に急峻な界面を形成する五酸化タンタルを挿入する。五酸化タンタルは従来のキャップ層絶縁膜材料であるアルミナに比べ誘電率が大きく、挿入による酸化膜換算膜厚の増大を抑制できる。また、キャップ層絶縁膜五酸化タンタルによる二酸化ハフニウムの伝導体オフセットの低下は、アルミナをキャップ層絶縁膜に用いた場合に比べて抑制が可能であり、リーク電流抑制の観点からも有利である。

即ち、上部電極ルテニウムを二酸化ハフニウム上に直接積層すると、ルテニウムが二酸化ハフニウム中へ拡散することが判明した。ルテニウムの二酸化ハフニウム中への拡散を抑制するために、界面に各々の材料と元素プロファイルが深さ方向に急峻な界面を形成する五酸化タンタルを挿入する。五酸化タンタルは従来のキャップ層絶縁膜材料であるアルミナに比べ誘電率が大きく、挿入による酸化膜換算膜厚の増大を抑制できる。また、キャップ層絶縁膜五酸化タンタルによる二酸化ハフニウムの伝導体オフセットの低下は、アルミナをキャップ層絶縁膜に用いた場合に比べて抑制が可能であり、リーク電流抑制の観点からも有利である。

更に、本願発明においては、第1の電極は、ルテニウム以外に酸化ルテニウム、キャパシタ用絶縁膜は、酸化ハフニウム以外に、イットリウムを添加した酸化ハフニウム、及び酸化ジルコニウム、第2の電極は、窒化チタン、チタン、窒化タンタル、タンタル、窒化タングステン、タングステン、リンをドーピングしたポリシリコン、金、銀、銅、及びプラチナなどを用いても同等の効果を得ることが出来る。尚、前記酸化ハフニウムへのイットリウムの添加は、好もしいイットリウム添加量が概ね10at%より20at%の範囲である。同材料は誘電率の観点で好ましい。

<製造方法の例示>

図42は、実施例1のDRAMの等価回路図である。等価回路自体は通例のものであるので詳細説明は省略するが、その概要は次の通りである。DRAMアレーは、基本的に、マトリクス状に配置された複数のワード線WL(WL0、WL1,・・・)と複数のビット線BL(BL0、BL1、・・・)およびこれらの交点に配置された複数のメモリセル(MC)により構成されている。1個のメモリセルは、1個のキャパシタCとこれに直列に接続された1個のメモリセル選択用のFETとで構成されている。メモリセル選択用のFETのソース及びドレインの一方は、キャパシタCと電気的に接続され、他方はビット線BLと電気的に接続されている。ワード線WLの一端は、ワードドライバ(図示されていない)に接続され、ビット線BLの一端は、センスアンプSAに接続されている。尚、I/Oは共通データ出力線、Coはデータ線寄生容量、S1は列選択スイッチ、S2はプリチャージスイッチである。

図42は、実施例1のDRAMの等価回路図である。等価回路自体は通例のものであるので詳細説明は省略するが、その概要は次の通りである。DRAMアレーは、基本的に、マトリクス状に配置された複数のワード線WL(WL0、WL1,・・・)と複数のビット線BL(BL0、BL1、・・・)およびこれらの交点に配置された複数のメモリセル(MC)により構成されている。1個のメモリセルは、1個のキャパシタCとこれに直列に接続された1個のメモリセル選択用のFETとで構成されている。メモリセル選択用のFETのソース及びドレインの一方は、キャパシタCと電気的に接続され、他方はビット線BLと電気的に接続されている。ワード線WLの一端は、ワードドライバ(図示されていない)に接続され、ビット線BLの一端は、センスアンプSAに接続されている。尚、I/Oは共通データ出力線、Coはデータ線寄生容量、S1は列選択スイッチ、S2はプリチャージスイッチである。

本発明によるキャパシタを有するDRAMメモリキャパシタの製造方法を説明する。尚、本例では、情報蓄積用キャパシタは、絶縁膜の孔内の内面を、前記第2の電極、及び前記第2の電極上に成膜されたキャパシタ用絶縁膜、及び前記キャパシタ用絶縁膜上に成膜されたキャップ層絶縁膜、及び前記キャップ層絶縁膜上に成膜された第1の電極が形成された例である。

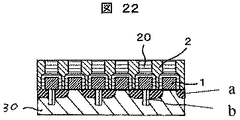

通例の方法で形成されたメモリセル選択トランジスタの上にビット線1を形成し、又、選択トランジスタとキャパシタとの電気的接続を行うポリシリコンプラグ2を形成する。図22が、このメモリの主要部の断面図である。図22中、符号aはトランジスタの拡散層を示す。拡散層aはシリコン基板30に通例の方法によりドーパントをインプラントして形成し、n型もしくはp型とする。また、図中、符号bに示すのはアイソレーションであり,隣接するトランジスタ同士の電気的分離を行なうものである。図中、符号20は絶縁膜を示す。尚、本例での図面は、メモリ部のトタンジスタに接続されるメモリ容量部の構造に関する発明であるので、この部分のみ図示し、半導体基板上に形成される半導体素子部については、以下の図面では、図示及び詳細説明は省略する。

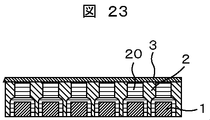

この上に、図23に示すように膜厚100nm程度の窒化シリコン膜3を化学気相成長法によって堆積する。このシリコン窒化膜は、以下の加工の際のエッチングストッパとして機能する。次に、図24に示すように、窒化シリコン膜3の上部にテトラエトキシシランを原料とする酸化シリコン膜4を形成した。この酸化シリコン膜4を、柱状酸化シリコン膜22に加工する。この状態の断面図が図25である。前記の加工は、フォトレジスト膜、ポリシリコン、タングステン、またはカーボン等、酸化シリコン膜とのエッチングの選択比が大きい材料をマスクとしてドライエッチング法を用いる。更に、窒化シリコン膜3のドライエッチングを続けて行い、図26に示すようにポリシリコンプラグ2の上部に下部電極用の溝21を形成した。更に、図27に示すように、下部電極材料として窒化チタン膜5を化学気相成長法または原子層成長法により35nm堆積する。下部電極材料はチタン、窒化タンタル、タンタル、窒化タングステン、タングステン、リンをドーピングしたポリシリコン、金、銀、銅、白金、など、酸化ハフニウム等の絶縁膜と積層した場合に急峻な界面を形成する材料であれば適用可能である。次に、図28に示すようなフォトレジスト膜を用いた通例のエッチバック技術によって、この窒化チタン膜5を各ビット毎5−1、5−2に分離する。尚、装置間搬送の際に、窒化チタン5表面に酸化チタンが2nm程度形成する。この酸化チタンは、例えばフッ化水素酸などを用いてウエットエッチングして除去する。続けて、図29に示すように絶縁膜として化学気相成長法または原子層成長法により酸化ハフニウム6を成膜する。その際、原子層成長法で成膜する場合の原料は、TEMAH(テトラ・エチル・メチル・アミド・ハフニウム)とオゾンを用いる。同絶縁膜は、酸化ジルコニウムでも良い。この酸化ハフニウム膜は、キャパシタの絶縁膜である。次に、図30に示すように、キャップ層絶縁膜として酸化タンタル7を化学気相成長法又は原子層成長法により2nm以上4nm以下成膜する。同キャップ層絶縁膜はニオブ酸化膜でも良い。次に、図31に示すように化学気相成長法または原子層成長法により上部電極向けのルテニウム8を原子層成長法により成膜する。上部電極材料は、酸化ルテニウムも適用可能である。

<実施例2>

実施例1で示した結果は、キャパシタの上下関係を入れ替えても成立すると考えられる。つまり、下部電極にルテニウム、絶縁膜に二酸化ハフニウム、同ルテニウムと同二酸化ハフニウムは積層するとルテニウムが二酸化ハフニウム中に拡散するため、同界面にキャップ層絶縁膜として五酸化タンタルを挿入する。最後に上部電極として窒化チタンを形成する。同構造のキャパシタにおいても、実施例1で示したルテニウムが二酸化ハフニウム中に拡散してリーク電流密度のばらつきが増大するという問題点が生じるため、その解決方法として同界面に五酸化タンタルキャップ層絶縁膜を挿入し、同反応を抑制可能である。

実施例1で示した結果は、キャパシタの上下関係を入れ替えても成立すると考えられる。つまり、下部電極にルテニウム、絶縁膜に二酸化ハフニウム、同ルテニウムと同二酸化ハフニウムは積層するとルテニウムが二酸化ハフニウム中に拡散するため、同界面にキャップ層絶縁膜として五酸化タンタルを挿入する。最後に上部電極として窒化チタンを形成する。同構造のキャパシタにおいても、実施例1で示したルテニウムが二酸化ハフニウム中に拡散してリーク電流密度のばらつきが増大するという問題点が生じるため、その解決方法として同界面に五酸化タンタルキャップ層絶縁膜を挿入し、同反応を抑制可能である。

本実施例に即したキャパシタを有するDRAMメモリキャパシタの製造方法を説明する。尚、本例においても、図面は、メモリ部のトタンジスタに接続されるメモリ容量部の構造に関する発明であるので、この部分のみ図示し、半導体基板上に形成される半導体素子部については、図示及び詳細説明は省略する。

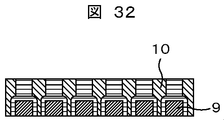

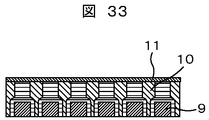

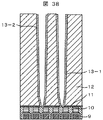

図32に示すように、通例の方法で形成されたメモリセル選択トランジスタの上にビット線9を形成し、また、選択トランジスタとキャパシタとの電気的接続を行なうポリシリコンプラグ10を形成する。この上に図33に示すように、膜厚100nm程度の窒化シリコン膜11を化学気相成長法によって堆積し、シリコン窒化膜を加工する際のエッチングストッパとする。次に、図34に示すように、窒化シリコン膜11の上部にテトラエトキシシランを原料とする酸化シリコン膜12を形成した。この酸化シリコン膜12を、図35に示すように柱状酸化シリコン22に加工する。この加工は、フォトレジスト膜、ポリシリコン、タングステン、またはカーボン等、酸化シリコン膜とのエッチングの選択比が大きい材料をマスクとしてドライエッチング法を用いた。更に、窒化シリコン膜11のドライエッチングを続けて行い、図36に示すようにポリシリコンプラグの上部に下部電極用の溝21を形成した。更に、図37に示すように、下部電極材料にルテニウム膜13を化学気相成長法又は原子層成長法により20nm堆積する。下部電極材料は特性が近い酸化ルテニウムも適用可能である。次に、図38に示すように、フォトレジスト膜を用いたエッチバック技術によって、このルテニウム膜13を各ビット毎13−1、13−2に分離する。尚、装置間搬送の際にルテニウム表面に酸化ルテニウムが1nm程度形成する。この酸化ルテニウムは、例えばフッ化水素酸などを用いてウエットエッチングして除去しても良い。続けて、図39に示すように、キャップ層絶縁膜14として酸化タンタルを化学気相成長法または原子層成長法により2nm以上5nm以下で成膜する。同キャップ層絶縁膜は、酸化ニオブでも良い。次に、図40に示すように絶縁膜として酸化ハフニウム15を化学気相成長法または原子層成長法により成膜する。原子層成長法により成膜する際の原料は、TEMAH(テトラ・エチル・メチル・アミド・ハフニウム)とオゾンを用いる。同絶縁膜は特性の近い酸化ジルコニウムでも良い。次に、図41に示すように上部電極向けの窒化チタン16を化学気相成長法又は原子層成長法により成膜する。上部電極材料は、チタン、窒化タンタル、タンタル、窒化タングステン、タングステン、リンをドーピングしたポリシリコン、金、銀、銅、白金など、絶縁膜と急峻な界面を形成する材料であれば適用可能である。

本構造においても、実施例1と同等の装置特性を示した。

1:ビット線、2:プラグ、3:窒化シリコン、4:酸化シリコン、5:下部電極(例えば、窒化チタン)、6:キャパシタ絶縁膜(例えば、酸化ハフニウム)、7:キャップ絶縁膜(例えば、酸化タンタル)、8:上部電極(例えば、ルテニウム)、9:ビット線、10:プラグ、11:窒化シリコン、12:酸化シリコン、13:下部電極(例えば、ルテニウム)、14:キャップ絶縁膜(例えば、酸化タンタル)、15:キャパシタ絶縁膜(例えば、酸化ハフニウム)、16:上部電極(例えば、窒化チタン)、20:絶縁膜、21:溝、22:柱状酸化シリコン膜:5−1、5−2:各ビット毎に分けられた窒化チタン膜、13−1、13−2:各ビット毎に分けられたルテニウム膜、30:シリコン基板、WL0、WL1:ワード線、BL0、BL2:ビット線、MC:メモリセル、C:キャパシタ、FET:電界効果型トランジスタ、C0:寄生容量、S1:列選択スイッチ、S2:プリチャージスイッチ。

Claims (8)

- 半導体基板上に形成された複数のワード線と、複数のビット線と、前記複数のワード線と前記複数のビット線の所定の交点に設けられたメモリ選択用トランジスタと該メモリセル選択用トランジスタに電気的に直列に接続され、前記半導体基板上に形成された情報蓄積用キャパシタとから構成されるメモリセルとを備えた半導体集積回路装置であって、

前記情報蓄積用キャパシタは、第2の電極、及び前記第2の電極上に成膜されたキャパシタ用絶縁膜、及び前記キャパシタ用絶縁膜上に成膜されたキャップ層絶縁膜、及び前記キャップ層絶縁膜上に成膜された第1の電極を有し、

前記第1の電極は、ルテニウム及び酸化ルテニウムから選ばれた少なくとも一者であり、

前記キャパシタ用絶縁膜は、酸化ハフニウム、イットリウムを添加した酸化ハフニウム、及び酸化ジルコニウムの群から選ばれた少なくとも一者であり、

前記キャップ層絶縁膜は、前記キャップ層絶縁膜は前記絶縁膜よりも誘電率の高い、酸化タンタル及び酸化ニオブから選ばれた少なくとも一者であり、

前記第2の電極は、窒化チタン、チタン、窒化タンタル、タンタル、窒化タングステン、タングステン、リンをドーピングしたポリシリコン、金、銀、銅、及びプラチナの群から選ばれた少なくとも一者であり、且つ

前記キャップ層絶縁膜が、連続膜を構成し且つ3nm以下の厚さであることを特徴とする半導体集積回路装置。 - 前記キャップ層絶縁膜の膜厚が、2nm以上3nm以下の厚さであることを特徴とする請求項1に記載の半導体集積回路装置。

- 前記キャップ層絶縁膜は、前記絶縁膜と前記上部電極の間に挿入することにより、アルミナをキャップ層絶縁膜として用いた場合に比べて、前記絶縁膜の伝導体オフセットの低下量が小さいことを特徴とする、請求項1に記載の半導体集積回路装置。

- 前記情報蓄積用キャパシタは、絶縁膜の孔内の内面を、前記第2の電極、及び前記第2の電極上に成膜されたキャパシタ用絶縁膜、及び前記キャパシタ用絶縁膜上に成膜されたキャップ層絶縁膜、及び前記キャップ層絶縁膜上に成膜された第1の電極が形成されてなることを特徴とする請求項1に記載の半導体集積回路装置。

- 半導体基板上に形成された複数のワード線と、複数のビット線と、前記複数のワード線と前記複数のビット線の所定の交点に設けられたメモリ選択用トランジスタと該メモリセル選択用トランジスタに電気的に直列に接続され、前記半導体基板上に形成された情報蓄積用キャパシタとから構成されるメモリセルとを備えた半導体集積回路装置であって、

前記情報蓄積用キャパシタは、第2の電極、及び前記第2の電極上に成膜されたキャップ層絶縁膜、及び前記キャップ層絶縁膜上に成膜されたキャパシタ用絶縁膜、及び前記キャップ層絶縁膜上に成膜された第1の電極を有し、

前記第1の電極は、ルテニウム及び酸化ルテニウムから選ばれた少なくとも一者であり、

前記キャパシタ用絶縁膜は、酸化ハフニウム、イットリウムを添加した酸化ハフニウム、及び酸化ジルコニウムの群から選ばれた少なくとも一者であり、

前記キャップ層絶縁膜は、前記キャップ層絶縁膜は前記キャパシタ用絶縁膜よりも誘電率の高い、酸化タンタル及び酸化ニオブから選ばれた少なくとも一者であり、

前記第2の電極は、窒化チタン、チタン、窒化タンタル、タンタル、窒化タングステン、タングステン、リンをドーピングしたポリシリコン、金、銀、銅、及びプラチナの群から選ばれた少なくとも一者であり、且つ

前記キャップ層絶縁膜が、連続膜を構成し且つ3nm以下の厚さであることを特徴とする半導体集積回路装置。 - 前記キャップ層絶縁膜の膜厚が、2nm以上3nm以下の厚さであることを特徴とする請求項5に記載の半導体集積回路装置。

- 前記キャップ層絶縁膜は、前記絶縁膜と前記上部電極の間に挿入することにより、アルミナをキャップ層絶縁膜として用いた場合に比べて、前記絶縁膜の伝導体オフセットの低下量が小さいことを特徴とする、請求項5に記載の半導体集積回路装置。

- 前記情報蓄積用キャパシタは、絶縁膜の孔内の内面を、前記第2の電極、及び前記第2の電極上に成膜されたキャップ層絶縁膜、及び前記キャップ層絶縁膜上に成膜されたキャパシタ用絶縁膜、及び前記キャパシタ用絶縁膜上に成膜された第1の電極が形成されてなることを特徴とする請求項5に記載の半導体集積回路装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006351721A JP2008166360A (ja) | 2006-12-27 | 2006-12-27 | 半導体集積回路装置 |

| KR1020070104883A KR20080061250A (ko) | 2006-12-27 | 2007-10-18 | 반도체 집적회로장치 |

| US11/940,667 US20080157157A1 (en) | 2006-12-27 | 2007-11-15 | Semiconductor integrated circuit device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006351721A JP2008166360A (ja) | 2006-12-27 | 2006-12-27 | 半導体集積回路装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2008166360A true JP2008166360A (ja) | 2008-07-17 |

Family

ID=39582586

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006351721A Pending JP2008166360A (ja) | 2006-12-27 | 2006-12-27 | 半導体集積回路装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20080157157A1 (ja) |

| JP (1) | JP2008166360A (ja) |

| KR (1) | KR20080061250A (ja) |

Families Citing this family (366)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10378106B2 (en) | 2008-11-14 | 2019-08-13 | Asm Ip Holding B.V. | Method of forming insulation film by modified PEALD |

| US9394608B2 (en) | 2009-04-06 | 2016-07-19 | Asm America, Inc. | Semiconductor processing reactor and components thereof |

| US8802201B2 (en) | 2009-08-14 | 2014-08-12 | Asm America, Inc. | Systems and methods for thin-film deposition of metal oxides using excited nitrogen-oxygen species |

| US9312155B2 (en) | 2011-06-06 | 2016-04-12 | Asm Japan K.K. | High-throughput semiconductor-processing apparatus equipped with multiple dual-chamber modules |

| US10364496B2 (en) | 2011-06-27 | 2019-07-30 | Asm Ip Holding B.V. | Dual section module having shared and unshared mass flow controllers |

| US10854498B2 (en) | 2011-07-15 | 2020-12-01 | Asm Ip Holding B.V. | Wafer-supporting device and method for producing same |

| US20130023129A1 (en) | 2011-07-20 | 2013-01-24 | Asm America, Inc. | Pressure transmitter for a semiconductor processing environment |

| US9017481B1 (en) | 2011-10-28 | 2015-04-28 | Asm America, Inc. | Process feed management for semiconductor substrate processing |

| US9659799B2 (en) | 2012-08-28 | 2017-05-23 | Asm Ip Holding B.V. | Systems and methods for dynamic semiconductor process scheduling |

| US9021985B2 (en) | 2012-09-12 | 2015-05-05 | Asm Ip Holdings B.V. | Process gas management for an inductively-coupled plasma deposition reactor |

| US10714315B2 (en) | 2012-10-12 | 2020-07-14 | Asm Ip Holdings B.V. | Semiconductor reaction chamber showerhead |

| KR20140048654A (ko) | 2012-10-16 | 2014-04-24 | 삼성전자주식회사 | 반도체 소자 |

| US8871621B2 (en) * | 2012-12-20 | 2014-10-28 | Intermolecular, Inc. | Method of forming an asymmetric MIMCAP or a schottky device as a selector element for a cross-bar memory array |

| US20160376700A1 (en) | 2013-02-01 | 2016-12-29 | Asm Ip Holding B.V. | System for treatment of deposition reactor |

| US9589770B2 (en) | 2013-03-08 | 2017-03-07 | Asm Ip Holding B.V. | Method and systems for in-situ formation of intermediate reactive species |

| US9484191B2 (en) | 2013-03-08 | 2016-11-01 | Asm Ip Holding B.V. | Pulsed remote plasma method and system |

| US9240412B2 (en) | 2013-09-27 | 2016-01-19 | Asm Ip Holding B.V. | Semiconductor structure and device and methods of forming same using selective epitaxial process |

| US10683571B2 (en) | 2014-02-25 | 2020-06-16 | Asm Ip Holding B.V. | Gas supply manifold and method of supplying gases to chamber using same |

| US10167557B2 (en) | 2014-03-18 | 2019-01-01 | Asm Ip Holding B.V. | Gas distribution system, reactor including the system, and methods of using the same |

| US11015245B2 (en) | 2014-03-19 | 2021-05-25 | Asm Ip Holding B.V. | Gas-phase reactor and system having exhaust plenum and components thereof |

| US10858737B2 (en) | 2014-07-28 | 2020-12-08 | Asm Ip Holding B.V. | Showerhead assembly and components thereof |

| US9890456B2 (en) | 2014-08-21 | 2018-02-13 | Asm Ip Holding B.V. | Method and system for in situ formation of gas-phase compounds |

| US10941490B2 (en) | 2014-10-07 | 2021-03-09 | Asm Ip Holding B.V. | Multiple temperature range susceptor, assembly, reactor and system including the susceptor, and methods of using the same |

| US9657845B2 (en) | 2014-10-07 | 2017-05-23 | Asm Ip Holding B.V. | Variable conductance gas distribution apparatus and method |

| KR102263121B1 (ko) | 2014-12-22 | 2021-06-09 | 에이에스엠 아이피 홀딩 비.브이. | 반도체 소자 및 그 제조 방법 |

| US10529542B2 (en) | 2015-03-11 | 2020-01-07 | Asm Ip Holdings B.V. | Cross-flow reactor and method |

| US10276355B2 (en) | 2015-03-12 | 2019-04-30 | Asm Ip Holding B.V. | Multi-zone reactor, system including the reactor, and method of using the same |

| US10458018B2 (en) | 2015-06-26 | 2019-10-29 | Asm Ip Holding B.V. | Structures including metal carbide material, devices including the structures, and methods of forming same |

| US10600673B2 (en) | 2015-07-07 | 2020-03-24 | Asm Ip Holding B.V. | Magnetic susceptor to baseplate seal |

| US10083836B2 (en) | 2015-07-24 | 2018-09-25 | Asm Ip Holding B.V. | Formation of boron-doped titanium metal films with high work function |

| US9960072B2 (en) | 2015-09-29 | 2018-05-01 | Asm Ip Holding B.V. | Variable adjustment for precise matching of multiple chamber cavity housings |

| US10211308B2 (en) | 2015-10-21 | 2019-02-19 | Asm Ip Holding B.V. | NbMC layers |

| US10322384B2 (en) | 2015-11-09 | 2019-06-18 | Asm Ip Holding B.V. | Counter flow mixer for process chamber |

| KR102406971B1 (ko) | 2015-12-24 | 2022-06-10 | 삼성전자주식회사 | 커패시터를 포함하는 반도체 장치 및 이의 제조 방법 |

| US11139308B2 (en) | 2015-12-29 | 2021-10-05 | Asm Ip Holding B.V. | Atomic layer deposition of III-V compounds to form V-NAND devices |

| US10529554B2 (en) | 2016-02-19 | 2020-01-07 | Asm Ip Holding B.V. | Method for forming silicon nitride film selectively on sidewalls or flat surfaces of trenches |

| US10468251B2 (en) | 2016-02-19 | 2019-11-05 | Asm Ip Holding B.V. | Method for forming spacers using silicon nitride film for spacer-defined multiple patterning |

| US10501866B2 (en) | 2016-03-09 | 2019-12-10 | Asm Ip Holding B.V. | Gas distribution apparatus for improved film uniformity in an epitaxial system |

| US10343920B2 (en) | 2016-03-18 | 2019-07-09 | Asm Ip Holding B.V. | Aligned carbon nanotubes |

| US9892913B2 (en) | 2016-03-24 | 2018-02-13 | Asm Ip Holding B.V. | Radial and thickness control via biased multi-port injection settings |

| US10190213B2 (en) | 2016-04-21 | 2019-01-29 | Asm Ip Holding B.V. | Deposition of metal borides |

| US10865475B2 (en) | 2016-04-21 | 2020-12-15 | Asm Ip Holding B.V. | Deposition of metal borides and silicides |

| US10367080B2 (en) | 2016-05-02 | 2019-07-30 | Asm Ip Holding B.V. | Method of forming a germanium oxynitride film |

| US10032628B2 (en) | 2016-05-02 | 2018-07-24 | Asm Ip Holding B.V. | Source/drain performance through conformal solid state doping |

| KR102592471B1 (ko) | 2016-05-17 | 2023-10-20 | 에이에스엠 아이피 홀딩 비.브이. | 금속 배선 형성 방법 및 이를 이용한 반도체 장치의 제조 방법 |

| US11453943B2 (en) | 2016-05-25 | 2022-09-27 | Asm Ip Holding B.V. | Method for forming carbon-containing silicon/metal oxide or nitride film by ALD using silicon precursor and hydrocarbon precursor |

| US10388509B2 (en) | 2016-06-28 | 2019-08-20 | Asm Ip Holding B.V. | Formation of epitaxial layers via dislocation filtering |

| US10612137B2 (en) | 2016-07-08 | 2020-04-07 | Asm Ip Holdings B.V. | Organic reactants for atomic layer deposition |

| US9859151B1 (en) * | 2016-07-08 | 2018-01-02 | Asm Ip Holding B.V. | Selective film deposition method to form air gaps |

| US10714385B2 (en) | 2016-07-19 | 2020-07-14 | Asm Ip Holding B.V. | Selective deposition of tungsten |

| US10381226B2 (en) | 2016-07-27 | 2019-08-13 | Asm Ip Holding B.V. | Method of processing substrate |

| KR102532607B1 (ko) | 2016-07-28 | 2023-05-15 | 에이에스엠 아이피 홀딩 비.브이. | 기판 가공 장치 및 그 동작 방법 |

| US10395919B2 (en) | 2016-07-28 | 2019-08-27 | Asm Ip Holding B.V. | Method and apparatus for filling a gap |

| US9887082B1 (en) | 2016-07-28 | 2018-02-06 | Asm Ip Holding B.V. | Method and apparatus for filling a gap |

| US9812320B1 (en) | 2016-07-28 | 2017-11-07 | Asm Ip Holding B.V. | Method and apparatus for filling a gap |

| US10410943B2 (en) | 2016-10-13 | 2019-09-10 | Asm Ip Holding B.V. | Method for passivating a surface of a semiconductor and related systems |

| US10643826B2 (en) | 2016-10-26 | 2020-05-05 | Asm Ip Holdings B.V. | Methods for thermally calibrating reaction chambers |

| US11532757B2 (en) | 2016-10-27 | 2022-12-20 | Asm Ip Holding B.V. | Deposition of charge trapping layers |

| US10714350B2 (en) | 2016-11-01 | 2020-07-14 | ASM IP Holdings, B.V. | Methods for forming a transition metal niobium nitride film on a substrate by atomic layer deposition and related semiconductor device structures |

| US10435790B2 (en) | 2016-11-01 | 2019-10-08 | Asm Ip Holding B.V. | Method of subatmospheric plasma-enhanced ALD using capacitively coupled electrodes with narrow gap |

| US10229833B2 (en) | 2016-11-01 | 2019-03-12 | Asm Ip Holding B.V. | Methods for forming a transition metal nitride film on a substrate by atomic layer deposition and related semiconductor device structures |

| US10643904B2 (en) | 2016-11-01 | 2020-05-05 | Asm Ip Holdings B.V. | Methods for forming a semiconductor device and related semiconductor device structures |

| US10134757B2 (en) | 2016-11-07 | 2018-11-20 | Asm Ip Holding B.V. | Method of processing a substrate and a device manufactured by using the method |

| KR102546317B1 (ko) | 2016-11-15 | 2023-06-21 | 에이에스엠 아이피 홀딩 비.브이. | 기체 공급 유닛 및 이를 포함하는 기판 처리 장치 |

| US10340135B2 (en) | 2016-11-28 | 2019-07-02 | Asm Ip Holding B.V. | Method of topologically restricted plasma-enhanced cyclic deposition of silicon or metal nitride |

| KR102762543B1 (ko) | 2016-12-14 | 2025-02-05 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| US11581186B2 (en) | 2016-12-15 | 2023-02-14 | Asm Ip Holding B.V. | Sequential infiltration synthesis apparatus |

| US11447861B2 (en) | 2016-12-15 | 2022-09-20 | Asm Ip Holding B.V. | Sequential infiltration synthesis apparatus and a method of forming a patterned structure |

| KR102700194B1 (ko) | 2016-12-19 | 2024-08-28 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| US10269558B2 (en) | 2016-12-22 | 2019-04-23 | Asm Ip Holding B.V. | Method of forming a structure on a substrate |

| US10867788B2 (en) | 2016-12-28 | 2020-12-15 | Asm Ip Holding B.V. | Method of forming a structure on a substrate |

| US11390950B2 (en) | 2017-01-10 | 2022-07-19 | Asm Ip Holding B.V. | Reactor system and method to reduce residue buildup during a film deposition process |

| US10655221B2 (en) | 2017-02-09 | 2020-05-19 | Asm Ip Holding B.V. | Method for depositing oxide film by thermal ALD and PEALD |

| US10468261B2 (en) | 2017-02-15 | 2019-11-05 | Asm Ip Holding B.V. | Methods for forming a metallic film on a substrate by cyclical deposition and related semiconductor device structures |

| US10283353B2 (en) | 2017-03-29 | 2019-05-07 | Asm Ip Holding B.V. | Method of reforming insulating film deposited on substrate with recess pattern |

| US10529563B2 (en) | 2017-03-29 | 2020-01-07 | Asm Ip Holdings B.V. | Method for forming doped metal oxide films on a substrate by cyclical deposition and related semiconductor device structures |

| KR102457289B1 (ko) | 2017-04-25 | 2022-10-21 | 에이에스엠 아이피 홀딩 비.브이. | 박막 증착 방법 및 반도체 장치의 제조 방법 |

| US10892156B2 (en) | 2017-05-08 | 2021-01-12 | Asm Ip Holding B.V. | Methods for forming a silicon nitride film on a substrate and related semiconductor device structures |

| US10446393B2 (en) | 2017-05-08 | 2019-10-15 | Asm Ip Holding B.V. | Methods for forming silicon-containing epitaxial layers and related semiconductor device structures |

| US10770286B2 (en) | 2017-05-08 | 2020-09-08 | Asm Ip Holdings B.V. | Methods for selectively forming a silicon nitride film on a substrate and related semiconductor device structures |

| US10504742B2 (en) | 2017-05-31 | 2019-12-10 | Asm Ip Holding B.V. | Method of atomic layer etching using hydrogen plasma |

| US10886123B2 (en) | 2017-06-02 | 2021-01-05 | Asm Ip Holding B.V. | Methods for forming low temperature semiconductor layers and related semiconductor device structures |

| US12040200B2 (en) | 2017-06-20 | 2024-07-16 | Asm Ip Holding B.V. | Semiconductor processing apparatus and methods for calibrating a semiconductor processing apparatus |

| US11306395B2 (en) | 2017-06-28 | 2022-04-19 | Asm Ip Holding B.V. | Methods for depositing a transition metal nitride film on a substrate by atomic layer deposition and related deposition apparatus |

| US10685834B2 (en) | 2017-07-05 | 2020-06-16 | Asm Ip Holdings B.V. | Methods for forming a silicon germanium tin layer and related semiconductor device structures |

| KR20190009245A (ko) | 2017-07-18 | 2019-01-28 | 에이에스엠 아이피 홀딩 비.브이. | 반도체 소자 구조물 형성 방법 및 관련된 반도체 소자 구조물 |

| US11018002B2 (en) | 2017-07-19 | 2021-05-25 | Asm Ip Holding B.V. | Method for selectively depositing a Group IV semiconductor and related semiconductor device structures |

| US10541333B2 (en) | 2017-07-19 | 2020-01-21 | Asm Ip Holding B.V. | Method for depositing a group IV semiconductor and related semiconductor device structures |

| US11374112B2 (en) | 2017-07-19 | 2022-06-28 | Asm Ip Holding B.V. | Method for depositing a group IV semiconductor and related semiconductor device structures |

| US10312055B2 (en) | 2017-07-26 | 2019-06-04 | Asm Ip Holding B.V. | Method of depositing film by PEALD using negative bias |

| US10590535B2 (en) | 2017-07-26 | 2020-03-17 | Asm Ip Holdings B.V. | Chemical treatment, deposition and/or infiltration apparatus and method for using the same |

| US10605530B2 (en) | 2017-07-26 | 2020-03-31 | Asm Ip Holding B.V. | Assembly of a liner and a flange for a vertical furnace as well as the liner and the vertical furnace |

| TWI815813B (zh) | 2017-08-04 | 2023-09-21 | 荷蘭商Asm智慧財產控股公司 | 用於分配反應腔內氣體的噴頭總成 |

| US10770336B2 (en) | 2017-08-08 | 2020-09-08 | Asm Ip Holding B.V. | Substrate lift mechanism and reactor including same |

| US10692741B2 (en) | 2017-08-08 | 2020-06-23 | Asm Ip Holdings B.V. | Radiation shield |

| US11769682B2 (en) | 2017-08-09 | 2023-09-26 | Asm Ip Holding B.V. | Storage apparatus for storing cassettes for substrates and processing apparatus equipped therewith |

| US10249524B2 (en) | 2017-08-09 | 2019-04-02 | Asm Ip Holding B.V. | Cassette holder assembly for a substrate cassette and holding member for use in such assembly |

| US11139191B2 (en) | 2017-08-09 | 2021-10-05 | Asm Ip Holding B.V. | Storage apparatus for storing cassettes for substrates and processing apparatus equipped therewith |

| US20190057860A1 (en) * | 2017-08-18 | 2019-02-21 | Lam Research Corporation | Methods for improving performance in hafnium oxide-based ferroelectric material using plasma and/or thermal treatment |

| US10236177B1 (en) | 2017-08-22 | 2019-03-19 | ASM IP Holding B.V.. | Methods for depositing a doped germanium tin semiconductor and related semiconductor device structures |

| USD900036S1 (en) | 2017-08-24 | 2020-10-27 | Asm Ip Holding B.V. | Heater electrical connector and adapter |

| US11830730B2 (en) | 2017-08-29 | 2023-11-28 | Asm Ip Holding B.V. | Layer forming method and apparatus |

| US11295980B2 (en) | 2017-08-30 | 2022-04-05 | Asm Ip Holding B.V. | Methods for depositing a molybdenum metal film over a dielectric surface of a substrate by a cyclical deposition process and related semiconductor device structures |

| US11056344B2 (en) | 2017-08-30 | 2021-07-06 | Asm Ip Holding B.V. | Layer forming method |

| KR102491945B1 (ko) | 2017-08-30 | 2023-01-26 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| KR102401446B1 (ko) | 2017-08-31 | 2022-05-24 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| US10607895B2 (en) | 2017-09-18 | 2020-03-31 | Asm Ip Holdings B.V. | Method for forming a semiconductor device structure comprising a gate fill metal |

| KR102630301B1 (ko) | 2017-09-21 | 2024-01-29 | 에이에스엠 아이피 홀딩 비.브이. | 침투성 재료의 순차 침투 합성 방법 처리 및 이를 이용하여 형성된 구조물 및 장치 |

| US10844484B2 (en) | 2017-09-22 | 2020-11-24 | Asm Ip Holding B.V. | Apparatus for dispensing a vapor phase reactant to a reaction chamber and related methods |

| US10658205B2 (en) | 2017-09-28 | 2020-05-19 | Asm Ip Holdings B.V. | Chemical dispensing apparatus and methods for dispensing a chemical to a reaction chamber |

| US10403504B2 (en) | 2017-10-05 | 2019-09-03 | Asm Ip Holding B.V. | Method for selectively depositing a metallic film on a substrate |

| US10319588B2 (en) | 2017-10-10 | 2019-06-11 | Asm Ip Holding B.V. | Method for depositing a metal chalcogenide on a substrate by cyclical deposition |

| US10923344B2 (en) | 2017-10-30 | 2021-02-16 | Asm Ip Holding B.V. | Methods for forming a semiconductor structure and related semiconductor structures |

| US10910262B2 (en) | 2017-11-16 | 2021-02-02 | Asm Ip Holding B.V. | Method of selectively depositing a capping layer structure on a semiconductor device structure |

| KR102443047B1 (ko) | 2017-11-16 | 2022-09-14 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 방법 및 그에 의해 제조된 장치 |

| US11022879B2 (en) | 2017-11-24 | 2021-06-01 | Asm Ip Holding B.V. | Method of forming an enhanced unexposed photoresist layer |

| KR102633318B1 (ko) | 2017-11-27 | 2024-02-05 | 에이에스엠 아이피 홀딩 비.브이. | 청정 소형 구역을 포함한 장치 |

| WO2019103613A1 (en) | 2017-11-27 | 2019-05-31 | Asm Ip Holding B.V. | A storage device for storing wafer cassettes for use with a batch furnace |

| US10290508B1 (en) | 2017-12-05 | 2019-05-14 | Asm Ip Holding B.V. | Method for forming vertical spacers for spacer-defined patterning |

| US10872771B2 (en) | 2018-01-16 | 2020-12-22 | Asm Ip Holding B. V. | Method for depositing a material film on a substrate within a reaction chamber by a cyclical deposition process and related device structures |

| TWI852426B (zh) | 2018-01-19 | 2024-08-11 | 荷蘭商Asm Ip私人控股有限公司 | 沈積方法 |

| CN111630203A (zh) | 2018-01-19 | 2020-09-04 | Asm Ip私人控股有限公司 | 通过等离子体辅助沉积来沉积间隙填充层的方法 |

| USD903477S1 (en) | 2018-01-24 | 2020-12-01 | Asm Ip Holdings B.V. | Metal clamp |

| US11018047B2 (en) | 2018-01-25 | 2021-05-25 | Asm Ip Holding B.V. | Hybrid lift pin |

| USD880437S1 (en) | 2018-02-01 | 2020-04-07 | Asm Ip Holding B.V. | Gas supply plate for semiconductor manufacturing apparatus |

| US10535516B2 (en) | 2018-02-01 | 2020-01-14 | Asm Ip Holdings B.V. | Method for depositing a semiconductor structure on a surface of a substrate and related semiconductor structures |

| US11081345B2 (en) | 2018-02-06 | 2021-08-03 | Asm Ip Holding B.V. | Method of post-deposition treatment for silicon oxide film |

| JP7124098B2 (ja) | 2018-02-14 | 2022-08-23 | エーエスエム・アイピー・ホールディング・ベー・フェー | 周期的堆積プロセスにより基材上にルテニウム含有膜を堆積させる方法 |

| US10896820B2 (en) | 2018-02-14 | 2021-01-19 | Asm Ip Holding B.V. | Method for depositing a ruthenium-containing film on a substrate by a cyclical deposition process |

| US10731249B2 (en) | 2018-02-15 | 2020-08-04 | Asm Ip Holding B.V. | Method of forming a transition metal containing film on a substrate by a cyclical deposition process, a method for supplying a transition metal halide compound to a reaction chamber, and related vapor deposition apparatus |

| KR102636427B1 (ko) | 2018-02-20 | 2024-02-13 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 및 장치 |

| US10658181B2 (en) | 2018-02-20 | 2020-05-19 | Asm Ip Holding B.V. | Method of spacer-defined direct patterning in semiconductor fabrication |

| US10975470B2 (en) | 2018-02-23 | 2021-04-13 | Asm Ip Holding B.V. | Apparatus for detecting or monitoring for a chemical precursor in a high temperature environment |

| US11473195B2 (en) | 2018-03-01 | 2022-10-18 | Asm Ip Holding B.V. | Semiconductor processing apparatus and a method for processing a substrate |

| US11629406B2 (en) | 2018-03-09 | 2023-04-18 | Asm Ip Holding B.V. | Semiconductor processing apparatus comprising one or more pyrometers for measuring a temperature of a substrate during transfer of the substrate |

| US11114283B2 (en) | 2018-03-16 | 2021-09-07 | Asm Ip Holding B.V. | Reactor, system including the reactor, and methods of manufacturing and using same |

| KR102646467B1 (ko) | 2018-03-27 | 2024-03-11 | 에이에스엠 아이피 홀딩 비.브이. | 기판 상에 전극을 형성하는 방법 및 전극을 포함하는 반도체 소자 구조 |

| US11230766B2 (en) | 2018-03-29 | 2022-01-25 | Asm Ip Holding B.V. | Substrate processing apparatus and method |

| US10510536B2 (en) | 2018-03-29 | 2019-12-17 | Asm Ip Holding B.V. | Method of depositing a co-doped polysilicon film on a surface of a substrate within a reaction chamber |

| US11088002B2 (en) | 2018-03-29 | 2021-08-10 | Asm Ip Holding B.V. | Substrate rack and a substrate processing system and method |

| KR102501472B1 (ko) | 2018-03-30 | 2023-02-20 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 |

| KR102600229B1 (ko) | 2018-04-09 | 2023-11-10 | 에이에스엠 아이피 홀딩 비.브이. | 기판 지지 장치, 이를 포함하는 기판 처리 장치 및 기판 처리 방법 |

| US12025484B2 (en) | 2018-05-08 | 2024-07-02 | Asm Ip Holding B.V. | Thin film forming method |

| KR102709511B1 (ko) | 2018-05-08 | 2024-09-24 | 에이에스엠 아이피 홀딩 비.브이. | 기판 상에 산화물 막을 주기적 증착 공정에 의해 증착하기 위한 방법 및 관련 소자 구조 |

| US12272527B2 (en) | 2018-05-09 | 2025-04-08 | Asm Ip Holding B.V. | Apparatus for use with hydrogen radicals and method of using same |

| TWI816783B (zh) | 2018-05-11 | 2023-10-01 | 荷蘭商Asm 智慧財產控股公司 | 用於基板上形成摻雜金屬碳化物薄膜之方法及相關半導體元件結構 |

| KR102596988B1 (ko) | 2018-05-28 | 2023-10-31 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 및 그에 의해 제조된 장치 |

| US11718913B2 (en) | 2018-06-04 | 2023-08-08 | Asm Ip Holding B.V. | Gas distribution system and reactor system including same |

| TWI840362B (zh) | 2018-06-04 | 2024-05-01 | 荷蘭商Asm Ip私人控股有限公司 | 水氣降低的晶圓處置腔室 |

| US11286562B2 (en) | 2018-06-08 | 2022-03-29 | Asm Ip Holding B.V. | Gas-phase chemical reactor and method of using same |

| KR102568797B1 (ko) | 2018-06-21 | 2023-08-21 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 시스템 |

| US10797133B2 (en) | 2018-06-21 | 2020-10-06 | Asm Ip Holding B.V. | Method for depositing a phosphorus doped silicon arsenide film and related semiconductor device structures |

| KR20250134000A (ko) | 2018-06-27 | 2025-09-09 | 에이에스엠 아이피 홀딩 비.브이. | 금속 함유 재료를 형성하기 위한 주기적 증착 방법 및 금속 함유 재료를 포함하는 필름 및 구조체 |

| CN112292477A (zh) | 2018-06-27 | 2021-01-29 | Asm Ip私人控股有限公司 | 用于形成含金属的材料的循环沉积方法及包含含金属的材料的膜和结构 |

| KR102686758B1 (ko) | 2018-06-29 | 2024-07-18 | 에이에스엠 아이피 홀딩 비.브이. | 박막 증착 방법 및 반도체 장치의 제조 방법 |

| US10612136B2 (en) | 2018-06-29 | 2020-04-07 | ASM IP Holding, B.V. | Temperature-controlled flange and reactor system including same |

| US10755922B2 (en) | 2018-07-03 | 2020-08-25 | Asm Ip Holding B.V. | Method for depositing silicon-free carbon-containing film as gap-fill layer by pulse plasma-assisted deposition |

| US10388513B1 (en) | 2018-07-03 | 2019-08-20 | Asm Ip Holding B.V. | Method for depositing silicon-free carbon-containing film as gap-fill layer by pulse plasma-assisted deposition |

| US10767789B2 (en) | 2018-07-16 | 2020-09-08 | Asm Ip Holding B.V. | Diaphragm valves, valve components, and methods for forming valve components |

| US10483099B1 (en) | 2018-07-26 | 2019-11-19 | Asm Ip Holding B.V. | Method for forming thermally stable organosilicon polymer film |

| US11053591B2 (en) | 2018-08-06 | 2021-07-06 | Asm Ip Holding B.V. | Multi-port gas injection system and reactor system including same |

| US10883175B2 (en) | 2018-08-09 | 2021-01-05 | Asm Ip Holding B.V. | Vertical furnace for processing substrates and a liner for use therein |

| US10829852B2 (en) | 2018-08-16 | 2020-11-10 | Asm Ip Holding B.V. | Gas distribution device for a wafer processing apparatus |

| US11430674B2 (en) | 2018-08-22 | 2022-08-30 | Asm Ip Holding B.V. | Sensor array, apparatus for dispensing a vapor phase reactant to a reaction chamber and related methods |

| KR102707956B1 (ko) | 2018-09-11 | 2024-09-19 | 에이에스엠 아이피 홀딩 비.브이. | 박막 증착 방법 |

| US11024523B2 (en) | 2018-09-11 | 2021-06-01 | Asm Ip Holding B.V. | Substrate processing apparatus and method |

| US11049751B2 (en) | 2018-09-14 | 2021-06-29 | Asm Ip Holding B.V. | Cassette supply system to store and handle cassettes and processing apparatus equipped therewith |

| CN110970344B (zh) | 2018-10-01 | 2024-10-25 | Asmip控股有限公司 | 衬底保持设备、包含所述设备的系统及其使用方法 |

| US11232963B2 (en) | 2018-10-03 | 2022-01-25 | Asm Ip Holding B.V. | Substrate processing apparatus and method |

| KR102592699B1 (ko) | 2018-10-08 | 2023-10-23 | 에이에스엠 아이피 홀딩 비.브이. | 기판 지지 유닛 및 이를 포함하는 박막 증착 장치와 기판 처리 장치 |

| US10847365B2 (en) | 2018-10-11 | 2020-11-24 | Asm Ip Holding B.V. | Method of forming conformal silicon carbide film by cyclic CVD |

| US10811256B2 (en) | 2018-10-16 | 2020-10-20 | Asm Ip Holding B.V. | Method for etching a carbon-containing feature |

| KR102605121B1 (ko) | 2018-10-19 | 2023-11-23 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 및 기판 처리 방법 |

| KR102546322B1 (ko) | 2018-10-19 | 2023-06-21 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 및 기판 처리 방법 |

| USD948463S1 (en) | 2018-10-24 | 2022-04-12 | Asm Ip Holding B.V. | Susceptor for semiconductor substrate supporting apparatus |

| US10381219B1 (en) | 2018-10-25 | 2019-08-13 | Asm Ip Holding B.V. | Methods for forming a silicon nitride film |

| US12378665B2 (en) | 2018-10-26 | 2025-08-05 | Asm Ip Holding B.V. | High temperature coatings for a preclean and etch apparatus and related methods |

| US11087997B2 (en) | 2018-10-31 | 2021-08-10 | Asm Ip Holding B.V. | Substrate processing apparatus for processing substrates |

| KR102748291B1 (ko) | 2018-11-02 | 2024-12-31 | 에이에스엠 아이피 홀딩 비.브이. | 기판 지지 유닛 및 이를 포함하는 기판 처리 장치 |

| US11572620B2 (en) | 2018-11-06 | 2023-02-07 | Asm Ip Holding B.V. | Methods for selectively depositing an amorphous silicon film on a substrate |

| US11031242B2 (en) | 2018-11-07 | 2021-06-08 | Asm Ip Holding B.V. | Methods for depositing a boron doped silicon germanium film |

| US10818758B2 (en) | 2018-11-16 | 2020-10-27 | Asm Ip Holding B.V. | Methods for forming a metal silicate film on a substrate in a reaction chamber and related semiconductor device structures |

| US10847366B2 (en) | 2018-11-16 | 2020-11-24 | Asm Ip Holding B.V. | Methods for depositing a transition metal chalcogenide film on a substrate by a cyclical deposition process |

| US10559458B1 (en) | 2018-11-26 | 2020-02-11 | Asm Ip Holding B.V. | Method of forming oxynitride film |

| US12040199B2 (en) | 2018-11-28 | 2024-07-16 | Asm Ip Holding B.V. | Substrate processing apparatus for processing substrates |

| US11217444B2 (en) | 2018-11-30 | 2022-01-04 | Asm Ip Holding B.V. | Method for forming an ultraviolet radiation responsive metal oxide-containing film |

| KR102636428B1 (ko) | 2018-12-04 | 2024-02-13 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치를 세정하는 방법 |

| US11158513B2 (en) | 2018-12-13 | 2021-10-26 | Asm Ip Holding B.V. | Methods for forming a rhenium-containing film on a substrate by a cyclical deposition process and related semiconductor device structures |

| TWI874340B (zh) | 2018-12-14 | 2025-03-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成裝置結構之方法、其所形成之結構及施行其之系統 |

| TWI866480B (zh) | 2019-01-17 | 2024-12-11 | 荷蘭商Asm Ip 私人控股有限公司 | 藉由循環沈積製程於基板上形成含過渡金屬膜之方法 |

| KR102727227B1 (ko) | 2019-01-22 | 2024-11-07 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| CN111524788B (zh) | 2019-02-01 | 2023-11-24 | Asm Ip私人控股有限公司 | 氧化硅的拓扑选择性膜形成的方法 |

| JP7509548B2 (ja) | 2019-02-20 | 2024-07-02 | エーエスエム・アイピー・ホールディング・ベー・フェー | 基材表面内に形成された凹部を充填するための周期的堆積方法および装置 |

| KR102626263B1 (ko) | 2019-02-20 | 2024-01-16 | 에이에스엠 아이피 홀딩 비.브이. | 처리 단계를 포함하는 주기적 증착 방법 및 이를 위한 장치 |

| TWI873122B (zh) | 2019-02-20 | 2025-02-21 | 荷蘭商Asm Ip私人控股有限公司 | 填充一基板之一表面內所形成的一凹槽的方法、根據其所形成之半導體結構、及半導體處理設備 |

| KR20200102357A (ko) | 2019-02-20 | 2020-08-31 | 에이에스엠 아이피 홀딩 비.브이. | 3-d nand 응용의 플러그 충진체 증착용 장치 및 방법 |

| TWI842826B (zh) | 2019-02-22 | 2024-05-21 | 荷蘭商Asm Ip私人控股有限公司 | 基材處理設備及處理基材之方法 |

| KR102762833B1 (ko) | 2019-03-08 | 2025-02-04 | 에이에스엠 아이피 홀딩 비.브이. | SiOCN 층을 포함한 구조체 및 이의 형성 방법 |

| KR102858005B1 (ko) | 2019-03-08 | 2025-09-09 | 에이에스엠 아이피 홀딩 비.브이. | 실리콘 질화물 층을 선택적으로 증착하는 방법, 및 선택적으로 증착된 실리콘 질화물 층을 포함하는 구조체 |

| KR102782593B1 (ko) | 2019-03-08 | 2025-03-14 | 에이에스엠 아이피 홀딩 비.브이. | SiOC 층을 포함한 구조체 및 이의 형성 방법 |

| US10627696B1 (en) | 2019-03-18 | 2020-04-21 | Psiwuantum, Corp. | Active photonic devices incorporating high dielectric constant materials |

| KR20200116033A (ko) | 2019-03-28 | 2020-10-08 | 에이에스엠 아이피 홀딩 비.브이. | 도어 개방기 및 이를 구비한 기판 처리 장치 |

| KR102809999B1 (ko) | 2019-04-01 | 2025-05-19 | 에이에스엠 아이피 홀딩 비.브이. | 반도체 소자를 제조하는 방법 |

| KR102897355B1 (ko) | 2019-04-19 | 2025-12-08 | 에이에스엠 아이피 홀딩 비.브이. | 층 형성 방법 및 장치 |

| KR20200125453A (ko) | 2019-04-24 | 2020-11-04 | 에이에스엠 아이피 홀딩 비.브이. | 기상 반응기 시스템 및 이를 사용하는 방법 |

| KR102869364B1 (ko) | 2019-05-07 | 2025-10-10 | 에이에스엠 아이피 홀딩 비.브이. | 비정질 탄소 중합체 막을 개질하는 방법 |

| KR102929471B1 (ko) | 2019-05-07 | 2026-02-20 | 에이에스엠 아이피 홀딩 비.브이. | 딥 튜브가 있는 화학물질 공급원 용기 |

| KR102929472B1 (ko) | 2019-05-10 | 2026-02-20 | 에이에스엠 아이피 홀딩 비.브이. | 표면 상에 재료를 증착하는 방법 및 본 방법에 따라 형성된 구조 |

| JP7612342B2 (ja) | 2019-05-16 | 2025-01-14 | エーエスエム・アイピー・ホールディング・ベー・フェー | ウェハボートハンドリング装置、縦型バッチ炉および方法 |

| JP7598201B2 (ja) | 2019-05-16 | 2024-12-11 | エーエスエム・アイピー・ホールディング・ベー・フェー | ウェハボートハンドリング装置、縦型バッチ炉および方法 |

| USD947913S1 (en) | 2019-05-17 | 2022-04-05 | Asm Ip Holding B.V. | Susceptor shaft |

| USD975665S1 (en) | 2019-05-17 | 2023-01-17 | Asm Ip Holding B.V. | Susceptor shaft |

| USD935572S1 (en) | 2019-05-24 | 2021-11-09 | Asm Ip Holding B.V. | Gas channel plate |

| USD922229S1 (en) | 2019-06-05 | 2021-06-15 | Asm Ip Holding B.V. | Device for controlling a temperature of a gas supply unit |

| KR20200141003A (ko) | 2019-06-06 | 2020-12-17 | 에이에스엠 아이피 홀딩 비.브이. | 가스 감지기를 포함하는 기상 반응기 시스템 |

| KR102918757B1 (ko) | 2019-06-10 | 2026-01-28 | 에이에스엠 아이피 홀딩 비.브이. | 석영 에피택셜 챔버를 세정하는 방법 |

| KR20200143254A (ko) | 2019-06-11 | 2020-12-23 | 에이에스엠 아이피 홀딩 비.브이. | 개질 가스를 사용하여 전자 구조를 형성하는 방법, 상기 방법을 수행하기 위한 시스템, 및 상기 방법을 사용하여 형성되는 구조 |

| USD944946S1 (en) | 2019-06-14 | 2022-03-01 | Asm Ip Holding B.V. | Shower plate |

| US11256115B1 (en) | 2019-06-21 | 2022-02-22 | Psiquantum, Corp. | Active photonic devices with enhanced Pockels effect via isotope substitution |

| USD931978S1 (en) | 2019-06-27 | 2021-09-28 | Asm Ip Holding B.V. | Showerhead vacuum transport |

| KR102911421B1 (ko) | 2019-07-03 | 2026-01-12 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치용 온도 제어 조립체 및 이를 사용하는 방법 |

| JP7499079B2 (ja) | 2019-07-09 | 2024-06-13 | エーエスエム・アイピー・ホールディング・ベー・フェー | 同軸導波管を用いたプラズマ装置、基板処理方法 |

| CN112216646B (zh) | 2019-07-10 | 2026-02-10 | Asmip私人控股有限公司 | 基板支撑组件及包括其的基板处理装置 |

| KR102895115B1 (ko) | 2019-07-16 | 2025-12-03 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| KR20210010816A (ko) | 2019-07-17 | 2021-01-28 | 에이에스엠 아이피 홀딩 비.브이. | 라디칼 보조 점화 플라즈마 시스템 및 방법 |

| KR102860110B1 (ko) | 2019-07-17 | 2025-09-16 | 에이에스엠 아이피 홀딩 비.브이. | 실리콘 게르마늄 구조를 형성하는 방법 |

| US11643724B2 (en) | 2019-07-18 | 2023-05-09 | Asm Ip Holding B.V. | Method of forming structures using a neutral beam |

| TWI839544B (zh) | 2019-07-19 | 2024-04-21 | 荷蘭商Asm Ip私人控股有限公司 | 形成形貌受控的非晶碳聚合物膜之方法 |

| KR102903090B1 (ko) | 2019-07-19 | 2025-12-19 | 에이에스엠 아이피 홀딩 비.브이. | 토폴로지-제어된 비정질 탄소 중합체 막을 형성하는 방법 |

| TWI851767B (zh) | 2019-07-29 | 2024-08-11 | 荷蘭商Asm Ip私人控股有限公司 | 用於利用n型摻雜物及/或替代摻雜物選擇性沉積以達成高摻雜物併入之方法 |

| US12169361B2 (en) | 2019-07-30 | 2024-12-17 | Asm Ip Holding B.V. | Substrate processing apparatus and method |

| CN112309899B (zh) | 2019-07-30 | 2025-11-14 | Asmip私人控股有限公司 | 基板处理设备 |

| CN112309900B (zh) | 2019-07-30 | 2025-11-04 | Asmip私人控股有限公司 | 基板处理设备 |

| US11587815B2 (en) | 2019-07-31 | 2023-02-21 | Asm Ip Holding B.V. | Vertical batch furnace assembly |

| US11587814B2 (en) | 2019-07-31 | 2023-02-21 | Asm Ip Holding B.V. | Vertical batch furnace assembly |

| US11227782B2 (en) | 2019-07-31 | 2022-01-18 | Asm Ip Holding B.V. | Vertical batch furnace assembly |

| CN112323048B (zh) | 2019-08-05 | 2024-02-09 | Asm Ip私人控股有限公司 | 用于化学源容器的液位传感器 |

| CN112342526A (zh) | 2019-08-09 | 2021-02-09 | Asm Ip私人控股有限公司 | 包括冷却装置的加热器组件及其使用方法 |

| USD965044S1 (en) | 2019-08-19 | 2022-09-27 | Asm Ip Holding B.V. | Susceptor shaft |

| USD965524S1 (en) | 2019-08-19 | 2022-10-04 | Asm Ip Holding B.V. | Susceptor support |

| JP7810514B2 (ja) | 2019-08-21 | 2026-02-03 | エーエスエム・アイピー・ホールディング・ベー・フェー | 成膜原料混合ガス生成装置及び成膜装置 |

| USD979506S1 (en) | 2019-08-22 | 2023-02-28 | Asm Ip Holding B.V. | Insulator |

| USD930782S1 (en) | 2019-08-22 | 2021-09-14 | Asm Ip Holding B.V. | Gas distributor |

| KR20210024423A (ko) | 2019-08-22 | 2021-03-05 | 에이에스엠 아이피 홀딩 비.브이. | 홀을 구비한 구조체를 형성하기 위한 방법 |

| USD940837S1 (en) | 2019-08-22 | 2022-01-11 | Asm Ip Holding B.V. | Electrode |

| USD949319S1 (en) | 2019-08-22 | 2022-04-19 | Asm Ip Holding B.V. | Exhaust duct |

| KR102928101B1 (ko) | 2019-08-23 | 2026-02-13 | 에이에스엠 아이피 홀딩 비.브이. | 비스(디에틸아미노)실란을 사용하여 peald에 의해 개선된 품질을 갖는 실리콘 산화물 막을 증착하기 위한 방법 |

| US11286558B2 (en) | 2019-08-23 | 2022-03-29 | Asm Ip Holding B.V. | Methods for depositing a molybdenum nitride film on a surface of a substrate by a cyclical deposition process and related semiconductor device structures including a molybdenum nitride film |

| CN112442674A (zh) | 2019-09-03 | 2021-03-05 | Asm Ip私人控股有限公司 | 用于沉积硫族化物膜的方法和设备以及包括膜的结构 |

| KR102806450B1 (ko) | 2019-09-04 | 2025-05-12 | 에이에스엠 아이피 홀딩 비.브이. | 희생 캡핑 층을 이용한 선택적 증착 방법 |

| KR102733104B1 (ko) | 2019-09-05 | 2024-11-22 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| US12469693B2 (en) | 2019-09-17 | 2025-11-11 | Asm Ip Holding B.V. | Method of forming a carbon-containing layer and structure including the layer |

| US11562901B2 (en) | 2019-09-25 | 2023-01-24 | Asm Ip Holding B.V. | Substrate processing method |

| CN112593212B (zh) | 2019-10-02 | 2023-12-22 | Asm Ip私人控股有限公司 | 通过循环等离子体增强沉积工艺形成拓扑选择性氧化硅膜的方法 |

| TW202128273A (zh) | 2019-10-08 | 2021-08-01 | 荷蘭商Asm Ip私人控股有限公司 | 氣體注入系統、及將材料沉積於反應室內之基板表面上的方法 |

| TWI846953B (zh) | 2019-10-08 | 2024-07-01 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理裝置 |

| CN112626493B (zh) | 2019-10-08 | 2024-10-25 | Asmip私人控股有限公司 | 反应器系统以及其使用方法 |

| TWI846966B (zh) | 2019-10-10 | 2024-07-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成光阻底層之方法及包括光阻底層之結構 |

| US12009241B2 (en) | 2019-10-14 | 2024-06-11 | Asm Ip Holding B.V. | Vertical batch furnace assembly with detector to detect cassette |

| TWI834919B (zh) | 2019-10-16 | 2024-03-11 | 荷蘭商Asm Ip私人控股有限公司 | 氧化矽之拓撲選擇性膜形成之方法 |

| US11637014B2 (en) | 2019-10-17 | 2023-04-25 | Asm Ip Holding B.V. | Methods for selective deposition of doped semiconductor material |

| KR102845724B1 (ko) | 2019-10-21 | 2025-08-13 | 에이에스엠 아이피 홀딩 비.브이. | 막을 선택적으로 에칭하기 위한 장치 및 방법 |

| KR20210050453A (ko) | 2019-10-25 | 2021-05-07 | 에이에스엠 아이피 홀딩 비.브이. | 기판 표면 상의 갭 피처를 충진하는 방법 및 이와 관련된 반도체 소자 구조 |

| US11646205B2 (en) | 2019-10-29 | 2023-05-09 | Asm Ip Holding B.V. | Methods of selectively forming n-type doped material on a surface, systems for selectively forming n-type doped material, and structures formed using same |

| KR102890638B1 (ko) | 2019-11-05 | 2025-11-25 | 에이에스엠 아이피 홀딩 비.브이. | 도핑된 반도체 층을 갖는 구조체 및 이를 형성하기 위한 방법 및 시스템 |

| US11501968B2 (en) | 2019-11-15 | 2022-11-15 | Asm Ip Holding B.V. | Method for providing a semiconductor device with silicon filled gaps |

| KR102861314B1 (ko) | 2019-11-20 | 2025-09-17 | 에이에스엠 아이피 홀딩 비.브이. | 기판의 표면 상에 탄소 함유 물질을 증착하는 방법, 상기 방법을 사용하여 형성된 구조물, 및 상기 구조물을 형성하기 위한 시스템 |

| CN112951697B (zh) | 2019-11-26 | 2025-07-29 | Asmip私人控股有限公司 | 基板处理设备 |

| KR20210065848A (ko) | 2019-11-26 | 2021-06-04 | 에이에스엠 아이피 홀딩 비.브이. | 제1 유전체 표면과 제2 금속성 표면을 포함한 기판 상에 타겟 막을 선택적으로 형성하기 위한 방법 |

| CN120998766A (zh) | 2019-11-29 | 2025-11-21 | Asm Ip私人控股有限公司 | 基板处理设备 |

| CN120432376A (zh) | 2019-11-29 | 2025-08-05 | Asm Ip私人控股有限公司 | 基板处理设备 |

| JP7527928B2 (ja) | 2019-12-02 | 2024-08-05 | エーエスエム・アイピー・ホールディング・ベー・フェー | 基板処理装置、基板処理方法 |

| KR20210070898A (ko) | 2019-12-04 | 2021-06-15 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| TWI869506B (zh) | 2019-12-17 | 2025-01-11 | 荷蘭商Asm Ip私人控股有限公司 | 形成氮化釩層之方法與系統以及包括該氮化釩層之結構 |

| US11527403B2 (en) | 2019-12-19 | 2022-12-13 | Asm Ip Holding B.V. | Methods for filling a gap feature on a substrate surface and related semiconductor structures |

| TWI901623B (zh) | 2020-01-06 | 2025-10-21 | 荷蘭商Asm Ip私人控股有限公司 | 氣體供應總成以及閥板總成 |

| TWI887322B (zh) | 2020-01-06 | 2025-06-21 | 荷蘭商Asm Ip私人控股有限公司 | 反應器系統、抬升銷、及處理方法 |

| US11993847B2 (en) | 2020-01-08 | 2024-05-28 | Asm Ip Holding B.V. | Injector |

| KR102882467B1 (ko) | 2020-01-16 | 2025-11-05 | 에이에스엠 아이피 홀딩 비.브이. | 고 종횡비 피처를 형성하는 방법 |

| KR102675856B1 (ko) | 2020-01-20 | 2024-06-17 | 에이에스엠 아이피 홀딩 비.브이. | 박막 형성 방법 및 박막 표면 개질 방법 |

| TWI889744B (zh) | 2020-01-29 | 2025-07-11 | 荷蘭商Asm Ip私人控股有限公司 | 污染物捕集系統、及擋板堆疊 |

| TW202513845A (zh) | 2020-02-03 | 2025-04-01 | 荷蘭商Asm Ip私人控股有限公司 | 半導體裝置結構及其形成方法 |

| KR20210100010A (ko) | 2020-02-04 | 2021-08-13 | 에이에스엠 아이피 홀딩 비.브이. | 대형 물품의 투과율 측정을 위한 방법 및 장치 |

| US11776846B2 (en) | 2020-02-07 | 2023-10-03 | Asm Ip Holding B.V. | Methods for depositing gap filling fluids and related systems and devices |

| KR102916725B1 (ko) | 2020-02-13 | 2026-01-23 | 에이에스엠 아이피 홀딩 비.브이. | 수광 장치를 포함하는 기판 처리 장치 및 수광 장치의 교정 방법 |

| KR20210103953A (ko) | 2020-02-13 | 2021-08-24 | 에이에스엠 아이피 홀딩 비.브이. | 가스 분배 어셈블리 및 이를 사용하는 방법 |

| TWI855223B (zh) | 2020-02-17 | 2024-09-11 | 荷蘭商Asm Ip私人控股有限公司 | 用於生長磷摻雜矽層之方法 |

| TWI895326B (zh) | 2020-02-28 | 2025-09-01 | 荷蘭商Asm Ip私人控股有限公司 | 專用於零件清潔的系統 |

| CN113363196A (zh) | 2020-03-04 | 2021-09-07 | Asm Ip私人控股有限公司 | 用于反应器系统的对准夹具 |

| KR20210116249A (ko) | 2020-03-11 | 2021-09-27 | 에이에스엠 아이피 홀딩 비.브이. | 록아웃 태그아웃 어셈블리 및 시스템 그리고 이의 사용 방법 |

| KR20210116240A (ko) | 2020-03-11 | 2021-09-27 | 에이에스엠 아이피 홀딩 비.브이. | 조절성 접합부를 갖는 기판 핸들링 장치 |

| CN113394086A (zh) | 2020-03-12 | 2021-09-14 | Asm Ip私人控股有限公司 | 用于制造具有目标拓扑轮廓的层结构的方法 |

| US12173404B2 (en) | 2020-03-17 | 2024-12-24 | Asm Ip Holding B.V. | Method of depositing epitaxial material, structure formed using the method, and system for performing the method |

| KR102755229B1 (ko) | 2020-04-02 | 2025-01-14 | 에이에스엠 아이피 홀딩 비.브이. | 박막 형성 방법 |

| TWI887376B (zh) | 2020-04-03 | 2025-06-21 | 荷蘭商Asm Ip私人控股有限公司 | 半導體裝置的製造方法 |

| TWI888525B (zh) | 2020-04-08 | 2025-07-01 | 荷蘭商Asm Ip私人控股有限公司 | 用於選擇性蝕刻氧化矽膜之設備及方法 |

| US11821078B2 (en) | 2020-04-15 | 2023-11-21 | Asm Ip Holding B.V. | Method for forming precoat film and method for forming silicon-containing film |

| KR20210128343A (ko) | 2020-04-15 | 2021-10-26 | 에이에스엠 아이피 홀딩 비.브이. | 크롬 나이트라이드 층을 형성하는 방법 및 크롬 나이트라이드 층을 포함하는 구조 |

| US11996289B2 (en) | 2020-04-16 | 2024-05-28 | Asm Ip Holding B.V. | Methods of forming structures including silicon germanium and silicon layers, devices formed using the methods, and systems for performing the methods |

| KR102901748B1 (ko) | 2020-04-21 | 2025-12-17 | 에이에스엠 아이피 홀딩 비.브이. | 기판을 처리하기 위한 방법 |

| KR102866804B1 (ko) | 2020-04-24 | 2025-09-30 | 에이에스엠 아이피 홀딩 비.브이. | 냉각 가스 공급부를 포함한 수직형 배치 퍼니스 어셈블리 |

| TW202208671A (zh) | 2020-04-24 | 2022-03-01 | 荷蘭商Asm Ip私人控股有限公司 | 形成包括硼化釩及磷化釩層的結構之方法 |

| KR20210132600A (ko) | 2020-04-24 | 2021-11-04 | 에이에스엠 아이피 홀딩 비.브이. | 바나듐, 질소 및 추가 원소를 포함한 층을 증착하기 위한 방법 및 시스템 |

| TW202539998A (zh) | 2020-04-24 | 2025-10-16 | 荷蘭商Asm Ip私人控股有限公司 | 包含釩化合物之組成物與容器及用於穩定釩化合物之方法及系統 |

| TWI884193B (zh) | 2020-04-24 | 2025-05-21 | 荷蘭商Asm Ip私人控股有限公司 | 形成含氮化釩層及包含該層的結構之方法 |

| KR102783898B1 (ko) | 2020-04-29 | 2025-03-18 | 에이에스엠 아이피 홀딩 비.브이. | 고체 소스 전구체 용기 |

| KR20210134869A (ko) | 2020-05-01 | 2021-11-11 | 에이에스엠 아이피 홀딩 비.브이. | Foup 핸들러를 이용한 foup의 빠른 교환 |

| TWI907417B (zh) | 2020-05-04 | 2025-12-11 | 荷蘭商Asm Ip私人控股有限公司 | 半導體處理系統 |

| JP7736446B2 (ja) | 2020-05-07 | 2025-09-09 | エーエスエム・アイピー・ホールディング・ベー・フェー | 同調回路を備える反応器システム |

| KR102788543B1 (ko) | 2020-05-13 | 2025-03-27 | 에이에스엠 아이피 홀딩 비.브이. | 반응기 시스템용 레이저 정렬 고정구 |

| US12057314B2 (en) | 2020-05-15 | 2024-08-06 | Asm Ip Holding B.V. | Methods for silicon germanium uniformity control using multiple precursors |

| KR102905441B1 (ko) | 2020-05-19 | 2025-12-30 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 |

| KR102795476B1 (ko) | 2020-05-21 | 2025-04-11 | 에이에스엠 아이피 홀딩 비.브이. | 다수의 탄소 층을 포함한 구조체 및 이를 형성하고 사용하는 방법 |

| KR20210145079A (ko) | 2020-05-21 | 2021-12-01 | 에이에스엠 아이피 홀딩 비.브이. | 기판을 처리하기 위한 플랜지 및 장치 |

| KR102702526B1 (ko) | 2020-05-22 | 2024-09-03 | 에이에스엠 아이피 홀딩 비.브이. | 과산화수소를 사용하여 박막을 증착하기 위한 장치 |

| KR20210146802A (ko) | 2020-05-26 | 2021-12-06 | 에이에스엠 아이피 홀딩 비.브이. | 붕소 및 갈륨을 함유한 실리콘 게르마늄 층을 증착하는 방법 |

| TWI876048B (zh) | 2020-05-29 | 2025-03-11 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理方法 |

| TW202212620A (zh) | 2020-06-02 | 2022-04-01 | 荷蘭商Asm Ip私人控股有限公司 | 處理基板之設備、形成膜之方法、及控制用於處理基板之設備之方法 |

| KR20210156219A (ko) | 2020-06-16 | 2021-12-24 | 에이에스엠 아이피 홀딩 비.브이. | 붕소를 함유한 실리콘 게르마늄 층을 증착하는 방법 |

| TWI908816B (zh) | 2020-06-24 | 2025-12-21 | 荷蘭商Asm Ip私人控股有限公司 | 形成含矽層之方法 |

| TWI873359B (zh) | 2020-06-30 | 2025-02-21 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理方法 |

| TWI896694B (zh) | 2020-07-01 | 2025-09-11 | 荷蘭商Asm Ip私人控股有限公司 | 沉積方法、半導體結構、及沉積系統 |

| KR102707957B1 (ko) | 2020-07-08 | 2024-09-19 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 |

| TWI864307B (zh) | 2020-07-17 | 2024-12-01 | 荷蘭商Asm Ip私人控股有限公司 | 用於光微影之結構、方法與系統 |

| TWI878570B (zh) | 2020-07-20 | 2025-04-01 | 荷蘭商Asm Ip私人控股有限公司 | 用於沉積鉬層之方法及系統 |

| KR20220011092A (ko) | 2020-07-20 | 2022-01-27 | 에이에스엠 아이피 홀딩 비.브이. | 전이 금속층을 포함하는 구조체를 형성하기 위한 방법 및 시스템 |

| US12322591B2 (en) | 2020-07-27 | 2025-06-03 | Asm Ip Holding B.V. | Thin film deposition process |

| KR20220020210A (ko) | 2020-08-11 | 2022-02-18 | 에이에스엠 아이피 홀딩 비.브이. | 기판 상에 티타늄 알루미늄 카바이드 막 구조체 및 관련 반도체 구조체를 증착하는 방법 |

| KR102915124B1 (ko) | 2020-08-14 | 2026-01-19 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 |

| US12040177B2 (en) | 2020-08-18 | 2024-07-16 | Asm Ip Holding B.V. | Methods for forming a laminate film by cyclical plasma-enhanced deposition processes |

| KR20220026500A (ko) | 2020-08-25 | 2022-03-04 | 에이에스엠 아이피 홀딩 비.브이. | 표면을 세정하는 방법 |

| US11725280B2 (en) | 2020-08-26 | 2023-08-15 | Asm Ip Holding B.V. | Method for forming metal silicon oxide and metal silicon oxynitride layers |

| KR20220027772A (ko) | 2020-08-27 | 2022-03-08 | 에이에스엠 아이피 홀딩 비.브이. | 다중 패터닝 공정을 사용하여 패터닝된 구조체를 형성하기 위한 방법 및 시스템 |

| TWI904232B (zh) | 2020-09-10 | 2025-11-11 | 荷蘭商Asm Ip私人控股有限公司 | 沉積間隙填充流體之方法及相關系統和裝置 |

| USD990534S1 (en) | 2020-09-11 | 2023-06-27 | Asm Ip Holding B.V. | Weighted lift pin |

| KR20220036866A (ko) | 2020-09-16 | 2022-03-23 | 에이에스엠 아이피 홀딩 비.브이. | 실리콘 산화물 증착 방법 |

| USD1012873S1 (en) | 2020-09-24 | 2024-01-30 | Asm Ip Holding B.V. | Electrode for semiconductor processing apparatus |

| TWI889903B (zh) | 2020-09-25 | 2025-07-11 | 荷蘭商Asm Ip私人控股有限公司 | 基板處理方法 |

| US12009224B2 (en) | 2020-09-29 | 2024-06-11 | Asm Ip Holding B.V. | Apparatus and method for etching metal nitrides |

| CN114388427A (zh) | 2020-10-06 | 2022-04-22 | Asm Ip私人控股有限公司 | 用于在特征的侧壁上形成氮化硅的方法和系统 |

| KR20220045900A (ko) | 2020-10-06 | 2022-04-13 | 에이에스엠 아이피 홀딩 비.브이. | 실리콘 함유 재료를 증착하기 위한 증착 방법 및 장치 |

| CN114293174A (zh) | 2020-10-07 | 2022-04-08 | Asm Ip私人控股有限公司 | 气体供应单元和包括气体供应单元的衬底处理设备 |

| KR102855834B1 (ko) | 2020-10-14 | 2025-09-04 | 에이에스엠 아이피 홀딩 비.브이. | 단차형 구조 상에 재료를 증착하는 방법 |

| KR102873665B1 (ko) | 2020-10-15 | 2025-10-17 | 에이에스엠 아이피 홀딩 비.브이. | 반도체 소자의 제조 방법, 및 ether-cat을 사용하는 기판 처리 장치 |

| KR20220053482A (ko) | 2020-10-22 | 2022-04-29 | 에이에스엠 아이피 홀딩 비.브이. | 바나듐 금속을 증착하는 방법, 구조체, 소자 및 증착 어셈블리 |

| TW202223136A (zh) | 2020-10-28 | 2022-06-16 | 荷蘭商Asm Ip私人控股有限公司 | 用於在基板上形成層之方法、及半導體處理系統 |

| TW202229620A (zh) | 2020-11-12 | 2022-08-01 | 特文特大學 | 沉積系統、用於控制反應條件之方法、沉積方法 |

| TW202229795A (zh) | 2020-11-23 | 2022-08-01 | 荷蘭商Asm Ip私人控股有限公司 | 具注入器之基板處理設備 |

| TW202235649A (zh) | 2020-11-24 | 2022-09-16 | 荷蘭商Asm Ip私人控股有限公司 | 填充間隙之方法與相關之系統及裝置 |

| KR20220076343A (ko) | 2020-11-30 | 2022-06-08 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치의 반응 챔버 내에 배열되도록 구성된 인젝터 |

| KR20220077875A (ko) | 2020-12-02 | 2022-06-09 | 에이에스엠 아이피 홀딩 비.브이. | 샤워헤드 어셈블리용 세정 고정구 |

| US12255053B2 (en) | 2020-12-10 | 2025-03-18 | Asm Ip Holding B.V. | Methods and systems for depositing a layer |

| US12159788B2 (en) | 2020-12-14 | 2024-12-03 | Asm Ip Holding B.V. | Method of forming structures for threshold voltage control |

| CN114639631A (zh) | 2020-12-16 | 2022-06-17 | Asm Ip私人控股有限公司 | 跳动和摆动测量固定装置 |

| TW202232639A (zh) | 2020-12-18 | 2022-08-16 | 荷蘭商Asm Ip私人控股有限公司 | 具有可旋轉台的晶圓處理設備 |

| TW202231903A (zh) | 2020-12-22 | 2022-08-16 | 荷蘭商Asm Ip私人控股有限公司 | 過渡金屬沉積方法、過渡金屬層、用於沉積過渡金屬於基板上的沉積總成 |

| TW202226899A (zh) | 2020-12-22 | 2022-07-01 | 荷蘭商Asm Ip私人控股有限公司 | 具匹配器的電漿處理裝置 |

| TW202242184A (zh) | 2020-12-22 | 2022-11-01 | 荷蘭商Asm Ip私人控股有限公司 | 前驅物膠囊、前驅物容器、氣相沉積總成、及將固態前驅物裝載至前驅物容器中之方法 |

| USD980814S1 (en) | 2021-05-11 | 2023-03-14 | Asm Ip Holding B.V. | Gas distributor for substrate processing apparatus |

| USD980813S1 (en) | 2021-05-11 | 2023-03-14 | Asm Ip Holding B.V. | Gas flow control plate for substrate processing apparatus |

| USD981973S1 (en) | 2021-05-11 | 2023-03-28 | Asm Ip Holding B.V. | Reactor wall for substrate processing apparatus |

| USD1023959S1 (en) | 2021-05-11 | 2024-04-23 | Asm Ip Holding B.V. | Electrode for substrate processing apparatus |

| USD990441S1 (en) | 2021-09-07 | 2023-06-27 | Asm Ip Holding B.V. | Gas flow control plate |

| USD1099184S1 (en) | 2021-11-29 | 2025-10-21 | Asm Ip Holding B.V. | Weighted lift pin |

| USD1060598S1 (en) | 2021-12-03 | 2025-02-04 | Asm Ip Holding B.V. | Split showerhead cover |

| EP4203038A1 (en) | 2021-12-21 | 2023-06-28 | IMEC vzw | Ferroelectric device |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101001741B1 (ko) * | 2003-08-18 | 2010-12-15 | 삼성전자주식회사 | 반도체 장치의 커패시터 및 그 제조 방법과 커패시터를구비하는 메모리 장치 |

| KR100541551B1 (ko) * | 2003-09-19 | 2006-01-10 | 삼성전자주식회사 | 적어도 3층의 고유전막들을 갖는 아날로그 커패시터 및그것을 제조하는 방법 |

| DE102004043857B3 (de) * | 2004-09-10 | 2006-03-30 | Infineon Technologies Ag | DRAM-Zellenpaar und DRAM-Speicherzellenfeld mit Stack- und Trench-Speicherzellen sowie Verfahren zur Herstellung eines DRAM-Speicherzellenfeldes |

-

2006

- 2006-12-27 JP JP2006351721A patent/JP2008166360A/ja active Pending

-

2007

- 2007-10-18 KR KR1020070104883A patent/KR20080061250A/ko not_active Withdrawn

- 2007-11-15 US US11/940,667 patent/US20080157157A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| KR20080061250A (ko) | 2008-07-02 |

| US20080157157A1 (en) | 2008-07-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2008166360A (ja) | 半導体集積回路装置 | |

| US20200227423A1 (en) | Ferroelectric Devices and Methods of Forming Ferroelectric Devices | |

| US7859081B2 (en) | Capacitor, method of increasing a capacitance area of same, and system containing same | |

| US11769816B2 (en) | Ferroelectric assemblies and methods of forming ferroelectric assemblies | |

| US10685964B2 (en) | Semiconductor structure for preventing row hammering issue in DRAM cell and method for manufacturing the same | |

| TWI808570B (zh) | 半導體裝置 | |

| US6664157B2 (en) | Semiconductor integrated circuit device and the method of producing the same | |

| US12426246B2 (en) | Semiconductor structure and method for forming same | |

| KR20210050817A (ko) | 반도체 장치 및 이의 제조 방법 | |

| US11488958B2 (en) | Semiconductor device electrodes including fluorine | |

| US20220406735A1 (en) | Semiconductor device and method for manufacturing same | |

| US6235579B1 (en) | Method for manufacturing stacked capacitor | |

| US12513888B2 (en) | Memory device and manufacturing method thereof | |

| US9006906B2 (en) | DRAM cell based on conductive nanochannel plate | |

| JP2006140405A (ja) | 半導体装置及びその製造方法 | |

| US20230232607A1 (en) | Semiconductor device structure and method making the same | |

| Schroeder et al. | Materials for DRAM memory cell applications | |

| CN114284216A (zh) | 电容器阵列结构及其制造方法与半导体存储器件 | |

| KR20240016914A (ko) | 스페이서 막 방식 형태 편광 개선 | |

| CN113764419B (zh) | 半导体装置及其形成方法 | |

| CN116507117A (zh) | 半导体器件及其形成方法、存储器 | |

| US20240315007A1 (en) | Semiconductor device | |

| US12016174B2 (en) | Semiconductor device and method for forming the same | |

| US20240098976A1 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| JP2007266438A (ja) | 半導体記憶装置 |