-

Diese Erfindung betrifft eine Halbleitervorrichtung und im speziellen eine Halbleitervorrichtung mit einem Hochpotentialinselbereich (im Weiteren als ”Hochspannungs-IC” oder ”HVIC” = integrierte Hochspannungschaltung bezeichnet).

-

JP 2002-324848 A offenbart eine Technik für eine HVIC. Diese Technik verwendet einen RESURF-Effekt (REduced SURface Field/reduziertes Oberflächenfeld), um eine hohe Durchbruchspannung zu erreichen, und liefert elektrische Ladung an ein Halbleiterelement, an das durch Verwenden eines Kapazitätselements für das Halbleiterelement ein hohes Potential angelegt ist.

-

US 4 292 642 A beschreibt zum Beispiel den RESURF-Effekt. Ferner offenbart

JP 05-190693 A (1993) eine Technik des Bildens mehrerer Feldplatten, die von der Umgebung isoliert sind und ein elektrisches Feld an einer Oberfläche eines Halbleitersubstrats durch kapazitive Kopplung zwischen den Feldplatten stabilisieren.

-

Bei der in der

JP 2002-324848 A beschriebenen Technik wird das Kapazitätselement durch eine Diode geladen. Deshalb ist in dem Kapazitätselement angesammelte elektrische Ladung manchmal aufgrund eines Spannungsabfalls der Diode nicht ausreichend und die erwünschten elektrischen Eigenschaften sind manchmal abhängig von der erforderten Spezifikation einer Halbleitervorrichtung nicht erreichbar.

-

Auch ist bei der in

JP 2002-324848 A beschriebenen Technik ein p-Typ Dotierungsbereich, der ein Anodenbereich der Diode ist, in einer n-Typ Halbleiterschicht auf einem p-Typ Halbleitersubstrat ausgebildet. Deshalb bilden der p-Typ Dotierungsbereich, die n-Typ Halbleiterschicht und das p-Typ Halbleitersubstrat einen parasitären pnp-Bipolartransistor, der derart arbeitet, dass manchmal Leckverlust eines Ladestroms zu dem Kapazitätselement verursacht wird, was die gewünschten elektrischen Eigenschaften unerreichbar macht.

-

US 6 507 085 B2 beschreibt eine Halbleitervorrichtung, die eine Verringerung der Durchbruchspannung minimiert, die durch eine Metallelektrode bewirkt wird, an die eine hohe Spannung angelegt wird. Eine n

–-Halbleiterschicht ist auf einem p

–-Halbleitersubstrat gebildet. Ein p

+-Dotierungsbereich ist in der n

–-Halbleiterschicht gebildet und erstreckt sich von der Oberfläche der n

–-Halbleiterschicht bis zu der Grenzfläche zwischen der n

–-Halbleiterschicht und dem p

–-Halbleitersubstrat. Der p

+-Dotierungsbereich ist so gebildet, dass er einen Teil der n

–-Halbleiterschicht umgibt, und bildet einen Hochpotentialinselbereich, in dem eine Logikschaltung, ein n

+-Dotierungsbereich, der einen Kathodenbereich einer Bootstrap-Diode bildet, und ein p

+-Dotierungsbereich der ein Anodenberich ist, angeordnet sind.

-

DE 10 2004 022 376 A1 beschreibt eine Halbleitervorrichtung, in der ein p-leitender Fremdstoffbereich einen RESURF-Isolierbereich in einer n

–-leitenden Halbleiterschicht bildet. Eine Grabenisolierstruktur und der p-leitende Fremdstoffbereich bilden zusammen einen Gabenisolierbereich in der einer n

–-leitenden Halbleiterschicht in dem RESURF-Isolierbereich. Ein nMOS-Transistor ist in dem Grabenisolierbereich vorgesehen. Eine Steuerschaltung ist in dem RESURF-Isolierbereich außerhalb von dem Grabenisolierbereich vorgesehen. Ein n

+-leitender vergrabener Fremdstoffbereich ist an der Grenzfläche zwischen der n

–-leitenden Halbleiterschicht und einem p

–leitenden Halbleitersubstrat sowie unter einem n

+-leitenden Fremdstoffbereichvorgesehen, der mit einer Drainelektrode des nMOS-Transistors verbunden ist.

-

Es ist Aufgabe dieser Erfindung, eine Technik bereitzustellen, die geeignet ist, die elektrischen Eigenschaften einer Halbleitervorrichtung zu verbessern.

-

Die Aufgabe wird durch eine Halbleitervorrichtung gemäß Anspruch 1 gelöst. Weiterbildungen der Erfindung sind jeweils in den Unteransprüchen gekennzeichnet.

-

Das Anlegen einer Rückwärtsspannung an einen pn-Übergang, der von dem ersten Dotierungsbereich des p-Typs und der Halbleiterschicht des n-Typs gebildet ist, führt zu dem Ausbilden einer Verarmungsschicht um das Halbleiterelement herum, wodurch das Halbleiterelement geschützt wird.

-

Ferner kann ein parasitärer JFET derart ausgebildet werden, dass beide Endabschnitte der Halbleiterschicht in dem dritten Bereich als dessen Drain bzw. Source dienen, und der erste Dotierungsbereich in Kontakt mit der Halbleiterschicht in dem dritten Bereich dient als dessen Gate. Dementsprechend ermöglicht das Anlegen eines Vorwärtspotentials an die Halbleiterschicht in dem zweiten Bereich, dass das elektrisch mit der Halbleiterschicht in dem ersten Bereich verbundene Kapazitätselement durch den JFET geladen wird. Deshalb wird der Ladestrom an das Kapazitätselement geliefert, ohne durch den pn-Übergang zu gehen, was ausreichender elektrische Ladung an das Kapazitätselement liefert, als durch eine Diode. Als Ergebnis kann eine Halbleitervorrichtung mit exzellenten elektrischen Eigenschaften erhalten werden.

-

Außerdem kann, weil die Breite der Halbleiterschicht in dem dritten Bereich derart gesetzt ist, dass sie schmaler als die der Halbleiterschicht in dem ersten Bereich ist, die Breite der Halbleiterschicht in dem dritten Bereich bei dem Verbreitern der Breite der Halbleiterschicht in dem ersten Bereich zum Bilden eines Halbleiterelements mit einer großen Grundfläche auf einem kleinen Wert gehalten werden, was ermöglicht, dass eine Verarmungsschicht über fast die gesamte Halbleiterschicht in dem dritten Bereich leicht ausgebildet werden kann. Deshalb kann der Leckverlust der akkumulierten elektrischen Ladung in dem Kapazitätselement selbst dann reduziert werden, wenn, nachdem das Laden vollendet ist, das Potential an der Halbleiterschicht in dem ersten Bereich größer wird als das an der Halbleiterschicht in dem zweiten Bereich.

-

Vorzugsweise enthält die Halbleitervorrichtung weiter einen zweiten Dotierungsbereich des p-Typs und eine zweite vergrabene Dotierungsschicht des n-Typs.

-

Das Anlegen eines Vorwärtspotentials an die Halbleiterschicht in dem zweiten Bereich ermöglicht, dass der Ladestrom dem Kapazitätselement durch eine pn-Übergangs-Diode zugeführt wird, die von dem zweiten Dotierungsbereich und der damit in Kontakt stehenden Halbleiterschicht gebildet ist. Dementsprechend kann der Leckverlust der akkumulierten elektrischen Ladung in dem Kapazitätselement selbst dann reduziert werden, wenn das Potential an der Halbleiterschicht in dem ersten Bereich nach dem Laden größer wird, als das an der Halbleiterschicht in dem zweiten Bereich.

-

Ferner reduziert das Vorsehen der zweiten vergrabenen Dotierungsschicht des n-Typs mit einer höheren Dotierungskonzentration als die Halbleiterschicht den Stromverstärkungsfaktor eines parasitären pnp-Bipolartransistors, der von dem zweiten Dotierungsbereich des p-Typs, der Halbleiterschicht des n-Typs und dem Halbleitersubstrat des p-Typs gebildet ist, wodurch der durch den Betrieb des parasitären pnp-Bipolartransistors verursachte Leckverlust des Ladestroms reduziert ist. Dies verbessert die elektrischen Eigenschaften einer Halbleitervorrichtung.

-

Während das Vorsehen des zweiten vergrabenen Dotierungsbereichs des n-Typs das Ausbreiten einer Verarmungsschicht in der Halbleiterschicht in dem zweiten Bereich hindert, sind die Halbleiterschichten in dem zweiten Bereich und dem ersten Bereich durch die Halbleiterschicht in dem dritten Bereich verbunden. Die Halbleiterschicht in dem dritten Bereich kann leicht verarmt werden, da deren Breite schmaler ist, als die der Halbleiterschicht in dem ersten Bereich. Deshalb können die Halbleiterelemente zuverlässig von der Verarmungsschicht umgeben werden, wodurch eine durch Vorsehen des zweiten vergrabenen Dotierungsbereichs verursachte Reduktion der Durchbruchspannung reduziert wird.

-

Weitere Merkmale und Zweckmäßigkeiten der Erfindung ergeben sich aus der Beschreibung von Ausführungsbeispielen anhand der beigefügten Zeichnungen. Von den Figuren zeigen:

-

1 eine äquivalente Schaltung einer Halbleitervorrichtung nach einer ersten bevorzugten Ausführungsform dieser Erfindung;

-

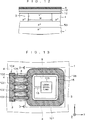

2 eine Draufsicht der Halbleitervorrichtungsstruktur nach der ersten bevorzugten Ausführungsform;

-

3 bis 5 Querschnittsansichten der Halbleitervorrichtungsstruktur nach der ersten bevorzugten Ausführungsform;

-

6 ein Schaltungsdiagramm der Halbleitervorrichtung nach der ersten bevorzugten Ausführungsform, wobei eine Spannungsquelle und ein Urladekapazitätselement direkt verbunden sind;

-

7 ein Schaltungsdiagramm der Halbleitervorrichtung nach der ersten bevorzugten Ausführungsform, wobei die Spannungsquelle und das Urladekapazitätselement durch einen Begrenzungswiderstand verbunden sind;

-

8A und 8B Illustrationen von Ladeeigenschaften beim Laden des Urladekapazitätselements;

-

9A bis 9C eine Darstellung, wie eine Verarmungsschicht ausgebildet wird;

-

10 bis 12 Querschnittsansichten einer Halbleitervorrichtungsstruktur nach einer zweiten bevorzugten Ausführungsform dieser Erfindung;

-

13 eine Draufsicht einer Halbleitervorrichtungsstruktur nach einer dritten bevorzugten Ausführungsform dieser Erfindung;

-

14 eine Querschnittsansicht der Halbleitervorrichtungsstruktur nach der dritten bevorzugten Ausführungsform;

-

15 eine Querschnittsansicht einer Struktur einer Modifikation der Halbleitervorrichtung nach der dritten bevorzugten Ausführungsform;

-

16 eine Draufsicht einer Halbleitervorrichtungsstruktur nach einer vierten bevorzugten Ausführungsform dieser Erfindung;

-

17 eine Querschnittsansicht der Halbleitervorrichtungsstruktur nach der vierten bevorzugten Ausführungsform;

-

18 eine Draufsicht einer Halbleitervorrichtungsstruktur nach einer fünften bevorzugten Ausführungsform dieser Erfindung;

-

19 bis 21 Querschnittsansichten der Halbleitervorrichtungsstruktur nach der fünften bevorzugten Ausführungsform;

-

22 eine Darstellung der Beziehung zwischen einem Anlegepotential Vg und einem Anfangsladestrom;

-

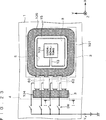

23 eine Draufsicht einer Halbleitervorrichtungsstruktur nach einer sechsten bevorzugten Ausführungsform dieser Erfindung;

-

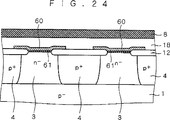

24 eine Querschnittsansicht der Halbleitervorrichtungsstruktur nach der sechsten bevorzugten Ausführungsform;

-

25 eine Draufsicht einer Halbleitervorrichtungsstruktur nach einer siebten bevorzugten Ausführungsform dieser Erfindung;

-

26 bis 28 Querschnittsansichten der Halbleitervorrichtungsstruktur nach der siebten bevorzugten Ausführungsform;

-

29 eine äquivalente Schaltung der Halbleitervorrichtung nach der siebten bevorzugten Ausführungsform;

-

30 eine Darstellung eins parasitären Bipolartransistors;

-

31 eine Draufsicht einer Halbleitervorrichtungsstruktur nach einer achten bevorzugten Ausführungsform dieser Erfindung;

-

32A bis 32C Darstellungen von Potentialsignalverläufen eines Potentials Vb, eines Potentials V0 bzw. eines Detektionssignals DS0;

-

33 eine Draufsicht einer Halbleitervorrichtungsstruktur nach einer neunten bevorzugten Ausführungsform dieser Erfindung;

-

34A bis 34C Darstellungen von Potentialsignalverläufen des Potentials Vb, des Potentials V0 bzw. eines Detektionssignals DS1.

-

Erste bevorzugte Ausführungsform

-

1 zeigt eine äquivalente Schaltung einer Halbleitervorrichtung nach einer ersten bevorzugten Ausführungsform dieser Erfindung und von deren peripheren Schaltungen. Die Halbleitervorrichtung der ersten bevorzugten Ausführungsform ist ein HVIC, das eine Logikschaltung 103, die, wie später diskutiert wird, in einem Hochpotentialinselbereich 101 ausgebildet ist, und einen n-Kanal-Typ JFET (junction FET/Übergangs-FET) 102 beinhaltet, dessen Source mit der Logikschaltung 103 verbunden ist. Die Source des JFET 102 ist zum Beispiel mit einem positiven Leistungsversorgungsanschluß der Logikschaltung 103 verbunden.

-

Das eine Ende 200a und das andere Ende 200b eines Urladekapazitätselements 200 sind mit der Logikschaltung 103 verbunden. In diesem Beispiel sind das eine Ende 200a und das andere Ende 200b mit dem positiven Leistungsversorgungsanschluß bzw. einem negativen Leistungsversorgungsanschluß der Logikschaltung 103 verbunden. Das Potential an dem einen Ende 200a wird als ein ”Potential Vb” bezeichnet.

-

Der JFET 102 weist ein mit einer Spannungsquelle 150L verbundenes Drain und ein mit einem Massepotential versorgtes Gate auf. Ferner ist eine nicht gezeigte Last mit dem anderen Ende 200b des Urladekapazitätselements 200 verbunden und das Potential an dem Knoten variiert mit den Lastbedingungen. Zum Beispiel wird das Knotenpotential ein Massepotential oder ein hohes Potential von einigen hundert Volt (im weiteren als ein ”Potential VH” bezeichnet). Es wird deshalb angenommen, wie in 1 gezeigt ist, daß eine virtuelle Spannungsquelle 150H, die eine virtuelle variable Spannungsquelle ist, mit dem anderen Ende 200b verbunden ist, und ein Ausgangspotential VS an der virtuellen Spannungsquelle 150H wird ein Massepotential oder das Potential VH.

-

Die mit dem anderen Ende 200b des Urladekapazitätselements 200 verbundene Last kann zwei IGBT beinhalten, die Totem-Poleverbunden zwischen das Potential VH und ein Massepotential geschaltet sind, wobei der Knoten zwischen jenen beiden IGBT mit dem anderen Ende 200b verbunden ist. Die zwei IGBT führen zu voneinander verschiedenen Zeiten Schaltvorgänge durch und versorgen die mit dem Knoten zwischen ihnen verbundene Last mit dem Potential VH oder einem Massepotential. Die Spannungsquelle 150L ist z. B. eine Konstantspannungsquelle mit einem Ausgangspotential VL von einigen Dutzend Volt.

-

Als nächstes wird der Betrieb der Halbleitervorrichtung nach der ersten bevorzugten Ausführungsform diskutiert. Wenn bei ungeladenem Urladekapazitätselement 200 das Ausgangspotential VS an der virtuellen Spannungsquelle 150H ein Massepotential (0V) ist, wird das Urladekapazitätselement 200 durch den JFET 102 mit der elektrischen Ladung von der Spannungsquelle 150L versorgt, so daß es geladen wird. Folglich wird die Spannung VL (= VL – 0V) in dem Urladekapazitätselement 200 akkumuliert. Währenddessen ist die Spannung VL an die Leistungsversorgung der Logikschaltung 103 angelegt, was den Betrieb der Logikschaltung 103 beeinflußt.

-

Wenn mit geladenem Urladekapazitätselement 200 das Ausgangspotential VS an der virtuellen Spannungsquelle 150H das Potential VH wird, steigt das Sourcepotential an dem JFET 102 um das Potential VH an, sodass es (VL + VH) wird, weil, wie später diskutiert wird, von der Source zu dem Drain des JFET 102 kaum ein Strom fließt. Folglich kommt die Stromversorgung von der Spannungsquelle 150L zu dem positiven Leistungsversorgungsanschluß der Logikschaltung 103 zu einem Halt und die elektrische Ladung in dem Urladekapazitätselement 200 wird an den positiven Leistungsversorgungsanschluß der Logikschaltung 103 geliefert. Das heißt, ein Potential (VL + VH) liegt an dem positiven Leistungsversorgungsanschluß der Logikschaltung 103 an und das Potential VH an dem negativen Leistungsversorgungspotential. Auf diese Weise wird immer die Spannung VL an die Leistungsversorgung der Logikschaltung 103 geliefert, was ermöglicht, daß die Logikschaltung 103 unabhängig von dem Wert des Ausgangspotentials VS an der virtuellen Spannungsquelle 150H mit einer konstanten Spannungsquelle arbeitet.

-

Als nächstes wird die Struktur der Halbleitervorrichtung nach der ersten bevorzugten Ausführungsform diskutiert. 2 ist eine schematische Draufsicht der Halbleitervorrichtungsstruktur und die 3 bis 5 sind Querschnittsansichten, die entlang den jeweiligen durch die Pfeile in 2 bezeichneten Linien A-A bis C-C genommen sind. Aus Gründen der Einfachheit ist eine Isolierschicht 8 in den 3 bis 5 nicht in 2 gezeigt, die nur die Elektroden 13 und 15 der auf einer Isolierschicht 18 ausgebildeten Elektroden zeigt. Dies trifft ebenfalls auf die folgenden Draufsichten zu.

-

In der folgenden Erklärung bezeichnen die Symbole ”p”, ”p+”, ”p–”, ”n+”, ”n–” die Dotierungsleitungstypen und Dotierungskonzentrationen der Halbleitervorrichtung. Die Dotierungskonzentration steigt in der Reihenfolge ”p–”, ”p”, ”p+” an und ist bei ”n+” größer als bei ”n–”. Ferner ist die Dotierungskonzentration bei ”p”, ”p+” größer als bei ”n–” und ist bei ”p–”, ”p” niedriger als bei ”n+”.

-

Bei der Halbleitervorrichtung der ersten bevorzugten Ausführungsform ist, wie in den 2 bis 5 gezeigt, eine n–-Halbleiterschicht 3 auf einem p–-Halbleitersubstrat 1 ausgebildet. Sich von einer oberen Oberfläche der n–-Halbleiterschicht 3 zu der Grenzfläche zwischen der n–-Halbleiterschicht 3 und dem p–-Halbleitersubstrat 1 erstreckend ist ein p+-Dotierungsbereich 4 in der n–-Halbleiterschicht 3 ausgebildet. Der p+-Dotierungsbereich 4 ist derart ausgebildet, daß er einen Teil der n–-Halbleiterschicht 3 umgibt, und definiert den Hochpotentialinselbereich 101, in dem die Logikschaltung 103 angeordnet ist, einen Niedrigpotentialinselbereich 104, an den das Ausgangspotential VL an der Spannungsquelle 150L anliegt, und einen Schlitzbereich 105 in der n–-Halbleiterschicht 3.

-

Die n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 und die n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104 sind durch die n–-Halbleiterschicht 3 in dem Schlitzbereich 105 verbunden. Anders ausgedrückt ist die n–-Halbleiterschicht 3 in dem Schlitzbereich 105 zwischen den n–-Halb-leiterschichten 3 in dem Hochpotentialinselbereich 101 und dem Niedrigpotentialinselbereich 104 angeordnet und ist mit beiden verbunden.

-

Wie in 2 gezeigt ist die n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 in Draufsicht wie ein Quadrat geformt und weist eine Mehrzahl von Seiten auf. Die n–-Halbleiterschichten 3 in dem Niedrigpotentialinselbereich 104 und dem Schlitzbereich 105 sind in Draufsicht wie ein Rechteck geformt.

-

In Draufsicht sind der Hochpotentialinselbereich 101, der Schlitzbereich 105 und der Niedrigpotentialinselbereich 104 linear in dieser Reihenfolge entlang der Richtung der X-Achse angeordnet. Und in Draufsicht ist eine Breite W der n–-Halbleiterschicht 3 in der Richtung der Y-Achse in dem Schlitzbereich 105 derart gesetzt, daß sie schmaler ist, als eine Breite HW der n–-Halbleiterschicht 3 in der Richtung der Y-Achse in dem Hochpotentialinselbereich 101. Hierbei ist die Richtung der Y-Achse senkrecht zu der Richtung der X-Achse. Deshalb können wir sagen, daß die Breite der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 in der Richtung senkrecht zu der Richtung, entlang der der Hochpotentialinselbereich 101 und der Schlitzbereich 105 angeordnet sind, schmaler ist, als die in dem Hochpotentialinselbereich 101. Die Z-Achse in 2 ist orthogonal zu der X- und der Y-Achse. Das heißt, die X-, die Y- und die Z-Achse bilden ein orthogonales Koordinatensystem.

-

Wie oben diskutiert, ist die Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 niedriger als die Breite HW der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101. Folglich kann in Draufsicht, wie in 2 gezeigt, die n–-Halbleiterschicht 3 in dem Schlitzbereich 105 teilweise mit einer Seite der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 verbunden sein.

-

An der Grenzfläche zwischen der n–-Halbleiterschicht 3 und dem p–-Halbleitersubstrat 1 in dem Hochpotentialinselbereich 101 ist selektiv ein n+-vergrabener Dotierungsbereich 2 ausgebildet. Die Logikschaltung 103 ist in der n–-Halbleiterschicht 3 oberhalb des n+-vergrabenen Dotierungsbereichs 2 ausgebildet.

-

Die Logikschaltung 103 beinhaltet zum Beispiel einen p-Kanal MOFET 130 und einen n-Kanal MOSFET 131. Der p-Kanal MOSFET 130 weist einen p+-Drainbereich 31, einen p+-Sourcebereich 32 und eine Gateelektrode 36 auf. Der Drainbereich 31 und der Sourcebereich 32 sind mit einem vorbestimmten Abstand in der oberen Oberfläche der n–-Halbleiterschicht 3 ausgebildet und die Gateelektrode 36 ist über eine Gateisolierschicht 34 auf der n–-Halbleiterschicht 3 zwischen dem Drainbereich 31 und dem Sourcebereich 32 ausgebildet. Ferner ist in der oberen Oberfläche der n–-Halbleiterschicht 3 ein n+-Dotierungsbereich 30 mit einem vorbestimmten Abstand benachbart zu dem Drainbereich 31 ausgebildet.

-

Der n-Kanal MOSFET 131 ist benachbart zu dem p-Kanal MOSFET 130 angeordnet und in einem p-Grabenbereich 20 in der oberen Oberflache der n–Halbleiterschicht 3 ausgebildet. Der n-Kanal MOSFET 131 weist einen n+-Drainbereich 23, einen Sourcebereich 22 und eine Gateelektrode 26 auf. Der Drainbereich 23 und der Sourcebereich 22 sind mit vorbestimmtem Abstand in einer oberen Oberfläche des p-Grabenbereichs 20 ausgebildet und die Gateelektrode 26 ist über eine Gateisolierschicht 24 auf dem p-Grabenbereich 20 zwischen dem Drainbereich 23 und dem Sourcebereich 22 ausgebildet. Ferner ist in der oberen Oberfläche des p-Grabenbereichs 20 ein p+-Dotierungsbereich 21 mit vorbestimmtem Abstand benachbart zu dem Sourcebereich 22 ausgebildet.

-

Ebenfalls in der oberen Oberfläche der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 ist ein n+-Dotierungsbereich 5, der n+-Dotierungsbereiche 5a und 5b beinhaltet, ausgebildet. Der n+-Dotierungsbereich 5 ist von der oberen Oberfläche der n–-Halbleiterschicht 3 bis zu dem n+-vergrabenen Dotierungsbereich 2 vorgesehen und mit der Peripherie des n+-vergrabenen Dotierungsbereichs 2 verbunden. Der n+-Dotierungsbereich 5 ist derart ausgebildet, daß er die Logikschaltung 103 umgibt. Der n+-Dotierungsbereich 5a ist in der Nähe der oberen Oberfläche der n–-Halbleiterschicht 3 ausgebildet und der n+-Dotierungsbereich 5b ist mit dem n+-Dotierungsbereich 5a verbunden und erstreckt sich zu dem n+-vergrabenen Dotierungsbereich 2.

-

Ferner ist in der oberen Oberfläche der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 ein p+-Dotierungsbereich 7 entlang dem Umfang des Hochpotentialinselbereichs 101 außerhalb des n+-Dotierungsbereichs 5 ausgebildet, der mit dem p+-Dotierungsbereich 4 verbunden ist. Der p+-Dotierungsbereich 7 ist in der n–-Halbleiterschicht 3 an der Grenze zwischen dem Hochpotentialinselbereich 101 und dem Schlitzbereich 105 nicht vorgesehen. In der oberen Oberfläche der n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104 ist ein n+-Dotierungsbereich 6 getrennt von dem p+-Dotierungsbereich 4 ausgebildet.

-

Eine Oxidschicht 12 ist auf den oberen Oberflächen der n–-Halbleiterschichten 3 in dem Hochpotentialinselbereich 101, dem Niedrigpotentialinselbereich 104 und dem Schlitzbereich 105, auf einer oberen Oberfläche des p+-Dotierungsbereichs 4 und auf der oberen Oberfläche des p-Grabenbereichs 20 derart ausgebildet, daß die n+-Dotierungsbereiche 5 und 30, die p+-Dotierungsbereiche 7 und 21, die Sourcebereiche 22 und 32, die Drainbereiche 23 und 31 und der n+-Dotierungsbereich 6 freigelegt sind. Auf der Oxidschicht 12 ist, auf der oberen Oberfläche der n–-Halbleiterschichten 3 zwischen dem n+-Dotierungsbereich 5 und dem p+-Dotierungsbereich 7 bereitgestellt, eine Mehrzahl von Elektroden 9 derart ausgebildet, daß sie den n+-Dotierungsbereich 5 und die Logikschaltung 103 in Draufsicht umgeben. Die Mehrzahl von Elektroden 9 bildet mehrere Feldplatten für eine verbesserte Durchbruchspannung der Halbleitervorrichtung der ersten bevorzugten Ausführungsform. Die Elektrode 9 sowie die Gateelektroden 26 und 36 bestehen z. B. aus Polysilizium.

-

Bei der Halbleitervorrichtung der ersten bevorzugten Ausführungsform ist die Isolierschicht 18 derart ausgebildet, daß sie die n–-Halbleiterschichten 3, die Oxidschicht 12, die Gateelektroden 26 und 36 und die Elektroden 9 bedeckt. Durch die Isolierschicht 18 hindurch sind eine Elektrode 16 mit dem n+-Dotierungsbereich 6, die Elektrode 15 mit dem n+-Dotierungsbereich 5 und eine Elektrode 17 mit dem p+-Dotierungsbereich 7 verbunden. Eine Elektrode 35 ist durch die Isolierschicht 18 hindurch mit dem Drainbereich 31, dem Sourcebereich 32 und der Gateelektrode 36 des p-Kanal MOSFET 130 und dem n+-Dotierungsbereich 30 verbunden. Eine Elektrode 25 ist durch die Isolierschicht 18 hindurch mit dem Drainbereich 23, dem Sourcebereich 22 und der Gateelektrode 26 des n-Kanal MOSFET 131 und dem p+-Dotierungsbereich 21 verbunden.

-

Die Elektrode 15 ist entlang dem n+-Dotierungsbereich 5, mit dem die Elektrode 15 selbst verbunden ist, angeordnet, so daß sie die Logikschaltung 103 in Draufsicht umgibt. Die Elektrode 15 ist durch eine Elektrode 13 mit der Elektrode 35 auf dem Drainbereich 31 und dem n+-Dotierungsbereich 30 verbunden. Die Elektrode 17 ist entlang dem p+-Dotierungsbereich 7, mit dem die Elektrode 17 selbst verbunden ist, ausgebildet, so daß sie die Logikschaltung 103 und die Elektrode 15 in Draufsicht umgibt.

-

Eine Mehrzahl von schwebenden Elektroden 10 ist auf der Isolierschicht 18 über den Elektroden 9 angeordnet und kapazitive Kopplung zwischen den Elektroden 10 und 9 verbessert die Durchbruchsspannung der Halbleitervorrichtung der ersten bevorzugten Ausführungsform. Die Isolierschicht 8 ist auf der Isolierschicht 18 derart ausgebildet, daß sie die jeweiligen Elektroden bedeckt.

-

Bei der Halbleitervorrichtung der ersten bevorzugten Ausführungsform ist der parasitäre JFET 102 derart ausgebildet, daß beide Endabschnitte in der Richtung der X-Achse der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 als dessen Source und Drain dienen und der die n–-Halbleiterschicht 3 in der Richtung der Y-Achse dazwischenliegend einschließende p+-Dotierungsbereich 4 dient als dessen Gate. Der Betrieb dieses JFET 102 ermöglicht es, daß ausreichend elektrische Ladung zu dem Urladekapazitätselement 200 geliefert wird, wie später diskutiert wird. Zwischen den beiden Endabschnitten arbeitet der eine auf der Seite des Niedrigpotentialinselbereichs 104 als das Drain des JFET 102 und der andere auf der Seite des Hochpotentialinselbereichs 101 als die Source.

-

Bei der Halbleitervorrichtung der ersten bevorzugten Ausführungsform mit der obigen Struktur wird ein Massepotential an die p+-Dotierungsbereiche 4 und 7 und das p–-Halbleitersubstrat 1 angelegt. Währenddessen wird das Ausgangspotential VL an der Spannungsquelle 150L an die Elektrode 16 angelegt, wodurch das Potential VL an die n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104 und an das Drain des JFET 102 angelegt wird.

-

Die mit dem p+-Dotierungsbereich 21 verbundene Elektrode 25 ist der negative Leistungsversorgungsanschluß der Logikschaltung 103, an den das Ausgangspotential VS an der virtuellen Spannungsquelle 150H angelegt ist. Die mit dem n+-Dotierungsbereich 30 verbundene Elektrode 35 ist der positive Leistungsversorgungsanschluß der Logikschaltung 103, der elektrisch mit dem einen Ende 200a des Urladekapazitätselements 200 verbunden ist. Entsprechend liegt das Potential Vb an dem Potential an der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 und an der Source des JFET 102 an.

-

Wenn bei ungeladenem Urladekapazitätselement 200 das Potential VS ein Massepotential ist, wird wie oben diskutiert das Urladekapazitätselement 200 durch die Spannungsquelle 150L geladen. Der Ladestrom geht durch die n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104, die n–-Halbleiterschicht 3 in dem Schlitzbereich 105, die ein Kanal des JFET 102 ist, und die n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 in dieser Reihenfolge, so daß er an das Urladekapazitätselement 200 geliefert wird.

-

Auf diese Art wird bei der ersten bevorzugten Ausführungsform der Ladestrom an das Urladekapazitätselement 200 geliefert ohne durch einen pn-Übergang zu gehen. Deshalb kann das Potential Vb auf das Ausgangspotential VL an der Spannungsquelle 150 L erhöht werden.

-

Wenn das Ausgangspotential VS an der virtuellen Spannungsquelle 150H das Potential VH wird, wird nachdem das Urladekapazitätselement 200 geladen wurde das Potential Vb zu (VL + VH). Das resultierende Anlegen einer Umkehrspannung einer Höhe von einigen hundert Volt an einen pn-Übergang, der von der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 und dem ihn in der Richtung der Y-Achse dazwischenliegend einschließenden p+-Dotierungsbereich 4 gebildet ist, führt zu dem Ausbilden einer Verarmungsschicht über fast die gesamte n–-Halbleiterschicht 3 in dem Schlitzbereich 105. Selbst wenn das Potential Vb zu (VL + VH) wird, was wie oben diskutiert höher als das Ausgangspotential VL an der Spannungsquelle 150L ist, fließt als ein Ergebnis die akkumulierte elektrische Ladung in dem Urladekapazitätselement 200 kaum in Richtung der n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104, was dem Potential Vb ermöglicht (VL + VH) zu halten. Deshalb wird zu allen Zeiten die Spannung VL an die Leistungsversorgung der Logikschaltung 103 geliefert.

-

Wenn das Ausgangspotential VS an der virtuellen Spannungsquelle 150H das Potential VH wird, wird ferner eine Umkehrspannung in der Höhe von einigen hundert Volt an einen pn-Übergang angelegt, der von der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 und dem ihn umgebenden p+-Dotierungsbereich 4 gebildet ist. Ein resultierender RESURF-Effekt führt zu dem Ausbilden einer Verarmungsschicht in der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 gegenüber der Logikschaltung 103 bezüglich des n+-Dotierungsbereichs 5, d. h. in der gesamten n–-Halbleiterschicht 3 außerhalb des n+-Dotierungsbereichs 5 in dem Hochpotentialinselbereich 101. Die Logikschaltung 103 ist folglich von der Verarmungsschicht umgeben, wodurch eine Halbleitervorrichtung mit einer hohen Durchbruchspannung erzielt wird. Ein durch die schräge Linie in 2 bezeichneter RESURF-Isolationsbereich 106 zeigt einen groben Umriß eines Bereichs, in dem die Verarmungsschicht ausgebildet wird, wenn das Ausgangspotential VS an der virtuellen Spannungsquelle 150H das Potential VH wird.

-

Bei der Halbleitervorrichtung der ersten bevorzugten Ausführungsform ist eine Schaltung (nicht gezeigt), die die Spannungsquelle 150L als deren positive Leistungsversorgung verwendet, ebenfalls in der n–-Halbleiterschicht 3 ausgebildet, die in einem anderen als dem Niedrigpotentialinselbereich 104, dem Schlitzbereich 105 und dem Hochpotentialinselbereich 101 ist und die mit diesen Bereichen durch den p+-Dotierungsbereich 4 verbunden ist. Diese Schaltung wird im weiteren als eine ”Niedrigdurchbruchsspannungschaltung” bezeichnet.

-

Bei der Halbleitervorrichtung der ersten bevorzugten Ausführungsform, bei der der parasitäre JFET 102 derart ausgebildet ist, daß beide Endabschnitte der n–-Halbleiterschicht 3 in der Richtung der X-Achse in dem Schlitzbereich 105 als dessen Source und Drain dienen, und der die n–-Halbleiterschicht 3 in der Richtung der Y-Achse dazwischen liegend anschließende p+-Dotierungsbereich 4 als dessen Gate dient, kann auf diese Art das Urladekapazitätselement 200 durch den JFET 102 geladen werden. Dementsprechend wird der Ladestrom ohne durch einen pn-Übergang zu gehen an das Urladekapazitätselement 200 geliefert, was es ermöglicht, daß ausreichendere elektrische Ladung an das Urladekapazitätselement 200 geliefert wird als durch eine Diode. Als ein Ergebnis kann eine Halbleitervorrichtung mit exzellenten elektrischen Eigenschaften erhalten werden.

-

Ferner ist bei der ersten bevorzugten Ausführungsform die Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 derart gesetzt, daß sie kleiner ist, als die Breite HW der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101. Falls umgekehrt die Breite W derart gesetzt ist, daß sie nicht kleiner als die Breite HW ist, führt das Vergrößern der Breite HW zum Ausbilden einer Logikschaltung 103 großen Ausmaßes mit einer großen Grundfläche ebenfalls zu dem Verbreitern der Breite W, was es, selbst wenn das Potential VS auf ein hohes Potential gesetzt ist, für eine Verarmungsschicht erschwert, über fast die gesamte n–Halbleiterschicht 3 in dem Schlitzbereich 105 ausgebildet zu werden. Dies erhöht die Möglichkeiten von Leckverlust der akkumulierten elektrischen Ladung in dem Urladekapazitätselement 200 in Richtung der n–-Halbleiterschicht 3 in dem Schlitzbereich 105.

-

Bei der ersten bevorzugten Ausführungsform, bei der die Breite W derart gesetzt ist, daß sie kleiner als die Breite HW ist, kann andererseits die Breite W bei dem Vergrößern der Breite HW zum Ausbilden einer Logikschaltung 103 großen Ausmaßes auf einem kleinen Wert gehalten werden, was es für eine Verarmungsschicht leicht macht, über fast die gesamte n–-Halbleiterschicht 3 in dem Schlitzbereich 105 ausgebildet zu werden. Deshalb kann der Leckverlust der akkumulierten elektrischen Ladung in dem Urladekapazitätselement 200 reduziert werden und das Potential Vb kann bei (VL + VH) gehalten werden.

-

Außerdem ist es wünschenswert, daß die Breite W der n

–-Halbleiterschicht

3 in dem Schlitzbereich

105 in dem folgenden Ausdruck (1) genügt:

-

In dem obigen Ausdruck gilt Na >> Nd, es bezeichnet die dielektrische Konstante (F/cm) des in der Halbleitervorrichtung der ersten bevorzugten Ausführungsform verwendeten Halbleiters, q bezeichnet die Einheitsladungsmenge (C), Nd bezeichnet die Dotierungskonzentration (cm–3) der n–-Halbleiterschicht 3 und Na bezeichnet die Dotierungskonzentration (cm–3) des p+-Dotierungsbereichs 4.

-

Der obige Ausdruck (1) ist ein Konditionalausdruck, bei dem der Endabschnitt auf der Drainseite der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 beim Laden des Urladekapazitätselements 200 in einen Abschnürzustand eintritt. Als ein Ergebnis arbeitet der JFET 102 als ein Strombegrenzungswiderstand gegen den Ladestrom, wodurch die für die Spannungsquelle 150L erforderlich Strombelastbarkeit reduziert werden kann. Der Grund dafür wird unten beschrieben.

-

6 zeigt ein Schaltungsdiagramm der Halbleitervorrichtung der ersten bevorzugten Ausführungsform, bei der die Spannungsquelle 150L und das Urladekapazitätselement 200 direkt ohne Vorsehen des JFET 102 verbunden sind, und 7 zeigt ein Schaltungsdiagramm, bei dem ein Strombegrenzungswiderstand 201 anstelle des JFET 102 bereitgestellt ist. Die 8A und 8B illustrieren die Ladeeigenschaften der in den 6 und 7 gezeigten Schaltungen, wobei 8A das Verhältnis zwischen einem Ladestrom I und einer Ladezeit t bezüglich des Urladekapazitätselements 200 illustriert und 8B das Verhältnis zwischen dem Potential Vb und der Ladezeit t illustriert. Der Einfachheit halber ist die Logikschaltung 103 in den 6 und 7 nicht gezeigt. Die gestrichelten Linien und durchgehenden Linien in den 8A und 8B bezeichnen die Eigenschaften der in den 6 bzw. 7 gezeigten Schaltungen.

-

Wenn die Spannungsquelle 150L und das Urladekapazitätselement 200 wie in 6 gezeigt direkt verbunden sind, ist der Ladestrom direkt nach dem Start des Ladens (im weiteren als ein ”Anfangsladestrom” bezeichnet) beachtlich groß, wie in 8A gezeigt. Deswegen muß die Spannungsquelle 150L mit einer großen Strombelastbarkeit in diesem Fall verwendet werden, um eine mögliche Reduktion in dem Ausgangspotential VL an der Spannungsquelle 150L zu verhindern, wenn der Anfangsladestrom fließt. Da das Ausgangspotential VL wie oben ausgeführt als die positive Leistungsversorgung der nicht gezeigten Niedrigdurchbruchsspannungsschaltung verwendet ist, kann dessen Reduktion fehlerhaftes Arbeiten der Niedrigdurchbruchsspannungsschaltung verursachen. Deshalb muß die Spannungsquelle 150L mit einer großen Belastbarkeit vorbereitet sein, um die Reduktion zu verhindern.

-

Wenn die Spannungsquelle 150L und das Urladekapazitätselement 200 wie in 7 gezeigt durch den Strombegrenzungswiderstand 201 verbunden sind, kann andererseits der Anfangsladestrom wie in 8A gezeigt reduziert werden. Folglich kann in diesem Fall die Spannungsquelle 150L mit einer kleineren Strombelastbarkeit verwendet werden, als wenn sie direkt verbunden sind. Das bedeutet, daß das Arbeiten des JFET 102 als ein Strombegrenzungswiderstand die Strombelastung der Spannungsquelle 150L reduzieren kann.

-

9 zeigt, wie die Verarmungsschicht in der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 beim Laden des Urladekapazitätselements 200 ausgebildet wird, wobei es sich um eine Draufsicht von oben auf die n–-Halbleiterschicht 3 handelt. 9A zeigt eine Stufe, bei der Vb = 0 V gilt, d. h. wenn das Laden zu dem Urladekapazitätselement 200 beginnt, 9B zeigt eine Stufe, bei der 0 < Vb < VL gilt, d. h. die Periode, während der das Laden beginnt und abschließt und 9C zeigt eine Stufe, bei der Vb = VL gilt, d. h. wenn das Laden abgeschlossen ist.

-

Bei dem Beginn des Ladens erstrecken sich, wie in 9A gezeigt, Verarmungsschichten 250 von dem die n–-Halbleiterschicht 3 dazwischenliegend einschließendem p+-Dotierungsbereich 4 in die Richtung der Y-Achse an dem Endabschnitt der Drainseite der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 und geraten in Kontakt zueinander, so daß in den Abschnürzustand eingetreten wird. Dies ermöglicht es dem JFET 102, am Anfang des Ladens als ein Strombegrenzungswiderstand zu arbeiten. Nachdem die elektrische Ladung in dem Urladekapazitätselement 200 akkumuliert ist und das Potential Vb ansteigt, wie in 9B gezeigt, erstrecken sich dann die Verarmungsschichten 250 auch von dem p+-Dotierungsbereich 4 an dem Endabschnitt auf der Sourceseite der n–-Halbleiterschicht 3 in dem Schlitzbereich 105.

-

Auf diese Art werden mit dem Fortschreiten des Ladens zu dem Urladekapazitätselement 200 die Verarmungsschichten 250 auch an dem Endabschnitt auf der Sourceseite der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 ausgebildet, was ein Ansteigen der Impedanz des Kanals des JFET 102 einschließt. Das Ansteigen der Impedanz beeinflußt die Ladezeit jedoch nicht besonders, weil der erforderliche Ladestrom I mit voranschreitender Ladezeit t abfällt, wie in 8A gezeigt ist.

-

Wenn Vb auf VL ansteigt, wie in 9C gezeigt, sind dann die Verarmungsschichten 250 über die gesamte n–-Halbleiterschicht 3 in dem Schlitzbereich 105 ausgebildet. Selbst wenn das Potential VS danach auf das Potential VH gesetzt wird und das Potential Vb größer als das Potential VL wird, fließt deshalb die akkumulierte elektrische Ladung in dem Urladekapazitätselement 200 kaum in Richtung der n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104, wodurch das Potential Vb zuverlässig auf (VL + VH) gehalten wird.

-

Auf diese Arten arbeitet der JFET 102 durch Setzen der Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 so als ein Strombegrenzungswiderstand, daß der Ausdruck (1) erfüllt ist, wodurch die erforderliche Strombelastbarkeit für die Spannungsquelle 150L, die ein Potential an die n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104 liefert, reduziert werden kann. Weil die n–-Halbleiterschicht 3 in dem Schlitzbereich 105 komplett mit der Verarmungsschicht bedeckt ist, wenn Vb auf VL ansteigt, kann weiterhin der Leckverlust der akkumulierten elektrischen Ladung in dem Urladekapazitätselement 200 reduziert werden und gleichzeitig zuverlässig das Potential Vb an dem einen Ende 200a des Urladekapazitätselements 200 auf das Potential VL erhöht werden.

-

Zweite bevorzugte Ausführungsform

-

Die 10 bis 12 sind Querschnittsansichten einer Halbleitervorrichtungsstruktur nach einer zweiten bevorzugten Ausführungsform dieser Erfindung. Die 10 bis 12 sind Querschnittsansichten, die entlang der in 2 durch die Pfeile bezeichneten jeweiligen Linien A-A bis C-C genommen sind. Die Halbleitervorrichtung der zweiten bevorzugten Ausführungsform ist eine Modifikation, von der der zuvor erwähnten ersten bevorzugten Ausführungsform, die im wesentlichen ferner einen p+-vergrabenen Dotierungsbereich 50 beinhaltet.

-

Wie in den 10 bis 12 gezeigt, ist der p+-vergrabene Dotierungsbereich 50 an der Grenzfläche zwischen der n–-Halbleiterschicht 3 und dem p–-Halbleitersubstrat 1 derart ausgebildet, daß der n+-vergrabene Dotierungsbereich 2 umgeben ist. Speziell ist der p+-vergrabene Dotierungsbereich 50 an der Grenzfläche zwischen der Peripherie der n–-Halbleiterschicht 3 und dem p–-Halbleitersubstrat 1 in dem Hochpotentialinselbereich 101 und an den Grenzflächen zwischen den n–-Halbleiterschichten 3 und dem p–-Halbleitersubstrat 1 ausgebildet, wobei die n–-Halbleiterschichten 3 sich in anderen als dem Hochpotentialinselbereich 101 befinden und jene in dem Niedrigpotentialinselbereich 104 und dem Schlitzbereich 105 beinhalten, so daß der vergrabene Dotierungsbereich Dotierungsbereich 2 umgeben ist. Anders als bei der ersten bevorzugten Ausführungsform ist der p+-Dotierungsbereich 4 derart ausgebildet, daß er den p+-vergrabenen Dotierungsbereich 50 erreicht. Die anderen Komponenten der Struktur sind identisch zu denen der Halbleitervorrichtung der ersten bevorzugten Ausführungsform und folglich wird deren Beschreibung unterlassen.

-

Wie oben ausgeführt, ist bei der Halbleitervorrichtung der zweiten bevorzugten Ausführungsform der p+-vergrabene Dotierungsbereich 50, der mit dem p+-Dotierungsbereich 4 verbunden ist und eine höhere Dotierungskonzentration als die n–-Halbleiterschicht 3 aufweist, an der Grenzfläche zwischen der n–-Halbleiterschicht 3 und dem p–-Halbleitersubstrats 1 in dem Schlitzbereich 105 vorgesehen. Entsprechend verursacht das Anlegen einer Umkehrspannung an einen pn-Übergang, der von dem p+-Dotierungsbereich 4, dem p+-vergrabenen Dotierungsbereich 50 und der n–-Halbleiterschicht 3 gebildet ist, daß sich Verarmungsschichten in einem großen Ausmaß in Richtung der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 sowohl von dem p+-Dotierungsbereich 4, der die n–-Halbleiterschicht 3 in der Richtung der Y-Achse dazwischenliegend einschließt, sowie von dem p+-vergrabenen Dotierungsbereich 50 erstreckt. Dies verbessert die Impedanz des Kanals des JFET 102 während des Betriebs der Halbleitervorrichtung. Deshalb kann der Leckverlust der akkumulierten elektrischen Ladung in dem Urladekapazitätselement 200, wenn das Potential Vb größer als das Potential VL wird, weiter reduziert werden.

-

Weiterhin kann der p+-Dotierungsbereich 4 der zweiten bevorzugten Ausführungsform, der derart ausgebildet ist, daß der vergrabene Dotierungsbereich Dotierungsbereich 50 erreicht wird, derart ausgebildet werden, daß er flacher diffundiert als der p+-Dotierungsbereich 4 der ersten bevorzugten Ausführungsform, der derart ausgebildet ist, daß die Grenzfläche zwischen der n–-Halbleiterschicht 3 und dem p–-Halbleitersubstrat 1 erreicht wird. Deshalb können Variationen der Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 unter einer Mehrzahl von Halbleitervorrichtungen minimiert werden.

-

Der Leckstrom der akkumulierten elektrischen Ladung in dem Urladekapazitätselement 200 kann auch in der zweiten bevorzugten Ausführungsform durch Setzen der Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105, so daß dem vorgenannten Ausdruck (1) genügt ist, weiter reduziert werden.

-

Dritte bevorzugte Ausführungsform

-

13 ist eine schematische Draufsicht einer Halbleitervorrichtungsstruktur nach einer dritten bevorzugten Ausführungsform dieser Erfindung und 14 ist eine Querschnittsansicht, die entlang der durch die Pfeile in 13 bezeichneten Linie D-D genommen ist. Die Halbleitervorrichtung der dritten bevorzugten Ausführungsform ist eine Modifikation von der der vorgenannten ersten bevorzugten Ausführungsform, die eine Mehrzahl von Schlitzbereichen 105 beinhaltet.

-

Wie in den 13 und 14 gezeigt, ist der p+-Dotierungsbereich 4 der dritten bevorzugten Ausführungsform derart ausgebildet, daß ein Teil der n–-Halbleiterschicht 3 umgeben ist, und definiert den Hochpotentialinselbereich 101, den Niedrigpotentialinselbereich 104 und die Mehrzahl von Schlitzbereichen 105. Jede der n–-Halbleiterschichten 3 in der Mehrzahl von Schlitzbereichen 105 ist zwischen den n–-Halbleiterschichten 3 in dem Hochpotentialinselbereich 101 und dem Niedrigpotentialinselbereich 104 angeordnet und ist mit beiden verbunden. Die weiteren Komponenten der Struktur sind identisch zu denen der Halbleitervorrichtung der ersten bevorzugten Ausführungsform und folglich wird deren Beschreibung ausgelassen.

-

Als solches sind in der Halbleitervorrichtung der dritten bevorzugten Ausführungsform, bei der die Mehrzahl von Schlitzbereichen 105 bereitgestellt ist, eine Mehrzahl von parasitären JFET 102 bereitgestellt. Folglich kann das Urladekapazitätselement 200 mit der Mehrzahl von parallel geschalteten JFET 102 geladen werden. Deshalb kann, selbst wenn ein ausreichender Ladestrom mit einem JFET 102 aufgrund der hohen Impedanz von dessen Kanal usw. nicht geliefert werden kann, die Mehrzahl von JFET 102 gemäß der Kapazität des Urladekapazitätselements 200 bereitgestellt sein, wodurch die Ladezeit reduziert wird.

-

Der Leckverlust der akkumulierten elektrischen Ladung in dem Urladekapazitätselement 200 kann auch in der dritten bevorzugten Ausführungsform durch Setzen der Breite W der n–-Halbleiterschicht 3 in jedem der Schlitzbereiche 105, so daß der vorgenannte Ausdruck (1) erfüllt ist, weiter reduziert werden. Es ist besonders effektiv, die Mehrzahl von JFET 102 durch Bereitstellen der Mehrzahl von Schlitzbereichen 105 wie in der dritten bevorzugten Ausführungsform zu bilden, weil in einem solchen Fall der Ladestrom zu dem Urladekapazitätselement 200 aufgrund eines Abschnüreffektes beachtlich begrenzt ist.

-

Wie die der dritten bevorzugten Ausführungsform kann die Halbleitervorrichtung der zweiten bevorzugten Ausführungsform die Mehrzahl von Schlitzbereichen 105 beinhalten. 15 ist eine Querschnittsansicht in einem solchen Fall, die entlang der durch die Pfeile in 13 gezeigten Linie D-D genommen ist.

-

Vierte bevorzugte Ausführungsform

-

16 ist eine schematische Draufsicht einer Halbleitervorrichtungsstruktur nach einer vierten bevorzugten Ausführungsform dieser Erfindung und 17 ist eine Querschnittsansicht, die entlang der durch die Pfeile in 16 bezeichneten Linie E-E genommen ist. Die Halbleitervorrichtung der vierten bevorzugten Ausführungsform ist eine Modifikation von der der vorgenannten dritten bevorzugten Ausführungsform, die im wesentlichen den Niedrigpotentialinselbereich 104 in eine Mehrzahl von Bereichen unterteilt.

-

Wie in den 16 und 17 gezeigt, ist der Niedrigpotentialinselbereich 104 der vierten bevorzugten Ausführungsform in eine Mehrzahl von geteilten Bereichen 104a unterteilt. Kurz gesagt, definiert der p+-Dotierungsbereich 4 der vierten bevorzugten Ausführungsform die Mehrzahl von geteilten Bereichen 104a in der n–-Halbleiterschicht 3. Die n–-Halbleiterschichten 3 in der Mehrzahl von geteilten Bereichen 104a sind mit den n–-Halbleiterschichten 3 in der Mehrzahl von Schlitzbereichen 105 jeweils eine mit einer verbunden. Der n+-Dotierungsbereich 6 und die Elektrode 16 sind unabhängig für jeden der geteilten Bereiche 104a bereitgestellt.

-

Ferner ist in der Halbleitervorrichtung der vierten bevorzugten Ausführungsform eine Mehrzahl von Schalterschaltungen SW bereitgestellt. Die einen Enden der Schalterschaltungen SW sind mit der Mehrzahl von Elektroden 16 jeweils eins mit einer elektrisch verbunden und deren andere Enden mit der Spannungsquelle 150L.

-

Die Schalterschaltungen SW werden zuvor in dem An-Zustand oder dem Aus-Zustand fixiert. Durch Ausbilden der Schalterschaltungen SW mit einer Mehrzahl von zu der Mehrzahl von Elektroden 16 je einer zu einer verbundenen Elektrodenanschlüssen, den Elektrodenanschlüssen mit der Spannungsquelle 150L verbunden und sie verbindende Aluminiumverdrahtungen und durch Durchführen von Verdrahtungsverbinden oder nicht in einem Aufbauprozeß kann zum Beispiel zuvor der An-/Aus-Zustand der Schalterschaltungen SW fixiert werden.

-

Alternativ kann der An-/Aus-Zustand der Schalterschaltungen SW zuvor durch Ausbilden der Schalterschaltungen SW mit einer Mehrzahl von mit der Mehrzahl von Elektroden 16 einer zu einer verbundenen Elektrodenanschlüssen, den Elektrodenanschlüssen mit der Spannungsquelle 150L verbunden und einer Mehrzahl von sie unabhängig verbindenden Verdrahtungen und durch Durchtrennen der Verdrahtungen oder nicht mit einem Laser oder ähnlichem in einem Aufbauprozeß fixiert werden.

-

Alternativ können Halbleiterschalter als die Schalterschaltungen SW angewandt werden. In diesem Fall sollte die Konfiguration derart sein, daß ein ROM in einem Wafer-Verfahren ausgebildet ist und die Halbleiterschalter durch in den ROM geschriebene Information steuerbar sind. Dann wird die An-/Aus-Information über die Halbleiterschalter in einem folgenden Testverfahren in den ROM geschrieben, wodurch der An-/Aus-Zustand von jedem der Halbleiterschalter zuvor fixiert wird. Die Schalterschaltungen SW und der ROM sind auf der vorgenannten Niedrigdurchbruchspannungsschaltung bereitgestellt. Die weiteren Komponenten der Struktur sind identisch zu denen der Halbleitervorrichtung der dritten bevorzugten Ausführungsform und folglich wird deren Beschreibung ausgelassen.

-

Auf diese Weise gibt das Vorsehen der Schalterschaltungen SW bei der Halbleitervorrichtung der vierten bevorzugten Ausführungsform, bei der der Niedrigpotentialinselbereich 104 die Mehrzahl von geteilten Bereichen 104a enthält und die n–-Halbleiter-schichten 3 in der Mehrzahl von geteilten Bereichen 104a mit den n–-Halbleiterschichten 3 in der Mehrzahl von Schlitzbereichen 105 einer zu einer verbunden sind, eine Auswahlfreiheit unter der Mehrzahl von JFET 102, die zum Laden des Urladekapazitätselements 200 in einem Verfahren verwendet werden sollen, das einem Waferverfahren z. B. in einem Aufbauverfahren oder Testverfahren folgt. Deshalb kann eine Mehrzahl von Halbleitervorrichtungen, die die Urladekapazitätselemente 200 unterstützen, die unterschiedliche Kapazitäten aufweisen, durch Verwenden desselben Waferverfahrens hergestellt werden, wodurch die Herstellungskosten reduziert werden.

-

Fünfte bevorzugte Ausführungsform

-

18 ist eine schematische Draufsicht einer Halbleitervorrichtungsstruktur nach einer fünften bevorzugten Ausführungsform dieser Erfindung. Die 19 bis 21 sind Querschnittsansichten, die entlang jeweiligen durch die Pfeile in 18 gekennzeichneten Linien F-F bis H-H genommen sind. Die Halbleitervorrichtung der fünften bevorzugten Ausführungsform ist eine Modifikation von der der vorgenannten ersten bevorzugten Ausführungsform, die im wesentlichen ferner eine Gateelektrode 60 und eine Gateisolierschicht 61 beinhaltet.

-

Wie in den 18 bis 21 gezeigt, ist die Gateisolierschicht 61, die viel dünner als die Oxidschicht 12 ist, anstelle der Oxidschicht 12 auf der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 vorgesehen und die Gateelektrode 60 ist darauf bereitgestellt. Die Gateelektrode 60 ist auch teilweise über die Oxidschicht 12 auf dem die n–-Halbleiterschicht 3 in dem Schlitzbereich 105 in der Richtung der Y-Achse dazwischenliegend einschließenden p+-Dotierungsbereich 4 vorgesehen.

-

Die Gateelektrode 60 ist zum Beispiel eine aus Polysilizium bestehende leitende Schicht. Die Gateisolierschicht 61 besteht zum Beispiel aus einer Siliziumoxidschicht. Die weiteren Komponenten der Struktur sind identisch zu jenen der Halbleitervorrichtung der ersten bevorzugten Ausführungsform und folglich wird deren Beschreibung ausgelassen.

-

In dieser Weise führt bei der Halbleitervorrichtung der fünften bevorzugten Ausführungsform, bei der die Gateelektrode 60 über die Gateisolierschicht 61 auf der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 vorgesehen ist, das Anwenden eines positiven Potentials auf die Gateelektrode 60 zu dem Ausbilden einer Akkumulationsschicht in der Nähe der oberen Oberfläche der n–-Halbleiterschicht 3 in dem Schlitzbereich 105. Dies verbessert die Mobilität der Elektronen in dem Kanal des JFET 102. Folglich steigt der Ladestrom zu dem Urladekapazitätselement 200, sodaß das Laden in einer kurzen Zeit komplettiert wird.

-

Wenn ein Anlegepotential Vg zu der Gateelektrode 60 ansteigt, wird die Mobilität von Elektronen in der n–-Halbleiterschicht 3 in dem Schlitzbereich 105 verbessert, wodurch der Anfangsladestrom ansteigt. Kurz gesagt ist der Anfangsladestrom durch das an die Gateelektrode 60 angelegte Potential Vg steuerbar. 22 zeigt die Beziehung zwischen dem Anlegepotential Vg und dem Anfangsladestrom und erklärt, daß der Anfangsladestrom ansteigt, wenn das Potential Vg zu der Gateelektrode 60 ansteigt.

-

Wenn das Laden zu dem Urladekapazitätselement 200 komplettiert ist und das Potential VS auf das Potential VH gesetzt ist, kann der Leckverlust der angesammelten elektrischen Ladung in dem Urladekapazitätselement 200 durch Anlegen eines Massepotentials an die Gateelektrode 60 reduziert werden. Während die Gateelektrode 60 auch teilweise über die Oxidschicht 12 auf dem p+-Dotierungsbereich 4 vorgesehen ist, ist es möglich durch Einstellen der Dicke der Oxidschicht 12 zu verhindern, daß eine Inversionsschicht in der Nähe der Oberfläche des p+-Dotierungsbereich 4 ausgebildet wird.

-

Die Halbleitervorrichtungen der vorgenannten dritten und vierten bevorzugten Ausführungsform können ebenfalls durch Ausbilden der Gateisolierschicht 61 auf den n–-Halbleiterschichten 3 in der Mehrzahl von Schlitzbereichen 105, Vorsehen der Gateelektrode 60 gemeinsam für die Mehrzahl von Schlitzbereichen 105 auf den Gateisolierschichten 61 und Anlegen eines positiven Potentials an die Gateelektrode 60 die Mobilität der Elektronen in dem Kanal von jedem JFET 102 verbessern, so daß ähnliche Effekte zu der Halbleitervorrichtung der fünften bevorzugten Ausführungsform erzeugt werden.

-

Sechste bevorzugte Ausführungsform

-

23 ist eine schematische Draufsicht einer Halbleitervorrichtungsstruktur nach einer sechsten bevorzugten Ausführungsform dieser Erfindung. 24 ist eine Querschnittsansicht, die entlang der durch die Pfeile in 23 bezeichneten Linie I-I genommen ist. Die Halbleitervorrichtung der sechsten bevorzugten Ausführungsform ist eine Modifikation von der der vorgenannten dritten bevorzugten Ausführungsform, die im wesentlichen die Gateelektrode 60 und die Gateisolierschicht 61 für jeden der Schlitzbereiche 105 beinhaltet.

-

Wie in den 23 und 24 gezeigt, sind Gateisolierschichten 61 voneinander getrennt auf den jeweiligen n–-Halbleiterschichten 3 in der Mehrzahl von Schlitzbereichen 105 vorgesehen und die Gateelektroden 60 sind voneinander getrennt auf den jeweiligen Gateisolierschichten 61 vorgesehen. Kurz gesagt sind die Gateelektroden 60 jeweils eine für eine entsprechend für die n–-Halb-leiterschichten 3 in der Mehrzahl von Schlitzbereichen 105 vorgesehen.

-

Die Halbleitervorrichtung der sechsten bevorzugten Ausführungsform beinhaltet ferner die vorgenannte Mehrzahl von Schalterschaltungen SW, deren eine Enden elektrisch mit der Mehrzahl von Gateelektroden 60 je eines zu einer verbunden sind und deren andere Enden mit der Spannungsquelle 150L verbunden sind. Wie bei der vierten bevorzugten Ausführungsform wird in einem Verfahren, das einem Waferverfahren folgt, z. B. in einem Aufbauverfahren oder Testverfahren, für die Mehrzahl von Schalterschaltungen SW der sechsten bevorzugten Ausführungsform unabhängig bestimmt, ob sie in dem An-Zustand oder dem Aus-Zustand sein sollen.

-

Auf diese Weise gibt bei der Halbleitervorrichtung der sechsten bevorzugten Ausführungsform, bei der die Gateelektroden 60 unabhängig durch die Gateisolierschichten 61 auf den jeweiligen n–-Halbleiterschichten 3 in der Mehrzahl von Schlitzbereichen 105 bereitgestellt sind, das Vorsehen der vorgenannten Schalterschaltungen SW in einem Verfahren, das einem Waferverfahren folgt, z. B. in einem Aufbauverfahren oder Testverfahren, die Auswahlfreiheit unter den n–-Halbleiterschichten 3 in der Mehrzahl von Schlitzbereichen 105, wo eine Akkumulationsschicht ausgebildet werden soll. Kurz gesagt kann nach einem Waferverfahren eine Entscheidung getroffen werden, in welchem JFET 102 unter der Mehrzahl von JFET 102 die Mobilität der Elektronen in dem Kanal verbessert wird. Deshalb kann eine Mehrzahl von Halbleitervorrichtungen, die die Urladekapazitätselemente 200 unterstützen, die unterschiedliche Kapazitäten aufweisen, durch Verwenden desselben Waferprozesses hergestellt werden, wodurch Herstellungskosten reduziert werden.

-

Siebte bevorzugte Ausführungsform

-

25 ist eine schematische Draufsicht einer Halbleitervorrichtungsstruktur nach einer siebten bevorzugten Ausführungsform dieser Erfindung. Die 26 bis 28 sind Querschnittsansichten, die entlang jeweiligen in 25 durch die Pfeile bezeichneten Linien J-J bis L-L genommen sind. Die Halbleitervorrichtung der siebten bevorzugten Ausführungsform ist eine Modifikation von der der vorgenannten ersten bevorzugten Ausführungsform, die einen p+-Dotierungsbereich 70 anstelle des n+-Dotierungsbereichs 6 beinhaltet und ferner einen n+-vergrabenen Dotierungsbereich 71 beinhaltet.

-

Wie in den 25 bis 28 gezeigt, ist der p+-Dotierungsbereich 70 getrennt von dem p+-Dotierungsbereich 4 in der oberen Oberfläche der n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104 vorgesehen. Die Elektrode 16 ist mit dem p+-Dotierungsbereich 70 verbunden. Der n+-vergrabene Dotierungsbereich 71 ist an der Grenzfläche zwischen der n–-Halbleiterschicht 3 und dem p–-Halbleitersubstrat 1 in dem Niedrigpotentialinselbereich 104 unterhalb des p+-Dotierungsbereichs 70 vorgesehen. Die weiteren Komponenten der Struktur sind identisch zu jenen der Halbleitervorrichtung der ersten bevorzugten Ausführungsform und folglich wird deren Beschreibung ausgelassen.

-

Wie oben diskutiert, ist bei der Halbleitervorrichtung der siebten bevorzugten Ausführungsform der p+-Dotierungsbereich 70 mit der Elektrode 16 verbunden, an die das Potential VL anliegt, in der oberen Oberfläche der n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104 vorgesehen. Folglich bilden der p+-Dotierungsbereich 70 und die damit in Kontakt stehende n–-Halbleiterschicht 3 eine pn-Übergang-Diode.

-

29 zeigt eine äquivalente Schaltung der Halbleitervorrichtung der siebten bevorzugten Ausführungsform. Wie in 29 gezeigt, bedeutet das Vorsehen des p+-Dotierungsbereichs 70 das äquivalente Einsetzen einer Diode 110 zwischen dem Drain des JFET 102 und der Spannungsquelle 150L, so daß der Ladestrom zu dem Urladekapazitätselement 200 durch die Diode 110 und den JFET 102 geliefert wird. Kurz gesagt geht der von der Spannungsquelle 150L gelieferte Ladestrom durch den p+-Dotierungsbereich 70, der ein Anodenbereich der Diode 110 ist, die n–-Halbleiterschicht 3 in dem Schlitzbereich 105 und die n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 in dieser Reihenfolge, so daß er zu dem Urladekapazitätselement 200 geliefert wird.

-

Bei der Halbleitervorrichtung der siebten bevorzugten Ausführungsform, bei der der Ladestrom zu dem Urladekapazitätselement 200 durch die Diode geliefert wird, die von dem p+-Dotierungsbereich 70 und der damit in Kontakt stehenden n–-Halbleiterschicht 3 gebildet ist, kann auf diese Weise der Leckverlust der akkumulierten elektrischen Ladung in dem Urladekapazitätselement 200 reduziert werden, selbst wenn nachdem das Laden komplettiert ist, das Potential Vb größer als das Potential VL wird.

-

Bei der Halbleitervorrichtung der siebten bevorzugten Ausführungsform, bei der der n+-vergrabene Dotierungsbereich 71 mit einer höheren Dotierungskonzentration als die n–-Halbleiterschicht 3 vorgesehen ist, kann weiterhin der durch einen in der Halbleitervorrichtung gebildeten parasitären Bipolartransistor verursachte Leckverlust reduziert werden. Dies wird unten im Detail erklärt.

-

30 zeigt den in der Halbleitervorrichtung der siebten bevorzugten Ausführungsform gebildeten parasitären Bipolartransistor und ist eine Querschnittsansicht entlang der durch die Pfeile in 25 bezeichneten Linie L-L. Aus Gründen der Einfachheit sind in 30 die Elektrode 16 und die Isolierschichten 8 und 18 nicht gezeigt.

-

Wie in 30 gezeigt, bilden der p+-Dotierungsbereich 4, die n–-Halbleiterschicht 3 und der p+-Dotierungsbereich 70 einen parasitären pnp-Bipolartransistor 160. Währenddessen bilden das p–-Halbleitersubstrat 1, die n–-Halbleiterschicht 3, der n+-vergrabene Dotierungsbereich 71 und der p+-Dotierungsbereich 70 einen parasitären pnp-Bipolartransistor 161. Die Transistoren 160 und 161 sind parallel geschaltet.

-

Bei der Halbleitervorrichtung der siebten bevorzugten Ausführungsform, bei der die obigen parasitären pnp-Bipolartransistoren 160 und 161 ausgebildet sind, wird, wenn die Transistoren 160 und 161 zum Laden des Urladekapazitätselements 200 arbeiten, ein Teil des von der Spannungsquelle 150L gelieferten Ladestroms zu Kollektorströmen der Transistoren und entweicht in Richtung des p–-Halbleitersubstrats 1, das auf ein Massepotential gesetzt ist. Deshalb müssen die Stromverstärkungsfaktoren hFE der Transistoren 160 und 161 reduziert werden, um den Leckverlust des Ladestroms zu unterdrücken.

-

Bei der siebten bevorzugten Ausführungsform, bei der der n+-vergrabene Dotierungsbereich 71 an der Grenzfläche zwischen der n–-Halbleiterschicht 3 und dem p–-Halbleitersubstrat 1 in dem Niedrigpotentialinselbereich 104 unterhalb des p+-Dotierungsbereichs 70 vorgesehen ist, steigt die Dotierungskonzentration eines Basisbereiches des parasitären pnp-Bipolartransistors 161 höher an, als wenn der Bereich 71 nicht vorgesehen ist. Dies reduziert den Stromverstärkungsfaktor hFE des Transistors 161, wodurch der Leckverlust des Ladestroms unterdrückt wird.

-

Andererseits kann der Stromverstärkungsfaktor hFE des parasitären pnp-Bipolartransistors 160 durch Vergrößern eines Abstandes L zwischen dem p+-Dotierungsbereich 4 und dem p+-Dotierungsbereich 70 reduziert werden, wie in 28 gezeigt.

-

Bei der siebten bevorzugten Ausführungsform verhindert das Vorsehen des n+-vergrabenen Dotierungsbereichs 71 das Ausbreiten einer Verarmungsschicht in der n–-Halbleiterschicht 3 in dem Niedrigpotentialinselbereich 104. Die n–-Halbleiterschichten 3 in dem Niedrigpotentialinselbereich 104 und dem Hochpotentialinselbereich 101 sind jedoch zwar nicht direkt aber doch durch die n–-Halbleiterschicht 3 in dem Schlitzbereich 105 verbunden. Diese n–-Halbleiterschicht 3 in dem Schlitzbereich 105 kann leicht verarmt werden, weil deren Breite W derart gesetzt ist, daß sie geringer als die Breite HW der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 ist. Dementsprechend kann die Logikschaltung 103 aufgrund des RESURF-Effektes zuverlässig von der Verarmungsschicht umgeben werden, wodurch eine durch das Vorsehen des n+-vergrabenen Dotierungsbereichs 7 verursachte Reduktion der Durchbruchsspannung reduziert wird.

-

Achte bevorzugte Ausführungsform

-

31 ist eine schematische Draufsicht einer Halbleitervorrichtungsstruktur nach einer achten bevorzugten Ausführungsform dieser Erfindung. Die Halbleitervorrichtung der achten bevorzugten Ausführungsform ist eine Modifikation von der der vorgenannten vierten bevorzugten Ausführungsform, die im wesentlichen nur zwei Paare, von denen jedes aus dem Schlitzbereich 105 und dem geteilten Bereich 104a besteht, und eine Detektionsschaltung 80 anstelle der Schalterschaltungen SW beinhaltet, die elektrisch mit der n–-Halbleiterschicht 3 in dem geteilten Bereich 104a eines Paares verbunden ist.

-

Wie in 31 gezeigt, sind bei der achten bevorzugten Ausführungsform zwei Schlitzbereiche 105 und zwei geteilte Bereiche 104a bereitgestellt und die n–-Halbleiterschichten 3 in den geteilten Bereichen 104a und die n–-Halbleiterschichten 3 in den Schlitzbereichen 105 sind jeweils eine zu einer verbunden. Der n+-Dotierungsbereich 6 und die Elektrode 16 sind unabhängig für jeden der geteilten Bereiche 104a bereitgestellt.

-

Bei der achten bevorzugten Ausführungsform wird das Ausgangspotential VL an der Spannungsquelle 150L an die n–-Halbleiterschicht 3 in einem der zwei geteilten Bereiche 104a durch die Elektrode 16 und den n+-Dotierungsbereich 6 angelegt, während die Detektionsschaltung 80 elektrisch mit der n–-Halbleiterschicht 3 in dem anderen geteilten Bereich 104a verbunden ist. Der eine und der andere geteilte Bereich 104a werden im weiteren als ”geteilter Bereich 104aa” bzw. ”geteilter Bereich 104ab” bezeichnet. Ferner wird der eine der Schlitzbereiche 105, der mit dem geteilten Bereich 104aa gepaart ist, als ein ”Schlitzbereich 105aa” bezeichnet und der andere mit dem geteilten Bereich 104ab gepaarte Schlitzbereich 105 als ein ”Schlitzbereich 105ab”.

-

Die Detektionsschaltung 80 detektiert ein Potential V0 an der n–-Halbleiterschicht 3 in dem geteilten Bereich 104ab und ist in der vorgenannten Niedrigdurchbruchspannungsschaltung vorgesehen. Die Detektionsschaltung 80 beinhaltet einen p-Kanal MOSFET 80p vom Anreicherungstyp, einen n-Kanal MOSFET 80n vom Anreicherungstyp und eine Schutzdiode 80d und als dessen positives Leistungsversorgungspotential ist das Potential VL angelegt.

-

Der p-Kanal MOSFET 80p und der n-Kanal MOSFET 80n bilden einen CMOS-Invertierer 80pn und das Potential VL und ein Massepotential sind an die Source des p-Kanal MOSFET 80p bzw. des n-Kanal MOSFET 80n angelegt. Die Gates des p-Kanal MOSFET 80p und des n-Kanal MOSFET 80n sind elektrisch mit der n–-Halbleiterschicht 3 in dem geteilten Bereich 104ab und ferner mit der Kathode der Schutzdiode 80d verbunden. Ein Massepotential liegt an der Anode der Schutzdiode 80d an. Die Detektionsschaltung 80 gibt das Ausgangspotential an dem CMOS-Invertierer 80pn, d. h. das Potential an den Drains des p-Kanal MOSFET 80p und des n-Kanal MOSFET 80n, die miteinander verbunden sind, als ein Detektionssignal DS0 aus.

-

Die Detektionsschaltung 80 mit der obigen Struktur gibt das Detektionssignal DS0 eines hohen Pegels aus, wenn das Potential V0 an der n–-Halbleiterschicht 3 in dem geteilten Bereich 104ab niedriger als ein Schwellenpotential Vth0 an dem CMOS-Invertierer 80pn ist, und gibt das Detektionssignal DS0 eines niedrigen Pegels aus, wenn das Potential V0 das Schwellenpotential Vth0 übersteigt.

-

Bei der achten bevorzugten Ausführungsform kann das Potential an der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101, d. h. das Potential Vb, indirekt durch Detektieren des Potentials V0 mit der Detektionsschaltung 80 detektiert werden. Dies wird unten im Detail erklärt.

-

Die 32A bis 32C zeigen Potentialsignalverläufe des Potentials Vb, des Potentials V0 bzw. des Detektionssignals DS0, 32A das Potential Vb anzeigend, 32B das Potential V0 anzeigend und 32C das Detektionssignal DS0 anzeigend. Wenn das Potential VL an die n–-Halbleiterschicht 3 in dem geteilten Bereich 104aa angelegt wird, um das Laden des Urladekapazitätselements 200 zu beginnen, steigt, wie in 32A gezeigt, das Potential Vb an. Mit dem Ansteigen des Potentials Vb wird das Potential V0, das als in einem schwebenden Zustand betrachtet werden kann, durch das Potential Vb induziert und steigt an, wie in 32B gezeigt. Dann steigt mit dem Ansteigen in den Potentialen Vb und V0 die Proportion einer Verarmungsschicht in der n–-Halbleiterschicht 3 in dem geteilten Bereich 104ab an.

-

Wenn das Laden zu dem Urladekapazitätselement 200 vervollständigt ist und Vb auf VL ansteigt, wird das Ausgangspotential VS an der virtuellen Spannungsquelle 150H auf das Potential VH gesetzt, wodurch das Potential Vb auf (VL + VH) ansteigt. Zu dieser Zeit steigt das Potential V0 dort, wo die n–-Halbleiterschicht 3 in dem geteilten Bereich 104ab komplett mit der Verarmungsschicht bedeckt ist, nur auf ein Potential VF an, das auf einige zig Volt gesetzt ist. Folglich steigt das Potential V0 nicht höher als einige zig Volt an. Der Wert des Potentials VF kann durch Variieren der Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 1058ab eingestellt werden. Beispielsweise ist das Potential VF durch Setzen der Breite W, so daß der vorgenannte Ausdruck (1) erfüllt ist, auf einige zig Volt gesetzt.

-

Auf diese Weise steigt bei der achten bevorzugten Ausführungsform das Potential V0 an, wenn das Potential Vb ansteigt und steigt nicht höher als einige zig Volt an, selbst wenn das Potential Vb einige hundert Volt wird. Deshalb kann das Potential V0 mit einer Schaltung wie der Detektionsschaltung 80, die mit einer Leistungsversorgung von einigen zig Volt arbeitet, detektiert werden.

-

Bei der Detektionsschaltung 80 ist das Schwellenpotential Vth0 an dem CMOS-Invertierer 80pn derart gesetzt, daß es niedriger als das Potential VF ist. Dementsprechend gibt, wie in 32C gezeigt, die Detektionsschaltung 80 zu Beginn des Ladens des Urladekapazitätselements 200 das Detektionssignal DS0 eines niedrigen Pegels aus und gibt das Detektionssignal DS0 eines niedrigen Pegels aus, wenn das Laden komplettiert ist und das Potential Vb ein hohes Potential wird.

-

Auf diese Weise können bei der Halbleitervorrichtung der achten bevorzugten Ausführungsform, bei der das Potential V0 an der n–-Halbleiterschicht 3 in dem geteilten Bereich 104ab mit einem Ansteigen in dem Potential Vb ansteigt, Beobachtungen der Potentialvariationen in der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 durch Detektieren des Potentials V0 gemacht werden.

-

Weil das Potential V0 aufhört anzusteigen, nachdem die Potentiale Vb und V0 ansteigen, so daß die n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab komplett verarmt wird, kann ferner, selbst wenn ein hohes Potential an die n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 anliegt, die Detektionsschaltung 80 durch angemessenes Einstellen der Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab mit einer Leistungsversorgung relativ niedrigen Potentials wie bei der achten bevorzugten Ausführungsform arbeiten. Dies reduziert das Schaltungsausmaß der gesamten Halbleitervorrichtung.

-

Weil die Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab derart gesetzt ist, daß sie geringer als die Breite HW der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 ist, kann noch ferner die Breite W bei gleichzeitigem Erhalten der Breite HW eingestellt werden. Deshalb kann das Potential V0, bei dem die gesamte n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab verarmt ist, verringert werden und dabei ein Bereich, in dem die Logikschaltung 103 auszubilden ist, bewahrt werden.

-

Weiterhin kann dank der Detektionsschaltung 80, die das Detektionssignal DS0 eines niedrigen Pegels ausgibt, wenn das Potential V0 die positive Schwellenspannung Vth0 überschreitet, eine grobe Beurteilung gemacht werden, ob das Urladekapazitätselement 200 geladen wird oder nicht.

-

Neunte bevorzugte Ausführungsform

-

33 ist eine schematische Draufsicht einer Halbleitervorrichtungsstruktur nach einer neunten bevorzugten Ausführungsform dieser Erfindung. Die Halbleitervorrichtung in der neunten bevorzugten Ausführungsform ist eine Modifikation von der der vorgenannten achten bevorzugten Ausführungsform, die eine Detektionsschaltung 81 anstelle der Detektionsschaltung 80 beinhaltet.

-

Wie in 33 gezeigt, beinhaltet die Detektionsschaltung 81 einen n-Kanal MOSFET 81n des Verarmungstyps und einen Widerstand 81r und als dessen positives Leistungsversorgungspotential liegt das Potential VL an. Der n-Kanal MOSFET 81n weist ein Drain mit dem einen Ende des Widerstands 81r verbunden und eine Source auf, an die ein Massepotential anliegt. Das Potential VL liegt an dem anderen Ende des Widerstands 81r an. Die Detektionsschaltung 81 gibt das Drainpotential des n-Kanal MOSFET 81n als ein Detektionssignal DS1 aus. Die Detektionsschaltung 81 ist ebenfalls in der vorgenannten Niedrigdurchbruchsspannungsschaltung vorgesehen.

-

Die Detektionsschaltung 81, die die obige Struktur aufweist, gibt das Detektiersignal DS1 eines niedrigen Pegels aus, wenn das Potential V0 an der n–-Halbleiterschicht 3 in dem geteilten Bereich 104ab größer als deren negatives Schwellenpotential Vth1 ist, und gibt das Detektionssignal DS1 eines hohen Pegels aus, wenn das Potential V0 niedriger ist als das Schwellenpotential Vth1.

-

Wie oben diskutiert, ist das andere Ende 200b des Urladekapazitätselements 200 zum Beispiel mit dem Knoten zwischen zwei IGBT verbunden, die zwischen dem Potential VH und einem Massepotential Totem-Pole-verbunden sind. Wenn eine Last einer Induktorkomponente mit dem Knoten verbunden ist, erzeugt ein Übergang des hochpotentialseitigen IGBT von dem An-Zustand in den Aus-Zustand zusammen mit einem Übergang des niedrigpotentialseitigen IGBT von dem An-Zustand in den Aus-Zustand aufgrund der Induktorkomponente Spitzenstörungen eines negativen Potentials an dem Knoten. Resultierendes Anlegen eines hohen negativen Potentials an das andere Ende 200b macht das Potential Vb negativ. Infolgedessen ist eine Vorwärtsspannung an einen pn-Übergang angelegt, der aus dem p–-Halbleitersubstrat 1 und der n–-Halbleiterschicht 3 gebildet ist, und ein hoher Strom geht durch das p–-Halbleitersubstrat 1 hindurch, was möglicherweise verursacht, daß die Niedrigdurchbruchsspannungsschaltung fehlerhaft arbeitet.

-

Dementsprechend muß das Anliegen eines negativen Potentials an die n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 detektiert werden, um einen Schutzvorgang an der Niedrigdurchbruchsspannungsschaltung durchzuführen. Bei der Halbleitervorrichtung der neunten bevorzugten Ausführungsform kann das Anliegen eines negativen Potentials an der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 indirekt durch Detektieren des Potentials V0 an der n–-Halbleiterschicht 3 in dem geteilten Bereich 104ab mit der Detektionsschaltung 81 detektiert werden. Dies ist unten im Detail erklärt.

-

Die 34A bis 34C zeigen Potentialsignalverläufe des Potentials Vb, des Potentials V0 bzw. des Detektionssignals DS1, 34A das Potential Vb anzeigend, 34B das Potential V0 anzeigend und 34C das Detektionssignal DS1 anzeigend. Wie in den 34A und 34B gezeigt, beginnt das Laden des Urladekapazitätselements 200 und das Potential Vb steigt an, wodurch das Potential V0 ansteigt. Dann vervollständigt das Laden und das Potential VS wird auf das Potential VH gesetzt, wodurch das Potential Vb zu (VL + VH) wird. Wie obig diskutiert, steigt zu dieser Zeit das Potential V0 nur dort auf das Potential VF an, wo die n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab komplett mit einer Verarmungsschicht bedeckt ist.

-

Zwischen den zwei mit dem anderen Ende 200b des Urladekapazitätselements 200 verbundenen IGBT reduziert ein Übergang des hochpotentialseitigen IGBT von dem An-Zustand in den Aus-Zustand zusammen mit einem Übergang des niedrigpotentialseitigen IGBT von dem Aus-Zustand in den An-Zustand das Potential VH, wodurch das Potential Vb reduziert wird. Dann wird das Potential VH aufgrund der mit den IGBT verbundenen Last der Induktorkomponente negativ, wodurch das Potential Vb ebenfalls negativ wird. Zu dieser Zeit wird, wie in 34B gezeigt, das Potential VO durch das Potential Vb induziert und wird ebenfalls negativ.

-

Wenn sich das Potential V0 negativ und niedriger als das negative Schwellenpotential Vth1 an dem n-Kanal MOSFET 81n in der Detektionsschaltung 81 erstreckt, tritt der n-Kanal MOSFET 81n in den Aus-Zustand ein und, wie in 34C gezeigt, gibt die Detektionsschaltung 81 das Detektionssignal DS1 eines hohen Pegels aus. Nachfolgend wird das Potential VH ein Massepotential, um das Potential Vb ebenfalls zu einem Massepotential zu ändern, wodurch das Potential V0 ebenfalls ein Massepotential wird. Wenn das Potential V0 ein Massepotential ist, das größer als das Schwellenpotential Vth1 an dem n-Kanal MOSFET 81n ist, dann gibt die Detektionsschaltung 81 das Detektionssignal DS1 eines niedrigen Pegels aus.

-

In dieser Weise kann bei der Halbleitervorrichtung der neunten bevorzugten Ausführungsform, bei der das Potential V0 durch das Potential an der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 induziert ist, das Anlegen eines negativen Potentials an die n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 durch Detektieren mit der Detektionsschaltung 81, ob das Potential V0 negativ ist oder nicht, detektiert werden. Deshalb kann das Anlegen der Vorwärtsspannung an den pn-Übergang, der von dem p–-Halbleitersubstrat 1 und der n–-Halbleiterschicht 3 gebildet ist, verhindert werden, wodurch eine Fehlfunktion in der Niedrigdurchbruchsspannungsschaltung verhindert wird.

-

Weil das Potential V0 nachdem die Potentiale Vb und V0 ansteigen, so daß die n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab komplett verarmt ist, aufhört anzusteigen, kann weiterhin wie bei der Halbleitervorrichtung der achten bevorzugten Ausführungsform, selbst wenn ein hohes Potential an die n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 angelegt ist, die Detektionsschaltung 81 durch angemessenes Einstellen der Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab wie bei der neunten bevorzugten Ausführungsform mit einer Leistungsversorgung eines relativ niedrigen Potentials arbeiten. Dies reduziert das Schaltungsausmaß der gesamten Halbleitervorrichtung.

-

Weil die Breite W der n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab derart gesetzt ist, daß sie geringer als die Breite HW der n–-Halbleiterschicht 3 in dem Hochpotentialinselbereich 101 ist, kann ferner weiterhin die Breite W eingestellt werden und dabei die Breite HW erhalten werden. Deshalb kann das Potential V0, bei dem die gesamte n–-Halbleiterschicht 3 in dem Schlitzbereich 105ab verarmt ist, herabgesetzt werden und dabei ein Bereich, in dem die Logikschaltung 103 auszubilden ist, erhalten werden.

-

Wie aus der obigen Diskussion klar ist, weisen die Halbleitervorrichtungen der achten und der neunten bevorzugten Ausführungsform eine Struktur auf, bei der ein Paar, das aus dem Niedrigpotentialinselbereich 104 und dem Schlitzbereich 105 besteht, und eine Detektionsschaltung zum Detektieren des Potentials V0 an der n–-Halbleiterschicht 3 in dem zusätzlich bereitgestellten Niedrigpotentialinselbereich 104 bei der Halbleitervorrichtung der ersten bevorzugten Ausführungsform bereitgestellt sind. Alternativ erzeugen die Halbleitervorrichtungen der zweiten bis siebten bevorzugten Ausführungsform durch darin Vorsehen der ähnlichen Strukturen ähnliche Effekte zu denen der Halbleitervorrichtungen der achten und neunten bevorzugten Ausführungsform.