KR20090042861A - 향상된 링크 제어를 제공하는 고속 데이터 레이트 인터페이스 - Google Patents

향상된 링크 제어를 제공하는 고속 데이터 레이트 인터페이스 Download PDFInfo

- Publication number

- KR20090042861A KR20090042861A KR1020097005776A KR20097005776A KR20090042861A KR 20090042861 A KR20090042861 A KR 20090042861A KR 1020097005776 A KR1020097005776 A KR 1020097005776A KR 20097005776 A KR20097005776 A KR 20097005776A KR 20090042861 A KR20090042861 A KR 20090042861A

- Authority

- KR

- South Korea

- Prior art keywords

- packet

- data

- client

- host

- type

- Prior art date

Links

- 230000001976 improved effect Effects 0.000 title description 4

- 238000004891 communication Methods 0.000 claims abstract description 100

- 230000006854 communication Effects 0.000 claims abstract description 100

- 238000000034 method Methods 0.000 claims description 110

- 230000004044 response Effects 0.000 claims description 98

- 230000000977 initiatory effect Effects 0.000 claims description 4

- 238000012546 transfer Methods 0.000 abstract description 53

- 230000007246 mechanism Effects 0.000 abstract description 31

- 230000002441 reversible effect Effects 0.000 description 198

- 238000012545 processing Methods 0.000 description 94

- 230000005540 biological transmission Effects 0.000 description 90

- 239000000872 buffer Substances 0.000 description 82

- 238000005259 measurement Methods 0.000 description 47

- 230000008569 process Effects 0.000 description 42

- 230000008859 change Effects 0.000 description 38

- 239000004020 conductor Substances 0.000 description 32

- 230000000875 corresponding effect Effects 0.000 description 28

- 230000007958 sleep Effects 0.000 description 28

- 238000005538 encapsulation Methods 0.000 description 26

- 230000000630 rising effect Effects 0.000 description 23

- 238000005070 sampling Methods 0.000 description 21

- 238000005516 engineering process Methods 0.000 description 17

- 238000004519 manufacturing process Methods 0.000 description 15

- 230000007704 transition Effects 0.000 description 14

- 230000008901 benefit Effects 0.000 description 12

- 230000001934 delay Effects 0.000 description 12

- 230000001360 synchronised effect Effects 0.000 description 12

- 238000013461 design Methods 0.000 description 11

- 230000033001 locomotion Effects 0.000 description 10

- 230000015654 memory Effects 0.000 description 10

- 238000003860 storage Methods 0.000 description 10

- 230000000007 visual effect Effects 0.000 description 10

- 230000000694 effects Effects 0.000 description 9

- 230000003111 delayed effect Effects 0.000 description 8

- 230000003287 optical effect Effects 0.000 description 8

- 238000010586 diagram Methods 0.000 description 7

- 238000012856 packing Methods 0.000 description 7

- 238000011084 recovery Methods 0.000 description 7

- 238000004364 calculation method Methods 0.000 description 6

- 230000000295 complement effect Effects 0.000 description 6

- 238000001514 detection method Methods 0.000 description 6

- 238000009413 insulation Methods 0.000 description 6

- 230000000737 periodic effect Effects 0.000 description 6

- 230000002457 bidirectional effect Effects 0.000 description 4

- 230000003139 buffering effect Effects 0.000 description 4

- 239000003086 colorant Substances 0.000 description 4

- 239000002131 composite material Substances 0.000 description 4

- 238000012937 correction Methods 0.000 description 4

- 230000002452 interceptive effect Effects 0.000 description 4

- 230000002829 reductive effect Effects 0.000 description 4

- 230000011664 signaling Effects 0.000 description 4

- 230000003068 static effect Effects 0.000 description 4

- 230000009471 action Effects 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 230000006399 behavior Effects 0.000 description 3

- 230000007175 bidirectional communication Effects 0.000 description 3

- 239000000945 filler Substances 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 238000003780 insertion Methods 0.000 description 3

- 230000037431 insertion Effects 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 230000005291 magnetic effect Effects 0.000 description 3

- 229920001690 polydopamine Polymers 0.000 description 3

- 230000000750 progressive effect Effects 0.000 description 3

- 230000008054 signal transmission Effects 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 101001053395 Arabidopsis thaliana Acid beta-fructofuranosidase 4, vacuolar Proteins 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000012790 confirmation Methods 0.000 description 2

- 125000004122 cyclic group Chemical group 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 230000018109 developmental process Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 238000000802 evaporation-induced self-assembly Methods 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 235000021384 green leafy vegetables Nutrition 0.000 description 2

- 230000036039 immunity Effects 0.000 description 2

- 238000010295 mobile communication Methods 0.000 description 2

- 238000003032 molecular docking Methods 0.000 description 2

- 230000036961 partial effect Effects 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 210000001747 pupil Anatomy 0.000 description 2

- 230000008439 repair process Effects 0.000 description 2

- 230000005236 sound signal Effects 0.000 description 2

- 230000008093 supporting effect Effects 0.000 description 2

- 238000012795 verification Methods 0.000 description 2

- 101001053401 Arabidopsis thaliana Acid beta-fructofuranosidase 3, vacuolar Proteins 0.000 description 1

- 238000012935 Averaging Methods 0.000 description 1

- HBBGRARXTFLTSG-UHFFFAOYSA-N Lithium ion Chemical compound [Li+] HBBGRARXTFLTSG-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- OFHCOWSQAMBJIW-AVJTYSNKSA-N alfacalcidol Chemical compound C1(/[C@@H]2CC[C@@H]([C@]2(CCC1)C)[C@H](C)CCCC(C)C)=C\C=C1\C[C@@H](O)C[C@H](O)C1=C OFHCOWSQAMBJIW-AVJTYSNKSA-N 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000004883 computer application Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000002592 echocardiography Methods 0.000 description 1

- 230000005670 electromagnetic radiation Effects 0.000 description 1

- 238000013073 enabling process Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000013467 fragmentation Methods 0.000 description 1

- 238000006062 fragmentation reaction Methods 0.000 description 1

- 230000006266 hibernation Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000009434 installation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000002372 labelling Methods 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 229910001416 lithium ion Inorganic materials 0.000 description 1

- 238000011068 loading method Methods 0.000 description 1

- 230000007787 long-term memory Effects 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 230000005055 memory storage Effects 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000007723 transport mechanism Effects 0.000 description 1

- 230000002618 waking effect Effects 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

- 230000003442 weekly effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/64—Hybrid switching systems

- H04L12/6418—Hybrid transport

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L65/00—Network arrangements, protocols or services for supporting real-time applications in data packet communication

- H04L65/1066—Session management

- H04L65/1069—Session establishment or de-establishment

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L65/00—Network arrangements, protocols or services for supporting real-time applications in data packet communication

- H04L65/1066—Session management

- H04L65/1101—Session protocols

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L65/00—Network arrangements, protocols or services for supporting real-time applications in data packet communication

- H04L65/60—Network streaming of media packets

- H04L65/61—Network streaming of media packets for supporting one-way streaming services, e.g. Internet radio

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L65/00—Network arrangements, protocols or services for supporting real-time applications in data packet communication

- H04L65/80—Responding to QoS

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/12—Protocol engines

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/18—Multiprotocol handlers, e.g. single devices capable of handling multiple protocols

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/22—Parsing or analysis of headers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/24—Negotiation of communication capabilities

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/30—Definitions, standards or architectural aspects of layered protocol stacks

- H04L69/32—Architecture of open systems interconnection [OSI] 7-layer type protocol stacks, e.g. the interfaces between the data link level and the physical level

- H04L69/322—Intralayer communication protocols among peer entities or protocol data unit [PDU] definitions

- H04L69/324—Intralayer communication protocols among peer entities or protocol data unit [PDU] definitions in the data link layer [OSI layer 2], e.g. HDLC

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/40—Network security protocols

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M1/00—Substation equipment, e.g. for use by subscribers

- H04M1/72—Mobile telephones; Cordless telephones, i.e. devices for establishing wireless links to base stations without route selection

- H04M1/724—User interfaces specially adapted for cordless or mobile telephones

- H04M1/72403—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality

- H04M1/72409—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality by interfacing with external accessories

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04W—WIRELESS COMMUNICATION NETWORKS

- H04W80/00—Wireless network protocols or protocol adaptations to wireless operation

- H04W80/02—Data link layer protocols

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M1/00—Substation equipment, e.g. for use by subscribers

- H04M1/72—Mobile telephones; Cordless telephones, i.e. devices for establishing wireless links to base stations without route selection

- H04M1/724—User interfaces specially adapted for cordless or mobile telephones

- H04M1/72403—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality

- H04M1/72409—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality by interfacing with external accessories

- H04M1/72412—User interfaces specially adapted for cordless or mobile telephones with means for local support of applications that increase the functionality by interfacing with external accessories using two-way short-range wireless interfaces

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D30/00—Reducing energy consumption in communication networks

- Y02D30/70—Reducing energy consumption in communication networks in wireless communication networks

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Multimedia (AREA)

- Computer Security & Cryptography (AREA)

- Business, Economics & Management (AREA)

- General Business, Economics & Management (AREA)

- Human Computer Interaction (AREA)

- Communication Control (AREA)

- Mobile Radio Communication Systems (AREA)

- Information Transfer Systems (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Two-Way Televisions, Distribution Of Moving Picture Or The Like (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Computer And Data Communications (AREA)

- Small-Scale Networks (AREA)

Abstract

미리-선택된 세트의 디지털 제어 및 표현 데이터를 전달하기 위한 통신 프로토콜을 형성하기 위해 함께 링크된 패킷 구조들을 사용하여 통신 경로를 통해 호스트와 클라이언트 사이에서 디지털 데이터를 전달하기 위한 데이터 인터페이스가 제시된다. 신호 프로토콜은 통신 프로토콜을 형성하는 패킷들을 생성, 전송 및 수신하고 디지털 데이터를 하나 이상의 데이터 패킷 타입들로 형성하도록 구성된 링크 제어기들에 의해 사용되며, 링크 제어기들 중 적어도 하나는 호스트 장치에 위치하며 통신 경로를 통해 클라이언트로 연결된다. 상기 인터페이스는 짧은-범위의 "직렬" 타입 데이터 링크를 통해 비용-효율적, 저전력, 양방향성 및 고속 데이터 전달 메커니즘을 제공하며, 상기 "직렬" 타입 데이터 링크는 착용가능한 마이크로-디스플레이들을 휴대용 컴퓨터들 및 무선 통신 장치들로 연결하는데 특히 유용한 소형 커넥터들과 얇고 플렉서블한 케이블들을 사용하여 구현한다.

Description

본 특허출원은 "스위칭 가능 임계 차동 인터페이스"라는 명칭으로 2003년 9월 10일자 제출된 예비 출원 60/519,833호에 대한 우선권을 주장하며, 이는 본원의 양수인에게 양도되었으며 이로써 본원에 명백히 통합된다.

본 발명의 실시예들은 호스트 장치와 클라이언트 장치 사이에 높은 데이터 전송률로 신호를 교환 또는 전송하기 위한 디지털 신호 프로토콜 및 프로세스에 관한 것이다. 보다 구체적으로, 본원은 내부 및 외부 장치 애플리케이션을 갖는 저전력 고속 데이터 전송 메커니즘을 이용하여 최종 사용자에게 프리젠테이션 또는 디스플레이하기 위해 호스트 또는 제어기 장치로부터 클라이언트 장치로 멀티미디어나 다른 종류의 디지털 신호들을 전송하기 위한 기술에 관한 것이다.

컴퓨터, 전자오락 관련 제품 및 다양한 비디오 기술(예를 들어 DVD 및 고화질 VCR)은 지난 수년간 상당히 진보하여, 어떤 종류의 텍스트를 포함하더라도 점점 더 높은 해상도의 스틸, 비디오, 주문형 비디오 및 그래픽 이미지 표현을 이러한 기기의 최종 사용자들에게 제공해왔다. 이러한 진보는 고화질 비디오 모니터, HDTV 모니터 또는 특수 이미지 프로젝션 엘리먼트와 같은 고해상도 전자 시청 장치의 사용을 요구했다. CD 타입 음향 재생, DVD, 서라운드 음향, 및 관련 오디오 신호 출력을 갖는 다른 장치들을 이용하는 경우와 같이 이러한 시각적 이미지와 고화질 또는 고품질 오디오 데이터의 결합이 사용되어 최종 사용자에게 보다 사실적이고 컨텐츠가 풍부한 또는 정확한 멀티미디어 체험을 일으킨다. 또한, 최종 사용자에 대한 오디오 전용 프리젠테이션을 위해 MP3 플레이어와 같은 고도의 이동성, 고품질 사운드 시스템 및 음악 전송 메커니즘이 개발되었다. 그 결과, 컴퓨터에서부터 텔레비전, 심지어 전화기까지 현재 익숙한 그리고 높은 또는 프리미엄급의 출력을 기대하는 시판용 전자 기기에 대한 일반 사용자들의 기대치가 증가하게 되었다.

전자공학 제품을 포함하는 통상의 비디오 프리젠테이션 시나리오에서, 비디오 데이터는 통상적으로 느린 또는 중간이라고 할 수 있는 초당 1 내지 10 킬로비트 정도의 속도로 현재의 기술을 이용하여 전송된다. 이 데이터는 원하는 시청 장치에서의 지연(나중에) 재생을 위해 버퍼링되거나 일시적인 또는 장기 메모리 장치에 저장된다. 예를 들어, 이미지들은 이미지의 디지털 표현에 유용한 데이터를 수신 또는 송신하기 위한 모뎀이나 다른 종류의 인터넷 접속 장치를 갖는 컴퓨터에 상주하는 프로그램을 이용하여 "전역으로" 또는 인터넷을 이용하여 전송될 수 있다. 무선 모뎀을 장착한 휴대용 컴퓨터나, 무선 개인 휴대 단말(PDA) 또는 무선 전화 등의 무선 장치를 이용하여 비슷한 전송이 이루어질 수 있다.

데이터가 수신되면, 재생을 위해 소형 하드드라이브 등의 내부 또는 외부 저장 장치를 포함하는, RAM이나 플레이 메모리와 같은 메모리 엘리먼트, 회로 또는 장치에 로컬 저장된다. 데이터량 및 이미지 해상도에 따라 재생은 비교적 빠르게 시작할 수도 있고 장기간 지연될 수도 있다. 즉, 어떤 경우에는 이미지 프리젠테이션은 많은 데이터를 요구하지 않는 매우 작은 또는 저해상도 이미지에 대해, 또는 어떤 종류의 버퍼링을 이용하여 약간의 지연 후 더 많은 자료가 전송되는 동안 일부 자료가 프리젠테이션되도록 어느 정도의 실시간 재생을 허용한다. 전송 링크에 인터럽트가 없거나, 사용되고 있는 전송 채널에 대한 다른 시스템이나 사용자들로부터의 간섭이 없을 경우, 프리젠테이션이 시작되면 전송은 시청 장치의 최종 사용자에게 상당히 투명하다. 물론, 다수의 사용자가 무선 인터넷 접속과 같은 단일 통신 경로를 공유하는 경우, 전송은 인터럽트될 수도 있고 원하는 것보다 느려질 수도 있다.

스틸 이미지나 모션 비디오를 생성하는데 사용되는 데이터는 흔히 통신 링크를 통한 데이터 전송 속도를 높이기 위해 JPEG(Joint Photographic Experts Group), MPEG(Motion Picture Experts Group), 및 미디어, 컴퓨터, 통신 산업에서 잘 알려진 다른 표준화 기관이나 회사에 의해 지정된 것과 같이 잘 알려진 여러 기술 중 하나를 이용하여 압축된다. 이는 소정량의 정보를 전송하는데 더 적은 수의 비트를 사용함으로써 이미지 또는 데이터 전송을 더욱 빠르게 한다.

메모리나 자기 또는 광 저장 엘리먼트 등의 저장 메커니즘을 갖는 컴퓨터와 같은 "로컬" 장치에 또는 다른 수신측 장치에 데이터가 전송되면, 결과적인 정보가 압축 해제되고(또는 특별한 디코딩 플레이어를 이용하여 재생되고), 필요하다면 디코딩되어, 해당하는 유효 프리젠테이션 해상도 및 제어 엘리먼트에 기반한 적절한 프리젠테이션이 준비된다. 예를 들어, 원하는 대로 또는 필요에 따라 다양한 다른 해상도가 가능한 것이 일반적이지만, X 대 Y 픽셀들의 스크린 해상도에 관한 통상의 컴퓨터 비디오 해상도는 통상적으로 480×640 픽셀의 낮은 해상도에서부터 600×800을 거쳐 1024×1024 범위이다.

또한, 이미지 프리젠테이션은 이미지 컨텐츠, 미리 정해진 특정 색상 레벨 또는 색상 심도(색상 생성에 사용되는 픽셀 당 비트들의 수) 및 명암의 관점에서, 이미지를 조정하는 주어진 비디오 제어기의 성능 및 사용되는 추가적인 오버헤드 비트들에 의해 영향을 받는다. 예를 들어, 다른 값들이 사용될 수도 있지만, 통상의 컴퓨터 프리젠테이션은 다양한 색상(명암 및 색조)을 표현하는데 픽셀 당 약 8 내지 32, 또는 그 이상의 비트를 예상하게 된다.

상기 값들로부터 소정의 스크린 이미지는 최저에서부터 최고의 통상 해상도 및 심도 범위에 걸쳐 각각 2.45 메가비트(Mb) 내지 약 33.55 Mb의 데이터 전송을 요구할 것을 알 수 있다. 초당 30 프레임 속도의 비디오 또는 모션 타입 이미지를 볼 때, 필요한 데이터량은 초당 약 73.7 내지 1,006 메가비트(Mbps)의 데이터, 또는 초당 약 9.21 내지 125.75 메가바이트(MBps)이다. 또한, 멀티미디어 프리젠테이션을 위해, 또는 CD 음질 음악과 같은 개별 고해상도 오디오 프리젠테이션으로서, 오디오 데이터를 이미지와 함께 프리젠테이션하는 것이 바람직할 수도 있다. 또한, 대화식 명령, 제어 또는 신호와 관계하는 추가 신호가 사용될 수도 있다. 이들 각각은 전송될 훨씬 더 많은 데이터의 추가를 옵션으로 한다. 더욱이, 고화질(HD) 텔레비전을 포함하는 더욱 새로운 전송 기술들 및 영화 레코딩은 훨씬 많은 데이터 및 제어 정보를 추가할 수 있다. 어떤 경우에도, 고품질 또는 고해상도 이미지 데이터 및 고품질 오디오 정보 또는 데이터 신호를 최종 사용자에게 전송하여 풍부한 컨텐츠 체험을 일으키는 것이 바람직할 경우, 프리젠테이션 엘리먼트와 이러한 타입의 데이터를 제공하도록 구성된 소스 또는 호스트 장치 사이에 고속 데이터 링크가 필요하다.

초당 약 115 킬로바이트(KBps) 또는 920 킬로비트(Kbps)의 데이터 전송률은 일상적으로 임의의 최신 직렬 인터페이스에 의해 처리될 수 있다. USB 직렬 인터페이스와 같은 다른 인터페이스들은 12 MBps의 높은 속도의 데이터 전송을 제공할 수 있으며, 전기 전자 학회(IEEE) 1394 표준을 이용하여 구성된 것과 같은 특수 고속 전송은 100 내지 400 MBps 정도의 속도로 일어날 수 있다. 공교롭게도, 이러한 속도는 미래의 무선 데이터 장치 및 고해상도, 풍부한 컨텐츠, 휴대용 비디오 디스플레이나 오디오 장치를 구동하기 위한 출력 신호를 제공하는 서비스에서의 사용이 기대되는 상술한 바람직한 높은 데이터 전송률에 미치지 않는다. 이는 사업용 컴퓨터 및 다른 프리젠테이션, 게임기 등을 포함한다. 추가로, 이들 인터페이스는 작동을 위해 상당량의 호스트 또는 시스템 및 클라이언트 소프트웨어의 사용을 요구한다. 또한, 이들의 소프트웨어 프로토콜 스택은 특히 이동 무선 장치나 전화 애플리케이션에서 바람직하지 않은 많은 양의 오버헤드를 생성한다. 이러한 장치는 이미 부과된 연산 용량은 물론, 엄밀한 메모리 및 전력 소비 한계를 갖는다. 더욱이, 이들 인터페이스의 일부는 비용이 추가되거나 단순히 너무 많은 전력을 소비하는 매우 심미 지향적인 모바일 애플리케이션, 복합 커넥터에는 만족스럽지 않 고 너무 무거운 큰 케이블을 이용한다.

아날로그 비디오 그래픽 어댑터(VGA), 디지털 비디오 인터랙티브(DVI) 또는 기가비트 비디오 인터페이스(GVIF)와 같은 다른 공지된 인터페이스들이 있다. 이들 중 처음 두 개는 보다 높은 전송률로 데이터를 처리하지만 무거운 케이블을 이용하고 몇 와트 정도의 상당량의 전력을 소비하는 병렬형 인터페이스이다. 이들 특성 중 어느 것도 휴대용 전자 장치에 사용할 여지가 없다. 세 번째 인터페이스 또한 너무 많은 전력을 소비하며 고가의 또는 부피가 큰 커넥터를 사용한다.

상기 인터페이스들 중 일부의 경우, 그리고 고정식 컴퓨터 기기에 대한 데이터 전송과 관련된 다른 초고속 데이터 시스템/프로토콜 또는 전송 메커니즘의 경우, 또 다른 중요한 결점이 있다. 원하는 데이터 전송률을 제공하기 위해서는 상당량의 전력 및/또는 높은 전력 레벨에서의 동작이 요구된다. 이는 매우 모바일 소비자 지향적인 제품에 대해 이러한 기술들의 유용성을 크게 감소시킨다.

일반적으로, 광섬유형 접속 및 전송 엘리먼트 등의 대안을 이용하여 이러한 데이터 전송률을 제공하기 위해서는, 사실상 민간 소비자 지향 제품에 대해 원하는 것보다 훨씬 높은 복잡도 및 비용을 유발하는 다수의 추가 변환기 및 엘리먼트를 필요로 한다. 광학 시스템의 일반적인 고가 특성은 차치하고, 그 전력 요건 및 복잡도는 경량이고 저전력인 휴대용 애플리케이션에 대한 일반적인 사용을 방해한다.

휴대용, 무선 또는 모바일 애플리케이션 산업에서 부족했던 것은 모바일 최종 사용자들에게 오디오 기반이든, 비디오 기반이든, 멀티미디어 기반이든 고품질의 프리젠테이션 체험을 제공하는 기술이다. 즉, 휴대용 컴퓨터, 무선 전화, PDA 또는 다른 이동 통신 장치나 기기를 이용할 때, 현재 사용되고 있는 비디오 및 오디오 프리젠테이션 시스템 또는 장치는 간단히 원하는 고품질 레벨로 출력을 전달할 수 없다. 흔히, 부족한 것으로 인식되는 품질은 고품질 프리젠테이션 데이터 전송에 필요한 높은 데이터 전송률을 얻기가 어렵기 때문이다. 이는 최종 사용자에게 프리젠테이션하기 위한 보다 효율적이고 진보된 또는 특징 부과된 외부 장치로의 전송, 또는 호스트와 컴퓨터, 게임기, 및 이동 전화와 같은 무선 장치 등의 휴대용 장치 내부의 클라이언트 사이의 전송을 모두 포함할 수 있다.

후자의 경우, 내부 비디오 스크린에 점점 더 높은 해상도를 부가하는데 있어서, 그리고 소위 3세대 전화와 같은 무선 장치 및 소위 랩탑 컴퓨터에 대한 다른 특수한 입력 및/또는 출력 장치 및 접속에 있어서 장족의 발전이 이루어졌다. 그러나 내부 데이터 버스 및 접속이 호스트 및/또는 각종 다른 제어 엘리먼트 및 출력 컴포넌트들이 상주하는 메인 하우징에 비디오 스크린 또는 다른 엘리먼트를 장착 또는 접속하는 회전 또는 슬라이딩 힌지나 힌지형 구조와 교차하는 브리징을 포함할 수 있다. 일례로, 무선 전화에 대해 원하는 스루풋을 얻기 위해 90개까지 또는 그 이상의 컨덕터를 필요로 할 수 있는 종래의 기술을 이용하여 높은 스루풋의 데이터 전송 인터페이스를 구성하는 것은 매우 어렵다. 이는 극복해야 하는 많은 제조, 상당한 비용 및 신뢰성 면에 있어 도전적인 이슈를 나타낸다.

이러한 이슈 및 요건은 설비나 다른 소비자 장치에 통신 또는 연산형 장치가 추가되어 진보된 데이터 용량, 인터넷 및 데이터 전송 접속 또는 내장형 엔터테인먼트를 제공하는 고정 위치 설치에서 나타나고 있다. 다른 예는 개별 비디오 및 오디오 프리젠테이션 스크린이 시트백에 장착된 비행기나 버스가 된다. 그러나 이러한 상황에서는 정보의 프리젠테이션을 위한 상호 접속 링크 또는 채널을 가진 시각적 스크린 또는 오디오 출력으로부터 거리를 두고 메인 저장, 처리 또는 통신 제어 엘리먼트를 배치하는 것이 종종 더 편리하고 효율적이며 확실히 실용적이다. 이 링크는 상술한 바와 같이 원하는 스루풋을 달성하기 위해 상당량의 데이터를 처리할 필요가 있을 것이다.

따라서 데이터를 제공하는 호스트 장치와 최종 사용자에게 출력을 제시하는 클라이언트 디스플레이 장치 또는 엘리먼트 사이의 데이터 스루풋을 증가시키기 위한 새로운 전송 메커니즘이 필요하다.

미국 특허출원 10/020,520호 및 10/236,657호에 이러한 새로운 전송 메커니즘이 제안되었으며, 상기 출원은 모두 "고속 데이터 신호 전송을 위한 통신 프로토콜 및 인터페이스 생성 및 구현"이라는 명칭으로 현재 특허되었으며, 본 발명의 양수인에게 양도되어 본원에서 참조된다. 또한, 출원 10/860,116호는 "고속 데이터용 신호 프로토콜 및 인터페이스 생성 및 구현"이라는 명칭이다. 이들 출원에 개시된 기술은 고속 데이터 신호에서 상당량의 데이터 전송 속도를 크게 향상시킬 수 있다. 그러나 데이터 전송률을 증가시키라는, 특히 비디오 프리젠테이션에 관련된 요구가 계속해서 증가하고 있다. 데이터 신호 기술에서 다른 진행중인 개발에도, 더욱 빠른 전송 속도, 개선된 통신 링크 효율 및 더욱 강력한 통신 링크를 얻으려는 노력이 여전히 필요하다. 따라서 호스트와 클라이언트 장치 사이의 데이터 스루풋 증가가 필요한 새로운 또는 개선된 전송 메커니즘을 개발하는 것이 계속해서 필요하다.

종래기술상의 상기 결점 및 다른 결점들은 호스트 장치와 수신측 클라이언트 장치 사이에 높은 데이터 전송률로 데이터를 전송하기 위한 새로운 프로토콜 및 데이터 전송 수단, 방법 및 메커니즘을 제공하는 본 발명의 실시예에 의해 해결된다.

본 발명의 실시예들은 서로 연결되어 호스트와 클라이언트 장치 간 미리 선택된 디지털 제어 및 프리젠테이션 데이터 세트를 전달하는 통신 프로토콜을 형성하는 다수의 또는 일련의 패킷 구조를 이용하는 통신 경로를 통해 호스트 장치와 클라이언트 장치 간에 고속으로 디지털 데이터를 전송하기 위한 이동 데이터 디지털 인터페이스(MDDI)에 관련된다. 신호 통신 프로토콜 또는 링크 계층이 호스트 또는 클라이언트 링크 제어기의 물리 계층에 의해 사용된다. 호스트 장치에 상주하는 적어도 하나의 링크 제어기가 통신 경로 또는 링크를 통해 클라이언트 장치에 연결되어, 통신 프로토콜을 형성하는 패킷들을 생성, 송신 및 수신하고, 디지털 프리젠테이션 데이터를 하나 이상의 타입의 데이터 패킷으로 형성하도록 구성된다. 인터페이스는 호스트와 클라이언트 사이의 양방향 정보 전송을 제공하고, 이는 공통 전체 하우징 또는 지지 구조 내에 상주할 수 있다.

디지털 CMOS 칩에 쉽게 구현될 수 있는 차동 드라이버 및 수신기를 제외하고, 구현은 본래 일반적으로 모두 디지털이고, 6개와 같이 적은 신호를 필요로 하며, 시스템 설계자에게 편리한 거의 임의의 데이터 전송률로 동작한다. 간단한 물리 및 링크 계층 프로토콜은 통합을 용이하게 하고, 이러한 단순성 및 절전 상태는 휴대용 시스템이 매우 낮은 시스템 전력 소비를 갖게 할 수 있다.

사용 및 수용에 도움이 되도록, 인터페이스는 장치 비용이 거의 추가되지 않고, 표준 배터리 전압을 이용하여 인터페이스를 통해 디스플레이에 전력을 공급하는 동안 전력 소비가 거의 없으며, 포켓용 폼-팩터를 갖는 장치를 제공할 수 있다. 인터페이스는 HDTV 이상의 해상도를 지원하도록 스케일링될 수 있고, 디스플레이 장치에 동시 스테레오 비디오 및 7.1 오디오를 지원하며, 임의의 스크린 영역에 대해 조건부 업데이트를 수행하고, 양방향으로 다중 데이터 타입을 지원한다.

본 발명의 부가적인 양상들에서, 적어도 하나의 클라이언트 링크 제어기 또는 클라이언트 수신기가 클라이언트 장치에 배치되고 통신 경로 또는 링크를 통해 호스트 장치에 연결된다. 또한, 클라이언트 링크 제어기는 통신 프로토콜을 형성하는 패킷을 생성, 송신 및 수신하고, 디지털 프리젠테이션 데이터를 하나 이상의 타입의 데이터 패킷으로 형성하도록 구성된다. 일반적으로, 호스트 또는 링크 제어기는 명령 또는 특정 타입의 신호 준비 및 문의 처리에 사용되는 데이터 패킷을 처리하기 위해 상태 머신을 이용하지만, 통신 프로토콜에 사용되는 더 적은 복합 패킷의 일부 및 데이터를 조종하기 위해 더 저속의 범용 프로세서를 사용할 수 있다. 호스트 제어기는 하나 이상의 차동 라인 드라이버를 포함하는 한편, 클라이언트 수신기는 통신 경로에 연결된 하나 이상의 차동 라인 수신기를 포함한다.

패킷은 상이한 가변 길이를 갖는 미리 결정된 개수의 패킷으로 미리 정해진 고정 길이를 가지며 호스트와 클라이언트 장치 사이에 통신하는 미디어 프레임 내에서 함께 그룹화된다. 패킷은 각각 패킷 길이 필드, 하나 이상의 패킷 데이터 필드 및 순환 중복 검사 필드를 포함한다. 서브 프레임 헤더 패킷은 호스트 링크 제 어기로부터 다른 패킷들의 최초 전송시 전송 또는 위치가 정해진다. 통신 프로토콜에 의해 하나 이상의 비디오 스트림 타입 패킷 및 오디오 스트림 타입 패킷이 사용되어 클라이언트 장치 사용자에게 프리젠테이션하기 위해 순방향 링크를 통해 호스트에서 클라이언트로 각각 비디오 타입 데이터 및 오디오 타입 데이터를 전송한다. 통신 프로토콜에 의해 하나 이상의 역방향 링크 캡슐화 타입 패킷이 사용되어 클라이언트 장치로부터 호스트 링크 제어기로 데이터를 전송한다. 일부 실시예에서의 이러한 전송은 적어도 하나의 MDDI 장치를 갖는 내부 제어기로부터 내부 비디오 스크린으로의 데이터 전송을 포함한다. 다른 실시예들은 내부 사운드 시스템으로의 전송 및 조이스틱 및 복합 키보드를 포함하는 각종 입력 장치로부터 내부 호스트 장치로의 전송을 포함한다.

호스트 링크 제어기에 의해 채움(filler) 타입 패킷이 생성되어 데이터를 갖지 않는 순방향 링크 전송 기간을 차지한다. 통신 프로토콜에 의해 다수의 다른 패킷이 사용되어 비디오 정보를 전송한다. 이러한 패킷은 컬러맵, 비트 블록 전송, 비트맵 영역 채움, 비트맵 패턴 채움 및 투명색 인에이블 타입 패킷을 포함한다. 사용자 정의 스트림 타입 패킷이 통신 프로토콜에 의해 사용되어 인터페이스-사용자 정의 데이터를 전송한다. 키보드 데이터 및 포인팅 장치 데이터 타입 패킷이 통신 프로토콜에 의해 사용되어 상기 클라이언트 장치와 관련된 사용자 입력 장치에 또는 사용자 입력 장치로부터 데이터를 전송한다. 링크 셧다운 타입 패킷이 통신 프로토콜에 의해 사용되어 상기 통신 경로를 통해 어느 한 방향으로의 데이터 전송을 종료한다.

통신 경로는 일반적으로 연속된 4개 이상의 컨덕터 및 실드를 갖는 케이블을 이용한다. 추가로, 필요에 따라 인쇄 배선 또는 컨덕터가 사용될 수 있고, 일부는 플렉서블 기판상에 상주한다.

호스트 링크 제어기는 클라이언트가 상기 인터페이스를 통해 어떤 데이터 및 데이터 전송률을 수용할 수 있는지를 결정하기 위해 상기 클라이언트로부터의 디스플레이 성능 정보를 요구한다. 클라이언트 링크 제어기는 적어도 하나의 클라이언트 성능 타입 패킷을 이용하여 호스트 링크 제어기에 디스플레이 또는 프리젠테이션 성능을 전달한다. 통신 프로토콜에 의해 다수의 전송 모드가 사용되며, 각각의 모드는 주어진 시간에 대해 상이한 최대 개수의 데이터 비트의 병렬 전송을 가능하게 하고, 각 모드는 호스트와 클라이언트 링크 제어기 사이의 협상에 의해 선택할 수 있다. 전송 모드는 데이터 전송 도중 동적으로 조정될 수 있으며, 역방향 링크에 순방향 링크에 사용된 것과 동일한 전송 모드가 사용될 필요는 없다.

본 발명의 일부 실시예의 다른 양상에 있어서, 호스트 장치는 무선 전화, 무선 PDA, 또는 무선 모뎀이 배치된 휴대용 컴퓨터 등의 무선 통신 장치를 포함한다. 통상의 클라이언트 장치는 마이크로 디스플레이 장치 및/또는 휴대용 오디오 프리젠테이션 시스템 등의 휴대용 비디오 디스플레이를 포함한다. 더욱이, 호스트는 클라이언트 장치 사용자에게 제시하기 위해 전송될 프리젠테이션 또는 멀티미디어 데이터를 저장하는 저장 수단 또는 엘리먼트를 사용할 수 있다.

일부 실시예들의 또 다른 양상에 있어서, 호스트 장치는 무선 전화, 무선 PDA 또는 휴대용 컴퓨터 등의 무선 통신 장치와 같은 휴대용 전자 장치 내에 있는 후술하는 드라이버와 함께 제어기 또는 통신 링크 제어 장치를 포함한다. 이러한 구성에서 통상의 클라이언트 장치는 호스트에 연결되며 동일 장치 내에 있는, 그리고 이동 전화의 고해상도 스크린과 같이 내부 비디오 디스플레이에 연결되는 클라이언트 회로나 집적 회로 또는 모듈, 및/또는 휴대용 오디오 프리젠테이션 시스템 또는 다른 종류의 입력 시스템 또는 장치를 포함한다.

본 발명의 각종 실시예의 구조 및 동작은 물론, 본 발명의 추가적인 특징 및 이점은 첨부 도면을 참조로 하기에 상세히 설명한다. 도면에서 동일 참조 부호는 일반적으로 동일하고 성능적으로 유사하며 그리고/또는 구조적으로 유사한 엘리먼트 또는 처리 단계들을 나타낸다.

Ⅰ. 개요

본 발명의 전체적인 목적은 후술하는 바와 같이 이동 디스플레이 디지털 인터페이스(MDDI)를 제공하는 것이며, 이는 "직렬"형 데이터 링크 또는 채널을 이용하여 호스트 장치와 디스플레이 엘리먼트와 같은 클라이언트 장치 사이의 단거리 통신 링크를 통한 고속 또는 초고속 데이터 전송을 가능하게 하는 비용 효율적이고 전력 소비가 낮은 전송 메커니즘을 제공한다. 이 메커니즘은 (하우징이나 지지 프레임의) 내부 디스플레이 엘리먼트나 입력 장치를 중앙 제어기에, 또는 착용 가능한 마이크로 디스플레이(고글이나 프로젝터)와 같은 외부 디스플레이 엘리먼트나 장치를 휴대용 컴퓨터, 무선 통신 장치 또는 엔터테인먼트 장치에 연결하는데 특히 유용한 소형 커넥터 및 얇은 플렉서블 케이블에 의한 구현에 적합하다.

이동 및 디스플레이라는 용어는 프로토콜 명칭과 관련되지만, 이는 편의상 인터페이스 및 프로토콜을 다루는 당업자들에 의해 쉽게 이해되는 표준 명칭을 갖는 것으로만 이해해야 한다. 그러나 많은 비-이동 및 비-디스플레이 관련 애플리케이션이 이 프로토콜 및 결과적인 인터페이스 구조의 적용으로부터 이익을 얻을 수 있음을 후술하는 실시예들의 검토 후 쉽게 이해될 것이며, MDDI 라벨은 본 발명 또는 그 다양한 실시예의 특성이나 유용성에 대한 어떤 제한도 갖지 않는다.

본 발명의 실시예의 이점은 복잡도가 낮고 비용이 낮으며 신뢰성이 높고 사용 환경에 잘 맞춰지며 매우 확고한 동시에 여전히 매우 융통성 있는 데이터 전송 기술이 제공된다는 점이다.

본 발명의 실시예들은 일반적으로 오디오, 비디오 또는 멀티미디어 애플리케이션을 위한 상당량의 데이터를 이러한 데이터가 생성되거나 저장되는 호스트 또는 소스 장치로부터 클라이언트 디스플레이 또는 프리젠테이션 장치로 고속으로 전달 또는 전송하는 다양한 환경에 사용될 수 있다. 후술하는 통상의 애플리케이션은 휴대용 컴퓨터나 무선 전화 또는 모뎀으로부터 소형 비디오 스크린, 또는 소형 투사 렌즈 및 스크린을 포함하는 고글이나 헬멧 형태의 착용 가능한 마이크로 디스플레이 기기와 같은 시각적 디스플레이 장치로의, 또는 호스트에서 이러한 컴포넌트들 내의 클라이언트 장치로의 데이터 전송이다. 즉, 클라이언트를 이용하는 다양한 내부 또는 외부 입력 장치로부터 내부적으로 위치하는(동일 장치 하우징 또는 지지 구조 내에 배치된) 호스트로, 그리고 프로세서로부터 내부 스크린 또는 다른 프리젠테이션 엘리먼트로의 데이터 전송이다.

MDDI의 특징 또는 속성은 이들이 특정 디스플레이 또는 프리젠테이션 기술에 무관하다는 점이다. 이는 데이터의 내부 구조는 물론 데이터가 구현하는 데이터 또는 명령들의 성능적 양상에도 무관하게 고속으로 데이터를 전송하는 매우 융통성 있는 메커니즘이다. 이는 전송되는 데이터 패킷의 타이밍이 특정 장치 고유의 디스플레이 요구에 대한 것과 같이 특정 클라이언트 장치의 특이성에 맞게, 또는 일부 A-V 시스템에 대한, 또는 조이스틱, 터치패드 등의 특정 입력 장치에 대한 조합된 오디오 및 비디오 요건을 충족하도록 조정될 수 있게 한다. 인터페이스는 선택된 프로토콜이 뒤따르는 경우, 바로 디스플레이 엘리먼트 또는 클라이언트 장치 불가지론(agnostic)이다. 추가로, 총 직렬 링크 데이터 또는 데이터 전송률은 통신 시스템 또는 호스트 장치 설계자가 비용, 전력 요건, 클라이언트 장치 복잡도 및 클라이언트 장치 업데이트 속도를 최적화할 수 있게 하는 크기의 수배에 걸쳐 달라질 수 있다.

데이터 인터페이스는 주로 "무선" 신호 링크 또는 소형 케이블을 통해 상당량의 고속 데이터를 전송하는데 사용하기 위해 제시된다. 그러나 일부 애플리케이션은 광 기반 링크를 포함하여, 인터페이스 프로토콜을 위해 개발된 동일 패킷 및 데이터 구조를 사용하도록 구성된 무선 링크를 이용할 수 있으며, 전력 소비 또는 복잡도가 여전히 현실적으로 충분히 낮게 원하는 전송 레벨을 계속할 수 있다.

Ⅱ. 환경

통상의 애플리케이션은 휴대용 또는 랩탑 컴퓨터(100) 및 무선 전화 또는 PDA 장치(102)가 오디오 재생 시스템(108, 112) 및 디스플레이 장치(104, 106)와 데이터를 교환하는 것으로 도시된 도 1a 및 도 1b에서 알 수 있다. 또한, 도 1a는 더 큰 디스플레이나 스크린(114) 또는 이미지 프로젝터(116)에 대한 잠재적 접속을 나타내며, 이는 간결성을 위해 한 도면에만 도시하였지만 무선 장치(102)에도 접속 가능하다. 무선 장치는 현재 데이터를 수신하고 있을 수도 있고 무선 장치의 최종 사용자에 의한 시청 및/또는 청취를 위한 나중의 프리젠테이션을 위해 메모리 엘리먼트나 장치에 일정량의 멀티미디어 타입 데이터를 미리 저장했을 수도 있다. 통상의 무선 장치는 대부분의 시간에 음성 및 간단한 텍스트 통신에 사용되기 때문에, 장치(102) 사용자에게 정보를 전달하기 위해 오히려 작은 디스플레이 스크린 및 간단한 오디오 시스템(스피커)을 갖는다.

컴퓨터(100)는 훨씬 큰 스크린을 갖지만, 여전히 부적합한 외부 사운드 시스템을 가지며, 고화질 텔레비전이나 영화 스크린과 같은 다른 멀티미디어 프리젠테이션 장치에 미치지 못한다. 컴퓨터(100)는 설명을 위해 사용된 것이며, 다른 종류의 프로세서, 대화식 비디오 게임 또는 소비자 전자제품이 본 발명에 사용될 수도 있다. 컴퓨터(100)는 이에 한정되는 것은 아니지만 무선 모뎀이나 다른 무선 통신용 내장 장치를 이용할 수도 있고, 또는 필요에 따라 케이블이나 무선 링크를 이용하여 이러한 장치에 접속될 수도 있다.

이는 보다 복잡한 또는 "풍부한" 데이터의 프리젠테이션을 만족시키지 못한다. 따라서 관련 산업은 최종 사용자들에게 정보를 제시하고 최소 레벨의 원하는 즐거움 또는 긍정적인 체험을 제공하기 위한 다른 메커니즘 및 장치를 개발하고 있 다.

상술한 바와 같이, 장치(100)의 최종 사용자들에게 정보를 제시하기 위해 여러 종류의 디스플레이 장치가 개발되어 왔으며 또는 현재 개발중이다. 예를 들어, 하나 이상의 회사가 장치 사용자 눈 앞에 이미지를 투사하여 시각적 디스플레이를 제시하는 착용 가능한 고글 세트를 개발했다. 이러한 장치가 정확하게 배치되면, 사용자 눈으로 인식되는 경우 시각적 출력을 제공하는 엘리먼트보다 훨씬 큰 가상 이미지를 "투사"한다. 즉, 매우 작은 투사 엘리먼트가 사용자 눈(들)이 통상의 LCD 스크린 등으로 가능한 것보다 훨씬 큰 규모로 이미지를 "볼 수 있게 한다". 또한, 더 큰 가상 스크린 이미지의 사용은 한정된 LCD 스크린 디스플레이로 가능한 것보다 훨씬 높은 해상도 이미지의 사용을 가능하게 한다. 다른 디스플레이 장치는 이에 한정되는 것은 아니지만 소형 LCD 스크린 또는 다양한 평판 디스플레이 엘리먼트, 투사 렌즈 및 표면에 이미지를 투사하는 디스플레이 드라이버 등을 포함할 수 있다.

*또한, 다른 곳에 신호를 전송하거나 이를 그 내부에 저장하는 다른 장치 또는 다른 사용자에게 출력을 제시하기 위해 무선 장치(102) 또는 컴퓨터(100)에 접속된 또는 이들의 사용과 관련된 추가 엘리먼트가 있을 수 있다. 예를 들어, 데이터는 나중에 사용하기 위해 예를 들어 쓰기 가능 CD 매체를 이용하여 플래시 메모리에 광 형태로, 또는 자기 테이프 레코더와 같은 자기 매체에 저장될 수 있다.

또한, 많은 무선 장치 및 컴퓨터는 내장형 MP3 음악 디코딩 성능 및 다른 진 보된 사운드 디코더 및 시스템을 갖는다. 휴대용 컴퓨터는 일반적으로 CD 및 DVD 재생 능력을 이용하며, 일부는 미리 녹음된 오디오 파일을 수신하는 소형 전용 플래시 메모리 판독기를 갖는다. 이러한 능력을 통해 디지털 음악 파일은 매우 증가한 특징의 풍부한 경험을 약속하지만, 디코딩 및 재생 프로세스가 유지될 수 있는 경우에만 그러하다. 이는 디지털 비디오 파일에 대해서도 사실이다.

사운드 재생을 돕기 위해, 도 1a에 외부 스피커(112)가 도시되며, 이는 서브 우퍼나 전방 및 후방 사운드 프로젝션을 위한 "서라운드 음향" 스피커와 같은 추가 엘리먼트가 동반될 수도 있다. 동시에, 스피커 또는 이어폰(108)은 도 1b의 마이크로 디스플레이 장치(106)의 지지 프레임 또는 메커니즘에 내장형으로 전용된다. 알려진 바와 같이, 전력 증폭 또는 사운드 변환 장치를 포함하는 다른 오디오 또는 사운드 재생 엘리먼트가 사용될 수 있다.

어떤 경우인든, 상술한 바와 같이 고품질 또는 고해상도 이미지 데이터 및 고품질 오디오 정보 또는 데이터 신호를 데이터 소스로부터 하나 이상의 통신 링크(110)를 통해 최종 사용자에게 전송하는 것이 바람직할 때, 높은 데이터 전송률이 요구된다. 즉, 현재 전송 메커니즘은 통상적으로 원하는 높은 데이터 전송률을 달성하지 않기 때문에, 전송 링크(100)는 상술한 바와 같이 데이터 통신에 있어 잠재적인 장애임이 명백하며, 시스템 성능을 제한하고 있다. 예를 들어, 상술한 바와 같이, 픽셀 당 24~32 비트의 색상 심도 및 30 fps의 데이터 전송률을 갖는 1024×1024 픽셀과 같이 높은 이미지 해상도에 대해, 데이터 전송률은 755 Mbps 또는 그 이상을 초과하는 속도에 가까워질 수 있다. 또한, 이러한 이미지는 오디오 데 이터 및 잠재적으로 대화식 게임 또는 통신을 다루는 추가 신호, 또는 각종 명령, 제어 또는 신호를 포함하는 멀티미디어 프리젠테이션의 일부로서 제시되어, 데이터 양 및 데이터 전송률을 더 증가시킬 수도 있다.

또한, 데이터 링크를 확립하는데 더 적은 케이블 또는 상호 접속이 요구될 수록, 디스플레이 관련 모바일 장치들의 사용이 더 용이하고 더 많은 사용자들에 의해 채택될 확률이 높아지게 된다. 이는 특히 완전한 오디오-시각적 체험을 확립하는데 다수의 장치가 공통으로 사용되는 경우에, 특히 디스플레이 및 오디오 출력 장치의 품질 레벨이 증가할 때 그러하다.

비디오 화면 및 다른 출력 또는 입력 장치에 있어서의 많은 개선과 관련된 다른 통상의 애플리케이션은 휴대용 또는 랩탑 컴퓨터(130) 및 무선 전화 또는 PDA 장치(140)가 오디오 재생 시스템(136, 146)과 함께 "내부" 디스플레이 장치(134, 144)와 각각 데이터를 통신하는 것으로 나타낸 도 1c 및 도 1d에서 알 수 있다.

도 1c 및 도 1d에서는, 오늘날 전자 산업 전반에 사용되는 일부 알려진 종류의 회전 조인트와 교차하여 하나 이상의 내부 호스트 및 제어기를 해당 클라이언트를 갖는 비디오 디스플레이 엘리먼트 또는 스크린에 연결하는 일반화된 통신 링크(여기서는 각각 138, 148)를 갖는 장치의 일 부분에서 하나 이상의 내부 호스트 및 제어기의 위치를 나타내기 위해 전체 전자 장치 또는 제품들의 작은 절단면이 사용된다. 이들 전송에 수반되는 데이터 량은 링크(138, 148)를 구성하기 위해 상당수의 컨덕터를 필요로 함을 알 수 있다. 병렬형 또는 이러한 데이터를 전송하는데 이용 가능한 다른 공지된 인터페이스 기술 때문에 이러한 장치에 진보된 컬러 및 그래픽 인터페이스, 디스플레이 엘리먼트를 이용하려는 오늘날의 성장하는 요구를 만족시키기 위해 이러한 통신 링크는 90개 또는 그 이상의 컨덕터에 이르고 있는 것으로 추정된다.

불행하게도, 이러한 높은 데이터 전송률은 단위 시간당 전송되어야 하는 원(raw) 데이터 량과 비용 효율적인 물리적 전송 메커니즘의 제조 면에서 데이터 전송에 가용한 현재의 기술을 능가한다.

프리젠테이션 엘리먼트와 데이터 소스 사이의 데이터 전송 링크 또는 통신 경로에 대해 (보다) 낮은 전력, 경량 및 가능한 한 간단하고 경제적인 케이블 구조를 가능하게 하며, 더욱 고속으로 데이터를 전송하는 기술, 구조, 수단 또는 방법이 필요하다. 출원인들은 모바일, 휴대용 또는 심지어 고정 위치 장치들의 어레이가 원하는 디스플레이, 마이크로 디스플레이 또는 오디오 전송 엘리먼트에 원하는 저전력 소비 및 복잡도를 유지하면서 매우 높은 데이터 전송률로 데이터를 전송할 수 있게 하는 목적을 달성하는 새로운 기술, 또는 방법 및 장치를 개발해왔다.

Ⅲ. 고속 디지털 데이터 인터페이스 시스템 구조

새로운 장치 인터페이스를 구성하고 효율적으로 이용하기 위해, 저전력 신호를 이용하여 매우 높은 데이터 전송률을 제공하는 신호 프로토콜 및 시스템 구조가 형성되었다. 이러한 프로토콜은 패킷 및 공통 프레임 구조, 또는 인터페이스에 부과된 명령 또는 동작 구조와 함께 미리 선택된 한 세트의 데이터 또는 데이터 타입을 교환하는 프로토콜을 형성하기 위해서 함께 연결된 구조들을 기반으로 한다.

A. 개요

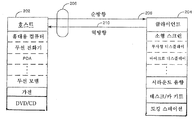

MDDI 링크에 의해 연결된 또는 MDDI 링크를 통해 통신하는 장치들은 호스트 및 클라이언트라 하며, 클라이언트는 다른 출력 및 입력 장치를 생각할 수도 있지만 통상적으로 임의의 디스플레이 장치이다. 호스트에서 디스플레이로의 데이터는 (순방향 트래픽 또는 링크라 하는) 순방향으로 이동하고, 클라이언트에서 호스트로의 데이터는 호스트에 의해 인에이블될 때 역방향(역방향 트래픽 또는 링크)으로 이동한다. 이는 도 2에 나타낸 기본 구성으로 설명된다. 도 2에서 호스트(202)는 순방향 링크(208) 및 역방향 링크(210)를 포함하는 것으로 도시된 양방향 통신 채널(206)을 이용하여 클라이언트(204)에 접속된다. 그러나 이들 채널은 순방향 또는 역방향 링크 동작 사이에 데이터 전송이 효율적으로 스위칭되는 공통 컨덕터 세트에 의해 형성된다. 이는 컨덕터 수를 매우 감소시켜, 모바일 전자 장치에 대한 저전력 환경에서의 고속 데이터 전송에 관한 현재의 접근법이 당면한 많은 문제 중 하나를 즉시 해결한다.

호스트는 본 발명을 이용하여 이익을 얻을 수 있는 여러 종류의 장치 중 하나를 포함한다. 예를 들어, 호스트(202)는 휴대형, 랩탑 또는 비슷한 이동 연산 장치 형태의 휴대용 컴퓨터일 수 있다. 또한, 개인 휴대 단말(PDA), 페이징 장치, 또는 많은 무선 전화 또는 모뎀 중 하나일 수도 있다. 대안으로, 호스트(202)는 휴대용 DVD 또는 CD 플레이어와 같은 휴대용 오락 또는 프리젠테이션 장치, 또는 게임기일 수도 있다.

또한, 호스트는 클라이언트와의 고속 통신 링크가 바람직한 다양한 그 밖의 널리 사용되는 또는 계획된 상품에서 호스트 장치 또는 제어 엘리먼트로서 존재할 수 있다. 예를 들어, 비디오 레코딩 장치로부터 개선된 응답용 저장 기반 클라이언트로, 또는 프리젠테이션용 고해상도 대형 스크린으로 데이터를 고속으로 전송하는데 호스트가 사용될 수 있다. 내장 목록 또는 연산 시스템 및/또는 블루투스 접속을 다른 가정용 장치에 통합한 냉장고 등의 가전제품은 인터넷 또는 블루투스 접속 모드로 동작할 때 디스플레이 성능을 향상시킬 수 있고, 또는 전자 컴퓨터나 제어 시스템(호스트)이 캐비넷에 있는 동안 실내 디스플레이(클라이언트) 및 키보드나 스캐너(클라이언트)에 필요한 배선을 줄일 수 있다. 일반적으로, 당업자들은 이러한 인터페이스의 사용으로부터 이익을 얻을 수 있는 광범위한 현대 전자 장치 및 가전제품들을 인식할 것이다.

동시에, 클라이언트(204)는 최종 사용자에게 정보를 제시하거나 사용자로부터 호스트로 정보를 제시하는데 유용한 다양한 장치를 포함할 수 있다. 예를 들어, 고글이나 안경에 통합된 마이크로 디스플레이, 모자나 헬멧에 설치된 투사 장치, 창이나 전면 유리와 같이 차량에 설치된 소형 스크린 또는 심지어 입체 영상 엘리먼트, 또는 각종 스피커, 헤드폰, 또는 고품질 사운드나 음악을 제공하는 사운드 시스템이 있다. 다른 프리젠테이션 장치는 미팅, 또는 영화 및 텔레비전 이미지용 정보를 제공하는데 사용되는 프로젝터나 투사 장치를 포함한다. 다른 예는 장치 또는 시스템 사용자로부터의 상당량의 정보를 사용자로부터의 터치, 음성, 또는 실제 "입력"사에 통신을 보낼 수 있는 터치 패드나 감지 장치, 음성 인식 입력 장치, 보안 스캐너 등의 사용이다. 컴퓨터용 도킹 스테이션 및 무선 전화용 카 키트 또는 데스크탑 키트 및 홀더가 최종 사용자 또는 다른 장치 및 기기에 대한 인터페이스 역할을 할 수 있으며, 클라이언트(마우스와 같은 출력 또는 입력 장치)나 호스트를 이용하여 데이터의 전송, 특별히 고속 네트워크가 수반되는 데이터 전송을 돕는다.

그러나 당업자들은 본 발명이 이들 장치에 한정되지 않으며, 저장 및 전송 면에서 또는 재생시 프리젠테이션 면에서 최종 사용자에게 고품질 이미지 및 사운드를 제공하도록 사용이 제안된 시장의 다른 많은 장치가 있음을 쉽게 인지할 것이다. 본 발명은 각종 엘리먼트 또는 장치들 간의 데이터 스루풋을 증가시켜 요구되는 사용자 체험을 실현하는데 필요한 높은 데이터 전송률을 수용하는데 유용하다.

호스트 프로세서, 제어기 또는 회로 구성요소와 장치 또는 장치 하우징 또는 구조 내의 디스플레이 사이의 상호 접속(내부 모드로 지칭함)을 간소화하기 위해 독창적인 MDD 인터페이스 및 통신 신호 프로토콜이 사용되어, 비용 또는 복잡도 및 관련 전력 및 제어 요건 또는 이들 접속의 강제를 감소시키고, 외부 엘리먼트, 장치 또는 기기에 대한 접속(외부 모드로 지칭함)뿐 아니라, 신뢰성을 향상시킬 수 있다.

이 인터페이스 구조에 의해 사용되는 각 신호 쌍에 대한 총 직렬 링크 데이터 전송률은 여러 범위에 걸쳐 달라질 수 있으며, 이는 시스템 또는 장치 설계자가 소정 애플리케이션 또는 목적에 대해 비용, 전력, 구현 복잡도 및 디스플레이 업데이트 속도를 쉽게 최적화할 수 있게 한다. MDDI의 속성은 디스플레이나 다른 프리 젠테이션 장치(타깃 클라이언트) 기술에 무관하다. 인터페이스를 통해 전송되는 데이터 패킷들의 타이밍은 디스플레이 장치, 사운드 시스템, 메모리 및 제어 엘리먼트와 같은 특정 클라이언트의 특이성, 또는 오디오-비디오 시스템의 조합 타이밍 요건에 맞게 쉽게 조정될 수 있다. 이는 시스템이 매우 적은 전력 소비를 갖게 할 수 있지만, 적어도 일정 레벨로 MDDI 프로토콜을 사용하기 위해 다양한 클라이언트가 프레임 버퍼를 가질 필요는 없다.

B. 인터페이스 타입

MDD 인터페이스는 통신 및 컴퓨터 산업에서 발견된 적어도 4개, 잠재적으로는 그 이상의 별개의 물리적 인터페이스 타입들을 다룬다. 사용되는 특정 애플리케이션 또는 관련된 산업에 따라 당업자들에 의해 다른 라벨이나 표시가 부착될 수도 있지만, 이들은 간단히 타입 1, 타입 2, 타입 3, 타입 4라 한다. 예를 들어, 간단한 오디오 시스템들은 보다 복잡한 멀티미디어 시스템보다 적은 접속을 이용하고, "채널"과 같은 특징들을 다르게 참조할 수 있다.

타입 1 인터페이스는 6-선(또는 다른 종류의 컨덕터 또는 도전 엘리먼트) 인터페이스로 구성되며, 이 인터페이스는 이동 또는 무선 전화, PDA, 전자 오락, 및 CD 플레이어나 MP3 플레이어와 같은 휴대용 미디어 플레이어, 및 이와 비슷한 장치나 비슷한 종류의 전자 소비자 기술에 사용되는 장치에 적합하다. 일 실시예에서, 인터페이스는 랩탑, 노트북 또는 데스크탑 개인용 컴퓨터 및 이와 비슷한 장치나 애플리케이션에 더욱 적합하고, 고속 데이터 업데이트를 필요로 하지 않으며, 내장 형 MDDI 링크 제어기를 갖지 않는 8-선 (컨덕터) 인터페이스로 구성될 수 있다. 이 인터페이스 타입은 추가 2-선 범용 직렬 버스(USB) 인터페이스의 사용에 의해 구별될 수도 있으며, 이는 기존의 운영 시스템 또는 대부분의 개인용 컴퓨터에서 발견되는 소프트웨어 지원을 제공하는데 매우 유용하다.

타입 2, 타입 3, 타입 4 인터페이스는 고성능 클라이언트 또는 장치에 적합하며, 추가적인 꼬임 쌍(twisted-pair) 타입의 컨덕터를 갖는 훨씬 더 복합한 배선을 이용하여 데이터 신호에 적절한 차폐 및 저손실 전송을 제공한다.

타입 1 인터페이스는 디스플레이, 오디오, 제어 및 한정된 시그널링 정보를 포함할 수 있는 신호들을 전달하고, 통상적으로 고해상도 고속 비디오 데이터를 필요로 하지 않는 모바일 클라이언트나 클라이언트 장치에 사용된다. 타입 1 인터페이스는 30 fps 및 5.1 채널 오디오의 SVGA 해상도를 쉽게 지원할 수 있으며, 최소한의 구성에서는 단지 총 3쌍의 배선, 즉 데이터 전송용 2쌍 및 전력 전송용 1쌍만을 이용할 수 있다. 이러한 타입의 인터페이스는 주로 이동 무선 장치와 같은 장치를 위한 것이며, 여기서 USB 호스트는 통상적으로 신호 접속 및 전송을 위해 이러한 장치 내에서 이용 가능하지 않다. 이러한 구성에서, 이동 무선 장치는 MDDI 호스트 장치이며, 호스트로부터의 통신 링크를 제어하는 "마스터" 역할을 하고, 일반적으로 프리젠테이션, 디스플레이 또는 재생을 위해 클라이언트에 (순방향 트래픽 또는 링크) 데이터를 전송한다.

이 인터페이스에서, 호스트는 클라이언트가 지정된 지속기간 동안 버스(링크)를 차지하여 역방향 패킷으로서 호스트로의 데이터 전송을 허용하는 특별한 명 령 또는 패킷 타입을 클라이언트로 전송함으로써 클라이언트로부터(역방향 트래픽 또는 링크) 호스트에서의 통신 데이터 수신을 인에이블 한다. 이는 도 3에 도시되어 있으며, (후술하는) 암호화 패킷이라 하는 패킷 종류가 사용되어 전송 링크를 통한 역방향 패킷 전송을 제공하여 역방향 링크를 형성한다. 데이터를 위해 클라이언트를 폴링하기 위해 호스트에 할당된 시간 간격은 호스트에 의해 미리 결정되며, 각 지정된 애플리케이션의 요건에 기반한다. 클라이언트로부터의 정보 또는 데이터 전송에 USB 포트를 이용할 수 없는 경우에 이러한 종류의 반이중 양방향 데이터 전송이 특별히 유리하다.

HDTV형 또는 고해상도가 가능한 고성능 디스플레이는 풀 모션 비디오를 지원하기 위해 약 1.5 Gbps 속도의 데이터 스트림을 필요로 한다. 타입 2 인터페이스는 병렬로 2비트를 전송함으로써, 타입 3 인터페이스는 병렬로 4비트를 전송함으로써, 타입 4 인터페이스는 8비트를 병렬로 전송함으로써, 고속 데이터 전송률을 지원한다. 타입 2 및 타입 3 인터페이스는 타입 1과 동일한 케이블 및 커넥터를 사용하지만, 2배 및 4배의 데이터 전송률로 동작하여 휴대용 장치에 보다 고성능의 비디오 애플리케이션을 지원할 수 있다. 타입 4 인터페이스는 초고성능 클라이언트 또는 디스플레이에 적합하며, 추가적인 꼬임 쌍 데이터 신호를 포함하는 약간 더 큰 케이블을 필요로 한다.

MDDI에 의해 사용되는 프로토콜은 사용될 수 있는 가능한 최고 데이터 전송률이 얼마인지를 협의함으로써 각각 타입 1, 2, 3 또는 4 호스트가 일반적으로 타입 1, 2, 3 또는 4 클라이언트와 통신할 수 있게 한다. 최소 가능 장치로 지칭될 수 있는 가용한 특징들 또는 성능은 링크 성능을 설정하는데 사용된다. 원칙적으로, 호스트 및 클라이언트 모두 타입 2, 타입 3 또는 타입 4 인터페이스를 이용할 수 있는 시스템이라 하더라도, 모두 타입 1 인터페이스로서 동작을 시작한다. 이어서 호스트는 타깃 클라이언트의 성능을 결정하고, 특정 애플리케이션에 적절하게 타입 2, 타입 3 또는 타입 4 모드로의 핸드오프 또는 재구성 동작을 협의한다.

일반적으로, 호스트는 (후술하는) 적절한 링크 계층 프로토콜을 사용하고 일반적으로 임의의 시간에 전력을 절약하기 위해 저속 모드로 전력을 낮추거나 다시 동작을 재구성하고, 또는 더 높은 해상도의 디스플레이 컨텐츠에 대한 보다 고속의 전송을 지원하는 고속 모드로 전력을 높일 수 있다. 예를 들어, 호스트는 시스템이 배터리와 같은 전원으로부터 AC 전력으로 전환될 때, 또는 디스플레이 매체의 소스가 낮은 또는 높은 해상도의 포맷으로 전환될 때 인터페이스 타입을 변경할 수도 있고, 또는 이러한 또는 다른 조건이나 이벤트의 조합을 인터페이스 타입 또는 전송 모드 변경의 기초로 간주할 수도 있다.

또한, 시스템은 일 방향에서 한 모드 및 다른 방향에서 다른 모드를 이용하여 데이터를 전달할 수 있다. 예를 들어, 고속으로 디스플레이에 데이터를 전송하는데 타입 4 인터페이스 모드가 사용될 수 있는 한편, 키보드나 포인팅 장치와 같은 주변 장치들로부터 호스트 장치로 데이터 전송시 타입 1 모드가 사용된다. 당업자들은 호스트 및 클라이언트가 다른 속도로 출력 데이터를 전달할 수 있음을 잘 인식할 것이다.

흔히, MDDI 프로토콜의 사용자들은 "외부" 모드 및 "내부" 모드를 구별할 수 있다. 외부 모드는 한 장치의 호스트를 약 2미터까지 외부 클라이언트에 접속하기 위한 프로토콜 및 인터페이스의 사용을 기술한다. 이러한 상황에서, 호스트는 외부 클라이언트에 전력을 전송하여 두 장치가 모바일 환경에서 쉽게 동작할 수 있다. 내부 모드는 호스트가 공통 하우징이나 지지 프레임 또는 동일 종류의 구조 내에서와 같이 동일 장치 내에 포함된 클라이언트에 접속되는 경우를 기술한다. 예로서 클라이언트는 디스플레이나 디스플레이 드라이버, 또는 키패드나 터치 패드와 같은 입력 장치, 또는 사운드 시스템이고, 호스트는 중앙 제어기, 그래픽 엔진 또는 CPU 엘리먼트인 무선 전화나 다른 무선 장치, 또는 휴대용 컴퓨터나 게임기 내의 애플리케이션이다. 외부 모드 애플리케이션과 달리 클라이언트는 내부 모드 애플리케이션의 호스트에 훨씬 가깝게 배치되기 때문에, 일반적으로 이러한 구성에서 클라이언트에 대한 전력 접속에 관해 논의되는 요건은 존재하지 않는다.

C. 물리적 인터페이스 구조

호스트와 클라이언트 장치 사이의 통신을 확립하기 위한 장치 또는 링크 제어기의 일반적인 배치는 도 4 및 도 5에 도시된다. 도 4 및 도 5에서 MDDI 링크 제어기(402, 502)는 호스트 장치(202)에 설치된 것으로 도시되고, MDDI 링크 제어기(404, 504)는 클라이언트 장치(204)에 설치된 것으로 도시된다. 상기와 같이, 호스트(202)는 일련의 컨덕터를 포함하는 양방향 통신 채널(406)을 이용하여 클라이언트(204)에 접속된다. 후술하는 바와 같이, 호스트 및 클라이언트 링크 제어기 양자 모두 호스트 제어기(드라이버)나 클라이언트 제어기(수신기)로서 응답하도록 설정, 조정 또는 프로그래밍 될 수 있는 단일 회로 설계를 이용한 집적 회로로서 제조될 수 있다. 이는 보다 큰 스케일의 단일 회로 장치 제조로 인해 보다 저렴한 비용을 제공한다.

도 5에서, MDDI 링크 제어기(502)는 호스트 장치(202')에 설치된 것으로 도시되고, MDDI 링크 제어기(504)는 클라이언트 장치(204')에 설치된 것으로 도시된다. 상기와 같이, 호스트(202')는 일련의 컨덕터를 포함하는 양방향 통신 채널(506)을 이용하여 클라이언트(204')에 접속된다. 상술한 바와 같이, 호스트 및 클라이언트 링크 제어기 양자 모두 단일 회로 설계를 이용하여 제조될 수 있다.

MDDI 링크 또는 사용되는 물리적 컨덕터를 통해 호스트와 디스플레이 장치와 같은 클라이언트 사이에 전달되는 신호 또한 도 4 및 도 5에 도시된다. 도 4 및 도 5에 나타낸 바와 같이, MDDI를 통한 데이터 전송의 주 경로 또는 메커니즘은 MDDI_Data0+/- 및 MDDI_Stb+/-로 표기한 데이터 신호를 이용한다. 이들 각각은 케이블의 다른 배선 쌍을 통해 전송되는 저전압 데이터 신호이다. 인터페이스를 통해 전송되는 각 비트에 대해 MDDI_Data0 쌍 또는 MDDI_Stb 쌍에 한 번의 전이(transition)만이 있다. 이는 전류 기반이 아니라 전압 기반 전송 메커니즘이므로, 정적 전류 소비는 거의 0이다. 호스트는 클라이언트 디스플레이로 MDDI_Stb 신호를 구동한다.

데이터는 MDDI_Data 쌍을 통해 순방향 및 역방향으로 흐를 수 있으며(즉 이는 양방향 전송 경로임) 호스트는 데이터 링크의 마스터 또는 제어기이다. MDDI_Data0 및 MDDI_Stb 신호 경로는 다른 모드로 동작하여 잡음 면역성을 최대화 한다. 이들 라인 상의 신호의 데이터 전송률은 호스트에 의해 전송되는 클록의 속도에 의해 결정되고, 약 1 kbps 내지 400 Mbps 또는 그 이상의 범위에 걸쳐 변화한다.

타입 2 인터페이스는 타입 1 에 비해 하나의 추가 데이터 쌍 또는 컨덕터 또는 경로를 포함하며, 이는 MDDI_Data11+/-라 한다. 타입 3 인터페이스는 타입 2 인터페이스 이상의 2개의 추가 데이터 쌍 또는 신호 경로를 포함하며, 이는 MDDI_Data2+/- 및 MDDI_Data3+/-라 한다. 타입 4 인터페이스는 타입 3 인터페이스에 비해 4개의 추가 데이터 쌍 또는 신호 경로를 포함하며, 이는 각각 MDDI_Data4+/-, MDDI_Data5+/-, MDDI_Data6+/- 및 MDDI_Data7+/-라 한다. 상기 각각의 인터페이스에 비해, 호스트는 HOST_Pwr 및 HOST_Gnd로 지정된 배선 쌍 또는 신호를 이용하여 클라이언트 또는 디스플레이에 전력을 전송할 수 있다. 후술하는 바와 같이, 전력 전송은 다른 모드에 이용 가능하거나 제공되는 것보다 적은 컨덕터를 사용하는 인터페이스 "타입"이 사용되고 있을 경우, MDDI_Data4+/-, MDDI_Data5+/-, MDDI_Data6+/- 또는 MDDI_Data7+/- 컨덕터에 대한 어떤 구성에서도 원하는 대로 조절될 수도 있다. 이 전력 전송은 일반적으로 외부 모드에 대해 이용되며, 일부 애플리케이션은 다를 수도 있지만 일반적으로 내부 모드에는 불필요하다.

각종 모드에 대한 MDDI 링크를 통해 호스트와 클라이언트(디스플레이) 사이에 전달되는 신호의 요약은 인터페이스 타입에 따라 하기의 표 1에서 설명한다.

[표 1]

| 타입 1 HOST_Pwr/Gnd MDDI_Stb+/- MDDI_Data0+/- 선택적 전력 선택적 전력 선택적 전력 선택적 전력 | 타입 2 HOST_Pwr/Gnd MDDI_Stb+/- MDDI_Data0+/- MDDI_Data1+/- 선택적 전력 선택적 전력 선택적 전력 선택적 전력 | 타입 3 HOST_Pwr/Gnd MDDI_Stb+/- MDDI_Data0+/- MDDI_Data1+/- MDDI_Data2+/- MDDI_Data3+/- 선택적 전력 선택적 전력 선택적 전력 선택적 전력 | 타입 4 HOST_Pwr/Gnd MDDI_Stb+/- MDDI_Data0+/- MDDI_Data1+/- MDDI_Data2+/- MDDI_Data3+/- MDDI_Data4+/- MDDI_Data5+/- MDDI_Data6+/- MDDI_Data7+/- |

또한, 호스트로부터의 전송을 위한 HOST_Pwr/Gnd 접속은 일반적으로 외부 모드에 제공됨에 유의한다. 내부 애플리케이션 또는 동작 모드는 일반적으로 다른 내부 자원으로부터 직접 전력을 끌어오는 클라이언트를 가지며, 당업자로부터 명백하듯이, 전력 분배를 제어하기 위해 MDDI를 사용하지 않으므로 이러한 분배는 여기서 더 상세히 설명하지 않는다. 그러나 당업자에 의해 이해되는 바와 같이 특정 종류의 전력 제어, 동기화 또는 상호 접속 편의를 허용하도록 전력이 MDDI 인터페이스를 통해 분포되도록 하는 것이 가능하다.

상기 구조 및 동작을 구현하는데 일반적으로 사용되는 케이블은 명목상 길이가 1.5미터 정도, 일반적으로는 2미터 이하이고, 3쌍의 꼬임 쌍 컨덕터를 포함하며, 각각 다중 꼬임 30 AWG 배선이다. 3개의 꼬임 상 위에 추가 드레인 배선으로서 박막 실드 커버링이 싸이거나 달리 말하면 형성된다. 꼬임 쌍 및 실드 드레인 컨덕터는 클라이언트 커넥터에서 클라이언트에 대한 실드에 접속된 실드로 마무리되며, 공지된 바와 같이 전체 케이블을 커버하는 절연 층이 있다. 배선은 HOST_Gnd 및 HOST_Pwr; MDDI_Stb+ 및 MDDI_Stb-; MDDI_Data0+ 및 MDDI_Data0-; MDDI_Data1+ 및 MDDI_Data1- 등으로 쌍을 이룬다. 그러나, 다양한 도체들 및 케이블이 특정 응용들에 따라 본 발명의 실시예들을 구현하기 위하여 종래에 이해되는 바와같이 사용될 수 있다. 예컨대, 무거운 외측 코팅들 또는 균일한 금속 층들은 일부 용용들에서 케이블을 보호하기 위하여 사용될 수 있고, 보다 얇고 평평한 도체 리본형 구조들은 다른 응용들에 적합할 수 있다.

D. 데이터 타입 및 전송률

전 범위의 사용자 체험 및 애플리케이션에 대해 유용한 인터페이스를 달성하기 위해, 이동 디지털 데이터 인터페이스(MDDI)는 제어 정보와 함께 이동 디스플레이 장치에 집적 또는 이와 협력하여 동작할 수 있는 다양한 클라이언트 및 디스플레이 정보, 오디오 트랜스듀서, 키보드, 포인팅 장치 및 많은 다른 입력 및 출력 장치, 및 이들의 조합에 대한 지원을 제공한다. MDD 인터페이스는 최소한의 케이블 또는 컨덕터를 사용하여 순방향 또는 역방향 링크로 호스트와 클라이언트 사이에 이동하는 데이터 스트림의 다양한 잠재적 타입을 수용할 수 있도록 설계된다. 등시성 스트림 및 비동기 스트림(업데이트) 모두 지원된다. 총 데이터 전송률이 바람직한 최대 MDDI 링크 속도보다 작거나 같은 한 여러 조합의 데이터 타입이 가능하며, 이는 최대 직렬 레이트 및 사용되는 데이터 에어 수에 의해 제한된다. 이들은 하기의 표 2 및 3에 기재된 아이템들을 포함하지만, 이에 한정되는 것은 아니다.

[표 2]

| 호스트로부터 클라이언트로의 전송 | ||

| 등시성 비디오 데이터 | 702×480, 12비트, 30f/s | ~ 124.5Mbps |

| 등시성 스테레오 오디오 데이터 | 44.1㎑, 16비트, 스테레오 | ~ 1.4Mbps |

| 비동기 그래픽 데이터 | 800×600, 12비트, 10f/s, 스테레오 | ~ 115.2Mbps |

| 비동기 제어 | 최소 | ≪ 1.0Mbps |

[표 3]

| 클라이언트로부터 호스트로의 전송 | ||

| 등시성 음성 데이터 | 8㎑, 8비트 | ≪ 1.0Mbps |

| 등시성 비디오 데이터 | 640×480, 12비트, 24f/s | ~ 88.5Mbps |

| 비동기 상태, 사용자 입력 등 | 최소 | ≪ 1.0Mbps |

인터페이스는 고정되는 것이 아니라, 미래의 시스템 유연성을 위해 사용자 정의 데이터를 포함하는 다양한 정보 "타입"의 전송을 지원할 수 있도록 확장 가능하다. 수용될 수 있는 데이터의 특정 예는 전체 또는 일부 스크린 비트맵 필드나 압축 비디오 형태의 풀 모션 비디오; 전력을 보존하고 구현 비용을 줄이기 위한 저속의 정적 비트맵; 다양한 해상도 또는 전송률의 PCM 또는 압축 오디오 데이터; 포인팅 장치 위치 및 선택, 및 아직 정의되지 않은 성능에 대한 사용자 정의 가능 데이터이다. 이러한 데이터는 제어 또는 상태 정보와 함께 전송되어 장치 성능 또는 설정된 작동 파라미터를 검출할 수 있다.

본 발명의 실시예들은 이에 한정되는 것은 아니지만 영화(비디오 디스플레이 및 오디오) 시청; 제한된 개인용 뷰잉(viewing)(그래픽, 디스플레이, 때때로 비디오 및 오디오의 조합)을 갖는 개인용 컴퓨터의 이용; PC, 콘솔 또는 개인용 장치상에서의 비디오 게임(동영상 디스플레이 또는 종합 비디오 및 오디오); 비디오폰(양 방향 저속 비디오 및 오디오), 스틸 디지털 사진용 카메라 또는 디지털 비디오 이미지 캡처용 캠코더 형태의 장치를 이용한 인터넷 "서핑"; 프리젠테이션을 제공하기 위해 프로젝터로 도킹되는 비디오 모니터, 키보드 및 마우스에 접속된 데스크탑 도킹 스테이션으로 도킹된 전화, 컴퓨터 또는 PDA의 사용; 및 무선 포인팅 장치 및 키보드 데이터를 포함하여, 셀룰러 폰, 스마트 폰 또는 PDA를 사용한 생산성 향상 또는 엔터테인먼트를 포함하는 데이터 전송에 이용되는 기술을 향상시킨다.

후술하는 고속 데이터 인터페이스는 일반적으로 배선 또는 케이블형 링크로서 구성되는 통신 또는 전송 링크를 통해 상당량의 A-V 타입 데이터를 제공하는 것에 관하여 제시된다. 그러나 신호 구조, 프로토콜, 타이밍 또는 전송 메커니즘은 원하는 레벨의 데이터 전송을 유지할 수 있다면 광 또는 무선 매체 형태로 링크를 제공하도록 조정될 수 있음이 명백할 것이다.

MDD 인터페이스 신호들은 기본 신호 프로토콜 또는 구조에 대한 공통 프레임 레이트(CFR)로서 알려진 개념을 이용한다. 공통 프레임 레이트의 사용을 통해 동시 등시성 데이터 스트림에 동기화 펄스를 제공하게 된다. 클라이언트 장치는 이 공통 프레임 레이트를 시간 기준으로 사용할 수 있다. 낮은 CF 레이트는 서브 프레임 헤더를 전송하기 위해 오버헤드를 감소시킴으로써 채널 효율을 향상시킨다. 한편, 높은 CF 레이트는 대기 기간을 감소시키고, 오디오 샘플에 대해 보다 작은 유연한 데이터 버퍼를 허용한다. 본 발명의 인터페이스의 CF 레이트는 동적으로 프로그래밍 가능하며, 특정 애플리케이션에 사용되는 등시성 스트림에 적절한 많은 값 중 하나로 설정될 수 있다. 즉, CF 값은 원하는 대로 소정 클라이언트 및 호스 트 구성에 가장 적합하게 선택된다.

비디오 또는 마이크로 디스플레이와 같은 애플리케이션에 가장 사용하기 쉬운 등시성 데이터 스트림에 대해 조정 가능한 또는 프로그래밍 가능한 서브 프레임당 일반적으로 필요한 바이트 수는 표 4에 나타낸다.

[표 4]

| 공통 프레임 레이트 ( CFR ) = 300㎐ | |||||||

| X | Y | 비트 | 프레임 레이트 | 채널 | 레이트 (Mbps) | 바이트/ 서브 프레임 | |

| 컴퓨터 게임 | 720 | 480 | 24 | 10 | 1 | 248.832 | 103680 |

| 컴퓨터 그래픽 | 800 | 600 | 24 | 10 | 1 | 115.200 | 48000 |

| 비디오 | 640 | 480 | 12 | 29.9710 또는 30 | 1 | 221.184 | 92160 |

| CD 오디오 | 1 | 1 | 16 | 44100 | 2 | 1.4112 | 588 |

| 음성 | 1 | 1 | 8 | 8000 | 1 | 0.064 | 26-2/3 |

서브 프레임당 바이트의 단편적인(fractional) 카운트는 간단한 프로그래밍 가능 M/N 카운터 구조를 이용하여 쉽게 얻어진다. 예를 들어, 각각 26 바이트의 한 서브 프레임이 뒤따르는 27 바이트의 2개의 프레임을 전송함으로써 CF 당 26-2/3 바이트의 카운트가 구현된다. 더 낮은 CF 전송률이 선택되어 서브 프레임당 정수 개의 바이트를 생성할 수 있다. 그러나 일반적으로, 하드웨어에 간단한 M/N 카운터를 구현하는 것은 큰 오디오 샘플 FIFO 버퍼에 필요한 영역에 비해 본 발명의 일부 또는 모든 실시예를 구현하는데 사용되는 집적 회로 칩 또는 전자 모듈 내에 보다 적은 영역을 필요로 한다.

다른 데이터 전송률 및 데이터 타입의 영향을 설명하는 전형적인 애플리케이션은 가라오케 시스템이다. 가라오케 시스템은 최종 사용자 또는 사용자들이 뮤직 비디오 프로그램에 따라 노래하는 시스템이다. 노래의 가사가 통상적으로 스크린 밑 어딘가에 표시되어, 사용자는 불러야 할 단어 및 노래의 타이밍을 알게 된다. 이러한 애플리케이션은 드문드문 그래픽이 업데이트되고, 사용자의 음성 또는 음성들이 스테레오 오디오 스트림과 혼합되는 비디오 디스플레이를 필요로 한다.

300 ㎐의 공통 프레임 레이트를 가정하면, 각 서브 프레임은 클라이언트 디스플레이 장치에 대한 순방향 링크에서 92,160 바이트의 비디오 컨텐츠 및 (스테레오에서 147개의 16 비트 샘플에 기반한) 588 바이트의 오디오 컨텐츠로 구성될 것이며, 평균 26.67(26-2/3) 바이트의 음성이 마이크에서 모바일 노래방 기계로 다시 전송된다. 비동기 패킷이 호스트와 헤드 장착된 디스플레이 사이에 전송된다. 이는 기껏해야 768 바이트의 그래픽 데이터(1/4 스크린 높이) 및 잡다한 제어 및 상태 명령들에 대해 200 바이트(여러) 미만의 바이트를 포함한다.

표 5는 가라오케 예의 경우 서브 프레임 내에 데이터가 어떻게 할당되는지를 보여준다. 사용되는 총 레이트는 약 279 Mbps로 선택된다. 280 Mbps의 약간 높은 레이트는 서브 프레임당 약 400 바이트의 데이터가 전송될 수 있게 하고, 이는 임시 제어 및 상태 메시지의 사용을 가능하게 한다.

[표 5]

| 엘리먼트 레이트 | 서브 프레임당 오버헤드 바이트 | 서브 프레임당 미디어 바이트 |

| 640×480픽셀 및 30fps의 뮤직비디오 | 2*28 = 56 | 92160 |

| 10 서브프레임, 1/30초로 업데이트되는 640×120픽셀 및 1fps의 가사 텍스트 | 28 | 768 |

| 44,100sps, 스테레오, 16비트의 CD 오디오 | 2*16 =32 | 588 |

| 8000sps, 모노, 8비트의 음성 | 28+8+8+(4*16)+(3*27) = 125 | 26.67 |

| 서브 프레임 헤더 | 22 | |

| 총 바이트/CF | 263 | 115815 |

| 총 레이트(Mbps) | (263+115815)*8*300 = 278.5872 | |

Ⅲ.(계속) 고속 디지털 데이터 인터페이스 시스템 구조

E. 링크 계층

MDD 인터페이스 고속 직렬 데이터 신호를 이용하여 전송되는 데이터는 차례로 연결된 시간 멀티플렉싱 패킷 스트림으로 구성된다. 전송 장치가 전송할 데이터가 없을 때에도, MDDI 링크 제어기는 일반적으로 채움 패킷을 자동으로 전송하여 패킷 스트림을 유지한다. 간단한 패킷 구조의 사용은 비디오 및 오디오 신호 또는 데이터 스트림에 대해 신뢰할 수 있는 등시성 타이밍을 확보한다.

패킷 그룹은 서브 프레임이라 하는 신호 엘리먼트 또는 구조 내에 포함되며, 서브 프레임 그룹은 미디어 프레임이라 하는 신호 엘리먼트 또는 구조 내에 포함된다. 서브 프레임은 각각의 크기 및 데이터 전송 용도에 따라 하나 이상의 패킷을 포함하고, 미디어 프레임은 하나 이상의 서브 프레임을 포함한다. 본원의 실시예에 의해 이용되는 프로토콜에 의해 제공되는 가장 큰 서브 프레임은 232-1 또는 4,294,967,295 바이트 정도이므로, 가장 큰 미디어 프레임 크기는 216-1 또는 65,535개 정도의 서브 프레임이 된다.

특별한 서브 프레임 헤더 패킷은 후술하는 바와 같이 각 서브 프레임 시작에 나타나는 고유 식별자를 포함한다. 그 식별자는 호스트와 클라이언트가 시작할 때 클라이언트 장치에서 프레임 타이밍을 획득하는데 사용된다. 링크 타이밍 획득은 뒤에 보다 상세히 설명한다.

통상적으로, 디스플레이 스크린은 풀 모션 비디오가 디스플레이되고 있을 때 미디어 프레임당 한 번 업데이트된다. 디스플레이 프레임 레이트는 미디어 프레임 레이트와 동일하다. 링크 프로토콜은 원하는 애플리케이션에 따라 전체 디스플레이, 또는 단지 정적 이미지에 의해 둘러싸인 작은 영역의 풀 모션 비디오 컨텐츠에 대해 풀 모션 비디오를 지원한다. 웹페이지 또는 이메일 보기 등의 일부 저전력 모바일 애플리케이션에서, 디스플레이 스크린은 이따금 업데이트될 필요만 있다. 이러한 상황에서, 단일 서브 프레임을 전송한 다음 링크를 셧다운하거나 비활성화하여 전력 소비를 최소화하는 것이 유리하다. 또한, 인터페이스는 스테레오 비전과 같은 효과를 지원하고, 그래픽 원색을 처리한다.

서브 프레임은 시스템이 높은 우선순위의 패킷을 주기적으로 전송할 수 있게 한다. 이는 동시 등시성 스트림이 최소량의 데이터 버퍼링으로 공존할 수 있게 한다. 이는 디스플레이 프로세스에 제공되는 한 가지 이점이며, 다중 데이터 스트림(비디오, 음성, 제어, 상태, 포인팅 장치 데이터 등의 고속 통신)이 본질적으로 공통 채널을 공유할 수 있게 한다. 또한, 수평 동기 펄스 및 CRT 모니터에 대한 블랭크 간격과 같은 디스플레이 기술 특유의 동작이나 다른 클라이언트 기술 특유 의 동작이 존재하게 한다.

F. 링크 제어기

도 4 및 도 5에 나타낸 MDDI 링크 제어기가 MDDI 데이터 및 스트로브 신호를 수신하는데 사용되는 차동 라인 수신기를 제외하고 완전히 디지털로 구현되도록 제조 또는 조립된다. 그러나 차동 라인 드라이버 및 수신기들도 CMOS형 IC를 제작하는 경우와 같이 링크 제어기와 함께 동일한 디지털 집적 회로에 구현될 수 있다. 비트 복원을 위해 또는 링크 제어기용 하드웨어 구현을 위해 어떤 아날로그 성능 또는 위상 고정 루프(PLL)도 요구되지 않는다. 호스트 및 클라이언트 링크 제어기는 링크 동기화를 위한 상태 머신을 포함하는 클라이언트 인터페이스를 제외하고, 매우 비슷한 성능들을 포함한다. 따라서, 본 발명의 실시예는 전체적으로 링크 제어를 위해 제조 비용을 감소할 수 있는 호스트 또는 클라이언트로 구성될 수 있는 단일 제어 설계 또는 회로를 생성할 있는 실질적인 장점을 갖게 한다.

IV. 인터페이스 링크 프로토콜

A. 프레임 구조

패킷 전송을 위한 순방향 링크 통신을 구현하는데 사용되는 신호 프로토콜 또는 프레임 구조가 도6에 도시된다. 도6에 도시된 바와 같이, 정보 또는 디지털 데이터는 패킷으로 알려진 구성 요소로 그룹화된다. 멀티미디어 패킷은 "서브 프레임"을 형성하기 위해 차례로 서로 그룹화되며, 다수의 서브 프레임은 "미디어" 프레임을 구성하기 위해 차례로 서로 그룹화된다. 프레임의 형성 및 서브 프레임의 전송을 제어하기 위해, 각각의 서브 프레임은 서브 프레임 헤더 패킷(SHP)으로 알려진 특정하게 정의된 패킷으로 시작한다.

호스트 장치는 소정의 전송을 위해 사용되는 데이터 레이트를 선택한다. 이러한 레이트는 호스트의 최대 전송 성능, 또는 호스트에 의해 소스로부터 검색된 데이터, 및 클라이언트의 최대 성능 또는 데이터가 전송될 다른 장치에 기초하여 호스트 장치에 의해 동적으로 변경될 수 있다.

MDDI 또는 본 발명의 신호 프로토콜과 동작하도록 설계된 수신 클라이언트 장치는 사용할 수 있는 최대 또는 현재의 최대 데이터 레이트를 결정하기 위해 호스트에 의해 질의될 수 있거나, 디폴트 저속 최소 레이트가 사용가능한 데이터 타입 및 지원된 특성과 함께 사용될 수도 있다. 이러한 정보는 후술하는 바와 같이, 클라이언트 성능 패킷(DCP)을 사용하여 전송될 수 있다. 클라이언트 디스플레이 장치는 사전 선택된 최소 데이터 레이트 또는 최소 데이터 레이트 영역 내에서 데이터를 전송하거나 인터페이스를 사용하는 다른 장치와 통신할 수 있으며, 호스트는 클라이언트 장치의 전체 성능을 결정하기 위해 이러한 영역 내에서 데이터 레이트를 사용하는 질의를 할 수 있다.

비트맵의 특성 및 클라이언트의 비디오 프레임 레이트 성능을 한정하는 다른 상태 정보는 호스트가 실제로 유효하거나 선택적인, 또는 소정의 시스템 제한 내에서 요구되는 인터페이스를 구성할 수 있도록 상태 패킷으로 호스트로 전송될 수 있다.

호스트는, 현재 서브 프레임에서 전송될 데이터 패킷이 더 이상 없는 경우, 또는 호스트가 순방향 링크에 대해 선택된 데이터 송신 레이트와 보조를 맞추기에 충분한 레이트로 전송할 수 없는 경우, 채움(filler) 패킷을 전송한다. 각각의 서브 프레임이 서브 프레임 헤더 패킷으로 시작하기 때문에, 앞선 서브 프레임의 마지막은 앞선 서브 프레임을 완전히 채우는 패킷(채움 패킷과 거의 유사)을 포함한다. 패킷을 갖는 데이터에 대한 공간이 부족한 경우, 채움 패킷은 서브 프레임의 또는 다음의 앞선 서브 프레임의 말단 및 서브 프레임 헤더 패킷 이전의 최종 패킷과 거의 유사할 것이다. 상기 서브 프레임 내에서 송신될 각각의 패킷에 대한 서브 프레임에 잔존하는 충분한 공간이 있다는 것을 보장하는 것은 호스트 장치에서의 제어 연산의 작업이다. 동시에, 일단 호스트 장치가 데이터 패킷의 전송을 개시하면, 호스트는 데이터 언더-런 조건을 유발하지 않고 프레임 내의 그 크기를 갖는 패킷을 연속하여 완료할 수 있다.

실시예의 일 양상에서, 서브 프레임 송신은 두 모드를 갖는다. 하나의 모드는 라이브 비디오 및 오디오 스트림을 송신하는데 사용되는 주기적인 서브 프레임 모드이거나, 주기적인 타이밍 에포크(epoch)이다. 이러한 모드에서, 서브 프레임 길이는 0이 아닌 것으로 정의된다. 두 번째 모드는 비동기 또는 비주기 모드로서, 프레임은 새로운 정보가 이용가능할 때, 비트맵 데이터를 클라이언트로 제공하는데 사용된다. 이러한 모드는 서브 프레임 헤더 패킷에서 서브 프레임 길이를 0으로 설정함으로써 한정된다. 주기적인 모드를 사용할 때, 서브 프레임 패킷 수신은 클라이언트가 순방향 링크 프레임 구조와 동기화된 때 개시할 수도 있다. 이는 도49 또는 도63과 관련하여 후술되는 상태 다이어그램에 따라 한정된 "in sync" 상태에 대응한다. 비동기 비주기 서브 프레임 모드에서, 수신은 제1 서브 프레임 헤더 패킷이 수신된 후 개시한다.

B. 전체 패킷 구조

실시예에 의해 구현되는 통신 또는 신호 프로토콜, 또는 데이터를 송신하기 위한 방법 및 수단을 구성하는데 사용되는 패킷의 형식 또는 구조가 이하에 설명되는데, 인터페이스는 확장가능하고 추가의 패킷 구조는 원하는 대로 부가될 수 있음을 이해해야 한다. 패킷은 인터페이스에서 이들의 성능에 따라 다양한 "패킷 타입", 즉 명령, 정보, 값, 또는 데이터로 분류되거나 나뉜다. 따라서, 각각의 패킷 타입은 전송될 패킷 및 데이터를 조작하는데 사용되는 소정의 패킷에 대한 예정된 패킷 구조를 나타낸다. 명백하듯이, 패킷은 예정된 길이를 갖거나, 이들 각각의 성능에 따라 가변 또는 동적 변화가능한 길이를 갖는다. 또한, 비록 동일한 성능이 실현되더라도 표준으로의 수용 동안 프로토콜이 변화할 경우 발생할 수 있는 바와 같이, 패킷은 상이한 이름을 가질 수 있다. 다양한 패킷에 사용된 바이트들 또는 바이트 값은 부호 없는 다중 비트 정수(8 또는 16비트)로 구성된다. 타입 순서로 리스트된 "타입" 지정과 함께 이용되는 패킷의 요약이 표 VI-1 내지 VI-4에 도시된다.

각각의 표는 예시 또는 이해의 용이함을 위해 전체 패킷 구조 내에서 패킷의 일반 "타입"을 나타낸다. 이러한 그룹에 의해 본원 발명을 설명하기 위해 부과된 제한은 없으며, 패킷은 원하는 다양한 형태로 구성될 수 있다. 패킷의 전송이 유효한 것으로 고려되는 방향이 또한 표시된다.

표 VI-1: 링크 제어 패킷들

| 패킷 이름 | 패킷 타입 | 순방향에서 유효성 | 역방향에서 유효성 |

| 서브 프레임 헤더 패킷 | 15359 | × | |

| 채움 패킷 | 0 | × | × |

| 역방향 링크 캡슐화 패킷 | 65 | × | |

| 링크 셧다운 패킷 | 69 | × | |

| 인터페이스 타입 핸드오프 요청 패킷 | 75 | × | |

| 인터페이스 타입 응답 패킷 | 76 | × | |

| 수행 타입 핸드오프 패킷 | 77 | × | |

| 순방향 오디오 채널 인에이블 패킷 | 78 | × | |

| 왕복 지연 측정 패킷 | 82 | × | |

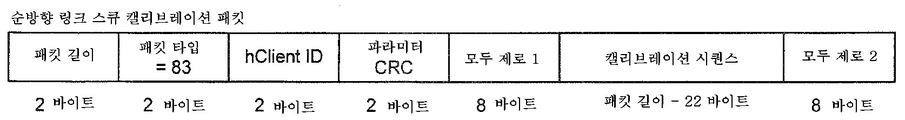

| 순방향 스큐 계산 패킷 | 83 | × |

표 VI-2: 기본 미디어 스트림 패킷

| 패킷 이름 | 패킷 타입 | 순방향에서 유효성 | 역방향에서 유효성 |

| 비디오 스트림 패킷 | 16 | × | × |

| 오디오 스트림 패킷 | 2 | × | × |

| 비축된 스트림 패킷 | 1-15,18-31,33-55 | × | × |

| 사용자 정의 스트림 패킷 | 6-63 | × | × |

| 제어 맵 패킷 | 4 | × | × |

| 역(reverse) 오디오 샘플 레이트 패킷 | 9 | × | |

| 투명 컬러 인에이블 패킷 | 1 | × |

표 VI-3: 클라이언트 상태 및 제어 패킷들

| 패킷 이름 | 패킷 타입 | 순방향에서 유효성 | 역방향에서 유효성 |

| 클라이언트 성능 패킷 | 66 | × | |

| 키보드 데이터 패킷 | 67 | × | × |

| 포인팅 장치 데이터 패킷 | 68 | × | × |

| 클라이언트 요청 및 상태 패킷 | 70 | × | |

| 디지털 컨텐츠 보호 오버헤드 패킷 | 80 | × | × |

| 요청 VCP 특성 패킷 | 128 | × | |

| VCP 특성 응답 패킷 | 129 | × | |

| 세트 VCP 특성 패킷 | 130 | × | |

| 요청 유효 파라미터 패킷 | 131 | × | |

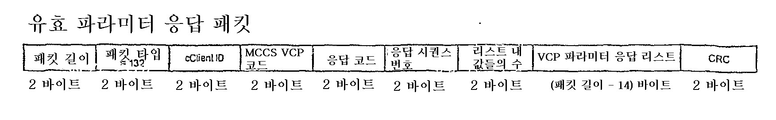

| 유효 파라미터 응답 패킷 | 132 | × | |

| 요청 특성 상태 패킷 | 138 | × | |

| 유효 상태 응답 리스크 패킷 | 139 | × | |

| 패킷 프로세싱 지연 파라미터 패킷 | 140 | × | |

| 개인 디스플레이 성능 패킷 | 141 | × | |

| 클라이언트 에러 보고 패킷 | 142 | × | |

| 스케일링된 비디오 스트림 성능 패킷 | 143 | × | |

| 클라이언트 식별 패킷 | 144 | × | |

| 대안적 디스플레이 성능 패킷 | 145 | × | |

| 레지스터 액세스 패킷 | 146 | × | × |

표 VI-4: 진보한 그래픽 및 디스플레이 패킷

| 패킷 이름 | 패킷 타입 | 순방향에서 유효성 | 역방향에서 유효성 |

| 비트 블록 전송 패킷 | 71 | × | |

| 비트맵 영역 채움 패킷 | 72 | × | |

| 비트맵 패턴 채움 패킷 | 73 | × | |

| 판독 프레임 버퍼 패킷 | 74 | × | |

| 알파 커서 이미지 성능 패킷 | 133 | × | |

| 알파 커서 투명 맵 패킷 | 134 | × | |

| 알파 커서 이미지 오프셋 패킷 | 135 | × | |

| 알파 커서 비디오 스트림 패킷 | 17 | × | |

| 스케일링된 비디오 스트림 성능 패킷 | 143 | × | |

| 스케일링된 비디오 스트림 셋업 패킷 | 136 | × | |

| 스케일링된 비디오 스트림 응답 패킷 | 137 | × | |

| 스케일링된 비디오 스트림 패킷 | 18 | × |

본 명세서 내의 다른 논의와 명확하게 구별되는 것은 역방향 캡슐화 패킷, 클라이언트 성능 패킷, 및 클라이언트 요청 및 상태 패킷은 각각 외부 모드 연산의 경우 통신 인터페이스의 많은 실시예에서 중요하고, 내부 모드 연산의 경우 이들은 선택적이다. 이는 감소된 세트의 통신 패킷, 및 대응하는 제어 및 타이밍의 간략화와 함께 매우 높은 속도로 데이터의 통신을 가능하게 하는 MDD 인터페이스 프로토콜의 또다른 타입을 생성한다.

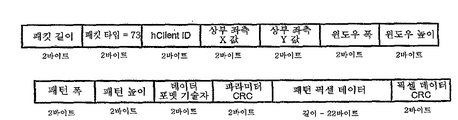

패킷은 패킷 길이 필드, 패킷 타입 필드, 데이터 바이트 필드, 및 도7에 도시된 CRC를 포함하는 최소 필드의 전체 세트 또는 공통의 기본 구조를 갖는다. 도7에 도시된 바와 같이, 패킷 길이 필드는 패킷에서 전체 비트의 수 또는 패킷 길이 필드와 CRC 필드 사이의 길이를 특정하는 다중 비트 또는 바이트 값의 형태로 정보를 포함한다. 일 실시예에서, 패킷 길이 필드는 패킷 길이를 한정하는 16 비트 또는 2 바이트 폭의 부호 없는 정수를 포함한다. 패킷 타입 필드는 패킷 내에 포함된 정보의 타입을 나타내는 다른 멀티 비트 필드이다. 실시예에서, 이는 16비트 부호 없는 정수의 형태로 16비트 또는 2 바이트 폭이며, 이러한 데이터 타입을 디 스플레이 성능, 핸드오프, 비디오 또는 오디오 스트림, 상태 등으로서 특정한다.

제3 필드는 데이터 바이트 필드로서, 패킷의 일부로서 호스트와 클라이언트 장치 사이에서 송신 또는 전송되는 비트 또는 데이터를 포함한다. 데이터의 포맷은 송신될 데이터의 특정 타입에 따른 각각의 패킷 타입에 대해 구체적으로 한정되며 부가의 필드의 시리즈로 분리될 수도 있는데, 각각은 자신 고유의 요구 조건을 갖는다. 즉, 각각의 패킷 타입은 이러한 부분 또는 필드에 대해 한정된 형태를 가질 것이다. 최종 필드는 데이터 바이트, 패킷 타입, 및 패킷 길이 필드에 대해 계산되는 16비트 순환 중복 검사의 결과를 포함하는 CRC 필드인데, 패킷에서 정보의 무결성을 형성하는데 사용된다. 다시 말해, CRC 필드 자체를 제외하고 전체 패킷에 대해 계산된다. 클라이언트는 일반적으로 검출된 CRC 에러의 전체 양을 유지하고 이를 클라이언트 요청 및 상태 패킷에서 호스트로 보고한다(이하 참조).

일반적으로, 이러한 필드 폭 및 구성은 짝수 바이트 경계에 정렬된 2바이트 필드, 및 4바이트 경계에 정렬된 4바이트 필드를 유지하도록 설계된다. 이는 패킷 구조가 대부분 또는 통상 사용되는 프로세서 또는 제어 회로에 대한 데이터 타입 정렬 규칙을 깨트리지 않고 호스트와 클라이언트의 또는 이와 관련한 주메모리 공간에 용이하게 구축되게 한다.

패킷의 전송 동안, 필드는 우선 최하위 비트(LSB)에서 시작하여 최종으로 전송된 최상위 비트(MSB)로 종료하게 송신된다. 길이가 1바이트 이상인 파라미터는 먼저 최하위 비트를 이용하여 송신되는데, 이는 LSB가 먼저 송신되는 경우, 더 짧은 파라미터에 사용됨에 따라 8비트 길이보다 큰 파라미터에 대해 사용되는 동일한 비트 송신 패턴을 초래한다. 각각의 패킷의 데이터 필드는 일반적으로 이하의 뒤이은 섹션에서 한정된 순서로 송신되는데, 리스트된 제1 필드가 우선 송신되고, 설명된 최종 필드가 마지막으로 송신된다. MDDI_Data0 신호 경로에 대한 데이터는 타입1, 타입2, 타입3, 또는 타입4 중 하나의 모드에서 인터페이스에 대해 송신된 바이트들 비트의 '0'과 정렬된다.

디스플레이를 위해 데이터를 조작할 때, 픽셀의 어레이를 위한 데이터는 전자 분야에서 통상적으로 행해지는 바와 같이, 우선 행으로 송신되고, 이어 열로 송신된다. 다시 말해, 비트 맵의 동일한 행에 나타나는 모든 픽셀은 가장 좌측 픽셀이 우선 송신되고 가장 우측 픽셀이 최종으로 송신되는 순서로 송신된다. 행의 최우측 픽셀이 송신된 후, 시퀀스의 다음 픽셀은 다음 행의 가장 좌측 픽셀이다. 다른 구성이 필요에 따라 수용될 수 있지만, 픽셀의 행들이 일반적으로 디스플레이의 최상부로부터 하부의 순으로 송신된다. 더욱이, 비트맵을 다룰 때, 본 명세서에 따르는 통상의 방법은 위치 또는 오프셋 "0,0"으로서 비트맵의 좌상부 코너를 라벨링함으로써 기준 포인트를 한정하는 것이다. 비트맵에서 위치를 한정 또는 결정하기 위해 사용되는 X 및 Y 좌표는 각각 비트맵의 우측 및 하부에 도달함에 따라 증가한다. 제1 행 및 제1 열(이미지의 좌상부 코너)은 0의 지수 값으로 시작한다. 디스플레이의 사용자에 의해 보여지는 바와 같이, X 좌표의 크기는 이미지의 우측을 향해 증가하며, Y 좌표의 크기는 이미지의 하부를 향해 증가한다.

*디스플레이 윈도우는 비트맵의 가시 부분이며, 비트맵의 픽셀 부분은 물리 적인 디스플레이 매체 상에서 사용자에 의해 보여질 수 있다. 디스플레이 유닛 및 비트맵이 동일한 크기인 경우가 통상적이다. 디스플레이 윈도우의 좌측 상부 코너는 언제나 비트맵 픽셀 위치 '0,0'를 디스플레이한다. 디스플레이 윈도우의 폭은 비트맵의 X축에 대응하며, 이러한 실시예의 디스플레이 윈도우 폭은 대응하는 비트맵의 폭과 동일하거나 작다. 윈도우의 높이는 비트맵의 Y축에 대응하며, 본 실시예에 대한 디스플레이 윈도우 높이는 대응하는 비트맵의 높이와 동일하거나 작다. 디스플레이 윈도우 그 자체는 비트맵의 가시적 부분으로만 한정되기 때문에 프로토콜에 어드레싱 가능하지 않다.

비트맵과 디스플레이 윈도우 사이의 관계는 컴퓨터, 전자 분자, 인터넷 통신, 및 다른 전자 관련 기술분야에 공지되어 있다. 따라서, 이러한 원리의 추가 논의 또는 설명은 제공되지 않는다.

C. 패킷 정의

*1. 서브 프레임 헤더 패킷

서브 프레임 헤더 패킷은 모든 서브 프레임의 제1 패킷이며, 도8에 도시된 기본 구조를 갖는다. 서브 프레임 헤더 패킷은 호스트 클라이언트 동기화를 위해 사용되며, 모든 호스트는 이러한 패킷을 생성할 수 있는 반면, 모든 클라이언트는 이러한 패킷을 수신 및 번역할 수 있어야 한다. 도8의 일 실시예에 도시되는 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, 고유 워드, 예약 1, 서브 프레 임 길이, 프로토콜 버전, 서브 프레임 카운트 및 미디어 프레임 카운트 필드를 일반적으로 이 순서로 갖도록 구성된다. 일 실시예에서, 이러한 타입의 패킷은 타입 15359(0x3bff 16진수)로서 일반적으로 한정되며 20 바이트의 예정된 고정 길이를 이용하지만, 패킷 길이 필드는 포함하지 않는다.

패킷 타입 필드 및 고유 워드 필드는 각각 2바이트 값(16비트 부호 없는 정수)을 사용한다. 이러한 두 필드의 4바이트 조합은 양호한 자동 상관을 갖는 32비트 고유 워드를 형성한다. 일 실시예에서, 실제 고유 워드는 0x005a3bff이며, 하위 16비트는 패킷 타입으로 우선 송신되고, 최상위 16비트는 그 후에 송신된다.

예약 1 필드는 미래의 사용을 위해 예비된 공간인 2바이트를 포함하며, 일반적으로 이 시점에서 모든 비트가 0으로 구성된다. 이러한 필드의 일 목적은 연속한 2바이트 필드가 16비트 워드 어드레스로 정렬되게 하고 4바이트 필드가 32비트 워드 어드레스로 정렬되게 한다. 최하위 바이트는 호스트가 다중 클라이언트 장치를 어드레싱할 수 있는 지를 나타내기 위해 예비된다. 이러한 바이트를 위한 0의 값은 호스트가 단일 클라이언트 장치와 동작가능하다는 것을 나타내기 위해 예비된다.

서브 프레임 길이 필드는 서브 프레임당 바이트의 수를 한정하는 4바이트의 정보, 또는 값을 포함한다. 일 실시예에서, 필드의 길이는 단지 하나의 서브 프레임이 링크가 휴지 상태로 닫히기 전에 호스트에 의해 송신될 것을 나타내기 위해 0으로 설정될 수도 있다. 이러한 필드에서의 값은 하나의 서브 프레임으로부터 다음 서브 프레임으로 전이시 동적으로 변화하는 "온-더-플라이"일 수 있다. 이러한 성능은 등시성 데이터 스트림을 수용하기 위해 동기 펄스에서 다소의 시간 조절을 하는데 유용하다. 서브 프레임 헤더 패킷의 CRC가 유효하지 않으면, 링크 제어기는 현재 서브 프레임의 길이를 추정하기 위해 공지된 양호한 서브 프레임 헤더 패킷의 서브 프레임 길이를 이용해야 한다.

프로토콜 버전 필드는 호스트에 의해 사용된 프로토콜 버전을 설명하는 2바이트를 포함한다. 프로토콜 버전 필드는 사용될 프로토콜의 제1 또는 현재 버전을 설명하기 위해 '0'으로 설정될 수도 있다. 이러한 값은 새로운 버전이 생성됨에 따라 시간에 대해 변화할 것이며, 일부 버전 필드에 대해 '1'의 값으로 이미 업그레이드된다. 버전 값은 MDDI와 같은 인터페이스를 커버하는 승인된 표준 문서에 대한 현재 버전 번호를 따른다.

서브 프레임 카운트 필드는 미디어 프레임의 개시 이후, 송신된 서브 프레임의 수를 나타내는 시퀀스 번호를 규정하는 2바이트를 포함한다. 미디어 프레임의 제1 서브 프레임은 0의 서브 프레임 카운트를 갖는다. 미디어 프레임의 최종 서브 프레임은 n-1의 값을 갖는데, 여기서, n은 미디어 프레임당 서브 프레임의 수이다. 서브 프레임 카운트 필드의 값은 0의 카운트를 가질 미디어 프레임의 서브 프레임을 제외하고, 앞선 서브 프레임 패킷의 서브 프레임 카운트에 1을 더한 것과 같다. 만일 서브 프레임 길이가 0 이면(비주기적 서브 프레임을 나타냄), 서브 프레임 카운트는 또한 0으로 세팅된다.

미디어 프레임 카운트 필드는 전송되는 현재 미디어 아이템 또는 데이터의 개시 이후 송신된 미디어 프레임의 수를 나타내는 시퀀스 번호를 규정하는 4 바이 트(32비트 부호 없는 정수)를 포함한다. 미디어 아이템의 제1 미디어 프레임은 0의 미디어 프레임 카운트를 갖는다. 미디어 프레임 카운트는 각각의 미디어 프레임의 서브 프레임 바로 앞에서 증가하며, 최대 미디어 프레임 카운트(예를 들어, 미디어 프레임의 수 232-1=4,294,967,295)가 사용된 후, 0으로 돌아온다. 미디어 프레임 카운트 값은 엔드 애플리케이션의 요구에 적합하게 하기 위해 호스트에 의해 소정의 시간에서 일반적으로 리셋될 수도 있다.

*2. 채움 패킷

채움 패킷은 어떠한 다른 정보도 순방향 또는 역방향 링크상으로 전송되는 것이 가용하지 않을 경우 클라이언트 장치와 송수신하는 패킷이다. 채움 패킷이 필요한 경우 채움 패킷이 다른 패킷을 송신하는 최대 유연성을 가능하게 하기 위해 최소 길이를 갖는 것이 권장된다. 서브 프레임 또는 역방향 링크 캡슐화 패킷(이하 참조)의 단부(end)에서, 링크 제어기는 완전한 패킷을 유지하기 위해 잔여 공간을 채우는 채움 패킷의 크기를 설정한다. 채움 패킷은 호스트 또는 클라이언트가 송신 또는 교환할 어떠한 정보도 없는 경우, 링크 상의 시간을 유지하는데 유용하다. 모든 호스트 및 클라이언트는 인터페이스의 효과적인 사용을 위해 이러한 패킷을 송신 및 수신하는 것을 필요로 한다.

채움 패킷의 포맷 및 콘텐츠의 실시예는 도9에 도시된다. 도9에 도시된 바 와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, 채움 바이트, 및 CRC 필드를 갖도록 구성된다. 일 실시예에서, 이러한 타입의 패킷은 통상적으로 타입 0으로 식별되며, 이는 2바이트 타입 필드에서 표시된다. 채움 바이트 필드의 비트 또는 바이트는 채움 패킷이 원하는 길이가 되도록 모든 0비트 값의 가변 수를 포함한다. 가장 작은 채움 패킷은 이러한 필드에서 어떠한 바이트도 포함하지 않는다. 즉, 패킷은 단지 패킷 길이, 패킷 타입, 및 CRC로 구성되며, 일 실시예에서 6바이트의 예정된 고정 길이 또는 4의 패킷 길이 값을 이용한다. CRC 값은 패킷 길이를 포함하는 패킷에서 모든 바이트에 대해 결정되는데, 이는 다른 패킷 타입에서 제외될 수도 있다.

3. 비디오

스트림

패킷

비디오 스트림 패킷은 디스플레이 장치의 통상적인 직사각형 영역을 업데이트 하기 위한 비디오 데이터를 운반한다. 이러한 영역의 크기는 단일 픽셀만큼 작거나, 전체 디스플레이만큼 클 수도 있다. 스트림을 디스플레이하기 위해 필요한 모든 컨텐츠가 비디오 스트림 패킷 내에 포함되므로, 스트림 리소스에 의해 한정되며, 동시에 디스플레이되는 거의 제한없는 수의 스트림이 존재한다. 비디오 스트림 패킷(비디오 데이터 포맷 기술자)의 일 실시예의 포맷은 도10에 도시된다. 도10에 도시된 바와 같이, 일 실시예에서, 이러한 타입의 패킷은 패킷 길이(2바이트), 패킷 타입, b클라이언트 ID, 비디오 데이터 포맷 기술자, 픽셀 디스플레이 속성, X 좌측 에지, Y 상부 에지, X 우측 에지, Y 하부 에지, X 및 Y 시작, 픽셀 카 운트, 파라미터 CRC, 픽셀 데이터, 및 픽셀 데이터 CRC 필드를 갖도록 구성된다. 이러한 타입의 패킷은 일반적으로 타입 16으로 식별되며, 이는 2바이트 타입 필드에서 표시된다. 일 실시예에서, 클라이언트는 클라이언트 성능 패킷의 RGB, 단색, 및 Y Cr Cb 성능 필드를 사용하여, 비디오 스트림 패킷을 수신하는 능력을 나타낸다.

일 실시예에서, b클라이언트 ID 필드는 클라이언트 ID에 대해 유지된 2바이트의 정보를 포함한다. 이는 새롭게 개발된 통신 프로토콜이므로, 실제 클라이언트 ID는 아직 알려지지 않거나 충분히 통신가능하지 않다. 따라서, 이러한 필드의 비트는 통상적으로 상기 ID 값이 알려지기 전까지 0으로 설정되는데, 이때 ID 값은 기술 분야의 당업자에게 명확하듯이, 삽입되거나 사용될 수 있다. 동일한 프로세스가 통상적으로 후술하는 클라이언트 ID 필드에 대해 적용된다.

전술한 공통 프레임 개념은 오디오 버퍼 크기를 최소화하고 대기지연을 감소시키는 효율적인 방식이다. 그러나 비디오 데이터의 경우, 미디어 프레임 내의 다수의 비디오 스트림 패킷에 걸쳐 하나의 비디오 프레임의 픽셀을 확산시킬 필요가 있을 수도 있다. 단일 비디오 스트림 패킷에서의 픽셀이 디스플레이에 대해 완벽한 직사각형 윈도우에 대응하지 않을 가능성이 매우 높다. 초당 30 프레임의 비디오 프레임 레이트의 경우, 초당 300 서브 프레임이 존재하며, 이는 미디어 프레임당 10 서브 프레임을 초래한다. 만일 각각의 프레임에서 480 행의 픽셀이 존재하면, 각각의 서브 프레임에서 각각의 비디오 스트림 패킷은 48 행의 픽셀을 포함할 것이다. 다른 상황에서, 비디오 스트림 패킷은 정수의 픽셀 행을 포함하지 않을 수 도 있다. 이는 미디어 프레임당 서브 프레임의 수가 비디오 프레임당 행의 수(비디오 라인으로도 알려짐)로 균등하게 분할되지 않는 다른 비디오 프레임 크기에 대해서도 적용된다. 효율적인 동작을 위해, 각각의 비디오 스트림 패킷이 심지어 정수 행의 픽셀을 포함하지 않는다고 해도, 통상적으로 정수의 픽셀을 포함해야 한다. 이는 픽셀이 각각 2바이트 이상이거나, 이들이 도12에 도시된 패킷 형태인 경우 중요하다.

전술한 바와 같이, 예로든 비디오 데이터 기술자 필드의 연산을 실현하기 위해 사용된 포맷 및 컨텐츠는 도11A-11E에 도시된다. 도11A-11E에서, 비디오 데이터 포맷 기술자 필드는 현재 패킷에서 현재의 스트림의 픽셀 데이터에서 각각의 픽셀의 포맷을 설명하는 16비트 부호 없는 정수 형태의 2바이트를 포함한다. 상이한 비디오 스트림 패킷이 상이한 픽셀 데이터 포맷을 사용할 수 있고, 즉 비디오 데이터 포맷 기술자에서 상이한 값을 사용할 수도 있으며, 유사하게, 스트림(디스플레이의 영역)은 자신의 데이터 포맷 온-더-플라이를 변경할 수도 있다. 픽셀 데이터 포맷은 클라이언트 성능 패킷에서 한정된 바와 같이 클라이언트에 대한 유효한 포맷 중 적어도 하나에 따를 수 있다. 비디오 데이터 포맷 기술자는 일정한 포맷이 특정 비디오 스트림의 수명 동안 계속하여 사용될 것을 의미하지 않는 단지 현재 패킷에 대한 픽셀 포맷을 한정한다.

도11A 내지 11D는 비디오 데이터 포맷 기술자가 코딩되는 방법을 설명한다. 이러한 도면에서 사용된 바와 같이, 이러한 실시예에서, 비트[15:13]는 도11A에 도시된 바와 같이 '000'과 동일하며, 비디오 데이터는 단색 픽셀의 어레이로 구성되 는데, 픽셀당 비트의 수는 비디오 데이터 포맷 기술자 워드의 비트 3 내지 0으로 한정된다. 비트 11 내지 4는 통상적으로 미래의 사용 또는 애플리케이션을 위해 예비되며 이러한 상황에서는 0으로 설정된다. 비트[15:13]이 값'001'로 인서팅되면, 도 11B에 도시된 바와 같이, 비디오 데이터는 컬러 맵(팔레트)에 대한 컬러를 각각 규정하는 컬러 픽셀의 어레이로 구성된다. 이러한 상황에서, 비디오 데이터 포맷 기술자 워드의 비트 5 내지 0은 픽셀당 비트의 수를 한정하며, 비트 11 내지 6은 통상적으로 미래의 사용 또는 애플리케이션을 위해 예비되며 0으로 설정된다. 비트[15:13]이 '010'으로 인서팅되면, 도11C에 도시된 바와 같이, 비디오 데이터는 컬러 픽셀의 어레이로 구성되는데, 적색의 픽셀당 비트의 수는 비트 11 내지 8로 한정되며, 녹색의 픽셀당 비트 수는 비트 7 내지 4로 한정되며, 청색의 픽셀당 비트의 수는 비트 3 내지 0으로 한정된다. 이러한 상황에서, 각각의 픽셀에서 전체 비트의 수는 적색, 녹색, 및 청색에 사용된 비트의 수의 합이다.

그러나 비트[15:13]이 도11D에 도시된 바와 같이, 값 또는 스트링 '011'과 동일할 경우, 비디오 데이터는 휘도 및 색상 정보를 갖는 4:2:2 YCbCr 포맷의 비디오 데이터 어레이로 구성되는데, 휘도(Y)의 픽셀당 비트의 수는 비트 11 내지 8로 한정되며, Cb 성분의 비트의 수는 비트 7 내지 4로 한정되며, Cr 성분의 비트의 수는 비트 3 내지 0으로 한정된다. 각각의 픽셀에서 비트의 전체 수는 적색, 녹색 및 청색에 사용된 비트의 수의 합이다. Cb 및 Cr 성분은 Y의 절반 레이트로 전송된다. 게다가, 이러한 패킷의 픽셀 데이터 부분의 비디오 샘플은 다름과 같이 구성된다: Cbn, Yn, Crn, Yn+1, Cbn+2, Yn+2, Yn+3,...이며, 여기서 Cbn 및 Crn은 Yn 및 Yn+1과 관련되며, Cbn+2 및 Crn+2는 Yn+2 및 Yn+3 등과 관련된다.

Yn, Yn+1, Yn+2 및 Yn+3은 좌측에서 우측으로 단일 행의 4개의 연속한 픽셀의 휘도 값이다. 만일 비디오 스트림 패킷에 의해 참조되는 윈도우에서 행(X 우측 에지-X 좌측 에지+1)의 픽셀들의 수가 홀수이면, 각각의 행의 최종 픽셀에 대응하는 Y 값에 뒤이어 다음 행의 첫 번째 픽셀의 Cb 값이 이어지며, Cr값은 행의 최종 픽셀을 위해 전송되지 않는다. Y Cb Cr 포맷을 사용하는 윈도우는 픽셀들의 수가 짝수인 폭을 갖는 것이 권장된다. 패킷에서의 픽셀 데이터는 짝수의 픽셀들을 포함해야 한다. 이는 픽셀 데이터의 최종 픽셀이 비디오 스트림 패킷 헤더에 설명된 윈도우에서 행의 최종 픽셀에 대응하는 경우, 즉 픽셀 데이터에서 최종 픽셀의 X 위치는 X 우측 에지와 동일한 때, 픽셀의 홀수 및 짝수를 포함할 수도 있다.

대신에 비트[15:13]이 값'100'과 동일한 경우, 비디오 데이터는 Bayer 픽셀 어레이로 구성되는데, 여기서 픽셀당 비트의 수는 비디오 데이터 포맷 기술자 워드의 비트 3 내지 0으로 한정된다. 픽셀 그룹 패턴은 도11E에 도시된 바와 같이 비트 5 및 4로 한정된다. 픽셀 데이터의 순서는 수평 또는 수직일 수 있으며, 행 또는 열에서의 픽셀은 순방향 또는 역방향 순서로 전송될 수도 있으며, 비트 8 내지 6으로 한정된다. 비트 11 내지 9는 0으로 설정된다. Bayer 포맷에서 픽셀 그룹의 4개의 픽셀 그룹은 소정의 디스플레이 기술에서 단일 픽셀로 종종 언급되는 것과 유사하다. 그러나 Bayer 포맷에서 하나의 픽셀은 픽셀 그룹 모자이크 패턴의 4개의 컬러링 된 픽셀 중 하나이다.

도면에 도시된 모든 5개 포맷의 경우, "P"로 표시된 비트 12는 픽셀 데이터 샘플이 패킹된 픽셀 데이터인지 또는 바이트 정렬된 픽셀 데이터인 지 여부를 규정한다. 이러한 필드에서의 '0'의 값은 픽셀 데이터 필드에서 각각의 픽셀이 MDD 인터페이스 바이트 경계와 바이트 정렬되는 것을 나타낸다. '1'의 값은 각각의 픽셀 및 각각의 픽셀 내의 각각의 컬러가 이전 픽셀 또는 픽셀 내의 컬러에 대해 패킹-업되어, 사용되지 않는 비트를 남기지 않음을 나타낸다. 바이트 정렬과 패킹된 픽셀 데이터 포맷 사이의 차이는 도12에 더욱 상세하게 도시되며, 데이터 서브 프레임의 사용되지 않는 부분을 남기지 않는 패킹된 픽셀 포맷과 대조적으로, 데이터 서브 프레임의 사용되지 않은 부분을 남길 수 있음을 보여준다.

특정 디스플레이 윈도우에 대한 미디어 프레임의 제1 비디오 스트림 패킷에서 제1 픽셀은 X 좌측 에지 및 Y 상부 에지에 의해 정의된 스트림 윈도우의 상부 좌측 코너로 진행할 것이며, 수신된 다음의 픽셀은 동일한 행의 다음 픽셀 위치에 배치된다. 미디어 프레임의 이러한 제1 패킷에서, X 시작 값은 X 좌측 가장 자리와 통상적으로 동일하며, Y 시작 값은 통상적으로 Y 상부 에지와 동일할 것이다. 동일한 스크린 윈도우에 대응하는 뒤이은 패킷에서, X 및 Y 시작 값은 통상적으로 앞선 서브 프레임에서 송신된 비디오 스트림 패킷에서 전송된 최종 픽셀을 뒤 따르는 스크린 윈도우에서의 픽셀 위치로 설정될 것이다.

4. 오디오

스트림

패킷

오디오 스트림 패킷들은 클라이언트의 오디오 시스템을 통해, 또는 독립 오디오 프리젠테이션 장치를 통해 플레이되는 오디오 데이터를 전달한다. 상이한 오 디오 데이터 스트림들이 사운드 시스템의 개별 오디오 채널들에 할당될 수 있다:예를 들면, 사용되는 오디오 시스템 타입에 따라 좌측-전방, 우측-전방, 중앙, 좌측-후방, 및 우측-후방. 오디오 채널들의 완전한 보완은 강화된 공간-음향 신호 처리를 포함하는 헤드셋을 통해 제공된다. 클라이언트는 클라이언트 성능 패킷의 오디오 채널 성능 및 오디오 샘플 레이트 필드들을 사용하여 오디오 스트림 패킷을 수신한다. 오디오 스트림 패킷의 포맷은 도 13에 제시된다.

도 13에 제시된 바와 같이, 이러한 타입의 패킷은 일 실시예에서 패킷 길이, 패킷 타입, bClient ID, 오디오 채널 ID, 예약 1, 오디오 샘플 카운트, 샘플 및 패킹당 비트, 오디오 샘플 레이트, 파라미터 CRC, 디지털 오디오 데이터, 및 오디오 데이터 CRC 필드들을 가지도록 구성된다. 일 실시예에서, 이러한 타입의 패킷은 일반적으로 타입 32 패킷으로 식별된다.

bClient ID 필드는 이전에 사용된 것과 같이 클라이언트 ID를 위해 예약되는 2 바이트 정보를 포함한다. 예약 1 필드는 차후 사용을 위해 예약되는 2 바이트를 포함하고, 일반적으로 이 지점에서 모든 비트들은 0으로 설정되도록 구성된다.

샘플 및 패킹당 비트들 필드는 오디오 데이터의 패킹 포맷을 규정하는 부호를 갖지 않는 8비트 정수 형태의 1 바이트를 포함한다. 이러한 사용되는 포맷은 일반적으로 PCM 오디오 샘플당 비트들의 수를 정의하기 위한 비트 4 내지 0을 위한 것이다. 비트 5는 디지털 오디오 데이터 샘플들이 패킹되는지 여부를 규정한다. 패킹 및 바이트-정렬 오디오 샘플들 사이의 차이는(여기서, 10비트 샘플들을 사용함) 도 14에 제시된다. 값 "0"은 디지털 오디오 데이터 필드 내의 각각의 PCM 오 디오 샘플이 MDDI 인터페이스 바이트 경계와 바이트-정렬된다는 것을 표시하고, 값 "1"은 각각의 연속적인 PCM 오디오 샘플이 이전 오디오 샘플과 패킹된다는 것을 표시한다. 이러한 비트는 일반적으로 비트 4-0에서 정의되는 값(PCM 오디오 샘플당 비트들의 수)이 8의 배수가 아닌 경우에만 효과적이다. 비트 7-6은 차후 사용을 위해 예약되고, 일반적으로 0 값으로 설정된다.

5. 예약된

스트림

패킷

일 실시예에서, 패킷 타입 1 내지 15, 18 내지 31, 및 33 내지 55는 다양한 애플리케이션에 요구되는 바와 같이, 미래의 버전 또는 패킷 프로토콜의 변화시에 사용하기 위해 정의되는 스트림 패킷을 위해 예약된다. 또한, 이는 다른 기술과 비교하여 기술 및 시스템의 변화에 직면하여 MDD 인터페이스가 더욱 유연하고 유용하게 하는 부분이다.

6. 사용자 정의된

스트림

패킷

타입 56 내지 63으로 알려진 8개의 데이트 스트림 타입은 MDDI 링크와 사용하기 위해 설비 제조자에 의해 정의될 수도 있는 적절한 애플리케이션에 사용하기 위해 예비된다. 이들은 사용자 정의 스트림 패킷으로 알려져 있다. 이러한 패킷은 소정의 목적을 위해 사용될 수도 있지만, 호스트 및 클라이언트는 이러한 사용의 결과가 잘 이해되고 알려지는 상황에서만 상기 패킷을 사용한다. 이러한 패킷 타입에 대한 스트림 파라미터 및 데이터의 특정한 정의는 이러한 패킷 타입을 구현 하고 이들의 사용을 탐색하는 특정한 설비 제조자 또는 인터페이스 설계자에 남겨진다. 사용자 정의 스트림 패킷의 몇몇 사용예는 테스트 파라미터 및 테스트 결과, 공장 고정 데이터, 및 주변 특정 사용 데이터를 운반하는 것이다. 일 실시예에서 사용된 바와 같은 사용자 정의 스트림 패킷의 포맷은 도15에 도시된다. 도15에 도시된 바와 같이, 이러한 타입의 패킷은 패킷 길이(2바이트), 패킷 타입, b클라이언트 ID 번호, 스트림 파라미터, 파라미터 CRC, 스트림 데이터, 및 스트림 데이터 CRC 필드를 갖도록 구성된다.

7. 컬러 맵 패킷

컬러 맵 패킷은 클라이언트에 대해 컬러를 제공하기 위해 사용되는 컬러 맵 룩업 테이블의 컨텐츠를 설명한다. 일부 애플리케이션은 단일 패킷에서 송신가능한 데이터의 양보다 더 큰 컬러 맵을 필요로 할 수도 있다. 이러한 경우, 후술되는 각각의 칼라맵 패킷이 아래에서 설명되는 오프셋 및 길이 필드를 사용함으로써 컬러 맵의 상이한 서브셋을 갖는, 다수의 컬러 맵 패킷들이 전송될 수 있다. 일 실시예에서 컬러 맵 패킷의 포맷은 도16에 도시된다. 도16에 도시된 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, h클라이언트 ID, 컬러 맵 아이템 카운트, 컬러 맵 오프셋, 파라미터 CRC, 컬러 맵 데이터, 및 데이터 CRC 필드를 갖도록 구성된다. 일 실시예에서, 이러한 타입의 패킷은 일반적으로 패킷 타입 필드(2바이트)에 규정된 바와 같이 타입 64 패킷(비디오 데이터 포맷 및 컬러 맵 패킷)으로서 식별된다. 클라이언트는 클라이언트 성능 패킷의 컬러 맵 폭 필드와 컬러 맵 크기를 사용하여 컬러 맵 패킷을 수신하는 성능을 나타낸다.

8. 역방향 링크 캡슐화 패킷

일 실시예에서, 데이터는 역방향 링크 캡슐화 패킷을 이용하여 역방향으로 전송된다. 순방향 패킷이 전송되며 MDDI 링크 연산(전송 방향)은 패킷이 역방향으로 전송될 수 있도록 이러한 패킷의 중앙 부근에서 변경 또는 전환된다. 일 실시예에서 역방향 링크 캡슐화 패킷의 포맷은 도17에 도시된다. 도17에 도시된 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, h클라이언트 ID, 역방향 링크 플래그, 역방향 레이트 제수, 전환(turn around) 1, 역방향 데이터 패킷, 전환(turn around) 2, 및 모두 제로(all-zero) 2 필드를 갖도록 구성된다. 일 실시예에서, 이러한 타입의 패킷은 일반적으로 타입65 패킷으로 식별된다. 외부 모드에 대해, 모든 호스트는 이러한 패킷을 생성하고 데이터를 수신해야 하며, 모든 클라이언트는 요구된 프로토콜 및 결과적인 속도의 사용을 효율적으로 이용하기 위해 호스트로 데이터를 전송할 수 있어야 한다. 이러한 패킷의 구현은 인터넷 모드에 대해 선택적이지만, 역방향 링크 캡슐화 패킷은 클라이언트로부터 데이터를 수신하기 위해 호스트에 대해 사용된다.

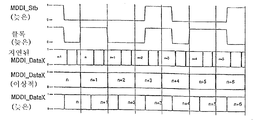

MDDI 링크 제어기는 역방향 링크 캡슐화 패킷을 전송하면서 특정한 방식으로 동작한다. MDD 인터페이스는 링크의 제어기로서 호스트에 의해 일반적으로 항상 구동되는 스트로브 신호를 갖는다. 호스트는 역방향 링크 캡슐화 패킷의 전환(turn around) 및 역방향 데이터 패킷 부분의 각각의 비트에 대해 0을 송신하는 것처럼 동작한다. 호스트는 두 개의 전환(turn around) 시간 동안 그리고 역방향 데이터 패킷에 대해 한정된 시간 동안 각각의 비트 경계에서 MDDI_스트로브 신호를 토글한다. (이는 모두 제로 데이터를 송신하는 것과 동일한 특성이다.)

호스트는 전환(turn around)1에 의해 규정된 시간 주기 동안 MDDI 데이터 신호 라인 드라이버를 디세이블하고, 클라이언트는 전환(turn around) 2 필드에 의해 규정된 시간 주기 후에 드라이버 리인에이블 필드 동안 자신의 라인 드라이버를 리인에이블한다. 클라이언트는 전환(turn around) 길이 파라미터를 판독하고 전환(turn around) 1 필드에서 마지막 비트 후에 즉시 호스트를 향해 데이터 신호를 구동시킨다. 즉, 클라이언트는 이하의 패킷 컨텐츠에서 설명되고 곳곳에서 설명된 바와 같이, 새로운 데이터를 MDDI 스트로브의 소정의 상승 에지에 대한 링크로 클록킹한다. 클라이언트는 패킷을 호스트로 전송할 수 있는 시간의 길이를 알기 위해 패킷 길이 및 전환(turn around) 길이 파라미터를 이용한다. 클라이언트는 호스트로 전송한 데이터가 없는 경우 채움 패킷을 전송하거나 데이터 라인을 0으로 구동시킬 수도 있다. 만일 데이터 라인이 0으로 구동되면, 호스트는 이를 0의 길이(유효한 길이가 아님)를 가진 패킷으로 해석하고, 호스트는 현재의 역방향 링크 캡슐화 패킷의 지속 기간 동안 클라이언트로부터 소정 이상의 패킷을 수신하지 않는다.

호스트는 MDDI_데이터 신호를 모두 제로 1 필드 동안 로직 제로 레벨로 구동시키고, 클라이언트는 전환(turn around) 2 필드의 시작 전에, 즉 모두 제로 2 필드 기간 동안 적어도 하나의 역방향 링크 클록 기간 동안 MDDI 데이터 라인을 로직 제로 레벨로 구동시킨다. 이는 데이터 라인을 전환(turn around) 1 및 전환(turn around) 2 필드 시간 기간 동안 결정론적인(deterministic) 상태로 유지시킨다. 만일 클라이언트가 전송할 더이상의 패킷이 없는 경우, 절전 바이어스 레지스터(다른 곳에서 설명함)가 역방향 데이터 패킷 필드의 나머지에 대해 또는 약 16개의 순방향 링크 또는 그 이상의 기간에 대해 논리 제로 레벨로 데이터 라인을 유지하기 때문에, 클라이언트는 패킷들을 구동시킨 후 데이터 라인을 로직 제로 레벨로 디세이블할 수도 있다.

일 실시예에서, 클라이언트 요청 및 상태 패킷의 역방향 링크 요청 필드는 클라이언트가 데이터를 호스트로 다시전송하기 위해 역방향 링크 캡슐화 패킷에서 필요로 하는 바이트의 수를 호스트에게 통보하는데 사용될 수도 있다. 호스트는 역방향 링크 캡슐화 패킷에서 바이트의 최소한의 수를 할당함으로써 요청을 승인하도록 시도한다. 호스트는 서브 프레임에서 하나 이상의 역방향 링크 캡슐화 패킷을 전송할 수도 있다. 클라이언트는 클라이언트 요청 및 상태 패킷을 거의 언제든지 전송할 수 있으며, 호스트는 하나의 서브 프레임에서 요청된 바이트의 전체 수로서 역방향 링크 요청 파라미터를 해석할 것이다.

9. 클라이언트 성능 패킷

호스트는 일반적으로 최적 또는 원하는 방식으로 호스트 대 클라이언트 링크를 구성하기 위해서 통신하고 있는 클라이언트(디스플레이)의 성능을 알 필요가 있다. 디스플레이가 순방향 링크 동기화가 획득된 후 호스트로 클라이언트 성능 패 킷을 전송하는 것이 권장된다. 이러한 패킷의 전송은 역방향 링크 캡슐화 패킷에서 역방향 링크 플래그를 이용하는 호스트에 의해 요청될 때 요구된다. 클라이언트 성능 패킷은 호스트에게 클라이언트의 성능을 통보하기 위해 사용된다. 외부 모드의 경우, 모든 호스트는 이러한 패킷을 수신할 수 있어야 하며, 모든 클라이언트는 이러한 인터페이스 및 프로토콜을 전적으로 이용하기 위해 이러한 패킷을 전송할 수 있어야 한다. 이러한 패킷의 구현은 인터넷 모드에 대해 선택적인데, 이는 이러한 상황에서 디스플레이, 키보드 또는 다른 입/출력 장치와 같은 클라이언트의 성능이 미리 잘 한정되고 소정 타입의 단일 구성 또는 유닛으로 제조 또는 어셈블리시 호스트에 알려져야 하기 때문이다.

일 실시예에서 클라이언트 성능 패킷의 포맷은 도18에 도시된다. 도18에 도시된 바와 같이, 이러한 실시예의 경우, 이러한 패킷의 타입은 패킷 길이, 패킷 타입, 예약된 cCLIENT ID, 프로토콜 버전, 최소 프로토콜 버전, 데이터 레이트 성능, 인터페이스 타입 성능, Alt 디스플레이의 수, 예약 1, 비트맵 폭, 비트맵 높이, 디스플레이 윈도우 폭, 디스플레이 윈도우 높이, 컬러 맵 크기, 컬러 맵 RGB 폭, RGB 성능, 색상 성능, 예약 2, Y, Cr Cb 성능, Bayer 성능, 알파-커서 이미지 평면, 클라이언트 특성 성능, 최대 비디오 프레임 레이트, 최소 비디오 프레임 레이트, 최소 서브 프레임 레이트, 오디오 버퍼 깊이, 오디오 채널 성능, 오디오 샘플 레이트 성능, 오디오 샘플 해상도, 최소 오디오 샘플 해상도, 최소 샘플 레이트 성능, 키보드 데이터 포맷, 포인팅 장치 데이터 포맷, 컨텐츠 보호 타입, Mfr. 명칭, 제조 코드, 예약 3, 일련 번호, 주간 Mfr, 연간 Mfr, 및 CRC 필드를 갖도록 구성된다. 실시예에서, 이러한 타입의 패킷은 일반적으로 타입 66 패킷으로 식별된다.

*10. 키보드 데이터 패킷

키보드 데이터 패킷은 클라이언트로부터의 키보드 데이터를 호스트로 전송하는데 사용된다. 무선(또는 유선) 키보드는 헤드 장착된 비디오 디스플레이/오디오 제공 장치를 포함하는 다양한 디스플레이 또는 오디오 장치와 관련하여 사용되지만 이에 한정되지 않는다. 키보드 데이터 패킷은 몇몇 공지된 키보드형 장치로부터 수신된 키보드 데이터를 호스트로 전달한다. 이러한 패킷은 데이터를 키보드로 전송하기 위해 순방향 링크에 사용될 수도 있다. 클라이언트는 클라이언트 성능 패킷에서 키보드 데이터 필드를 이용하여 키보드 데이터 패킷을 전송 및 수신하는 성능을 표시한다.

키보드 데이터 패킷의 포맷은 도19에 도시되며, 키보드로부터 또는 키보드에 대한 정보의 가변 수의 정보 바이트들을 포함한다. 도19에 도시된 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, b클라이언트 ID, 키보드 데이터 포맷, 키보드 데이터, 및 CRC 필드를 갖도록 구성된다. 여기서, 이러한 타입의 패킷은 일반적으로 타입 67 패킷으로 식별된다.

b클라이언트 ID는 전술한 바와 같이 예비된 필드이며, CRC는 패킷의 전체 바이트에 대해 실행된다. 키보드 데이터 포맷 필드는 키보드 데이터 포맷을 규정하는 2바이트 값을 포함한다. 비트 6 내지 0은 클라이언트 성능 패킷에서 키보드 데 이터 포맷 필드와 동일해야 한다. 이러한 값은 127과 동일하지 않다. 비트 15 내지 7은 미래의 사용을 위해 예비되고, 결국 현재 0으로 설정된다.

11.

포인팅

장치 데이터 패킷

포인팅 장치 데이터 패킷은 무선 마우스 또는 다른 포인팅 장치로부터의 위치 정보를 클라이언트로부터 호스트로 전송하기 위한 방법, 구조 또는 수단으로 사용된다. 데이터는 이러한 패킷을 사용하여 순방향 링크 상의 포인팅 장치로 송신될 수 있다. 포인팅 장치 데이터 패킷의 포맷의 예는 도20에 도시되며, 포인팅 자치로부터 또는 그에 대한 가변 수의 정보 바이트들을 포함한다. 도20에 도시된 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, b클라이언트 ID, 포인팅 장치 포맷, 포인팅 장치 데이터, 및 CRC 필드를 갖도록 구성된다. 실시예에서, 이러한 타입의 패킷은 일반적으로 1-바이트 타입 필드에서 타입 68 패킷으로 식별된다.

12. 링크

셧다운

패킷

링크 셧다운 패킷은 MDDI 데이터 및 스트로브가 셧다운되고 저전력 소비 "절전" 상태로 진입할 것을 나타내는 방법 또는 수단으로서 호스트로부터 클라이언트로 전송된다. 이러한 패킷은 링크를 셧다운하는데 사용되며, 정적 비트맵이 이동통신 장치로부터 디스플레이로 전송된 후 또는 당분간 호스트로부터 클라이언트로 전송할 추가의 정보가 없는 경우, 전력을 보전한다. 정상 동작은 호스트가 패킷들을 다시 전송하는 경우에 재개된다. 절전 모드 후에 전송되는 제 1 패킷은 서브 프레임 헤더 패킷이다. 일 실시예에 대한 클라이언트 상태 패킷의 포맷은 도 21에 제시된다. 도 21에 제시된 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, CRC 필드 및 모두 제로 필드들을 갖도록 구성된다. 일 실시예에서, 이러한 타입의 패킷은 일반적으로 1-바이트 타입 필드에서 타입 69 패킷으로 식별된다.

패킷 길이 필드는 패킷 길이 필드를 포함하지 않고 패킷에서 전체 바이트의 수를 규정하기 위해 2바이트를 사용한다. 일 실시예에서, 이러한 패킷의 패킷 길이는 링크 셧다운 패킷이 전송된 시간에서 인터넷 타입 또는 링크 모드에 의존한다. 따라서, 통상의 패킷 길이는 타입 1 모드에 대해 20바이트(패킷에서 총 22바이트), 타입 2 모드에 대해 36바이트(패킷에서 총 38바이트), 타입 3 모드 링크에 대해 68바이트(패킷에서 총 70바이트), 및 타입 4 모드에 대해 132 바이트(패킷에서 총 134 바이트)가 된다.

모두 제로 필드는 MDDI_Data 신호가 충분한 시간 동안 로직 제로 레벨에 있어서 클라이언트가 호스트의 라인 드라이버를 디세이블하기 전에 단지 MDDI_Stb를 이용하여 클록을 복구하기 시작하는 것을 보장하기 위해 가변 수의 바이트들을 사용한다. 모두 제로 필드의 길이는 링크 셧 다운 패킷이 전송된 시간에 인터페이스 타입 또는 링크 동작 모드에 의존한다. 모두 제로 필드의 길이는 소정의 인터페이스 타입 세팅에 대해 MDDI_Stb에 대한 64 펄스를 생성하도록 의도된다. 따라서, 각각의 인터페이스 타입에 대한 모두 제로 길이는 타입1에 대해 16바이트, 타입2에 대해 32바이트, 타입3에 대해 64바이트, 및 타입4에 대해 128바이트가 된다.

CRC 필드는 패킷 길이로부터 패킷 타입까지의 바이트의 16비트 CRC를 포함하 는 2바이트를 사용한다.

저전력 절전 상태에서, MDDI_Data() 드라이버는 모두 제로 필드의 최종 비트 이후 16 내지 48번째 MDDI_Stb 사이클 이후 시작하는 높은 임피던스 상태로 디세이블된다. 타입-2, 타입-3, 또는 타입-4 링크에 대해, MDDI_Data 1 내지 MDDI_DataPwr 7 신호들은 높은 임피던스 상태로 배치되는데, 동시에 MDDI_Data() 드라이버는 디세이블된다. 호스트 또는 클라이언트는 MDDI 링크가 절전 상태로부터 깨어나도록 할 수도 있는데, 이는 본 발명의 장점을 위한 핵심적인 사항이다.

모두 제로 필드의 정의에서 설명한 바와 같이, MDDI_Stb는 클라이언트 제어기에서 정연하게 셧다운을 용이하게 하기 위해 링크 셧다운 패킷의 CRC 필드의 MSB 직후의 64 사이클 동안 토글링한다. 일 사이클은 하이-투-로우 전이에 앞서는 로우-투-하이 전이이거나, 로우-투-하이 전이에 앞서는 하이-투-로우 전이이다. 모두 제로 필드가 전송된 후, 호스트에서 MDDI_Stb 드라이버는 디세이블된다.

13. 클라이언트 요청 및 상태 패킷들

호스트는 일반적으로 최적의 방식으로 호스트-클라이언트 링크를 구성하기 위해서 클라이언트로부터 적은 양의 정보를 필요로 한다. 클라이언트는 하나의 클라이언트 요청 및 상태 패킷을 호스트로 각각의 서브 프레임에서 전송하는 것이 바람직하다. 클라이언트는 이러한 패킷이 신뢰성 있게 호스트로 전달되는 것을 보장하기 위해서 역방향 링크 캡슐화 패킷의 제 1 패킷으로서 이러한 패킷을 전송하여야 한다. 이러한 패킷의 전송은 또한 역방향 링크 캡슐화 패킷의 역방향 링크 플 래그들을 사용하여 호스트에 의해 요청되는 경우에 또한 수행된다. 클라이언트 요청 및 상태 패킷은 호스트로 에러 및 상태를 보고하는데 사용된다. 외부 모드 동작에 대해, 모든 호스트는 이러한 패킷을 수신할 수 있어야 하며, 모든 클라이언트는 적절하게 또는 최적으로 MDD 인터페이스 프로토콜을 사용하기 위해서 이러한 패킷을 전송할 수 있어야 한다. 내부 연산을 위해 내부 호스트 및 내부 클라이언트가 권장되지만, 이러한 패킷에 대해 지원될 수 있으며, 이는 요구되지 않는다.

클라이언트 요청 및 상태 패킷의 포맷은 도 22에 제시된다. 도 22에 제시되는 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, cClient ID, 역방향 링크 요청, 성능 변경, 클라이언트 비지, CRC 에러 카운트, 및 CRC 필드들을 갖도록 구성된다. 이러한 타입의 패킷은 일반적으로 1 바이트 타입 필드에서 타입 70 패킷으로 식별되고, 일반적으로 미리 선택된 고정된 12 바이트 길이를 사용한다.

역방향 링크 요청 필드는 데이터를 다시 호스트로 전송하기 위해서 역방향 링크 캡슐화 패킷에서 클라이언트가 필요한 바이트들의 수를 호스트에게 통보하는데 사용된다. 호스트는 역방향 링크 캡슐화 패킷에서 적어도 그 숫자만큼의 바이트를 할당함으로써 그 요청의 허용을 시도하여야 한다. 호스트는 데이터를 수용하기 위해서 서브 프레임에서 하나 이상의 역방향 링크 캡슐화 패킷을 전송할 수도 있다. 클라이언트는 클라이언트 요청 및 상태 패킷을 임의의 시점에서 전송할 수 있고, 호스트는 하나의 서브 프레임에서 요청된 바이트들의 총 수로서 역방향 링크 요청 파라미터를 해석할 것이다. 역방향 링크 데이터가 다시 호스트로 어떻게 전송되는 지에 관한 구체적인 내용 및 예는 후술될 것이다.

14. 비트 블록 전송 패킷

비트 블록 전송 패킷은 임의의 방향에서 디스플레이 영역들을 스크롤하는 수단, 구성 또는 방법을 제공한다. 이러한 성능을 갖는 디스플레이들은 클라이언트 성능 패킷의 디스플레이 특징 성능 표시자의 비트 0에서 이러한 성능을 보고할 것이다. 비트 블록 전송 패킷의 일 실시예에 대한 포맷은 도 23에 제시된다. 도 23에 제시되는 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, hClient ID, 상부 좌측 X 값, 상부 좌측 Y 값, 윈도우 폭, 윈도우 높이, 윈도우 X 이동, 윈도우 Y 이동, 및 CRC 필드들을 갖도록 구성된다. 이러한 타입의 패킷은 일반적으로 타입 71 패킷으로 식별되고, 일 실시예에서 미리 선택된 고정된 15 바이트 길이를 사용한다.

이러한 필드들은 이동될 윈도우의 상부 좌측 코너 좌표의 X 및 Y 값, 이동될 윈도우의 폭 및 높이, 및 픽셀들의 수를 규정하는데 사용되어 윈도우가 수평 및 수직으로 각각 이동되도록 한다. 상기 후자의 2개의 필드의 양의 값은 윈도우가 우측 및 아래로 이동하도록 하고, 음의 값은 좌측 및 상부로 이동하도록 한다.

15. 비트맵 영역 채움 패킷

비트맵 영역 채움(fill) 패킷은 디스플레이 영역을 하나의 컬러로 쉽게 초기화하는 수단, 구성 또는 방법을 제공한다. 이러한 성능을 갖는 디스플레이들은 클라이언트 성능 패킷의 클라이언트 특징 성능 표시자 필드의 비트 1에서 이러한 성 능을 표시할 것이다. 비트맵 영역 채움 패킷의 포맷에 대한 일 실시예는 도 24에 제시된다. 도 24에 제시되는 바와 같이, 이러한 경우, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, hClient ID, 상부 좌측 X 값, 상부 좌측 Y 값, 윈도우 폭, 윈도우 높이, 데이터 포맷 기술자, 픽셀 영역 채움값, 및 CRC 필드를 갖도록 구성된다. 이러한 타입의 패킷은 일반적으로 1 바이트 타입 필드에서 타입 72 패킷으로 식별되고, 미리 선택된 고정된 17 바이트 길이를 사용한다.

16. 비트맵 패턴 채움 패킷

비트맵 패턴 채움(fill) 패킷은 디스플레이 영역을 미리 선택된 패턴으로 쉽게 초기화하는 수단 또는 구조를 제공한다. 이러한 능력을 갖는 디스플레이는 클라이언트 성능 패킷의 클라이언트 특징 성능 필드의 비트 2에서 이러한 성능을 보고할 것이다. 이러한 채움 패턴의 상부 좌측 코너는, 수평 또는 수직 패턴 오프셋이 비 제로가 아니라면, 채워질 윈도우의 상부 좌측 코너와 정렬된다. 채워질 윈도우가 채움 패턴보다 넓거나 길면, 패턴은 윈도우를 채우기 위해서 수평 또는 수직으로 여러 번 반복될 것이다. 최종 반복된 패턴의 우측 또는 바닥은 필요에 따라 잘려진다(truncated). 윈도우가 채움 패턴보다 작으면, 채움 패턴의 우측 또는 바닥은 윈도우와 맞추기 위해서 잘려진다.

만일 수평 패턴 오프셋이 비제로이면, 윈도우의 좌측 사이드와 수평 패턴 오프셋을 더한 우측 사이드 사이의 픽셀들은 패턴의 가장 우측 픽셀로 채워진다. 수평 패턴 오프셋은 패턴 폭보다 작을 것이다. 유사하게, 수직 패턴 오프셋이 비제 로이면, 위도우의 상부측과 수직 패턴 오프셋을 더한 측면의 상부 사이의 픽셀은 가장 낮은 패턴의 픽셀로 채워진다. 수직 패턴 오프셋은 패턴 높이보다 적을 것이다.

비트맵 패턴 채움 패킷의 포맷에 대한 일 실시예는 도 25에 제시된다. 도 25에 제시되는 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, hClient ID, 상부 좌측 X 값, 상부 좌측 Y 값, 윈도우 폭, 윈도우 높이, 패턴 폭, 패턴 높이, 수평 패턴 오프셋, 수직 패턴 오프셋, 데이터 포맷 기술자, 파라미터 CRC, 패턴 픽셀 데이터, 및 픽셀 데이터 CRC 필드를 갖도록 구성된다. 소정의 실시예에서, 이러한 타입의 패킷은 일반적으로 1 바이트 타입 필드에서 타입 73 패킷으로 식별된다.

17. 통신 링크 데이터 채널 패킷

통신 링크 데이터 채널 패킷은 PDA와 같은 고-레벨 계산 성능을 갖는 클라이언트가 셀룰러 전화 또는 무선 데이터 포트 장치와 같은 무선 트랜시버와 통신하는 구성, 수단 또는 방법을 제공한다. 이러한 상황에서, MDDI 링크는 통신 장치와 이동 디스플레이를 갖는 계산 장치 사이의 편리한 고속 인터페이스로서 동작하고, 여기서 이러한 패킷은 그 장치에 대한 운영 시스템의 데이터 링크 계층에서 데이터를 전달한다. 예를 들어, 웹 브라우저, 이메일 클라이언트, 또는 PDA가 이동 디스플레이 내에 구축되는 경우, 이러한 패킷이 사용될 수 있다. 이러한 성능을 갖는 디스플레이들은 클라이언트 성능 패킷의 클라이언트 특징 성능 필드의 비트 3에서 이 러한 성능을 보고할 것이다.

통신 링크 데이터 채널 패킷에 대한 일 실시예의 포맷은 도 26에 제시된다. 도 26에 제시되는 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, hClient ID, 파라미터 CRC, 통신 링크 데이터, 및 통신 데이터 CRC 필드를 갖도록 구성된다. 일 실시예에서, 이러한 타입의 패킷은 일반적으로 타입 필드에서 타입 74 패킷으로 식별된다.

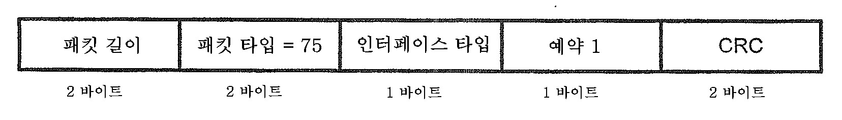

18. 인터페이스 타입 핸드오프 요청 패킷

인터페이스 타입 핸드오프 요청 패킷은 호스트로 하여금, 클라이언트 또는 디스플레이가 기존 또는 현재 모드에서 타입 1(직렬), 타입 2(비트 병렬), 타입 3(4 비트 병렬), 또는 타입 4(8 비트 병렬) 모드로 이동하도록 하는 요청을 할 수 있도록 하는 수단, 방법 또는 구조를 제공한다. 호스트가 특정 모드를 요청하기 전에, 호스트는 클라이언트 성능 패킷의 디스플레이 특징 성능 표시자의 비트 6 및 7을 검사하여 클라이언트가 요구되는 모드에서 동작할 수 있다는 것을 확인하여야 한다. 인터페이스 타입 핸드오프 요청 패킷의 포맷에 대한 일 실시예는 도 27에 제시된다. 도 27에 제시되는 바와 같이, 이러한 타입의 패킷은 패킷 길이, 패킷 타입, 인터페이스 타입, 예약 1, 및 CRC 필드를 갖도록 구성된다. 이러한 타입의 패킷은 일반적으로 타입 75 패킷으로서 식별되고, 미리 선택된 고정된 4 바이트 길이를 사용한다.

19. 인터페이스 타입 확인 패킷