JP6115505B2 - 電子装置 - Google Patents

電子装置 Download PDFInfo

- Publication number

- JP6115505B2 JP6115505B2 JP2014065942A JP2014065942A JP6115505B2 JP 6115505 B2 JP6115505 B2 JP 6115505B2 JP 2014065942 A JP2014065942 A JP 2014065942A JP 2014065942 A JP2014065942 A JP 2014065942A JP 6115505 B2 JP6115505 B2 JP 6115505B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- mold resin

- electronic device

- mold

- electronic component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000758 substrate Substances 0.000 claims description 193

- 229920005989 resin Polymers 0.000 claims description 124

- 239000011347 resin Substances 0.000 claims description 124

- 238000007789 sealing Methods 0.000 claims description 27

- 238000000465 moulding Methods 0.000 claims description 12

- 238000005520 cutting process Methods 0.000 description 15

- 238000000034 method Methods 0.000 description 13

- 238000004519 manufacturing process Methods 0.000 description 6

- 238000012986 modification Methods 0.000 description 6

- 230000004048 modification Effects 0.000 description 6

- 239000000463 material Substances 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 3

- 239000002344 surface layer Substances 0.000 description 3

- 239000003822 epoxy resin Substances 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 238000001721 transfer moulding Methods 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000006835 compression Effects 0.000 description 1

- 238000007906 compression Methods 0.000 description 1

- 238000000748 compression moulding Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- PCHJSUWPFVWCPO-RNFDNDRNSA-N gold-201 Chemical compound [201Au] PCHJSUWPFVWCPO-RNFDNDRNSA-N 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 239000010410 layer Substances 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3121—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed a substrate forming part of the encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/561—Batch processing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19105—Disposition of discrete passive components in a side-by-side arrangement on a common die mounting substrate

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Geometry (AREA)

- Dicing (AREA)

Description

本発明の第1実施形態について図面を参照しつつ説明する。なお、この電子装置は、例えば自動車等の車両に搭載され、車両用の各装置を駆動するための装置として適用されると好適である。

本発明の第2実施形態について説明する。本実施形態は、第1実施形態に対して第2面40bの形状を変更したものであり、その他に関しては第1実施形態と同様であるため、ここでは説明を省略する。

上記第2実施形態では、ダイシングライン101の中央部上のみでモールド樹脂40が連結されるようにモールド樹脂40を形成する例について説明した。しかしながら、図10に示されるように、ダイシングライン101の中央部上では、各基板10に連結されたモールド樹脂40が連結されず、その両側で各基板10に連結されたモールド樹脂40が連結されるようにしてもよい。

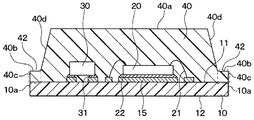

本発明の第3実施形態について図2、図12〜図16を参照して説明する。本実施形態は、第1実施形態に対して、モールド樹脂40のうち電子部品20、30を覆う部分の厚さよりも薄くされた部分(以下、薄肉部42という)の構成を変更したものである。薄肉部42は、具体的には、上記第1実施形態に記載のモールド樹脂40のうち電子部品20、30を覆う部分であって、基板10の一面11における長手方向と平行となる辺の近傍に形成された部分のことである。その他に関しては基本的には第1実施形態と同様であるため、ここでは第1実施形態と異なる部分についてのみを説明する。

上記第3実施形態では、薄肉部42が、基板10の一面11の長手方向において、第4面40dから基板10の一面11の端まで薄肉部42が延設された部分と、第4面40dから薄肉部42が全く延設されていない部分とが交互に配置されていた。しかしながら、図17〜図19に示されるように、第3実施形態において、薄肉部42が第4面40dから全く延設されていない部分における露出領域を挟んで電子部品20、30を封止する部分とは反対側において、該露出領域に当接して封止領域が配置されてもよい。そして、複数の第1電極16は、それぞれ、モールド樹脂40のうち、交互配置部分5の封止領域に位置する部分と、電子部品20、30を封止する部分と、電子部品20、30を封止する部分とは反対側に配置された封止領域に位置する部分とによって囲まれていてもよい。この場合、複数の第1電極16それぞれの周辺が、より高い強度とされるため、より耐振性が優れた電子装置とすることができる。

本発明の第4実施形態について図2、図12、図21〜図23を参照して説明する。本実施形態は、第3実施形態に対して薄肉部42の形状を変更したものであり、その他に関しては基本的には第3実施形態と同様であるため、ここでは第3実施形態と異なる部分のみについて説明する。

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

11 一面

12 他面

20、30 電子部品

40 モールド樹脂

41 溝部

42 薄肉部

43 モールド突出部

100 多連基板

100a 一面

101 ダイシングライン

210 ダイシングブレード

Claims (5)

- 基板(10)と、

前記基板の一面(11)上に搭載された電子部品(20、30)と、

前記電子部品と共に前記基板の一面を封止するモールド樹脂(40)と、を備え、

前記基板における前記一面と反対側の他面(12)が前記モールド樹脂から露出する電子装置であって、

前記モールド樹脂は、前記基板の一面と他面との間の側面の少なくとも1つの側面(10a)と同一平面となる面(40c)を有し、当該面を構成する部分は前記同一平面となる面と連結され、かつ前記基板の一面と平行な面(40b)を有すると共に前記電子部品を封止する部分の厚さよりも薄くされ、

前記モールド樹脂のうち前記基板の前記1つの側面と同一平面となる面(40c)を構成する部分は、前記基板の一面と平行な面であって前記同一平面となる面と連結された面である平行面(40b)を有すると共に、前記モールド樹脂のうち前記平行面を挟んで前記基板の前記1つの側面とは反対側に位置する部分であって前記電子部品を封止する部分の厚さよりも薄くされた薄肉部(42)として構成されており、

前記基板の一面と前記モールド樹脂のうち前記基板の前記1つの側面と同一平面となる面との境界線の方向において、前記薄肉部が形成された封止領域と前記薄肉部が形成されていない露出領域とが交互に配置された部分である交互配置部分(5)を有する構成とされ、

前記交互配置部分における異なる前記露出領域において、前記基板の一面上に異なる電位の電極である複数の第1電極(16)が設けられていることを特徴とする電子装置。 - 前記薄肉部は、異なる前記露出領域に配置された電位の異なる前記第1電極それぞれの間に配置された前記封止領域に位置する前記モールド樹脂の厚さが、該電位の異なる前記第1電極の厚さよりも厚くされていることを特徴とする請求項1に記載の電子装置。

- 前記薄肉部は、前記交互配置部分における前記露出領域を挟んで前記モールド樹脂のうち前記電子部品を封止する部分とは反対側において、前記封止領域が配置された構成とされており、

前記複数の第1電極は、それぞれ、前記モールド樹脂のうち、前記交互配置部分における前記封止領域に位置する部分と、前記電子部品を封止する部分と、前記電子部品を封止する部分とは反対側に配置された前記封止領域に位置する部分と、によって囲まれた構成とされていることを特徴とする請求項1または2に記載の電子装置。 - 前記薄肉部が、前記モールド樹脂のうち前記電子部品を封止する部分を挟んで両側にそれぞれ配置されており、前記基板の一面と前記モールド樹脂のうち前記基板の前記1つの側面と同一平面となる面との境界線の方向において、前記モールド樹脂のうち前記電子部品を封止する部分よりも外側に突出したモールド突出部(43)を有し、

前記基板の一面には、前記モールド突出部を有する前記薄肉部におけるそれぞれの前記モールド突出部の間の領域において、第1電極とは別の電極である第2電極(13)が設けられていることを特徴とする請求項1ないし3のいずれか1つに記載の電子装置。 - 基板(10)と、

前記基板の一面(11)上に搭載された電子部品(20、30)と、

前記電子部品と共に前記基板の一面を封止するモールド樹脂(40)と、を備え、

前記基板における前記一面と反対側の他面(12)が前記モールド樹脂から露出する電子装置であって、

前記基板の一面と他面との間の側面の少なくとも1つの側面(10a)は、前記モールド樹脂と共に切断された切断面とされており、

前記モールド樹脂は、前記基板と共に切断され、前記切断面と同一平面となる面(40c)を有し、当該面を構成する部分は前記同一平面となる面と連結され、かつ前記基板の一面と平行な面(40b)を有すると共に前記電子部品を封止する部分の厚さよりも薄くされ、

前記薄肉部が、前記モールド樹脂のうち前記電子部品を封止する部分を挟んで両側にそれぞれ配置されており、前記基板の一面と前記モールド樹脂のうち前記切断面と同一平面となる面との境界線の方向において、前記モールド樹脂のうち前記電子部品を封止する部分よりも外側に突出したモールド突出部(43)を有し、

前記基板の一面には、前記モールド突出部を有する前記薄肉部におけるそれぞれの前記モールド突出部の間の領域において、第1電極とは別の電極である第2電極(13)が設けられていることを特徴とする電子装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014065942A JP6115505B2 (ja) | 2013-06-21 | 2014-03-27 | 電子装置 |

| PCT/JP2014/002924 WO2014203477A1 (ja) | 2013-06-21 | 2014-06-03 | 電子装置およびその製造方法 |

| US14/894,637 US9941182B2 (en) | 2013-06-21 | 2014-06-03 | Electronic device and method for manufacturing same |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013130304 | 2013-06-21 | ||

| JP2013130304 | 2013-06-21 | ||

| JP2014065942A JP6115505B2 (ja) | 2013-06-21 | 2014-03-27 | 電子装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015026811A JP2015026811A (ja) | 2015-02-05 |

| JP2015026811A5 JP2015026811A5 (ja) | 2015-10-15 |

| JP6115505B2 true JP6115505B2 (ja) | 2017-04-19 |

Family

ID=52104229

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014065942A Active JP6115505B2 (ja) | 2013-06-21 | 2014-03-27 | 電子装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9941182B2 (ja) |

| JP (1) | JP6115505B2 (ja) |

| WO (1) | WO2014203477A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7369510B2 (ja) | 2017-10-16 | 2023-10-26 | 大倉工業株式会社 | ストレッチフィルムを用いたスリーブ包装方法、スリーブ包装用ストレッチフィルム、およびスリーブ包装体の製造方法 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6194804B2 (ja) | 2014-01-23 | 2017-09-13 | 株式会社デンソー | モールドパッケージ |

| CN110785838B (zh) * | 2017-05-02 | 2023-10-24 | 日立能源瑞士股份公司 | 具有暴露的端子区域的树脂封装功率半导体模块 |

Family Cites Families (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01175240A (ja) | 1987-12-28 | 1989-07-11 | Sharp Corp | 半導体チップの製造方法 |

| US5834336A (en) * | 1996-03-12 | 1998-11-10 | Texas Instruments Incorporated | Backside encapsulation of tape automated bonding device |

| JP3569386B2 (ja) | 1996-05-27 | 2004-09-22 | 株式会社ルネサステクノロジ | 半導体集積回路装置の製造方法およびそれにより得られるモジュール基板ならびに電子機器 |

| DE19640304C2 (de) * | 1996-09-30 | 2000-10-12 | Siemens Ag | Chipmodul insbesondere zur Implantation in einen Chipkartenkörper |

| JP3859318B2 (ja) | 1997-08-29 | 2006-12-20 | シチズン電子株式会社 | 電子回路のパッケージ方法 |

| JP2000040711A (ja) | 1998-07-23 | 2000-02-08 | Sony Corp | 樹脂封止型半導体装置とその製造方法 |

| JP2002110718A (ja) | 2000-09-29 | 2002-04-12 | Hitachi Ltd | 半導体装置の製造方法 |

| JP2002190565A (ja) | 2000-12-20 | 2002-07-05 | Taiyo Yuden Co Ltd | ハイブリッドic及びその製造方法 |

| JP3820991B2 (ja) * | 2002-01-08 | 2006-09-13 | 日立電線株式会社 | 半導体装置及びその製造方法 |

| JP2005161695A (ja) * | 2003-12-03 | 2005-06-23 | Towa Corp | 樹脂封止装置及び樹脂封止方法 |

| JP4477976B2 (ja) * | 2004-09-30 | 2010-06-09 | 株式会社ルネサステクノロジ | 半導体装置の製造方法 |

| WO2006129926A1 (en) | 2005-06-02 | 2006-12-07 | Tsp Co., Ltd. | Mold for manufacturing semiconductor device and semiconductor device manufactred using the same |

| JP2007109831A (ja) | 2005-10-13 | 2007-04-26 | Towa Corp | 電子部品の樹脂封止成形方法 |

| FR2893764B1 (fr) * | 2005-11-21 | 2008-06-13 | St Microelectronics Sa | Boitier semi-conducteur empilable et procede pour sa fabrication |

| JP2007281207A (ja) | 2006-04-07 | 2007-10-25 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP4836661B2 (ja) * | 2006-05-17 | 2011-12-14 | Towa株式会社 | 電子部品の樹脂封止成形方法及び樹脂封止成形用金型 |

| JP4376884B2 (ja) * | 2006-09-20 | 2009-12-02 | シャープ株式会社 | 半導体装置及び、半導体装置の製造方法 |

| JP2008082768A (ja) | 2006-09-26 | 2008-04-10 | Kobe Steel Ltd | 熱式流量センサ |

| TWI336502B (en) * | 2006-09-27 | 2011-01-21 | Advanced Semiconductor Eng | Semiconductor package and semiconductor device and the method of making the same |

| JP4926869B2 (ja) | 2007-07-26 | 2012-05-09 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP5157456B2 (ja) * | 2008-01-08 | 2013-03-06 | 富士通セミコンダクター株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP2009170476A (ja) * | 2008-01-11 | 2009-07-30 | Panasonic Corp | 半導体装置および半導体装置の製造方法 |

| DE102008052393B3 (de) | 2008-10-21 | 2010-02-25 | Continental Automotive Gmbh | Massenstromsensorvorrichtung |

| JP2011077199A (ja) * | 2009-09-29 | 2011-04-14 | Sumitomo Bakelite Co Ltd | 半導体パッケージおよび半導体装置 |

| JP2012238725A (ja) | 2011-05-12 | 2012-12-06 | Toshiba Corp | 半導体装置とその製造方法、およびそれを用いた半導体モジュール |

| JP5419230B2 (ja) * | 2011-08-01 | 2014-02-19 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| CN102931105A (zh) * | 2011-08-10 | 2013-02-13 | 飞思卡尔半导体公司 | 半导体器件管芯键合 |

| JP5994613B2 (ja) * | 2012-12-05 | 2016-09-21 | 株式会社デンソー | 電子装置の取付構造体 |

| CN106158778B (zh) * | 2015-03-12 | 2020-07-17 | 恩智浦美国有限公司 | 具有侧面接触垫和底部接触垫的集成电路封装 |

| US9443830B1 (en) * | 2015-06-09 | 2016-09-13 | Apple Inc. | Printed circuits with embedded semiconductor dies |

-

2014

- 2014-03-27 JP JP2014065942A patent/JP6115505B2/ja active Active

- 2014-06-03 WO PCT/JP2014/002924 patent/WO2014203477A1/ja active Application Filing

- 2014-06-03 US US14/894,637 patent/US9941182B2/en not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7369510B2 (ja) | 2017-10-16 | 2023-10-26 | 大倉工業株式会社 | ストレッチフィルムを用いたスリーブ包装方法、スリーブ包装用ストレッチフィルム、およびスリーブ包装体の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2014203477A1 (ja) | 2014-12-24 |

| US20160104653A1 (en) | 2016-04-14 |

| JP2015026811A (ja) | 2015-02-05 |

| US9941182B2 (en) | 2018-04-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10825758B2 (en) | Semiconductor device | |

| JP4600576B2 (ja) | 半導体装置およびその製造方法 | |

| JP6288254B2 (ja) | 半導体モジュールおよびその製造方法 | |

| JP5076549B2 (ja) | 半導体装置 | |

| JP6138500B2 (ja) | パワー半導体装置 | |

| JP6226068B2 (ja) | 半導体装置 | |

| US9905490B2 (en) | Semiconductor device | |

| JP6115505B2 (ja) | 電子装置 | |

| JP2020038914A (ja) | 半導体装置 | |

| EP2571047A2 (en) | Insulating ring for packaging, insulating ring assembly and package | |

| JP6165025B2 (ja) | 半導体モジュール | |

| JP2018157070A (ja) | 半導体装置 | |

| JP2021072329A (ja) | パワー半導体装置 | |

| JP5124329B2 (ja) | 半導体装置 | |

| JP5037398B2 (ja) | 半導体装置 | |

| JP4728032B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP6171841B2 (ja) | 半導体装置 | |

| JP2023006103A (ja) | 半導体装置および樹脂製構造体 | |

| US20180166620A1 (en) | Electronic device | |

| JP5408039B2 (ja) | 電子装置 | |

| JP2020202292A (ja) | 半導体装置、および半導体装置の製造方法 | |

| JP2013175551A (ja) | 半導体装置 | |

| JP2020198351A (ja) | 半導体装置 | |

| JP2009224674A (ja) | 電子装置およびその製造方法 | |

| JP2010135373A (ja) | モールドパッケージおよびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20141126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160404 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160830 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160915 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170221 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170306 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6115505 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |