JP6091239B2 - プリント回路板、プリント配線板および電子機器 - Google Patents

プリント回路板、プリント配線板および電子機器 Download PDFInfo

- Publication number

- JP6091239B2 JP6091239B2 JP2013025454A JP2013025454A JP6091239B2 JP 6091239 B2 JP6091239 B2 JP 6091239B2 JP 2013025454 A JP2013025454 A JP 2013025454A JP 2013025454 A JP2013025454 A JP 2013025454A JP 6091239 B2 JP6091239 B2 JP 6091239B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- branch

- branch point

- signal

- printed

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0237—High frequency adaptations

- H05K1/0246—Termination of transmission lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/023—Detection or location of defective auxiliary circuits, e.g. defective refresh counters in clock generator or timing circuitry

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/025—Detection or location of defective auxiliary circuits, e.g. defective refresh counters in signal lines

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0237—High frequency adaptations

- H05K1/0243—Printed circuits associated with mounted high frequency components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

- H05K1/112—Pads for surface mounting, e.g. lay-out directly combined with via connections

- H05K1/114—Pad being close to via, but not surrounding the via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10007—Types of components

- H05K2201/10159—Memory

Description

図1は、本発明の第1実施形態に係るプリント回路板の一例としてのメモリシステムの配線構成を示すトポロジー図である。プリント回路板であるメモリシステム100は、プリント配線板であるマザーボード200と、送信回路であるメモリコントローラ301と、複数の受信回路である複数のメモリデバイス302A〜302Dと、を備えている。本第1実施形態では、メモリデバイス302A〜302Dは、DDR3−SDRAM(Double Data Rate 3 Synchronous Dynamic Random Access Memory)である。これらメモリコントローラ301及び複数のメモリデバイス302A〜302Dは、マザーボード200に実装されている。

図9は、実施例1の配線構造においてシミュレーションを行った結果を示す波形図である。この図9は、図1の配線構造において、以下の条件でシミュレーションを行った結果である。

次に、本発明の第2実施形態に係るプリント回路板について説明する。図10は、本発明の第2実施形態に係るプリント回路板の一例としてのメモリシステムの配線構成を示すトポロジー図である。なお、上記第1実施形態と同様の構成については、同一符号を付して説明を省略する。

図12は、実施例2の配線構造においてシミュレーションを行った結果を示す波形図である。この図12は、図10の配線構造において、以下の条件でシミュレーションを行った結果である。

次に、本発明の第3実施形態に係るプリント回路板について説明する。図13は、本発明の第3実施形態に係るプリント配線板の一例として、メモリデバイスが実装される付近のマザーボードの平面図である。なお、上記第1、第2実施形態と同様の構成については、同一符号を付している。

Claims (11)

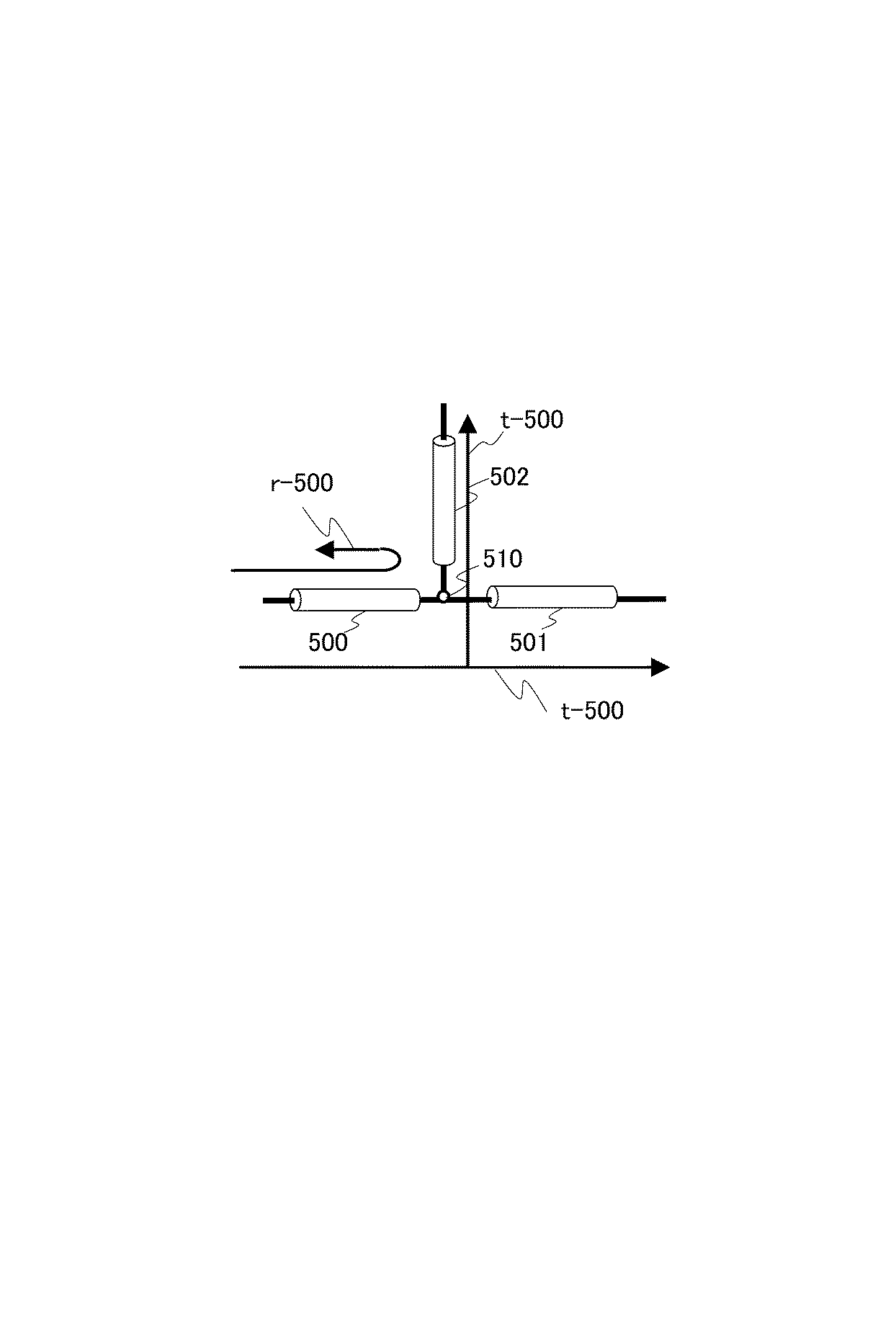

- プリント配線板と、

前記プリント配線板に実装され、送信回路から送信された信号を、前記プリント配線板を介して受信する第1受信回路及び第2受信回路と、を備え、

前記プリント配線板は、

始端が前記送信回路に電気的に接続される主配線と、

一端が前記主配線上の第1分岐点に電気的に接続され、他端が前記第1受信回路に電気的に接続された第1分岐配線と、

一端が前記始端に対して前記第1分岐点よりも遠い前記主配線上の第2分岐点に電気的に接続され、他端が前記第2受信回路に電気的に接続された第2分岐配線と、

前記始端と前記第1分岐点との間の前記主配線上の第1接続点に電気的に接続された第1接続端、及び前記第1接続端に対して反対側の第1開放端を有する第1オープンスタブ配線と、を有していることを特徴とするプリント回路板。 - 前記第1オープンスタブ配線は、5[mm]以上かつ30[mm]以下の配線長に設定されていることを特徴とする請求項1に記載のプリント回路板。

- 前記第1オープンスタブ配線は、前記第1開放端で反射した反射波が、前記第1分岐配線に直接伝搬する直接波に対して所定の第1伝搬遅延時間、遅れて前記第1分岐点に到達する配線長に設定されていることを特徴とする請求項1又は2に記載のプリント回路板。

- 前記プリント配線板は、前記始端と前記第1分岐点との間の前記主配線上の第2接続点に電気的に接続された第2接続端、及び前記第2接続端に対して反対側の第2開放端を有する第2オープンスタブ配線を有し、

前記第2オープンスタブ配線は、前記第2開放端で反射した反射波が、前記第1分岐配線に直接伝搬する直接波に対して所定の第2伝搬遅延時間、遅れて前記第1分岐点に到達する配線長に設定されていることを特徴とする請求項1乃至3のいずれか1項に記載のプリント回路板。 - 前記第2オープンスタブ配線は、5[mm]以上かつ30[mm]以下の配線長に設定されていることを特徴とする請求項4に記載のプリント回路板。

- 前記送信回路が、前記プリント配線板に実装されていることを特徴とする請求項1乃至5のいずれか1項に記載のプリント回路板。

- 前記第1受信回路及び前記第2受信回路が、メモリデバイスであり、

前記送信回路が、前記メモリデバイスを制御するメモリコントローラであることを特徴とする請求項1乃至6のいずれか1項に記載のプリント回路板。 - 前記メモリデバイスが、DDR3−SDRAMであることを特徴とする請求項7に記載のプリント回路板。

- 送信回路、第1受信回路及び第2受信回路のうち、少なくとも前記第1受信回路及び前記第2受信回路が実装されるプリント配線板において、

始端が前記送信回路に電気的に接続される主配線と、

一端が前記主配線上の第1分岐点に電気的に接続され、他端が前記第1受信回路に電気的に接続される第1分岐配線と、

一端が前記始端に対して前記第1分岐点よりも遠い前記主配線上の第2分岐点に電気的に接続され、他端が前記第2受信回路に電気的に接続される第2分岐配線と、

前記始端と前記第1分岐点との間の前記主配線上の接続点に電気的に接続された接続端、及び前記接続端に対して反対側の開放端を有するオープンスタブ配線と、を備え、

前記オープンスタブ配線は、前記開放端で反射した反射波が、前記第1分岐配線に直接伝搬する直接波に対して所定の伝搬遅延時間、遅れて前記第1分岐点に到達する配線長に設定されていることを特徴とするプリント配線板。 - 前記オープンスタブ配線は、5[mm]以上かつ30[mm]以下の配線長に設定されていることを特徴とする請求項9に記載のプリント配線板。

- 請求項1乃至8のいずれか1項に記載のプリント回路板を備えた電子機器。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013025454A JP6091239B2 (ja) | 2013-02-13 | 2013-02-13 | プリント回路板、プリント配線板および電子機器 |

| US14/174,787 US9456489B2 (en) | 2013-02-13 | 2014-02-06 | Printed circuit board and printed wiring board |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013025454A JP6091239B2 (ja) | 2013-02-13 | 2013-02-13 | プリント回路板、プリント配線板および電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014155155A JP2014155155A (ja) | 2014-08-25 |

| JP2014155155A5 JP2014155155A5 (ja) | 2016-03-31 |

| JP6091239B2 true JP6091239B2 (ja) | 2017-03-08 |

Family

ID=51297290

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013025454A Active JP6091239B2 (ja) | 2013-02-13 | 2013-02-13 | プリント回路板、プリント配線板および電子機器 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9456489B2 (ja) |

| JP (1) | JP6091239B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101190443B1 (ko) * | 2004-02-04 | 2012-10-11 | 소니 주식회사 | 고체 촬상 장치 |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6176917B2 (ja) | 2012-11-20 | 2017-08-09 | キヤノン株式会社 | プリント配線板、プリント回路板及び電子機器 |

| JP5925352B2 (ja) * | 2014-04-14 | 2016-05-25 | キヤノン株式会社 | プリント回路板及びプリント配線板 |

| JP2016005155A (ja) * | 2014-06-18 | 2016-01-12 | キヤノン株式会社 | プリント回路板及びプリント配線板 |

| KR102246342B1 (ko) * | 2014-06-26 | 2021-05-03 | 삼성전자주식회사 | 멀티 스택 칩 패키지를 갖는 데이터 저장 장치 및 그것의 동작 방법 |

| KR102542979B1 (ko) * | 2016-07-18 | 2023-06-13 | 삼성전자주식회사 | 데이터 저장 장치 및 이의 동작 방법 |

| US10477686B2 (en) | 2017-07-26 | 2019-11-12 | Canon Kabushiki Kaisha | Printed circuit board |

Family Cites Families (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5394121A (en) * | 1993-10-15 | 1995-02-28 | International Business Machines Corporation | Wiring topology for transfer of electrical signals |

| JP2944403B2 (ja) * | 1993-12-24 | 1999-09-06 | 日本電気株式会社 | 半導体装置 |

| JP2882266B2 (ja) * | 1993-12-28 | 1999-04-12 | 株式会社日立製作所 | 信号伝送装置及び回路ブロック |

| JPH07321828A (ja) * | 1994-05-20 | 1995-12-08 | Fujitsu Ltd | 電子装置 |

| DE4445846A1 (de) * | 1994-12-22 | 1996-06-27 | Sel Alcatel Ag | Verfahren und Schaltungsanordnung für den Abschluß einer zu einer integrierten CMOS-Schaltung führenden Leitung |

| JP4108817B2 (ja) * | 1998-03-20 | 2008-06-25 | 富士通株式会社 | マイクロ波・ミリ波回路装置とその製造方法 |

| JP3647307B2 (ja) * | 1999-04-19 | 2005-05-11 | キヤノン株式会社 | プリント配線基板および電子機器 |

| JP3820843B2 (ja) * | 1999-05-12 | 2006-09-13 | 株式会社日立製作所 | 方向性結合式メモリモジュール |

| JP3880286B2 (ja) * | 1999-05-12 | 2007-02-14 | エルピーダメモリ株式会社 | 方向性結合式メモリシステム |

| JP4002378B2 (ja) * | 1999-12-27 | 2007-10-31 | エルピーダメモリ株式会社 | 電子回路 |

| US6715014B1 (en) * | 2000-05-25 | 2004-03-30 | Hewlett-Packard Development Company, L.P. | Module array |

| US6976114B1 (en) * | 2001-01-25 | 2005-12-13 | Rambus Inc. | Method and apparatus for simultaneous bidirectional signaling in a bus topology |

| US6675272B2 (en) * | 2001-04-24 | 2004-01-06 | Rambus Inc. | Method and apparatus for coordinating memory operations among diversely-located memory components |

| US6686768B2 (en) * | 2001-07-05 | 2004-02-03 | Alan Elbert Comer | Electrically-programmable interconnect architecture for easily-configurable stacked circuit arrangements |

| JP3808335B2 (ja) * | 2001-07-26 | 2006-08-09 | エルピーダメモリ株式会社 | メモリモジュール |

| KR100471162B1 (ko) * | 2002-02-27 | 2005-03-08 | 삼성전자주식회사 | 고속 메모리 시스템 |

| JP4159415B2 (ja) * | 2002-08-23 | 2008-10-01 | エルピーダメモリ株式会社 | メモリモジュール及びメモリシステム |

| JP4221238B2 (ja) * | 2002-09-26 | 2009-02-12 | エルピーダメモリ株式会社 | メモリモジュール |

| JP3742051B2 (ja) * | 2002-10-31 | 2006-02-01 | エルピーダメモリ株式会社 | メモリモジュール、メモリチップ、及びメモリシステム |

| US7245145B2 (en) * | 2003-06-11 | 2007-07-17 | Micron Technology, Inc. | Memory module and method having improved signal routing topology |

| JP4006447B2 (ja) * | 2004-04-16 | 2007-11-14 | キヤノン株式会社 | 半導体装置およびプリント回路板 |

| US7224595B2 (en) * | 2004-07-30 | 2007-05-29 | International Business Machines Corporation | 276-Pin buffered memory module with enhanced fault tolerance |

| US7187249B2 (en) * | 2004-09-24 | 2007-03-06 | Avago Technologies Wireless Ip (Singapore) Pte. Ltd. | Interconnecting a port of a microwave circuit package and a microwave component mounted in the microwave circuit package |

| JP4633455B2 (ja) * | 2004-12-24 | 2011-02-16 | 富士通セミコンダクター株式会社 | 半導体装置 |

| JP4585340B2 (ja) * | 2005-03-16 | 2010-11-24 | 株式会社東芝 | 集積回路搭載基板のバス構造とその定在波抑圧方法 |

| KR100689967B1 (ko) * | 2006-02-03 | 2007-03-08 | 삼성전자주식회사 | 개선된 멀티 모듈 메모리 버스 구조를 가진 메모리 시스템 |

| US20070189049A1 (en) * | 2006-02-16 | 2007-08-16 | Srdjan Djordjevic | Semiconductor memory module |

| US7389381B1 (en) * | 2006-04-05 | 2008-06-17 | Co Ramon S | Branching memory-bus module with multiple downlink ports to standard fully-buffered memory modules |

| JP5196868B2 (ja) | 2006-06-16 | 2013-05-15 | キヤノン株式会社 | プリント回路板 |

| JP4999922B2 (ja) * | 2007-03-30 | 2012-08-15 | 三菱電機株式会社 | 半導体チップおよび高周波回路 |

| US8384423B2 (en) * | 2007-07-19 | 2013-02-26 | Rambus Inc. | Reference voltage and impedance calibration in a multi-mode interface |

| JP5696301B2 (ja) * | 2007-09-28 | 2015-04-08 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | アドレス線配線構造及びこれを有するプリント配線基板 |

| JP5040587B2 (ja) * | 2007-10-25 | 2012-10-03 | ソニー株式会社 | 高周波回路装置 |

| JP2009232076A (ja) * | 2008-03-21 | 2009-10-08 | Mitsubishi Electric Corp | 高周波電力増幅器 |

| JP2009296306A (ja) * | 2008-06-05 | 2009-12-17 | Toshiba Corp | 配線基板 |

| JP5463286B2 (ja) * | 2008-06-30 | 2014-04-09 | 富士通株式会社 | 波形整形回路および光スイッチ装置 |

| KR101526318B1 (ko) * | 2009-01-09 | 2015-06-05 | 삼성전자주식회사 | 메인 보드 상에 스터브 저항이 형성된 메모리 보드를 포함하는 메모리 시스템 |

| JP5539403B2 (ja) * | 2009-02-12 | 2014-07-02 | コンバーサント・インテレクチュアル・プロパティ・マネジメント・インコーポレイテッド | オンダイ終端のための終端回路 |

| JP2010282510A (ja) * | 2009-06-05 | 2010-12-16 | Elpida Memory Inc | メモリモジュール |

| US8681546B2 (en) * | 2011-02-22 | 2014-03-25 | Apple Inc. | Variable impedance control for memory devices |

| JP2012203807A (ja) * | 2011-03-28 | 2012-10-22 | Elpida Memory Inc | メモリモジュール |

| JP2013114416A (ja) * | 2011-11-28 | 2013-06-10 | Elpida Memory Inc | メモリモジュール |

| US9082464B2 (en) * | 2012-02-14 | 2015-07-14 | Samsung Electronics Co., Ltd. | Memory module for high-speed operations |

-

2013

- 2013-02-13 JP JP2013025454A patent/JP6091239B2/ja active Active

-

2014

- 2014-02-06 US US14/174,787 patent/US9456489B2/en active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101190443B1 (ko) * | 2004-02-04 | 2012-10-11 | 소니 주식회사 | 고체 촬상 장치 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20140226278A1 (en) | 2014-08-14 |

| JP2014155155A (ja) | 2014-08-25 |

| US9456489B2 (en) | 2016-09-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6091239B2 (ja) | プリント回路板、プリント配線板および電子機器 | |

| US5945886A (en) | High-speed bus structure for printed circuit boards | |

| US6614664B2 (en) | Memory module having series-connected printed circuit boards | |

| JP6176917B2 (ja) | プリント配線板、プリント回路板及び電子機器 | |

| US8526267B2 (en) | Electronic device | |

| US9313890B2 (en) | Attenuation reduction structure for high frequency signal contact pads of circuit board | |

| US20140078702A1 (en) | Multilayer printed circuit board | |

| US8036011B2 (en) | Memory module for improving signal integrity and computer system having the same | |

| KR100913711B1 (ko) | 인쇄 회로 보드 | |

| JPH11204726A (ja) | 集積回路装置モジュール | |

| JP2016005155A (ja) | プリント回路板及びプリント配線板 | |

| CN110875288A (zh) | 半导体器件封装 | |

| US10271420B2 (en) | Electronic apparatus | |

| JP5925352B2 (ja) | プリント回路板及びプリント配線板 | |

| US20080301352A1 (en) | Bus architecture | |

| KR102078065B1 (ko) | 메모리 모듈 전기 커플링에서 전자 대역 갭(ebg) 구조들을 제공하는 회로들 및 방법들 | |

| US8988160B2 (en) | Data transmission system and semiconductor circuit | |

| JP2008078314A (ja) | 高速信号回路装置 | |

| JP6385074B2 (ja) | プリント回路板及び電子機器 | |

| CN220305760U (zh) | 集成板卡、量子测控系统及量子计算机 | |

| JP2014160296A (ja) | プリント回路板 | |

| JP2023017299A (ja) | プリント配線板及び情報処理装置 | |

| JPH08330523A (ja) | 配線配置方法 | |

| TW201635281A (zh) | 抑制雙倍數據率同步動態隨機存取記憶體訊號之電磁輻射干擾的電路結構 | |

| JP2006222364A (ja) | ボールグリッドアレイパッケージ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160208 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161209 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170207 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6091239 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |