JP4755831B2 - 低誘電率および超低誘電率のSiCOH誘電体膜ならびにその形成方法 - Google Patents

低誘電率および超低誘電率のSiCOH誘電体膜ならびにその形成方法 Download PDFInfo

- Publication number

- JP4755831B2 JP4755831B2 JP2005007763A JP2005007763A JP4755831B2 JP 4755831 B2 JP4755831 B2 JP 4755831B2 JP 2005007763 A JP2005007763 A JP 2005007763A JP 2005007763 A JP2005007763 A JP 2005007763A JP 4755831 B2 JP4755831 B2 JP 4755831B2

- Authority

- JP

- Japan

- Prior art keywords

- dielectric

- dielectric material

- sicoh

- precursor

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title description 38

- 239000003989 dielectric material Substances 0.000 claims description 103

- 239000002243 precursor Substances 0.000 claims description 46

- 239000000463 material Substances 0.000 claims description 42

- 239000000758 substrate Substances 0.000 claims description 34

- 229910018557 Si O Inorganic materials 0.000 claims description 32

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Inorganic materials [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 claims description 32

- 229910052710 silicon Inorganic materials 0.000 claims description 29

- 239000004215 Carbon black (E152) Substances 0.000 claims description 24

- 229930195733 hydrocarbon Natural products 0.000 claims description 24

- 150000002430 hydrocarbons Chemical class 0.000 claims description 23

- 229910052760 oxygen Inorganic materials 0.000 claims description 23

- 229910052799 carbon Inorganic materials 0.000 claims description 22

- 229910052739 hydrogen Inorganic materials 0.000 claims description 22

- 238000012545 processing Methods 0.000 claims description 21

- 238000000151 deposition Methods 0.000 claims description 19

- 239000007789 gas Substances 0.000 claims description 19

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 claims description 19

- 230000008021 deposition Effects 0.000 claims description 15

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 claims description 14

- -1 acyclic silanes Chemical class 0.000 claims description 13

- 238000005033 Fourier transform infrared spectroscopy Methods 0.000 claims description 12

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical group C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 claims description 11

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 11

- JJQZDUKDJDQPMQ-UHFFFAOYSA-N dimethoxy(dimethyl)silane Chemical compound CO[Si](C)(C)OC JJQZDUKDJDQPMQ-UHFFFAOYSA-N 0.000 claims description 10

- 238000010894 electron beam technology Methods 0.000 claims description 10

- 239000000126 substance Substances 0.000 claims description 8

- 238000000862 absorption spectrum Methods 0.000 claims description 7

- 239000000203 mixture Substances 0.000 claims description 7

- 230000005855 radiation Effects 0.000 claims description 7

- 125000004122 cyclic group Chemical group 0.000 claims description 5

- DGXPASZXUJQWLQ-UHFFFAOYSA-N diethyl(methoxy)silane Chemical compound CC[SiH](CC)OC DGXPASZXUJQWLQ-UHFFFAOYSA-N 0.000 claims description 5

- 239000011148 porous material Substances 0.000 claims description 5

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 4

- 239000001301 oxygen Substances 0.000 claims description 4

- UIUXUFNYAYAMOE-UHFFFAOYSA-N methylsilane Chemical compound [SiH3]C UIUXUFNYAYAMOE-UHFFFAOYSA-N 0.000 claims description 3

- 239000007800 oxidant agent Substances 0.000 claims description 3

- 239000000376 reactant Substances 0.000 claims description 3

- GJEZBVHHZQAEDB-UHFFFAOYSA-N 6-oxabicyclo[3.1.0]hexane Chemical compound C1CCC2OC21 GJEZBVHHZQAEDB-UHFFFAOYSA-N 0.000 claims description 2

- 125000000484 butyl group Chemical group [H]C([*])([H])C([H])([H])C([H])([H])C([H])([H])[H] 0.000 claims description 2

- QUZPNFFHZPRKJD-UHFFFAOYSA-N germane Chemical group [GeH4] QUZPNFFHZPRKJD-UHFFFAOYSA-N 0.000 claims description 2

- 229910052986 germanium hydride Inorganic materials 0.000 claims description 2

- 125000001449 isopropyl group Chemical group [H]C([H])([H])C([H])(*)C([H])([H])[H] 0.000 claims description 2

- 125000001183 hydrocarbyl group Chemical group 0.000 claims 2

- 229910052756 noble gas Inorganic materials 0.000 claims 2

- 230000001590 oxidative effect Effects 0.000 claims 1

- 239000010410 layer Substances 0.000 description 182

- 239000011810 insulating material Substances 0.000 description 67

- 239000004020 conductor Substances 0.000 description 41

- 230000035882 stress Effects 0.000 description 36

- 230000008569 process Effects 0.000 description 28

- 238000005498 polishing Methods 0.000 description 24

- 238000001020 plasma etching Methods 0.000 description 20

- 238000002835 absorbance Methods 0.000 description 17

- 229910052751 metal Inorganic materials 0.000 description 17

- 239000002184 metal Substances 0.000 description 17

- 239000011229 interlayer Substances 0.000 description 16

- 238000009792 diffusion process Methods 0.000 description 14

- 230000004888 barrier function Effects 0.000 description 13

- 239000012071 phase Substances 0.000 description 13

- 229910052581 Si3N4 Inorganic materials 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 10

- 238000004519 manufacturing process Methods 0.000 description 10

- 239000004065 semiconductor Substances 0.000 description 10

- 239000010703 silicon Substances 0.000 description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 10

- 229910052814 silicon oxide Inorganic materials 0.000 description 9

- 238000001157 Fourier transform infrared spectrum Methods 0.000 description 8

- 229910010271 silicon carbide Inorganic materials 0.000 description 8

- 238000000137 annealing Methods 0.000 description 7

- NBBQQQJUOYRZCA-UHFFFAOYSA-N diethoxymethylsilane Chemical compound CCOC([SiH3])OCC NBBQQQJUOYRZCA-UHFFFAOYSA-N 0.000 description 7

- 229910052786 argon Inorganic materials 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 238000010438 heat treatment Methods 0.000 description 6

- 229910052734 helium Inorganic materials 0.000 description 6

- 239000012705 liquid precursor Substances 0.000 description 6

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 6

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 5

- 239000007788 liquid Substances 0.000 description 5

- 239000007769 metal material Substances 0.000 description 5

- 239000011261 inert gas Substances 0.000 description 4

- 230000010354 integration Effects 0.000 description 4

- 238000009832 plasma treatment Methods 0.000 description 4

- 239000003870 refractory metal Substances 0.000 description 4

- 230000003595 spectral effect Effects 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 125000004429 atom Chemical group 0.000 description 3

- 125000004432 carbon atom Chemical group C* 0.000 description 3

- 230000015556 catabolic process Effects 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 238000006731 degradation reaction Methods 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 229910052735 hafnium Inorganic materials 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 230000002209 hydrophobic effect Effects 0.000 description 3

- 238000010348 incorporation Methods 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 125000004430 oxygen atom Chemical group O* 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 229910052726 zirconium Inorganic materials 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- YZCKVEUIGOORGS-UHFFFAOYSA-N Hydrogen atom Chemical compound [H] YZCKVEUIGOORGS-UHFFFAOYSA-N 0.000 description 2

- 229910018540 Si C Inorganic materials 0.000 description 2

- 238000005336 cracking Methods 0.000 description 2

- LPIQUOYDBNQMRZ-UHFFFAOYSA-N cyclopentene Chemical compound C1CC=CC1 LPIQUOYDBNQMRZ-UHFFFAOYSA-N 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000002920 hazardous waste Substances 0.000 description 2

- 125000005842 heteroatom Chemical group 0.000 description 2

- 150000004678 hydrides Chemical class 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 238000002844 melting Methods 0.000 description 2

- 230000008018 melting Effects 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 229910052755 nonmetal Inorganic materials 0.000 description 2

- 238000004806 packaging method and process Methods 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 2

- 239000004810 polytetrafluoroethylene Substances 0.000 description 2

- 239000003361 porogen Substances 0.000 description 2

- 230000002285 radioactive effect Effects 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- HMDDXIMCDZRSNE-UHFFFAOYSA-N [C].[Si] Chemical compound [C].[Si] HMDDXIMCDZRSNE-UHFFFAOYSA-N 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 150000004759 cyclic silanes Chemical class 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 239000000539 dimer Substances 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 238000010336 energy treatment Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- 230000004907 flux Effects 0.000 description 1

- 239000012634 fragment Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 229920000592 inorganic polymer Polymers 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 125000004433 nitrogen atom Chemical group N* 0.000 description 1

- 229920000620 organic polymer Polymers 0.000 description 1

- RGSFGYAAUTVSQA-UHFFFAOYSA-N pentamethylene Natural products C1CCCC1 RGSFGYAAUTVSQA-UHFFFAOYSA-N 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005240 physical vapour deposition Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 238000000992 sputter etching Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- 239000013638 trimer Substances 0.000 description 1

- PQDJYEQOELDLCP-UHFFFAOYSA-N trimethylsilane Chemical compound C[SiH](C)C PQDJYEQOELDLCP-UHFFFAOYSA-N 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02126—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/30—Deposition of compounds, mixtures or solid solutions, e.g. borides, carbides, nitrides

- C23C16/40—Oxides

- C23C16/401—Oxides containing silicon

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/56—After-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H01L21/02208—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si

- H01L21/02214—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound comprising silicon and oxygen

- H01L21/02216—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound comprising silicon and oxygen the compound being a molecule comprising at least one silicon-oxygen bond and the compound having hydrogen or an organic group attached to the silicon or oxygen, e.g. a siloxane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02299—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment

- H01L21/02304—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment formation of intermediate layers, e.g. buffer layers, layers to improve adhesion, lattice match or diffusion barriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

- H01L21/02337—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to a gas or vapour

- H01L21/0234—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to a gas or vapour treatment by exposure to a plasma

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

- H01L21/02345—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to radiation, e.g. visible light

- H01L21/02348—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to radiation, e.g. visible light treatment by exposure to UV light

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

- H01L21/02345—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to radiation, e.g. visible light

- H01L21/02351—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to radiation, e.g. visible light treatment by exposure to corpuscular radiation, e.g. exposure to electrons, alpha-particles, protons or ions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

- H01L21/02362—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment formation of intermediate layers, e.g. capping layers or diffusion barriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/316—Inorganic layers composed of oxides or glassy oxides or oxide based glass

- H01L21/31604—Deposition from a gas or vapour

- H01L21/31633—Deposition of carbon doped silicon oxide, e.g. SiOC

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

- H01L23/53295—Stacked insulating layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02203—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being porous

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H01L21/02208—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si

- H01L21/02211—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound being a silane, e.g. disilane, methylsilane or chlorosilane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Mechanical Engineering (AREA)

- Organic Chemistry (AREA)

- Metallurgy (AREA)

- Materials Engineering (AREA)

- General Chemical & Material Sciences (AREA)

- Plasma & Fusion (AREA)

- Inorganic Chemistry (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Formation Of Insulating Films (AREA)

- Organic Insulating Materials (AREA)

Description

好ましい1つのプロセス実施形態では、PECVDツールの中の300℃〜425℃、好ましくは350℃に加熱されたウェハ・チャック上に300mm基板を配置する。本発明では任意のPECVD付着反応装置を使用することができる。次いで、気体および液体前駆物質の流量を安定させて圧力が6トルに達するようにする。ただし1〜10トルの圧力を使用することができる。

k=2.5〜2.6の本発明のSiCOH材料を製造するためには、小さな変更を加えた第1の実施例と同様のプロセスを使用する。具体的には、圧力を6トルよりも高くし、SiCOH OMCTS前駆物質の流量を約1500〜3000mg/分まで下げ、シャワーヘッドのRF電力をわずかに低くする(10〜20%減)。ウェハ・チャックのRF電力を20〜50%引き下げることが重要である。

好ましい1つのプロセス実施形態では、PECVDツールの中の100℃〜400℃、好ましくは200℃〜350℃に加熱されたウェハ・チャック上に300mm基板を配置する。一般に、アプライド・マテリアルズ(Applied Materials)社製のプロデューサ(Producer)(R)、ノーベラス・システムズ(NovellusSystems)社製のベクタ(Vector)(R)などのツールを使用するが、本発明では任意のPECVD付着反応装置を使用することができる。

k=2.2〜2.5の本発明のSiCOH材料を製造するためには、小さな変更を加えた第3の実施例と同様のプロセスを使用する。具体的には、第1のSiCOH前駆物質に対する第2の炭化水素前駆物質の比をより小さくする。

k=2.0〜2.1の本発明のSiCOH材料を製造するためには、第3の実施例と同様のプロセスを使用する。k<2.1である材料の多孔率は30%超であり、より高いポロゲン/SiCOH比を使用する。

32 シリコン基板

34 第1の絶縁材料層

36 第1の金属領域

38 第1のSiCOH誘電膜層

40 第1の導体層

44 第2のSiCOH誘電膜層

50 第2の導体層

60 電子デバイス

62 誘電体キャップ層

70 電子デバイス

72 誘電体キャップ層(研磨ストップ層)

74 誘電体キャップ層(研磨ストップ層)

80 電子デバイス

82 誘電体材料層

84 層間絶縁膜層

86 層内誘電体層

92 ビア

94 相互接続

96 拡散バリア層

Claims (15)

- Si、C、O、H元素を含む、誘電率2.8以下、引張応力45MPa未満、弾性率2から15GPa、硬さ0.2から2GPa、凝集強度1.7から4.5J/m2、水中亀裂発達速度が1.1から2.8ミクロンの膜厚に対して1×10−10m/秒以下の誘電体材料であって、前記誘電体材料は、

(1)PECVDツール内のウェハー・チャックを100℃乃至425℃に加熱し、

(2)前記ウェハ・チャック上に基板を配置し、

(3)希ガスとSiCOH前駆物質の混合体の圧力を0.1乃至10トルに維持し、前記前駆物質は、テトラメチルシクロテトラシロキサン(TMCTS)またはオクタメ チルシクロテトラシロキサン(OMCTS)、ジエトキシメチルシラン(DEMS)、ジメチルジメトキシシラン(DMDMOS)、ジエチルメトキシシラン (DEDMOS)、ならびに関連環状および非環状シラン、シロキサンのいずれか1つを含み、

(4)前記前駆物質の流量を50乃至3500mg/分に維持し、

(5)前記PECVDツールのガス導入プレートに、周波数0.26、0.35、0.45若しくは13.6MHz、電力200乃至450Wの高周波エネルギを印加して誘電体材料を前記基板に付着させ、

(6)前記誘電体付着後の処理として、熱エネルギー及び化学作用、電子ビーム、マイクロ波またはプラズマ・エネルギー源の少なくとも1つの第2のエネルギ源からの放射を印加し、形成された、前記誘電体材料。 - 共有結合3次元ネットワーク構造を有する、請求項1に記載の誘電体材料。

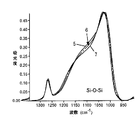

- 前記共有結合3次元ネットワーク構造がさらに、付着後の処理を用いて、ネットワークSi−O強度に対するケージSi−O強度の比が低下するFTIR吸光度スペクトルを生み出すSi−O結合を含む、請求項2に記載の誘電体材料。

- 水との接触角が70°超である、請求項1に記載の誘電体材料。

- ナノメートル・サイズの多数の細孔をさらに含む、請求項1に記載の誘電体材料。

- 少なくとも、Si、C、O、H元素を含む、誘電率2.8以下、引張応力45MPa未満、弾性率2から15GPa、硬さ0.2から2GPa、凝集強度1.7から4.5J/m2、水中亀裂発達速度が1.1から2.8ミクロンの膜厚に対して1×10−10m/秒以下の誘電体材料と、配線領域とを含む電子デバイス構造であって、前記誘電体材料は、

(1)PECVDツール内のウェハー・チャックを100℃乃至425℃に加熱し、

(2)前記ウェハ・チャック上に基板を配置し、

(3)希ガスとSiCOH前駆物質の混合体の圧力を0.1乃至10トルに維持し、前記前駆物質は、テトラメチルシクロテトラシロキサン(TMCTS)またはオクタメ チルシクロテトラシロキサン(OMCTS)、ジエトキシメチルシラン(DEMS)、ジメチルジメトキシシラン(DMDMOS)、ジエチルメトキシシラン (DEDMOS)、ならびに関連環状および非環状シラン、シロキサンのいずれか1つを含み、

(4)前記前駆物質の流量を50乃至3500mg/分に維持し、

(5)前記PECVDツールのガス導入プレートに、周波数0.26、0.35、0.45若しくは13.6MHz、電力200乃至450Wの高周波エネルギを印加して誘電体材料を前記基板に付着させ、

(6)前記誘電体付着後の処理として、熱エネルギー及び化学作用、電子ビーム、マイクロ波またはプラズマ・エネルギー源の少なくとも1つの第2のエネルギ源からの放射を印加し、形成された、前記電子デバイス構造。 - 前記誘電体材料が共有結合3次元ネットワーク構造を有する、請求項6に記載の電子デバイス構造。

- 前記共有結合3次元ネットワーク構造がさらに、付着後の処理を用いて、ネットワークSi−O強度に対するケージSi−O強度の比が低下するFTIR吸光度スペクトルを生み出すSi−O結合を含む、請求項7に記載の電子デバイス構造。

- 前記誘電体材料の水との接触角が70°超である、請求項6に記載の電子デバイス構造。

- 前記誘電体材料がさらに、ナノメートル・サイズの多数の細孔を含む、請求項6に記載の電子デバイス構造。

- 第2の前駆物質をさらに含み、前記第2の前駆物質が、環構造を有する分子と、炭化水素環に結合した枝分れ第三級ブチル基またはイソプロピル基を含む分子とからなるグループから選択された炭化水素分子を含む、請求項1に記載の誘電体材料。

- 前記第2の前駆物質が酸素を含む炭化水素分子である、請求項11に記載の誘電体材料。

- 前記第2の前駆物質が酸化シクロペンタン酸化物である、請求項11に記載の誘電体材料。

- 第3の前駆物質をさらに含み、前記第3の前駆物質がゲルマニウム水素化物またはGe源を含む他の反応物である、請求項11に記載の誘電体材料。

- 前記反応装置に酸化剤を供給するステップをさらに含む、請求項11に記載の誘電体材料。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/758,724 US7030468B2 (en) | 2004-01-16 | 2004-01-16 | Low k and ultra low k SiCOH dielectric films and methods to form the same |

| US10/758724 | 2004-01-16 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008224431A Division JP4833268B2 (ja) | 2004-01-16 | 2008-09-02 | 低誘電率および超低誘電率のSiCOH誘電体膜の形成方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005203794A JP2005203794A (ja) | 2005-07-28 |

| JP4755831B2 true JP4755831B2 (ja) | 2011-08-24 |

Family

ID=34749564

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005007763A Expired - Fee Related JP4755831B2 (ja) | 2004-01-16 | 2005-01-14 | 低誘電率および超低誘電率のSiCOH誘電体膜ならびにその形成方法 |

| JP2008224431A Expired - Fee Related JP4833268B2 (ja) | 2004-01-16 | 2008-09-02 | 低誘電率および超低誘電率のSiCOH誘電体膜の形成方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008224431A Expired - Fee Related JP4833268B2 (ja) | 2004-01-16 | 2008-09-02 | 低誘電率および超低誘電率のSiCOH誘電体膜の形成方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US7030468B2 (ja) |

| JP (2) | JP4755831B2 (ja) |

| CN (1) | CN100378990C (ja) |

| TW (1) | TWI324381B (ja) |

Families Citing this family (164)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6734533B2 (en) * | 2002-05-30 | 2004-05-11 | Intel Corporation | Electron-beam treated CDO films |

| JP4338495B2 (ja) * | 2002-10-30 | 2009-10-07 | 富士通マイクロエレクトロニクス株式会社 | シリコンオキシカーバイド、半導体装置、および半導体装置の製造方法 |

| US7485570B2 (en) | 2002-10-30 | 2009-02-03 | Fujitsu Limited | Silicon oxycarbide, growth method of silicon oxycarbide layer, semiconductor device and manufacture method for semiconductor device |

| US7288292B2 (en) * | 2003-03-18 | 2007-10-30 | International Business Machines Corporation | Ultra low k (ULK) SiCOH film and method |

| US7208389B1 (en) | 2003-03-31 | 2007-04-24 | Novellus Systems, Inc. | Method of porogen removal from porous low-k films using UV radiation |

| US20050260420A1 (en) * | 2003-04-01 | 2005-11-24 | Collins Martha J | Low dielectric materials and methods for making same |

| US7081673B2 (en) * | 2003-04-17 | 2006-07-25 | International Business Machines Corporation | Multilayered cap barrier in microelectronic interconnect structures |

| JP4295730B2 (ja) * | 2003-04-28 | 2009-07-15 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US20040253378A1 (en) * | 2003-06-12 | 2004-12-16 | Applied Materials, Inc. | Stress reduction of SIOC low k film by addition of alkylenes to OMCTS based processes |

| US20050037153A1 (en) * | 2003-08-14 | 2005-02-17 | Applied Materials, Inc. | Stress reduction of sioc low k films |

| US7341761B1 (en) | 2004-03-11 | 2008-03-11 | Novellus Systems, Inc. | Methods for producing low-k CDO films |

| US7781351B1 (en) * | 2004-04-07 | 2010-08-24 | Novellus Systems, Inc. | Methods for producing low-k carbon doped oxide films with low residual stress |

| US7253125B1 (en) | 2004-04-16 | 2007-08-07 | Novellus Systems, Inc. | Method to improve mechanical strength of low-k dielectric film using modulated UV exposure |

| JP4470627B2 (ja) * | 2004-07-15 | 2010-06-02 | 日本電気株式会社 | 光学基板、発光素子および表示装置 |

| US7223670B2 (en) * | 2004-08-20 | 2007-05-29 | International Business Machines Corporation | DUV laser annealing and stabilization of SiCOH films |

| US7491658B2 (en) * | 2004-10-13 | 2009-02-17 | International Business Machines Corporation | Ultra low k plasma enhanced chemical vapor deposition processes using a single bifunctional precursor containing both a SiCOH matrix functionality and organic porogen functionality |

| US20060081965A1 (en) * | 2004-10-15 | 2006-04-20 | Ju-Ai Ruan | Plasma treatment of an etch stop layer |

| US9659769B1 (en) | 2004-10-22 | 2017-05-23 | Novellus Systems, Inc. | Tensile dielectric films using UV curing |

| US7790633B1 (en) | 2004-10-26 | 2010-09-07 | Novellus Systems, Inc. | Sequential deposition/anneal film densification method |

| US7695765B1 (en) | 2004-11-12 | 2010-04-13 | Novellus Systems, Inc. | Methods for producing low-stress carbon-doped oxide films with improved integration properties |

| US7357977B2 (en) * | 2005-01-13 | 2008-04-15 | International Business Machines Corporation | Ultralow dielectric constant layer with controlled biaxial stress |

| US7892648B2 (en) * | 2005-01-21 | 2011-02-22 | International Business Machines Corporation | SiCOH dielectric material with improved toughness and improved Si-C bonding |

| US20060166491A1 (en) * | 2005-01-21 | 2006-07-27 | Kensaku Ida | Dual damascene interconnection having low k layer and cap layer formed in a common PECVD process |

| US7166531B1 (en) | 2005-01-31 | 2007-01-23 | Novellus Systems, Inc. | VLSI fabrication processes for introducing pores into dielectric materials |

| US7510982B1 (en) | 2005-01-31 | 2009-03-31 | Novellus Systems, Inc. | Creation of porosity in low-k films by photo-disassociation of imbedded nanoparticles |

| US7202564B2 (en) * | 2005-02-16 | 2007-04-10 | International Business Machines Corporation | Advanced low dielectric constant organosilicon plasma chemical vapor deposition films |

| US7253105B2 (en) * | 2005-02-22 | 2007-08-07 | International Business Machines Corporation | Reliable BEOL integration process with direct CMP of porous SiCOH dielectric |

| US8980769B1 (en) | 2005-04-26 | 2015-03-17 | Novellus Systems, Inc. | Multi-station sequential curing of dielectric films |

| US8282768B1 (en) | 2005-04-26 | 2012-10-09 | Novellus Systems, Inc. | Purging of porogen from UV cure chamber |

| US8889233B1 (en) | 2005-04-26 | 2014-11-18 | Novellus Systems, Inc. | Method for reducing stress in porous dielectric films |

| US8454750B1 (en) | 2005-04-26 | 2013-06-04 | Novellus Systems, Inc. | Multi-station sequential curing of dielectric films |

| US8137465B1 (en) | 2005-04-26 | 2012-03-20 | Novellus Systems, Inc. | Single-chamber sequential curing of semiconductor wafers |

| US7314828B2 (en) * | 2005-07-19 | 2008-01-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Repairing method for low-k dielectric materials |

| US7323410B2 (en) * | 2005-08-08 | 2008-01-29 | International Business Machines Corporation | Dry etchback of interconnect contacts |

| JP5355892B2 (ja) * | 2005-09-16 | 2013-11-27 | ルネサスエレクトロニクス株式会社 | 配線構造並びに半導体装置及びその製造方法 |

| WO2007043205A1 (ja) * | 2005-10-14 | 2007-04-19 | Yatabe Massao | 照射装置、照射方法及び半導体デバイス |

| US7622378B2 (en) | 2005-11-09 | 2009-11-24 | Tokyo Electron Limited | Multi-step system and method for curing a dielectric film |

| WO2007061134A1 (ja) * | 2005-11-24 | 2007-05-31 | Nec Corporation | 多孔質絶縁膜の形成方法、半導体装置の製造装置、半導体装置の製造方法及び半導体装置 |

| US20070173071A1 (en) * | 2006-01-20 | 2007-07-26 | International Business Machines Corporation | SiCOH dielectric |

| JP4666308B2 (ja) * | 2006-02-24 | 2011-04-06 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| US20070246830A1 (en) * | 2006-04-21 | 2007-10-25 | Toshiba America Electronic Components, Inc. | Long-lifetime interconnect structure and method for making |

| US7825038B2 (en) * | 2006-05-30 | 2010-11-02 | Applied Materials, Inc. | Chemical vapor deposition of high quality flow-like silicon dioxide using a silicon containing precursor and atomic oxygen |

| US20070277734A1 (en) * | 2006-05-30 | 2007-12-06 | Applied Materials, Inc. | Process chamber for dielectric gapfill |

| US7790634B2 (en) * | 2006-05-30 | 2010-09-07 | Applied Materials, Inc | Method for depositing and curing low-k films for gapfill and conformal film applications |

| US7902080B2 (en) * | 2006-05-30 | 2011-03-08 | Applied Materials, Inc. | Deposition-plasma cure cycle process to enhance film quality of silicon dioxide |

| US8232176B2 (en) * | 2006-06-22 | 2012-07-31 | Applied Materials, Inc. | Dielectric deposition and etch back processes for bottom up gapfill |

| JP2008021800A (ja) * | 2006-07-12 | 2008-01-31 | Sanyo Electric Co Ltd | 半導体装置およびその製造方法 |

| US8956457B2 (en) * | 2006-09-08 | 2015-02-17 | Tokyo Electron Limited | Thermal processing system for curing dielectric films |

| JP2008103586A (ja) * | 2006-10-20 | 2008-05-01 | Renesas Technology Corp | 半導体装置の製造方法および半導体装置 |

| US10037905B2 (en) | 2009-11-12 | 2018-07-31 | Novellus Systems, Inc. | UV and reducing treatment for K recovery and surface clean in semiconductor processing |

| US8465991B2 (en) | 2006-10-30 | 2013-06-18 | Novellus Systems, Inc. | Carbon containing low-k dielectric constant recovery using UV treatment |

| US7906174B1 (en) | 2006-12-07 | 2011-03-15 | Novellus Systems, Inc. | PECVD methods for producing ultra low-k dielectric films using UV treatment |

| US20080173985A1 (en) * | 2007-01-24 | 2008-07-24 | International Business Machines Corporation | Dielectric cap having material with optical band gap to substantially block uv radiation during curing treatment, and related methods |

| US20080188074A1 (en) * | 2007-02-06 | 2008-08-07 | I-I Chen | Peeling-free porous capping material |

| US7847402B2 (en) | 2007-02-20 | 2010-12-07 | International Business Machines Corporation | BEOL interconnect structures with improved resistance to stress |

| US8242028B1 (en) * | 2007-04-03 | 2012-08-14 | Novellus Systems, Inc. | UV treatment of etch stop and hard mask films for selectivity and hermeticity enhancement |

| US7622162B1 (en) | 2007-06-07 | 2009-11-24 | Novellus Systems, Inc. | UV treatment of STI films for increasing tensile stress |

| US7851288B2 (en) * | 2007-06-08 | 2010-12-14 | International Business Machines Corporation | Field effect transistor using carbon based stress liner |

| FR2918997B1 (fr) * | 2007-07-20 | 2010-12-03 | Commissariat Energie Atomique | Procede de preparation de couches minces de materiaux dielectriques nanoporeux. |

| US7745352B2 (en) * | 2007-08-27 | 2010-06-29 | Applied Materials, Inc. | Curing methods for silicon dioxide thin films deposited from alkoxysilane precursor with harp II process |

| US20090061237A1 (en) * | 2007-08-28 | 2009-03-05 | International Business Machines Corporation | LOW k POROUS SiCOH DIELECTRIC AND INTEGRATION WITH POST FILM FORMATION TREATMENT |

| US20090061649A1 (en) | 2007-08-28 | 2009-03-05 | International Business Machines Corporation | LOW k POROUS SiCOH DIELECTRIC AND INTEGRATION WITH POST FILM FORMATION TREATMENT |

| US8211510B1 (en) | 2007-08-31 | 2012-07-03 | Novellus Systems, Inc. | Cascaded cure approach to fabricate highly tensile silicon nitride films |

| US20090075491A1 (en) * | 2007-09-13 | 2009-03-19 | Tokyo Electron Limited | Method for curing a dielectric film |

| US20090093135A1 (en) * | 2007-10-04 | 2009-04-09 | Asm Japan K.K. | Semiconductor manufacturing apparatus and method for curing material with uv light |

| US7803722B2 (en) * | 2007-10-22 | 2010-09-28 | Applied Materials, Inc | Methods for forming a dielectric layer within trenches |

| US7943531B2 (en) * | 2007-10-22 | 2011-05-17 | Applied Materials, Inc. | Methods for forming a silicon oxide layer over a substrate |

| US7867923B2 (en) * | 2007-10-22 | 2011-01-11 | Applied Materials, Inc. | High quality silicon oxide films by remote plasma CVD from disilane precursors |

| US7977256B2 (en) | 2008-03-06 | 2011-07-12 | Tokyo Electron Limited | Method for removing a pore-generating material from an uncured low-k dielectric film |

| US7858533B2 (en) * | 2008-03-06 | 2010-12-28 | Tokyo Electron Limited | Method for curing a porous low dielectric constant dielectric film |

| US20090226695A1 (en) * | 2008-03-06 | 2009-09-10 | Tokyo Electron Limited | Method for treating a dielectric film with infrared radiation |

| US20090226694A1 (en) * | 2008-03-06 | 2009-09-10 | Tokyo Electron Limited | POROUS SiCOH-CONTAINING DIELECTRIC FILM AND A METHOD OF PREPARING |

| US8357435B2 (en) * | 2008-05-09 | 2013-01-22 | Applied Materials, Inc. | Flowable dielectric equipment and processes |

| US20100143580A1 (en) * | 2008-05-28 | 2010-06-10 | American Air Liquide, Inc. | Stabilization of Bicycloheptadiene |

| US8298965B2 (en) * | 2008-09-03 | 2012-10-30 | American Air Liquide, Inc. | Volatile precursors for deposition of C-linked SiCOH dielectrics |

| US9050623B1 (en) | 2008-09-12 | 2015-06-09 | Novellus Systems, Inc. | Progressive UV cure |

| US8895942B2 (en) * | 2008-09-16 | 2014-11-25 | Tokyo Electron Limited | Dielectric treatment module using scanning IR radiation source |

| US20100065758A1 (en) * | 2008-09-16 | 2010-03-18 | Tokyo Electron Limited | Dielectric material treatment system and method of operating |

| US20100081293A1 (en) * | 2008-10-01 | 2010-04-01 | Applied Materials, Inc. | Methods for forming silicon nitride based film or silicon carbon based film |

| US20100151206A1 (en) | 2008-12-11 | 2010-06-17 | Air Products And Chemicals, Inc. | Method for Removal of Carbon From An Organosilicate Material |

| JPWO2010082250A1 (ja) * | 2009-01-13 | 2012-06-28 | パナソニック株式会社 | 半導体装置及びその製造方法 |

| JP2010171081A (ja) * | 2009-01-20 | 2010-08-05 | Toshiba Corp | 半導体装置及びその製造方法 |

| SG174296A1 (en) | 2009-03-10 | 2011-10-28 | Air Liquide | Cyclic amino compounds for low-k silylation |

| US20120032323A1 (en) * | 2009-04-30 | 2012-02-09 | Masahiro Matsumoto | Semiconductor device and method of manufacturing the same |

| US20110006406A1 (en) * | 2009-07-08 | 2011-01-13 | Imec | Fabrication of porogen residues free and mechanically robust low-k materials |

| US8974870B2 (en) * | 2009-07-08 | 2015-03-10 | Imec | Fabrication of porogen residues free low-k materials with improved mechanical and chemical resistance |

| US8980382B2 (en) * | 2009-12-02 | 2015-03-17 | Applied Materials, Inc. | Oxygen-doping for non-carbon radical-component CVD films |

| US8741788B2 (en) * | 2009-08-06 | 2014-06-03 | Applied Materials, Inc. | Formation of silicon oxide using non-carbon flowable CVD processes |

| US7935643B2 (en) * | 2009-08-06 | 2011-05-03 | Applied Materials, Inc. | Stress management for tensile films |

| US7989365B2 (en) * | 2009-08-18 | 2011-08-02 | Applied Materials, Inc. | Remote plasma source seasoning |

| US20110136347A1 (en) * | 2009-10-21 | 2011-06-09 | Applied Materials, Inc. | Point-of-use silylamine generation |

| EP2319821A1 (en) | 2009-11-06 | 2011-05-11 | L'Air Liquide Société Anonyme pour l'Etude et l'Exploitation des Procédés Georges Claude | Stabilization of bicycloheptadiene |

| US8528224B2 (en) | 2009-11-12 | 2013-09-10 | Novellus Systems, Inc. | Systems and methods for at least partially converting films to silicon oxide and/or improving film quality using ultraviolet curing in steam and densification of films using UV curing in ammonia |

| US8449942B2 (en) * | 2009-11-12 | 2013-05-28 | Applied Materials, Inc. | Methods of curing non-carbon flowable CVD films |

| KR20120111738A (ko) | 2009-12-30 | 2012-10-10 | 어플라이드 머티어리얼스, 인코포레이티드 | 융통성을 가진 질소/수소 비율을 이용하여 제조된 라디칼에 의한 유전체 필름의 성장 |

| US8329262B2 (en) * | 2010-01-05 | 2012-12-11 | Applied Materials, Inc. | Dielectric film formation using inert gas excitation |

| JP2013517616A (ja) | 2010-01-06 | 2013-05-16 | アプライド マテリアルズ インコーポレイテッド | 酸化物ライナを使用する流動可能な誘電体 |

| CN102714156A (zh) | 2010-01-07 | 2012-10-03 | 应用材料公司 | 自由基成分cvd的原位臭氧固化 |

| US8314005B2 (en) * | 2010-01-27 | 2012-11-20 | International Business Machines Corporation | Homogeneous porous low dielectric constant materials |

| US8492239B2 (en) | 2010-01-27 | 2013-07-23 | International Business Machines Corporation | Homogeneous porous low dielectric constant materials |

| TWI550121B (zh) | 2010-02-17 | 2016-09-21 | 液態空氣喬治斯克勞帝方法研究開發股份有限公司 | SiCOH低K膜之氣相沈積法 |

| US8569183B2 (en) * | 2010-03-01 | 2013-10-29 | Fairchild Semiconductor Corporation | Low temperature dielectric flow using microwaves |

| CN102844848A (zh) * | 2010-03-05 | 2012-12-26 | 应用材料公司 | 通过自由基成分化学气相沉积的共形层 |

| US8236708B2 (en) | 2010-03-09 | 2012-08-07 | Applied Materials, Inc. | Reduced pattern loading using bis(diethylamino)silane (C8H22N2Si) as silicon precursor |

| US20110232677A1 (en) * | 2010-03-29 | 2011-09-29 | Tokyo Electron Limited | Method for cleaning low-k dielectrics |

| US7994019B1 (en) | 2010-04-01 | 2011-08-09 | Applied Materials, Inc. | Silicon-ozone CVD with reduced pattern loading using incubation period deposition |

| US8476142B2 (en) | 2010-04-12 | 2013-07-02 | Applied Materials, Inc. | Preferential dielectric gapfill |

| US20110297088A1 (en) * | 2010-06-04 | 2011-12-08 | Texas Instruments Incorporated | Thin edge carrier ring |

| US8524004B2 (en) | 2010-06-16 | 2013-09-03 | Applied Materials, Inc. | Loadlock batch ozone cure |

| US8318584B2 (en) | 2010-07-30 | 2012-11-27 | Applied Materials, Inc. | Oxide-rich liner layer for flowable CVD gapfill |

| US9285168B2 (en) | 2010-10-05 | 2016-03-15 | Applied Materials, Inc. | Module for ozone cure and post-cure moisture treatment |

| US8664127B2 (en) | 2010-10-15 | 2014-03-04 | Applied Materials, Inc. | Two silicon-containing precursors for gapfill enhancing dielectric liner |

| US10283321B2 (en) | 2011-01-18 | 2019-05-07 | Applied Materials, Inc. | Semiconductor processing system and methods using capacitively coupled plasma |

| US8450191B2 (en) | 2011-01-24 | 2013-05-28 | Applied Materials, Inc. | Polysilicon films by HDP-CVD |

| US8716154B2 (en) | 2011-03-04 | 2014-05-06 | Applied Materials, Inc. | Reduced pattern loading using silicon oxide multi-layers |

| US8445078B2 (en) | 2011-04-20 | 2013-05-21 | Applied Materials, Inc. | Low temperature silicon oxide conversion |

| US8466073B2 (en) | 2011-06-03 | 2013-06-18 | Applied Materials, Inc. | Capping layer for reduced outgassing |

| US8927430B2 (en) | 2011-07-12 | 2015-01-06 | International Business Machines Corporation | Overburden removal for pore fill integration approach |

| US8541301B2 (en) | 2011-07-12 | 2013-09-24 | International Business Machines Corporation | Reduction of pore fill material dewetting |

| US9404178B2 (en) | 2011-07-15 | 2016-08-02 | Applied Materials, Inc. | Surface treatment and deposition for reduced outgassing |

| US8828489B2 (en) | 2011-08-19 | 2014-09-09 | International Business Machines Corporation | Homogeneous modification of porous films |

| US8637412B2 (en) * | 2011-08-19 | 2014-01-28 | International Business Machines Corporation | Process to form an adhesion layer and multiphase ultra-low k dielectric material using PECVD |

| US8617989B2 (en) | 2011-09-26 | 2013-12-31 | Applied Materials, Inc. | Liner property improvement |

| US8551891B2 (en) | 2011-10-04 | 2013-10-08 | Applied Materials, Inc. | Remote plasma burn-in |

| CN103165576B (zh) * | 2011-12-13 | 2015-10-14 | 中芯国际集成电路制造(上海)有限公司 | 半导体器件及其制造方法 |

| US8889566B2 (en) | 2012-09-11 | 2014-11-18 | Applied Materials, Inc. | Low cost flowable dielectric films |

| WO2014049740A1 (ja) * | 2012-09-26 | 2014-04-03 | トヨタ自動車株式会社 | 電気部品 |

| US8987859B2 (en) * | 2012-12-04 | 2015-03-24 | Intel Corporation | Techniques for enhancing dielectric breakdown performance |

| US9018108B2 (en) | 2013-01-25 | 2015-04-28 | Applied Materials, Inc. | Low shrinkage dielectric films |

| US9058983B2 (en) | 2013-06-17 | 2015-06-16 | International Business Machines Corporation | In-situ hardmask generation |

| US9281238B2 (en) * | 2014-07-11 | 2016-03-08 | United Microelectronics Corp. | Method for fabricating interlayer dielectric layer |

| US9412581B2 (en) | 2014-07-16 | 2016-08-09 | Applied Materials, Inc. | Low-K dielectric gapfill by flowable deposition |

| JP2016127080A (ja) * | 2014-12-26 | 2016-07-11 | 株式会社Screenホールディングス | 基板処理装置および基板処理方法 |

| US20160225652A1 (en) | 2015-02-03 | 2016-08-04 | Applied Materials, Inc. | Low temperature chuck for plasma processing systems |

| US10262876B2 (en) | 2015-02-16 | 2019-04-16 | SCREEN Holdings Co., Ltd. | Substrate processing apparatus |

| KR102624608B1 (ko) | 2016-01-19 | 2024-01-16 | 삼성전자주식회사 | 저유전막의 형성 방법 및 이를 이용한 반도체 소자의 제조 방법 |

| US9768061B1 (en) | 2016-05-31 | 2017-09-19 | Taiwan Semiconductor Manufacturing Co., Ltd. | Low-k dielectric interconnect systems |

| TWI590350B (zh) * | 2016-06-30 | 2017-07-01 | 欣興電子股份有限公司 | 線路重分佈結構的製造方法與線路重分佈結構單元 |

| US9847221B1 (en) | 2016-09-29 | 2017-12-19 | Lam Research Corporation | Low temperature formation of high quality silicon oxide films in semiconductor device manufacturing |

| US10224224B2 (en) | 2017-03-10 | 2019-03-05 | Micromaterials, LLC | High pressure wafer processing systems and related methods |

| US10622214B2 (en) | 2017-05-25 | 2020-04-14 | Applied Materials, Inc. | Tungsten defluorination by high pressure treatment |

| JP7190450B2 (ja) | 2017-06-02 | 2022-12-15 | アプライド マテリアルズ インコーポレイテッド | 炭化ホウ素ハードマスクのドライストリッピング |

| US10361137B2 (en) | 2017-07-31 | 2019-07-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device and method |

| CN111095513B (zh) | 2017-08-18 | 2023-10-31 | 应用材料公司 | 高压高温退火腔室 |

| US10276411B2 (en) | 2017-08-18 | 2019-04-30 | Applied Materials, Inc. | High pressure and high temperature anneal chamber |

| CN111095524B (zh) | 2017-09-12 | 2023-10-03 | 应用材料公司 | 用于使用保护阻挡物层制造半导体结构的设备和方法 |

| US10643867B2 (en) | 2017-11-03 | 2020-05-05 | Applied Materials, Inc. | Annealing system and method |

| CN117936417A (zh) | 2017-11-11 | 2024-04-26 | 微材料有限责任公司 | 用于高压处理腔室的气体输送系统 |

| SG11202003438QA (en) | 2017-11-16 | 2020-05-28 | Applied Materials Inc | High pressure steam anneal processing apparatus |

| WO2019099255A2 (en) | 2017-11-17 | 2019-05-23 | Applied Materials, Inc. | Condenser system for high pressure processing system |

| CN111699549A (zh) | 2018-01-24 | 2020-09-22 | 应用材料公司 | 使用高压退火的接缝弥合 |

| WO2019173006A1 (en) | 2018-03-09 | 2019-09-12 | Applied Materials, Inc. | High pressure annealing process for metal containing materials |

| US10714331B2 (en) | 2018-04-04 | 2020-07-14 | Applied Materials, Inc. | Method to fabricate thermally stable low K-FinFET spacer |

| US10950429B2 (en) | 2018-05-08 | 2021-03-16 | Applied Materials, Inc. | Methods of forming amorphous carbon hard mask layers and hard mask layers formed therefrom |

| US10566188B2 (en) | 2018-05-17 | 2020-02-18 | Applied Materials, Inc. | Method to improve film stability |

| US10704141B2 (en) | 2018-06-01 | 2020-07-07 | Applied Materials, Inc. | In-situ CVD and ALD coating of chamber to control metal contamination |

| US10748783B2 (en) | 2018-07-25 | 2020-08-18 | Applied Materials, Inc. | Gas delivery module |

| US10675581B2 (en) | 2018-08-06 | 2020-06-09 | Applied Materials, Inc. | Gas abatement apparatus |

| JP7179172B6 (ja) | 2018-10-30 | 2022-12-16 | アプライド マテリアルズ インコーポレイテッド | 半導体用途の構造体をエッチングするための方法 |

| KR20210077779A (ko) | 2018-11-16 | 2021-06-25 | 어플라이드 머티어리얼스, 인코포레이티드 | 강화된 확산 프로세스를 사용한 막 증착 |

| WO2020117462A1 (en) | 2018-12-07 | 2020-06-11 | Applied Materials, Inc. | Semiconductor processing system |

| CN110158052B (zh) | 2019-05-17 | 2021-05-14 | 江苏菲沃泰纳米科技股份有限公司 | 低介电常数膜及其制备方法 |

| CN110129769B (zh) * | 2019-05-17 | 2021-05-14 | 江苏菲沃泰纳米科技股份有限公司 | 疏水性的低介电常数膜及其制备方法 |

| US11901222B2 (en) | 2020-02-17 | 2024-02-13 | Applied Materials, Inc. | Multi-step process for flowable gap-fill film |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20010006553A (ko) * | 1997-04-17 | 2001-01-26 | 크리스 로저 에이치 | 다중밀도의 미세공극성 유전체 코팅된 기판 및 그 코팅방법 |

| US6284655B1 (en) * | 1998-09-03 | 2001-09-04 | Micron Technology, Inc. | Method for producing low carbon/oxygen conductive layers |

| US6200893B1 (en) * | 1999-03-11 | 2001-03-13 | Genus, Inc | Radical-assisted sequential CVD |

| US6472306B1 (en) * | 2000-09-05 | 2002-10-29 | Industrial Technology Research Institute | Method of forming a dual damascene opening using CVD Low-K material and spin-on-polymer |

| US6768200B2 (en) * | 2000-10-25 | 2004-07-27 | International Business Machines Corporation | Ultralow dielectric constant material as an intralevel or interlevel dielectric in a semiconductor device |

| SG98468A1 (en) * | 2001-01-17 | 2003-09-19 | Air Prod & Chem | Organosilicon precursors for interlayer dielectric films with low dielectric constants |

| US6780499B2 (en) * | 2001-05-03 | 2004-08-24 | International Business Machines Corporation | Ordered two-phase dielectric film, and semiconductor device containing the same |

| US6798043B2 (en) * | 2001-06-28 | 2004-09-28 | Agere Systems, Inc. | Structure and method for isolating porous low-k dielectric films |

| US6890850B2 (en) * | 2001-12-14 | 2005-05-10 | Applied Materials, Inc. | Method of depositing dielectric materials in damascene applications |

| US7307343B2 (en) * | 2002-05-30 | 2007-12-11 | Air Products And Chemicals, Inc. | Low dielectric materials and methods for making same |

| US6764774B2 (en) * | 2002-06-19 | 2004-07-20 | International Business Machines Corporation | Structures with improved adhesion to Si and C containing dielectrics and method for preparing the same |

| US20040089470A1 (en) * | 2002-11-12 | 2004-05-13 | Nec Corporation | Printed circuit board, semiconductor package, base insulating film, and manufacturing method for interconnect substrate |

-

2004

- 2004-01-16 US US10/758,724 patent/US7030468B2/en not_active Expired - Lifetime

-

2005

- 2005-01-10 TW TW094100612A patent/TWI324381B/zh not_active IP Right Cessation

- 2005-01-14 JP JP2005007763A patent/JP4755831B2/ja not_active Expired - Fee Related

- 2005-01-14 CN CNB2005100043046A patent/CN100378990C/zh active Active

- 2005-11-07 US US11/268,106 patent/US7282458B2/en not_active Expired - Lifetime

-

2008

- 2008-09-02 JP JP2008224431A patent/JP4833268B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP4833268B2 (ja) | 2011-12-07 |

| TWI324381B (en) | 2010-05-01 |

| CN100378990C (zh) | 2008-04-02 |

| US20050156285A1 (en) | 2005-07-21 |

| US7030468B2 (en) | 2006-04-18 |

| TW200531248A (en) | 2005-09-16 |

| CN1645608A (zh) | 2005-07-27 |

| US7282458B2 (en) | 2007-10-16 |

| US20060055004A1 (en) | 2006-03-16 |

| JP2009044162A (ja) | 2009-02-26 |

| JP2005203794A (ja) | 2005-07-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4755831B2 (ja) | 低誘電率および超低誘電率のSiCOH誘電体膜ならびにその形成方法 | |

| KR101006329B1 (ko) | 원자외선 레이저 어닐링 및 SiCOH 박막의 안정화 | |

| JP5466365B2 (ja) | 基板上にSiCOH誘電体を形成する方法 | |

| KR100724508B1 (ko) | 초저 K(ULK) SiCOH 막 및 그 형성 방법 | |

| JP5398258B2 (ja) | 誘電体スタック及びそれを備える相互接続構造体 | |

| JP5065054B2 (ja) | 制御された二軸応力を有する超低誘電率膜および該作製方法 | |

| JP4756036B2 (ja) | 超低誘電率膜を製造するための方法、誘電材料、相互接続構造及び配線構造 | |

| KR100702508B1 (ko) | 유전 물질 및 beol 상호 접속 구조체 | |

| JP4410783B2 (ja) | 低誘電率膜を作製する方法 | |

| US7226876B2 (en) | Method of modifying interlayer adhesion | |

| TWI240959B (en) | Mechanical enhancement of dense and porous organosilicate materials by UV exposure | |

| JP2013520841A (ja) | プラズマ化学気相堆積による、有機官能基と共にシリコンを含有するハイブリッド前駆体を使用する超低誘電材料 | |

| JP2008527757A5 (ja) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080205 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080403 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080507 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080805 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080902 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20080912 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20081003 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20101213 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20101220 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110117 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110124 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110414 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110530 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140603 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |