JP4485605B2 - 抵抗変化素子の駆動方法、初期処理方法、及び不揮発性記憶装置 - Google Patents

抵抗変化素子の駆動方法、初期処理方法、及び不揮発性記憶装置 Download PDFInfo

- Publication number

- JP4485605B2 JP4485605B2 JP2009554808A JP2009554808A JP4485605B2 JP 4485605 B2 JP4485605 B2 JP 4485605B2 JP 2009554808 A JP2009554808 A JP 2009554808A JP 2009554808 A JP2009554808 A JP 2009554808A JP 4485605 B2 JP4485605 B2 JP 4485605B2

- Authority

- JP

- Japan

- Prior art keywords

- resistance

- voltage

- metal oxide

- voltage pulse

- voltage value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0007—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising metal oxide memory material, e.g. perovskites

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0033—Disturbance prevention or evaluation; Refreshing of disturbed memory data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0064—Verifying circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0073—Write using bi-directional cell biasing

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0083—Write to perform initialising, forming process, electro forming or conditioning

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/009—Write using potential difference applied between cell electrodes

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/31—Material having complex metal oxide, e.g. perovskite structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/32—Material having simple binary metal oxide structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/34—Material includes an oxide or a nitride

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Materials Engineering (AREA)

- Semiconductor Memories (AREA)

Description

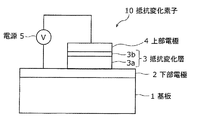

[抵抗変化素子の構成]

まず、本発明の実施の形態1の抵抗変化素子の構成について説明する。

次に、抵抗変化素子10の製造方法について説明する。

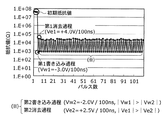

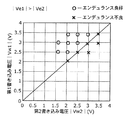

次に、上述した製造方法により得られた抵抗変化素子10の動作について説明する。

以下、比較例1の抵抗変化素子について説明する。なお、この比較例1の抵抗変化素子の構成は、本実施の形態の抵抗変化素子10と同様であるため、説明を省略する。

次に、比較例2の抵抗変化素子について説明する。なお、この比較例2の抵抗変化素子の構成も、本実施の形態の抵抗変化素子10と同様であるため、説明を省略する。

上述したように、実施の形態1の駆動方法は、抵抗変化素子10に良好なエンデュランス特性を与えているが、極めて稀に、第2書き込み過程または第2消去過程における書き込みに失敗する(つまり、抵抗変化層が所望の抵抗状態に変化しない)場合がある。実施の形態2の抵抗変化素子は、そのような失敗が起きた場合に、回復書き込み過程または回復消去過程を実行することによって、より安定した動作を得ることができるものである。

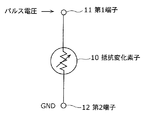

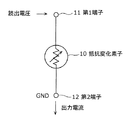

実施の形態3は、実施の形態1において説明した抵抗変化素子を備える不揮発性記憶装置である。以下、この不揮発性記憶装置の構成及び動作について説明する。

図15は、本発明の実施の形態3の不揮発性記憶装置の構成の一例を示すブロック図である。図15に示すように、不揮発性記憶装置200は、抵抗変化素子を具備するメモリアレイ201と、アドレスバッファ202と、制御部203と、行デコーダ204と、ワード線ドライバ205と、列デコーダ206と、ビット線/プレート線ドライバ207とを備えている。ここで、制御部203と、ワード線ドライバ205と、ビット線/プレート線ドライバ207とを、駆動部208と総称する。

以下、上述したように構成される不揮発性記憶装置200の動作例を、上記の記憶モード(メモリセルに入力データDinを書き込むモード)、リセットモード(メモリセルに書き込まれたデータをリセットするモード)、及び再生モード(メモリセルに書き込まれたデータを出力データDoutとして出力(再生)するモード)の各モードに分けて説明する。ここで、上記の第1書き込み過程及び第2書き込み過程は記憶モードに該当し、第1消去過程及び第2消去過程はリセットモードに該当する。

制御部203は、外部回路から入力データDinを受け取る。ここで、制御部203は、この入力データDinが「1」である場合に、「記憶電圧印加」を示す制御信号CONTをビット線/プレート線ドライバ207に出力する。一方、制御部203は、入力データDinが「0」である場合には制御信号CONTを出力しない。

制御部203は、「再生電圧印加」を指示する制御信号CONTをビット線/プレート線ドライバ207に出力する。

リセットモードにおいては、まず制御部203が、上記再生モードを実行することによってメモリセルMC211の抵抗値の状態(記憶状態)を取得する。そして、メモリセルMC211に「1」を示すビットデータが記憶されていると判定した場合(メモリセルMC211が低抵抗状態にあると判定した場合)、制御部203は、「リセット電圧印加」を示す制御信号CONTをビット線/プレート線ドライバ207に出力する。他方、メモリセルMC211に「0」を示すビットデータが記憶されていると判定した場合(メモリセルMC211が高抵抗状態にあると判定した場合)は、制御部203は上記制御信号CONTを出力しない。

実施の形態4は、実施の形態1において説明した抵抗変化素子を備えるクロスポイント型の不揮発性記憶装置である。ここで、クロスポイント型の不揮発性記憶装置とは、ワード線とビット線との交点(立体交差点)にアクティブ層を介在させた態様の記憶装置である。

図16は、本発明の実施の形態4の不揮発性記憶装置の構成の一例を示すブロック図である。図16に示すように、クロスポイント型の不揮発性記憶装置100は、抵抗変化素子を具備するメモリアレイ101と、アドレスバッファ102と、制御部103と、行デコーダ104と、ワード線ドライバ105と、列デコーダ106と、ビット線ドライバ107とを備えている。ここで、制御部103と、ワード線ドライバ105と、ビット線ドライバ107とを、駆動部108と総称する。

以下、上述したように構成される不揮発性記憶装置100の動作例を、上記の書き込みモード及び読み出しモードの各モードに分けて説明する。なお、ビット線及びワード線を選択する方法、並びに電圧パルスを印加する方法などについては、周知のものが利用可能であるため、詳細な説明を省略する。

メモリセルMC122に「1」を表す1ビットデータを書き込む(記憶する)場合、ビット線ドライバ107によりビット線B102が接地され、ワード線ドライバ105によりワード線W102と制御部103とが電気的に接続される。そして、制御部103により、ワード線W102に書き込み電圧パルスが印加される。ここで、書き込み電圧パルスの電圧値は、モード選択信号MODEの指定に応じて、第1書き込み過程においては−3.5Vに、第2書き込み過程においては−2.5Vにそれぞれ設定される。また、そのパルス幅は100nsに設定される。

メモリセルMC122に書き込まれているデータを読み出す場合、ビット線ドライバ107によりビット線B102が接地され、ワード線ドライバ105によりワード線W102と制御部103とが電気的に接続される。そして、制御部103により、ワード線W102に読出電圧が印加される。ここで、読出電圧の電圧値は+0.5Vに設定される。

上記の各実施の形態において、抵抗変化層はタンタル酸化物の積層構造で構成されていたが、本発明はこれに限定されるわけではない。例えば、ハフニウム(Hf)酸化物の積層構造またはジルコニウム(Zr)酸化物の積層構造などであってもよい。

2 下部電極

3 抵抗変化層

3a 第1タンタル酸化物層

3b 第2タンタル酸化物層

4 上部電極

5 電源

10 抵抗変化素子

11 第1端子

12 第2端子

100 不揮発性記憶装置

101 メモリアレイ

102 アドレスバッファ

103 制御部

104 行デコーダ

105 ワード線ドライバ

106 列デコーダ

107 ビット線ドライバ

108 駆動部

W101、W102、W103 ワード線

B101、B102、B103 ビット線

MC111、MC112、MC113、MC121、MC122、MC123、MC131、MC132、MC133 メモリセル

D111、D112、D113、D121、D122、D123、D131、D132、D133 電流制限素子

200 不揮発性記憶装置

201 メモリアレイ

202 アドレスバッファ

203 制御部

204 行デコーダ

205 ワード線ドライバ

206 列デコーダ

207 ビット線/プレート線ドライバ

208 駆動部

W201、W202 ワード線

B201、B202 ビット線

P201、P202 プレート線

MC211、MC212、MC221、MC222 メモリセル

T211、T212、T221、T222 トランジスタ

Claims (14)

- 与えられる電気的パルスに応じてその抵抗値が増加および減少する金属酸化物を備えた抵抗変化素子を駆動するための駆動方法であって、

前記金属酸化物は、第1の酸化物層と、当該第1の酸化物層よりも酸素含有率が高い第2の酸化物層とが積層されて構成されており、

前記駆動方法は、

第1の極性の電圧パルスである書き込み電圧パルスを前記金属酸化物に与えることによって、当該金属酸化物の抵抗状態を高から低へ変化させる、1回以上の書き込み過程と、

前記第1の極性とは異なる第2の極性の電圧パルスである消去電圧パルスを前記金属酸化物に与えることによって、当該金属酸化物の抵抗状態を低から高へ変化させる、1回以上の消去過程とを有し、

第1回目から第N回目(Nは1以上)までの前記書き込み過程における書き込み電圧パルスの電圧値をVw1とし、第(N+1)回目以降の前記書き込み過程における書き込み電圧パルスの電圧値をVw2とした場合に|Vw1|>|Vw2|を満たし、且つ、第1回目から第M回目(Mは1以上)までの前記消去過程における消去電圧パルスの電圧値をVe1とし、第(M+1)回目以降の前記消去過程における消去電圧パルスの電圧値をVe2とした場合に|Ve1|>|Ve2|を満たしており、

第M回目の消去過程の次に第(N+1)回目の前記書き込み過程が続く、抵抗変化素子の駆動方法。 - |Ve1|≧|Vw1|且つ|Ve2|≧|Vw2|をさらに満たす、請求項1に記載の抵抗変化素子の駆動方法。

- 第(N+1)回目以降の前記書き込み過程において、前記金属酸化物の抵抗状態を高から低への変化させることに失敗した場合に、電圧値がVw3(但し、|Vw3|>|Vw2|)である回復書き込み電圧パルスを前記金属酸化物に与えることによって、前記金属酸化物の抵抗状態を高から低へ変化させる回復書き込み過程と、

第(M+1)回目以降の前記消去過程において、前記金属酸化物の抵抗状態を低から高へ変化させることに失敗した場合に、電圧値がVe3(但し、|Ve3|>|Ve2|)である回復消去電圧パルスを前記金属酸化物に与えることによって、前記金属酸化物の抵抗状態を低から高へ変化させる回復消去過程と、

をさらに含む請求項1または2に記載の抵抗変化素子の駆動方法。 - 電圧値Vw1と電圧値Vw3とが等しく、且つ電圧値Ve1と電圧値Ve3とが等しい、請求項3に記載の抵抗変化素子の駆動方法。

- 前記第1の酸化物は、TaOx(但し、0.8≦x≦1.9)で表される組成を有するタンタル酸化物で構成され、

前記第2の酸化物は、TaOy(但し、2.1≦y<2.5)で表される組成を有するタンタル酸化物で構成される、請求項1乃至4の何れかに記載の抵抗変化素子の駆動方法。 - 第1電極と、第2電極と、前記第1電極と前記第2電極との間に介在し、両電極間に与えられる電気的パルスに応じてその抵抗値が増加および減少する金属酸化物を具備する抵抗変化素子と、駆動部とを備え、

前記金属酸化物は、第1の酸化物層と、当該第1の酸化物層よりも酸素含有率が高い第2の酸化物層とが積層されて構成されており、

前記駆動部は、

第1の極性の電圧パルスである書き込み電圧パルスを前記第1電極と前記第2電極との間に与えることによって、前記金属酸化物の抵抗状態を高から低へ変化させる書き込み過程と、

前記第1の極性とは異なる第2の極性の電圧パルスである消去電圧パルスを前記第1電極と前記第2電極との間に与えることによって、前記金属酸化物の抵抗状態を低から高へ変化させる消去過程とを実行し、

第1回目から第N回目(Nは1以上)までの前記書き込み過程における書き込み電圧パルスの電圧値をVw1とし、第(N+1)回目以降の前記書き込み過程における書き込み電圧パルスの電圧値をVw2とした場合に|Vw1|>|Vw2|を満たし、且つ、第1回目から第M回目(Mは1以上)までの前記消去過程における消去電圧パルスの電圧値をVe1とし、第(M+1)回目以降の前記消去過程における消去電圧パルスの電圧値をVe2とした場合に|Ve1|>|Ve2|を満たしており、

第M回目の消去過程の次に第(N+1)回目の前記書き込み過程が続く、不揮発性記憶装置。 - |Ve1|≧|Vw1|且つ|Ve2|≧|Vw2|をさらに満たす、請求項6に記載の不揮発性記憶装置。

- 前記駆動部は、

第(N+1)回目以降の前記書き込み過程において、前記金属酸化物の抵抗状態を高から低への変化させることに失敗した場合に、電圧値がVw3(但し、|Vw3|>|Vw2|)である回復書き込み電圧パルスを前記第1電極と前記第2電極との間に与えることによって、前記金属酸化物の抵抗状態を高から低へ変化させる回復書き込み過程と、

第(M+1)回目以降の前記消去過程において、前記金属酸化物の抵抗状態を低から高へ変化させることに失敗した場合に、電圧値がVe3(但し、|Ve3|>|Ve2|)である回復消去電圧パルスを前記第1電極と前記第2電極との間に与えることによって、前記金属酸化物の抵抗状態を低から高へ変化させる回復消去過程と、

をさらに実行する、請求項6または7に記載の不揮発性記憶装置。 - 電圧値Vw1と電圧値Vw3とが等しく、且つ電圧値Ve1と電圧値Ve3とが等しい、請求項8に記載の不揮発性記憶装置。

- 前記第1の酸化物は、TaOx(但し、0.8≦x≦1.9)で表される組成を有するタンタル酸化物で構成され、

前記第2の酸化物は、TaOy(但し、2.1≦y<2.5)で表される組成を有するタンタル酸化物で構成される、請求項6乃至9の何れかに記載の不揮発性記憶装置。 - 前記第1電極または前記第2電極に電気的に接続された電流制限素子をさらに備える、請求項6乃至10の何れかに記載の不揮発性記憶装置。

- 前記電流制限素子が選択トランジスタである、請求項11に記載の不揮発性記憶装置。

- 前記電流制限素子がダイオードである、請求項11に記載の不揮発性記憶装置。

- 与えられる電気的パルスに応じてその抵抗値が増加および減少する金属酸化物を備えた抵抗変化素子に対して初期処理を行うための初期処理方法であって、

前記金属酸化物は、第1の酸化物層と、当該第1の酸化物層よりも酸素含有率が高い第2の酸化物層とが積層されて構成されており、

第1の極性でかつ電圧値がVw2の書き込み電圧パルスを前記金属酸化物に与えることによって、前記金属酸化物の抵抗状態を高から低へ変化させる書き込み過程と、

前記書き込み過程に続いて、前記第1の極性とは異なる第2の極性でかつ電圧値がVe2の消去電圧パルスを前記金属酸化物に与えることによって、前記金属酸化物の抵抗状態を低から高へ変化させる消去過程と、

を繰り返すことによって、前記抵抗変化素子へのデータの書き込みと消去とが行われる場合に、

前記初期処理方法は、

前記第1の極性でかつ|Vw1|>|Vw2|を満たす電圧値Vw1の電圧パルスを前記金属酸化物に与えることによって、前記金属酸化物の抵抗状態を高から低へ変化させる、1回以上の初期書き込み過程と、

前記初期書き込み過程に続いて、前記第2の極性でかつ|Ve1|>|Ve2|を満たす電圧値Ve1の電圧パルスを前記金属酸化物に与えることによって、前記金属酸化物の抵抗状態を低から高へ変化させる、1回以上の初期消去過程と、

を含み、最後の前記初期消去過程の次に最初の前記書き込み過程が続く、抵抗変化素子の初期処理方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008253107 | 2008-09-30 | ||

| JP2008253107 | 2008-09-30 | ||

| PCT/JP2009/005017 WO2010038442A1 (ja) | 2008-09-30 | 2009-09-30 | 抵抗変化素子の駆動方法、初期処理方法、及び不揮発性記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP4485605B2 true JP4485605B2 (ja) | 2010-06-23 |

| JPWO2010038442A1 JPWO2010038442A1 (ja) | 2012-03-01 |

Family

ID=42073224

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009554808A Active JP4485605B2 (ja) | 2008-09-30 | 2009-09-30 | 抵抗変化素子の駆動方法、初期処理方法、及び不揮発性記憶装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8345465B2 (ja) |

| JP (1) | JP4485605B2 (ja) |

| CN (1) | CN101878507B (ja) |

| WO (1) | WO2010038442A1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8861265B2 (en) | 2011-09-22 | 2014-10-14 | Kabushiki Kaisha Toshiba | Semiconductor storage device and data control method thereof |

| US9111610B2 (en) | 2012-04-20 | 2015-08-18 | Panasonic Intellectual Property Management Co., Ltd. | Method of driving nonvolatile memory element and nonvolatile memory device |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102301425B (zh) | 2010-02-02 | 2013-10-30 | 松下电器产业株式会社 | 电阻变化元件的驱动方法、初始处理方法、以及非易失性存储装置 |

| US8385102B2 (en) * | 2010-05-11 | 2013-02-26 | Sandisk 3D Llc | Alternating bipolar forming voltage for resistivity-switching elements |

| US8520425B2 (en) | 2010-06-18 | 2013-08-27 | Sandisk 3D Llc | Resistive random access memory with low current operation |

| US8395927B2 (en) | 2010-06-18 | 2013-03-12 | Sandisk 3D Llc | Memory cell with resistance-switching layers including breakdown layer |

| JP5431267B2 (ja) * | 2010-08-04 | 2014-03-05 | パナソニック株式会社 | 抵抗変化素子の駆動方法及び不揮発性記憶装置 |

| JP5161946B2 (ja) * | 2010-09-30 | 2013-03-13 | シャープ株式会社 | 不揮発性半導体記憶装置 |

| KR101797106B1 (ko) * | 2010-10-26 | 2017-11-13 | 삼성전자주식회사 | 저항성 메모리 장치와 상기 저항성 메모리 장치를 포함하는 전자 장치들 |

| US8699258B2 (en) * | 2011-01-21 | 2014-04-15 | Macronix International Co., Ltd. | Verification algorithm for metal-oxide resistive memory |

| JP5723253B2 (ja) * | 2011-01-31 | 2015-05-27 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| CN103339680B (zh) * | 2011-02-01 | 2016-04-13 | 松下电器产业株式会社 | 非易失性半导体存储装置 |

| WO2012108151A1 (ja) | 2011-02-07 | 2012-08-16 | パナソニック株式会社 | 不揮発性ラッチ回路、不揮発性フリップフロップ回路および不揮発性信号処理装置 |

| WO2012108185A1 (ja) * | 2011-02-10 | 2012-08-16 | パナソニック株式会社 | 不揮発性記憶素子の駆動方法及び初期化方法、並びに不揮発性記憶装置 |

| JP5490961B2 (ja) * | 2011-03-14 | 2014-05-14 | パナソニック株式会社 | 不揮発性記憶素子の駆動方法及び不揮発性記憶装置 |

| WO2012132341A1 (ja) * | 2011-03-25 | 2012-10-04 | パナソニック株式会社 | 抵抗変化型不揮発性素子の書き込み方法および記憶装置 |

| JP5291269B2 (ja) * | 2011-06-27 | 2013-09-18 | パナソニック株式会社 | 不揮発性半導体記憶素子、不揮発性半導体記憶装置およびその製造方法 |

| JP5209151B1 (ja) * | 2011-08-11 | 2013-06-12 | パナソニック株式会社 | 抵抗変化型不揮発性記憶素子の書き込み方法 |

| JP5634367B2 (ja) * | 2011-09-26 | 2014-12-03 | 株式会社東芝 | 半導体記憶装置 |

| WO2013057912A1 (ja) * | 2011-10-18 | 2013-04-25 | パナソニック株式会社 | 不揮発性記憶素子、不揮発性記憶装置、及び不揮発性記憶素子の書き込み方法 |

| US9142773B2 (en) | 2012-01-25 | 2015-09-22 | Panasonic intellectual property Management co., Ltd | Variable resistance nonvolatile memory element and method of manufacturing the same |

| US9202565B2 (en) | 2012-03-23 | 2015-12-01 | Panasonic Intellectual Property Management Co., Ltd. | Write method for writing to variable resistance nonvolatile memory element and variable resistance nonvolatile memory device |

| JP5602175B2 (ja) * | 2012-03-26 | 2014-10-08 | 株式会社東芝 | 不揮発性半導体記憶装置及びそのデータ書き込み方法 |

| US9053789B1 (en) * | 2012-04-23 | 2015-06-09 | Adesto Technologies Corporation | Triggered cell annihilation for resistive switching memory devices |

| JP2014038675A (ja) * | 2012-08-15 | 2014-02-27 | Sony Corp | 記憶装置および駆動方法 |

| US8861258B2 (en) | 2013-02-21 | 2014-10-14 | Sandisk 3D Llc | Set/reset algorithm which detects and repairs weak cells in resistive-switching memory device |

| US9286976B2 (en) | 2014-05-29 | 2016-03-15 | Intel Corporation | Apparatuses and methods for detecting write completion for resistive memory |

| FR3029341B1 (fr) * | 2014-12-02 | 2016-12-30 | Commissariat Energie Atomique | Procede de programmation d'une memoire vive resistive |

| CN109410997B (zh) * | 2017-08-16 | 2021-04-30 | 华邦电子股份有限公司 | 电阻式存储器存储装置及其写入方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007004849A (ja) * | 2005-06-21 | 2007-01-11 | Sony Corp | 記憶装置及び記憶装置の駆動方法 |

| JP2007004873A (ja) * | 2005-06-22 | 2007-01-11 | Sony Corp | 記憶装置の初期化方法 |

| WO2008149484A1 (ja) * | 2007-06-05 | 2008-12-11 | Panasonic Corporation | 不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置 |

Family Cites Families (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6204139B1 (en) * | 1998-08-25 | 2001-03-20 | University Of Houston | Method for switching the properties of perovskite materials used in thin film resistors |

| US7663132B2 (en) * | 2002-04-04 | 2010-02-16 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US7767993B2 (en) * | 2002-04-04 | 2010-08-03 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US6972238B2 (en) * | 2003-05-21 | 2005-12-06 | Sharp Laboratories Of America, Inc. | Oxygen content system and method for controlling memory resistance properties |

| KR100773537B1 (ko) | 2003-06-03 | 2007-11-07 | 삼성전자주식회사 | 한 개의 스위칭 소자와 한 개의 저항체를 포함하는비휘발성 메모리 장치 및 그 제조 방법 |

| JP4113493B2 (ja) * | 2003-06-12 | 2008-07-09 | シャープ株式会社 | 不揮発性半導体記憶装置及びその制御方法 |

| US6930909B2 (en) * | 2003-06-25 | 2005-08-16 | Micron Technology, Inc. | Memory device and methods of controlling resistance variation and resistance profile drift |

| WO2005066969A1 (en) * | 2003-12-26 | 2005-07-21 | Matsushita Electric Industrial Co., Ltd. | Memory device, memory circuit and semiconductor integrated circuit having variable resistance |

| US7233520B2 (en) * | 2005-07-08 | 2007-06-19 | Micron Technology, Inc. | Process for erasing chalcogenide variable resistance memory bits |

| JP5049491B2 (ja) | 2005-12-22 | 2012-10-17 | パナソニック株式会社 | 電気素子,メモリ装置,および半導体集積回路 |

| JP4816088B2 (ja) | 2006-01-11 | 2011-11-16 | ソニー株式会社 | 記憶装置の初期化方法 |

| JP4203506B2 (ja) * | 2006-01-13 | 2009-01-07 | シャープ株式会社 | 不揮発性半導体記憶装置及びその書き換え方法 |

| WO2007145295A1 (ja) * | 2006-06-16 | 2007-12-21 | Panasonic Corporation | 不揮発性メモリ装置 |

| JP2008028228A (ja) * | 2006-07-24 | 2008-02-07 | Seiko Epson Corp | 可変抵抗素子および抵抗変化型メモリ装置 |

| EP1883109B1 (en) * | 2006-07-28 | 2013-05-15 | Semiconductor Energy Laboratory Co., Ltd. | Memory element and method of manufacturing thereof |

| JP5377839B2 (ja) * | 2006-07-28 | 2013-12-25 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP4373486B2 (ja) * | 2006-10-16 | 2009-11-25 | パナソニック株式会社 | 不揮発性記憶素子アレイおよびその製造方法 |

| JP4221031B2 (ja) * | 2007-02-09 | 2009-02-12 | シャープ株式会社 | 不揮発性半導体記憶装置及びその書き換え方法 |

| US8097878B2 (en) * | 2007-03-05 | 2012-01-17 | Intermolecular, Inc. | Nonvolatile memory elements with metal-deficient resistive-switching metal oxides |

| US7629198B2 (en) * | 2007-03-05 | 2009-12-08 | Intermolecular, Inc. | Methods for forming nonvolatile memory elements with resistive-switching metal oxides |

| US8144498B2 (en) * | 2007-05-09 | 2012-03-27 | Intermolecular, Inc. | Resistive-switching nonvolatile memory elements |

| JP4967176B2 (ja) | 2007-05-10 | 2012-07-04 | シャープ株式会社 | 可変抵抗素子とその製造方法及び不揮発性半導体記憶装置 |

| US8338816B2 (en) | 2007-10-15 | 2012-12-25 | Panasonic Corporation | Nonvolatile memory element, and nonvolatile semiconductor device using the nonvolatile memory element |

| JP2009164580A (ja) * | 2007-11-07 | 2009-07-23 | Interuniv Micro Electronica Centrum Vzw | 抵抗スイッチングNiO層を含むメモリ素子の製造方法、およびそのデバイス |

| JP2009141225A (ja) * | 2007-12-07 | 2009-06-25 | Sharp Corp | 可変抵抗素子、可変抵抗素子の製造方法、不揮発性半導体記憶装置 |

| WO2009107370A1 (ja) * | 2008-02-25 | 2009-09-03 | パナソニック株式会社 | 抵抗変化素子の駆動方法およびそれを用いた抵抗変化型記憶装置 |

| US8134194B2 (en) * | 2008-05-22 | 2012-03-13 | Micron Technology, Inc. | Memory cells, memory cell constructions, and memory cell programming methods |

| JP4469023B2 (ja) | 2008-07-11 | 2010-05-26 | パナソニック株式会社 | 不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置 |

| JP2010021381A (ja) | 2008-07-11 | 2010-01-28 | Panasonic Corp | 不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置 |

| JP5512525B2 (ja) * | 2008-09-08 | 2014-06-04 | 株式会社東芝 | 不揮発性記憶素子及び不揮発性記憶装置 |

| WO2010109876A1 (ja) * | 2009-03-25 | 2010-09-30 | パナソニック株式会社 | 抵抗変化素子の駆動方法及び不揮発性記憶装置 |

| US8305795B2 (en) * | 2009-04-27 | 2012-11-06 | Panasonic Corporation | Nonvolatile variable resistance memory element writing method, and nonvolatile variable resistance memory device |

| US8325508B2 (en) * | 2009-06-08 | 2012-12-04 | Panasonic Corporation | Writing method for variable resistance nonvolatile memory element, and variable resistance nonvolatile memory device |

| CN102301425B (zh) * | 2010-02-02 | 2013-10-30 | 松下电器产业株式会社 | 电阻变化元件的驱动方法、初始处理方法、以及非易失性存储装置 |

-

2009

- 2009-09-30 US US12/745,300 patent/US8345465B2/en active Active

- 2009-09-30 WO PCT/JP2009/005017 patent/WO2010038442A1/ja not_active Ceased

- 2009-09-30 CN CN2009801011725A patent/CN101878507B/zh active Active

- 2009-09-30 JP JP2009554808A patent/JP4485605B2/ja active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007004849A (ja) * | 2005-06-21 | 2007-01-11 | Sony Corp | 記憶装置及び記憶装置の駆動方法 |

| JP2007004873A (ja) * | 2005-06-22 | 2007-01-11 | Sony Corp | 記憶装置の初期化方法 |

| WO2008149484A1 (ja) * | 2007-06-05 | 2008-12-11 | Panasonic Corporation | 不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8861265B2 (en) | 2011-09-22 | 2014-10-14 | Kabushiki Kaisha Toshiba | Semiconductor storage device and data control method thereof |

| US9111610B2 (en) | 2012-04-20 | 2015-08-18 | Panasonic Intellectual Property Management Co., Ltd. | Method of driving nonvolatile memory element and nonvolatile memory device |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100271860A1 (en) | 2010-10-28 |

| US8345465B2 (en) | 2013-01-01 |

| CN101878507B (zh) | 2013-10-23 |

| CN101878507A (zh) | 2010-11-03 |

| WO2010038442A1 (ja) | 2010-04-08 |

| JPWO2010038442A1 (ja) | 2012-03-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4485605B2 (ja) | 抵抗変化素子の駆動方法、初期処理方法、及び不揮発性記憶装置 | |

| JP4778125B1 (ja) | 抵抗変化素子の駆動方法、初期処理方法、及び不揮発性記憶装置 | |

| JP4628501B2 (ja) | 抵抗変化素子の駆動方法及び不揮発性記憶装置 | |

| JP4607252B2 (ja) | 抵抗変化素子の駆動方法およびそれを用いた抵抗変化型記憶装置 | |

| JP5133471B2 (ja) | 抵抗変化型不揮発性素子の書き込み方法および記憶装置 | |

| JP4563511B2 (ja) | 不揮発性記憶装置 | |

| JPWO2008081742A1 (ja) | 抵抗変化型素子、抵抗変化型記憶装置、および抵抗変化型装置 | |

| JP5069339B2 (ja) | 不揮発性可変抵抗素子の抵抗制御方法 | |

| CN109791791B (zh) | 非易失性存储装置、以及驱动方法 | |

| JP5312709B1 (ja) | 抵抗変化素子の駆動方法及び不揮発性記憶装置 | |

| JP2014063549A (ja) | 半導体記憶装置 | |

| JP5431267B2 (ja) | 抵抗変化素子の駆動方法及び不揮発性記憶装置 | |

| JP2011233211A (ja) | 抵抗変化素子の駆動方法及び不揮発性記憶装置 | |

| JP2012169000A (ja) | 抵抗変化素子の駆動方法、不揮発性記憶装置、抵抗変化素子および多値記憶方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100223 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100324 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4485605 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130402 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130402 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140402 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |