JP2012009845A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2012009845A JP2012009845A JP2011113043A JP2011113043A JP2012009845A JP 2012009845 A JP2012009845 A JP 2012009845A JP 2011113043 A JP2011113043 A JP 2011113043A JP 2011113043 A JP2011113043 A JP 2011113043A JP 2012009845 A JP2012009845 A JP 2012009845A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- insulating layer

- oxide semiconductor

- oxide

- electrode layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 183

- 239000001257 hydrogen Substances 0.000 claims abstract description 90

- 229910052739 hydrogen Inorganic materials 0.000 claims abstract description 90

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims abstract description 75

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical group O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 23

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 22

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 20

- 229910052710 silicon Inorganic materials 0.000 claims description 20

- 239000010703 silicon Substances 0.000 claims description 20

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 8

- 229910000449 hafnium oxide Inorganic materials 0.000 claims description 4

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims description 4

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 4

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 claims description 4

- 229910001936 tantalum oxide Inorganic materials 0.000 claims description 4

- 150000002431 hydrogen Chemical class 0.000 abstract description 15

- 238000009792 diffusion process Methods 0.000 abstract description 9

- 238000009413 insulation Methods 0.000 abstract 6

- 230000006866 deterioration Effects 0.000 abstract 1

- 230000002542 deteriorative effect Effects 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 386

- 239000010408 film Substances 0.000 description 75

- 125000004429 atom Chemical group 0.000 description 72

- 239000000758 substrate Substances 0.000 description 68

- 239000007789 gas Substances 0.000 description 50

- 238000000034 method Methods 0.000 description 50

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 46

- 238000004544 sputter deposition Methods 0.000 description 44

- 238000010438 heat treatment Methods 0.000 description 40

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 31

- 229910052760 oxygen Inorganic materials 0.000 description 30

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 26

- 239000001301 oxygen Substances 0.000 description 26

- 238000005530 etching Methods 0.000 description 24

- 229910052786 argon Inorganic materials 0.000 description 23

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 22

- 238000004519 manufacturing process Methods 0.000 description 21

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 20

- 229910052719 titanium Inorganic materials 0.000 description 20

- 239000010936 titanium Substances 0.000 description 20

- 239000012298 atmosphere Substances 0.000 description 17

- 229910004298 SiO 2 Inorganic materials 0.000 description 16

- 238000006243 chemical reaction Methods 0.000 description 16

- 229910007541 Zn O Inorganic materials 0.000 description 15

- 239000012535 impurity Substances 0.000 description 13

- 239000011701 zinc Substances 0.000 description 13

- 230000002349 favourable effect Effects 0.000 description 12

- 239000011521 glass Substances 0.000 description 12

- 238000000151 deposition Methods 0.000 description 11

- 229910052757 nitrogen Inorganic materials 0.000 description 11

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 11

- 230000008021 deposition Effects 0.000 description 10

- 239000000463 material Substances 0.000 description 9

- 238000000206 photolithography Methods 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 8

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 8

- 230000007547 defect Effects 0.000 description 8

- 229910052733 gallium Inorganic materials 0.000 description 8

- 229910044991 metal oxide Inorganic materials 0.000 description 8

- 150000004706 metal oxides Chemical class 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 7

- 239000001307 helium Substances 0.000 description 7

- 229910052734 helium Inorganic materials 0.000 description 7

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 7

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 230000006870 function Effects 0.000 description 6

- 239000011261 inert gas Substances 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 229910052754 neon Inorganic materials 0.000 description 6

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 6

- 238000001552 radio frequency sputter deposition Methods 0.000 description 6

- 229910052725 zinc Inorganic materials 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 229910052738 indium Inorganic materials 0.000 description 5

- 238000009616 inductively coupled plasma Methods 0.000 description 5

- 239000000203 mixture Substances 0.000 description 5

- 239000011733 molybdenum Substances 0.000 description 5

- 229910052750 molybdenum Inorganic materials 0.000 description 5

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- 239000012300 argon atmosphere Substances 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 4

- 239000004973 liquid crystal related substance Substances 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 238000009832 plasma treatment Methods 0.000 description 4

- 238000004151 rapid thermal annealing Methods 0.000 description 4

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 3

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 3

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 3

- 229910019092 Mg-O Inorganic materials 0.000 description 3

- 229910019395 Mg—O Inorganic materials 0.000 description 3

- 229910052779 Neodymium Inorganic materials 0.000 description 3

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 3

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 238000005401 electroluminescence Methods 0.000 description 3

- 238000003780 insertion Methods 0.000 description 3

- 230000037431 insertion Effects 0.000 description 3

- 239000007769 metal material Substances 0.000 description 3

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 229960001730 nitrous oxide Drugs 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 238000001678 elastic recoil detection analysis Methods 0.000 description 2

- 150000004678 hydrides Chemical class 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 235000013842 nitrous oxide Nutrition 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- 239000003870 refractory metal Substances 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- 229910052706 scandium Inorganic materials 0.000 description 2

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- 229910052723 transition metal Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- BSYNRYMUTXBXSQ-UHFFFAOYSA-N Aspirin Chemical compound CC(=O)OC1=CC=CC=C1C(O)=O BSYNRYMUTXBXSQ-UHFFFAOYSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 108010083687 Ion Pumps Proteins 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229910020923 Sn-O Inorganic materials 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- JYMITAMFTJDTAE-UHFFFAOYSA-N aluminum zinc oxygen(2-) Chemical compound [O-2].[Al+3].[Zn+2] JYMITAMFTJDTAE-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 229910052810 boron oxide Inorganic materials 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- -1 copper-magnesium-aluminum Chemical compound 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000018044 dehydration Effects 0.000 description 1

- 238000006297 dehydration reaction Methods 0.000 description 1

- 238000006356 dehydrogenation reaction Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- JKWMSGQKBLHBQQ-UHFFFAOYSA-N diboron trioxide Chemical compound O=BOB=O JKWMSGQKBLHBQQ-UHFFFAOYSA-N 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 150000002222 fluorine compounds Chemical class 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000001755 magnetron sputter deposition Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- QKCGXXHCELUCKW-UHFFFAOYSA-N n-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amine Chemical compound C1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21 QKCGXXHCELUCKW-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 238000000859 sublimation Methods 0.000 description 1

- 230000008022 sublimation Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 239000013077 target material Substances 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910000314 transition metal oxide Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/24—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only semiconductor materials not provided for in groups H01L29/16, H01L29/18, H01L29/20, H01L29/22

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

- H01L29/513—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures the variation being perpendicular to the channel plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/517—Insulating materials associated therewith the insulating material comprising a metallic compound, e.g. metal oxide, metal silicate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/518—Insulating materials associated therewith the insulating material containing nitrogen, e.g. nitride, oxynitride, nitrogen-doped material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

- Formation Of Insulating Films (AREA)

Abstract

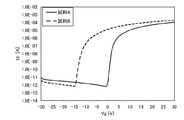

【解決手段】酸化物半導体層と接する絶縁層に水素濃度が6×1020atoms/cm3未満である絶縁層を用いる。さらに、水素濃度が6×1020atoms/cm3未満であるゲート絶縁層を用いてもよい。このようにすることで、酸化物半導体層に水素が拡散することを抑制することができ、良好な電気特性を有する半導体装置を提供することができる。

【選択図】図1

Description

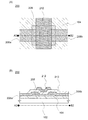

本実施の形態では、本発明の一態様である半導体装置について図1を用いて説明する。

本実施の形態では、実施の形態1で示した半導体装置の作製方法について図2を用いて説明する。

本実施の形態では、本発明の別の一態様である半導体装置について図3を用いて説明する。

得られる酸化シリコン層の水素濃度を低減させるため、好ましくは、SiO2ターゲットとし、より好ましくは、SiO2ターゲットに含まれる水酸基濃度が1000ppm以下、またはSIMSで測定した水素濃度が3.5×1019atoms/cm3以下であるSiO2ターゲットとすることである。さらに、形成する際に供給するガスはアルゴン等の希ガスおよび、酸素とする。そして、該形成する際に供給するガスは、水素、水、水酸基または水素化物などの不純物濃度がppm程度、またはppb程度まで除去された高純度ガスを用いることが好ましい。

本実施の形態では、実施の形態3に記載した半導体装置の作製方法について図4を用いて説明する。

上記実施の形態で説明したトランジスタを作製し、該トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置(表示装置ともいう)を作製することができる。また、トランジスタを用いた駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。また、上記実施の形態で記載した酸化物半導体を用いたトランジスタで、メモリセルを含んだ半導体装置を作製することもできる。

上記実施の形態で説明したトランジスタを用いた表示装置は、電子インクを駆動させて表示する電子ペーパーに適用することができる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍(電子ブック)、ポスター、デジタルサイネージ、PID(Public Information Display)、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図5に示す。

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラやデジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などがある。

102 基板

104 絶縁層

106a ソース電極層

106b ドレイン電極層

107 酸化物半導体層

108 酸化物半導体層

110 ゲート絶縁層

112 ゲート電極層

200 トランジスタ

206a ソース電極層

206b ドレイン電極層

207 酸化物半導体層

208 酸化物半導体層

210 ゲート絶縁層

212 ゲート電極層

2700 電子書籍

2701 筐体

2703 筐体

2705 表示部

2706 光電変換装置

2707 表示部

2708 光電変換装置

2711 軸部

2721 電源

2723 操作キー

2725 スピーカ

9301 上部筐体

9302 下部筐体

9303 表示部

9304 キーボード

9305 外部接続ポート

9306 ポインティングデバイス

9307 表示部

9600 テレビジョン装置

9601 筐体

9603 表示部

9605 スタンド

9607 表示部

9609 操作キー

9610 リモコン操作機

9700 デジタルフォトフレーム

9701 筐体

9703 表示部

Claims (7)

- ゲート電極層と、

酸化物半導体層と、

前記酸化物半導体層と接するソース電極層およびドレイン電極層と、

前記ゲート電極層と前記酸化物半導体層の間に設けられるゲート絶縁層と、

前記酸化物半導体層を介して、前記ゲート絶縁層と対向し、且つ前記酸化物半導体層に接する水素濃度が6×1020atoms/cm3未満である絶縁層と、を有することを特徴とする半導体装置。 - 請求項1において、

前記絶縁層および前記ゲート絶縁層は、酸化物絶縁層であることを特徴とする半導体装置。 - 請求項2において、

前記酸化物絶縁層は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ハフニウム、酸化アルミニウム、または酸化タンタルであることを特徴とする半導体装置。 - 請求項1乃至請求項3のいずれか一において、

前記ゲート電極層は、前記ゲート絶縁層を介して前記酸化物半導体層に重畳し、且つ前記ソース電極層と前記ドレイン電極層との間に設けられることを特徴とする半導体装置。 - 請求項1乃至請求項4のいずれか一において、

前記ソース電極層および前記ドレイン電極層は、前記酸化物半導体層と前記ゲート絶縁層との間に有することを特徴とする半導体装置。 - 請求項1乃至請求項4のいずれか一において、

前記ソース電極層および前記ドレイン電極層は、前記酸化物半導体層と前記絶縁層との間に有することを特徴とする半導体装置。 - 請求項1乃至請求項6のいずれか一において、

前記ゲート絶縁層における水素濃度が6×1020atoms/cm3未満であることを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011113043A JP2012009845A (ja) | 2010-05-21 | 2011-05-20 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010117086 | 2010-05-21 | ||

| JP2010117086 | 2010-05-21 | ||

| JP2011113043A JP2012009845A (ja) | 2010-05-21 | 2011-05-20 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015240237A Division JP2016034046A (ja) | 2010-05-21 | 2015-12-09 | 半導体装置の作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012009845A true JP2012009845A (ja) | 2012-01-12 |

| JP2012009845A5 JP2012009845A5 (ja) | 2014-06-19 |

Family

ID=44971763

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011113043A Withdrawn JP2012009845A (ja) | 2010-05-21 | 2011-05-20 | 半導体装置 |

| JP2015240237A Withdrawn JP2016034046A (ja) | 2010-05-21 | 2015-12-09 | 半導体装置の作製方法 |

| JP2017183258A Active JP6469797B2 (ja) | 2010-05-21 | 2017-09-25 | 半導体装置の作製方法 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015240237A Withdrawn JP2016034046A (ja) | 2010-05-21 | 2015-12-09 | 半導体装置の作製方法 |

| JP2017183258A Active JP6469797B2 (ja) | 2010-05-21 | 2017-09-25 | 半導体装置の作製方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US8853684B2 (ja) |

| JP (3) | JP2012009845A (ja) |

| TW (4) | TWI603474B (ja) |

| WO (1) | WO2011145484A1 (ja) |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013168642A (ja) * | 2012-01-18 | 2013-08-29 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2014225624A (ja) * | 2012-08-31 | 2014-12-04 | 株式会社神戸製鋼所 | 薄膜トランジスタおよび表示装置 |

| JP2015005672A (ja) * | 2013-06-21 | 2015-01-08 | 出光興産株式会社 | 酸化物トランジスタ |

| JP2015144172A (ja) * | 2014-01-31 | 2015-08-06 | 国立研究開発法人物質・材料研究機構 | 酸化物半導体およびその製法 |

| JPWO2015198604A1 (ja) * | 2014-06-26 | 2017-04-20 | 株式会社Joled | 薄膜トランジスタ及び有機el表示装置 |

| KR101778224B1 (ko) | 2010-10-12 | 2017-09-15 | 삼성전자주식회사 | 트랜지스터와 그 제조방법 및 트랜지스터를 포함하는 전자소자 |

| KR20180079114A (ko) * | 2016-12-30 | 2018-07-10 | 엘지디스플레이 주식회사 | 박막 트랜지스터 기판 및 표시 장치 |

| US10566457B2 (en) | 2012-08-31 | 2020-02-18 | Kabushiki Kaisha Kobe Seiko Sho (Kobe Steel, Ltd.) | Thin film transistor and display device |

| US11387258B2 (en) | 2018-11-12 | 2022-07-12 | Seiko Epson Corporation | Substrate for electro-optical device, electro-optical device, and electronic apparatus |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011145484A1 (en) | 2010-05-21 | 2011-11-24 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8860023B2 (en) | 2012-05-01 | 2014-10-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6152729B2 (ja) * | 2013-03-26 | 2017-06-28 | ソニー株式会社 | 撮像装置および撮像表示システム |

| CN103236441B (zh) * | 2013-04-22 | 2015-11-25 | 深圳市华星光电技术有限公司 | 开关管及其制备方法、显示面板 |

| CN103487982A (zh) * | 2013-08-19 | 2014-01-01 | 京东方科技集团股份有限公司 | 显示装置、阵列基板、像素结构及制作方法 |

| WO2015083303A1 (ja) * | 2013-12-02 | 2015-06-11 | 株式会社Joled | 薄膜トランジスタ及びその製造方法 |

| TWI669761B (zh) * | 2014-05-30 | 2019-08-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置、包括該半導體裝置的顯示裝置 |

| TWI666776B (zh) | 2014-06-20 | 2019-07-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置以及包括該半導體裝置的顯示裝置 |

| CN113223967A (zh) * | 2015-03-03 | 2021-08-06 | 株式会社半导体能源研究所 | 半导体装置、该半导体装置的制造方法或包括该半导体装置的显示装置 |

| US10192995B2 (en) | 2015-04-28 | 2019-01-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR102374537B1 (ko) | 2015-08-21 | 2022-03-15 | 삼성디스플레이 주식회사 | 표시 장치 |

| TWI648844B (zh) | 2017-11-06 | 2019-01-21 | Industrial Technology Research Institute | 薄膜電晶體及其製造方法 |

| CN111403425B (zh) * | 2020-03-31 | 2023-04-14 | 成都京东方显示科技有限公司 | 阵列基板及其制作方法、显示面板 |

| US12009432B2 (en) | 2021-03-05 | 2024-06-11 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006165529A (ja) * | 2004-11-10 | 2006-06-22 | Canon Inc | 非晶質酸化物、及び電界効果型トランジスタ |

| WO2007148601A1 (ja) * | 2006-06-19 | 2007-12-27 | Panasonic Corporation | 薄膜トランジスタおよびその製造方法ならびにそれを用いた電子機器 |

| JP2008042088A (ja) * | 2006-08-09 | 2008-02-21 | Nec Corp | 薄膜デバイス及びその製造方法 |

| JP2008141119A (ja) * | 2006-12-05 | 2008-06-19 | Canon Inc | 酸化物半導体を用いた表示装置及びその製造方法 |

| JP2009141002A (ja) * | 2007-12-04 | 2009-06-25 | Canon Inc | 絶縁層を有する酸化物半導体素子およびそれを用いた表示装置 |

| JP2009224479A (ja) * | 2008-03-14 | 2009-10-01 | Fujifilm Corp | 薄膜電界効果型トランジスタおよびその製造方法 |

| JP2010016347A (ja) * | 2008-06-30 | 2010-01-21 | Samsung Mobile Display Co Ltd | 薄膜トランジスタ、その製造方法及び薄膜トランジスタを備える平板表示装置 |

| JP2010062229A (ja) * | 2008-09-01 | 2010-03-18 | Semiconductor Energy Lab Co Ltd | 薄膜トランジスタ及び薄膜トランジスタの作製方法 |

Family Cites Families (135)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| US4987102A (en) * | 1989-12-04 | 1991-01-22 | Motorola, Inc. | Process for forming high purity thin films |

| US5210050A (en) * | 1990-10-15 | 1993-05-11 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device comprising a semiconductor film |

| JPH0529301A (ja) * | 1991-07-23 | 1993-02-05 | Seiko Epson Corp | Cvd法 |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3451380B2 (ja) * | 1992-11-24 | 2003-09-29 | 東京エレクトロン株式会社 | 半導体装置の製造方法 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| WO1997006554A2 (en) | 1995-08-03 | 1997-02-20 | Philips Electronics N.V. | Semiconductor device provided with transparent switching element |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP2002075987A (ja) | 2000-08-25 | 2002-03-15 | Toyota Central Res & Dev Lab Inc | 半導体装置の製造方法 |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| TWI247182B (en) * | 2000-09-29 | 2006-01-11 | Toshiba Corp | Flat panel display device and method for manufacturing the same |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| US6852997B2 (en) * | 2001-10-30 | 2005-02-08 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US7061014B2 (en) | 2001-11-05 | 2006-06-13 | Japan Science And Technology Agency | Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| CN1445821A (zh) | 2002-03-15 | 2003-10-01 | 三洋电机株式会社 | ZnO膜和ZnO半导体层的形成方法、半导体元件及其制造方法 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| TWI288443B (en) * | 2002-05-17 | 2007-10-11 | Semiconductor Energy Lab | SiN film, semiconductor device, and the manufacturing method thereof |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| JP4620046B2 (ja) | 2004-03-12 | 2011-01-26 | 独立行政法人科学技術振興機構 | 薄膜トランジスタ及びその製造方法 |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| JP2005285975A (ja) * | 2004-03-29 | 2005-10-13 | Seiko Epson Corp | 半導体装置及びその製造方法、電気光学装置並びに電子機器 |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| WO2006051995A1 (en) | 2004-11-10 | 2006-05-18 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| JP5126729B2 (ja) | 2004-11-10 | 2013-01-23 | キヤノン株式会社 | 画像表示装置 |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| CA2708335A1 (en) | 2004-11-10 | 2006-05-18 | Canon Kabushiki Kaisha | Amorphous oxide and field effect transistor |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| JP5118810B2 (ja) | 2004-11-10 | 2013-01-16 | キヤノン株式会社 | 電界効果型トランジスタ |

| AU2005302963B2 (en) | 2004-11-10 | 2009-07-02 | Cannon Kabushiki Kaisha | Light-emitting device |

| US7989694B2 (en) | 2004-12-06 | 2011-08-02 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion element, solar battery, and photo sensor |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| US7608531B2 (en) | 2005-01-28 | 2009-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP5084169B2 (ja) * | 2005-04-28 | 2012-11-28 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TWI408734B (zh) | 2005-04-28 | 2013-09-11 | Semiconductor Energy Lab | 半導體裝置及其製造方法 |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4850457B2 (ja) * | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| EP3614442A3 (en) | 2005-09-29 | 2020-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having oxide semiconductor layer and manufactoring method thereof |

| JP5064747B2 (ja) | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101117948B1 (ko) | 2005-11-15 | 2012-02-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 디스플레이 장치 제조 방법 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| JP5110803B2 (ja) * | 2006-03-17 | 2012-12-26 | キヤノン株式会社 | 酸化物膜をチャネルに用いた電界効果型トランジスタ及びその製造方法 |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5235333B2 (ja) * | 2006-05-26 | 2013-07-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| WO2007138937A1 (en) | 2006-05-26 | 2007-12-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| US7642114B2 (en) | 2006-07-19 | 2010-01-05 | Semiconductor Energy Laboratory Co., Ltd. | Micro electro mechanical device and manufacturing method thereof |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| KR101440930B1 (ko) | 2007-04-20 | 2014-09-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | Soi 기판의 제작방법 |

| WO2008133345A1 (en) | 2007-04-25 | 2008-11-06 | Canon Kabushiki Kaisha | Oxynitride semiconductor |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| US20080296567A1 (en) * | 2007-06-04 | 2008-12-04 | Irving Lyn M | Method of making thin film transistors comprising zinc-oxide-based semiconductor materials |

| US8809203B2 (en) * | 2007-06-05 | 2014-08-19 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device using a microwave plasma CVD apparatus |

| US8049253B2 (en) * | 2007-07-11 | 2011-11-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| CN101933147B (zh) | 2008-01-14 | 2012-07-04 | 沃特拉半导体公司 | 具保护沟道的功率晶体管及其制造方法 |

| JP2010040552A (ja) * | 2008-07-31 | 2010-02-18 | Idemitsu Kosan Co Ltd | 薄膜トランジスタ及びその製造方法 |

| KR101497425B1 (ko) * | 2008-08-28 | 2015-03-03 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| JP5627071B2 (ja) | 2008-09-01 | 2014-11-19 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| KR101612147B1 (ko) * | 2008-10-23 | 2016-04-12 | 이데미쓰 고산 가부시키가이샤 | 박막 트랜지스터 및 그 제조방법 |

| CN101464892A (zh) | 2008-12-31 | 2009-06-24 | 中兴通讯股份有限公司 | 一种动态数据库的登录方法及装置 |

| WO2010103935A1 (en) | 2009-03-12 | 2010-09-16 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR101645146B1 (ko) | 2009-06-30 | 2016-08-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제조 방법 |

| CN102576677B (zh) | 2009-09-24 | 2015-07-22 | 株式会社半导体能源研究所 | 半导体元件及其制造方法 |

| WO2011048959A1 (en) | 2009-10-21 | 2011-04-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| WO2011145484A1 (en) * | 2010-05-21 | 2011-11-24 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8552425B2 (en) | 2010-06-18 | 2013-10-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

-

2011

- 2011-04-28 WO PCT/JP2011/060792 patent/WO2011145484A1/en active Application Filing

- 2011-05-17 US US13/109,594 patent/US8853684B2/en active Active

- 2011-05-18 TW TW105106499A patent/TWI603474B/zh not_active IP Right Cessation

- 2011-05-18 TW TW104127325A patent/TWI535026B/zh active

- 2011-05-18 TW TW106103299A patent/TWI612675B/zh active

- 2011-05-18 TW TW100117408A patent/TWI508292B/zh active

- 2011-05-20 JP JP2011113043A patent/JP2012009845A/ja not_active Withdrawn

-

2014

- 2014-09-30 US US14/501,965 patent/US9443988B2/en active Active

-

2015

- 2015-12-09 JP JP2015240237A patent/JP2016034046A/ja not_active Withdrawn

-

2016

- 2016-09-08 US US15/259,294 patent/US9842939B2/en active Active

-

2017

- 2017-09-25 JP JP2017183258A patent/JP6469797B2/ja active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006165529A (ja) * | 2004-11-10 | 2006-06-22 | Canon Inc | 非晶質酸化物、及び電界効果型トランジスタ |

| WO2007148601A1 (ja) * | 2006-06-19 | 2007-12-27 | Panasonic Corporation | 薄膜トランジスタおよびその製造方法ならびにそれを用いた電子機器 |

| JP2008042088A (ja) * | 2006-08-09 | 2008-02-21 | Nec Corp | 薄膜デバイス及びその製造方法 |

| JP2008141119A (ja) * | 2006-12-05 | 2008-06-19 | Canon Inc | 酸化物半導体を用いた表示装置及びその製造方法 |

| JP2009141002A (ja) * | 2007-12-04 | 2009-06-25 | Canon Inc | 絶縁層を有する酸化物半導体素子およびそれを用いた表示装置 |

| JP2009224479A (ja) * | 2008-03-14 | 2009-10-01 | Fujifilm Corp | 薄膜電界効果型トランジスタおよびその製造方法 |

| JP2010016347A (ja) * | 2008-06-30 | 2010-01-21 | Samsung Mobile Display Co Ltd | 薄膜トランジスタ、その製造方法及び薄膜トランジスタを備える平板表示装置 |

| JP2010062229A (ja) * | 2008-09-01 | 2010-03-18 | Semiconductor Energy Lab Co Ltd | 薄膜トランジスタ及び薄膜トランジスタの作製方法 |

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101778224B1 (ko) | 2010-10-12 | 2017-09-15 | 삼성전자주식회사 | 트랜지스터와 그 제조방법 및 트랜지스터를 포함하는 전자소자 |

| US10483402B2 (en) | 2012-01-18 | 2019-11-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9614100B2 (en) | 2012-01-18 | 2017-04-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2013168642A (ja) * | 2012-01-18 | 2013-08-29 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2014225624A (ja) * | 2012-08-31 | 2014-12-04 | 株式会社神戸製鋼所 | 薄膜トランジスタおよび表示装置 |

| US9449990B2 (en) | 2012-08-31 | 2016-09-20 | Kobe Steel, Ltd. | Thin film transistor and display device |

| US10566457B2 (en) | 2012-08-31 | 2020-02-18 | Kabushiki Kaisha Kobe Seiko Sho (Kobe Steel, Ltd.) | Thin film transistor and display device |

| JP2015005672A (ja) * | 2013-06-21 | 2015-01-08 | 出光興産株式会社 | 酸化物トランジスタ |

| JP2015144172A (ja) * | 2014-01-31 | 2015-08-06 | 国立研究開発法人物質・材料研究機構 | 酸化物半導体およびその製法 |

| JPWO2015198604A1 (ja) * | 2014-06-26 | 2017-04-20 | 株式会社Joled | 薄膜トランジスタ及び有機el表示装置 |

| US10008611B2 (en) | 2014-06-26 | 2018-06-26 | Joled Inc. | Thin film transistor and organic EL display device |

| JP2018110226A (ja) * | 2016-12-30 | 2018-07-12 | エルジー ディスプレイ カンパニー リミテッド | 薄膜トランジスタ基板及び表示装置 |

| KR20180079114A (ko) * | 2016-12-30 | 2018-07-10 | 엘지디스플레이 주식회사 | 박막 트랜지스터 기판 및 표시 장치 |

| KR102627305B1 (ko) * | 2016-12-30 | 2024-01-18 | 한양대학교 산학협력단 | 박막 트랜지스터 기판 및 표시 장치 |

| US11387258B2 (en) | 2018-11-12 | 2022-07-12 | Seiko Epson Corporation | Substrate for electro-optical device, electro-optical device, and electronic apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017228806A (ja) | 2017-12-28 |

| US9842939B2 (en) | 2017-12-12 |

| TWI535026B (zh) | 2016-05-21 |

| WO2011145484A1 (en) | 2011-11-24 |

| US9443988B2 (en) | 2016-09-13 |

| US20160380106A1 (en) | 2016-12-29 |

| TW201210024A (en) | 2012-03-01 |

| TW201721874A (zh) | 2017-06-16 |

| TWI612675B (zh) | 2018-01-21 |

| US8853684B2 (en) | 2014-10-07 |

| JP2016034046A (ja) | 2016-03-10 |

| JP6469797B2 (ja) | 2019-02-13 |

| TW201622153A (zh) | 2016-06-16 |

| TWI508292B (zh) | 2015-11-11 |

| US20150053975A1 (en) | 2015-02-26 |

| US20110284854A1 (en) | 2011-11-24 |

| TW201545354A (zh) | 2015-12-01 |

| TWI603474B (zh) | 2017-10-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6469797B2 (ja) | 半導体装置の作製方法 | |

| JP6240703B2 (ja) | 半導体装置の作製方法 | |

| JP7561951B2 (ja) | 半導体装置 | |

| JP6630779B2 (ja) | 半導体装置の作製方法 | |

| JP5802068B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140425 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140425 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150331 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150427 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20151027 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20151210 |