本発明は、絶縁膜及びその作製方法に関する。また、半導体装置又は不揮発性半導体記憶装置及びその作製方法に関する。

近年、集積回路や様々な高機能素子などの発展に伴い、素子の微細化が進んでいる。それに伴い、スイッチング素子等に用いられるトランジスタのゲート絶縁膜の薄膜化が検討されている。

しかし、ゲート絶縁膜を薄膜化すると、ゲート電極と半導体膜もしくは半導体基板との間にリーク電流が流れる等の不良が生じ、半導体装置の信頼性が低下するおそれがある。したがって、高耐圧な絶縁膜が求められている。

例えば、特許文献1では、酸化膜を形成する際に酸化イオンを注入し、その後に熱処理することによって酸化膜の耐圧強度を向上させる技術が開示されている。

また、一般的な酸化膜形成工程では、酸化膜中に水素が取り込まれやすいことが知られている。酸化膜中に水素が取り込まれると、O−H結合が生成されやすい。酸化膜中にO−H結合が存在すると、O−H結合が電子トラップとなり、酸化膜の耐圧を低下させたり、MIS(Metal Insulator Semiconductor)型電界効果型トランジスタ(FET:Field Effect Transistor)の閾値を変動させるなど、劣化の要因となる。したがって、ゲート絶縁膜は、電子トラップが少ない膜であることが求められている。

特開平5−55200号公報

そこで本発明は、膜特性に優れる絶縁膜を製造する技術を提供することを目的とする。

また、本発明は、緻密で高耐圧な絶縁膜を製造する技術を提供することを目的とする。

また、本発明は、電子トラップの少ない絶縁膜を製造する技術を提供することを目的とする。

また、本発明は信頼性の高い半導体装置又は不揮発性半導体記憶装置を歩留まり良く製造する技術を提供することを目的とする。

本発明は、酸素を含む絶縁膜に対して、マイクロ波等の高周波により励起されたプラズマを用いてプラズマ処理を行うことを特徴としている。具体的には、高周波を用いて励起され、電子密度が1×1011cm−3以上、且つ電子温度が1.5eV以下の条件のプラズマを利用してプラズマ処理を行うことを特徴としている。

酸素を含む絶縁膜としては、CVD法、スパッタ法又は熱酸化法等を用いて形成する。例えば、酸素を含む絶縁膜として、酸化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等を含む膜を形成することができる。

また、本発明は、酸素と水素を含む絶縁膜に対して、マイクロ波等の高周波により励起されたプラズマを用いてプラズマ処理を行うことを特徴としている。具体的には、高周波を用いて電子密度が1×1011cm−3以上、且つ電子温度が1.5eV以下の条件でプラズマ処理を行うことを特徴としている。

酸素と水素とを含む絶縁膜は、CVD法、スパッタ法又は熱酸化法等を用いて形成することができる。これらの方法は、形成工程において膜中に水素を取り込みやすい。したがって、例えば、CVD法、スパッタ法又は熱酸化法を用いて酸化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等を含む膜を形成すると、膜中に水素が含まれる膜を形成することができる。

プラズマ処理は、マイクロ波等の高周波により励起されたプラズマを用いて行う。具体的には、高周波を用いて電子密度が1×1011cm−3以上、且つ電子温度が1.5eV以下の条件でプラズマ処理を行う。詳しくは、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上1×1013cm−3以下、且つ電子温度が0.5eV以上1.5eV以下のプラズマを利用して行うことが好ましい。

また、プラズマ処理は、少なくとも酸素を含む雰囲気下で行う。このとき、酸素の他、希ガス(He、Ne、Ar、Kr、Xeの少なくとも1つを含む)を含む雰囲気であることが好ましい。なお、希ガスを含む雰囲気下でプラズマ処理を行う場合には、プラズマ処理後の絶縁膜に希ガスが含まれる場合がある。

以下、本明細書では、酸素を含む雰囲気下で、上記条件のようなプラズマ処理を行うことを「プラズマ酸化」という場合がある。

また、本発明は、酸素と水素を含む絶縁膜に対してプラズマ処理を行うことで、膜中の水素含有量(水素濃度)を低減させることができる。例えば、上記条件を用いてプラズマ処理を行った場合、二次イオン質量分析(SIMS)による水素濃度測定において、プラズマ処理後の膜中の水素濃度を5×1019atoms/cm3以下とすることができる。

また、プラズマ処理が行われた酸素を含む絶縁膜、又は酸素と水素とを含む絶縁膜は、プラズマ処理する前の絶縁膜よりも0.5wt%フッ化水素酸に対するエッチング速度が遅くなることを特徴とする。例えば、上記条件を用いてプラズマ処理を行った場合、0.5wt%フッ化水素酸に対するエッチング速度を8nm/min以下とすることができる。

本発明の具体的な構成は、半導体膜領域を形成し、該半導体膜領域上に酸素及び水素を含む第1の絶縁膜を形成し、酸素を含む雰囲気下で、マイクロ波により励起されたプラズマを用いて第1の絶縁膜をプラズマ処理することにより膜中の水素含有量を低減し、第1の絶縁膜上に浮遊ゲート電極を形成し、該浮遊ゲート電極上に第2の絶縁膜を形成し、酸素を含む雰囲気下で、マイクロ波により励起されたプラズマを用いて第2の絶縁膜をプラズマ処理し、第2の絶縁膜上に制御ゲート電極を形成し、該制御ゲート電極をマスクとして不純物元素を添加し、半導体領域に一対の不純物領域を形成する。

また、本発明の他の構成は、半導体領域を形成し、該半導体領域上に酸素及び水素を含むゲート絶縁膜を形成し、酸素を含む雰囲気下で、マイクロ波により励起されたプラズマを用いてゲート絶縁膜をプラズマ処理することにより膜中の水素含有量を低減し、ゲート絶縁膜上にゲート電極を形成し、該ゲート電極をマスクとして不純物元素を添加し、半導体領域に一対の不純物領域を形成する。

また、本発明の他の構成は、酸素及び水素を含む絶縁膜を形成し、酸素を含む雰囲気下で、マイクロ波により励起されたプラズマを用いて絶縁膜をプラズマ処理することにより膜中の水素含有量を低減する。

上記構成において、酸素及び水素を含む絶縁膜はCVD法、スパッタ法又は熱酸化法のいずれかの方法を用いて形成することができる。また、酸素及び水素を含む絶縁膜としては、例えば酸化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化タンタル又は酸化ハフニウムを含む絶縁膜を形成することができる。

また、上記構成において、第1の絶縁膜、第2の絶縁膜、ゲート絶縁膜、又は酸素及び水素を含む絶縁膜のプラズマ処理は、酸素の他に希ガスを含む雰囲気下で行うことができる。

また、本発明の他の構成は、互いに離間して形成された一対の不純物領域の間にチャネル形成領域を有する半導体領域と、半導体領域の上方に第1の絶縁膜を介して設けられた浮遊ゲート電極と、浮遊ゲート電極の上方に第2の絶縁膜を介して設けられた制御ゲート電極と、を有する不揮発性半導体記憶装置である。第1の絶縁膜又は前記第2の絶縁膜は、二次イオン質量分析(SIMS)による水素濃度測定において、水素濃度が5×1019atoms/cm3以下である。

また、上記構成の不揮発性半導体記憶装置は、第1の絶縁膜又は第2の絶縁膜に希ガス(例えば、He、Ne、Ar、Kr、Xeの少なくとも1つを含む)が含まれる膜を用いることができる。

また、上記構成の不揮発性半導体記憶装置は、0.5wt%フッ化水素酸に対するエッチング速度が8nm/min以下の第1の絶縁膜又は第2の絶縁膜を用いることができる。

また、本発明の他の構成は、互いに離間して形成された一対の不純物領域の間にチャネル形成領域を有する半導体領域と、半導体領域の上方にゲート絶縁膜を介して設けられたゲート電極と、を有する半導体装置である。ゲート絶縁膜は、二次イオン質量分析(SIMS)による水素濃度測定において、水素濃度が5×1019atoms/cm3以下である。

また、上記構成の半導体装置は、ゲート絶縁膜に希ガス(例えば、He、Ne、Ar、Kr、Xeの少なくとも1つを含む)が含まれる膜を用いることができる。

また、上記構成の半導体装置は、0.5wt%フッ化水素酸に対するエッチング速度が8nm/min以下のゲート絶縁膜を用いることができる。

なお、本明細書において「半導体領域」とは、半導体基板に形成された領域や、基板上に形成された半導体膜を示すものとする。

本発明を用いることによって、緻密で高耐圧な絶縁膜を提供することができる。

本発明を用いることによって、膜中の水素含有量が少ない絶縁膜を提供することができる。

また、本発明を用いることによって、緻密で高耐圧なゲート絶縁膜を提供することができる。したがって、半導体基板に形成された半導体領域または基板上に形成された半導体領域(半導体膜)とゲート電極との間のリーク電流を低減することができる。

また、本発明を用いることによって、膜中の水素含有量が少なく、電子トラップの少ないゲート絶縁膜を提供することができる。したがって、半導体基板に形成された半導体領域または基板上に形成された半導体領域(半導体膜)とゲート絶縁膜との界面の特性を良好にすることができる。

また、本発明を用いることによって、緻密で高耐圧な膜を有する半導体装置又は不揮発性半導体記憶装置を提供することができる。さらに、電子トラップの少ない膜を有する半導体装置又は不揮発性半導体記憶装置を提供することができる。したがって、半導体装置又は不揮発性半導体記憶装置の歩留まり、信頼性を向上することができる。

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

(実施の形態1)

本発明は、絶縁膜に対して酸素を含む雰囲気下でプラズマ処理(プラズマ酸化)を行うことを特徴としている。ここでは、基板上に形成した絶縁膜に対してプラズマ酸化を行う例について、図1を用いて説明する。

基板10上に第1の絶縁膜12を形成する(図1(A)参照)。基板10は、ガラス基板、石英基板、サファイア基板、セラミック基板、金属基板等が挙げられる。また、これらの基板に絶縁膜、半導体膜、ゲート電極等の通常の半導体装置の構成要素が形成された基板も含む。また、Si基板等の半導体基板、もしくは半導体基板に通常の半導体装置の構成要素が形成された基板も含む。さらに、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)、アクリル等のプラスチック基板、もしくはプラスチック基板に通常の半導体装置の構成要素が形成された基板も含む。

第1の絶縁膜12は形成した後にプラズマ酸化が行われる膜である。第1の絶縁膜12は、少なくとも酸素を含む膜を形成する。具体的には、酸化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等を含む膜を形成すればよい。また、第1の絶縁膜12は、CVD法(例えば、プラズマCVD法、LPCVD法)、スパッタ法、又は熱酸化法等を用いて形成することができる。

一例として、プラズマCVD法を用いて第1の絶縁膜12を形成する方法について説明する。図3には、プラズマCVD法で被膜(ここでは第1の絶縁膜12に該当する)の形成を行うための装置の構成例を示す。図3に示すプラズマCVD装置は、被処理基板331(ここでは基板10に該当する)を配置するための支持台351と、ガスを導入する細孔が開いた電極板360、高周波電力導入部361、ガス導入部362、排気口353とを有する処理室を具備している。また、支持台351に温度制御部357を設けることによって、被処理基板331の温度を制御することも可能である。

被処理基板331に形成したい膜に応じた原料ガスを処理室内に導入することで、所望の膜を形成することができる。例えば、第1の絶縁膜12として酸化窒化珪素膜を形成する場合には、シラン(SiH4)ガスと亜酸化窒素(N2O)ガスを処理室内に導入すればよい。

次に、第1の絶縁膜12に対してプラズマ酸化を行い(図1(B)参照)、第2の絶縁膜14を形成する(図1(C)参照)。プラズマ酸化には、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上、且つ電子温度が1.5eV以下のプラズマを利用する。より詳しくは、電子密度が1×1011cm−3以上1×1013cm−3以下、且つ電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。また、プラズマ酸化を行う雰囲気は、少なくとも酸素を含み、その他に希ガス(He、Ne、Ar、Kr、Xeの少なくとも1つ)を含んでいてもよい。希ガスとしては、例えばArを用いることができる。また、希ガスとしてArとKrとを混合したものを用いることもできる。

なお、第1の絶縁膜12に対して希ガスを含む雰囲気下でプラズマ酸化を行う場合、第1の絶縁膜12にプラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも1つを含む)が含まれる場合がある。例えば、希ガスとしてArを用いた場合、プラズマ酸化して形成される第2の絶縁膜14中にArが含有される場合がある。

図2には、プラズマ酸化を行うための装置の構成例を示す。図2に示すプラズマ処理装置は、プラズマ酸化を行う被膜が形成された基板10(図1(A)に示す第1の絶縁膜12が形成された基板10に相当する)を配置するための支持台88と、ガスを導入するためのガス供給部84、ガスを排気するために真空ポンプに接続する排気口86、アンテナ80、誘電体板82、プラズマ発生用のマイクロ波を供給するマイクロ波供給部92を有している。また、支持台88に温度制御部90を設けることによって、基板10の温度を制御することも可能である。

以下、図2に示すプラズマ処理装置を用いて、第1の絶縁膜12にプラズマ酸化を行う具体例を述べる。まず、図2に示すプラズマ処理装置の処理室内を真空にする。そして、ガス供給部84から少なくとも酸素を含むプラズマ処理用ガスを導入する。基板10は室温、若しくは温度制御部90により100℃以上550℃以下の範囲で加熱する。基板10と誘電体板82との間隔(以下、電極間隔ともいう)は、20mm以上80mm以下(好ましくは20mm以上60mm以下)程度である。次に、マイクロ波供給部92からアンテナ80にマイクロ波(周波数2.45GHz)を供給する。そしてマイクロ波をアンテナ80から誘電体板82を通して処理室内に導入することによって、プラズマ94を生成する。マイクロ波の導入によりプラズマの励起を行うと、低電子温度(3eV以下、好ましくは1.5eV以下)で高電子密度(1×1011cm−3以上)のプラズマを生成することができる。なお、本明細書では、マイクロ波の導入により生成された低電子温度で高電子密度のプラズマを高密度プラズマという場合もある。この高密度プラズマで生成された酸素ラジカル(以下、(O*)と表記する場合もある)によって、第1の絶縁膜12を酸化する。このとき、プラズマ処理用ガスにアルゴンなどの希ガスを混合させると、希ガスの励起種により酸素ラジカルを効率良く生成することができる。この方法は、プラズマで励起した活性なラジカルを有効に使うことにより、500℃以下の低温で固相反応による酸化を行うことができる。

例えば、図2に示すプラズマ処理装置を用いて、酸素ガス(O2)とアルゴンガス(Ar)とを含む雰囲気下でプラズマ処理を行った場合について説明する。プラズマ処理装置に導入された酸素ガス(O2)とアルゴンガス(Ar)は、マイクロ波により酸素ガスとアルゴンガスとが混合された高密度プラズマを生成する。酸素ガスとアルゴンガスとが混合された高密度プラズマ中では、導入されたマイクロ波によりアルゴンガスが励起されてアルゴンラジカル(以下、(Ar*)と表記する場合もある)が生成され、当該アルゴンラジカル(Ar*)と酸素分子とが衝突することにより酸素ラジカル(O*)が生成される。そして、生成された酸素ラジカル(O*)と基板10上に形成された第1の絶縁膜12とが反応し、第2の絶縁膜14を形成する。

第2の絶縁膜14は、第1の絶縁膜12を酸素を含む雰囲気下でプラズマ処理することで得られる緻密で高耐圧な膜である。また、従来の熱酸化法と比較して低温プロセスで作製することができる。本発明を用いることで、熱に脆弱なガラス等の基板上にも、膜特性の良好な膜を形成することが可能になる。

例えば、第1の絶縁膜12を酸素を含む雰囲気下でプラズマ処理することで得られる第2の絶縁膜14は、0.5wt%フッ化水素酸に対するエッチング速度を8nm/min以下とすることができる。

また、第1の絶縁膜12をCVD法、スパッタ法、ウェット酸化などの熱酸化法により形成すると膜中に水素が含まれるが、プラズマ酸化を行うことで、膜中の水素含有量を低減させることができる。本発明を用いることで、絶縁膜中に電子トラップが生じる要因となりうる水素を低減させることができる。

例えば、第1の絶縁膜12を酸素を含む雰囲気下でプラズマ処理することで得られる第2の絶縁膜14は、二次イオン質量分析(SIMS)による水素濃度測定において、水素濃度を5×1019atoms/cm3以下とすることができる。

ここで、プラズマ酸化処理前後における絶縁膜について、推定される構成を説明する。

上述したように、CVD法、スパッタ法、ウェット酸化などの熱酸化法により酸素を含む膜を形成した場合、膜中に水素が取り込まれやすい。このとき、酸素を含む膜に取り込まれた水素の一部は、膜中の酸素とO−H結合を生成していると考えられる。

膜中にO−H結合等の水素を含有する膜に対してプラズマ酸化を行うと、酸素ラジカルによる水素の脱離、又は水素と酸素の置換反応が起き、その結果、膜中の水素含有量が低減すると考えられる。

このように、膜中の水素が酸素ラジカルにより脱離する、又は膜中の水素と酸素との置換反応が起き、膜中のO−H結合が低減することで、絶縁膜中のO−H結合に起因する電子トラップを低減することができる。

また、膜中の水素が酸素ラジカルにより脱離する、又は膜中の水素と酸素との置換反応が起き、膜中の水素が低減することで、緻密で高耐圧な膜が形成することができると考えられる。

以上のように、本発明を用いることで、緻密で高耐圧な絶縁膜を形成することができる。また、膜中の水素含有量を低減することができ、電子トラップの少ない絶縁膜を形成することができる。したがって、膜特性の優れた絶縁膜を提供することができる。

本実施例では、本発明を用いた半導体装置の作製方法の一例について説明する。ここでは、本発明を用いて薄膜トランジスタ(以下、TFTともいう)を構成するゲート絶縁膜を作製する場合について説明する。なお、以下に説明する本発明の構成において、同じ要素を指す符号は異なる図面で共通して用い、その場合における繰り返しの説明は省略する場合がある。

まず、基板400上に下地絶縁膜402を形成する(図4(A)参照)。基板400としては、ガラス基板、石英基板、サファイア基板、セラミック基板、金属基板などを用いることができる。また、ポリエチレンテレフタレート、ポリエチレンナフタレート、ポリエーテルサルフォン、アクリル等のプラスチック基板を用いることもできる。その他、少なくともプロセス中に発生する熱に耐えうる基板であれば用いることができる。本実施例では、基板400としてガラス基板を用いる。

下地絶縁膜402は、酸化珪素、窒化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の絶縁材料を用いて形成する。また、下地絶縁膜402は、単層構造でも多層構造でもよい。下地絶縁膜402の形成方法については特に限定されず、CVD法やスパッタ法等を用いて形成することができる。下地絶縁膜402を設けることで、基板からの不純物拡散を防止することができる。なお、基板400の凹凸や不純物拡散が問題とならないのであれば、下地絶縁膜402は形成しなくともよい。本実施例では、下地絶縁膜402として、プラズマCVD法を用いて、第1層目に窒化酸化珪素膜、第2層目に酸化窒化珪素膜を形成する。

次に、下地絶縁膜402上に島状の半導体膜404を形成する(図4(A)参照)。島状の半導体膜404は、珪素(Si)を主成分とする材料(例えば、Si、SixGe1−x等)を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させた後に選択的にエッチングすることによって形成することができる。非晶質半導体膜は、CVD法やスパッタ法等を用いて形成することができる。なお、非晶質半導体膜は結晶化しなくともよい。その場合、非晶質半導体膜を選択的にエッチングすることにより、非晶質半導体膜からなる島状の半導体膜404を形成する。

非晶質半導体膜を結晶化する場合は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれらの方法を組み合わせた方法等により行うことができる。

また、レーザ光の照射によって半導体膜の結晶化若しくは再結晶化を行う場合には、レーザ光の光源として半導体レーザ(LD)励起の連続発振(CW)レーザ(YVO4、第2高調波(波長532nm))を用いることができる。特に第2高調波に限定する必要はないが、第2高調波はエネルギー効率の点で、さらに高次の高調波より優れている。CWレーザを半導体膜に照射すると、連続的に半導体膜にエネルギーが与えられるため、一旦半導体膜を溶融状態にすると、溶融状態を継続させることができる。さらに、CWレーザを走査することによって半導体膜の固液界面を移動させ、この移動の方向に沿って一方向に長い結晶粒を形成することができる。また、固体レーザを用いるのは、気体レーザ等と比較して、出力の安定性が高く、安定した処理が見込まれるためである。なお、CWレーザに限らず、繰り返し周波数が10MHz以上のパルスレーザを用いることも可能である。繰り返し周波数が高いパルスレーザを用いると、半導体膜が溶融してから固化するまでの時間よりもレーザのパルス間隔が短ければ、常に半導体膜を溶融状態にとどめることができ、固液界面の移動により一方向に長い結晶粒で構成される半導体膜を形成することができる。その他のCWレーザ及び繰り返し周波数が10MHz以上のパルスレーザを使用することもできる。例えば、気体レーザとしては、Arレーザ、Krレーザ、CO2レーザ等がある。また、気体レーザとしてヘリウムカドミウムレーザ等の金属蒸気レーザが挙げられる。固体レーザとしては、YAGレーザ、YLFレーザ、YAlO3レーザ、GdVO4レーザ、KGWレーザ、KYWレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、Y2O3レーザ、YVO4レーザ等がある。また、固体レーザには、YAGレーザ、Y2O3レーザ、GdVO4レーザ、YVO4レーザなどのセラミックスレーザもある。また、レーザ発振器において、レーザ光をTEM00(シングル横モード)で発振して射出すると、被照射面において得られる線状のビームスポットのエネルギー均一性を上げることができるので好ましい。その他にも、パルス発振のエキシマレーザを用いても良い。

次に、半導体膜404上に第1の絶縁膜406を形成する(図4(B)参照)。第1の絶縁膜406としては少なくとも酸素を含む膜を形成する。例えば、酸化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)、酸化アルミニウム(AlxOy)、酸化タンタル(TaOx)等の材料を用いて形成する。また、酸化ハフニウム(HfOx)等の高誘電率材料を用いることもできる。第1の絶縁膜406は、CVD法又はスパッタ法等により形成され、例えば酸化珪素、酸化窒化珪素ならば、好ましくは膜厚1nm以上100nm以下、より好ましくは膜厚1nm以上40nm以下で形成する。

第1の絶縁膜406として酸化窒化珪素膜を形成する場合、シラン(SiH4)ガスと亜酸化窒素(N2O)ガスを原料ガスとしてプラズマCVD法により成膜することができる。このときの酸化窒化珪素膜の成膜条件の一例を以下に示す。

原料ガスのガス質量流量比はSiH4:N2O=1:800(sccm)とする。なお、本明細書で示すガス質量流量比とは、成膜室内に供給する原料ガスのSiH4ガスの質量流量(sccm)とN2Oガスの質量流量(sccm)の比である。また、周波数60MHzで高周波電力150Wとし、成膜温度(基板温度)400℃、処理室内圧力40Pa、電極間隔28mmとする。

次に、第1の絶縁膜406に対してプラズマ酸化を行い(図4(C)参照)、第2の絶縁膜408を形成する(図4(D)参照)。プラズマ酸化は、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上で、プラズマの電子温度が1.5eV以下のプラズマを利用する。具体的には、電子密度が1×1011cm−3以上1×1013cm−3以下で、プラズマの電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。また、第1の絶縁膜406に対するプラズマ酸化時間は、60sec以上が好ましい。

また、プラズマ酸化は、少なくとも酸素を含む雰囲気下で行う。例えば、酸素(O2)を含む雰囲気下、酸素(O2)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも1つを含む)を含む雰囲気下、若しくは酸素(O2)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも1つを含む)と水素(H2)を含む雰囲気下で行うのが好ましい。なお、水素(H2)を含む場合は、酸素、希ガスと比較してなるべく少ない方が好ましい。

本実施例では、酸素(O2)とアルゴン(Ar)とを含む雰囲気下でプラズマ酸化を行う。具体的には、上記図2に示すようなプラズマ処理装置の処理室内に酸素とアルゴンの混合ガスをプラズマ処理用ガスとして導入する。例えば、酸素を0.1以上100sccm以下、アルゴンを100以上5000sccm以下の範囲で導入すればよい。ここでは、酸素ガスを5sccm、アルゴンガスを900sccm導入する。基板温度は400℃とし、処理室内圧力は106.67Paとする。また、周波数2.45GHzのマイクロ波を用いてプラズマを励起する。

本発明で行うプラズマ酸化は、プラズマの電子密度が1×1011cm−3以上と高密度であり、被処理物である第1の絶縁膜406付近での電子温度が低いため、形成される第2の絶縁膜408がプラズマにより損傷することを防止することができる。また、プラズマの電子密度が1×1011cm−3以上と高密度であるため、被処理物(ここでは第1の絶縁膜406)をプラズマ酸化することによって形成される膜(ここでは第2の絶縁膜408)は、CVD法やスパッタ法等により形成された膜と比較して緻密で高耐圧な膜を形成することができる。また、プラズマの電子温度が1.5eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で被処理物の酸化処理を行うことができる。例えば、ガラス基板の歪点よりも100度以上低い温度でプラズマ酸化を行っても十分に酸化処理を行うことができる。

以上の条件でプラズマ酸化すると、緻密で高耐圧な膜を得ることができる。また、CVD法又はスパッタ法により形成される水素が含まれる絶縁膜をプラズマ酸化することで、水素含有量が低減された膜を得ることができる。

また、本実施例では半導体膜404上に形成された第1の絶縁膜406に対してプラズマ酸化を行っている。このとき、第1の絶縁膜406の膜厚によっては、第1の絶縁膜406と接する半導体膜404の表面も酸化される。例えば、第1の絶縁膜406の膜厚が40nm以下であれば、第1の絶縁膜406と接する半導体膜404の表面も酸化される場合もある。したがって、第1の絶縁膜406に対するプラズマ処理前後で、半導体膜404の膜厚が減少する場合もある。

これは、第1の絶縁膜406の膜厚が薄い場合は、酸素ラジカルが第1の絶縁膜406を十分に透過するためである。第1の絶縁膜406を透過した酸素ラジカルは、半導体膜404表面を酸化する。酸化された半導体膜404の表面は、第2の絶縁膜408の一部となる。その結果、半導体膜404の膜厚は減少し、第2の絶縁膜408の膜厚は第1の絶縁膜406の膜厚よりも増加する。図4(D)では、プラズマ処理後の半導体膜404の膜厚が減少する例を示し、プラズマ処理前の半導体膜404の外縁を点線で示している。

ここで、半導体膜及び当該半導体膜上に形成された絶縁膜のプラズマ酸化処理前後の膜厚を測定した結果を表1に示す。測定は、ガラス基板上に結晶質珪素膜と、酸化珪素膜を積層した試料を用い、分光エリプソメトリーにて行った。測定装置には堀場製作所社製「分光エリプソメータ UVISEL」を用いた。なお、酸化珪素膜はプラズマCVD法を用いて形成した後、プラズマ酸化を行った。プラズマ酸化の処理条件は以下に記す。

O2流量:5sccm、Ar流量:900sccm、H2流量:5sccm、処理室内圧力:106.67Pa、高周波電力3800W(2.45GHz)、基板温度:400℃。

上記表1に示すように、酸化珪素(SiO2)膜はプラズマ酸化前後で膜厚が5.27nm増加した。一方、結晶質珪素膜(Si)はプラズマ酸化前後で膜厚が2.45nm減少した。このことからも、プラズマ酸化することによって結晶質珪素膜の膜厚は減少し、酸化珪素膜の膜厚は増加することがわかった。また、結晶質珪素膜が減少するのは、高密度プラズマにより生じた酸素ラジカルが酸化珪素膜を透過して結晶質珪素膜の表面を酸化したためと考えられる。

また、第1の絶縁膜406に対して希ガスを含む雰囲気下でプラズマ酸化を行う場合、第1の絶縁膜406にプラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも1つを含む)が含まれる場合がある。例えば、希ガスとしてArを用いた場合、プラズマ酸化して形成される第2の絶縁膜408中にArが含有される場合がある。

以上の工程で形成された第2の絶縁膜408は、トランジスタのゲート絶縁膜として機能する。したがって、緻密で高耐圧なゲート絶縁膜を形成することができる。また、CVD法又はスパッタ法等により形成された膜よりも水素含有量が低減され、電子トラップの少ないゲート絶縁膜を形成することができる。

次に、第2の絶縁膜408上に導電膜を形成する(図5(A)参照)。ここでは、導電膜として導電膜410と導電膜412を積層形成する例を示す。もちろん、導電膜は単層又は3層以上の積層構造を形成することもできる。

導電膜410、412は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料を用いて形成することができる。また、これらの元素を窒化した金属窒化膜で形成することもできる。他にも、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。導電膜410、導電膜412は、これらの材料を用いてCVD法やスパッタ法等により形成することができる。

ここでは、窒化タンタルを用いて導電膜410を形成し、当該導電膜410上にタングステンを用いて導電膜412を形成する。また、他にも、導電膜410として、窒化タングステン、窒化モリブデン又は窒化チタンから選択された材料を用いて形成される単層膜又は積層膜を用い、導電膜412として、タンタル、モリブデン、チタンから選択された材料を用いて形成される単層膜又は積層膜を用いることができる。

次に、導電膜410と導電膜412を選択的にエッチングすることによって、半導体膜404の上方の一部に導電膜410、導電膜412を残存させ、ゲート電極418を構成する導電膜414と導電膜416を形成する(図5(B)参照)。なお、本実施例では、ゲート電極418において、導電膜414と導電膜416の端部が概略一致するように形成したが、本発明は特に限定されない。例えば、下方に形成される導電膜414の幅(キャリアがチャネル形成領域を流れる方向(ソース領域とドレイン領域を結ぶ方向)に概略平行な方向に対する幅)が、導電膜416の幅よりも大きくなるように形成してもよい。

次に、ゲート電極418をマスクとして不純物元素を添加し、一対の不純物領域422と、一対の不純物領域の間に位置するチャネル形成領域420を形成する(図5(C)参照)。ここで形成される不純物領域422は、トランジスタのソース領域またはドレイン領域として機能する。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、不純物元素として、リン(P)を添加する。

次に、第2の絶縁膜408及びゲート電極418(導電膜416、導電膜414)を覆うように絶縁膜を形成する(図5(D)参照)。ここでは、絶縁膜として第3の絶縁膜424、第4の絶縁膜426を積層形成する例を示す。もちろん、本発明は特に限定されず、絶縁膜は単層または3層以上の積層構造で形成することもできる。

第3の絶縁膜424、第4の絶縁膜426としては、酸化珪素、窒化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の酸素または窒素を有する絶縁膜、DLC(ダイヤモンドライクカーボン)等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる膜を形成することができる。なお、シロキサン材料とは、Si−O−Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。第3の絶縁膜424、第4の絶縁膜426は、これらの材料を用い、CVD法、スパッタ法、塗布法等を用いて形成することができる。なお、絶縁膜は有機材料またはシロキサン材料で形成することで、半導体膜やゲート電極等による段差を平坦化することができる。ただし、有機材料またはシロキサン材料を用いて形成された膜は水分を吸収、通過しやすい。そのため、有機材料またはシロキサン材料を用いて形成された膜に接して半導体膜、ゲート絶縁膜、ゲート電極等が形成されていると、完成したトランジスタの電気特性に悪影響を与える。したがって、水分に対するブロッキング効果が高い無機材料を用いた膜を半導体膜、ゲート絶縁膜、ゲート電極等に接して形成するのが好ましい。特に、窒化珪素、窒化酸化珪素等を有する膜は、水分に対するブロッキング効果が高いので好ましい。ここでは、第3の絶縁膜424として無機材料を用いた膜を形成し、当該第3の絶縁膜424上に第4の絶縁膜426として有機材料又はシロキサン材料を用いた膜を形成する。

次に、第3の絶縁膜424、第4の絶縁膜426に、半導体膜404に形成された不純物領域422に達する開口部を設ける。そして、半導体膜404に形成された不純物領域422と電気的に接続する導電膜428を形成する(図5(D)参照)。ここでは、単層膜の導電膜を形成する例を示すが、もちろん2層以上の積層構造で形成することもできる。なお、導電膜428は、トランジスタのソース配線又はドレイン配線として機能する。

導電膜428は、CVD法やスパッタ法等により、アルミニウム(Al)、タングステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジウム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料を用いて形成することができる。例えば、アルミニウムを主成分とする合金材料としては、アルミニウムを主成分としニッケルを含む材料、又はアルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料が挙げられる。導電膜428は、例えば、バリア膜とアルミニウムシリコン(Al−Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(Al−Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜428を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができる。

以上の工程で、本発明の半導体装置を作製することができる。なお、本実施例で示したトランジスタの構造は一例であり、各種公知の構造を適用することができるのは言うまでもない。例えば、半導体膜にLDD領域を形成してもよいし、ゲート電極の側面にサイドウォールを形成してもよい。また、マルチゲート構造(直列に接続された少なくとも2つ以上のチャネル形成領域を含んだ半導体膜と、それぞれのチャネル形成領域に電界を印加する少なくとも2つ以上のゲート電極とを有する構造)や、デュアルゲート構造(半導体膜の上下をゲート電極で挟む構造)を適用することもできる。

本発明を用いてゲート絶縁膜を形成すると、比較的膜厚が薄く、緻密で高耐圧なゲート絶縁膜を実現できる。また、高温の加熱処理をせずとも、膜特性の良好なゲート絶縁膜を実現できる。さらに、CVD法やスパッタ法で形成した絶縁膜に対してプラズマ酸化を行ってゲート絶縁膜を形成することで、半導体膜を十分に被覆することが可能になる。したがって、ゲート絶縁膜の耐圧不良(耐圧の低下ともいう)、又はゲート絶縁膜の被覆不良によるゲート電極と半導体膜のチャネル形成領域との短絡及びリーク電流などの不良等を防止することができ、信頼性の高い半導体装置を作製することができる。

また、緻密で高耐圧、且つ被覆性の良いゲート絶縁膜の薄膜化が可能となるため、半導体装置のさらなる微細化、高精密化を行うことが可能となり、半導体装置の高性能化を達成することができる。また、そのような膜の形状不良による不良が軽減されるので、作製工程においても歩留まりよく生産することができ、完成する半導体装置の信頼性も向上させることができる。

また、本発明を用いてゲート絶縁膜を形成すると、CVD法やスパッタ法で形成した絶縁膜と比較して水素含有量を低減することができ、電子トラップの少ないゲート絶縁膜を実現できる。したがって、トランジスタの閾値電圧の変動やサブスレッショルド係数の低下等の不良を防止することができ、信頼性の高い半導体装置を作製することができる。

なお、本実施例は、本明細書で示した他の実施の形態又は実施例と適宜組み合わせて行うことができる。

本実施例では、上記実施例1で示した構造において、ゲート電極の側面に絶縁膜(以下、サイドウォールともいう)を設ける場合について、図8を用いて説明する。なお、上記実施例と同じものを指す場合には同じ符号を用いて示し、説明は省略する。

まず、実施例1で説明した図5(B)まで同様に形成する(図8(A)参照)。

次に、ゲート電極418をマスクとして半導体膜404に不純物元素を添加して、一対の第1の不純物領域822を形成する。ここで形成される不純物領域822は、後に完成するトランジスタの低濃度不純物領域(LDD領域ともいう)として機能する。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる(図8(B)参照)。

次に、ゲート電極418の側面に接する第3の絶縁膜824を形成する(図8(C)参照)。ゲート電極418の側面に接する第3の絶縁膜824は、サイドウォールともよばれる。

第3の絶縁膜824は、第2の絶縁膜408とゲート電極418とを覆うように絶縁膜を形成した後に、垂直方向を主体とした異方性エッチングにより選択的にエッチングすることによって形成することができる。絶縁膜(後に形成される第3の絶縁膜824)は、CVD法やスパッタ法により、酸化珪素、酸化窒化珪素等の材料を用いた単層膜又は積層膜で形成することができる。

また、第3の絶縁膜824は、プラズマ酸化を行うことが好ましい。プラズマ酸化は、第2の絶縁膜408を形成する際に第1の絶縁膜406に対して行った処理と同様に行えばよく、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上で、プラズマの電子温度が1.5eV以下のプラズマを利用することができる。具体的には、電子密度が1×1011cm−3以上1×1013cm−3以下で、プラズマの電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。また、プラズマ酸化を行う処理時間は、60sec以上が好ましい。サイドウォールとして機能する絶縁膜に対してプラズマ酸化を行うことで、緻密で高耐圧な膜を得ることができる。

なお、CVD法又はスパッタ法等を用いてサイドウォールとして機能する絶縁膜を形成した場合は、膜中に水分が含まれやすい。しかし、本発明のように、サイドウォールとして機能する絶縁膜に対してプラズマ酸化を行うことで、膜中の水素含有量を低減することができる。

また、プラズマ酸化は、少なくとも酸素を含む雰囲気下で行う。例えば、酸素(O2)を含む雰囲気下、酸素(O2)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも1つを含む)を含む雰囲気下、若しくは酸素(O2)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも1つを含む)と水素(H2)を含む雰囲気下で行うのが好ましい。なお、水素を含む場合は、酸素、希ガスと比較して少ない方が好ましい。

次に、ゲート電極418及び第3の絶縁膜824をマスクとして半導体膜404に不純物元素を添加して、チャネル形成領域825、一対の第2の不純物領域826、一対の第3の不純物領域827を形成する(図8(D)参照)。ここで添加する不純物元素は、第1の不純物領域822を形成する際(図8(B)参照)に添加した不純物元素よりも高濃度に添加する。したがって、第3の不純物領域827は、第2の不純物領域826よりも高濃度に不純物元素が添加された領域となる。また、第3の不純物領域827はソース領域又はドレイン領域として機能し、第2の不純物領域826は低濃度不純物領域(LDD領域)として機能する。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。

次に、第2の絶縁膜408、第3の絶縁膜824、及びゲート電極418を覆うように、絶縁膜を形成する。ここでは、絶縁膜は第4の絶縁膜828、第5の絶縁膜830の積層構造とする。もちろん本発明は特に限定されず、絶縁膜を単層膜又は3層以上の積層膜としてもよい。そして、半導体膜404に形成された第3の不純物領域827と電気的に接続する導電膜832を形成する(図8(E)参照)。

第4の絶縁膜828、第5の絶縁膜830は、酸化珪素、窒化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の酸素または窒素を有する絶縁膜、DLC(ダイヤモンドライクカーボン)等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる膜を形成することができる。なお、シロキサン材料とは、Si−O−Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。第4の絶縁膜828、第5の絶縁膜830は、これらの材料を用い、CVD法、スパッタ法、塗布法等を用いて形成することができる。なお、絶縁膜は有機材料またはシロキサン材料で形成することで、半導体膜やゲート電極等による段差を平坦化することができる。ただし、有機材料またはシロキサン材料を用いて形成された膜は水分を吸収、通過しやすい。そのため、有機材料またはシロキサン材料を用いて形成された膜に接して半導体膜、ゲート絶縁膜、ゲート電極等が形成されていると、完成したトランジスタの電気特性に悪影響を与える場合がある。したがって、水分に対するブロッキング効果が高い無機材料を用いた膜を半導体膜、ゲート絶縁膜、ゲート電極等に接して形成するのが好ましい。特に、窒化珪素、窒化酸化珪素等を有する膜は、水分に対するブロッキング効果が高いので好ましい。ここでは、第4の絶縁膜828として無機材料を用いた膜を形成し、当該第4の絶縁膜828上に第5の絶縁膜830として有機材料又はシロキサン材料を用いた膜を形成する。

導電膜832は、CVD法やスパッタ法等により、アルミニウム(Al)、タングステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジウム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料を用いて形成することができる。例えば、アルミニウムを主成分とする合金材料としては、アルミニウムを主成分としニッケルを含む材料、又はアルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料が挙げられる。導電膜832は、例えば、バリア膜とアルミニウムシリコン(Al−Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(Al−Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜832を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができる。

以上の工程で、本発明の半導体装置を作製することができる。なお、本実施例で示したトランジスタの構造は一例であり、各種公知の構造を適用することができるのは言うまでもない。例えば、マルチゲート構造(直列に接続された少なくとも2つ以上のチャネル形成領域を含んだ半導体膜と、それぞれのチャネル形成領域に電界を印加する少なくとも2つ以上のゲート電極とを有する構造)や、デュアルゲート構造(半導体膜の上下をゲート電極で挟む構造)を適用することもできる。

本発明を用いることで、緻密で高耐圧な絶縁膜(サイドウォール)をゲート電極の側面に形成することができる。したがって、ゲート電極側面からサイドウォールを通じての局所的なリーク電流などの不良等を防止することができ、より信頼性の高い半導体装置を作製することができる。

また、本実施例では、基板上に設けられた島状の半導体膜を有する薄膜トランジスタについて説明したが、本発明はこれに限定されない。例えば、半導体基板にチャネル形成領域が設けられたトランジスタのサイドウォールについても適用することができる。

なお、本実施例は、本明細書で示した他の実施の形態又は実施例と適宜組み合わせて行うことができる。

本実施例では、不揮発性半導体記憶装置である不揮発性メモリ素子の作製方法の一例を、図9、図10を用いて説明する。ここでは、基板上に設けられた半導体膜を用いた不揮発性メモリ素子について説明する。

不揮発性メモリなどに代表される不揮発性半導体記憶装置は、MOSFET(Metal Oxide Semiconductor Field effect transistor)と類似の構造を有し、電荷を長期間蓄積することのできる領域がチャネル形成領域上に設けられているところに特徴がある。この電荷蓄積領域は絶縁膜上に形成され、周囲と絶縁分離されていることから浮遊ゲート電極とも呼ばれる。浮遊ゲート電極上には、さらに絶縁膜を介して制御ゲート電極を備えている。このような構造を所謂浮遊ゲート型の不揮発性半導体記憶装置という。

上記のような構造を有する不揮発性半導体記憶装置は、制御ゲート電極に印加する電圧により、浮遊ゲート電極に電荷を蓄積させ、また放出させる動作が行われる。すなわち浮遊ゲート電極に保持させる電荷の出し入れにより、データを記憶する仕組みになっている。具体的に、浮遊ゲート電極への電荷の注入や引き抜きは、チャネル形成領域が形成される半導体膜と、制御ゲート電極の間に高電圧を印加して行われている。このときチャネル形成領域上の絶縁膜には、ファウラー−ノルドハイム(Fowler−Nordheim)型(F−N型)トンネル電流(NAND型)や、熱電子(NOR型)が流れると言われている。このことよりチャネル形成領域上に設けられる絶縁膜は、トンネル絶縁膜とも呼ばれている。本実施例では、このような浮遊ゲート型の不揮発性メモリ素子の作製方法の一例について説明する。

まず、基板900上に下地絶縁膜902を介して島状の半導体膜904を形成する。そして、半導体膜904上に第1の絶縁膜906を形成する(図9(A)参照)。

基板900としては、ガラス基板、石英基板、サファイア基板、セラミック基板、金属基板などを用いることができる。また、ポリエチレンテレフタレート、ポリエチレンナフタレート、ポリエーテルサルフォン、アクリル等のプラスチック基板を用いることもできる。その他、少なくともプロセス中に発生する熱に耐えうる基板であれば用いることができる。本実施例では、基板900としてガラス基板を用いる。

下地絶縁膜902は、酸化珪素、窒化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の絶縁材料を用いて形成する。また、下地絶縁膜902は、単層膜でも多層膜でもよい。下地絶縁膜902の形成方法については特に限定されず、CVD法やスパッタ法等を用いて形成することができる。下地絶縁膜902を設けることで、基板からの不純物拡散を防止することができる。なお、基板900の凹凸や不純物拡散が問題とならないのであれば、下地絶縁膜902は形成しなくともよい。本実施例では、下地絶縁膜902として、プラズマCVD法を用いて窒化酸化珪素膜を形成する。

島状の半導体膜904は、珪素(Si)を主成分とする材料(例えば、Si、SixGe1−x等)を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させた後に選択的にエッチングすることによって形成することができる。非晶質半導体膜は、CVD法やスパッタ法等を用いて形成することができる。なお、非晶質半導体膜は結晶化しなくともよい。その場合、非晶質半導体膜を選択的にエッチングして、非晶質半導体膜からなる島状の半導体膜904を形成する。

非晶質半導体膜の結晶化は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法、またはこれら方法を組み合わせた方法等により行うことができる。

また、レーザ光の照射によって半導体膜の結晶化若しくは再結晶化を行う場合には、レーザ光の光源としてLD励起の連続発振(CW)レーザ(YVO4)、第2高調波(波長532nm))を用いることができる。特に第2高調波に限定する必要はないが、第2高調波はエネルギー効率の点で、さらに高次の高調波より優れている。CWレーザを半導体膜に照射すると、連続的に半導体膜にエネルギーが与えられるため、一旦半導体膜を溶融状態にすると、溶融状態を継続させることができる。さらに、CWレーザを走査することによって半導体膜の固液界面を移動させ、この移動の方向に沿って一方向に長い結晶粒を形成することができる。また、固体レーザを用いるのは、気体レーザ等と比較して、出力の安定性が高く、安定した処理が見込まれるためである。なお、CWレーザに限らず、繰り返し周波数が10MHz以上のパルスレーザを用いることも可能である。繰り返し周波数が高いパルスレーザを用いると、半導体膜が溶融してから固化するまでの時間よりもレーザのパルス間隔が短ければ、常に半導体膜を溶融状態にとどめることができ、固液界面の移動により一方向に長い結晶粒で構成される半導体膜を形成することができる。その他のCWレーザ及び繰り返し周波数が10MHz以上のパルスレーザを使用することもできる。例えば、気体レーザとしては、Arレーザ、Krレーザ、CO2レーザ等がある。また、気体レーザとしてヘリウムカドミウムレーザ等の金属蒸気レーザが挙げられる。固体レーザとして、YAGレーザ、YLFレーザ、YAlO3レーザ、GdVO4レーザ、KGWレーザ、KYWレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、Y2O3レーザ、YVO4レーザ等がある。また、固体レーザには、YAGレーザ、Y2O3レーザ、GdVO4レーザ、YVO4レーザなどのセラミックスレーザがある。また、レーザ発振器において、レーザ光をTEM00(シングル横モード)で発振して射出すると、被照射面において得られる線状のビームスポットのエネルギーの均一性を上げることができるので好ましい。その他にも、パルス発振のエキシマレーザを用いても良い。

第1の絶縁膜906は、CVD法やスパッタ法等を用いて、酸化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の絶縁材料を用いて形成することができる。また、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等の材料を用いて形成してもよい。第1の絶縁膜906は、好ましくは膜厚1nm以上20nm以下、より好ましくは膜厚1nm以上10nm以下で形成する。

次に、第1の絶縁膜906に対してプラズマ酸化を行い、第2の絶縁膜907を形成し、当該第2の絶縁膜907上に電荷蓄積膜908を形成する(図9(B)参照)。ここで、第2の絶縁膜907は後に完成する不揮発性半導体記憶装置のトンネル絶縁膜として機能し、電荷蓄積膜908は浮遊ゲート電極として機能する。

第1の絶縁膜906に対して行うプラズマ酸化は、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上であり、プラズマの電子温度が1.5eV以下のプラズマを利用する。より詳しくは、電子密度が1×1011cm−3以上1×1013cm−3以下で、プラズマの電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。また、第1の絶縁膜906に対するプラズマ酸化時間は、60sec以上が好ましい。

また、プラズマ酸化は、少なくとも酸素を含む雰囲気下(例えば、酸素雰囲気下、酸素(O2)若しくは亜酸化窒素(N2O)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、又は酸素若しくは亜酸化窒素と水素(H2)と希ガス雰囲気下)で行う。なお、水素を含む場合は、酸素若しくは亜酸化窒素、希ガスと比較して少ない方が好ましい。

希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。プラズマ酸化を希ガス雰囲気中で行った場合、プラズマ酸化することにより形成される第2の絶縁膜907は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる場合がある。例えば、プラズマ酸化に希ガスとしてArを用いた場合には、第2の絶縁膜907にArが含まれる場合がある。

本発明で行うプラズマ酸化は、プラズマの電子密度が1×1011cm−3以上と高密度であり、被処理物である第1の絶縁膜906付近でのプラズマの電子温度が低いため、形成される第2の絶縁膜907がプラズマにより損傷することを防止することができる。また、プラズマの電子密度が1×1011cm−3以上と高密度であるため、被処理物(ここでは第1の絶縁膜906)をプラズマ酸化することによって形成される膜(ここでは第2の絶縁膜907)は、CVD法やスパッタ法等により形成された膜と比較して緻密で高耐圧な膜を形成することができる。また、プラズマの電子温度が1.5eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で被処理物の酸化処理を行うことができる。例えば、ガラス基板の歪点よりも100度以上低い温度でプラズマ酸化を行っても十分に酸化処理を行うことができる。

また、CVD法又はスパッタ法等により形成される水素が含まれる絶縁膜をプラズマ酸化することで、水素含有量が低減された膜を得ることができる。

本実施例では、被処理物のプラズマ酸化の際に、酸素(O2)とアルゴン(Ar)との混合ガスを導入する。ここで用いる混合ガスは、例えば、酸素を0.1sccm以上100sccm以下、アルゴンを100sccm以上5000sccm以下の範囲で導入すればよい。例えば、酸素を5sccm、アルゴンを900sccmとして導入すればよい。

本実施例において、第1の絶縁膜906に対してプラズマ酸化することにより形成された第2の絶縁膜907は、後に完成する不揮発性半導体記憶装置において、トンネル絶縁膜として機能する。従って、第2の絶縁膜907の膜厚が薄いほどトンネル電流が流れやすく、メモリとして高速動作が可能となる。また、第2の絶縁膜907の膜厚が薄いほど、後に形成される浮遊ゲート電極に低電圧で電荷を蓄積させることが可能となるため、半導体装置の消費電力を低減することができる。そのため、第2の絶縁膜907は、膜厚を薄く形成することが好ましい。

一般的に、半導体膜上に絶縁膜を薄く形成する方法として熱酸化法があるが、基板900としてガラス基板等の融点が十分に高くない基板を用いる場合には、熱酸化法により半導体膜上に絶縁膜を形成することは非常に困難である。また、CVD法やスパッタ法により形成した絶縁膜は、膜の内部に欠陥を含んでいるため膜質が十分でない。さらに、CVD法やスパッタ法により膜厚の薄い絶縁膜を形成した場合には絶縁耐圧が低く、且つピンホール等の欠陥が生じやすい問題がある。そのうえ、CVD法やスパッタ法により絶縁膜を形成した場合には、特に半導体膜の端部の被覆が十分でなく、後に形成される浮遊ゲート電極を構成する導電膜等と半導体膜とが短絡する場合がある。したがって、CVD法やスパッタ法により形成した第1の絶縁膜906をそのままトンネル絶縁膜として用いると、不良が生じる恐れが大きい。

そこで、本実施例で示すように、第1の絶縁膜906をプラズマ酸化して第2の絶縁膜907を形成することで、CVD法やスパッタ法等により形成した絶縁膜より緻密で高耐圧な膜を形成することができる。また、第1の絶縁膜906形成時に半導体膜904の端部を十分に被覆できなかった場合でも、プラズマ酸化することで十分に被覆可能な第2の絶縁膜907を形成することができる。その結果、メモリとして高速動作や電荷保持特性を向上させることができる。

また、後に完成する不揮発性半導体記憶装置は、トンネル絶縁膜を介して電子を注入することによって情報を記憶する。このとき、トンネル絶縁膜に電子トラップの要因となる水素が存在すると、書き込み及び消去を繰り返すうちに電圧が変動してしまい、メモリが劣化する原因となる。したがって、電子トラップの要因となるトンネル絶縁膜中の水素含有量は少ない方が好ましい。本実施例で示すように、第1の絶縁膜906をプラズマ酸化して第2の絶縁膜907を形成することで、CVD法やスパッタ法等により形成した絶縁膜より膜中の水素含有量を低減することができる。その結果、メモリとしての性能を向上させることができる。

電荷蓄積膜908は、単層膜または2層以上の積層膜で形成することができる。具体的には、電荷蓄積膜908は、シリコン(Si)、ゲルマニウム(Ge)、タングステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料(前記元素の窒化物、酸化物等)を用いて形成することができる。例えば、前記元素の化合物として、窒化シリコン、窒化酸化シリコン、炭化シリコン、ゲルマニウムを10原子%未満の濃度で含むシリコンゲルマニウム、窒化タンタル、酸化タンタル、窒化タングステン、窒化チタン、酸化チタン、酸化スズ等を用いることができる。また、前記元素のシリサイド(例えば、タングステンシリサイド、チタンシリサイド、ニッケルシリサイド))を用いることができる。また、シリコンを用いる場合は、リンやボロンなどの不純物を添加してもよい。ここでは、電荷蓄積膜908として、ゲルマニウム元素を含む雰囲気中(例えば、GeH4)でプラズマCVD法を行うことにより、ゲルマニウムを主成分とする膜を膜厚1nm以上20nm以下、好ましくは5nm以上10nm以下で形成する。

次に、電荷蓄積膜908上に第3の絶縁膜910を形成する(図9(C)参照)。第3の絶縁膜910は、CVD法やスパッタ法等を用いて、酸化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の絶縁材料を用いて形成することができる。また、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等の材料を用いて形成してもよい。第3の絶縁膜910は、CVD法又はスパッタ法等により、好ましくは膜厚1nm以上100nm以下、より好ましくは膜厚20nm以上60nm以下で形成する。

次に、第3の絶縁膜910に対してプラズマ酸化を行うことにより第4の絶縁膜911を形成し、当該第4の絶縁膜911上に導電膜を形成する(図10(A)参照)。ここでは、導電膜として導電膜912、導電膜914を順に積層して形成した例を示している。もちろん、導電膜は、単層又は3層以上の積層構造で形成してもよい。また、プラズマ酸化は、上記第2の絶縁膜の形成方法で示した方法を用いればよい。

導電膜912、914としては、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成することもできる。他にも、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。

次に、積層して設けられた導電膜912、914を選択的にエッチングして除去することによって、半導体膜904の上方の一部に導電膜912、914を残存させ、ゲート電極924を構成する導電膜920、922を形成する(図10(B)参照)。また、本実施例では、ゲート電極924と重ならない第2の絶縁膜907の表面を露出させる。

具体的には、ゲート電極924の下方に形成された第4の絶縁膜911、電荷蓄積膜908のうち当該ゲート電極924と重ならない部分を選択的に除去し、ゲート電極924、第4の絶縁膜918、電荷蓄積膜916の端部が概略一致するように形成する。

この場合、ゲート電極924(導電膜920、922)の形成と同時に重ならない部分の絶縁膜等を除去してもよいし、ゲート電極924を形成後残存したレジスト又は当該ゲート電極924をマスクとして重ならない部分の絶縁膜等を除去してもよい。なお、電荷蓄積膜916は浮遊ゲート電極として機能する。第4の絶縁膜918はコントロール絶縁膜として機能する。また、ゲート電極924は制御ゲート電極として機能する。なお、本明細書で「コントロール絶縁膜」とは浮遊ゲート電極として機能する電極と、制御ゲート電極として機能する電極と、の間に設けられた絶縁膜のことを示す。

次に、ゲート電極924をマスクとして不純物元素を添加し、一対の不純物領域928と、一対の不純物領域928間に位置するチャネル形成領域926を形成する(図10(C)参照)。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。

以上の工程で、本発明の不揮発性半導体記憶装置である不揮発性メモリ素子を作製することができる。なお、本実施例で示した不揮発性メモリ素子の構造は一例であり、各種公知の構造を適用することができるのは言うまでもない。

本発明を用いることで、比較的膜厚が薄く、緻密で高耐圧なトンネル絶縁膜を実現することができる。また、高温の加熱処理をせずとも、膜特性の良好なトンネル絶縁膜を実現できる。さらに、CVD法やスパッタ法で形成した絶縁膜に対してプラズマ酸化を行ってトンネル絶縁膜を形成することで、半導体膜を十分に被覆することが可能になる。したがって、トンネル絶縁膜の耐圧不良、又はトンネル絶縁膜の被覆不良による浮遊ゲート電極と半導体膜のチャネル形成領域との短絡及びリーク電流などの不良等を防止することができ、メモリとして高速動作や電荷保持特性を向上させることができる。その結果、信頼性の高い不揮発性半導体記憶装置を作製することができる。

また、本発明を用いることで、電子トラップの少ないトンネル絶縁膜を実現することができる。不揮発性半導体記憶装置は、トンネル絶縁膜を介して電子を注入して情報を記憶させるため、電子トラップの少ないトンネル絶縁膜を提供することで信頼性の高い不揮発性半導体記憶装置を作製することができる。

また、本発明を用いることで、緻密で高耐圧なコントロール絶縁膜を実現することもできる。したがって、メモリとして電荷保持特性を向上させることができ、信頼性の高い不揮発性半導体記憶装置を作製することができる。

なお、本実施例は、本明細書で示した他の実施の形態又は実施例と適宜組み合わせて行うことができる。

本実施例では、上記実施例3と異なる不揮発性メモリ素子の作製方法の一例を、図6、図7を用いて説明する。ここでは、半導体基板を用いた不揮発性メモリ素子の作製方法の一例について説明する。

まず、半導体基板600に素子を分離した領域601(以下、素子分離領域601ともいう)を形成し、当該領域601の表面に第1の絶縁膜603を形成する(図6(A)参照)。半導体基板600に設けられた領域601は、絶縁膜602(フィールド酸化膜ともいう)によって分離されている。

半導体基板600は、半導体基板であれば特に限定されず用いることができる。例えば、n型又はp型の導電型を有する単結晶Si基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、ZnSe基板等)、貼り合わせ法またはSIMOX(Separation by Implanted Oxygen)法を用いて作製されたSOI(Silicon on Insulator)基板等を用いることができる。

素子分離領域601は、選択酸化法(LOCOS(Local Oxidation of Silicon)法)又はトレンチ分離法等を適宜用いて形成することができる。

本実施例では、半導体基板600としてn型の導電型を有する単結晶Si基板を用いる。なお、n型の導電型を有する半導体基板を用いる場合、p型を示す不純物元素を導入することにより、素子分離領域601にpウェルを形成してもよい。p型を示す不純物元素としては、ボロン(B)やガリウム(Ga)等を用いることができる。一方、半導体基板600としてp型の導電型を有する半導体基板を用いる場合、n型を示す不純物元素を導入することにより、素子分離領域にnウェルを形成してもよい。n型を示す不純物元素としては、リン(P)やヒ素(As)を用いることができる。

第1の絶縁膜603は、熱酸化法を用いて半導体基板600に設けられた領域601の表面を酸化させることにより酸化珪素膜で形成することができる。ここでは、第1の絶縁膜603を1nm以上20nm以下、好ましくは1nm以上10nm以下で形成する。

また、第1の絶縁膜603は、熱酸化法を用いて基板600に設けられた領域601の表面を酸化させることにより形成した酸化珪素膜に対して、さらにプラズマ酸化を行うことにより形成するのが好ましい。これは、ウェット酸化などの熱酸化法により絶縁膜を形成すると膜中に水素が含まれるためであり、プラズマ酸化を行うことで膜中の水素含有量を低減することができる。

プラズマ酸化は、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上であり、プラズマの電子温度が1.5eV以下のプラズマを利用する。より詳しくは、電子密度が1×1011cm−3以上1×1013cm−3以下で、プラズマの電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。また、絶縁膜に対するプラズマ酸化時間は、60sec以上が好ましい。

また、プラズマ酸化は、少なくとも酸素を含む雰囲気下(例えば、酸素雰囲気下、酸素(O2)若しくは亜酸化窒素(N2O)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、又は酸素若しくは亜酸化窒素と水素(H2)と希ガス雰囲気下)で行う。なお、水素を含む場合は、酸素若しくは亜酸化窒素、希ガスと比較して少ない方が好ましい。

希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。プラズマ酸化を希ガス雰囲気中で行った場合、プラズマ酸化することにより形成される第1の絶縁膜603は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる場合がある。例えば、プラズマ酸化に希ガスとしてArを用いた場合には、第1の絶縁膜603にArが含まれる場合がある。

本発明で行うプラズマ酸化は、プラズマの電子密度が1×1011cm−3以上と高密度であり、被処理物である絶縁膜付近での電子温度が低いため、形成される第1の絶縁膜603がプラズマにより損傷することを防止することができる。

なお、領域601上に形成される第1の絶縁膜603は、後に完成する不揮発性メモリ素子のトンネル絶縁膜として機能する。したがって、第1の絶縁膜603の膜厚が薄いほど、後に形成される浮遊ゲート電極に低電圧で電荷を蓄積させることが可能となるため、不揮発性半導体記憶装置の消費電力を低減することができる。そのため、第1の絶縁膜603は、膜厚を薄く形成することが好ましい。

次に、第1の絶縁膜603上に電荷蓄積膜604を形成し(図6(B)参照)、当該電荷蓄積膜604を選択的にエッチング除去してゲート電極606を形成する(図6(C)参照)。ゲート電極606は、後に完成する不揮発性半導体記憶装置の浮遊ゲート電極として機能する。

電荷蓄積膜604は、単層膜または2層以上の積層膜で形成することができる。具体的には、電荷蓄積膜604は、珪素(Si)、ゲルマニウム(Ge)、タングステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料(前記元素の窒化物、酸化物等)を用いて形成することができる。例えば、前記元素の化合物として、窒化珪素、窒化酸化珪素、炭化珪素、ゲルマニウムを10原子%未満の濃度で含むシリコンゲルマニウム、窒化タンタル、酸化タンタル、窒化タングステン、窒化チタン、酸化チタン、酸化スズ等等を用いることができる。また、前記元素のシリサイド(例えば、タングステンシリサイド、チタンシリサイド、ニッケルシリサイド))を用いることができる。また、珪素膜を用いる場合は、リンやボロンなどの不純物を添加してもよい。ここでは、電荷蓄積膜604として、ゲルマニウム元素を含む雰囲気中(例えば、GeH4)でプラズマCVD法を行うことにより、ゲルマニウムを主成分とする膜を1nm以上20nm以下、好ましくは5nm以上10nm以下で形成する。

次に、ゲート電極606上に第2の絶縁膜608を形成する(図6(D)参照)。

第2の絶縁膜608は、CVD法、スパッタ法、熱酸化法等を用いて形成した絶縁膜に対してプラズマ酸化を行うことにより形成される。絶縁膜は、好ましくは膜厚1nm以上100nm以下、より好ましくは膜厚20nm以上60nm以下で形成する。プラズマ酸化は、上記第1の絶縁膜603の形成方法で示した方法を用いればよい。なお、プラズマ酸化を希ガス雰囲気中で行った場合、プラズマ酸化することにより形成される第2の絶縁膜608は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる場合がある。

プラズマ酸化することによって形成される第2の絶縁膜608は、CVD法やスパッタ法等により形成された膜と比較して緻密で高耐圧な膜を形成することができる。

また、プラズマ酸化することによって形成される第2の絶縁膜608は、CVD法やスパッタ法、熱酸化法等により形成された膜と比較して膜中の水素含有量を低減することができる。

なお、ここで形成される第2の絶縁膜608は、後に完成する不揮発性メモリ素子のコントロール絶縁膜として機能する。

次に、第2の絶縁膜608上に導電膜を形成する。導電膜は単層膜又は2層以上の積層膜で形成することができる。ここでは、導電膜として導電膜612、導電膜614の積層膜を形成する(図7(A)参照)。

導電膜612、導電膜614は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成することもできる。他にも、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。

ここでは、窒化タンタルを用いて導電膜612を形成し、当該導電膜612上にタングステンを用いて導電膜614を形成する。また、他にも、導電膜612として、窒化タングステン、窒化モリブデン又は窒化チタンから選択された材料を用いて形成される単層膜又は積層膜を用い、導電膜614として、タンタル、モリブデン、チタンから選択された材料を用いて形成される単層膜又は積層膜を用いることができる。

次に、積層して設けられた導電膜612、614を選択的にエッチング除去して、領域601の上方の一部に導電膜612、導電膜614を残存させ、ゲート電極620を形成する(図7(B)参照)。ここで、ゲート電極620は、残存した導電膜616、導電膜618により構成されている。また、本実施例では、ゲート電極620において、下方に形成される導電膜616の幅(キャリアがチャネル形成領域を流れる方向(ソース領域とドレイン領域を結ぶ方向)に概略平行な方向に対する幅)が導電膜618の幅より大きくなるようにする。なお、ゲート電極620は、後に完成する不揮発性メモリ素子の制御ゲート電極として機能する。

なお、本発明は特に限定されず、導電膜616と導電膜618の端部が概略一致するように形成してもよい。また、導電膜616と導電膜618とゲート電極606の端部が概略一致するように形成してもよい。また、ゲート電極620の側面に接する絶縁膜(サイドウォール)を形成してもよい。

次に、ゲート電極620をマスクとして不純物元素を添加し、チャネル形成領域622、一対の第1の不純物領域624、一対の第2の不純物領域626を形成する(図7(C)参照)。ここで、第1の不純物領域624上には浮遊ゲート電極として機能するゲート電極606及び導電膜618が存在するため、第1の不純物領域624は第2の不純物領域626よりも低濃度に不純物が添加された領域となる。なお、第1の不純物領域624は、低濃度不純物領域(LDD領域)として機能し、第2の不純物領域626はソース領域又はドレイン領域として機能する。

不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。

以上の工程で、本発明の不揮発性メモリ素子を作製することができる。なお、本実施例で示した不揮発性メモリ素子の構造は一例であり、各種公知の構造を適用することができるのは言うまでもない。

本発明を用いることで、緻密で高耐圧なトンネル絶縁膜を実現することができる。したがって、トンネル絶縁膜の耐圧不良による浮遊ゲート電極と半導体膜のチャネル形成領域とのリーク電流などの不良等を防止することができ、メモリとして高速動作や電荷保持特性を向上させることができる。その結果、信頼性の高い不揮発性半導体記憶装置を作製することができる。

また、本発明を用いることで、電子トラップの少ないトンネル絶縁膜を実現することができる。不揮発性半導体記憶装置は、トンネル絶縁膜を介して電子を注入して情報を記憶させるため、電子トラップの少ないトンネル絶縁膜を提供することで信頼性の高い不揮発性半導体記憶装置を作製することができる。

また、本発明を用いることで、緻密で高耐圧なコントロール絶縁膜を実現することもできる。したがって、メモリとして電荷保持特性を向上させることができ、信頼性の高い不揮発性半導体記憶装置を作製することができる。

なお、本実施例は、本明細書で示した他の実施の形態又は実施例と適宜組み合わせて行うことができる。

上記実施例3又は実施例4に述べたような不揮発性メモリ素子を用いて、様々な態様の不揮発性半導体記憶装置を得ることができる。

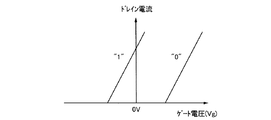

なお、上述したような所謂浮遊ゲート電極型の不揮発性メモリ素子は、制御ゲート電極に電圧を印加することにより、浮遊ゲート電極に電荷(キャリア)を蓄積させ、また放出させる動作が行われる。すなわち浮遊ゲート電極に保持させる電荷の出し入れにより、データを記憶する仕組みになっている。具体的に、浮遊ゲート電極への電荷の注入や引き抜きは、半導体膜のチャネル形成領域と制御ゲート電極との間、又は半導体基板のチャネル形成領域と制御ゲート電極との間に高電圧を印加して行われている。このときチャネル形成領域上の絶縁膜(トンネル絶縁膜)には、ファウラー−ノルドハイム(Fowler−Nordheim)型(F−N型)トンネル電流(NAND型)や、熱電子(NOR型)が流れると言われている。浮遊ゲート電極に電子を注入するには、上記熱電子を利用する方法と、F−N型トンネル電流を利用する方法がある。熱電子を利用する場合には、正の電圧を制御ゲート電極に印加して、ドレインに高電圧を印加して熱電子を発生させる。それにより、熱電子を浮遊ゲート電極に注入することができる。F−N型トンネル電流を利用する場合には、正の電圧を制御ゲート電極に印加して半導体膜のチャネル形成領域、又は半導体基板のチャネル形成領域からF−N型トンネル電流により浮遊ゲート電極に注入することができる。

図11に不揮発性メモリセルアレイの等価回路の一例を示す。1ビットの情報を記憶するメモリセルMCは、選択トランジスタSと不揮発性メモリ素子Mで構成されている。例えば、ビット線BL0及びワード線WL1で特定されるメモリセルMC01は、選択トランジスタS01と不揮発性メモリ素子M01で構成されている。選択トランジスタS01は、ビット線BL0と不揮発性メモリ素子M01の間に直列に挿入され、ゲートがワード線WL1に接続されている。不揮発性メモリ素子M01のゲートはワード線WL11に接続され、ソースまたはドレインの一方は選択トランジスタS01のソースまたはドレインに接続され、他方はソース線SL0に接続されている。不揮発性メモリ素子M01にデータを書き込むときは、ワード線WL1とビット線BL0をHレベル、ビット線BL1をLレベルとして、ワード線WL11に高電圧を印加すると、浮遊ゲート電極に電荷が蓄積される。データを消去する場合には、ワード線WL1とビット線BL0をHレベルとし、ワード線WL11に負の高電圧を印加すれば良い。

なお、図11において、選択トランジスタと不揮発性メモリ素子を、絶縁表面上に設けられた半導体膜を有し、当該半導体膜にチャネル形成領域が形成される構造とした場合、例えばメモリセルMC01において、選択トランジスタS01と不揮発性メモリ素子M01をそれぞれ、絶縁表面に島状に分離して形成された半導体膜で形成することにより、素子分離領域を特段設けなくても、他の選択トランジスタ若しくは不揮発性メモリ素子との干渉を防ぐことができる。また、メモリセルMC01内の選択トランジスタS01と不揮発性メモリ素子M01は共にnチャネル型なので、この両者を一つの島状に分離した半導体膜で形成することにより、この二つの素子を接続する配線を省略することができる。

図12は、ビット線に不揮発性メモリ素子を直接接続したNOR型の等価回路を示している。このメモリセルアレイは、ワード線WLとビット線BLが互いに交差して配設し、各交差部に不揮発性メモリ素子を配置している。NOR型は、個々の不揮発性メモリ素子のドレインをビット線BLに接続する。ソース線SLには不揮発性メモリ素子のソースが共通接続される。

なお、図12において、不揮発性メモリ素子を絶縁表面上に設けられた半導体膜を有し、当該半導体膜にチャネル形成領域が形成される構造とした場合、例えばメモリセルMC01において、不揮発性メモリ素子M01を絶縁表面に島状に分離して形成された半導体膜で形成することにより、素子分離領域を特段設けなくても、他の不揮発性メモリ素子との干渉を防ぐことができる。また、複数の不揮発性メモリ素子(例えば、図12に示すM01〜M23)を一つのブロックとして扱い、これらの不揮発性メモリ素子を一つの島状に分離した半導体膜で形成することにより、ブロック単位で消去動作を行うことができる。

NOR型の動作は、例えば、次の通りである。データ書き込みは、ソース線SLを0Vとし、データを書込むために選択されたワード線WLに高電圧を与え、ビット線BLにはデータ”0”と”1”に応じた電位を与える。例えば、”0”と”1”に対してそれぞれHレベル、Lレベルの電位をビット線BLに付与する。”0”データを書き込むべく、Hレベルが与えられた不揮発性メモリ素子ではドレイン近傍でホットエレクトロンが発生し、これが浮遊ゲート電極に注入される。”1”データの場合この様な電子注入は生じない。

”0”データが与えられたメモリセルでは、ドレインとソースとの間の強い横方向電界により、ドレインの近傍でホットエレクトロンが生成され、これが浮遊ゲート電極に注入される。これにより、浮遊ゲート電極に電子が注入されてしきい値電圧が高くなった状態が”0”である。”1”データの場合はホットエレクトロンが生成されず、浮遊ゲート電極に電子が注入されずしきい値電圧の低い状態、すなわち消去状態が保持される。

データを消去するときは、ソース線SLに10V程度の正の電圧を印加し、ビット線BLは浮遊状態としておく。そしてワード線に負の高電圧を印加して(制御ゲートに負の高電圧を印加して)、浮遊ゲート電極から電子を引き抜く。これにより、データ”1”の消去状態になる。

データ読み出しは、ソース線SLを0Vにすると共にビット線BLを0.8V程度とし、選択されたワード線WLに、データ”0”と”1”のしきい値の中間値に設定された読み出し電圧を与え、不揮発性メモリ素子の電流引き込みの有無を、ビット線BLに接続されるセンスアンプで判定することにより行う。

図13は、NAND型メモリセルアレイの等価回路を示す。ビット線BLには、複数の不揮発性メモリ素子を直列に接続したNANDセルNC1が接続されている。複数のNANDセルが集まってブロックBLKを構成している。図13で示すブロックBLK1のワード線は32本である(ワード線WL0〜WL31)。ブロックBLK1の同一行に位置する不揮発性メモリ素子には、この行に対応するワード線が共通接続されている。

図13において、選択トランジスタと不揮発性メモリ素子を、絶縁表面上に設けられた半導体膜を有し、当該半導体膜にチャネル形成領域が形成される構造とした場合、選択トランジスタS1、S2と不揮発性メモリ素子M0〜M31が直列に接続されているので、これらを一つのまとまりとして一つの半導体膜で形成しても良い。それにより不揮発性メモリ素子を繋ぐ配線を省略することが出来るので、集積化を図ることができる。また、隣接するNANDセルとの分離を容易に行うことができる。また、選択トランジスタS1、S2の半導体膜とNANDセルの半導体膜を分離して形成しても良い。不揮発性メモリ素子M0〜M31の浮遊ゲートから電荷を引き抜く消去動作を行うときに、そのNANDセルの単位で消去動作を行うことができる。また、一つのワード線に共通接続する不揮発性メモリ素子(例えばM30の行)を一つの半導体膜で形成しても良い。

書込み動作は、NANDセルNC1が消去状態、つまりNANDセルNC1の各不揮発性メモリ素子のしきい値を負電圧の状態にしてから実行される。書込みは、ソース線SL側のメモリ素子M0から順に行う。メモリ素子M0への書込みを例として説明すると概略以下のようになる。

図14(A)は、”0”書込みをする場合、選択ゲート線SG2に例えばVcc(電源電圧)を印加して選択トランジスタS2をオンにすると共にビット線BL0を0V(接地電圧)にする。選択ゲート線SG1は0Vとして、選択トランジスタS1はオフとする。次に、メモリセルM0のワード線WL0を高電圧Vpgm(20V程度)とし、これ以外のワード線を中間電圧Vpass(10V程度)にする。ビット線BLの電圧は0Vなので、選択されたメモリセルM0のチャネル形成領域の電位は0Vとなる。ワード線WL0とチャネル形成領域との間の電位差が大きいため、メモリセルM0の浮遊ゲート電極にはF−Nトンネル電流により電子が注入される。これにより、メモリセルM0のしきい値電圧が正の状態(”0”が書込まれた状態)となる。

一方”1”書込みをする場合は、図14(B)に示すように、ビット線BLに例えばVcc(電源電圧)が印加される。選択ゲート線SG2の電圧がVccであるので、選択トランジスタS2は遮断状態(カットオフ)となる。すなわち、メモリセルM0のチャネル形成領域はフローティング状態となる。次に、ワード線WL0に高電圧Vpgm(20V)、それ以外のワード線に中間電圧Vpass(10V)の電圧を印加すると、各ワード線とチャネル形成領域との容量カップリングにより、チャネル形成領域の電圧がVcc−Vthから上昇し、例えば8V程度となる。チャネル形成領域の電圧が高電圧に昇圧されるため、”0”の書込みの場合と異なり、ワード線WL0とチャネル形成領域の間の電位差が小さい。したがって、メモリセルM0の浮遊ゲート電極には、F−Nトンネル電流による電子注入が起こらない。よって、メモリセルM0のしきい値は、負の状態(”1”が書込まれた状態)に保たれる。

消去動作をする場合は、図15(A)に示すように、選択されたブロック内の全てのワード線に負の高電圧(Vers)を印加する。ビット線BL、ソース線SLはフローティング状態とする。これにより、ブロックの全てのメモリセルにおいて浮遊ゲート電極中の電子がトンネル電流により半導体膜、又は半導体基板に放出される。この結果、これらのメモリセルのしきい値電圧が負方向にシフトする。

図15(B)に示す読み出し動作では、読出しの選択がされたメモリセルM0のワード線WL0の電圧Vr(例えば0V)とし、非選択のメモリセルのワード線WL1〜31及び選択ゲート線SG1、SG2を電源電圧より少し高い読出し用中間電圧Vreadとする。すなわち、図16に示すように、選択メモリ素子以外のメモリ素子はトランスファートランジスタとして働く。これにより、読出しの選択がされたメモリセルM0に電流が流れるか否かを検出する。つまり、メモリセルM0に記憶されたデータが”0”の場合、メモリセルM0はオフなので、ビット線BLは放電しない。一方、”1”の場合、メモリセルM0はオンするので、ビット線BLが放電する。

図17は、不揮発性半導体記憶装置の回路ブロック図の一例を示している。不揮発性半導体記憶装置は、メモリセルアレイ52と周辺回路54が同一の基板上に形成されている。メモリセルアレイ52は、図11、図12、図13で示すような構成を有している。周辺回路54の構成は以下の通りである。

ワード線選択のためにロウデコーダ62と、ビット線選択のためにカラムデコーダ64が、メモリセルアレイ52の周囲に設けられている。アドレスは、アドレスバッファ56を介してコントロール回路58に送られ、内部ロウアドレス信号及び内部カラムアドレス信号がそれぞれロウデコーダ62及びカラムデコーダ64に転送される。

データ書き込み及び消去には、電源電位を昇圧した電位が用いられる。このため、コントロール回路58により動作モードに応じて制御される昇圧回路60が設けられている。昇圧回路60の出力はロウデコーダ62やカラムデコーダ64を介して、ワード線WLやビット線BLに供給される。センスアンプ66はカラムデコーダ64から出力されたデータが入力される。センスアンプ66により読み出されたデータは、データバッファ68に保持され、コントロール回路58からの制御により、データがランダムアクセスされ、データ入出力バッファ70を介して出力されるようになっている。書き込みデータは、データ入出力バッファ70を介してデータバッファ68に一旦保持され、コントロール回路58の制御によりカラムデコーダ64に転送される。

このような不揮発性半導体記憶装置では、データの書き込み及び消去がトンネル絶縁膜を介して行われる。したがって、不揮発性半導体記憶装置において、トンネル絶縁膜の膜特性は非常に重要である。

そこで、本発明を用いると、緻密で高耐圧なトンネル絶縁膜を実現できる。また、トンネル絶縁膜により半導体膜を十分に被覆することが可能になる。したがって、トンネル絶縁膜の耐圧不良、又はトンネル絶縁膜の被覆不良等を防止できるため、信頼性の高い不揮発性半導体記憶装置を提供することができる。

また、本発明を用いると、電子トラップの少ないトンネル絶縁膜を実現できる。したがって、信頼性の高い不揮発性半導体記憶装置を提供することができる。

本実施例では、不揮発性半導体記憶装置の一例について説明する。ここでは、不揮発性半導体記憶装置において、メモリ部を構成する不揮発性メモリ素子と、当該メモリ部と同一の基板上に設けられメモリ部の制御等を行うロジック部を構成するトランジスタ等の素子とを同時に形成する場合を示す。

まず、不揮発性半導体記憶装置におけるメモリ部の模式図を図11に示す。

本実施例で示すメモリ部は、選択トランジスタSと不揮発性メモリ素子Mを有するメモリセルが複数設けられている。図11では、選択トランジスタS01と不揮発性メモリ素子M01により一つのメモリセルMC01が形成されている。また、同様に、選択トランジスタS02と不揮発性メモリ素子M02、選択トランジスタS03と不揮発性メモリ素子M03、選択トランジスタS11と不揮発性メモリ素子M11、選択トランジスタS12と不揮発性メモリ素子M12、選択トランジスタS13と不揮発性メモリ素子M13とによりメモリセルが形成されている。

選択トランジスタS01のゲート電極はワード線WL1に接続され、ソース又はドレインの一方はビット線BL0に接続され、他方は不揮発性メモリ素子M01のソース又はドレインに接続されている。また、不揮発性メモリ素子M01のゲート電極はワード線WL11に接続され、ソース又はドレインの一方は選択トランジスタS01のソース又はドレインに接続され、他方はソース線SLに接続されている。

なお、メモリ部に設けられる選択トランジスタは、ロジック部に設けられるトランジスタと比較して駆動電圧が高いため、メモリ部に設けるトランジスタとロジック部に設けるトランジスタのゲート絶縁膜等を異なる厚さで形成することが好ましい。例えば、駆動電圧が小さくしきい値電圧のばらつきを小さくしたい場合にはゲート絶縁膜が薄いトランジスタを設けることが好ましく、駆動電圧が大きくゲート絶縁膜の耐圧性が求められる場合にはゲート絶縁膜が厚いトランジスタを設けることが好ましい。

従って、本実施例では、駆動電圧が小さくしきい値電圧のばらつきを小さくしたいロジック部のトランジスタに対しては膜厚が小さい絶縁膜を形成し、駆動電圧が大きくゲート絶縁膜の耐圧性が求められるメモリ部のトランジスタに対しては膜厚が大きい絶縁膜を形成する場合に関して以下に図面を参照して説明する。なお、図18〜図21において、A−B間及びC−D間はロジック部に設けられるトランジスタを示し、E−F間はメモリ部に設けられる不揮発性メモリ素子を示し、G−H間はメモリ部に設けられるトランジスタを示している。また、本実施例では、A−B間に設けられるトランジスタをpチャネル型、C−D間、G−H間に設けるトランジスタをnチャネル型、E−F間に設けられる不揮発性メモリ素子のキャリアの移動を電子で行う場合に関して説明するが、本発明の不揮発性半導体記憶装置はこれに限られるものでない。

まず、基板100上に下地絶縁膜102を介して島状の半導体膜104、106、108、110を形成し、当該島状の半導体膜104、106、108、110を覆うように第1の絶縁膜112、114、116、118をそれぞれ形成する。そして、第1の絶縁膜112、114、116、118を覆うように電荷蓄積膜120を形成する(図18(A)参照)。島状の半導体膜104、106、108、110は、基板100上にあらかじめ形成された下地絶縁膜102上にスパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えばSixGe1−x等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させた後に選択的にエッチングすることにより設けることができる。また、非晶質半導体膜を結晶化せずに選択的にエッチングし、非晶質半導体膜からなる島状の半導体膜104、106、108、110を形成してもよい。

非晶質半導体膜の結晶化は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれら方法を組み合わせた方法等により行うことができる。

また、レーザ光の照射によって半導体膜の結晶化若しくは再結晶化を行う場合には、レーザ光の光源としてLD励起の連続発振(CW)レーザ(YVO4、第2高調波(波長532nm))を用いることができる。特に第2高調波に限定する必要はないが、第2高調波はエネルギー効率の点で、さらに高次の高調波より優れている。CWレーザを半導体膜に照射すると、連続的に半導体膜にエネルギーが与えられるため、一旦半導体膜を溶融状態にすると、溶融状態を継続させることができる。さらに、CWレーザを走査することによって半導体膜の固液界面を移動させ、この移動の方向に沿って一方向に長い結晶粒を形成することができる。また、固体レーザを用いるのは、気体レーザ等と比較して、出力の安定性が高く、安定した処理が見込まれるためである。なお、CWレーザに限らず、繰り返し周波数が10MHz以上のパルスレーザを用いることも可能である。繰り返し周波数が高いパルスレーザを用いると、半導体膜が溶融してから固化するまでの時間よりもレーザのパルス間隔が短ければ、常に半導体膜を溶融状態にとどめることができ、固液界面の移動により一方向に長い結晶粒で構成される半導体膜を形成することができる。その他のCWレーザ及び繰り返し周波数が10MHz以上のパルスレーザを使用することもできる。例えば、気体レーザとしては、Arレーザ、Krレーザ、CO2レーザ等がある。また、気体レーザとしてヘリウムカドミウムレーザ等の金属蒸気レーザが挙げられる。固体レーザとしては、YAGレーザ、YLFレーザ、YAlO3レーザ、GdVO4レーザ、KGWレーザ、KYWレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、Y2O3レーザ、YVO4レーザ等がある。また、固体レーザにはYAGレーザ、Y2O3レーザ、GdVO4レーザ、YVO4レーザなどのセラミックスレーザもある。また、レーザ発振器において、レーザ光をTEM00(シングル横モード)で発振して射出すると、被照射面において得られる線状のビームスポットのエネルギー均一性を上げることができるので好ましい。その他にも、パルス発振のエキシマレーザを用いても良い。

基板100は、ガラス基板、石英基板、セラミック基板、金属基板(例えばステンレス基板など)等から選択されるものである。他にもプラスチック基板として、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)、アクリルなどの基板を選択することもできる。

下地絶縁膜102は、CVD法やスパッタ法等を用いて、酸化珪素、窒化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の絶縁材料を用いて形成する。例えば、下地絶縁膜102を2層の積層構造とする場合、第1層目の絶縁膜として窒化酸化珪素膜を形成し、第2層目の絶縁膜として酸化窒化珪素膜を形成するとよい。また、第1層目の絶縁膜として窒化珪素膜を形成し、第2層目の絶縁膜として酸化珪素膜を形成してもよい。このように、ブロッキング層として機能する下地絶縁膜102を形成することによって、基板100からNaなどのアルカリ金属やアルカリ土類金属が、基板上に形成する素子に悪影響を与えることを防ぐことができる。なお、基板100として石英を用いるような場合には下地絶縁膜102を省略してもよい。

第1の絶縁膜112、114、116、118は、CVD法やスパッタ法等を用いて絶縁膜を形成し、当該絶縁膜に対してプラズマ酸化を行うことで形成することが好ましい。例えば、CVD法又はスパッタ法を用いて、酸化珪素、酸化窒化珪素、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等を含む絶縁膜を形成し、当該絶縁膜に対してプラズマ酸化を行うことで第1の絶縁膜112、114、116、118を形成する。絶縁膜は、好ましくは膜厚1nm以上20nm以下、より好ましくは膜厚1nm以上10nm以下で形成する。

プラズマ酸化は、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上であり、プラズマの電子温度が1.5eV以下のプラズマを利用する。より詳しくは、電子密度が1×1011cm−3以上1×1013cm−3以下で、プラズマの電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。また、絶縁膜に対するプラズマ酸化時間は、60sec以上が好ましい。

また、プラズマ酸化は、少なくとも酸素を含む雰囲気下(例えば、酸素雰囲気下、酸素(O2)若しくは亜酸化窒素(N2O)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、又は酸素若しくは亜酸化窒素と水素(H2)と希ガス雰囲気下)で行う。なお、水素を含む場合は、酸素若しくは亜酸化窒素、希ガスと比較して少ない方が好ましい。

希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。プラズマ酸化を希ガス雰囲気中で行った場合、プラズマ酸化することにより形成される第1の絶縁膜112、114、116、118は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる場合がある。例えば、プラズマ酸化に希ガスとしてArを用いた場合には、第1の絶縁膜112、114、116、118にArが含まれる場合がある。

本発明で行うプラズマ酸化は、プラズマの電子密度が1×1011cm−3以上と高密度であり、被処理物である絶縁膜付近でのプラズマの電子温度が低いため、形成される第1の絶縁膜112、114、116、118がプラズマにより損傷することを防止することができる。また、プラズマの電子密度が1×1011cm−3以上と高密度であるため、被処理物をプラズマ酸化することによって形成される膜(ここでは第1の絶縁膜112、114、116、118)は、CVD法やスパッタ法等により形成された膜と比較して緻密で高耐圧な膜を形成することができる。また、プラズマの電子温度が1.5eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で被処理物の酸化処理を行うことができる。例えば、ガラス基板の歪点よりも100度以上低い温度でプラズマ酸化を行っても十分に酸化処理を行うことができる。

また、CVD法又はスパッタ法等により形成される水素が含まれる絶縁膜をプラズマ酸化することで、水素含有量が低減された膜を得ることができる。

本実施例では、被処理物のプラズマ酸化を行う場合、酸素(O2)、とアルゴン(Ar)との混合ガスを導入する。ここで用いる混合ガスは、酸素を0.1sccm以上100sccm以下、アルゴンを100sccm以上5000sccm以下として導入すればよい。例えば、酸素を5sccm、水素を5sccm、アルゴンを900sccmとして導入すればよい。

本実施例において、メモリ部に設けられた半導体膜108上に形成される第1の絶縁膜116は、後に完成する不揮発性メモリ素子において、トンネル絶縁膜として機能する。従って、第1の絶縁膜116の膜厚が薄いほど、トンネル電流が流れやすく、メモリとして高速動作が可能となる。また、第1の絶縁膜116の膜厚が薄いほど、後に形成される浮遊ゲート電極に低電圧で電荷を蓄積させることが可能となるため、不揮発性半導体記憶装置の消費電力を低減することができる。そのため、第1の絶縁膜112、114、116、118は、膜厚を薄く形成することが好ましい。

一般的に、半導体膜上に絶縁膜を薄く形成する方法として熱酸化法があるが、基板100としてガラス基板等の融点が十分に高くない基板を用いる場合には、熱酸化法により第1の絶縁膜112、114、116、118を形成することは非常に困難である。また、CVD法やスパッタ法により形成した絶縁膜は、膜の内部に欠陥を含んでいるため膜質が十分でなく、膜厚を薄く形成した場合にはピンホール等の欠陥が生じる問題がある。また、CVD法やスパッタ法により絶縁膜を形成した場合には、特に半導体膜の端部の被覆が十分でなく、後に第1の絶縁膜116上に形成される電荷蓄積膜等と半導体膜とが短絡する場合がある。従って、本実施例で示すように、プラズマ酸化を行った第1の絶縁膜112、114、116、118を形成することによって、CVD法やスパッタ法等により形成した絶縁膜より緻密で高耐圧な絶縁膜を形成することができる。また、半導体膜104、106、108、110の端部を第1の絶縁膜112、114、116、118で十分に被覆することができる。その結果、メモリとして高速動作や電荷保持特性を向上させることができる。

また、後に完成する不揮発性半導体記憶装置は、メモリ部に設けられた半導体膜108上に形成され、トンネル絶縁膜として機能する第1の絶縁膜116を介して電子を注入することによって情報を記憶する。このとき、トンネル絶縁膜に電子トラップの要因となる水素が存在すると、書き込み及び消去を繰り返すうちに電圧が変動してしまい、メモリが劣化する原因となる。したがって、電子トラップの要因となるトンネル絶縁膜中の水素含有量は少ない方が好ましい。本実施例で示すように、プラズマ酸化を行って第1の絶縁膜116を形成することで、CVD法やスパッタ法等により形成した絶縁膜より膜中の水素含有量を低減することができる。その結果、メモリとしての性能を向上させることができる。

電荷蓄積膜120は、単層膜または2層以上の積層膜で形成することができる。具体的には、電荷蓄積膜120は、シリコン(Si)、ゲルマニウム(Ge)、タングステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料(例えば、窒化物、酸化物等)を用いて形成することができる。前記元素の化合物としては、窒化シリコン、窒化酸化シリコン、炭化シリコン、ゲルマニウムを10原子%未満の濃度で含むシリコンゲルマニウム、窒化タンタル、酸化タンタル、窒化タングステン、窒化チタン、酸化チタン、酸化スズ等を用いることができる。また、前記元素のシリサイド(例えば、タングステンシリサイド、チタンシリサイド、ニッケルシリサイド))を用いることができる。また、シリコンを用いる場合は、リンやボロンなどの不純物を添加してもよい。ここでは、電荷蓄積膜120として、ゲルマニウム元素を含む雰囲気中(例えば、GeH4)でプラズマCVD法を行うことにより、ゲルマニウムを主成分とする膜を1nm以上20nm以下、好ましくは5nm以上10nm以下で形成する。メモリ部に設けられた半導体膜108上に形成される電荷蓄積膜120は、後に完成する不揮発性半導体記憶装置において、浮遊ゲート電極として機能する。例えば、半導体膜としてSiを主成分とする材料を用いて形成し、当該半導体膜上にトンネル絶縁膜として機能する第1の絶縁膜を介して浮遊ゲート電極として機能するSiよりエネルギーギャップの小さいゲルマニウムを含む導電膜を設けた場合は、半導体膜の電荷に対する絶縁膜により形成される第1の障壁に対して浮遊ゲート電極の電荷に対する絶縁膜により形成される第2の障壁がエネルギー的に高くなる。その結果、半導体膜から浮遊ゲート電極へ電荷を注入しやすくすることができ、浮遊ゲート電極から電荷が消失することを防ぐことができる。つまり、メモリとして動作する場合に、低電圧で高効率な書き込みをすることが出来、且つ電荷保持特性を向上させることができる。

次に、半導体膜104、106、110上に形成された、第1の絶縁膜112、114、118と電荷蓄積膜120を選択的に除去し、半導体膜108上に形成された、第1の絶縁膜116と電荷蓄積膜120を残存させる。ここでは、メモリ部に設けられた半導体膜108、第1の絶縁膜116、電荷蓄積膜120を選択的にレジストで覆い、半導体膜104、106、110上に形成された、第1の絶縁膜112、114、118と電荷蓄積膜120をエッチングすることによって選択的に除去する(図18(B)参照)。

次に、半導体膜104、106、110と、半導体膜108の上方に形成された電荷蓄積膜120の一部を選択的に覆うようにレジスト122を形成し、当該レジスト122に覆われていない電荷蓄積膜120をエッチングして選択的に除去することによって、電荷蓄積膜120の一部を残存させ、電荷蓄積膜121を形成する(図18(C)参照)。

次に、半導体膜110の特定の領域に不純物領域を形成する。ここでは、レジスト122を除去後、半導体膜104、106、108と、半導体膜110の一部を選択的に覆うようにレジスト124を形成し、当該レジスト124に覆われていない半導体膜110に不純物元素を導入することによって、不純物領域126を形成する(図19(A)参照)。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、不純物元素として、リン(P)を半導体膜110に導入する。

次に、半導体膜104、106、110と、半導体膜108の上方に形成された第1の絶縁膜116と電荷蓄積膜121を覆うように第2の絶縁膜128を形成する(図19(B)参照)。

第2の絶縁膜128は、CVD法やスパッタ法等を用いて絶縁膜を形成し、当該絶縁膜に対してプラズマ酸化を行うことで形成することが好ましい。例えば、CVD法又はスパッタ法を用いて、酸化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等を含む絶縁膜を形成し、当該絶縁膜に対してプラズマ酸化を行うことで第2の絶縁膜128を形成する。絶縁膜は、好ましくは膜厚1nm以上100nm以下、より好ましくは膜厚20nm以上60nm以下で形成する。

プラズマ酸化は、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上であり、プラズマの電子温度が1.5eV以下のプラズマを利用する。より詳しくは、電子密度が1×1011cm−3以上1×1013cm−3以下で、プラズマの電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。また、絶縁膜に対するプラズマ酸化時間は、60sec以上が好ましい。

また、プラズマ酸化は、少なくとも酸素を含む雰囲気下(例えば、酸素雰囲気下、酸素(O2)若しくは亜酸化窒素(N2O)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、又は酸素若しくは亜酸化窒素と水素(H2)と希ガス雰囲気下)で行う。なお、水素を含む場合は、酸素若しくは亜酸化窒素、希ガスと比較して少ない方が好ましい。

希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。プラズマ酸化を希ガス雰囲気中で行った場合、プラズマ酸化することにより形成される第2の絶縁膜128は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる場合がある。例えば、プラズマ酸化に希ガスとしてArを用いた場合には、第2の絶縁膜128にArが含まれる場合がある。

本発明で行うプラズマ酸化は、プラズマの電子密度が1×1011cm−3以上と高密度であり、被処理物である絶縁膜付近でのプラズマの電子温度が低いため、形成される第2の絶縁膜128がプラズマにより損傷することを防止することができる。また、プラズマの電子密度が1×1011cm−3以上と高密度であるため、被処理物をプラズマ酸化することによって形成される膜(ここでは第2の絶縁膜128)は、CVD法やスパッタ法等により形成された膜と比較して緻密で高耐圧な膜を形成することができる。また、プラズマの電子温度が1.5eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で被処理物の酸化処理を行うことができる。例えば、ガラス基板の歪点よりも100度以上低い温度でプラズマ酸化を行っても十分に酸化処理を行うことができる。

また、CVD法又はスパッタ法等により形成される水素が含まれる絶縁膜をプラズマ酸化することで、水素含有量が低減された膜を得ることができる。

本実施例では、被処理物のプラズマ酸化を行う場合、酸素(O2)、とアルゴン(Ar)との混合ガスを導入する。ここで用いる混合ガスは、酸素を0.1sccm以上100sccm以下、アルゴンを100sccm以上5000sccm以下として導入すればよい。例えば、酸素を5sccm、水素を5sccm、アルゴンを900sccmとして導入すればよい。

本実施例において、メモリ部に設けられた半導体膜108の上方に形成される第2の絶縁膜128は、後に完成する不揮発性メモリ素子において、コントロール絶縁膜として機能する。また、半導体膜110の上方に形成された第2の絶縁膜128は、後に完成するトランジスタにおいてゲート絶縁膜として機能する。従って、第2の絶縁膜128が緻密で高耐圧な膜であれば、後に完成する不揮発性メモリ素子の電荷保持特性を向上させることができる。また、後に完成するトランジスタのリーク電流などの不良を防止することができる。

また、第2の絶縁膜128は、酸化珪素、窒化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の絶縁材料を用いた単層膜又は積層膜で形成することもできる。例えば、第2の絶縁膜128を単層膜で形成する場合には、CVD法により酸化窒化珪素膜又は窒化酸化珪素膜を5nm以上50nm以下の膜厚で形成する。また、第2の絶縁膜128を3層の積層膜で形成する場合には、第1層目の絶縁膜として酸化窒化珪素膜を形成し、第2層目の絶縁膜として窒化珪素膜を形成し、第3層目の絶縁膜として酸化窒化珪素膜を形成する。また、他にも第2の絶縁膜128として、ゲルマニウムの酸化物又は窒化物等の材料を用いてもよい。

次に、半導体膜108、110の上方に形成された第2の絶縁膜128を覆うようにレジスト130を選択的に形成し、半導体膜104、106上に形成された第2の絶縁膜128を選択的に除去する(図19(C)参照)。

次に、半導体膜104、106を覆うように第3の絶縁膜132、134をそれぞれ形成する(図20(A)参照)。

第3の絶縁膜132、134は、上記第1の絶縁膜112、114、116、118の形成方法で示したいずれかの方法を用いて形成する。例えば、CVD法又はスパッタ法を用いて、酸化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等を含む絶縁膜を形成し、当該絶縁膜に対してプラズマ酸化を行うことで、当該半導体膜104、106上に第3の絶縁膜132、134を形成する。絶縁膜は、好ましくは膜厚1nm以上20nm以下、より好ましくは膜厚1nm以上10nm以下で形成する。半導体膜104、106の上方に形成された第3の絶縁膜132、134は、後に完成するトランジスタにおいてゲート絶縁膜として機能する。

次に、半導体膜104、106の上方に形成された第3の絶縁膜132、134、半導体膜108、110の上方に形成された第2の絶縁膜128を覆うように導電膜を形成する(図20(B)参照)。ここでは、導電膜として、導電膜136と導電膜138を順に積層して形成した例を示している。もちろん、導電膜は、単層膜又は3層以上の積層膜で形成してもよい。

導電膜136、138としては、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成することもできる。他にも、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。

ここでは、導電膜136として窒化タンタルを用いて形成し、その上に導電膜138としてタングステンを用いて形成する。また、他にも、導電膜136として、窒化タングステン、窒化モリブデン又は窒化チタンを用いて形成される単層膜又は積層膜を用い、導電膜138として、タンタル、モリブデン、又はチタンを用いて形成される単層膜又は積層膜を用いることができる。

次に、積層して設けられた導電膜136、138を選択的にエッチングして除去することによって、半導体膜104、106、108、110の上方の一部に導電膜136、138を残存させ、それぞれゲート電極140、ゲート電極142、ゲート電極144、ゲート電極146を形成する(図20(C)参照)。なお、メモリ部に設けられた半導体膜108の上方に形成されるゲート電極144は、後に完成する不揮発性メモリ素子において制御ゲート電極として機能する。また、ゲート電極140、142、146は、後に完成するトランジスタのゲート電極として機能する。

なお、本実施例ではゲート電極140、142、144、146を形成する際に、残存する導電膜136と導電膜138の端部が概略一致するようエッチングしたが、本発明は特に限定されない。例えば、ゲート電極を2層の積層構造とする場合、下方(第2の絶縁膜128、第3の絶縁膜132、134に接する側)の導電膜の幅(キャリアがチャネル形成領域を流れる方向(ソース領域とドレイン領域を結ぶ方向)に概略平行な方向に対する幅)が上方の導電膜の幅より大きくなるようにしてもよい。また、ゲート電極を形成した後、ゲート電極の側面にサイドウォールを形成してもよい。

次に、半導体膜104を覆うようにレジスト148を選択的に形成し、当該レジスト148、ゲート電極142、144、146をマスクとして半導体膜106、108、110に不純物元素を導入することによって不純物領域を形成する(図21(A)参照)。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、不純物元素として、リン(P)を用いる。

図21(A)においては、不純物元素を導入することによって、半導体膜106にソース領域又はドレイン領域を形成する高濃度不純物領域152とチャネル形成領域150が形成される。また、半導体膜108には、ソース領域又はドレイン領域を形成する高濃度不純物領域156とLDD領域を形成する低濃度不純物領域158とチャネル形成領域154が形成される。また、半導体膜110には、ソース領域又はドレイン領域を形成する高濃度不純物領域162とLDD領域を形成する低濃度不純物領域164とチャネル形成領域160が形成される。

また、半導体膜108に形成される低濃度不純物領域158は、図21(A)において導入された不純物元素が浮遊ゲート電極として機能する電荷蓄積膜121を突き抜けることによって形成される。従って、半導体膜108において、ゲート電極144及び電荷蓄積膜121の双方と重なる領域にチャネル形成領域154が形成され、電荷蓄積膜121と重なりゲート電極144と重ならない領域に低濃度不純物領域158が形成され、電荷蓄積膜121及びゲート電極144の双方と重ならない領域に高濃度不純物領域156が形成される。

次に、半導体膜106、108、110を覆うようにレジスト166を選択的に形成し、当該レジスト166、ゲート電極140をマスクとして半導体膜104に不純物元素を導入することによって不純物領域を形成する(図21(B)参照)。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、図21(A)で半導体膜106、108、110に導入した不純物元素と異なる導電型を有する不純物元素(例えば、ボロン(B))を導入する。その結果、半導体膜104にソース領域又はドレイン領域を形成する高濃度不純物領域170とチャネル形成領域168が形成される。

次に、第2の絶縁膜128、第3の絶縁膜132、134、ゲート電極140、142、144、146を覆うように絶縁膜172を形成し、当該絶縁膜172上に半導体膜104、106、108、110にそれぞれ形成された不純物領域152、156、162、170と電気的に接続する導電膜174を形成する(図21(C)参照)。

絶縁膜172は、CVD法やスパッタ法等により、酸化珪素、窒化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の酸素または窒素を有する絶縁膜やDLC(ダイヤモンドライクカーボン)等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる膜を用いて、単層または積層構造で設けることができる。なお、シロキサン材料とは、Si−O−Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

導電膜174は、CVD法やスパッタ法等により、アルミニウム(Al)、タングステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジウム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料を用いた単層膜又は積層膜で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜174は、例えば、バリア膜とアルミニウムシリコン(Al−Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(Al−Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜174を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができる。

本実施例は、本明細書で示した他の実施の形態又は実施例と組み合わせて行うことができる。

本実施例では、上記実施例6と異なる不揮発性半導体記憶装置の一例に関して図面を参照して説明する。なお、図22〜図25において、A−B間及びC−D間はロジック部に設けられるトランジスタを示し、E−F間はメモリ部に設けられる不揮発性メモリ素子を示し、G−H間はメモリ部に設けられるトランジスタを示している。また、本実施例では、A−B間に設けられるトランジスタをpチャネル型、C−D間、G−H間に設けるトランジスタをnチャネル型、E−F間に設けられる不揮発性メモリ素子のキャリアの移動を電子で行う場合に関して説明するが、本発明の不揮発性半導体記憶装置はこれに限定されるものでない。

まず、基板200に素子を分離した領域204、206、208、210を形成し、当該領域204、206、208、210の表面に第1の絶縁膜212、214、216、218を形成する。そして、当該第1の絶縁膜212、214、216、218を覆うように後に完成する不揮発性メモリ素子において浮遊ゲート電極として機能する電荷蓄積膜を形成する(図22(A)参照)。ここでは、浮遊ゲート電極として機能する電荷蓄積膜は、電荷蓄積膜220、電荷蓄積膜223の積層構造で形成する。基板200に設けられた領域204、206、208、210は、それぞれ絶縁膜202(フィールド酸化膜ともいう)によって分離されている。また、ここでは、基板200としてn型の導電型を有する単結晶Si基板を用い、基板200の領域206、208、210にpウェル207を設けた例を示している。

また、基板200は、半導体基板であれば特に限定されず用いることができる。例えば、n型又はp型の導電型を有する単結晶Si基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、ZnSe基板等)、貼り合わせ法またはSIMOX(Separation by IMplanted OXygen)法を用いて作製されたSOI(Silicon on Insulator)基板等を用いることができる。

素子が分離された領域204、206、208、210は、選択酸化法(LOCOS(Local Oxidation of Silicon)法)又はトレンチ分離法等を適宜用いることができる。

また、基板200の領域206、208、210に形成されたpウェルは、基板200にp型の導電型を有する不純物元素を選択的に導入することによって形成することができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。

なお、本実施例では、基板200としてn型の導電型を有する半導体基板を用いているため、領域204には不純物元素の導入を行っていないが、n型を示す不純物元素を導入することにより領域204にnウェルを形成してもよい。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。一方、p型の導電型を有する半導体基板を用いる場合には、領域204にn型を示す不純物元素を導入してnウェルを形成し、領域206、208、210には不純物元素の導入を行わない構成としてもよい。

第1の絶縁膜212、214、216、218は、熱酸化法を用いて基板200に設けられた領域204、206、208、210の表面を酸化させることにより酸化珪素膜で形成することができる。第1の絶縁膜212、214、216、218は、好ましくは膜厚1nm以上20nm以下、より好ましくは膜厚1nm以上10nm以下で形成する。

また、第1の絶縁膜212、214、216、218は、熱酸化法を用いて基板200に設けられた領域204、206、208、210の表面を酸化させることにより形成した酸化珪素膜に対して、さらにプラズマ酸化を行うことにより形成するのが好ましい。これは、ウェット酸化などの熱酸化法により絶縁膜を形成すると膜中に水素が含まれるためであり、プラズマ酸化を行うことで膜中の水素含有量を低減することができる。

プラズマ酸化は、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が1×1011cm−3以上であり、プラズマの電子温度が1.5eV以下のプラズマを利用する。より詳しくは、電子密度が1×1011cm−3以上1×1013cm−3以下で、プラズマの電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。また、絶縁膜に対するプラズマ酸化時間は、60sec以上が好ましい。

また、プラズマ酸化は、少なくとも酸素を含む雰囲気下(例えば、酸素雰囲気下、酸素(O2)若しくは亜酸化窒素(N2O)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、又は酸素若しくは亜酸化窒素と水素(H2)と希ガス雰囲気下)で行う。なお、水素を含む場合は、酸素若しくは亜酸化窒素、希ガスと比較して少ない方が好ましい。

希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。プラズマ酸化を希ガス雰囲気中で行った場合、プラズマ酸化することにより形成される第1の絶縁膜212、214、216、218は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる場合がある。例えば、プラズマ酸化に希ガスとしてArを用いた場合には、第1の絶縁膜212、214、216、218にArが含まれる場合がある。

本発明で行うプラズマ酸化は、プラズマの電子密度が1×1011cm−3以上と高密度であり、被処理物である絶縁膜付近での電子温度が低いため、形成される第1の絶縁膜212、214、216、218がプラズマにより損傷することを防止することができる。

ここでは、ウェット酸化を用いて領域204、206、208、210の表面に酸化珪素膜を形成した後、当該酸化珪素膜に対してプラズマ酸化を行うことにより第1の絶縁膜212、214、216、218を形成する。ここでのプラズマ酸化は、酸素(O2)を5sccm、アルゴンを900sccm導入して行う。

本実施例では、基板200において、メモリ部に設けられた領域208上に形成される第1の絶縁膜216は、後に完成する不揮発性メモリ素子において、トンネル絶縁膜として機能する。従って、第1の絶縁膜216の膜厚が薄いほど、トンネル電流が流れやすく、メモリとして高速動作が可能となる。また、第1の絶縁膜216の膜厚が薄いほど、後に形成される浮遊ゲート電極に低電圧で電荷を蓄積させることが可能となるため、不揮発性半導体記憶装置の消費電力を低減することができる。そのため、第1の絶縁膜212、214、216、218は、膜厚を薄く形成することが好ましい。

また、後に完成する不揮発性半導体記憶装置は、メモリ部に設けられた領域208上に形成され、トンネル絶縁膜として機能する第1の絶縁膜216を介して電子を注入することによって情報を記憶する。このとき、トンネル絶縁膜に電子トラップの要因となる水素が存在すると、書き込み及び消去を繰り返すうちに電圧が変動してしまい、メモリが劣化する原因となる。したがって、電子トラップの要因となるトンネル絶縁膜中の水素含有量は少ない方が好ましい。本実施例で示すように、プラズマ酸化を行って第1の絶縁膜216を形成することで、CVD法やスパッタ法等により形成した絶縁膜より膜中の水素含有量を低減することができる。その結果、メモリとしての性能を向上させることができる。

第1の絶縁膜上に形成する電荷蓄積膜は、単層膜または2層以上の積層膜で形成することができる。具体的には、電荷蓄積膜は、シリコン(Si)、ゲルマニウム(Ge)、タングステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料(例えば、窒化物、酸化物等)を用いて形成することができる。前記元素の化合物としては、窒化シリコン、窒化酸化シリコン、炭化シリコン、ゲルマニウムを10原子%未満の濃度で含むシリコンゲルマニウム、窒化タンタル、酸化タンタル、窒化タングステン、窒化チタン、酸化チタン、酸化スズ等を用いることができる。また、前記元素のシリサイド(例えば、タングステンシリサイド、チタンシリサイド、ニッケルシリサイド))を用いることができる。また、シリコンを用いる場合は、リンやボロンなどの不純物を添加してもよい。本実施例では、電荷蓄積膜220、223は、ゲルマニウム(Ge)又はシリコンゲルマニウム合金等のゲルマニウムを含む膜とシリコン(Si)を含む膜の積層構造で形成する。ここでは、電荷蓄積膜220として、ゲルマニウム元素を含む雰囲気中(例えば、GeH4)でプラズマCVD法を行うことにより、ゲルマニウムを主成分とする膜を1nm以上20nm以下、好ましくは1nm以上10nm以下で形成後、電荷蓄積膜223としてシリコン元素を含む雰囲気中(例えば、SiH4)でプラズマCVD法を行うことにより、シリコンを主成分とする膜を1nm以上50nm以下、好ましくは1nm以上20nm以下で形成することによって、ゲルマニウムとシリコンの積層構造で設ける。例えば、基板200として単結晶Si基板を用い、当該Si基板のある領域上にトンネル絶縁膜として機能する第1の絶縁膜を介してSiよりエネルギーギャップの小さいゲルマニウムを含む導電膜を設けた場合は、前記ある領域の電荷に対する絶縁膜により形成される第1の障壁に対して浮遊ゲート電極の電荷に対する絶縁膜により形成される第2の障壁がエネルギー的に高くなる。その結果、前記ある領域から浮遊ゲート電極へ電荷を注入しやすくすることができ、浮遊ゲート電極から電荷が消失することを防ぐことができる。つまり、メモリとして動作する場合に、低電圧で高効率な書き込みをすることが出来、且つ電荷保持特性を向上させることができる。なお、基板200において、メモリ部に設けられた領域208上に形成される電荷蓄積膜220及び電荷蓄積膜223を含む積層構造は、後に完成する不揮発性メモリ素子において、浮遊ゲート電極として機能する。また、ゲルマニウムを含む膜とシリコンゲルマニウム合金を含む膜を順に積層させて設けてもよい。

次に、基板200の領域204、206、210上に形成された、第1の絶縁膜212、214、218と電荷蓄積膜220、223を選択的に除去し、領域208上に形成された、第1の絶縁膜216と電荷蓄積膜220及び電荷蓄積膜223を含む積層構造を残存させる。ここでは、基板200において、メモリ部に設けられた領域208、第1の絶縁膜216、電荷蓄積膜220及び電荷蓄積膜223を含む積層構造を選択的にレジストで覆い、領域204、206、210上に形成された、第1の絶縁膜212、214、218と電荷蓄積膜220及び電荷蓄積膜223を含む積層構造をエッチングすることによって選択的に除去する(図22(B)参照)。

次に、基板200の領域204、206、210と、領域208の上方に形成された第1の絶縁膜216と電荷蓄積膜220、223を含む積層構造を覆うように第2の絶縁膜228を形成する(図22(C)参照)。

第2の絶縁膜228は、CVD法、スパッタ法、熱酸化法等を用いて絶縁膜を形成し、当該絶縁膜に対してプラズマ酸化を行うことで形成することが好ましい。例えば、CVD法、スパッタ法を用いて、酸化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム(AlxOy)、酸化タンタル(TaxOy)、酸化ハフニウム(HfOx)等を含む絶縁膜を形成し、当該絶縁膜に対してプラズマ酸化を行うことで第2の絶縁膜228を形成する。絶縁膜は、好ましくは膜厚1nm以上100nm以下、より好ましくは膜厚20nm以上60nm以下で形成する。プラズマ酸化は、上記第1の絶縁膜の形成方法で示した方法を用いればよい。

なお、領域208の上方に形成された第2の絶縁膜228は、後に完成する不揮発性メモリ素子においてコントロール絶縁膜として機能する。領域210の上方に形成された第2の絶縁膜228は、後に完成するトランジスタにおいてゲート絶縁膜として機能する。

次に、領域208、210の上方に形成された第2の絶縁膜228を覆うようにレジスト230を選択的に形成し、領域204、206上に形成された第2の絶縁膜228を選択的に除去する(図23(A)参照)。

次に、領域204、206を覆うように第3の絶縁膜232、234をそれぞれ形成する(図23(B)参照)。

第3の絶縁膜232、234は、上記第1の絶縁膜212、214又は第2の絶縁膜228の形成方法で示したいずれかの方法を用いて形成する。すなわち、熱酸化法、CVD法又はスパッタ法を用いて形成することができる。また、これらの方法を用いて形成された絶縁膜に対してプラズマ酸化を行ってもよい。基板200の領域204、206に形成された第3の絶縁膜232、234は、後に完成するトランジスタにおいてゲート絶縁膜として機能する。

次に、領域204、206の上方に形成された第3の絶縁膜232、234、領域208、210の上方に形成された第2の絶縁膜228を覆うように導電膜を形成する(図23(C)参照)。ここでは、導電膜として、導電膜236と導電膜238を順に積層して形成した例を示している。もちろん、導電膜は、単層又は3層以上の積層構造で形成してもよい。

導電膜236、238としては、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素、またはこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成することもできる。他にも、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。

ここでは、導電膜236として窒化タンタルを用いて形成し、その上に導電膜238としてタングステンを用いて形成する。また、他にも、導電膜236として、窒化タングステン、窒化モリブデン又は窒化チタンから選ばれた単層又は積層膜を用い、導電膜238として、タンタル、モリブデン、チタンから選ばれた単層又は積層膜を用いることができる。

次に、積層して設けられた導電膜236、238を選択的にエッチングして除去することによって、領域204、206、208、210の上方の一部に導電膜236、238を残存させ、それぞれゲート電極240、242、244、246を形成する(図24(A)参照)。また、本実施例では、ゲート電極240、242、244、246と重ならない領域204、206、208、210の表面を露出させる。

具体的には、領域204において、ゲート電極240の下方に形成された第3の絶縁膜232のうち当該ゲート電極240と重ならない部分を選択的に除去し、ゲート電極240と第3の絶縁膜232の端部が概略一致するように形成する。また、領域206において、ゲート電極242の下方に形成された第3の絶縁膜234のうち当該ゲート電極242と重ならない部分を選択的に除去し、ゲート電極242と第3の絶縁膜234の端部が概略一致するように形成する。また、領域208において、ゲート電極244の下方に形成された第2の絶縁膜228、電荷蓄積膜220及び電荷蓄積膜223を含む積層構造、第1の絶縁膜216のうち当該ゲート電極244と重ならない部分を選択的に除去し、ゲート電極244と第2の絶縁膜228、電荷蓄積膜221及び電荷蓄積膜225を含む積層構造及び第1の絶縁膜216の端部が概略一致するように形成する。また、領域210において、ゲート電極246の下方に形成された第2の絶縁膜228うち当該ゲート電極246と重ならない部分を選択的に除去し、ゲート電極246と第2の絶縁膜228の端部が概略一致するように形成する。

この場合、ゲート電極240、242、244、246の形成と同時に重ならない部分の絶縁膜等を除去してもよいし、ゲート電極240、242、244、246を形成後残存したレジスト又は当該ゲート電極240、242、244、246をマスクとして重ならない部分の絶縁膜等を除去してもよい。なお、基板200においてメモリ部に設けられた領域208の上方に形成されるゲート電極244は、後に完成する不揮発性メモリ素子において制御ゲート電極として機能する。また、ゲート電極240、242、246は、後に完成するトランジスタのゲート電極として機能する。

次に、基板200の領域204、206、208に不純物元素を選択的に導入する(図24(B)参照)。ここでは、領域206、208、210にゲート電極242、244、246をマスクとしてn型を付与する低濃度の不純物元素を選択的に導入し、領域204にゲート電極240をマスクとしてp型を付与する低濃度の不純物元素を選択的に導入する。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を付与する不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。

次に、ゲート電極240、242、244、246の側面に接する絶縁膜280(サイドウォールともよばれる)を形成する(図25(A)参照)。具体的には、プラズマCVD法やスパッタ法等により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む膜や、有機樹脂などの有機材料を含む膜を、単層又は積層して形成する。そして、当該絶縁膜を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、ゲート電極240、242、244、246の側面に接するように形成することができる。また、絶縁膜280は、絶縁膜を形成した後、上記第2の絶縁膜の形成方法で示したようにプラズマ酸化を行ってもよい。なお、絶縁膜280は、LDD(Lightly Doped drain)領域を形成する際のドーピング用のマスクとして用いる。また、ここでは、絶縁膜280は、ゲート電極240、242、244、246の下方に形成された絶縁膜や電荷蓄積膜の側面にも接するように形成されている。

次に、当該絶縁膜280、ゲート電極240、242、244、246をマスクとして基板200の領域204、206、208、210に不純物元素を導入することによって、ソース領域又はドレイン領域として機能する不純物領域を形成する(図25(A)参照)。ここでは、基板200の領域206、208、210に絶縁膜280とゲート電極242、244、246をマスクとして高濃度のn型を付与する不純物元素を導入し、領域204に絶縁膜280とゲート電極240をマスクとして高濃度のp型を付与する不純物元素を導入する。

その結果、基板200の領域204には、ソース領域又はドレイン領域を形成する不純物領域269と、LDD領域を形成する低濃度不純物領域267と、チャネル形成領域266が形成される。また、基板200の領域206には、ソース領域又はドレイン領域を形成する不純物領域253と、LDD領域を形成する低濃度不純物領域251と、チャネル形成領域250が形成される。また、基板200の領域208には、ソース領域又はドレイン領域を形成する不純物領域257と、LDD領域を形成する低濃度不純物領域255と、チャネル形成領域254が形成される。また、基板200の領域210には、ソース領域又はドレイン領域を形成する不純物領域263と、LDD領域を形成する低濃度不純物領域261と、チャネル形成領域260が形成される。

なお、本実施例では、ゲート電極240、242、244、246と重ならない基板200の領域204、206、208、210を露出させた状態で不純物元素の導入を行っている。従って、基板200の領域204、206、208、210にそれぞれ形成されるチャネル形成領域266、250、254、260はゲート電極240、242、244、246と自己整合的に形成することができる。

次に、基板200の領域204、206、208、210上に設けられた絶縁膜や電荷蓄積膜等を覆うように絶縁膜272を形成し、当該絶縁膜272上に領域204、206、208、210にそれぞれ形成された不純物領域269、253、257、263と電気的に接続する導電膜274を形成する(図25(B)参照)。

絶縁膜272は、CVD法やスパッタ法等により、酸化珪素、窒化珪素、酸化窒化珪素(SiOxNy)(x>y>0)、窒化酸化珪素(SiNxOy)(x>y>0)等の酸素若しくは窒素を有する絶縁膜やDLC(ダイヤモンドライクカーボン)等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる膜の単層または積層構造で設けることができる。なお、シロキサン材料とは、Si−O−Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

導電膜274は、CVD法やスパッタ法等により、アルミニウム(Al)、タングステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジウム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくはこれらの元素を主成分とする化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜274は、例えば、バリア膜とアルミニウムシリコン(Al−Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(Al−Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜274を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができる。

本実施例は、本明細書で示した他の実施の形態又は実施例と適宜組み合わせて行うことができる。

本実施例では、本発明を用いて作製した絶縁膜の特性について説明する。まず、測定に用いた試料A、試料B、試料C、試料D及びその作製方法について説明する。

試料A、試料B、試料Cは、Si基板上に設けられた酸化窒化珪素膜(SiOxNy)(x>y>0)と、当該酸化窒化珪素膜上に設けられたアルミニウム−チタン膜からなる電極とが順次積層された構造とした。また、酸化窒化珪素膜は、プラズマCVD法を用いて形成した酸化窒化珪素膜に対してプラズマ酸化を行った。以下、試料A、試料B、試料Cについて具体的に説明する。

試料Aは、まず、12.7cm角のSi基板を準備した。そして、当該Si基板上に、酸化窒化珪素膜をプラズマCVD法を用いて膜厚9nmで形成した。酸化窒化珪素膜の成膜条件を以下に記す。

SiH4流量:1sccm、N2O流量:800sccm、処理室内圧力:40Pa、高周波電力150W(60MHz)、電極間隔:28mm、成膜温度(基板温度):400℃。

次に、酸化窒化珪素膜に対してプラズマ酸化を180sec行った。プラズマ酸化処理後の酸化窒化珪素膜は、膜厚10nmであった。プラズマ酸化の処理条件を以下に記す。

O2流量:5sccm、Ar流量:900sccm、処理室内圧力:106.67Pa、高周波電力3800W(2.45GHz)、基板温度:400℃。

次に、酸化窒化珪素膜上に、アルミニウムとチタンの合金であるアルミニウム−チタン(Al−Ti)膜をスパッタ法によって400nm形成した。当該アルミニウム−チタン膜をフォトリソグラフィ法及びエッチング法を用いて選択的にエッチングし、面積1.96×10−3cm2の電極を形成した。以上の工程で、試料Aを得た。

試料Bは、まず、12.7cm角のSi基板上に、酸化窒化珪素膜をプラズマCVD法を用いて膜厚9.5nmで形成した。酸化窒化珪素膜の成膜条件は試料Aと同様であるので省略する。

次に、酸化窒化珪素膜に対してプラズマ酸化を120sec行った。プラズマ酸化処理後の酸化窒化珪素膜は、膜厚10nmであった。プラズマ酸化の処理条件は試料Aと同様であるので省略する。

次に、酸化窒化珪素膜上に、アルミニウムとチタンの合金であるアルミニウム−チタン(Al−Ti)膜をスパッタ法によって400nm形成した。当該アルミニウム−チタン膜をフォトリソグラフィ法及びエッチング法を用いて選択的にエッチングし、面積1.96×10−3cm2の電極を形成した。以上の工程で、試料Bを得た。

試料Cは、まず、12.7cm角のSi基板上に、酸化窒化珪素膜をプラズマCVD法を用いて膜厚10nmで形成した。酸化窒化珪素膜の成膜条件は試料Aと同様であるので省略する。

次に、酸化窒化珪素膜に対してプラズマ酸化を60sec行った。プラズマ酸化処理後の酸化窒化珪素膜は、膜厚10nmであった。プラズマ酸化の処理条件は試料Aと同様であるので省略する。

次に、酸化窒化珪素膜上に、アルミニウムとチタンの合金であるアルミニウム−チタン(Al−Ti)膜をスパッタ法によって400nm形成した。当該アルミニウム−チタン膜を選択的にエッチングし、面積1.96×10−3cm2の電極を形成した。以上の工程で、試料Cを得た。

試料Dは、Si基板上に設けられた酸化窒化珪素膜(SiOxNy)(x>y>0)と、当該酸化窒化珪素膜上に設けられたアルミニウム−チタン膜からなる電極とが順次積層された構造とした。また、酸化窒化珪素膜は、プラズマCVD法を用いて形成した。

具体的には、まず、12.7cm角のSi基板を準備した。そして、当該Si基板上に、酸化窒化珪素膜をプラズマCVD法によって膜厚10nmで形成した。酸化珪素膜の成膜条件を以下に記す。

SiH4流量:1sccm、N2O流量:800sccm、処理室内圧力:40Pa、高周波電力150W(60MHz)、電極間隔:28mm、成膜温度(基板温度):400℃。

次に、酸化窒化珪素膜上に、アルミニウムとチタンの合金であるアルミニウム−チタン(Al−Ti)膜をスパッタ法によって400nm形成した。当該アルミニウム−チタン膜を選択的にエッチングし、面積1.96×10−3cm2の電極を形成した。以上の工程で、試料Dを得た。

試料Aについて、電流密度−電界強度(J−E)特性を測定した結果を図26(A)に示す。また、試料Dについて、J−E特性を測定した結果を図26(B)に示す。図26(A)、(B)において、縦軸は電流密度(A/cm2)、横軸は電界強度(MV/cm)を表す。測定は基板面内112ポイントで行った。なお、図26(A)、(B)において、電流密度1A/cm2の目盛りを点線で示す。

また、図26(A)の電流密度1A/cm2における電界強度をヒストグラムにした結果を図27(A)に示す。また、図26(B)の電流密度1A/cm2における電界強度をヒストグラムにした結果を図27(B)に示す。図27において、縦軸は耐圧不良の割合(%)、横軸は絶縁破壊電界EBD(MV/cm)を表す。縦軸の耐圧不良の割合は、図26(A)、(B)において、電流密度が1A/cm2以上に跳ね上がっているポイントを耐圧不良とした。そして、全測定ポイント112に対する耐圧不良の割合を算出した。

また、図26(A)、(B)の電流密度1A/cm2における電界強度と累積耐圧不良率の関係を折れ線グラフにしたものを図28に示す。図28において、縦軸は累積不良率F(%)、横軸は絶縁破壊電界EBD(MV/cm)を表す。図28から、試料Dは絶縁破壊電界5MV/cm程度から不良率が確認されるが、試料Aは絶縁破壊電界8MV/cm程度まで不良が確認されないことがわかった。したがって、プラズマ酸化した試料Aは、試料Dと比較して高耐圧であることがわかった。

なお、図27、図28に示すグラフは、絶縁膜耐圧評価の一手法であり、TZDB(Time Zero Dielectric Breakdown)ヒストグラムともいわれる。TZDBヒストグラムでは、絶縁破壊電界0MV/cm〜2MV/cmまではAモード、絶縁破壊電界2MV/cm〜8MV/cmまではBモード、絶縁破壊電界8MV/cm以上はCモードといわれる。一般的に、トランジスタ等のデバイスを構成する絶縁膜として用いる際にAモード、Bモードで不良があると、歩留まり、信頼性を低下させる大きな要因となると言われている。プラズマ酸化した試料Aは、Aモード、Bモードでは不良がほとんどなく、高耐圧な膜であることがわかった。

以上の測定結果から、プラズマCVD法を用いて作製した膜にプラズマ酸化を行った膜(ここでは、試料Aに相当)は、プラズマCVD法のみで作製した膜(ここでは、試料Dに相当)と比較して、高耐圧な膜であることがわかった。

次に、試料A〜試料Dについて、電流−電圧(I−V)特性を測定した結果を図29(A)、(B)、図30(A)、(B)にそれぞれ示す。図29(A)〜図30(B)において、縦軸は電流(A)、横軸は電圧(V)を表す。ここでは、基板面内112ポイントのI−V特性を測定した結果を示す。なお、図29(A)〜図30(B)において、電圧10Vの目盛りを点線で示す。

また、試料A〜試料Dについて、耐圧不良率(%)を算出した結果を図31に示す。耐圧不良率は、図29(A)〜図30(B)に示したI−V特性の結果から、I−V曲線が10V未満で跳ね上がっているものを耐圧不良としてカウントし、全測定ポイント数から耐圧不良のポイント数の割合を算出して求めた。図31から、プラズマ酸化した試料A〜試料Cは、耐圧不良率が非常に低いことがわかった。また、試料A、試料B、試料Cの順に耐圧不良率が低いことがわかった。

また、試料A〜Dに一定電流(12μA)を流したときの電圧と時間の関係を図32(A)、(B)、図33(A)、(B)にそれぞれ示す。図32(A)〜図33(B)において、縦軸は電圧(V)、横軸は時間(sec)を表す。

また、図32、図33からQbd(C/cm2)を算出し、平均化した結果を表2に示す。

なお、Qbd値とは、試料A〜試料Dに流した電流値と、絶縁破壊に至った時間(電圧が0付近に降下した時間)を乗じた値である。つまり、Qbd値が大きいほど高耐圧な膜であることがわかる。したがって、表2の結果から、プラズマ酸化した試料A〜試料Cは、試料Dと比較してQbd値で一桁以上高耐圧であることがわかった。また、試料A、試料B、試料Cの順でQbd値が小さくなっており、プラズマ酸化処理時間が長いほど高耐圧な膜が得られることがわかった。

また、試料Aについて二次イオン質量分析法(SIMS)で測定した結果を図34に示し、試料Dについて測定した結果を図35に示す。図34、図35において、縦軸は濃度(atoms/cm3)、横軸は試料をエッチングした深さ(nm)を表す。また、約10nmの深さまでが酸化窒化珪素膜である。

図34、図35において、酸化窒化珪素膜中の水素濃度に注目すると、試料Aでは水素の濃度が約1×1019atoms/cm3以下(SIMSの測定限界以下)であるのに対し、試料Dでは水素の濃度が約1×1020atoms/cm3であり、水素の濃度が1桁以上異なっていることがわかる。したがって、プラズマ酸化を行うことで、酸化窒化珪素膜中の水素濃度が1桁以上減少することがわかった。

また、試料A、試料Dについて、酸化窒化珪素膜中のSiの結合状態をX線光電子分光法(XPS)を用いて測定した結果を図36(A)、(B)に示す。図36(A)、(B)において、エネルギーバンド(Binding Energy)99.4eV付近にピークを有するのはSi−Si結合であり、エネルギーバンド104eV付近にピークを有するのはSiO2等の結合である。試料A、試料Dいずれにおいても、104eV付近のピークについてピーク分離検出を行った結果、エネルギーバンド102eV、103eV付近に現れるSi−H結合起因のピークは確認されなかった。図34、図35に示したSIMS分析結果から、プラズマ酸化を行うことで酸化窒化珪素膜中の水素濃度が減少することがわかっており、XPS分析結果と合わせて考えると、プラズマ酸化を行うことで酸化窒化珪素膜中に含まれるO−H結合からの水素の脱離反応、又は水素と酸素の置換反応が起きていることがわかった。

また、試料A、試料Dについて、電流ストレス印加前後でCV測定を行った結果を図37(A)、(B)に示す。なお、試料Aの測定結果を図37(A)、試料Dの測定結果を図37(B)に示す。ここでは、電流ストレスとして、一定電流(1μA)を一定時間(10sec、又は100sec)流した。CV測定は、初期状態と、一定電流を10sec流した後と、一定電流を100sec流した後の3回行った。

図37(A)、(B)からわかるように、試料Dでは電流ストレス10sec印加後にCVカーブは大きくプラスシフトし、電流ストレス34sec程度印加後に絶縁破壊に至っている。一方、試料Aでは電流ストレス10sec印加後にCVカーブはプラスシフトするものの試料Dと比べるとそのシフトは非常に小さい。さらに、電流ストレス100sec印加後でも絶縁破壊に至らず、CVカーブのシフトは試料Dの電流ストレス10sec印加後よりも小さい。

CV測定において、電流ストレス印加後にCVカーブがプラスシフトし、CVカーブ立ち上がりの傾きが鈍くなるのは、酸化膜中に電子トラップが発生し、かつ界面準位密度が増加していることを示している。図37(A)、(B)からわかるように、試料Aは試料Dと比較してCVカーブのプラスシフト、及びCVカーブ立ち上がりの傾きが鈍くなる程度が小さい。以上のことから、プラズマ酸化により、電子トラップとなるO−H結合が減少し、電気的ストレスによる電子トラップの発生を抑制できることがわかった。

また、0.5wt%フッ化水素酸を用いて試料A、試料Dをエッチングした。このときのエッチング速度は、試料Dは8.43nm/min程度であった。一方、試料Aのエッチング速度は4.33nm/min程度であり、試料Dのおよそ半分の速度であった。したがって、プラズマ酸化を行うことで、より緻密な膜を得られることがわかった。

以上のように、本発明のようにプラズマCVD法を用いて形成した絶縁膜に対してプラズマ酸化を行うことで、緻密で高耐圧な膜が得られることがわかった。また、プラズマCVD法を用いて形成した絶縁膜に対してプラズマ酸化を行うことで、膜中の水素濃度が減少することがわかった。

以上の結果から、プラズマ酸化により、膜中に存在するO−H結合の水素が酸素ラジカルにより脱離する、又は膜中の水素と酸素との置換反応が起き、膜中の水素が低減することで、緻密で高耐圧な膜が得られると考えられる。

本実施例では、上述した本発明の不揮発性半導体記憶装置を備えた非接触でデータの入出力が可能である半導体装置の適用例に関して図面を参照して以下に説明する。非接触でデータの入出力が可能である半導体装置は利用の形態によっては、RFIDタグ、IDタグ、ICタグ、ICチップ、RFタグ、無線タグ、電子タグまたは無線チップともよばれる。

半導体装置8000は、非接触でデータを交信する機能を有し、高周波回路8010、電源回路8020、リセット回路8030、クロック発生回路8040、データ復調回路8050、データ変調回路8060、他の回路の制御を行う制御回路8070、記憶回路8080およびアンテナ8090を有している(図38(A))。高周波回路8010はアンテナ8090より信号を受信して、データ変調回路8060より受信した信号をアンテナ8090から出力する回路であり、電源回路8020は受信信号から電源電位を生成する回路であり、リセット回路8030はリセット信号を生成する回路であり、クロック発生回路8040はアンテナ8090から入力された受信信号を基に各種クロック信号を生成する回路であり、データ復調回路8050は受信信号を復調して制御回路8070に出力する回路であり、データ変調回路8060は制御回路8070から受信した信号を変調する回路である。また、制御回路8070としては、例えばコード抽出回路9010、コード判定回路9020、CRC判定回路9030および出力ユニット回路9040が設けられている。なお、コード抽出回路9010は制御回路8070に送られてきた命令に含まれる複数のコードをそれぞれ抽出する回路であり、コード判定回路9020は抽出されたコードとリファレンスに相当するコードとを比較して命令の内容を判定する回路であり、CRC判定回路9030は判定されたコードに基づいて送信エラー等の有無を検出する回路である。

次に、上述した半導体装置の動作の一例について説明する。まず、アンテナ8090により無線信号が受信される。無線信号は高周波回路8010を介して電源回路8020に送られ、高電源電位(以下、VDDと記す)が生成される。VDDは半導体装置8000が有する各回路に供給される。また、高周波回路8010を介してデータ復調回路8050に送られた信号は復調される(以下、復調信号)。さらに、高周波回路8010を介してリセット回路8030およびクロック発生回路8040を通った信号及び復調信号は制御回路8070に送られる。制御回路8070に送られた信号は、コード抽出回路9010、コード判定回路9020およびCRC判定回路9030等によって解析される。そして、解析された信号にしたがって、記憶回路8080内に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は出力ユニット回路9040を通って符号化される。さらに、符号化された半導体装置8000の情報はデータ変調回路8060を通って、アンテナ8090により無線信号として送信される。なお、半導体装置8000を構成する複数の回路においては、低電源電位(以下、VSS)は共通であり、VSSはGNDとすることができる。また、本発明の不揮発性半導体記憶装置を記憶回路8080に適用することができる。

このように、通信手段(例えばリーダ/ライタ、又はリーダ或いはライタいずれかの機能を有する手段)から半導体装置8000に信号を送り、当該半導体装置8000から送られてきた信号を通信手段で受信することによって、半導体装置のデータを読み取ることが可能となる。

また、半導体装置8000は、各回路への電源電圧の供給を電源(バッテリー)を搭載せず電磁波により行うタイプとしてもよいし、電源(バッテリー)を搭載して電磁波と電源(バッテリー)により各回路に電源電圧を供給するタイプとしてもよい。

次に、非接触でデータの入出力が可能な半導体装置の使用形態の一例について説明する。表示部3210を含む携帯端末の側面には、リーダ/ライタ3200が設けられ、品物3220の側面には半導体装置3230が設けられる(図38(B))。品物3220が含む半導体装置3230にリーダ/ライタ3200をかざすと、表示部3210に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。また、商品3260をベルトコンベアにより搬送する際に、リーダ/ライタ3240と、商品3260に設けられた半導体装置3250を用いて、該商品3260の検品を行うことができる(図38(C))。このように、システムに半導体装置を活用することで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。

また、本発明の不揮発性半導体記憶装置は、メモリを具備したあらゆる分野の電子機器に用いることが可能である。例えば、本発明の不揮発性半導体記憶装置を適用した電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDVD(digital versatile disc)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それら電子機器の具体例を図39に示す。

図39(A)、(B)は、デジタルカメラを示している。図39(B)は、図39(A)の裏側を示す図である。このデジタルカメラは、筐体2111、表示部2112、レンズ2113、操作キー2114、シャッターボタン2115などを有する。また、取り出し可能な不揮発性のメモリ2116を備えており、当該デジタルカメラで撮影したデータをメモリ2116に記憶させておく構成となっている。本発明を用いて形成された不揮発性の半導体記憶装置は当該メモリ2116に適用することができる。また、本発明を用いて形成された半導体装置は、表示部2112を駆動するスイッチング素子として適用することができる。

また、図39(C)は、携帯電話を示しており、携帯端末の1つの代表例である。この携帯電話は筐体2121、表示部2122、操作キー2123などを含む。また、携帯電話は、取り出し可能な不揮発性のメモリ2125を備えており、当該携帯電話の電話番号等のデータ、映像、音楽データ等をメモリ2125に記憶させ再生することができる。本発明を用いて形成された不揮発性の半導体記憶装置は当該メモリ2125に適用することができる。また、本発明を用いて形成された半導体装置は、表示部2122を駆動するスイッチング素子として適用することができる。

また、図39(D)は、デジタルプレーヤーを示しており、オーディオ装置の1つの代表例である。図39(D)に示すデジタルプレーヤーは、本体2130、表示部2131、メモリ部2132、操作部2133、イヤホン2134等を含んでいる。なお、イヤホン2134の代わりにヘッドホンや無線式イヤホンを用いることができる。メモリ部2132は、本発明を用いて形成された不揮発性の半導体記憶装置を用いることができる。また、本発明を用いて形成された半導体装置は、表示部2131を駆動するスイッチング素子として適用することができる。例えば、記録容量が20〜200ギガバイト(GB)のNAND型不揮発性メモリを用い、操作部2133を操作することにより、映像や音声(音楽)を記録、再生することができる。なお、表示部2131は黒色の背景に白色の文字を表示することで消費電力を抑えられる。これは携帯型のオーディオ装置において特に有効である。なお、メモリ部2132に設けられた不揮発性の半導体記憶装置は、取り出し可能な構成としてもよい。

また、図39(E)は、電子ブック(電子ペーパーともいう)を示している。この電子ブックは、本体2141、表示部2142、操作キー2143、メモリ部2144を含んでいる。またモデムが本体2141に内蔵されていてもよいし、無線で情報を送受信できる構成としてもよい。メモリ部2144は、本発明を用いて形成された不揮発性の半導体記憶装置を用いることができる。また、本発明を用いて形成された半導体装置は、表示部2142を駆動するスイッチング素子として適用することができる。例えば、記録容量が20〜200ギガバイト(GB)のNAND型不揮発性メモリを用い、操作キー2143を操作することにより、映像や音声(音楽)を記録、再生することができる。なお、メモリ部2144に設けられた不揮発性の半導体記憶装置は、取り出し可能な構成としてもよい。

以上の様に、本発明の不揮発性半導体記憶装置、及び半導体装置の適用範囲は極めて広く、メモリを有するものであればあらゆる分野の電子機器に用いることが可能である。

本実施例では、本発明を用いて作製した不揮発性メモリ素子の特性について説明する。まず、測定に用いた不揮発性メモリ素子A及び不揮発性メモリ素子Bの作製方法について説明する。

図40(A)にメモリ素子Aを、図40(B)にメモリ素子Bの構成を示す。

メモリ素子Aは、ガラス基板4000上に下地絶縁膜4002を介して半導体膜4004を形成し、当該半導体膜4004上にトンネル絶縁膜4012と、電荷蓄積膜4014と、コントロール絶縁膜4016と、制御ゲート電極4022とが順に積層された構造とした。下地絶縁膜4002は、プラズマCVD法を用いて、窒化酸化シリコン膜(膜厚50nm)と酸化窒化シリコン膜(膜厚150nm)とを順に積層して設けた。また、半導体膜4004は、多結晶シリコン膜で形成し、該半導体膜4004にはチャネル形成領域4006、LDD領域4008、ソース領域又はドレイン領域4010を設けた。トンネル絶縁膜4012は、半導体膜4004上にプラズマCVD法を用いて酸化シリコン膜を膜厚9nmで形成した後、プラズマ酸化を180秒行った。電荷蓄積膜4014は、プラズマCVD法を用いてシリコン膜を膜厚50nmで形成した後、リンを添加して形成した。コントロール絶縁膜4016は、プラズマCVD法を用いて酸化窒化シリコン膜を膜厚15nm、窒化シリコン膜を膜厚10nm、酸化窒化シリコン膜を膜厚15nmで連続成膜した後、プラズマ酸化を180秒行った。制御ゲート電極4022は、窒化タンタル膜4018(膜厚30nm)、タングステン膜4020(膜厚370nm)を順に積層して形成した。なお、ソース領域又はドレイン領域4010及びLDD領域4008はn型の導電型とし、ソース領域又はドレイン領域4010の不純物濃度が高くなるようにした。チャネル形成領域4006はp型の導電型とした。また、トンネル絶縁膜4012及びコントロール絶縁膜4016のプラズマ酸化は、プラズマCVD法を用いた絶縁膜の成膜の後に連続処理で行った。

メモリ素子Bは、メモリ素子Aの作製方法において、トンネル絶縁膜4212を形成する際にプラズマ酸化を行わず、プラズマCVD法で成膜したままの構成とした。

ここで、不揮発性メモリ素子A、Bを用いて書き込みと読み込みを繰り返し1000回行った場合のしきい値電圧(Vth)の変動結果(ΔVth)を表3に示す。下記表3には、書き込み/読み込みを行う前の初期段階のしきい値(initial Vth)、1000回書き込み/読み込みを繰り返し行った段階のしきい値(103回後のVth)を示している。また、初期段階のしきい値(initial Vth)から1000回書き込み/読み込み後のしきい値(103回後のVth)を引いた差分をしきい値変動値(ΔVth)として求めた。

上記表3に示すように、不揮発性メモリ素子Aは1000回書き込み/読み込みを繰り返し行った場合のしきい値変動はおよそ−0.9Vであった。一方、不揮発性メモリ素子Bの1000回書き込み/読み込みを繰り返し行った場合のしきい値変動はおよそ−1.6Vであった。したがって、本発明を適用して絶縁膜にプラズマ酸化を行うことで、書き込み/読み込みを繰り返すことによるしきい値変動を低減することができ、信頼性向上を図ることができることがわかった。

本発明の絶縁膜の作製方法の一例を示す図。

本発明の絶縁膜の作製方法の一例を示す図。

本発明の絶縁膜を作製する装置の一例を示す図。

本発明の半導体装置の作製方法の一例を示す図。

本発明の半導体装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の半導体装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

不揮発性メモリセルアレイの等価回路の一例を示す図。

NOR型不揮発性メモリセルアレイの等価回路の一例を示す図。

NAND型不揮発性メモリセルアレイの等価回路の一例を示す図。

NAND型不揮発性メモリの書き込み動作を説明する図。

NAND型不揮発性メモリの消去及び読み出し動作を説明する図。

電荷が蓄積された”0”の場合と消去された”1”の場合における不揮発性メモリのしきい値電圧の変化を示す図。

不揮発性半導体記憶装置の回路ブロック図の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の不揮発性半導体記憶装置の作製方法の一例を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の絶縁膜の特性を示す図。

本発明の半導体装置の使用形態の一例を示す図。

本発明の半導体装置の使用形態の一例を示す図。

本発明の不揮発性半導体記憶装置の特性を示す図。

符号の説明

10 基板

12 第1の絶縁膜

14 第2の絶縁膜

52 メモリセルアレイ

54 周辺回路

56 アドレスバッファ

58 コントロール回路

60 昇圧回路

62 ロウデコーダ

64 カラムデコーダ

66 センスアンプ

68 データバッファ

70 データ入出力バッファ

80 アンテナ

82 誘電体板

84 ガス供給部

86 排気口

88 支持台

90 温度制御部

92 マイクロ波供給部

94 プラズマ

100 基板

102 絶縁膜

104 半導体膜

106 半導体膜

108 半導体膜

110 半導体膜

112 第1の絶縁膜

116 第1の絶縁膜

120 電荷蓄積膜

121 電荷蓄積膜

122 レジスト

124 レジスト

126 不純物領域

128 第2の絶縁膜

130 レジスト

132 第3の絶縁膜

136 導電膜

138 導電膜

140 ゲート電極

142 ゲート電極

144 ゲート電極

146 ゲート電極

148 レジスト

150 チャネル形成領域

152 不純物領域

154 チャネル形成領域

156 高濃度不純物領域

158 低濃度不純物領域

160 チャネル形成領域

162 高濃度不純物領域

164 低濃度不純物領域

166 レジスト

168 チャネル形成領域

170 高濃度不純物領域

172 絶縁膜

174 導電膜

200 基板

202 絶縁膜

204 領域

206 領域

207 pウェル

208 領域

210 領域

212 第1の絶縁膜

216 第1の絶縁膜

220 電荷蓄積膜

221 電荷蓄積膜

223 電荷蓄積膜

225 電荷蓄積膜

228 第2の絶縁膜

230 レジスト

232 第3の絶縁膜

234 第3の絶縁膜

236 導電膜

238 導電膜

240 ゲート電極

242 ゲート電極

244 ゲート電極

246 ゲート電極

250 チャネル形成領域

251 低濃度不純物領域

253 不純物領域

254 チャネル形成領域

255 低濃度不純物領域

257 不純物領域

260 チャネル形成領域

261 低濃度不純物領域

263 不純物領域

266 チャネル形成領域

267 低濃度不純物領域

269 不純物領域

272 絶縁膜

274 導電膜

280 絶縁膜

331 被処理基板

351 支持台

353 排気口

357 温度制御部

360 電極板

361 高周波電力導入部

362 ガス導入部

400 基板

402 下地絶縁膜

404 半導体膜

406 第1の絶縁膜

408 第2の絶縁膜

410 導電膜

412 導電膜

414 導電膜

416 導電膜

418 ゲート電極

420 チャネル形成領域

422 不純物領域

424 第3の絶縁膜

426 絶縁膜

428 導電膜

600 基板

601 領域

602 絶縁膜

603 第1の絶縁膜

604 電荷蓄積膜

606 ゲート電極

608 第2の絶縁膜

612 導電膜

614 導電膜

616 導電膜

618 導電膜

620 ゲート電極

622 チャネル形成領域

624 不純物領域

626 不純物領域

822 不純物領域

824 第3の絶縁膜

825 チャネル形成領域

826 不純物領域

827 不純物領域

828 絶縁膜

830 絶縁膜

832 導電膜

900 基板

902 下地絶縁膜

904 半導体膜

906 第1の絶縁膜

907 第2の絶縁膜

908 電荷蓄積膜

910 第3の絶縁膜

911 絶縁膜

912 導電膜

914 導電膜

916 電荷蓄積膜

918 絶縁膜

920 導電膜

924 ゲート電極

926 チャネル形成領域

928 不純物領域

2111 筐体

2112 表示部

2113 レンズ

2114 操作キー

2115 シャッターボタン

2116 メモリ

2121 筐体

2122 表示部

2123 操作キー

2125 メモリ

2130 本体

2131 表示部

2132 メモリ部

2133 操作部

2134 イヤホン

2141 本体

2142 表示部

2143 操作キー

2144 メモリ部

3200 リーダ/ライタ

3210 表示部

3220 品物

3230 半導体装置

3240 リーダ/ライタ

3250 半導体装置

3260 商品

4000 ガラス基板

4002 下地絶縁膜

4004 半導体膜

4006 チャネル形成領域

4008 LDD領域

4010 ドレイン領域

4012 トンネル絶縁膜

4014 電荷蓄積膜

4016 コントロール絶縁膜

4018 窒化タンタル膜

4020 タングステン膜

4022 制御ゲート電極

4212 トンネル絶縁膜

4216 コントロール絶縁膜

8000 半導体装置

8010 高周波回路

8020 電源回路

8030 リセット回路

8040 クロック発生回路

8050 データ復調回路

8060 データ変調回路

8070 制御回路

8080 記憶回路

8090 アンテナ

9010 コード抽出回路

9020 コード判定回路

9030 CRC判定回路

9040 出力ユニット回路