JP2006302950A - 不揮発性半導体装置および不揮発性半導体装置の製造方法 - Google Patents

不揮発性半導体装置および不揮発性半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2006302950A JP2006302950A JP2005118505A JP2005118505A JP2006302950A JP 2006302950 A JP2006302950 A JP 2006302950A JP 2005118505 A JP2005118505 A JP 2005118505A JP 2005118505 A JP2005118505 A JP 2005118505A JP 2006302950 A JP2006302950 A JP 2006302950A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- gates

- semiconductor device

- floating

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 99

- 238000004519 manufacturing process Methods 0.000 title claims description 20

- 239000000758 substrate Substances 0.000 claims abstract description 30

- 238000000034 method Methods 0.000 claims description 27

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 21

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 17

- 230000006870 function Effects 0.000 abstract description 6

- 239000010408 film Substances 0.000 description 225

- 230000008569 process Effects 0.000 description 17

- 238000000151 deposition Methods 0.000 description 10

- 239000004020 conductor Substances 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 8

- 239000007789 gas Substances 0.000 description 7

- 230000008878 coupling Effects 0.000 description 6

- 238000010168 coupling process Methods 0.000 description 6

- 238000005859 coupling reaction Methods 0.000 description 6

- 230000007423 decrease Effects 0.000 description 6

- 230000008021 deposition Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 239000001257 hydrogen Substances 0.000 description 5

- 229910052739 hydrogen Inorganic materials 0.000 description 5

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 3

- 239000003870 refractory metal Substances 0.000 description 3

- 229910021332 silicide Inorganic materials 0.000 description 3

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- 239000011800 void material Substances 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 238000006557 surface reaction Methods 0.000 description 1

- 238000001947 vapour-phase growth Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/7682—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing the dielectric comprising air gaps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42324—Gate electrodes for transistors with a floating gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

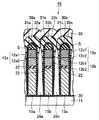

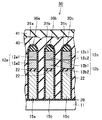

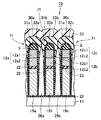

【解決手段】 主表面を有する半導体基板11と、半導体基板11の主表面上に間隔をあけて形成された第1と第2フローティングゲート15a、15bと、第1と第2フローティングゲート15a、15b上の第1と第2コントロールゲート12a、12bと、第1コントロールゲート12a上に形成された第1絶縁膜32aと、第2コントロールゲート12b上に形成され、第1絶縁膜32aに接触するように形成された第2絶縁膜32bと、第1絶縁膜32aと、第2絶縁膜32bとを接触させることで、少なくとも第1フローティングゲート15aと第2フローティングゲート15b間に形成された空隙部26aとを備える。

【選択図】 図3

Description

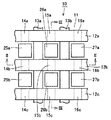

図1は、本実施の形態1に係る不揮発性半導体装置10の平面図である。この図1に示されるように、主表面を有する半導体基板11と、半導体基板11の主表面上に形成され一方向に向けて延在し、間隔を隔てて形成されたアシストゲート13a、13bと、半導体基板11の主表面上に形成されたフローティングゲート(第1フローティングゲート)14a〜16a、14c〜16cと、フローティングゲート14a〜16a、14c〜16cと間隔をあけて形成されたフローティングゲート(第2フローティングゲート)14b〜16bとを備えている。

図9に示されるように、ボトム膜厚が厚くなるほど、ΔVthが大きくなり、側壁膜厚が大きくなる程、ΔVthが大きくなる。そして、図8に示された空隙部26a、26bが形成されない場合においては、ΔVthが大きくなっていることがわかる。すなわち、図1において、空隙部25a〜27a、25b〜27b、25c〜27cの底面および側面に形成された絶縁膜の厚さが薄いほどフローティングゲート14a〜14c、15a〜15c、16a〜16c間の容量結合を低減することができることが分かる。

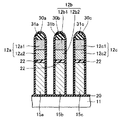

図10から図17を用いて、実施の形態2に係る不揮発性半導体装置50について、説明する。図10は、本実施の形態2に係る不揮発性半導体装置50の断面図である。この図10に示されるように、不揮発性半導体装置50は、半導体基板11の主表面上に形成された絶縁膜20と、絶縁膜20を介して主表面上に形成されたフローティングゲート15a〜15cと、このフローティングゲート15a〜15cの上面上に形成されたONO膜22と、このONO膜22を介してフローティングゲート15a〜15c上に形成されたコントロールゲート12a〜12cとを備えている。

Claims (11)

- 主表面を有する半導体基板と、

前記半導体基板の主表面上に間隔をあけて形成された第1と第2フローティングゲートと、

前記第1と第2フローティングゲート上の第1と第2コントロールゲートと、

前記第1コントロールゲート上に形成された第1絶縁膜と、

前記第2コントロールゲート上に形成され、前記第1絶縁膜に接触するように形成された第2絶縁膜と、

前記第1絶縁膜と、前記第2絶縁膜とを接触させることで、少なくとも前記第1フローティングゲートと前記第2フローティングゲート間に形成された空隙部と、

を備えた不揮発性半導体装置。 - 前記空隙部は、前記第1と第2フローティングゲート間から、前記第1と第2コントロールゲートの上端部より上方に亘って形成された、請求項1に記載の不揮発性半導体装置。

- 前記第1絶縁膜と前記第2絶縁膜とは、酸化シリコン膜より誘電率が低い多孔質の絶縁膜から形成された、請求項1または請求項2に記載の不揮発性半導体装置。

- 前記第1絶縁膜および前記第2絶縁膜の表面上に形成され、前記第1絶縁膜と前記第2絶縁膜との接触部を覆う第3絶縁膜が形成された、請求項1から請求項3のいずれかに記載の不揮発性半導体装置。

- 主表面を有する半導体基板と、

前記半導体基板の主表面上に形成された第1と第2フローティングゲートと、

前記第1フローティングゲートと前記第2フローティングゲートとの間に形成され、酸化シリコン膜より誘電率が低く、多孔質の絶縁膜と、

を備えた不揮発性半導体装置。 - 前記第1と第2フローティングゲート上に形成された第1と第2コントロールゲートをさらに備え、

前記第1フローティングゲートと前記第2フローティングゲートとの間および前記第1コントロールゲートと前記第2コントロールゲートとの間に前記絶縁膜が形成された請求項5に記載の不揮発性半導体装置。 - 前記絶縁膜の表面上に形成された他の絶縁膜をさらに備える、請求項5または請求項6に記載の不揮発性半導体装置。

- 半導体基板の主表面上に第1と第2フローティングゲートを形成する工程と、

前記第1と第2フローティングゲート上に第1と第2コントロールゲートを形成する工程と、

前記第1と第2コントロールゲート上に第1と第2絶縁膜を形成し、前記第1絶縁膜と前記第2絶縁膜とを接触させることで、少なくとも前記第1フローティングゲートと前記第2フローティングゲートとの間に空隙部を形成する工程と、

を備えた不揮発性半導体装置の製造方法。 - 前記第1と第2フローティングゲートおよび前記第1と第2コントロールゲートの表面上に第3絶縁膜を形成する工程をさらに備える、請求項8に記載の不揮発性半導体装置の製造方法。

- 前記第1絶縁膜および前記第2絶縁膜の表面上に、他の絶縁膜を形成する工程をさらに、備える、請求項8または請求項9に記載の不揮発性半導体装置の製造方法。

- 半導体基板の主表面上に複数のフローティングゲートを形成する工程と、

前記フローティングゲート間に酸化シリコン膜より誘電率が低く、多孔質の絶縁膜を形成する工程と、

を備えた、不揮発性半導体装置の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005118505A JP2006302950A (ja) | 2005-04-15 | 2005-04-15 | 不揮発性半導体装置および不揮発性半導体装置の製造方法 |

| US11/402,972 US7705392B2 (en) | 2005-04-15 | 2006-04-13 | Nonvolatile semiconductor device and method of manufacturing nonvolatile semiconductor device |

| US12/613,057 US20100044772A1 (en) | 2005-04-15 | 2009-11-05 | Nonvolatile semiconductor device and method of manufacturing nonvolatile semiconductor device |

| US12/727,890 US8211777B2 (en) | 2005-04-15 | 2010-03-19 | Method of manufacturing nonvolatile semiconductor device |

| US13/488,015 US8669172B2 (en) | 2005-04-15 | 2012-06-04 | Method of manufacturing nonvolatile semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005118505A JP2006302950A (ja) | 2005-04-15 | 2005-04-15 | 不揮発性半導体装置および不揮発性半導体装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012005997A Division JP5526162B2 (ja) | 2012-01-16 | 2012-01-16 | 不揮発性半導体装置および不揮発性半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006302950A true JP2006302950A (ja) | 2006-11-02 |

| JP2006302950A5 JP2006302950A5 (ja) | 2008-05-22 |

Family

ID=37107687

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005118505A Pending JP2006302950A (ja) | 2005-04-15 | 2005-04-15 | 不揮発性半導体装置および不揮発性半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (4) | US7705392B2 (ja) |

| JP (1) | JP2006302950A (ja) |

Cited By (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007088283A (ja) * | 2005-09-22 | 2007-04-05 | Renesas Technology Corp | 不揮発性半導体記憶装置と半導体装置および、不揮発性半導体記憶装置の製造方法 |

| KR100843044B1 (ko) | 2007-08-20 | 2008-07-01 | 주식회사 하이닉스반도체 | 반도체 소자의 제조방법 |

| JP2009027161A (ja) * | 2007-07-18 | 2009-02-05 | Hynix Semiconductor Inc | フラッシュメモリ素子の製造方法 |

| JP2009194305A (ja) * | 2008-02-18 | 2009-08-27 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP2009206152A (ja) * | 2008-02-26 | 2009-09-10 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP2010027922A (ja) * | 2008-07-22 | 2010-02-04 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| US7795092B2 (en) | 2007-06-27 | 2010-09-14 | Kabushiki Kaisha Toshiba | Semiconductor device and manufacturing method thereof |

| JP2010225786A (ja) * | 2009-03-23 | 2010-10-07 | Toshiba Corp | 半導体記憶装置及びその半導体記憶装置の製造方法 |

| US7884415B2 (en) | 2008-06-10 | 2011-02-08 | Kabushiki Kaisha Toshiba | Semiconductor memory device having multiple air gaps in interelectrode insulating film |

| US8008704B2 (en) | 2008-02-15 | 2011-08-30 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method of manufacturing the same |

| US20120238089A1 (en) * | 2005-04-15 | 2012-09-20 | Renesas Electronics Corporation | Method of manufacturing nonvolatile semiconductor device |

| US8357966B2 (en) | 2010-03-23 | 2013-01-22 | Kabushiki Kaisha Toshiba | Semiconductor device and method for manufacturing semiconductor device |

| US8563421B2 (en) | 2007-08-06 | 2013-10-22 | Samsung Electronics Co., Ltd. | Method of fabricating semiconductor device |

| US8609507B2 (en) | 2011-05-04 | 2013-12-17 | Hynix Semiconductor Inc. | Semiconductor device and method of manufacturing the same |

| KR20140038824A (ko) * | 2012-09-21 | 2014-03-31 | 삼성전자주식회사 | 반도체 소자 및 그의 제조 방법 |

| US9006815B2 (en) | 2011-02-25 | 2015-04-14 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method for manufacturing the same |

| CN105990324A (zh) * | 2015-02-15 | 2016-10-05 | 华邦电子股份有限公司 | 半导体元件及其制造方法 |

Families Citing this family (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7560344B2 (en) * | 2006-11-15 | 2009-07-14 | Samsung Electronics Co., Ltd. | Semiconductor device having a pair of fins and method of manufacturing the same |

| US7948021B2 (en) | 2007-04-27 | 2011-05-24 | Kabushiki Kaisha Toshiba | Semiconductor memory device and method of fabricating the same |

| JP2009212218A (ja) * | 2008-03-03 | 2009-09-17 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| US7919809B2 (en) * | 2008-07-09 | 2011-04-05 | Sandisk Corporation | Dielectric layer above floating gate for reducing leakage current |

| US7915124B2 (en) * | 2008-07-09 | 2011-03-29 | Sandisk Corporation | Method of forming dielectric layer above floating gate for reducing leakage current |

| US8207036B2 (en) * | 2008-09-30 | 2012-06-26 | Sandisk Technologies Inc. | Method for forming self-aligned dielectric cap above floating gate |

| JP2010283127A (ja) * | 2009-06-04 | 2010-12-16 | Toshiba Corp | 半導体装置およびその製造方法 |

| US8492224B2 (en) * | 2010-06-20 | 2013-07-23 | Sandisk Technologies Inc. | Metal control gate structures and air gap isolation in non-volatile memory |

| US20120007165A1 (en) * | 2010-07-12 | 2012-01-12 | Samsung Electronics Co., Ltd. | Semiconductor devices |

| KR20120015178A (ko) * | 2010-08-11 | 2012-02-21 | 삼성전자주식회사 | 반도체 소자 및 반도체 소자 제조 방법 |

| KR20120027906A (ko) * | 2010-09-14 | 2012-03-22 | 삼성전자주식회사 | 반도체 소자 및 반도체 소자 제조 방법 |

| SG10201408390TA (en) * | 2010-11-18 | 2015-01-29 | Toshiba Kk | Nonvolatile semiconductor memory device and manufacturing method of nonvolatile semiconductor memory device |

| JP5570953B2 (ja) | 2010-11-18 | 2014-08-13 | 株式会社東芝 | 不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法 |

| JP5591668B2 (ja) * | 2010-11-30 | 2014-09-17 | 株式会社東芝 | 不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法 |

| US8575000B2 (en) * | 2011-07-19 | 2013-11-05 | SanDisk Technologies, Inc. | Copper interconnects separated by air gaps and method of making thereof |

| JP2013042068A (ja) * | 2011-08-19 | 2013-02-28 | Toshiba Corp | 不揮発性半導体記憶装置とその製造方法 |

| US9136128B2 (en) | 2011-08-31 | 2015-09-15 | Micron Technology, Inc. | Methods and apparatuses including memory cells with air gaps and other low dielectric constant materials |

| JP2013089859A (ja) * | 2011-10-20 | 2013-05-13 | Toshiba Corp | 半導体装置の製造方法 |

| KR101813513B1 (ko) * | 2011-11-30 | 2018-01-02 | 삼성전자주식회사 | 반도체 소자 및 반도체 소자의 제조 방법 |

| JP5485309B2 (ja) * | 2012-01-30 | 2014-05-07 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP2013197187A (ja) * | 2012-03-16 | 2013-09-30 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP5889118B2 (ja) | 2012-06-13 | 2016-03-22 | 株式会社東芝 | 半導体装置及びその製造方法 |

| TWI464831B (zh) * | 2012-06-27 | 2014-12-11 | Powerchip Technology Corp | 半導體元件的製造方法 |

| JP5796029B2 (ja) | 2013-02-22 | 2015-10-21 | 株式会社東芝 | 半導体装置および半導体装置の製造方法 |

| US9543310B2 (en) | 2014-09-10 | 2017-01-10 | Kabushiki Kaisha Toshiba | Semiconductor storage device having communicated air gaps between adjacent memory cells |

| US9748311B2 (en) * | 2014-11-07 | 2017-08-29 | Micron Technology, Inc. | Cross-point memory and methods for fabrication of same |

| CN107293545B (zh) * | 2016-03-30 | 2020-04-07 | 中芯国际集成电路制造(上海)有限公司 | 半导体存储器件及其制造方法 |

| US10453855B2 (en) | 2017-08-11 | 2019-10-22 | Micron Technology, Inc. | Void formation in charge trap structures |

| US10680006B2 (en) | 2017-08-11 | 2020-06-09 | Micron Technology, Inc. | Charge trap structure with barrier to blocking region |

| US10164009B1 (en) | 2017-08-11 | 2018-12-25 | Micron Technology, Inc. | Memory device including voids between control gates |

| US10446572B2 (en) | 2017-08-11 | 2019-10-15 | Micron Technology, Inc. | Void formation for charge trap structures |

| US10665499B2 (en) * | 2018-06-28 | 2020-05-26 | Intel Corporation | Integrated circuit with airgaps to control capacitance |

| US11450601B2 (en) * | 2019-09-18 | 2022-09-20 | Micron Technology, Inc. | Assemblies comprising memory cells and select gates |

| CN113035713B (zh) * | 2019-12-24 | 2023-12-01 | 华邦电子股份有限公司 | 存储器结构及其制造方法 |

| TWI797467B (zh) * | 2020-08-03 | 2023-04-01 | 華邦電子股份有限公司 | 非揮發性記憶體結構及其製造方法 |

| CN114256252A (zh) * | 2020-09-22 | 2022-03-29 | 华邦电子股份有限公司 | 非易失性存储器结构及其制造方法 |

| US11322623B2 (en) * | 2020-09-29 | 2022-05-03 | Winbond Electronics Corp. | Non-volatile memory structure and method of manufacturing the same |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62188375A (ja) * | 1986-02-14 | 1987-08-17 | Hitachi Ltd | 半導体集積回路装置 |

| JPH03148875A (ja) * | 1989-11-06 | 1991-06-25 | Seiko Epson Corp | 半導体装置 |

| JPH09289209A (ja) * | 1996-04-23 | 1997-11-04 | Toshiba Corp | 半導体装置に使用する絶縁膜 |

| JPH10270575A (ja) * | 1997-03-21 | 1998-10-09 | Toshiba Corp | 不揮発性半導体記憶装置およびその製造方法 |

| JP2003197779A (ja) * | 2001-12-25 | 2003-07-11 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2003332468A (ja) * | 2002-05-09 | 2003-11-21 | Toshiba Corp | 不揮発性半導体記憶装置およびその製造方法 |

| WO2004107352A2 (en) * | 2003-05-21 | 2004-12-09 | Sandisk Corporation | Use of voids between elements in semiconductor structures for isolation |

| JP2004349549A (ja) * | 2003-05-23 | 2004-12-09 | Toshiba Corp | 半導体装置の製造方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5847464A (en) * | 1995-09-27 | 1998-12-08 | Sgs-Thomson Microelectronics, Inc. | Method for forming controlled voids in interlevel dielectric |

| JP2853661B2 (ja) | 1996-06-27 | 1999-02-03 | 日本電気株式会社 | 半導体集積回路装置の製造方法 |

| JP3638778B2 (ja) * | 1997-03-31 | 2005-04-13 | 株式会社ルネサステクノロジ | 半導体集積回路装置およびその製造方法 |

| JP2000100976A (ja) | 1998-09-21 | 2000-04-07 | Matsushita Electronics Industry Corp | 半導体メモリアレイ装置およびその製造方法 |

| KR100286126B1 (ko) * | 1999-02-13 | 2001-03-15 | 윤종용 | 다층의 패시배이션막을 이용한 도전층 사이에 공기 공간을 형성하는 방법 |

| JP4493182B2 (ja) * | 2000-08-23 | 2010-06-30 | 株式会社ルネサステクノロジ | 半導体装置 |

| JP2002280463A (ja) | 2001-03-16 | 2002-09-27 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP3936315B2 (ja) * | 2003-07-04 | 2007-06-27 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| KR100537278B1 (ko) * | 2003-09-05 | 2005-12-19 | 주식회사 하이닉스반도체 | 플래쉬 메모리소자의 제조방법 |

| JP2006302950A (ja) * | 2005-04-15 | 2006-11-02 | Renesas Technology Corp | 不揮発性半導体装置および不揮発性半導体装置の製造方法 |

-

2005

- 2005-04-15 JP JP2005118505A patent/JP2006302950A/ja active Pending

-

2006

- 2006-04-13 US US11/402,972 patent/US7705392B2/en active Active

-

2009

- 2009-11-05 US US12/613,057 patent/US20100044772A1/en not_active Abandoned

-

2010

- 2010-03-19 US US12/727,890 patent/US8211777B2/en active Active

-

2012

- 2012-06-04 US US13/488,015 patent/US8669172B2/en active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62188375A (ja) * | 1986-02-14 | 1987-08-17 | Hitachi Ltd | 半導体集積回路装置 |

| JPH03148875A (ja) * | 1989-11-06 | 1991-06-25 | Seiko Epson Corp | 半導体装置 |

| JPH09289209A (ja) * | 1996-04-23 | 1997-11-04 | Toshiba Corp | 半導体装置に使用する絶縁膜 |

| JPH10270575A (ja) * | 1997-03-21 | 1998-10-09 | Toshiba Corp | 不揮発性半導体記憶装置およびその製造方法 |

| JP2003197779A (ja) * | 2001-12-25 | 2003-07-11 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2003332468A (ja) * | 2002-05-09 | 2003-11-21 | Toshiba Corp | 不揮発性半導体記憶装置およびその製造方法 |

| WO2004107352A2 (en) * | 2003-05-21 | 2004-12-09 | Sandisk Corporation | Use of voids between elements in semiconductor structures for isolation |

| JP2004349549A (ja) * | 2003-05-23 | 2004-12-09 | Toshiba Corp | 半導体装置の製造方法 |

Cited By (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8669172B2 (en) * | 2005-04-15 | 2014-03-11 | Renesas Electronics Corporation | Method of manufacturing nonvolatile semiconductor device |

| US20120238089A1 (en) * | 2005-04-15 | 2012-09-20 | Renesas Electronics Corporation | Method of manufacturing nonvolatile semiconductor device |

| JP4731262B2 (ja) * | 2005-09-22 | 2011-07-20 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置および、不揮発性半導体記憶装置の製造方法 |

| JP2007088283A (ja) * | 2005-09-22 | 2007-04-05 | Renesas Technology Corp | 不揮発性半導体記憶装置と半導体装置および、不揮発性半導体記憶装置の製造方法 |

| US7795092B2 (en) | 2007-06-27 | 2010-09-14 | Kabushiki Kaisha Toshiba | Semiconductor device and manufacturing method thereof |

| KR101010798B1 (ko) * | 2007-07-18 | 2011-01-25 | 주식회사 하이닉스반도체 | 플래시 메모리 소자의 제조 방법 |

| JP2009027161A (ja) * | 2007-07-18 | 2009-02-05 | Hynix Semiconductor Inc | フラッシュメモリ素子の製造方法 |

| KR101356695B1 (ko) * | 2007-08-06 | 2014-01-29 | 삼성전자주식회사 | 반도체 소자의 제조 방법 |

| US8563421B2 (en) | 2007-08-06 | 2013-10-22 | Samsung Electronics Co., Ltd. | Method of fabricating semiconductor device |

| KR100843044B1 (ko) | 2007-08-20 | 2008-07-01 | 주식회사 하이닉스반도체 | 반도체 소자의 제조방법 |

| US8349686B2 (en) | 2008-02-15 | 2013-01-08 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method of manufacturing the same |

| US8008704B2 (en) | 2008-02-15 | 2011-08-30 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method of manufacturing the same |

| JP2009194305A (ja) * | 2008-02-18 | 2009-08-27 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP4703669B2 (ja) * | 2008-02-18 | 2011-06-15 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| JP2009206152A (ja) * | 2008-02-26 | 2009-09-10 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP4729060B2 (ja) * | 2008-02-26 | 2011-07-20 | 株式会社東芝 | 半導体記憶装置の製造方法 |

| US7915156B2 (en) | 2008-02-26 | 2011-03-29 | Kabushiki Kaisha Toshiba | Semiconductor memory device and method for manufacturing the same |

| US7884415B2 (en) | 2008-06-10 | 2011-02-08 | Kabushiki Kaisha Toshiba | Semiconductor memory device having multiple air gaps in interelectrode insulating film |

| US8581325B2 (en) | 2008-07-22 | 2013-11-12 | Kabushiki Kaisha Toshiba | Semiconductor memory device and manufacturing method thereof |

| US8158479B2 (en) | 2008-07-22 | 2012-04-17 | Kabushiki Kaisha Toshiba | Semiconductor memory device and manufacturing method thereof |

| JP2010027922A (ja) * | 2008-07-22 | 2010-02-04 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| US8253188B2 (en) | 2009-03-23 | 2012-08-28 | Kabushiki Kaisha Toshiba | Semiconductor storage device and method for manufacturing the same |

| JP2010225786A (ja) * | 2009-03-23 | 2010-10-07 | Toshiba Corp | 半導体記憶装置及びその半導体記憶装置の製造方法 |

| US8357966B2 (en) | 2010-03-23 | 2013-01-22 | Kabushiki Kaisha Toshiba | Semiconductor device and method for manufacturing semiconductor device |

| US8624314B2 (en) | 2010-03-23 | 2014-01-07 | Kabushiki Kaisha Toshiba | Semiconductor device and method for manufacturing semiconductor device |

| US9006815B2 (en) | 2011-02-25 | 2015-04-14 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method for manufacturing the same |

| US8609507B2 (en) | 2011-05-04 | 2013-12-17 | Hynix Semiconductor Inc. | Semiconductor device and method of manufacturing the same |

| KR20140038824A (ko) * | 2012-09-21 | 2014-03-31 | 삼성전자주식회사 | 반도체 소자 및 그의 제조 방법 |

| KR102054264B1 (ko) * | 2012-09-21 | 2019-12-10 | 삼성전자주식회사 | 반도체 소자 및 그의 제조 방법 |

| CN105990324A (zh) * | 2015-02-15 | 2016-10-05 | 华邦电子股份有限公司 | 半导体元件及其制造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8211777B2 (en) | 2012-07-03 |

| US20120238089A1 (en) | 2012-09-20 |

| US20100190330A1 (en) | 2010-07-29 |

| US7705392B2 (en) | 2010-04-27 |

| US20060231884A1 (en) | 2006-10-19 |

| US8669172B2 (en) | 2014-03-11 |

| US20100044772A1 (en) | 2010-02-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2006302950A (ja) | 不揮発性半導体装置および不揮発性半導体装置の製造方法 | |

| US9905510B2 (en) | Semiconductor memory device and method of manufacturing the same | |

| US7462905B2 (en) | Nonvolatile semiconductor memory device, semiconductor device and method of manufacturing nonvolatile semiconductor memory device | |

| JP5498011B2 (ja) | 不揮発性半導体記憶装置 | |

| KR20110058631A (ko) | 반도체 메모리 장치 | |

| JP5425378B2 (ja) | 半導体装置の製造方法 | |

| KR100533302B1 (ko) | 불휘발성 반도체 기억 장치 및 그 제조 방법 | |

| JP2008091614A (ja) | 半導体装置およびその製造方法 | |

| JPWO2007013155A1 (ja) | 半導体装置およびその製造方法 | |

| KR100927927B1 (ko) | 반도체 장치, 불휘발성 반도체 기억 장치 및 그 제조 방법 | |

| JP2008135715A (ja) | 不揮発性メモリ素子及びその製造方法 | |

| JP2011198963A (ja) | 不揮発性半導体記憶装置及びその製造方法 | |

| US9842766B2 (en) | Semiconductor device and method for fabricating semiconductor device | |

| JP2013042068A (ja) | 不揮発性半導体記憶装置とその製造方法 | |

| JP5526162B2 (ja) | 不揮発性半導体装置および不揮発性半導体装置の製造方法 | |

| KR100794085B1 (ko) | 플래시 메모리 소자의 제조 방법 | |

| US7602005B2 (en) | Memory devices including spacer-shaped electrodes on pedestals and methods of manufacturing the same | |

| US8502298B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP2006310564A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| KR100622030B1 (ko) | 비휘발성 메모리 소자의 제조방법 | |

| JP2015056601A (ja) | 半導体装置およびその製造方法 | |

| JP5363004B2 (ja) | 半導体装置の製造方法 | |

| JP2009164624A (ja) | 半導体装置の製造方法 | |

| JP2005294392A (ja) | 不揮発性半導体記憶装置 | |

| JP2009224426A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080403 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080403 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100526 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100615 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100610 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100806 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101026 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110125 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20111018 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120116 |