具体实施方式

下面,参照附图详细说明本发明的非易失性半导体存储器。

1.前提

首先,为了容易理解以下的说明,把前提条件规定如下。可是,该前提条件是为了容易理解说明而设定的,本发明在该前提条件以外的条件时也是成立的。

本发明是以在一个存储单元中存储n(n是2以上的自然数)位数据即2n值的多值闪存为对象,但是在以下的实施例中,作为代表例,说明4值NAND型闪存。

在存储单元中存储着4种数据“00”、“01”、“10”、“11”。存储单元的阈值电压为最低的状态,例如阈值电压为负、属于第一阈值带的状态为存储了数据“11”的状态;存储单元的阈值电压为第二低的状态,例如阈值电压为正、属于第二阈值带的状态为存储了数据“10”的状态;存储单元的阈值电压为第三低的状态,例如阈值电压为正、属于第三阈值带的状态为存储了数据“0”的状态;存储单元的阈值电压为最高的状态,例如阈值电压为正、属于第四阈值带的状态为存储了数据“01”的状态。

此外,因为在存储单元中存储了4种数据即4值数据,所以例如在数据编程/读出时需要对逻辑低位页数据的编程/读出动作和对逻辑高位页数据的编程/读出动作。这里,数据“**”中,右侧的*为逻辑低位页数据,左侧的*为逻辑高位页数据。

此外,关于存储单元,存储着数据“11”的状态为删除状态,存储着数据“10”、“00”、“01”的状态为写入状态。

2.概要

(1)全体结构例

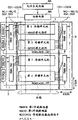

图1表示关于本发明一例的4值NAND单元型闪存的主要部分。

1是存储单元阵列。存储单元阵列1例如具有由串联的多个存储单元和连接在其两端上各一个的两个选择晶体管构成的NAND型单元部件。后面将描述存储单元阵列1的电路例和构造例。

数据电路2包含多个存储电路。后面将就数据电路2的电路例加以说明。这里,简单说明数据电路2的功能。

数据电路2在写入时暂时存储2位(4值)的写入数据,在读出时暂时存储2位(4值)的读出数据。因此,对于连接在成为写入/读出动作对象的选择的存储单元上的一条位线,最少设置两个存储电路。两个存储电路中的一个存储逻辑低位页数据,另一个存储逻辑高位页数据。

字线控制电路3包含行地址解码器和字线驱动器。字线控制电路3根据工作模式(写入、删除、读出等)和行地址信号指定的地址,控制存储单元阵列1内的多个字线电位。后面将详细描述字线控制电路3的电路例。

列解码器4根据列地址信号选择存储单元阵列1的列。

编程时,写入数据经由数据输入输出缓存器7和I/O读出放大器6输入到属于选择的列的数据电路2内的存储电路内。此外,在读出时,读出数据暂时存储在属于选择的列的数据电路2内的存储电路内,然后经由I/O读出放大器6和数据输入输出缓存器7向存储器片11的外部输出。

行地址信号经由地址缓存器5输入到字线控制电路3中。列地址信号经由地址缓存器5输入到列解码器4中。

势阱/源线电位控制电路8根据工作模式(写入、删除、读出等)分别控制与构成存储单元阵列1的多个块对应的多个势阱区(例如,由n势阱和p势阱构成的双势阱区)的电位和源线电位。

电位生成电路(升压电路)9A,例如,在写入时产生写入电位(例如约20V)Vpp、传输电位(例如约10V)Vpass等。这些电位Vpp、Vpass通过切换电路9B分配给从构成存储单元阵列1的多个块中选择出的块内的多条字线。

此外,电位生成电路9A,例如,在删除时产生删除电位(例如约20V)VppE,该电位VppE提供给与构成存储单元阵列1的多个块中一个或两个以上选择的块对应的一个或两个以上的势阱区(n势阱和p势阱)。

汇总检测电路(batch detection circuit)10在编程时检验给定数据是否正确写入到存储单元中,在删除时检验是否准确删除了存储单元的数据。

命令接口电路12根据由与存储器片11不同的芯片(例如主微机)生成的控制信号判断输入到数据输入输出缓存器7中的数据是否是从主微机提供的命令数据。当输入到数据输入输出缓存器7中的数据是命令数据时,命令接口电路12向状态机13(控制电路13)传输命令数据。

状态机13根据命令数据决定闪存的工作模式(写入、删除、读出等),并且按照该工作模式控制闪存的全体动作,具体而言,控制数据电路2、字线控制电路3、列解码器4、地址缓存器5、I/O读出放大器6、数据输入输出缓存器7、势阱/源线电位控制电路8、电位生成电路9A、切换电路9B和汇总检测电路10的动作。

(2)存储单元阵列的结构例

图2表示了存储单元阵列的结构例。图3是图2所示的多个块中的一个BLOCKi的电路例。

存储单元阵列1由多个(在本例中,1024个)块BLOCK0~BLOCK1023构成。多个块BLOCK0~BLOCK1023并排配置在Y方向上。块意味着删除的最小单位,即一次能删除的最小存储单元数。

一个块BLOCKi由排列在X方向上的多个(在本例中为8512个)NAND单元部件U构成。一个NAND单元部件U由串联的4个存储单元M1、M2、M3、M4构成的NAND列、连接在NAND列的一端的选择栅晶体管S1、连接在NAND列的另一端上的选择栅晶体管S2构成。

在本例中,NAND列由4个存储单元M1、M2、M3、M4构成,但是由一个或两个以上的存储单元构成即可,并不特别限定于4个。

选择栅晶体管S1连接在位线BLek或位线BloK上(k=0、1…4255),选择栅晶体管S2连接在源线C-source上。

字线(控制栅线)WL0-i、WL1-i、WL2-i、WL3-i在X方向延伸,共同连接在X方向的多个存储单元上。选择栅线SGD-i在X方向延伸,共同连接在X方向的多个选择栅晶体管S1上。选择栅线SGS-i也在X方向延伸,共同连接在X方向的多个选择栅晶体管S2上。

在本例中,在写入/读出动作时,从块BLOCKi的一端一侧开始数的位于第偶数条上的多条位线BLe0、BLe1、…BLe4255、与从该一端一侧开始计算的位于第奇数条(odd)的多条位线BLo0、BLo1、BLo4255彼此独立驱动。不过,位线是从0开始计算的。

即,对于连接在一条字线,例如字线WL3-i上的8512个存储单元中的连接在位于第偶数条的多条位线BLe0、BLe1、…BLe4255上的4256个存储单元(用△表示),同时执行写入/读出动作。此外,对于连接在字线WL3-i上的8512个存储单元中的连接在位于第奇数条的多条位线BLo0、BLo1、…BLo4255上的4256个存储单元(用○表示),同时执行写入/读出动作。

当1个存储单元存储1位数据时,位于一条字线,例如字线WL3-i与第偶数条的多条位线BLe0、BLe1、…BLe4255的交点上的4256个存储单元(用△表示)构成称作页的单位。同样,位于字线WL3-i与第奇数条的多条位线BLo0、BLo1、…BLo4255的交点上的4256个存储单元(用○表示)也构成称作页的单位。

此外,当象本例那样一个存储单元存储2位数据时,4256个存储单元(用△表示)存储2页部分的数据,4256个存储单元(用○表示)也存储2页部分的数据。

(3)器件构造例

①势阱构造例

图4表示NAND型闪存的势阱构造例。

在p型硅衬底(p-sub)11-1内形成由n型势阱区(Cell n-well)11-2和p型势阱区(Cell p-well)11-3构成的所谓的双势阱区、n型势阱区11-4以及p型势阱区11-5。

双势阱区形成在存储单元阵列部分,n型势阱区11-4和p型势阱区11-5形成在外围电路部分中。

存储单元由n沟道MOS晶体管构成,配置在p型势阱区11-3内。n型势阱区11-2和p型势阱区11-3设定为相同电位。

外加了比电源电压还高电压的高压n沟道MOS晶体管形成在P型硅衬底11-1内。外加了电源电压的低电压p沟道MOS晶体管形成在n型势阱区11-4,外加了电源电压的低电压n沟道MOS晶体管形成在p型势阱区11-5内。

②单元阵列构造例

图5表示NAND型闪存的存储单元阵列部分的Y方向剖面构造的例子。

在p型硅衬底11-1内形成由n型势阱区11-2和p型势阱区11-3构成的双势阱区。

串联的4个存储单元M1、M2、M3、M4配置在p型势阱区11-3内。4个存储单M1、M2、M3、M4分别由N沟道MOS晶体管构成,并且具有由浮栅电极FG和控制栅电极WL0-i、WL1-i、WL2-i、WL3-i构成的层叠栅构造。

在由串联的存储单元M1、M2、M3、M4构成的NAND列的一端连接着选择栅晶体管S1,在其另一端连接着选择栅晶体管S2。选择栅晶体管S1、S2由N沟道MOS晶体管构成,具有与存储单元M1、M2、M3、M4近似的构造,即二重结构的选择栅线SGS-i、SGD-i。

NAND单元部件的一端,即选择栅晶体管S1的扩散层(漏极扩散层)14经由接触插头CB1连接在第一金属布线层M0上。此外,第一金属布线层M0经由转接插头V1连接在作为位线BL的第二金属布线层M1上。位线BL连接在数据电路上。

NAND单元部件的另一端,即选择栅晶体管S2的扩散层(源极扩散层)15经由接触插头CB2连接在作为源线C-source的第一金属布线层M0上。源线C-source连接在源极电位控制电路上。

n型势阱区11-2经由n型扩散层16连接在C-p-well电位设定线18上,p型势阱区11-3经由p型扩散层17连接在C-p-well电位设定线18上。即n型势阱区11-2和p型势阱区11-3设定为相同电位。C-p-well电位设定线18连接在势阱电位控制电路上。

须指出的是,浮栅电极FG、控制栅电极WL0-i、WL1-i、WL2-i、WL3-i、选择栅线SGS-i、SGD-i,例如,由包含杂质的导电性多晶硅构成。此外,第一和第二金属布线层M0、M1例如由铝、铜、它们的合金等构成。

图6表示存储单元的X方向的剖面构造,图7表示选择栅晶体管的X方向的剖面构造。

X方向的多个存储单元(FG+WL)由STI(浅沟道隔离)构造的元件隔离层19彼此电隔离。在p型势阱区11-3上隔着非常薄的隧道氧化膜20配置了浮栅电极FG。在浮栅电极FG上隔着ONO(氧化物/氮化物/氧化物)膜21配置了控制栅电极WL。

选择栅线SGS/SGD为二重构造。下方的选择栅线SGS/SGD和上方的选择栅线SGS/SGD在存储单元阵列的端部彼此电连接,并且在存储单元阵列内,每隔一定间隔例如512条位线,彼此电连接。

(4)汇总检测电路的结构例

图8表示汇总检测电路的结构例。

汇总检测电路10具有在检验读出后对选择的全部存储单元调查是否准确进行了写入或删除的功能(程序/删除完成检测)。

在本例中,如存储单元阵列的结构例所述,在写入/读出动作时,以彼此独立驱动第偶数条的多条位线和第奇数条的多条位线为前提。因此,对于由第偶数条的1条位线和第奇数条的1条位线构成的合计2条位线设置有一个子数据电路。

具体而言,因为存在8512条位线BLek、BLok(k=0,1,…4255),所以数据电路2由4256个子数据电路构成。须指出的是,后面将就数据电路2内的各子数据电路的结构例加以说明。

在本例中,只表示4256个子数据电路的8个子数据电路REG1-0、REGR1-1、REGR1-2、REGR1-3、REGR2-0、REGR2-1、REGR2-2、REGR2-3。

子数据电路REGR1-y连接在2条位线BLej+y、BLoj+y上,并且连接在I/O线对IOj+y、nIOj+y上。此外,子数据电路REGR2-y连接在2条位线BLej+y+4、BLoj+y+4上,并且连接在I/O线对IOj+y+4、nIOj+y+4上。只是,y=0、1、2、3。

第一到第四子数据电路REGR1-0、REGR1-1、REGR1-2、REGR1-3的输出节点RCD1公共连接,该连接节点RCD1连接在P沟道MOS晶体管TP2的栅极上。同样,第五到第八子数据电路REGR2-0、REGR2-1、REGR2-2、REGR2-3的输出节点RCD2也公共连接,该连接节点RCD2连接在P沟道MOS晶体管TP3的栅极上。

P沟道MOS晶体管TP13、TP14具有在编程/删除完成的检验时,根据控制信号COMHn对节点RCD1、RCD2预充电的功能。即使控制信号COMHn为“L”,把节点RCD1、RCD2设定为电源电位Vdd后,使控制信号COMHn为“L”,使节点RCD1、RCD2为浮置状态。这时,P沟道MOS晶体管TP2、TP3变为断开状态。

N沟道MOS晶体管TN15具有在编程/删除完成的检验时,把节点NCOM设定为接地电位Vss后,成为浮置状态的功能。N沟道MOS晶体管TN15由控制信号NCOML控制。

在编程/删除完成的检验时,与未充分进行写入/删除的存储单元对应的子数据电路使公共节点RCD1或公共节点RCD2的电位水平从“H”下降到“L”。

因此,当至少存在一个未充分进行写入/删除的存储单元时,P沟道MOS晶体管TP2或P沟道MOS晶体管TP3变为导通状态,节点NCOM从“L”变为“H”,FLAG变为“L”。

而当对于全部存储单元充分进行了写入/删除时,全部的子数据电路把公共节点RCD1、公共节点RCD2的电位水平维持在“H”电平。因此,节点NCOM保持“L”,FLAG变为“H”。

这样,通过检测FLAG的电位水平,对于选择的全部存储单元,能调查是否准确进行了写入/删除。

在本例中,把8个子数据电路汇总为一个,对每8个子数据电路进行编程/删除完成的检验,即FRAG电压电平的检测。

把8个子数据电路汇总为一个是为了以与这8个子数据电路对应的列单位进行基于冗余电路的存储单元的置换。即如果切断熔丝元件(用虚线包围的部分),则连接在这8个子数据电路上的存储单元总是成为未选择状态,代替它,选择了冗余区的预备存储单元。

因此,当以与n(n为自然数)个子数据电路对应的n列单位进行基于冗余电路的存储单元置换时,把n个子数据电路汇总为一个。

须指出的是,FRAG变为与全部列对应的公共节点。例如,当数据电路2由4256个子数据电路构成时,如果以8个子数据电路作为冗余电路置换的一个电位,则在芯片内存在532个图8所示的电路。而且,这532个电路连接在公共节点FRAG上。

(5)数据电路的结构例

图9表示数据电路内的子数据电路的结构例。

在本例中,数据电路由多个(例如4256个)子数据电路构成,各子数据电路具有图9所示的结构。

子数据电路REGR具有四个数据存储部分DS1、DS2、DS3、DS4。使用这些数据存储部分DS1、DS2、DS3、DS4对选择的一个存储单元执行2位数据的读出动作和编程动作。在编程动作中包含写入动作和检验动作等。

此外,对由第偶数条的一条位线和第奇数条的一条位线构成的合计2条位线设置有一个子数据电路。第偶数条的位线BLek经由N沟道MOS晶体管Qn1连接在子数据电路REGR上,第奇数条位线BLok经由N沟道MOS晶体管Qn2连接在子数据电路REGR上。

控制信号BLSe为“H”、控制信号BLSo为“L”时,因为N沟道MOS晶体管Qn1变为导通状态,所以第偶数条的位线BLek电连接在子数据电路REGR上。此外,控制信号BLSe为“L”、控制信号BLSo为“H”时,N沟道MOS晶体管Qn2变为导通状态,所以第奇数条位线BLok电连接在子数据电路REGR上。

须指出的是,控制信号BLSe公共输入到连接在第偶数条的位线BLek上的MOS晶体管Qn1中,控制信号BLSo输入到连接在第奇数条位线BLok上的MOS晶体管Qn2中。

图10表示图9的子数据电路的电路例。

在本例中,与图9相对应地表示1列(与2条位线BLek、BLok对应)的子数据电路。

子数据电路REGR具有四个数据存储部分DS1、DS2、DS3、DS4。

数据存储部分DS1由耗尽型N沟道MOS电容器C1构成,数据存储部分DS2由N沟道MOS晶体管Qn8构成。数据存储部分DS3由具有时钟同步式倒相器CI1、CI2的CMOS双稳态多谐振荡器电路构成,数据存储部分DS4由具有时钟同步式倒相器CI3、CI4的CMOS双稳态多谐振荡器电路构成。

MOS电容器C1的一端经由N沟道MOS晶体管Qn5、Qn1、Qn2连接在位线BLek、BLok上,另一端连接在接地点Vss上。MOS晶体管Qn5是进行位线Qn1、Qn2一侧的节点N1和MOS电容器C1一侧的节点N2的电连接/切断的箝位晶体管。

当控制信号BLCLAMP为“H”时,MOS晶体管Qn5变为导通状态,例如第偶数条位线BLek被电连接在MOS电容器C1的一端上。这时,控制信号BLSe设定为“H”,控制信号BLSo设定为“L”。此外,这时控制信号BIASe设定为“L”,控制信号BIASo设定为“H”,偏压电位(例如接地电位)BLCRL提供给第奇数条位线BLok。

此外,当第奇数条位线BLok电连接在MOS电容器C1的一端上时,控制信号BLSe设定为“L”,控制信号BLSo设定为“H”。此外,这时控制信号BIASe设定为“H”,控制信号BIASo设定为“L”,偏压电位(例如接地电位)BLCRL提供给第偶数条位线BLek。

当控制信号BLCLAMP为“L”时,MOS晶体管Qn5变为断开状态,所以位线Qn1、Qn2一侧的节点N1和MOS电容器C1一侧的节点N2电切断。

N沟道MOS晶体管Qn6连接在MOS电容器C1的一端上。MOS晶体管Qn6是用于把MOS电容器C1的一端充电为预充电电位VPRE的元件。控制信号BLPRE为“H”时,MOS电容器C1的一端充电为预充电电位VPRE。

N沟道MOS晶体管Qn8经由N沟道MOS晶体管Qn7连接在MOS电容器C1的一端上。控制信号REG为“H”时,即MOS晶体管Qn7为导通状态时,MOS晶体管Qn8根据存储在数据存储部分DS2中的数据值强制使MOS电容器C1的一端的电位为VREG。

例如,存储在数据存储部分DS2中的数据为“1”,即MOS晶体管的栅极电平为“H”时,如果控制信号REG变为“H”,则MOS电容器C1的一端强制设定为VREG。此外,存储在数据存储部分DS2中的数据为“0”,即MOS晶体管的栅极电平为“L”时,MOS电容器C1的一端的电位不被VREG影响。

如上所述,数据存储部分DS3、DS4都由CMOS双稳态多谐振荡器电路构成。

N沟道MOS晶体管Qn11是用于补偿数据存储部分DS3内的CMOS双稳态多谐振荡器电路的两个输入端子,即时钟同步式倒相器CI1、CI2的输入端子的电位的元件。此外,N沟道MOS晶体管Qn13是用于补偿数据存储部分DS4内的CMOS双稳态多谐振荡器电路的两个输入端子,即时钟同步式倒相器CI3、CI4的输入端子的电位的元件。

MOS晶体管Qn11由控制信号EQ1控制,MOS晶体管Qn13由控制信号EQ2控制。

时钟同步式倒相器CI1与时钟信号SEN1、SEN1n同步工作,时钟同步式倒相器CI2与时钟信号LAT1、LATIn同步工作,时钟同步式倒相器CI3与时钟信号LAT2、LAT2n同步工作,时钟同步式倒相器CI4与时钟信号SEN2、SEN2n同步工作。

须指出的是,信号“***n”意味着把信号“***”的电平倒相的倒相信号。此外,作为时钟同步式倒相器CI1、CI2、CI3、CI4的结构的例子,可如图11所示。

图11的时钟同步式倒相器当时钟信号CLK为“H”、时钟信号CLKn为“L”时,作为CMOS倒相器工作。当时钟信号CLK为“L”、时钟信号CLKn为“H”时,输入信号IN和输出信号OUT变为无关。

数据存储部分DS1和数据存储部分DS3之间即CMOS电容C1的一端(节点N2)和时钟同步式倒相器CI1的输入端子(节点N3)之间连接有作为开关元件的N沟道MOS晶体管Qn10。MOS晶体管Qn10由控制信号BLC1控制,用于执行数据存储部分DS1和数据存储部分DS3之间的数据传输。

在数据存储部分DS2和数据存储部分DS3之间,即N沟道MOS晶体管Qn8的栅极和时钟同步式倒相器CI1输入端子之间,连接有作为开关元件的N沟道MOS晶体管Qn9。MOS晶体管Qn9由控制信号DTG控制,用于把存储在数据存储部分DS3中的数据传输给数据存储部分DS2。

在数据存储部分DS1和数据存储部分DS4之间,即CMOS电容器C1的一端(节点N2)和时钟同步式倒相器CI4的输入端子(节点N4)之间,连接有作为开关元件的N沟道MOS晶体管Qn12。MOS晶体管Qn12由控制信号BLC2控制,用于执行数据存储部分DS1和数据存储部分DS4之间的数据传输。

N沟道MOS晶体管Qn14是用于把数据存储部分DS4的数据复位的元件。例如在写入动作时,MOS晶体管Qn14在写入数据输入到数据存储部分DS4之前,把数据存储部分DS4的状态设定为“1”-数据保持的状态,即把节点N4设定为“H”的状态。

具体而言,如果控制信号PRST变为“H”,则时钟同步式倒相器CI4的输出端子变为“L”,节点N4变为“H”。

数据存储部分DS4经由作为列选择开关的N沟道MOS晶体管Qn15、Qn16连接在I/O线(数据线)IO、nIO上。

在由列选择信号选择的列中,因为列选择信号CSLk(K=0,1,…4255)变为“H”,所以选择的列内的数据存储部分DS4和I/O线IO、nIO电连接。

N沟道MOS晶体管Qn17是用于根据存储在数据存储部分DS3中的数据决定公共节点PCD的电平的元件。

例如,当“0”-编程时,把数据“0”存储在数据存储部分DS3中。即因为节点N4为“L”、节点N5为“H”状态,所以N沟道MOS晶体管Qn17变为导通状态,使公共节点PCD的电平为“L”。当检验读出时,如果准确地在存储单元中写有数据“0”,则读出数据变为“1”,所以在数据存储部分DS4中存储数据“1”。即因为节点N4变为“H”,节点N5变为“L”状态,所以N沟道MOS晶体管Qn17变为断开状态,使公共节点PCD的电平为“H”。

后面将就详细动作加以说明。

在上述的说明中,关于数据存在有“0”和“1”,关于节点的电平存在有“L”和“H”,但是两者的关系为“0”相当于“L”,“1”相当于“H”。

此外,在本例中,在1列内配置有2条位线BLek、BLok,在这2条位线BLek、BLok上连接着一个子数据电路。象这样在一个子数据电路上连接2条位线BLek、BLok的理由在于:①在读出时,防止彼此相邻的位线间产生电容耦合引起的噪声(采用屏蔽位线读出方法);②实现减少数据电路数,达到缩小芯片面积等目的。

(6)字线控制电路的结构例。

图12表示字线控制电路的结构例。

存储单元阵列1由配置在Y方向上的多个存储单元块构成。各存储单元块具有配置在X方向上的多个NAND单元部件。关于存储单元阵列和NAND单元部件的电路例,如图3所示。

只是在本例中,1块内的字线WL1、…WL16的数以16条为前提,与上述的例子(图3)不同。可是,这点并不是重要的点,所以就这样进行说明。

在本例中,对应于一个存储单元块,设置有一个行地址解码器和一个字线驱动器。

例如,第一存储单元块内的字线WL1、…WL16和选择栅线SG1、SG2连接在第一字线驱动器RMAIN1上,第一字线驱动器RMAIN1接收决定第一存储单元块的选择/未选择的第一行地址解码器RADD1的输出信号(解码结果)。

这样,第i(i=1,2,…)存储单元块内的字线WL1、…WL16和选择栅线SG1、SG2连接在第i字线驱动器RMAINi上,第i字线驱动器RMAINi接收决定第i存储单元块的选择/未选择的第i行地址解码器RADDi的输出信号(解码结果)。

这里,在本例子中,字线驱动器配置在存储单元阵列1的两侧(X方向的两个端部)。

具体而言,与第奇数个存储单元阵列块对应的字线驱动器RMAIN1、RMAIN3、…配置在存储单元阵列1的X方向的两个端部的一方(左侧),与第偶数个存储单元阵列块对应的字线驱动器RMAIN2、RMAIN4、…配置在存储单元阵列1的X方向的两个端部的另一方(右侧)。

这样通过把字线驱动器RMAINi配置在存储单元阵列1的两侧,能使字线驱动器RMAINi的设计变得容易(或布局的自由度增大)。即,在本例的情况下,一个字线驱动器在Y方向上能确保两个存储单元块的布局空间。

此外,一个存储单元块内的字线WL1、…WL16和选择栅线SG1、SG2通过与该存储单元块对应的字线驱动器总从存储单元阵列1的一方一侧(或另一方一侧)驱动,所以关于选择的块内的给定的一个NAND单元部件内的存储单元和选择晶体管,不产生提供驱动信号的定时的偏离。

而行地址解码器RADDi(i=1,2,…)只配置在存储单元阵列1的X方向的两个端部中的一方(一侧)。这时,可以只在存储单元阵列1的一侧配置用于向行地址解码器RADDi供给行地址信号的信号线(地址总线),所以能减少地址总线的面积,结果能对芯片面积的减小有贡献。

即假设与字线驱动器RMAINi同样在存储单元阵列1的X方向的两个端部分别配置行地址解码器RADDi,则也必须在存储单元阵列1的X方向的两个端部分别配置地址总线,对于芯片面积的减小是不利的。

只在存储单元阵列1的X方向的两个端部中的一方(一侧)配置行地址解码器RADDi的结果在本例中是信号线22配置在存储单元阵列1上。信号线22用于把与第偶数个存储单元阵列块对应的行地址解码器RADD2、RADD4、…的输出信号(解码结果)RDECADS提供给字线驱动器RMAIN2、RMAIN4、…。

在通常动作时,把信号RDECADS传输给该信号线22。因此,在通常动作时,有必要使该信号线22的电位对存储单元的动作不产生坏影响。须指出的是,后面将描述使信号线22的电位对存储单元的动作不产生坏影响的行地址解码器RADDi和字线驱动器RMAINi。

电位生成电路9A具有升压电路(充电泵电路),例如生成写入动作时使用的写入电位Vpp和传输电位Vpass。电位生成电路9A连接在切换电路9B上。切换电路9B具有把写入电位Vpp、传输电位Vpass、芯片内电源电位Vdd、接地电位Vss等电位分配给与字线WL1、…WL16对应的信号线CG1、…CG16的功能。

信号线CG1、…CG16连接在字线驱动器RMAINi上。即信号线CG1、…CG16经由字线驱动器RMAINi内的电位传输用晶体管HNt1、HNt2、…HNt16(后面描述)连接在WL1、…WL16上。

(7)行地址解码器和字线驱动器的电路例

图13表示与第奇数个存储单元块对应设置的行地址解码器的主要部分。

该行地址解码器RADD1正确地作为块解码器起作用。即例如当选择了第一存储单元块时,行地址信号AROWi、AROWj的全体变为“H”,输出信号RDECAD变为“H”。

图14表示与第奇数个存储单元块对应设置的字线驱动器的主要部分。

字线驱动器RMAIN1的主要构成要素是高电压开关电路26和传输用晶体管HN5、HN6、HNt1、…HNt16。

高电压开关电路26具有由MOS电容器DHN4和MOS晶体管IHN1构成的第一升压部件、由MOS电容器DHN5和MOS晶体管IHN2构成的第二升压部件。

MOS晶体管HN3的栅极连接在MOS晶体管IHN1、IHN2的连接节点B上。这时,MOS晶体管HN3的栅极和源极的电位电平维持反相,与时钟信号Owc同步,各节点A、B、TransferG1的电位渐渐上升,所以升压效率提高。

高电压开关电路26在行地址解码器RADD1的输出信号RDECAD为“H”时,变为工作状态。即当输出信号RDECAD为“H”时,NAND电路NAND1的输出信号成为与时钟信号Owc反相的时钟信号。NAND电路NAND1的输出信号外加在MOS电容器DHN4、DHN5的一端。

结果,升压电位外加在传输用晶体管HNt5、HNt6、…HNt16的栅极上,传输用晶体管HN5、HN6、HNt1…HNt16变为导通状态。

当行地址解码器RADD1的输出信号RDECAD为“H”时,MOS晶体管HN7、HN8变为断开状态。这时,信号线SGD、SGS变为芯片内电源电位Vdd,该Vdd经由传输用MOS晶体管HN5、HN6提供给选择栅线SG1、SG2。

此外,信号线CG1、CG2、…CG16由切换电路9B(参照图1)按照各工作模式设定到给定电位。而且,信号线CG1、CG2、…CG16的电位经由传输用MOS 晶体管HNt1…HNt16提供给字线WL1、WL2、…WL16。

图15表示与第偶数个存储单元块对应设置的行地址解码器的主要部分。

行地址解码器RADD2包含与图13的行地址解码器RADD1相同的电路。即用虚线X1包围的部分的电路与图13的行地址解码器RADD1相同。须指出的是,在图15中,对于与图13相同的部分采用了相同的符号。

该行地址解码器RADD2具有倒相器14、时钟控制式倒相器CINV3、CINV和耗尽型高电压N沟道MOS晶体管DHN6、DHN7。

时钟控制式倒相器CINV4具有下列功能:在删除时使与选择的存储单元块对应的行地址解码器的输出信号RDECADS(图12的信号线22的电位)为接地电位Vss,使与未选择的存储单元块对应的行地址解码器的输出信号RDECADS为芯片内电源电压Vdd。

MOS晶体管DHN6具有使信号线22(参照图12)与后面描述的图16的晶体管DHN9成为浮置状态的功能。

在删除时,在选择的存储单元块中,信号RDECADS1变为“H(Vdd)”,在未选择的存储单元块中,信号RDECADS1变为“L(Vss)”。

假如把该信号RDECADS1提供给存储单元阵列上的信号线22(参照图12),则在未选择的存储单元块中,存储单元阵列上的信号线22(参照图12)变为“L(Vss)”。

这时,由于单元势阱和字线的电容耦合,向单元势阱提供了删除电位Vera时,如果要使未选择的存储单元块内的字线的电位上升,则由于为接地电位Vss的信号线22(图12)的影响,字线的电位不充分上升。

在本例中,因为设置有时钟控制式倒相器CINV4,所以在删除时选择的存储单元块中,输出信号RDECADS变为“L(Vss)”,在未选择的存储单元块中,信号RDECADS变为“H(Vdd)”。

即在未选择的存储单元块中,存储单元阵列上的信号线22(参照图12)变为“H(Vdd)”,并且由于MOS晶体管DHN6和MOS晶体管DHN9(图16)的截止,变为浮置状态。

因此,由于单元势阱和字线的电容耦合,当使未选择的存储单元块内的字线的电位上升,为芯片内电源电位Vdd的信号线22(图12)的影响减小,字线的电位充分上升。

图16表示与第偶数个存储单元块对应设置的字线驱动器的主要部分。

关于字线驱动器RMAIN2的主要构成要素中的高电压开关电路26和传输用晶体管HN5、HN6、HNt1…HNt16,与图14所示的字线驱动器RMAIN1相同。即用虚线X2包围的部分的电路几乎与图14的行地址解码器RADD1几乎相同。须指出的是,对于与图14相同的部分采用了相同的符号。

字线驱动器RMAIN2具有时钟控制式倒相器CINV5、CINV6、CINV7、耗尽型高电压N沟道MOS晶体管DHN8、DHN9和增强型P沟道MOS晶体管TP6、TP7。

时钟控制式倒相器CINV7具有以下功能:在删除时使与选择的存储单元块对应的行地址解码器的输出信号RDECADS(图12的信号线22的电位)从接地电位Vss回到芯片内电源电位Vdd,使与未选择的存储单元块对应的行地址解码器的输出信号RDECADS从芯片内电源电位Vdd回到接地电位Vss后,作为信号RDECADS2提供给虚线X2内的电路。

MOS晶体管DHN9具有使信号线22(参照图12)与图15的MOS晶体管DHN6一起变为浮置状态的功能。

这样,图15的行地址解码器RADD2内的倒相器I4、时钟控制式倒相器CINV3、CINV4和耗尽型高电压N沟道MOS晶体管DHN6、DHN7、与图16的字线驱动器RMAIN2内的时钟控制式倒相器CINV5、CINV6、CINV7、耗尽型高电压N沟道MOS晶体管DHN8、DHN9和增强型P沟道MOS晶体管TP6、TP7为了实现统一目的,成对使用。

须指出的是,在图13~图16中,向这些电路提供了Vdd(比外部电源电位Vcc还低的芯片内电源电位)作为电源电位,但是也可以代之以提供外部电源电位Vcc。

(8)关于信号线22的电位电平

下面说明在各工作模式中,信号线22(参照图12)的电位如何变化。须指出的是,这里,只说明信号线22的电位电平。

在本例中,信号线22(参照图12)和与第偶数个存储单元块对应的行地址解码器(图15)和字线驱动器连接(图16)。因此,下面参照图15和图16说明在信号线22(参照图12)中传输的字线驱动器选择信号RDECADS的电位水平。

行地址解码器RADD2的输出信号RDECADS的电位电平根据工作模式而不同。

在删除动作以外的动作(写入、读出、检验读出)中,分别把ROWERASE1B、ROWPROG1、ROWERASE2B、ROWERASE3n、ROWGATE设定为电源电位Vdd(比外部电源电位Vcc还低的芯片内电源电位。可是,也可以是外部电源电位Vcc),把ROWERASE1、ROWPROG1B、ROWERASE2分别设定为接地电位Vss。

这时,时钟控制式倒相器CINV3、CINV4、CINV5、CINV6变为工作状态,时钟控制式倒相器CINV4、CINV7变为非工作状态。此外,MOS晶体管TP6变为断开状态。

在选择的存储单元块中,由虚线X1包围的部分的输出信号RDECADS1变为“H”,即芯片内电源电位Vdd,行地址解码器RADD2的输出信号RDECADS也变为“H”,即芯片内电源电位Vdd。

而在未选择的存储单元块中,由虚线X1包围的部分的输出信号RDECADS1变为“L”,即接地电位Vss,行地址解码器RADD2的输出信号RDECADS也变为“L”,即接地电位Vss。

因此,在删除动作以外的动作中,配置在未选择的存储单元块内的存储单元阵列上的信号线22(参照图12)变为接地电位Vss,未选择的存储单元块内的选择栅线SG1、SG2也变为接地电位Vss,这些信号线22、SG1、SG2作为位线和字线间的屏蔽线起作用。结果,能减少在位线中传输的数据中产生的噪声。

在删除动作中,分别把ROWERASE1B、ROWPROG1、ROWERASE2B、ROWERASE3n、ROWGATE设定为接地电位Vss,把ROWERASE1、ROWPROG1B、ROWERASE2分别设定为芯片内电源电位Vdd(也可以是电源电位Vcc)。

这时,时钟控制式倒相器CINV4、CINV7变为工作状态,时钟控制式倒相器CINV3、CINV5、CINV7变为非工作状态。此外,MOS晶体管TP6变为导通状态。

在选择的存储单元块中,由虚线X1包围的部分的输出信号RDECADS1变为“H”,即芯片内电源电位Vdd,行地址解码器RADD2的输出信号RDECADS变为“L”,即接地电位Vss。

而在未选择的存储单元块中,由虚线X1包围的部分的输出信号RDECADS1变为“L”,即接地电位Vss,行地址解码器RADD2的输出信号RDECADS变为“H”,即芯片内电源电位Vdd。

此外,因为ROWGATE为接地电位Vss,所以如果未选择的存储单元块内的信号线22(参照图12)的电位(RDECADS的电位)变为1~1.5左右,则由于MOS晶体管DHN6、DHN9截止,变为浮置状态。

这样,在删除动作中,配置在未选择的存储单元块内的信号线22(参照图12)为1~1.5V,并且为浮置状态。即当向单元势阱提供了删除电位Vera时,信号线22(参照图12)的电位也与字线同样地由于电容耦合而上升,所以信号线22(参照图12)不抑制字线电位的上升。

因此,当向单元势阱提供了删除电位Vera时,由于单元势阱和字线间的电容耦合,能取得未选择的存储单元块内的字线电位容易上升的效果。

此外,与此相伴,不会对未选择的存储单元块内的存储单元的隧道氧化膜加上大的电场,所以能防止未选择的存储单元块内的错误删除。

可是,当图15的虚线X内的熔丝元件(图13的熔丝元件也相同)与对应的存储单元块为用户用的存储区时,该熔丝元件(行地址解码器)不切断。

可是,当与该熔丝元件(行地址解码器)对应的存储单元块为用于存储器件代码的ROM·BLOCK区时,切断该熔丝元件,用户对ROM·BLOCK区不能自由进行写入/删除。

该ROM·BLOCK区具有以下的定义。

近年,NAND型闪存用于各种电子仪器的存储器中。可是,用于通过通话通信存储音乐信息的存储器等的NAND型闪存有时作为涉及到著作权的数据的存储器而使用。

因此,在NAND型闪存中,为了防止不正当复制,存储有芯片的编号即器件代码。

该器件代码是各NAND型闪存中固有的,假设能自由改写该器件代码,则无法实现器件代码本来的目的。

因此,器件代码在产品出厂前写入NAND型闪存的ROM·BLOCK区中,使用户对ROM·BLOCK区不能进行写入/删除。即在成为ROM·BLOCK区的存储单元块中,切断该熔丝元件。

据此,例如当要从信息提供一侧的NAND型闪存向信息接收一侧的NAND型闪存复制音乐信息时,从信息提供一侧的NAND型闪存读出器件代码,当它与信息接收一侧的NAND型闪存的器件代码不同时,就无法复制。

熔丝元件在向成为ROM·BLOCK区的存储单元块写入器件代码后被切断。

假设在不切断熔丝元件的状态下进行出厂前试验,则在该试验中,器件代码就被删除了。

即,在出厂前的试验中,为了缩短试验时间,同时选择全部块进行写入/删除。即因为全部行地址信号AROWi、…AROWj变为“H”,所以如果不切断熔丝元件,则即使CMD ROMBA为“L”,RDECADS1也变为“H”(在图13中,RDECAD为“H”),选择了成为ROM·BLOCK区的存储单元块。

而在出厂前试验中,即使全部行地址信号AROWi、…AROWj都变为“H”,如果切断了熔丝元件,则CMD ROMBA是“L”,所以RDECAD为“L”(在图13中,RDECAD为“L”),成为ROM·BLOCK区的存储单元块不被选择。

即使切断熔丝元件,也有必要读出存储在ROM·BLOCK区中的器件代码。

通过使CMD ROMBA为“H”,能实现对于ROM·BLOCK区的数据读出。即如果CMD ROMBA为“H”,ROM·BLOCK区内的AROWi、…AROWj变为“H”,则选择了成为ROM·BLOCK区的存储单元块。

此外,即使在切断了熔丝元件后,通过输入特殊的命令,通过使CMD ROMBA和ROM·BLOCK区内的AROWi、…AROWj为“H”,也能改写ROM·BLOCK区内的数据。这时,使CMD ROMBA为“H”的命令一般对用户是非公开的,无法不正当地改写ROM·BLOCK区内的数据。

须指出的是,在本例中,说明了切断ROM·BLOCK区的熔丝的情形,但是图13的熔丝和图15的虚线X内的熔丝即使存储单元块是不良的块,也被切断。这时,该不良的块通过冗余电路置换为预备的块。

3.基本动作的说明

下面,详细说明读出、编程等各工作模式中的本发明的4值NAND单元型闪存(图1)的主要部,特别是数据电路(图10)的动作。

在进行动作的说明前,首先简单说明存储单元的阈值电压和编程/读出方法的一例。

(1)存储单元的阈值电压和编程/读出方法

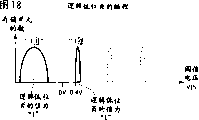

图17表示4值NAND型闪存的存储单元的阈值电压(Vth)的分布。

在一个存储单元中存储有2位数据(4值数据)。在本例中,如上所述,2位数据为“11”、“10”、“00”、“01”。2位数据中的1位是逻辑低位页数据(用□表示),此外另一位为逻辑高位页数据(用○表示),存储在同一存储单元中。

2位数据(“11”、“10”、“00”、“01”)和存储单元的阈值电压的关系成为图17所示的关系。

“11”是删除状态。在删除状态下,逻辑低位页数据和逻辑高位页数据的值都是“1”。删除状态的存储单元具有负的阈值电压Vth。

“10”、“00”、“01”是写入状态。写入状态的存储单元具有正的阈值电压Vth。此外,在写入状态中,“10”状态具有最低的阈值电压,“01”状态具有最高的“阈值电压”,“00”状态具有“10”状态和“01”状态间的阈值电压。

2位数据如上所述,由逻辑低位页数据和逻辑高位页数据构成,通过2次的写入动作,写入存储单元中。

首先进行逻辑低位页数据的编程。

最初全部存储单元为删除状态即“11”状态。然后,如图18所示,如果进行逻辑低位页数据的编程,则存储单元的阈值电压Vth的分布按照写入数据(逻辑低位页数据)的值(“1”、“0”)分为两个。

即,当逻辑低位页数据为“1”时,通过使位线为“H”(字线为写入电位),使存储单元的隧道氧化膜上不会作用高电场,从而防止存储单元的阈值电压Vth的上升。结果,存储单元维持删除状态(“11”状态)(逻辑低位页数据“1”的编程)。

而当逻辑低位页数据为“0”时,通过使位线为“L”(字线为写入电位),在存储单元的隧道氧化膜上作用高电场,把电子注入浮栅电极中,使存储单元的阈值电压Vth只上升给定量。结果存储单元变为写入状态(“10”状态)(逻辑低位页数据“0”的编程)。

然后,进行逻辑高位页数据的编程。

根据从芯片外部输入的写入数据(即逻辑高位页数据)和已经写入存储单元中的逻辑低位页数据进行逻辑高位页数据的编程。

此外,关于逻辑低位页数据,在进行逻辑高位页数据的编程前,从存储单元读出到数据电路中,并且保存住(Internal dataload)。

如图19所示,当逻辑高位页数据为“1”时,通过使位线为“H”(字线为写入电位),使存储单元的隧道氧化膜上不被作用高电场,防止存储单元的阈值电压Vth的上升。结果,逻辑低位页数据为“1”的“11”状态(删除)的存储单元就这样维持“11”状态(逻辑高位页数据“1”的编程)。此外,逻辑低位页数据为“0”的“10”状态的存储单元就这样维持“10”状态(逻辑高位页数据“1”的编程)。

而如图19所示,当逻辑高位页数据为“0”时,通过使位线为“L”(字线为写入电位),在存储单元的隧道氧化膜上作用高电场,把电子注入浮栅电极中,使存储单元的阈值电压Vth只上升给定量。结果,逻辑低位页数据为“1”的“11”状态(删除)的存储单元变为“01”状态(逻辑高位页数据为“0”的编程)。此外,逻辑低位页数据为“0”的“10”状态的存储单元变为“00”状态(逻辑低位页数据“0”的编程)。

即在本例中,逻辑低位页数据为“1”,逻辑高位页数据为“1”时,数据“11”写入存储单元,当逻辑低位页数据为“0”,逻辑高位页数据为“1”时,数据“10”写入存储单元中。此外,当逻辑低位页数据为“1”,逻辑高位页数据为“0”时,数据“01”写入存储单元;逻辑低位页数据为“0”,逻辑高位页数据为“0”时,数据“00”写入存储单元中。

这样通过2次的编程动作,存储单元的阈值电压Vth的分布分为4个(“11”、“10”、“00”、“01”)。

在本例中,当逻辑高位页数据为“0”时,状态“11”的存储单元变为“01”状态,“10”状态的存储单元变为“00”状态(参照图19)。

这里,从图19可知,从状态“11”变为“01”状态时的阈值电压的变动量比从状态“10”变为“00”状态时的阈值电压的变动量还大。即对于进行“00”-编程的存储单元和进行“01”-编程的存储单元,以同一条件提供写入脉冲,所以“00”-编程比“01”-编程还早结束。

这时,省略“00”-编程结束后的“00”-检验读出,然后只进行“01”-检验读出,能谋求编程时间的缩短。

须指出的是,在图17中,Vcgv10是用于“10”-检验读出的读出电位,例如变为0.4V。Vcgv00是用于“00”-检验读出的读出电位(例如,1.4V),Vcgv01是用于“01”-检验读出的读出电位(例如,2.4V)。Vread是提供给未选择的字线的传输电位。

如果存储单元的阈值电压低于Vcgr10,则存储单元的数据是“11”,如果存储单元的阈值电压超过Vcgr10,则低于Vcgr00时,存储单元的数据是“10”,存储单元的阈值电压超过Vcgr00,低于Vcgr01时,存储单元的数据是“00”,当存储单元的阈值电压超过Vcgr01时,存储单元的数据变为“01”。

逻辑低位页数据的通常读出由2次的读出动作(“READ01”、“READ10”)实现。READ01是使用了Vcgr01(例如2V)作为读出电位的读出动作,READ10是使用了Vcgr10(例如0V)作为读出电位的读出动作。此外,逻辑高位页数据的读出能由1次的读出动作(READ“00”实现)。READ00是使用了Vcgr00(例如1V)作为读出电位的读出动作。

这样,在本例中,通过合计3次的读出动作,能读出2位数据,能实现读出时间的缩短或读出动作的高速化。

(2)读出动作

首先,就读出动作加以说明。

①算法

图20表示读出动作的算法。

首先,命令接口电路一确认从主微机提供的读出命令,就接收该信号,把读出命令设定在状态机(控制电路)内(步骤S1)。

此外,一把地址信号从主微机提供到存储器片内,就接收该信号,把用于选择读出页的地址设定在状态机内(步骤S2)。

在状态机内如果设定了读出命令和地址信号,则在基于状态机的控制下,自动执行从步骤S3到步骤S6的动作。

当进行逻辑低位页数据的读出时,如上所述,执行2次的读出动作(“READ01”、“READ10”)(步骤S3~S5)。后面将对此作详细描述,但是通过READ01(Vcgr01=2V)读出的读出数据经由数据存储部分DS1存储到数据存储部分DS3中。在READ10(Vcgr10=0V)中,依存于读出数据和数据存储部分DS3的数据的数据从数据存储部分DS1被传输给数据存储部分DS4。

当进行逻辑高位页数据的读出时,执行1次读出动作(READ“00”)(步骤S3,S6)。后面将对此作详细描述,但是通过READ00(Vcgr00=1V)读出的读出数据经由数据存储部分DS1传输到存储数据部DS4中。

存储在数据部DS4中的读出数据经由I/O线、nIO、读出放大器、数据输入输出缓存器向存储器片的外部输出。

②基于动作波形的动作说明

下面,参照图21的动作波形进行具体动作的说明。

读出动作由逻辑低位页数据的读出动作和逻辑高位页数据的读出动作构成。

须指出的是,在图21的动作定时图中,只要未特别表示,则“L”电平为Vss(例如,0V),“H”电平为Vdd(例如,3V)。此外,在该动作定时图中,选择一个块BLOCKi,选择该块BLOCKi内的字线WL2-i和第奇数条位线BLek(参照图3)。

[1]逻辑低位页数据的读出动作

逻辑低位页数据的读出动作由2次的读出动作即“READ01”和“READ10”构成。首先进行“READ01”,接着进行“READ10”。

“READ01”和“READ10”分别由与这两个读出动作中公共的数据读出有关的部分(RCLK 1-E、SCLK 1-E、RRCV 1-E)和各读出动作中固有的数据传输的部分(EXCLK过程)构成。

[1]-1“READ01”

“READ01”动作是把读出电位(选择字线WL2-i的电位)设定为Vcgr01(例如2V),确认存储单元的数据是“01”或此外的数据“11”、“10”、“00”的动作。

[1]-1-1数据读出

首先,向位线一侧的选择栅线SGD和未选择的字线WL0-i、WL1i、WL3i分别提供传输电位Vread(例如,4.5V),向选择的字线WL2-i提供读出电位Vcgr01(RCLK1-2)。

控制信号BLPRE变为“H”,N沟道MOS晶体管Qn6(图10)变为导通状态。此外,控制信号BLCLAMP变为Vclamp(例如2V),控制信号BLSE通过变为Vsghh(例如4.5V),第奇数条位线BLek预先充电为给定电位(例如1V左右)。而控制信号BIASo变为Vsghh(例如,4.5V),所以第偶数条位线BLok固定在Vss(例如0V),作为屏蔽位线起作用(RCLK2-4)。

然后,控制信号BLCLAMP变为Vss(例如0V),控制信号BLPRE变为“L”,第奇数条位线BLek变为浮置状态(RCLK5-7)。

如果源线一侧的选择栅线SGS的电位设定为传输电位Vread,则按照选择了的存储单元的状态即存储在该存储单元中的数据的值,表现对位线BLek的电位的影响。

即选择了的存储单元的数据为“11”、“10”、“00”时,该选择的存储单元通过读出电位Vcgr01变为导通状态。因此,位线BLek的电荷放电,位线BLek的电位下降到0.8V以下(选择块内的存储单元由于Vread而处于导通状态)。

而当选择了的存储单元的数据为“01”时,该选择的存储单元因读出电位Vcgr01而不变为导通状态。因此,位线BLek的电荷不放电,位线BLek维持预充电电位(约1V)(RCLK6-E)。

由于控制信号BLPRE变为4.5V左右,控制信号VPRE变为Vdd(例如3V),数据存储部分DS1的电容器C1的一端即节点N2被充电为Vdd。然后,控制信号BLCLAMP如果变为Vsense(例如,1.8V),则数据存储部分DS1的电容器C1的一端电位变化如下。

即位线BLek的电位保持预充电电位(约1V)时(存储单元的数据为“01”时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)变为断开状态,数据存储部分DS1的电容器C1的一端电位维持在Vdd(“H”)。

而当位线BLek的电位为0.8V以下时(存储单元的数据为“11”、“10”、“00”时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是导通状态,数据存储部分DS1的电容器C1的一端的电荷放电到位线BLek中,该电位下降到比Vdd还低的值(“L”)(SCLK4-5)。

结果,在数据存储部分DS1(电容器C1的一端)中存储有基于读出电位Vcgr01的读出数据。即当存储单元的数据为“11”、“10”、“00”时,存储“L”即数据“0”,当存储单元的数据为“01”时,存储“H”,即数据“1”。

[1]-1-2数据传输

在“READ01”动作中,在向数据存储部分DS1读出了存储单元的数据后,执行把存储在该数据存储部分DS1中的读出数据向数据存储部分DS3传输的数据传输。该动作根据图22所示的EXCLK过程。

首先,控制信号SEN1、LAT1都变为“L”(EXCLK6),并且通过控制信号EQ1变为“H”(EXCLK7-8),构成数据存储部分DS3的双稳态多谐振荡器电路(图10)的状态被复位。

然后控制信号BLC1变为4.5V(EXCLK9),N沟道MOS晶体管Qn10变为导通状态。结果,数据存储部分DS1和数据存储部分DS3彼此电连接(图10)。

如果控制信号SEN1变为“H”(EXCLK10),则存储在数据存储部分DS1(电容器C1的一端)中的读出数据经由MOS晶体管Qn10由构成数据存储部分DS3的时钟控制式倒相器CI1读出。此外,如果控制信号LAT1变为“H”(EXCLK11),则该读出数据存储到数据存储部分DS3中(图10)。

须指出的是,“READ01”动作对连接在选择的字线WL2-i上的4256个存储单元同时进行。

[1]-2“READ10”

“READ10”动作是把读出电位(选择的字线WL2-i的电位)设定为Vcgr10(例如0V),识别存储单元的数据是“11”还是此外的数据“10”、“00”、“01”的动作。

[1]-2-1数据读出

首先,向位线一侧的栅选择线SGD和未选择的字线WL0-i、WL0-1、WL3-i分别提供传输电位Vread(例如4.5V),向选择的字线WL2-i提供读出电位Vcgr10(RCLK1-2)。

控制信号BLPRE变为“H”,N沟道MOS晶体管Qn6(图10)变为导通状态。此外,控制信号BLCLAMP变为Vclamp(例如2V),通过控制信号BLSe变为Vsghh(例如,4.5V),第奇数条位线BLek预先充电为给定电位(例如1V左右)。而控制信号BIASo变为Vsghh(例如4.5V),所以第偶数条位线BLok固定在Vss(例如0V),作为屏蔽位线起作用(RCLK2-4)。

然后控制信号BLCLAMP变为Vss(例如0V),控制信号BLPRE变为“L”,第奇数条位线BLek变为浮置状态(RCLK5-7)。

如果源线一侧的选择栅线SGS的电位设定为传输电位Vread,则按照选择的存储单元的状态即存储在该存储单元中的数据值,表现出对位线BLek的电位的影响。

即,被选择了的存储单元的数据为“11”时,由于读出电位Vcgr10,该选择的存储单元变为导通状态。因此,位线BLek的电荷放电,位线BLek的电位下降到0.8V以下(选择的块内的未选择的存储单元由于Vread,是导通状态)。

而当选择了的存储单元的数据为“10”、“00”、“01”时,由于读出电位Vcgr10,该选择的存储单元不变为导通状态。因此,位线BLek的电荷不放电,位线BLek维持预充电电位(约1V)(RCLK6-E)。

由于控制信号BLPRE变为4.5V左右,控制信号VPRE变为Vdd(例如3V),数据存储部分DS1的电容器C1的一端即节点N2被充电为Vdd。然后,控制信号BLCLAMP如果变为Vsense(例如,1.8V),则数据存储部分DS1的电容器C1的一端电位变化如下。

即位线BLek的电位保持预充电电位(约1V)时(存储单元的数据为“10”、“00”、“01”时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)变为断开状态,数据存储部分DS1的电容器C1的一端电位维持在Vdd(“H”)。

而当位线BLek的电位为0.8V以下时(存储单元的数据为“11”时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是导通状态,数据存储部分DS1的电容器C1的一端的电荷放电到位线BLek中,该电位下降到比Vdd还低的值(“L”)(SCLK4-5)。

结果,在数据存储部分DS1(电容器C1的一端)中存储有基于读出电位Vcgr10的读出数据。即当存储单元的数据为“11”时,存储“L”即数据“0”,当存储单元的数据为、“10”、“00”、“01”时,存储“H”,即数据“1”。

[1]-2-2数据传输

在“READ10”动作中,在数据存储部分DS1读出了存储单元的数据后,根据数据存储部分DS3的数据(即通过“READ01”从存储单元读出的读出数据)的值,执行维持或强制变更数据存储部分DS1的数据的动作,然后执行把存储在数据存储部分DS1中的读出数据传输给数据存储部分DS4的数据传输。该动作根据图23所示的EXCLK过程进行。

首先,控制信号DTG变为4.5V,N沟道MOS晶体管Qn9(图10)变为导通状态。结果,数据存储部分DS2和数据存储部分DS3变为彼此电连接,数据存储部分DS3的数据传输给数据存储部分DS2即N沟道MOS晶体管Qn8的栅极(EXCLK2-4)。

然后,如果控制信号REG变为“H”,则按照存储在数据存储部分DS3中的数据,维持或强制变更存储在数据存储部分DS1中的读出数据即通过“READ10”从存储单元读出的读出数据(EXCLK3-4)。

例如,当存储在数据存储部分DS3中的数据为“0”时,N沟道MOS晶体管Qn8的栅极电位电平变为“L”,所以该N沟道MOS晶体管Qn8变为断开状态(图10)。因此,数据存储部分DS1维持由“READ10”从存储单元读出的读出数据的值。

此外,当存储在数据存储部分DS3中的数据为“1”时,N沟道MOS晶体管Qn8的栅极电位电平变为“H”,所以该N沟道MOS晶体管Qn8变为变为导通状态(图10)。因此,数据存储部分DS1的数据与由“READ10”从存储单元读出的读出数据的值无关,强制地设定为“0”。

然后,控制信号SEN2、LAT2都变为“L”(EXCLK6),并且通过控制信号EQ2变为“H”(EXCLK7-8),构成数据存储部分DS4的双稳态多谐振荡器电路(图10)的状态被复位。

然后,控制信号BLC2变为4.5V(EXCLK9),N沟道MOS晶体管Qn12变为导通状态。结果,数据存储部分DS1和数据存储部分DS4彼此电连接(图10)。

如果控制信号SEN2变为“H”(EXCLK7-10),则存储在数据存储部分DS1(电容器C1的一端)中的读出数据经由MOS晶体管Qn12由构成数据存储部分DS4的时钟同步式倒相器CI4读出。此外,如果控制信号LAT2变为“H”(EXCLK7-11),则该读出数据存储在数据存储部分DS4(图10)中。

此外,“READ10”动作对连接在选择的字线WL2-i上的4256个存储单元同时进行。

[1]-3总结

图25简单表示了逻辑低位页数据的读出动作中的读出数据流。

在“READ01”中,使用Vcgr01(例如2V)作为读出电位执行读出动作,把这时的读出数据存储在数据存储部分DS1中。即当选择的存储单元的数据为“11”、“10”、“00”时,电容器C1的一端(节点N2)的电位变为“L”,当选择的存储单元的数据为“01”时,电容器C1的一端(节点N2)的电位变为“H”(①)。

然后,数据存储部分DS1的数据传输给数据存储部分DS3,并且存储(①)。

当“READ01”结束的时刻,数据存储部分DS3的数据为“H”时,判定存储单元的数据为“01”即逻辑低位页数据为“1”,但是当数据存储部分DS3的数据为“L”时,存储单元的数据为“11”、“10”、“00”中的任意一个,无法决定逻辑低位页数据的值。

因此,接着“READ01”进行“READ10”。

在“READ10”中,使用Vcgr10(例如0V)作为读出电位执行读出动作,把这时的读出数据存储在数据存储部分DS1中。即当选择的存储单元的数据为“11”时,电容器C1的一端(节点N2)的电位变为“L”,当选择的存储单元的数据为“10”、“00”、“01”时,电容器C1的一端(节点N2)的电位变为“H”。

可是,当数据存储部分DS3的数据为“H”时,即存储单元的数据为“01”时,使N沟道MOS晶体管Qn8为导通状态,强制把电容器C1的一端(节点N2)的电位变更为“L”(②)。

结果,当选择的存储单元的数据为“11”、“01”时,数据存储部分DS1的数据变为“L”,所以作为选择的存储单元的逻辑低位页数据,确认了“1”。此外,当选择的存储单元的数据为“10”、“00”时,数据存储部分DS1的数据变为“H”,所以阻我诶选择的存储单元的逻辑低位页数据,确认了“0”(②)。

须指出的是,在该时刻,“L”=“0”和H=“1”的关系颠倒。即变为“L”=“1”和H=“0”的关系。

然后,把数据存储部分DS1的数据传输给数据存储部分DS4,并且被存储。通过把列选择信号CSLk(图10)变为“H”,数据存储部分DS4的数据输出到I/O线(IO,nIO),并且经由数据输入输出缓存器,输出到存储器片的外部。

[2]逻辑高位页数据的读出动作

逻辑高位页数据的读出动作由1次的读出动作即“READ00”构成。“READ00”由涉及数据读出的部分(RCLK 1-E,SCLK 1-E,RRCV 1-E)、涉及数据传输的部分(EXCLK过程)构成。

[2]-1“READ00”

“READ00”动作是把读出电位(选择的字线WL2-i的电位)设定为Vcgr00(例如,1V),确认存储单元的数据是“11”、“10”(逻辑高位页数据为“1”)还是“00”、“01”的动作。

[2]-1-1数据读出

首先,向位线一侧的栅选择线SGD和未选择的字线WL0-i、WL0-1、WL3-i分别提供传输电位Vread(例如4.5V),向选择的字线WL2-i提供读出电位Vcgr00(RCLK1-2)。

控制信号BLPRE变为“H”,N沟道MOS晶体管Qn6(图10)变为导通状态。此外,控制信号BLCLAMP变为Vclamp(例如2V),通过控制信号BLSe变为Vsghh(例如,4.5V),把第奇数条位线BLek预先充电为给定电位(例如1V左右)。而控制信号BIASo变为Vsghh(例如4.5V),所以第偶数条位线BLok固定在Vss(例如0V),作为屏蔽位线起作用(RCLK2-4)。

然后控制信号BLCLAMP变为Vss(例如0V),控制信号BLPRE变为“L”,第奇数条位线BLek变为浮置状态(RCLK5-7)。

如果把源线一侧的选择栅极线SGS的电位设定为传输电位Vread,则按照选择的存储单元的状态(即存储在该存储单元中的数据值),表现对位线BLek的电位的影响。

即,被选择了的存储单元的数据为“11”、“10”时,该选择的存储单元由于读出电位Vcgr00而变为导通状态。因此,位线BLek的电荷放电,位线BLek的电位下降到0.8V以下(选择的块内的未选择的存储单元因Vread而是导通状态)。

而当选择了的存储单元的数据为“00”、“01”时,该选择的存储单元因读出电位Vcgr00不变为导通状态。因此,位线BLek的电荷不放电,位线BLek维持预充电电位(约1V)(RCLK6-E)。

由于控制信号BLPRE变为4.5V左右,控制信号VPRE变为Vdd(例如3V),数据存储部分DS1的电容器C1的一端(即节点N2)被充电为Vdd。然后,控制信号BLCLAMP如果变为Vsense(例如,1.8V),则数据存储部分DS1的电容器C1的一端电位变化如下。

即,位线BLek的电位保持预充电电位(约1V)时(存储单元的数据为“00”、“01”时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)变为断开状态,数据存储部分DS1的电容器C1的一端电位维持在Vdd(“H”)。

而当位线BLek的电位为0.8V以下时(存储单元的数据为“11”、“10”时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是导通状态,数据存储部分DS1的电容器C1的一端的电荷放电到位线BLek中,该电位下降到比Vdd还低的值(“L”)(SCLK4-5)。

结果,在数据存储部分DS1(电容器C1的一端)中存储有基于读出电位Vcgr00的读出数据。即当存储单元的数据为“11”、“10”时,存储“L”,即数据“1”;当存储单元的数据为“00”、“01”时,存储“H”,即数据“0”。

须指出的是,在该时刻,“L”=“0”和H=“1”的关系颠倒。即变为“L”=“1”和H=“0”的关系。

[2]-1-2数据传输

在“READ00”动作中,在向数据存储部分DS1读出了存储单元的数据后,执行把存储在数据存储部分DS1中的读出数据传输给数据存储部分DS4的数据传输。该动作根据图24所示的EXCLK过程。

首先,控制信号SEN2、LAT2都变为“L”(EXCLK6),并且通过控制信号EQ2变为“H”(EXCLK7-8),构成数据存储部分DS4的双稳态多谐振荡器电路(图10)的状态被复位。

然后,控制信号BLC2变为4.5V(EXCLK9),N沟道MOS晶体管Qn12变为导通状态。结果,数据存储部分DS1和数据存储部分DS4彼此电连接(图10)。

如果控制信号SEN2变为“H”(EXCLK10),则存储在数据存储部分DS1(电容器C1的一端)中的读出数据经由MOS晶体管Qn12由构成数据存储部分DS4的时钟同步式倒相器CI4读出。此外,如果数据存储部分LAT2变为“H”(EXCLK11),则该读出数据存储到数据存储部分DS4中(图10)。

须指出的是,“READ00”动作对连接在选择的字线WL2-i上的4256个存储单元同时进行。

[2]-3总结

图26简单表示逻辑高位页数据的读出动作的数据读出流。

在“READ00”中,使用Vcgr00(例如1V)作为读出电位执行读出动作,把这时的读出数据存储在数据存储部分DS1中。即当选择的存储单元的数据为“11”、“10”(逻辑高位页数据为“1”)时,电容器C1的一端(节点N2)的电位变为“L”,当选择的存储单元的数据为“00”、“01”时,电容器C1的一端(节点N2)的电位变为“H”。

须指出的是,在该时刻,“L”=“0”和H=“1”的关系颠倒。即变为“L”=“1”和H=“0”的关系。

然后,通过控制信号BLC2变为4.5V,数据存储部分DS1的数据传输给数据存储部分DS4并且存储。通过列选择信号CLSk(图10)变为“H”,数据存储部分DS4的数据输出到I/O线(IO,nIO),并且经由数据输入输出缓存器,输出到存储器片的外部。

(3)算法动作

下面说明算法动作。

①算法

[1]程序动作1

图27~图29表示程序动作的算法一例。

本例子成为采用了称作通过写入(Pass Write)的写入原理时的算法。通过写入是指对经过了编程检验的存储单元再执行编程动作,以高精度控制其阈值电压即让阈值分布的宽度变窄的手法(2次写入),由第一次的编程和第二次的编程构成。

须指出的是,第一次的编程称作第一轮通过(1st Pass),第二次的编程称作第二轮通过(2nd Pass)。

首先,命令接口电路接收从主微机提供的数据输入命令,接收后,把数据输入命令设定在状态机(控制电路)内(步骤S1)。

此外,一旦地址信号被从主微机提供给存储器片内,就接收该信号,把用于选择成为编程对象的页的地址设定在状态机内(步骤S2)。

然后,如果一页部分的编程数据经由输入输出缓存器输入到存储器片内,则把这一页部分的编程数据存储到数据存储部分DS4中(步骤S3)。须指出的是,数据存储部分DS4只存在与一页对应的数。

然后,命令接口电路如果确认从主微机提供的写入命令,就接受它,把写入命令设定在状态机内(步骤S4)。结果在基于状态机的控制下,自动执行图28的步骤S5到图29的步骤S28的动作。

[1]-1第一轮通过

首先,执行图28所示的第一次的编程(第一轮通过)。

存储在数据存储部分DS4中的编程数据分别复制到数据存储部分DS2、DS3中(步骤S5)。

然后,如果成为编程对象的页是逻辑高位页,则在写入动作前,执行内部数据加载(Internal Data Load)(步骤S6)。内部数据加载是指读出具有成为编程对象的逻辑高位页的选择的存储单元的逻辑低位页中存储的数据的动作。

需要内部数据加载的理由在于即使写入选择的存储单元的逻辑高位页中的数据相同,根据存储单元的逻辑低位页中存储的数据的值,在写入动作中成为目标的阈值电压也不同。

通过内部数据加载读出的逻辑低位页数据经由数据存储部分DS1存储到数据存储部分DS4中。

这里,应注意当逻辑低位页数据为“1”时,基于内部数据加载的读出数据为“0”(=“L”),数据“0”存储在数据存储部分DS4(节点N4)中,此外,当逻辑低位页数据为“0”时,基于内部数据加载的读出数据为“1”(=“H”),数据“1”存储在数据存储部分DS4(节点N4)中。

可是,关于该现象,在动作上完全没问题,相反恰好执行第二轮通过的“检验00(2nd通过)”。

然后,如果是对于逻辑低位页的编程,就把写入电压Vpgm设定为12V,如果是对于逻辑高位页的编程,就把写入电压Vpgm设定为13V。此外,把状态机内的编程计数器的值PC设定为0(步骤S7)。须指出的是,编程计数器的值PC表示写入动作的次数。

接着,执行写入动作(步骤S8)。

当存储在数据存储部分DS3中的编程数据为“0”时,例如向衬底和浮栅电极之间提供高电压,向浮栅电极注入电子,提高存储单元的阈值电压(“0”-编程)。当存储在数据存储部分DS3中的编程数据为“1”时,例如不向衬底和浮栅电极之间提供高电压,防止电子对浮栅电极的注入,使存储单元的阈值电压不变化(“1”-编程)。

在进行了写入动作后,在编程计数器的值PC中加“1”(步骤S8)。

然后,根据存储在数据存储部分DS3中的数据,判定编程检验是成为通过状态(编程结束的状态)还是成为NG的状态(编程未结束的状态)(步骤S9)。

这里,在最初的写入动作之后,一次也未进行“检验00(1st通过)”和“检验10(1st通过)”,所以数据存储部分DS3存储着编程数据。

所有列内的数据存储部分DS3(例如4256个)都存储着数据“1”时,即对于逻辑低位页或逻辑高位页的编程数据都为“1”时,在全部列中,图10的N沟道MOS晶体管Qn17为断开状态,例如图8的FLAG维持“H”。

因此,判断为编程检验为通过状态(编程结束的状态),向第二轮通过转移(步骤S15)。

而至少一列内的数据存储部分DS3存储着数据“0”时,即对于逻辑低位页或逻辑高位页的编程数据的至少一个为“0”时,连接在存储数据“0”的数据存储部分DS3上的N沟道MOS晶体管Qn17(图10)是导通状态,例如图8的FLAG变为“L”。

因此,判断为编程检验为NG状态(编程未结束的状态),向“检验00(1st通过)”和“检验10(1st通过)”转移。

如果是对逻辑低位页的编程,则执行“检验10(1st通过)”(步骤S12)。

“检验10(1st通过)”是指对于成为编程对象的选择的存储单元,使用读出电位Vcgv10(参照图17)执行读出动作,根据由该读出动作取得的读出数据和数据存储部分DS2的数据(编程数据),决定数据存储部分DS3中新存储的数据的值的动作。

当为对逻辑低位页的编程时,当初成为编程对象的选择的全部存储单元变为“11”状态。因此,关于成为“1”-编程的对象的存储单元(与存储数据“1”的数据存储部分DS3对应的存储单元),阈值电压没有变动,所以由“检验10(1st通过)”读出的读出数据总是“0”。

因此,在数据存储部分DS1中存储“0”。可是,如后所述,当在数据存储部分DS2中存储着“1”时,数据存储部分DS1的数据与读出数据无关,强制变更为“1”。即该数据“1”被从数据存储部分DS1再次存储到数据存储部分DS3中。

而关于成为“0”-编程的对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),当阈值电压由于写入动作(步骤S8)而充分上升(编程结束)时,由“检验10(1st通过)”读出的读出数据变为“1”。

因此,在数据存储部分DS1中存储“1”。该数据“1”从数据存储部分DS1传输给数据存储部分DS3。即数据存储部分DS3的数据从“0”变为“1”。

此外,关于成为“0”-编程的对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),当阈值电压通过写入动作(步骤S8)未充分上升(编程未结束)时,由“检验10(1st通过)”读出的读出数据变为“0”。

因此,在数据存储部分DS1中存储“0”。该数据“0”从数据存储部分DS1传输给数据存储部分DS3。即数据存储部分DS3的数据维持“0”。

如果是对逻辑高位页的编程,就执行“检验00(1st通过)”(步骤S11)。

“检验00(1st通过)”是指对于成为编程对象的选择的存储单元,使用读出电位Vcgv00(参照图17)执行读出动作,根据由该读出动作取得的读出数据和数据存储部分DS2的数据(编程数据),决定数据存储部分DS3中新存储的数据的值的动作。

当为对逻辑高位页的编程时,当初成为编程对象的选择的全部存储单元变为“11”状态或“10”状态。因此,关于成为“1”-编程的对象的存储单元(与存储数据“1”的数据存储部分DS3对应的存储单元),阈值电压没有变动,所以由“检验00(1st通过)”读出的读出数据总是“0”。

因此,在数据存储部分DS1中存储“0”。可是,如后所述,当在数据存储部分DS2中存储着“1”时,使数据存储部分DS1的数据与读出数据无关,强制变更为“1”。即该数据“1”从数据存储部分DS1再存储到数据存储部分DS3中。

而关于成为“0”-编程的对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),当阈值电压由于写入动作(步骤S8)而充分上升(编程结束)时,由“检验00(1st通过)”读出的读出数据变为“1”。

因此,在数据存储部分DS1中存储“1”。该数据“1”从数据存储部分DS1传输给数据存储部分DS3。即数据存储部分DS3的数据从“0”变为“1”。

须指出的是,在本阶段中,成为“0”-编程的对象的存储单元都变为“00”状态,但是根据由内部数据加载(步骤S6)读出的逻辑低位页数据(存储在数据存储部分DS4中),在第二轮通过中进行“检验(2nd通过)”(分为“00”状态和“01”状态),所以不会破坏逻辑低位页数据,并能对逻辑高位页数据编程。

此外,关于成为“0”-编程的对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),当阈值电压未因写入动作(步骤S8)而充分上升(编程未结束)时,由“检验00(1st通过)”读出的读出数据变为“0”。

因此,在数据存储部分DS1中存储“0”。该数据“0”从数据存储部分DS1传输给数据存储部分DS3。即数据存储部分DS3的数据维持“0”。

然后,如果编程计数器的值PC达到预先设定的最大写入次数PC max 1st,则在状态机内的状态寄存器中设定失败(编程不良),结束编程动作(步骤S13、S16)。

此外,如果编程计数器的值PC比预先设定的最大写入次数PCmax 1st还小,则使写入电压Vpgm上升例如0.02V左右后(增压),再度执行写入动作(步骤S13、S14、S8)。

然后,进行编程检验(步骤S9),但是如上所述,当进行“1”-编程时,数据存储部分DS3的数据总是“1”。此外,当进行“0”-编程时,在“0”-编程结束时,数据存储部分DS3的数据从“0”变为“1”,只在“0”-编程未结束时,数据存储部分DS3的数据维持“0”。

因此,对于成为编程对象的选择的全部存储单元,当编程(“1”-编程或“0”-编程)结束时,全部数据存储部分DS3存储着数据“1”。即在全部的列中,图10的N沟道MOS晶体管Qn17是断开状态,图8的FLAG变为H(编程检验通过的状态),向第二轮通过转移(步骤S15)。

此外,当对于成为编程对象的选择的存储单元的至少一个,编程(“0”-编程)还未结束时,至少一个数据存储部分DS3存储着数据“0”。即至少在一列中,图10的N沟道MOS晶体管Qn17变为导通状态,图8的FLAG变为“L”(编程检验为NG的状态),再次重复检验读出和写入动作(步骤S10~S14、S16、S8)。

这样,根据存储在数据存储部分DS3中的数据,能判断编程是否结束了。

[1]-2第二轮通过

在第一次编程(第一轮通过)的步骤S9中,当编程检验为通过时,继续执行第二次编程(第二轮通过)。

在第二轮通过中,首先把存储在数据存储部分DS2中的编程数据复制回数据存储部分DS3中(步骤S17)。

这样的复制具有以下的意义。

当初编程数据存储在数据存储部分DS2、DS3(步骤S5)中。可是,在第一轮通过中,如上所述,数据存储部分DS3的数据根据“检验10(1st通过)”或“检验00(1st通过)”的结果而变化。最终在第一轮通过的步骤S9中,当编程检验为通过时,全部的数据存储部分DS3的值变为“1”。

因此,在第二轮通过中,为了使编程数据再次存储到数据存储部分DS3中,从数据存储部分DS2把编程数据传输到数据存储部分DS3中。这是步骤S17的复制的意义。

然后,如果是对于逻辑低位页的编程,就再把写入电压Vpgm设定为12V,如果是对于逻辑高位页的编程,就再把写入电Vpgm设定为13V。此外,把状态机内的编程计数器的值PC再设定为0(步骤S7)。

接着,执行“检验10(2nd通过)”或“检验01”。

如果是对于逻辑低位页的编程,就执行“检验10(2nd通过)”(步骤S19~ST20)。

“检验10(2nd通过)”是指对于成为编程对象的选择的存储单元,使用读出电位Vcgv10(参照图17)执行读出动作,根据由该读出动作取得的读出数据和数据存储部分DS2的数据(编程数据),决定数据存储部分DS3中新存储的数据的值的动作。

在第二轮通过中,关于成为“1”-编程的对象的存储单元(与存储数据“1”的数据存储部分DS3对应的存储单元),维持“11”状态,所以由“检验10(2nd通过)”读出的读出数据总是“0”。

因此,在数据存储部分DS1中存储“0”。此外,因为在数据存储部分DS2中存储着“1”,所以使数据存储部分DS1的数据与读出数据无关地强制变更为“1”。因此,数据“1”从数据存储部分DS1传输到数据存储部分DS3中。

而关于成为“0”-编程的对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),认为通过第一轮通过几乎变为“10”状态。

关于阈值电压充分上升(编程结束)的存储单元,由“检验10(2nd通过)”读出的读出数据变为“1”。

因此,在数据存储部分DS1中存储“1”。该数据“1”从数据存储部分DS1传输给数据存储部分DS3。即数据存储部分DS3的数据从“0”变为“1”。

关于阈值电压未充分上升(编程未结束)的存储单元,由“检验10(2nd通过)”读出的读出数据变为“0”。

因此,在数据存储部分DS1中存储“0”。该数据“0”从数据存储部分DS1传输给数据存储部分DS3。即数据存储部分DS3的数据维持“0”。

如果是对逻辑高位页的编程,就连续执行“检验01”和“检验00(2nd通过)”(步骤S21~S22)。

“检验01”是指对于成为编程对象的选择的存储单元,使用读出电位Vcgv01(参照图17)执行读出动作,根据由该读出动作取得的读出数据和数据存储部分DS2的数据(编程数据),决定数据存储部分DS3中新存储的数据的值的动作。

“检验00(2nd通过)”是指对于成为编程对象的选择的存储单元,使用读出电位Vcgv00(参照图17)执行读出动作,根据由该读出动作取得的读出数据和数据存储部分DS2的数据(编程数据)和数据存储部分DS4的数据(逻辑低位页数据),决定数据存储部分DS3中新存储的数据的值的动作。

在第二轮通过中,关于成为“1”-编程的对象的存储单元(与存储数据“1”的数据存储部分DS3对应的存储单元),维持“11”状态或“10”,所以由“检验01”读出的读出数据总是“0”。

因此,在数据存储部分DS1中存储“0”。此外,因为在数据存储部分DS2中存储着“1”,所以使数据存储部分DS1的数据与读出数据无关地强制变更为“1”。因此数据“1”从数据存储部分DS1传输到数据存储部分DS3中。

此外,由“检验00(2nd通过)”读出的读出数据也总是“0”。

因此,在数据存储部分DS1中存储“0”。可是,因为数据存储部分DS2中存储着“1”,所以数据存储部分DS1的数据与读出数据无关,强制变更为“1”。因此数据“1”从数据存储部分DS1传输到数据存储部分DS3中。

而关于成为“0”-编程的对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),认为通过第一轮通过变为“00”状态。

因此,最初,由“检验01”读出的读出数据变为“0”。因此,在数据存储部分DS1中存储“0”。该数据“0”从数据存储部分DS1传输到数据存储部分DS3中。即数据存储部分DS3的数据维持“0”。

然后,接着“检验01”执行“检验00(2nd通过)”。

关于阈值电压充分上升(“00”-编程结束)的存储单元,由“检验00(2nd通过)”读出的读出数据变为“1”。

因此,在数据存储部分DS1中存储“1”。

可是,在这里,数据存储部分DS1的数据受到存储在数据存储部分DS4中的逻辑低位页数据的影响。

即,逻辑低位页数据为“1”时,数据存储部分DS4(节点N4)存储着“0”(=“L”)。因此,使数据存储部分DS1的数据强制变更为“0”。这意味着逻辑低位页数据为“1”时,当把“0”作为逻辑高位页数据进行编程时,存储单元为“01”状态(参照图19)。

该数据“0”从数据存储部分DS1传输到数据存储部分DS3中。即数据存储部分DS3的数据维持“0”。

逻辑低位页数据为“0”时,数据存储部分DS4(节点N4)存储着“1”(=“H”)。因此,数据存储部分DS1的数据维持“1”。

该数据“1”从数据存储部分DS1传输到数据存储部分DS3中。即数据存储部分DS3的数据从“0”变为“1”。

可是,如上所述,当把“0”作为逻辑高位页数据进行编程时,当逻辑低位页数据为“0”时,必须使存储单元为“00”状态,当逻辑低位页数据为“1”时,使存储单元为“01”状态。

此外,在第一轮通过结束的时刻,把“0”作为逻辑高位页数据进行编程的存储单元与逻辑低位页数据的值无关,变为“00”状态。

在本例的序列中,在“检验01”之后,连续执行“检验00(2nd通过)”,所以通过写入动作和“检验01”,只使逻辑低位页数据为“1”的存储单元的阈值电压上升,能成为“01”状态。换言之,关于逻辑低位页数据为“0”的存储单元,能通过“检验00(2nd通过)”,在变为“00”状态的时刻停止写入动作(对浮栅电极的电子注入)。

然后,如果程序计数器的值PC达到预先设定的最大写入次数PC max 2nd,则在状态机内的状态存储器中设定Fail(编程不良),结束编程动作(步骤S23、S28)。

此外,如果程序计数器的值PC比预先设定的最大写入次数PCmax 2nd还小,则使写入电压Vpgm上升了0.02V左右(增压)后,再度执行写入动作(步骤S23、S24、S25)。

当存储在数据存储部分DS3中的编程数据为“0”时,例如向衬底和浮栅电极之间提供高电压,向浮栅电极注入电子,提高存储单元的阈值电压(“0”-编程)。当存储在数据存储部分DS3中的编程数据为“1”时,例如不向衬底和浮栅电极之间提供高电压,防止电子对浮栅电极的注入,使存储单元的阈值电压不变化(“1”-编程)。

在进行了写入动作后,在编程计数器的值PC中加“1”(步骤S25)。

然后,根据存储在数据存储部分DS3中的数据,执行编程检验,判定编程检验是成为通过状态(编程结束的状态)或成为NG的状态(编程未结束的状态)(步骤S26)。

对于逻辑高位页的编程数据为“1”(“1”-编程)时,数据存储部分DS3的数据总为“1”。

此外,当对逻辑高位页数据的编程数据为“0”、逻辑低位页数据为“0”时(“00”-编程),当“00”-编程结束时,数据存储部分DS3的数据通过“检验00(2nd通过)”从“0”变更为“1”。

此外,当对于逻辑高位页的编程数据为“0”,逻辑低位页数据为“1”时(“01”-编程),在“01”-编程结束时,数据存储部分DS3的数据通过“检验01”从“0”变更为“1”。

因此,对于成为编程对象的全部存储单元,当编程(“00”-编程或“01”-编程)结束时,全部数据存储部分DS3存储着数据“1”。即在全部列中,图10的N沟道MOS晶体管Qn17是断开状态,图8的FLAG变为“H”(编程检验通过的状态)。而且,在状态机内的状态寄存器中设定通过(编程结束),结束编程动作(步骤S26、S27)。

此外,对于成为编程对象的选择的存储单元的至少一个,编程(“01”-编程)未结束时,至少一个数据存储部分DS3存储着数据“0”。即在至少一列中,图10的N沟道MOS晶体管Qn17变为导通状态,图8的FLAG变为“L”(编程检验为NG的状态),再次重复检验读出和写入动作(步骤S19~S25,S28)。

这样,根据存储在数据存储部分DS3中的数据,能判断编程是否结束。

[2]编程动作2

图30表示编程动作的算法的其他例子。

本例子成为采用称作快速通过写入(QPW)的写入原理时的算法。快速通过写入是通过写入(2度写入)的改良例,在并行处理通过写入中的第一轮通过和第二轮通过谋求写入时间的缩短上具有特征。

首先,命令接口电路接收从主微机提供的数据输入命令,接受它,把数据输入命令设定在状态机(控制电路)内(步骤S1)。

此外,如果地址信号从主微机提供给存储器片内,就接受它,把用于选择成为编程对象的页的地址设定在状态机内(步骤S2)。

然后,如果一页部分的编程数据经由输入输出缓存器输入到存储器片内,则这一页部分的编程数据存储到数据存储部分DS4中(步骤S3)。

然后,命令接口电路如果确认从主微机提供的写入命令,就接受它,结果在基于状态机的控制下,自动执行步骤S5到步骤S17的动作。

首先,把存储在数据存储部分DS4中的编程数据分别复制到数据存储部分DS2、DS3中(步骤S5)。

然后,如果成为编程对象的页是逻辑高位页,则在写入动作前,执行内部数据加载(步骤S6)。通过内部数据加载读出的逻辑低位页数据经由数据存储部分DS1存储到数据存储部分DS4中。

当逻辑低位页数据为“1”时,基于内部数据加载的读出数据为“0”(=“L”),数据“0”存储在数据存储部分DS4(节点N4)中。当逻辑低位页数据为“0”时,基于内部数据加载的读出数据为“1”(=“H”),数据“1”存储在数据存储部分DS4(节点N4)中。

然后,如果是对于逻辑低位页的编程,就把写入电压Vpgm设定为12V,如果是对于逻辑高位页的编程,就把写入电压Vpgm设定为13V。此外,把状态机内的编程计数器的值PC设定为0(步骤S7)。须指出的是,编程计数器的值PC表示写入动作的次数。

接着,执行写入动作(步骤S8)。

当存储在数据存储部分DS3中的编程数据为“0”时,例如向衬底和浮栅电极之间提供高电压,向浮栅电极注入电子,提高存储单元的阈值电压(“0”-编程)。当存储在数据存储部分DS3中的编程数据为“1”时,例如不向衬底和浮栅电极之间提供高电压,防止电子注入浮栅电极,使存储单元的阈值电压不变化(“1”-编程)。

在进行了写入动作后,在编程计数器的值PC中加“1”(步骤S8)。

然后,根据存储在数据存储部分DS3中的数据,判定编程检验是成为通过状态(编程结束的状态)或成为NG的状态(编程未结束的状态)(步骤S9)。

由于在最初的写入动作之后一次也未进行“检验01”、“检验00”和“检验10”,所以数据存储部分DS3存储着编程数据。

在所有列内的数据存储部分DS3(例如4256个)存储着数据“1”时,即对于逻辑低位页或逻辑高位页的编程数据都为“1”时,在全部列中,图10的N沟道MOS晶体管Qn17为断开状态,例如图8的FLAG维持“H”。

因此,判断为编程检验为通过状态(编程结束的状态),结果在状态寄存器中设定通过,结束编程动作(步骤S16)。

而至少一列内的数据存储部分DS3存储着数据“0”时,即对于逻辑低位页或逻辑高位页的编程数据的至少一个为“0”时,连接在存储数据“0”的数据存储部分DS3上的N沟道MOS晶体管Qn17(图10)是导通状态,例如图8的FLAG变为“L”。

因此,判断为编程检验为NG状态(编程未结束的状态),结果向“检验10”和“检验01”转移。

如果是对逻辑低位页的编程,则执行“检验10”(步骤S11)。

“检验10”是指对于成为编程对象的选择的存储单元,使用读出电位Vcgv10(参照图17)执行读出动作,根据由该读出动作取得的读出数据和数据存储部分DS2的数据(编程数据),决定数据存储部分DS3中新存储的数据的值的动作。

当为对逻辑低位页的编程时,当初成为编程对象的选择的全部存储单元变为“11”状态。因此,关于成为“1”-编程的对象的存储单元(与存储数据“1”的数据存储部分DS3对应的存储单元),阈值电压没有变动,所以由“检验10”读出的读出数据总是“0”。

因此,在数据存储部分DS1中存储“0”。可是,如后所述,当在数据存储部分DS2中存储着“1”时,数据存储部分DS1的数据与读出数据无关,强制变更为“1”。即该数据“1”从数据存储部分DS1再存储到数据存储部分DS3中。

而关于成为“0”-编程的对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),当阈值电压因写入动作(步骤S8)而充分上升(编程结束)时,由“检验10”读出的读出数据变为“1”。

因此,在数据存储部分DS1中存储“1”。该数据“1”从数据存储部分DS1传输给数据存储部分DS3。即数据存储部分DS3的数据从“0”变为“1”。

此外,关于成为“0”-编程的对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),当阈值电压未因写入动作(步骤S8)而充分上升(编程未结束)时,由“检验10”读出的读出数据变为“0”。

因此,在数据存储部分DS1中存储“0”。该数据“0”从数据存储部分DS1传输给数据存储部分DS3。即数据存储部分DS3的数据维持“0”。

如果是对逻辑高位页的编程,就执行“检验01”和“检验00”(步骤S12、步骤13)。

“检验01”是指对于成为编程对象的选择的存储单元,使用读出电位Vcgv01(参照图17)执行读出动作,根据由该读出动作取得的读出数据和数据存储部分DS2的数据(编程数据),决定数据存储部分DS3中新存储的数据的值的动作。

“检验00”是指对于成为编程对象的选择的存储单元,使用读出电位Vcgv00(参照图17)执行读出动作,根据由该读出动作取得的读出数据、数据存储部分DS2的数据(编程数据)和数据存储部分DS4的数据(逻辑低位页数据),决定数据存储部分DS3中新存储的数据的值的动作。

关于成为逻辑高位页数据“1”的编程(“1”-编程)对象的存储单元(与存储数据“1”的数据存储部分DS3对应的存储单元),维持“11”状态或“10”状态,所以由“检验01”读出的读出数据也总是“0”。

因此,在数据存储部分DS1中存储“0”。此外,因为在数据存储部分DS2中存储着“1”,所以数据存储部分DS1的数据与读出数据无关,强制变更为“1”。因此,数据“1”从数据存储部分DS1传输到数据存储部分DS3中。

此外,由“检验00”读出的读出数据也总是“0”。

因此,在数据存储部分DS1中存储“0”。可是,在数据存储部分DS2中存储着“1”,所以使数据存储部分DS1的数据与读出数据以及数据存储部分DS4的逻辑低位页数据无关地强制地被变更为“1”。因此,数据“1”从数据存储部分DS1传输到数据存储部分DS3中。

而关于成为逻辑高位页数据“0”的编程(“0”-编程)对象的存储单元(与存储数据“0”的数据存储部分DS3对应的存储单元),从“11”状态或“10”状态变为“00”状态后,再向“01”状态变化。

因此,最初由“检验01”读出的读出数据变为“0”。因此,在数据存储部分DS1中存储“0”。该数据“0”从数据存储部分DS1传输到数据存储部分DS3中。即到数据存储部分DS3的数据维持“0”。

然后,接着“检验01”执行“检验00”。

关于阈值电压充分上升(“00”-编程结束)的存储单元,由“检验00”读出的读出数据变为“1”。

因此,在数据存储部分DS1中存储“1”。

可是这里,数据存储部分DS1的数据受到存储在数据存储部分DS4中的逻辑低位页数据的影响。

即当逻辑低位页数据为“1”时,数据存储部分DS4(节点N4)存储着“0”(=“L”)。因此,数据存储部分DS1的数据强制变更为“0”。这意味着逻辑低位页数据为“1”时,当把“0”作为逻辑高位页数据进行编程时,使存储单元的阈值电压上升到“01”状态(参照图19)。

该数据“0”从数据存储部分DS1传输到数据存储部分DS3中。即数据存储部分DS3的数据维持“0”。

逻辑低位页数据为“0”时,数据存储部分DS4(节点N4)存储着“1”(=“H”)。因此,数据存储部分DS1的数据维持“1”。这意味着逻辑低位页数据为“0”时,当把“0”作为逻辑高位页数据进行编程时,存储单元的阈值电压停止在“00”状态(参照图19)。

该数据“1”从数据存储部分DS1传输到数据存储部分DS3中。即数据存储部分DS3的数据从“0”变为“1”。

然后,如果编程计数器的值PC达到了预先设定的最大写入次数PC max,则在状态机内的状态寄存器中设定失败(编程不良),结束编程动作(步骤S14、S17)。

此外,如果如果编程计数器的值PC比预先设定的最大写入次数PC max还小,则使写入电压Vpgm上升例如0.2V左右后(增压),执行写入动作(步骤S14、S15、S8)。

然后,根据存储在数据存储部分DS3中的数据,执行编程检验,判定编程是通过(编程结束的状态)还是NG(编程未结束的状态)(步骤S9)。

当对于逻辑高位页的编程数据为“1”(“1”-编程)时,数据存储部分DS3的数据总为“1”。

此外,对于逻辑高位页的编程数据为“0”,当逻辑低位页数据为“0”时(“00”-编程),当“00”-编程结束时,数据存储部分DS3的数据通过“检验00”从“0”变为“1”。

此外,对于逻辑高位页的编程数据为“0”,当逻辑低位页数据为“1”时(“01”-编程),当“01”-编程结束时,数据存储部分DS3的数据通过“检验01”从“0”变为“1”。

因此,对于成为编程对象的选择的全部存储单元,当编程(“00”-编程或“01”-编程)结束时,全部数据存储部分DS3存储着数据“1”。即在全部列中,图10的N沟道MOS晶体管Qn17是断开状态,图8的FLAG变为“H”(编程检验通过的状态)。而且,在状态机内的状态寄存器中设定通过(编程结束),结束编程动作(步骤S16)。

此外,对于成为编程对象的选择的存储单元的至少一个,编程(“00”-编程或“01”-编程)未结束时,至少一个数据存储部分DS3存储着数据“0”。即在至少一列中,图10的N沟道MOS晶体管Qn17变为导通状态,图8的FLAG变为“L”(编程检验为NG的状态),再次重复检验读出和写入动作(步骤S8~S17)。

这样,根据存储在数据存储部分DS3中的数据,能判断编程是否结束。

②基于动作波形的动作说明

下面,参照动作定时图进行具体的动作说明。

编程动作(通过写入)的主要部分由从数据存储部分DS4向数据存储部分DS2、DS3的编程数据的复制动作、内部数据加载动作、从数据存储部分DS2向数据存储部分DS3的编程数据的复制动作、写入动作、检验动作(检验10/00/01)构成。

此外,编程动作(快速通过写入)的主要部分由从数据存储部分DS4向数据存储部分DS2、DS3的编程数据的复制动作、内部数据加载动作、写入动作、检验动作(检验10/00/01)构成。

因此,就这些动作加以说明。

在以下说明的工作定时图中,只要未特别表示,则“L”电平为Vss(例如,0V),“H”电平为Vdd(例如,3V)。此外,在动作定时图中,选择一个块BLOCKi,选择该块BLOCKi内的字线WL2-i和第奇数条位线BLek(参照图3)。

[1]从DS4向DS2、DS3的复制动作

图31表示从数据存储部分DS4向数据存储部分DS2、DS3的编程数据的复制动作的动作波形图。图32表示从数据存储部分DS4向数据存储部分DS2、DS3的编程数据的复制动作的数据流。

该复制动作相当于图28和图30的步骤S5。

首先,在定时CPCLK1中,控制信号VPRE变为“H”,在定时CPCLK2,控制信号BLPRE变为4.5V。结果,N沟道MOS晶体管Qn6(图10)变为导通状态,数据存储部分DS1(节点N2)充电为“H”电平(Vdd)。

然后,在定时CPCLK6,控制信号BLC2变为“H”,则N沟道MOS晶体管Qn12变为导通状态,数据存储部分DS1和数据存储部分DS4电连接。

而且,如果数据存储部分DS4存储着“1”(=“H”)作为编程数据,则数据存储部分DS1即电容器C1的一端(节点N2)维持“H”电平(Vdd)。此外,如果数据存储部分DS4存储着“0”(=“L”)作为编程数据,则数据存储部分DS1即电容器C1的一端(节点N2)的电荷放电,数据存储部分DS1的数据从“H”变为“L”。

而在定时CPCLK8,控制信号SEN1、LAT1变为“L”,此外在定时CPCLK9,通过控制信号EQ1变为“H”,数据存储部分DS3的状态被复位。

在定时CPCLK1,如果控制信号BLC1变为“H”,则N沟道MOS晶体管Qn10变为导通状态,电连接了数据存储部分DS1和数据存储部分DS3。此外,在定时CPCLK12,如果控制信号SEN1变为“H”,则数据存储部分DS1即电容器C1的一端(节点N2)的数据由时钟同步式倒相器CI1读出。

然后在定时CPCLK13,如果控制信号LAT1变为″H″,则数据存储部分DS1的数据存储到数据存储部分DS3中。最后在定时CPCLK14,如果控制信号DTG变为4.5V,则N沟道MOS晶体管Qn9变为导通状态,数据存储部分DS3的数据传输给数据存储部分DS2。此外,在定时CPCLK15,如果控制信号DTG变为″L″,则数据存储部分DS3的数据存储到数据存储部分DS2中。

例如,数据存储部分DS1、DS4的数据如果为“1”(节点N2、N4为“H”),则数据存储部分DS2、DS3的数据也变为“1”(节点N3、N6为“H”)。此外,如果数据存储部分DS1、DS4的数据如果为“0”(节点N2、N4为“L”),则数据存储部分DS2、DS3的数据也变为“0”(节点N3、N6为“L”)。

须指出的是,从DS4向DS2、DS3的复制动作对全部列(例如4256个)的数据电路同时进行。

[2]内部数据加载动作

图33和图34表示内部数据加载动作的动作波形图。图35表示内部数据加载动作的数据流。

内部数据加载动作相当于图28和图30的步骤S6。

内部数据加载动作是指进行了逻辑低位页数据的编程后,进行逻辑高位页数据的编程时,为了决定在逻辑高位页数据的编程中成为目标的阈值电压,预先读出逻辑低位页数据的动作。

具体而言,把读出电位(选择的字线WL2-i的电位)设定为Vcgr10(例如0V),识别存储单元的数据为“11”(逻辑低位页数据为“1”)或“10”(逻辑低位页数据为“0”)。

内部数据加载动作由与数据读出有关的部分(RCLK 1-E、SCLK 1-E、RCV 1-E)和与数据传输有关的部分(EXCLK过程)构成。

[2]-1数据读出

首先,向位线一侧的选择栅线SGD和未选择的字线WL0-i、WL1i、WL3i分别提供传输电位Vread(例如,4.5V),向选择的字线WL2-i提供读出电位Vcgr10(例如,0V)(RCLK1-2)。

控制信号BLPRE变为“H”,N沟道MOS晶体管Qn6(图10)变为导通状态。此外,通过控制信号BLCLAMP变为Vclamp(例如2V)、控制信号BLSe变为Vsghh(例如4.5V),把第奇数条位线BLek预先充电为给定电位(例如1V左右)。而控制信号BIASo变为Vsghh(例如,4.5V),所以第偶数条位线BLok固定在Vss(,例如0V),作为屏蔽位线起作用(RCLK2-4)。

然后,控制信号BLCLAMP变为Vss(例如0V),控制信号BLPRE变为“L”,第奇数条位线BLek变为浮置状态(RCLK5-7)。

如果把源线一侧的选择栅线SGS的电位设定为传输电位Vread,则按照选择了的存储单元的状态,即存储在该存储单元中的数据的值,表现对位线BLek的电位的影响。

即,选择了的存储单元的数据为“11”时,由于读出电位Vcgr10,该选择的存储单元变为导通状态。因此,位线BLek的电荷放电,位线BLek的电位下降到0.8V以下(选择块内的存储单元因Vread而是导通状态)。

而当选择了的存储单元的数据为“10”时,由于读出电位Vcgr10,该选择的存储单元不变为导通状态。因此,位线BLek的电荷不放电,位线BLek维持预充电电位(约1V)(RCLK6-E)。

由于控制信号BLPRE变为4.5V左右,控制信号VPRE变为Vdd(例如3V),数据存储部分DS1的电容器C1的一端即节点N2被充电为Vdd。然后,控制信号BLCLAMP如果变为Vsense(例如,1.8V),则数据存储部分DS1的电容器C1的一端电位变化如下。

即位线BLek的电位保持预充电电位(约1V)时(存储单元的数据为“10”时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是断开状态,数据存储部分DS1的电容器C1的一端电位被维持在Vdd(“H”)。

而当位线BLek的电位为0.8V以下时(存储单元的数据为“11”时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是导通状态,数据存储部分DS1的电容器C1的一端的电荷放电到位线BLek中,该电位下降到比Vdd还低的值(“L”)(SCLK4-5)。

结果,在数据存储部分DS1(电容器C1的一端)中存储有基于读出电位Vcgr10的读出数据。即当存储单元的数据为“11”时,存储“L”即数据“1”,当存储单元的数据为“10”时,存储“H”即数据“0”。

须指出的是,在内部数据加载动作中,“L”=“0”和H=“1”的关系颠倒。即变为“L”=“1”和H=“0”的关系。

[2]-2数据传输

在内部数据加载动作中,把存储单元的数据读出到数据存储部分DS1中后,执行把存储在该数据存储部分DS1中的读出数据向数据存储部分DS4传输的数据传输。该工作根据图34所示的EXCLK过程进行。

首先,控制信号SEN1、LAT1都变为“L”(EXCLK6),并且通过控制信号EQ1变为“H”(EXCLK7-8),构成数据存储部分DS4的双稳态多谐振荡器电路(图10)的状态被复位。

然后控制信号BLC2变为4.5V(EXCLK9),N沟道MOS晶体管Qn12变为导通状态。结果,数据存储部分DS1和数据存储部分DS4彼此电连接。

如果控制信号SEN2变为“H”(EXCLK10),则存储在数据存储部分DS1(电容器C1的一端)中的读出数据经由MOS晶体管Qn12由构成数据存储部分DS4的时钟同步式倒相器CI4读出。此外,如果控制信号LAT2变为“H”(EXCLK11),则该读出数据存储到数据存储部分DS4中。

须指出的是,内部数据加载动作对全部列(例如4256个)的数据电路同时进行。

[3]从DS2向DS3的复制(复制回)动作

图36表示从数据存储部分DS2向数据存储部分DS3的编程数据的复制动作的动作波形图。图37表示从数据存储部分DS2向数据存储部分DS3的编程数据的复制动作的数据流。

该复制动作相当于图29的步骤S17。

首先,在定时CPCLK3,如果控制信号BLPRE变为“H”,则N沟道MOS晶体管Qn6(图10)变为导通状态。这时,控制信号VPRE保持Vss(0V),所以数据存储部分DS1(节点N2)被充电为“L”电平(Vss)。

然后,在定时CPCLK5,控制信号VREG变为“H”。此外,如果控制信号REG变为4.5V,则N沟道MOS晶体管Qn7变为导通状态,电连接数据存储部分DS1和数据存储部分DS2。

而且,如果数据存储部分DS2(节点N6)存储“1”(=“H”)作为编程数据,则N沟道MOS晶体管Qn8的栅极电位由于自举现象从Vdd左右上升到5V左右。结果VREG(=Vdd)经由N沟道MOS晶体管Qn7、Qn8传输给数据存储部分DS1。数据存储部分DS1即电容器C1的一端(节点N2)的电平从“L”变为“H”。

此外,如果如果数据存储部分DS2(节点N6)存储“0”(=“L”)作为编程数据,则N沟道MOS晶体管Qn8的栅极电位变为Vss(=0V)。结果,VREG(=Vdd)不向数据存储部分DS1传输,数据存储部分DS1即电容器C1的一端(节点N2)维持“L”电平。

在定时CPCLK8,控制信号SEN1、LAT1变为“L”,此外,在定时CPCLK9,通过控制信号EQ1变为“H”,数据存储部分DS3的状态被复位。

在定时CPCLK11,如果控制信号BLC1变为“H”,则N沟道MOS晶体管Qn10变为导通状态,数据存储部分DS1和数据存储部分DS3电连接。此外,在定时CPCLK12,如果控制信号SEN1变为“H”,则由时钟同步式倒相器CI1读出数据存储部分DS1,即电容器C1,的一端(节点N2)的数据。

然后,在定时CPCLK13,如果控制信号LAT1变为″H″,则数据存储部分DS1的数据被存储到数据存储部分DS3中。

通过以上的动作,从数据存储部分DS2向数据存储部分DS3的编程数据的复制动作,即所谓的复制回(copyback)动作,结束。

须指出的是,从DS2向DS3的复制动作在全部列(例如4256个)的数据电路中同时进行。

[4]写入动作(Write)

图38表示写入动作的动作波形图。图39表示写入动作中的数据流。

须指出的是,只要不图示,“L”电平为0V,“H”电平为Vdd(例如3V)。此外,在选择的块内,选择的字线是WL2,选择的位线是Ble。

写入动作相当于图28和图30的步骤S8、图29的步骤S25。

首先,在定时PCLK1,控制信号BLCLAMP、BLC1变为4.5V。此外,如果在定时PCLK3,BLSe变为4.5V,则位线BLek和数据存储部分DS3电连接。

数据存储部分DS3(节点N3)的数据为“1”时,位线BLek充电为Vdd。此外,数据存储部分DS3(节点N3)的数据为“0”时,位线BLek充电为Vss(0V)。

此外,在定时PCLK3,控制信号BLCRL变为″H″,控制信号BIASo变为4.5V。结果位线BLeo充电为Vdd。

然后,在定时PCLK6,向未选择的字线WL0-i、WL1-i、WL3-i提供10V的电压,在定时PCLK7,向选择的字线WL2-i提供Vpgm(最初12V或13V的电压。按照写入次数,每次上升0.2V)。结果,执行了对存储单元的编程。

例如,当存储在数据存储部分DS3中的数据为“1”时,位线BLek是Vdd,字线(控制栅电极)WL2-i和存储单元的沟道间的电位差未变成足以向存储单元的浮栅电极注入电子的值。

而当存储在数据存储部分DS3中的数据为“0”时,位线BLek为0V,字线(控制栅电极)WL2-i和存储单元的沟道间的电位差变为足以向存储单元的浮栅电极注入电子的值。

因此,当存储在数据存储部分DS3中的数据为“1”时,存储单元的阈值电压不上升,当存储在数据存储部分DS3中的数据为“0”时,存储单元的阈值电压上升。

在QPW(快速通过写入)时,在定时PCLK4,控制信号VREG变为Vdd,在定时PCLK5,控制信号BLC1变为“L”,在定时PCLK6,控制信号REG设定为2.0V。

因此,如果数据存储部分DS2的数据(编程数据)为“1”时,N沟道MOS晶体管Qn8的栅极由于自举现象从Vdd左右上升到5V左右。因此,VREG(=Vdd)被限制在控制信号REG(=2.0V),传输给位线BLek。

结果,位线BLek的电位与数据存储部分DS3中存储的数据无关,变为1V左右。

如果数据存储部分DS2的数据(编程数据)为“0”时,N沟道MOS晶体管Qn8的栅极为0V,所以位线BLek的电位维持在Vdd(数据存储部分DS3的数据为“1”)或0V(数据存储部分DS3的数据为“0”)

须指出的是,写入动作对连接在选择的字线WL2-i上的4256个存储单元同时进行。

[5]检验动作(检验10/00/01)

图40和图41表示检验动作中的检验读出的动作波形图。图42~图45表示检验读出中的数据流。

此外,只要未图示,“L”电平为0V,“H”电平为Vdd(例如3V)。此外,在选择的块内,选择的字线是WL2,选择的位线为Ble。

检验动作由检验读出和完成检测(Completion Dedection)构成。完成检测是指根据由检验读出而读出的数据,检测对选择的全部存储单元是否结束了编程的动作。这里,主要就检验读出加以说明。

检验读出相当于图28的步骤S11、S12、图29的步骤S20、S21、S22和图30的步骤S11、S12、S13。

检验读出是在写入动作后进行,从存储单元读出用于判定存储单元的阈值电压是否达到了给定电平(完成检测)的数据的动作。

在本例中,说明采用通过写入(2度写入)时的检验读出。如上所述,第一次的编程称作第一轮通过,第二次的编程称作第二轮通过。并行处理第一轮通过和第二轮通过的编程方法称作QPW(快速通过写入)。在QPW时,例如状态机(控制电路)内的QPW寄存器变为“1”,在通常的通过写入时,状态机内的QPW寄存器变为“0”。

首先,在定时RCLK1-2,向位线一侧的栅选择线SGD和未选择的字线WL0-i、WL0-1、WL3-i分别提供传输电位Vread(例如4.5V),向选择的字线WL2-i提供检验读出电位Vcgvxx。

检验读出电位Vcgvxx按照检验读出的种类变化如下。

[通过写入时]

VERIFY10 1st通过→Vcgvxx=0.25V,VERIFY10 2nd通过→Vcgvxx=0.40V,VERIFY00 1st通过→Vcgvxx=1.25V,VERIFY002nd通过→Vcgvxx=1.40V,VERIFY01→Vcgvxx=2.40V。

[QPW时]

VERIFY10→Vcgvxx=0.25V,VERIFY00→Vcgvxx=1.25V,VERIFY01→Vcgvxx=2.25V。

在定时RCLK 2-4,控制信号BLPRE变为“H”,N沟道MOS晶体管Qn6(图10)变为导通状态。此外,控制信号BLCLAMP变为Vclamp(例如2V),控制信号BLSe变为Vsghh(例如4.5V),第奇数条位线BLek电连接在VPRE(=Vdd)上。

结果,位线BLek预先充电为由N沟道MOS晶体管Qn5的阈值电压限制的给定电位,例如1V左右。此外,控制信号BIASo变为Vsghh(例如4.5V),所以第偶数条位线BLok固定在Vss(例如0V),作为屏蔽位线起作用。

如上所述,作为原则,对于位线BLek的预充电电源为VPRE。可是,关于通过写入动作中的第二轮通过时的“检验00(第二轮通过)”和QPW动作中的“检验00”,对于位线的预充电电源成为数据存储部分DS4。

因此,在“检验00(第二轮通过)”和“检验00”中,在定时RCLK2,控制信号BLC2变为“H”,控制信号BLPRE在定时RCLK2-6保持“L”不变。

结果,位线BLek电连接在数据存储部分DS4上。而且,当数据存储部分DS4(节点N3)的数据为“1”时,位线BLek预先充电到由N沟道MOS晶体管Qn5的阈值电压限制的给定电位,例如1V左右。此外,当数据存储部分DS4(节点N3)的数据为“0”时,位线BLek预先充电到0V。

然后,在定时RCLK5-7中,控制信号BLCLAMP变为Vss(例如0V),控制信号BLPRE变为“L”,位线BLek变为浮置状态。

如果把源线一侧的选择栅线SGS的电位设定为传输电位Vread,则按照选择的存储单元的状态,即该存储单元的现在的阈值电压,表现对存储单元的影响。

即,选择的存储单元的阈值电压比选择的字线WL2-i的电位(检验电位)Vcgxx低时,由该检验电位Vcgxx选择的存储单元变为导通状态。因此,位线BLek的电荷放电,位线BLek的电位下降到0.8V以下(选择块内的未选择的存储单元由于Vread,是导通状态)。

而选择的存储单元的阈值电压比检验读出电位Vcgvxx还高时,由该检验读出电位Vcgvxx选择的存储单元不变为导通状态,位线BLek维持在预充电电位(约1V)。

须指出的是,在“检验00(第二轮通过)”和“检验00”中,位线BLek预先充电为0V,所以与选择的存储单元的状态无关,位线BLek总是0V。

在定时RCLK8-E如果控制信号BLPRE变为“H”,数据存储部分DS1的电容器C1的一端即节点N2充电为VPRE(=0V)。此外,如果不是QPW动作(QPW寄存器的值=“0”),则然后执行图41所示的EXCLK过程(SCLK1-2)。

首先,在定时EXCLK2,控制信号VREG变为“H”。此外,如果控制信号VREG变为4.5V,则N沟道MOS晶体管Qn7变为导通状态,所以数据存储部分DS1的电容器C1的一端(节点N2)的电位受存储在数据存储部分DS2中的数据的影响。

例如,当存储在数据存储部分DS2中的数据(编程数据)为“1”时,N沟道MOS晶体管Qn8的栅极电位由于自举现象从Vdd程度上升到5V左右,VREG(=Vdd)传输给数据存储部分DS1的电容器C1的一端(节点N2)。

此外,存储在数据存储部分DS2中的数据(编程数据)为“0”时,N沟道MOS晶体管Qn8的栅极电位为0V,所以VREG(=Vdd)传输给数据存储部分DS1的电容器C1的一端(节点N2)。即数据存储部分DS1的电容器C1的一端电位不变。

此外,在定时EXCLK4-5,如果控制信号DTG变为4.5V,则数据存储部分DS3的数据传输给数据存储部分DS2。

然后,控制信号SEN1、LAT1都变为″L″(EXCLK6),并且通过控制信号EQ1变为″H″(EXCLK7-8),构成数据存储部分DS3的双稳态多谐振荡器电路(图10)的状态被复位。

然后,控制信号BLC1变为4.5V(EXCLK9),N沟道MOS晶体管Qn10变为导通状态。结果,数据存储部分DS1和数据存储部分DS3彼此电连接。

如果控制信号SEN1变为“H”(EXCLK10),则存储在数据存储部分DS1(电容器C1的一端)中的数据经由MOS晶体管Qn10由构成数据存储部分DS3的时钟同步式倒相器CI1读出。此外,如果控制信号LAT1变为“H”(EXCLK11),则该数据存储到数据存储部分DS3中。

在定时SCLK2,通过把控制信号BLPRE变为4.5V左右、控制信号VPRE变为Vdd(例如3V),数据存储部分DS1的电容器C1的一端即节点N2被充电为Vdd。然后,如果控制信号BLCLAMP变为Vsense(例如1.8V),则数据存储部分DS1的电容器C1的一端电位作如下变化。

即当位线BLek的电位为预充电电位(约1V)时(存储单元的阈值电压比Vcgvxx还高时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是断开状态,数据存储部分DS1的电容器C1的一端电位维持在Vdd(“H”)。

而当位线BLek的电位为0.8V以下时(存储单元的阈值电压比Vcgvxx还低时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是导通状态,数据存储部分DS1的电容器C1的一端的电荷放电到位线BLek中,其电位下降到比Vdd还低的值(“L”)(SCLK4-5)。

结果,在数据存储部分DS1(电容器C1的一端)中存储了基于检验读出电位Vcgvxx的读出数据。即存储单元的阈值电压比Vcgvxx还低时,在数据存储部分DS1中存储″L″,即数据″0″,当存储单元的阈值电压比Vcgvxx还高时,在数据存储部分DS1中存储″H″,即数据″1″。

然后,执行图41所示的EXCLK过程(SCLK5-E)。关于图41的EXCLK过程,已经进行了说明,所以这里省略了它的说明。

关于定时QPWCLK 1-E的动作,如果不是QPW动作(QPW寄存器的值=“0”),就省略。

如果是QPW动作(QPW寄存器的值=“1”),则通过状态机执行QPWCLK过程(QPWCLK1-E)。

在QPW时,在定时SCLK6,选择的字线WL2-i的电位(检验电位)Vcgvxx上升0.15V左右。即Vcgvxx变为4.5V+0.15V。

在定时QPWCLK2,通过控制信号BLPRE变为4.5V左右,控制信号VPRE变为Vdd(例如3V),数据存储部分DS1的电容器C1的一端即节点N2充电为Vdd。然后,在定时QPWCLK4,如果控制信号BLCLAMP变为Vsense(例如,1.8V),数据存储部分DS1的电容器C1的一端电位作如下变化。

即,当位线BLek的电位为预充电电位(约1V)时(存储单元的阈值电压比Vcgvxx还高时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是断开状态,数据存储部分DS1的电容器C1的一端电位维持在Vdd(“H”)。

而当位线BLek的电位为0.8V以下时(存储单元的阈值电压比Vcgvxx还低时),N沟道MOS晶体管(箝位晶体管)Qn5(图10)是导通状态,数据存储部分DS1的电容器C1的一端的电荷放电到位线BLek中,其电位下降到比Vdd还低的值(“L”)(QPWCLK4-5)。

结果,在数据存储部分DS1(电容器C1的一端)中存储了基于检验读出电位Vcgvxx的读出数据。即存储单元的阈值电压比Vcgvxx还低时,在数据存储部分DS1中存储″L″,即数据″0″,当存储单元的阈值电压比Vcgvxx还高时,在数据存储部分DS1中存储″H″,即数据″1″。

然后,执行图41所示的EXCLK过程(QPWCLK5-E)。关于图41的EXCLK过程,已经进行了说明,所以这里省略了它的说明。

须指出的是,检验动作对连接在选择的字线WL2-i上的4256个存储单元同时进行。

4.其他

在本实施例中,以多值NAND型闪存为例进行了说明,但是本发明当然能应用于其他类型的多值存储器中。例如,作为存储单元阵列,可以是NOR型、AND型(A.Nozoe:ISSCC,Digest ofTechnichal Papers,1995)、DINOR型(S.Kobayashi:ISSCC,Digest of Technichal Papers,1995)、Virtual Ground Array型(Lee,et al.:Syposiam on VLSI Circuits,Digest of TechnichalPapers,1994)、3-tr NAND型、4-tr NAND型等。

此外,本发明并不局限于闪存(Flash memory),例如也能应用于掩模ROM、EPROM等非易失性半导体存储器中。

如上所述,根据本发明,即使把向存储单元存储的数据多值化,芯片面积也不极端增加,此外,能提供可应用于能以高精度控制存储单元的阈值电压的2度写入法的闪存的数据电路。