WO2019047489A1 - 铁电存储集成电路及其操作方法和制备方法 - Google Patents

铁电存储集成电路及其操作方法和制备方法 Download PDFInfo

- Publication number

- WO2019047489A1 WO2019047489A1 PCT/CN2018/077485 CN2018077485W WO2019047489A1 WO 2019047489 A1 WO2019047489 A1 WO 2019047489A1 CN 2018077485 W CN2018077485 W CN 2018077485W WO 2019047489 A1 WO2019047489 A1 WO 2019047489A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- ferroelectric

- electrode

- single crystal

- memory cell

- ferroelectric memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/22—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using ferroelectric elements

- G11C11/225—Auxiliary circuits

- G11C11/2273—Reading or sensing circuits or methods

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/30—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the memory core region

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/22—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using ferroelectric elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/22—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using ferroelectric elements

- G11C11/221—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using ferroelectric elements using ferroelectric capacitors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/22—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using ferroelectric elements

- G11C11/225—Auxiliary circuits

- G11C11/2259—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/22—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using ferroelectric elements

- G11C11/225—Auxiliary circuits

- G11C11/2275—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/30—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having three or more electrodes, e.g. transistors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/004—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/77—Array wherein the memory element being directly connected to the bit lines and word lines without any access device being used

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/79—Array wherein the access device being a transistor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/82—Array having, for accessing a cell, a word line, a bit line and a plate or source line receiving different potentials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/021—Formation of switching materials, e.g. deposition of layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/823—Device geometry adapted for essentially horizontal current flow, e.g. bridge type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

- H10N70/8836—Complex metal oxides, e.g. perovskites, spinels

Definitions

- the invention belongs to the technical field of ferroelectric storage, and relates to a ferroelectric memory array based on electric domain wall conduction, a ferroelectric memory integrated circuit, an operating method thereof and a preparation method. More particularly, it relates to a crossbar structure and a ferroelectric memory integrated circuit design of a switching transistor and a ferroelectric memory cell (1T1R) structure and a method of fabricating the same.

- ferroelectric memories use ferroelectric materials to maintain polarization and store information non-volatilely.

- the polarization direction of the ferroelectric capacitor coincides with the voltage direction. After the voltage is removed, the polarization direction of the ferroelectric capacitor remains unchanged; when the reverse polarity is applied to the capacitor At a large voltage, the polarization direction of the capacitor is reversed, and after the voltage is removed, the polarization direction remains unchanged.

- the Boolean logic amount "1" or "0" is stored depending on the polarization direction of the ferroelectric capacitor.

- ferroelectric capacitors have the advantages of high remanent polarization, good coercive field, high fatigue resistance and low leakage current. They have been used in ferroelectric memory integrated circuits since the 1950s. See JR published in 1959. U.S. Patent 2,876,436 to Anderson et al. Since then, the field of ferroelectric memory technology has focused on the improvement of memory cell structure and read and write circuits. For example, S. Sheffield Eaton, J., et al., US Pat. No. 4,873,664, published in 1989, Kenneth J. Mobely et al. U.S. Patent No. 4, 888, 733, issued to U.S. Patent No. 5, 552, 964 issued to the United States of It involves 2T2C, 1T1C, reference circuit and addressing circuit. However, the principle of the read circuit is substantially the same, mainly reading the charge in the ferroelectric capacitor C.

- MFIS FET metal-ferroelectric-insulator-semiconductor field effect transistor structure

- a ferroelectric memory integrated circuit comprising:

- ferroelectric memory array having a memory cell array formed on a ferroelectric single crystal layer

- each of the memory cell arrays is correspondingly provided with a first electrode and a second electrode, and a polarization direction of the domains of the ferroelectric single crystal layer is substantially non-parallel to the ferroelectric single crystal layer a normal direction, when an electrical signal is applied between the first electrode and the second electrode, a ferroelectric single crystal layer for forming the memory cell substantially between the first electrode and the second electrode Reversing the domains to establish a domain wall conductive path connecting the first electrode and the second electrode;

- each ferroelectric memory cell of the ferroelectric memory array is formed mainly by one memory cell in the memory cell array, or is mainly formed by one of the memory cell array and the memory cell is electrically connected to the silicon cell A transistor on the silicon base of the base read and write circuit is formed.

- a ferroelectric memory array comprising an array of memory cells formed on a ferroelectric single crystal layer;

- each of the memory cell arrays is correspondingly provided with a first electrode and a second electrode, and a polarization direction of the domains of the ferroelectric single crystal layer is substantially non-parallel to the ferroelectric single crystal layer a normal direction, when an electrical signal is applied between the first electrode and the second electrode, a ferroelectric single crystal layer for forming the memory cell substantially between the first electrode and the second electrode Reversing the domains to establish a domain wall conductive path connecting the first electrode and the second electrode;

- each ferroelectric memory cell of the ferroelectric memory array is formed mainly by one memory cell in the memory cell array.

- a ferroelectric memory integrated circuit as described above, comprising:

- the step of reading the stored information applying a read signal of the first direction between the first electrode and the second electrode, the voltage of the read signal being smaller than a coercive field voltage of the memory cell.

- a method for fabricating the above-described ferroelectric memory integrated circuit comprising the steps of:

- An insulating layer is grown on the ferroelectric single crystal substrate

- the silicon-based read/write circuit and the bit line are formed on the silicon-based thin film layer.

- a method for fabricating the above-described ferroelectric memory integrated circuit comprising the steps of:

- a method for fabricating the above-described ferroelectric memory integrated circuit comprising the steps of:

- a second electrode that is substantially vertically aligned with the first electrode and a plate line that is connected to the second electrode are patterned over the ferroelectric single crystal thin film layer.

- Figure 1 is a cross-sectional view showing the crossbar structure of a ferroelectric memory cell of a ferroelectric memory integrated circuit in accordance with a first embodiment of the present invention.

- FIG. 2 is a cross-sectional view showing the structure of a 1T1R structure of a ferroelectric memory cell of a ferroelectric memory integrated circuit in accordance with a second embodiment of the present invention.

- Figure 3 is a cross-sectional view showing the crossbar structure of a ferroelectric memory cell of a ferroelectric memory integrated circuit in accordance with a third embodiment of the present invention.

- FIG. 4 is a cross-sectional view showing the structure of a 1T1R structure of a ferroelectric memory cell of a ferroelectric memory integrated circuit in accordance with a fourth embodiment of the present invention.

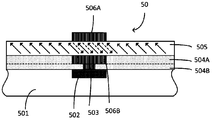

- Figure 5 is a cross-sectional view showing the crossbar structure of a ferroelectric memory cell of a ferroelectric memory integrated circuit in accordance with a fifth embodiment of the present invention.

- Figure 6 is a cross-sectional view showing the structure of a 1T1R structure of a ferroelectric memory cell of a ferroelectric memory integrated circuit in accordance with a sixth embodiment of the present invention.

- Fig. 7 is a circuit connection diagram of a crossbar structure of a ferroelectric memory cell according to the embodiment shown in Fig. 1, Fig. 3 or Fig. 5.

- Figure 8 is a view showing a configuration operation of writing storage information "1" to a certain ferroelectric memory cell of the ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 1, Figure 3 or Figure 5.

- Figure 9 is a view showing a configuration operation of writing information "0" to a ferroelectric memory cell of the ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 1, Figure 3 or Figure 5.

- Figure 10 is a view showing a configuration operation of reading information from a ferroelectric memory cell of a ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 1, Figure 3 or Figure 5.

- Figure 11 is a circuit connection diagram of a 1T1R structure of a ferroelectric memory cell in accordance with the embodiment shown in Figures 2, 4 or 6.

- Figure 12 is a diagram showing the configuration operation of writing storage information "1" to a certain ferroelectric memory cell of the ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 2, Figure 4 or Figure 6.

- Figure 13 is a view showing the configuration operation of writing information "0" to a certain ferroelectric memory cell of the ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 2, Figure 4 or Figure 6.

- Figure 14 is a diagram showing the operation of reading information from a ferroelectric memory cell of a ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 2, Figure 4 or Figure 6.

- 15 is an SEM image of a sample of a ferroelectric memory array of a ferroelectric memory cell having a crossbar structure in accordance with an embodiment of the present invention.

- Figure 16 is a diagram showing the I-V characteristics of the ferroelectric memory cell of the ferroelectric memory array in accordance with the embodiment of Figure 15, wherein the ordinate is in logarithmic form and the scan voltage ranges from 0 to +10V.

- Figure 17 is a diagram showing the I-V characteristics of the ferroelectric memory cell of the ferroelectric memory array in accordance with the embodiment of Figure 15, wherein the scan voltage ranges from -10V to +10V.

- Figure 18 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the first embodiment shown in Figure 1.

- Figure 19 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the second embodiment shown in Figure 2.

- Figure 20 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the third embodiment shown in Figure 3.

- Figure 21 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the fourth embodiment shown in Figure 4.

- Figure 22 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the fifth embodiment shown in Figure 5.

- Figure 23 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the sixth embodiment shown in Figure 6.

- the domain direction or the polarization direction is exemplarily given for clarity of description, but it should be understood that the domain direction or polarization direction of the ferroelectric memory is not limited to the embodiment as shown in the figure. The direction of the out.

- the ferroelectric single crystal refers to a single crystal structure or a single crystal-like structure in which a "grain boundary" of a polycrystalline structure is not present internally; the memory cell of the memory cell array formed thereon is also a single crystal structure, and the size of the memory cell is not limit.

- the ferroelectric single crystal may be a ferroelectric single crystal thin film layer or a ferroelectric single crystal substrate, and the ferroelectric single crystal thin film layer may be a single crystal thin film formed by epitaxial single crystal growth, or separated from the ferroelectric single crystal substrate or The formed film layer is cut.

- the ferroelectric memory integrated circuit includes a ferroelectric memory array, and the plurality of ferroelectric memory cells in the ferroelectric memory array are arranged in rows and columns; thus, by reading and writing circuits, corresponding rows are corresponding columns

- the ferroelectric memory cell can be selected for a corresponding write or read operation. It should be noted that the specific number, arrangement, and the like of the ferroelectric memory cells in the ferroelectric memory array are not limited.

- the ferroelectric memory integrated circuit 10 of this embodiment includes a ferroelectric single crystal substrate 101 which is formed by etching on a ferroelectric single crystal substrate 101 and formed at the left and right ends of each memory cell 102.

- the first electrode 103A and the second electrode 103B; in one embodiment, the ferroelectric memory integrated circuit 10 further includes an insulating layer 105 over the above structure of the ferroelectric single crystal substrate 101 and overlying the insulating layer 105 Silicon based read and write circuit 106, plate line 104 and bit line 108.

- the plate line 104 is also referred to as a "Plate Line” and may also be a drive line.

- the bit line 108 may pass through the contact hole 107 formed in the insulating layer 105 and the corresponding column of the memory unit 102.

- the second electrodes 103B are connected.

- the ferroelectric memory integrated circuit 20 includes a ferroelectric single crystal substrate 201.

- the memory cell array 202 is etched on the ferroelectric single crystal substrate 201, and the first electrode 203A and the left and right ends of the memory cell array 202 are respectively formed.

- the second electrode 203B is formed in one embodiment, the ferroelectric memory integrated circuit 20 further includes an insulating layer 205 and a silicon-based read/write circuit 206 and a transistor array 209 disposed on the insulating layer 205.

- the transistor array 209 is formed on the silicon-based read/write circuit 206.

- each transistor of the transistor array 209 is used to control the gating of the corresponding memory cell, and is therefore also referred to as a switching transistor; each transistor of the transistor array 209 has a gate 209C, a source 209A and a drain 209B, The on-off between the source 209A and the drain 209B is controlled by controlling the switching control signal applied to the gate 209C.

- the ferroelectric memory integrated circuit 20 further includes a plate line 204, a bit line 211, and a word line 210.

- the plate line 204 is also referred to as a "Plate Line" and may also be a drive line.

- the bit line 208 may pass through the contact hole 207 formed in the insulating layer 205 and the corresponding column of the memory unit 202.

- the second electrode 203B is connected, and the bit line 208 is also connected to, for example, the drain 209B of the transistor of the corresponding column.

- the ferroelectric single crystal substrate 101 or 201 may be, but not limited to, a ferroelectric single crystal epitaxial wafer, for example, on a conventional single crystal substrate (e.g., 100 orientation of a SrTiO 3 single crystal substrate).

- a ferroelectric thin film (such as BiFeO 3 , etc.) is formed.

- the ferroelectric memory integrated circuit 30 may include a silicon-based read/write circuit 301, an insulating layer 302, a ferroelectric single crystal thin film layer 303, a memory cell array 304 etched on the ferroelectric single crystal thin film 303, The first electrode 305A and the second electrode 305B, the plate line 306, and the bit line 308 formed at both ends of the memory cell array 304; wherein the silicon-based read/write circuit 301 can be formed, for example, by a single crystal silicon substrate or the like, and the insulating layer 302

- the ferroelectric single crystal thin film layer 303 is mainly used to form the memory cell array 304.

- the memory cells of the memory cell array 304 pass through the contact holes 307 in the insulating layer 302.

- the bit line 308 formed over the silicon-based read/write circuit 301 is

- the ferroelectric memory integrated circuit 40 may include a silicon-based read/write circuit 401 and a transistor array 409.

- the silicon-based read/write circuit 401 may be formed, for example, by a single crystal silicon substrate or the like, and the transistor array 409 may also pass through a single crystal.

- the ferroelectric memory integrated circuit 40 may further include an insulating layer 402, a ferroelectric single crystal thin film layer 403, and a memory cell array 404 formed on the ferroelectric single crystal film 403, on the left and right of the memory cell array 404.

- the first electrode 405A and the second electrode 405B respectively formed at both ends further include a plate line 406, a bit line 411, and a word line 410.

- each transistor in the transistor array 409 is used to gate a memory cell in the memory cell array 404 to which it is connected, having a gate 409C, a source 409A and a drain 409B, controlled by a switch applied on the gate 409C.

- the signal can control the on and off of the electrical connection of the bit line 411 to the corresponding memory cell; the bit line 411 is coupled to the source or drain (eg, source 409A) of the transistor 409 of the corresponding column of ferroelectric memory cells of the ferroelectric memory array, Word line 410 is coupled to gate 409C of transistor 409 of a corresponding column of ferroelectric memory cells of a ferroelectric memory array, such as patterned on gate 409C of transistor 409 of the corresponding column.

- FIG. 5 is a cross-sectional view showing the crossbar structure of a ferroelectric memory cell of a ferroelectric memory integrated circuit in accordance with a fifth embodiment of the present invention.

- the ferroelectric memory integrated circuit 50 can include a silicon-based read/write circuit 501, a bit line 502, and a contact hole 503.

- the bit line 502 and the second electrode 506B can be connected through a conductive connection in the contact hole 503.

- the electrical connection; the ferroelectric memory integrated circuit 50 may further include an insulating layer 504, a ferroelectric single crystal thin film layer 505, and a first electrode 506A over the ferroelectric single crystal thin film layer 505.

- the first electrode 506A may also be a part of the plate line, and the plate line is connected to the plurality of first electrodes 506A of the memory cells of the corresponding row or column of the ferroelectric memory unit, and the first electrode 506A may be substantially opposite to the second electrode 506B.

- the second electrode 506B is specifically formed on the upper and lower sides of the ferroelectric single crystal thin film layer 505, and the second electrode 506B is specifically patterned in the insulating layer 504.

- the insulating layer 504 includes a lower insulating layer 504B and an upper insulating layer. 504A.

- a portion of the ferroelectric single crystal thin film layer 505 between the first electrode 506A and the second electrode 506B constitutes a memory cell of an embodiment of the present invention, thereby enabling an electrical signal to be applied between the first electrode 506A and the second electrode 506B.

- the domain of the partial ferroelectric single crystal thin film layer 505 for forming the memory cell substantially between the first electrode 506A and the second electrode 506B is locally inverted (the other portion of the ferroelectric single crystal thin film layer 505 is not reversed)

- Figure 6 is a cross-sectional view showing the structure of a 1T1R structure of a ferroelectric memory cell of a ferroelectric memory integrated circuit in accordance with a sixth embodiment of the present invention.

- the ferroelectric memory integrated circuit 60 may include a silicon-based read/write circuit 601 and a transistor array 602.

- the silicon-based read/write circuit 601 may be formed, for example, by a single crystal silicon substrate or the like, and the transistor array 609 may also pass through a single crystal.

- a silicon substrate or the like is formed.

- the ferroelectric memory integrated circuit 60 can also include a bit line 604, a word line 603, and a contact hole 605 in the insulating layer, wherein the bit line 604 and the source of the transistor 602 of the corresponding column of ferroelectric memory cells of the ferroelectric memory array or The drains (e.g., source 602A) are connected, and the word lines 603 are coupled to the gate 602C of the transistor 602 of the corresponding column of ferroelectric memory cells of the ferroelectric memory array, for example, patterned on the gate 602C of the corresponding column of transistor 602.

- the bit line 604 can be electrically connected to the second electrode 608B through a conductive connection in the contact hole 605.

- the ferroelectric memory integrated circuit 50 may further include an insulating layer 606, a ferroelectric single crystal thin film layer 607, and a first electrode 608A over the ferroelectric single crystal thin film layer 607.

- the first electrode 608A may also be a part of the plate line, and the plate line is connected to the plurality of first electrodes 608A of the memory cells of the corresponding row or column of the ferroelectric memory unit, and the first electrode 608A may be substantially opposite to the second electrode 608B.

- the second electrode 608B is specifically formed on the upper and lower sides of the ferroelectric single crystal thin film layer 607, and the second electrode 608B is specifically patterned in the insulating layer 606.

- the insulating layer 606 includes a lower insulating layer 606A and an upper insulating layer. 606B.

- a portion of the ferroelectric single crystal film layer 607 between the first electrode 608A and the second electrode 608B constitutes a memory unit of the embodiment of the present invention, and the first electrode 608A can be connected through the memory unit. And a domain wall conductive path of the second electrode 608B substantially in the up and down direction.

- a material usable for the ferroelectric single crystal substrate or the ferroelectric single crystal thin film layer is selected from one or more of the following: lithium tantalate salt LiTaO 3 , lithium niobate LiNbO 3, bismuth iron BiFeO 3; or from one or more of the following: doped with MgO, Mn 2 O 5 or Fe salt of lithium tantalate LiTaO 2 O 3 of 3, lithium niobate LiNbO 3 , barium ferrite BiFeO 3 and so on.

- the doping amount of the lithium niobate LiTaO 3 and the lithium niobate LiNbO 3 doped with MgO, Mn 2 O 5 or Fe 2 O 3 may be 0.1 to 10 mol% (for example, 1 mol% or 4 mol%).

- the polarization direction of the ferroelectric single crystal layer (for example, a ferroelectric single crystal substrate or a ferroelectric single crystal thin film layer) as a storage medium may be limited to There is a component in the direction of the connection between the first electrode and the second electrode, and it can be understood that the polarization direction of the domain of the ferroelectric single crystal layer has a certain angle with the direction of the connection between the first electrode and the second electrode but There is a component in the wiring direction but not perpendicular to the wiring direction.

- the polarization direction of the domain is at an angle to the direction of the line connecting the first electrode and the second electrode in the in-plane (or "lateral" direction but in the direction of the connection.

- the direction has an angle but there is a component in the direction of the connection.

- each of the memory cells formed in the memory cell array of the ferroelectric single crystal substrate or the ferroelectric single crystal thin film layer is a regular bump pattern.

- Forming a convex pattern on the surface of the ferroelectric single crystal substrate by a semiconductor micro/nano processing process, that is, the memory cell is a relatively convex programming formed by patterning on a ferroelectric single crystal substrate or a ferroelectric single crystal thin film layer Bump.

- a memory array pattern can be formed on the surface of the ferroelectric single crystal substrate or the ferroelectric single crystal thin film layer by optical exposure or electron beam etching, and further, the bump storage can be further performed by wet etching or dry etching. unit.

- the bump is at least partially located between the first electrode and the second electrode, since the polarization direction of the domain is substantially non-parallel to the normal direction of the ferroelectric single crystal substrate or the ferroelectric single crystal film layer, at the first

- the ferroelectric single crystal of the at least partially convex portion of the ferroelectric single crystal substantially between the first electrode and the second electrode can be made to be ferroelectric single crystal substrate or ferroelectric with respect to other portions.

- the single crystal thin film layer is partially inverted, and the inverted ferroelectric single crystal can form an electrically conductive domain wall with respect to the remaining unreversed ferroelectric single crystal, thereby establishing domain wall conduction connecting the first electrode and the second electrode. aisle.

- the reading and writing operation of the information stored in the memory cell is to bias the corresponding voltage signal to the first electrode and the second electrode through the plate line and the bit line.

- the ferroelectric memory cell of the 1T1R structure it is also necessary to bias the corresponding gate control signal through the gate line of the word line to gate the transistor, thereby operating the corresponding ferroelectric memory cell. Storage unit.

- the selected electrode material is resistant to high temperature and has low resistivity

- the material of the first electrode and/or the second electrode may be, but not limited to, one selected from the following materials. Or a plurality of: TiN, Pt, PtSi, NiSi, TiW, Ta, Ti, W, Mo, Al, Cu, Cr or SrRuO 3 , RuO 2 , etc.; in the embodiment of Figures 1-4, except the first electrode and the first

- a third electrode may be disposed corresponding to each of the storage units, and the third electrode is located between the first electrode and the second electrode (for example, disposed on an upper surface of the bump-shaped memory unit), and respectively respectively Both the electrode and the second electrode have a gap.

- the height (h) of the bump of the memory cell may be greater than or equal to 2 nanometers and less than or equal to 5 micrometers, for example, 100 nanometers; the first electrode and the second electrode

- the thickness of one electrode and the second electrode may be greater than or equal to 1 nanometer and less than or equal to 500 nanometers, such as 50 nanometers.

- the insulating layer may comprise an insulating material such as silicon dioxide, aluminum oxide, hafnium oxide or silicon nitride, for example, the insulating layer is a silicon dioxide film.

- the method of preparing the insulating layer may be selected from one of the following methods: chemical vapor deposition, physical vapor deposition, atomic layer deposition, and the like.

- the circuit structure of the silicon-based read/write circuit is not limited, and may include corresponding circuits having various functions required for realizing the operation of the memory, for example, mainly including The current amplifying circuit, the reference circuit, the output comparator, the addressing circuit, and the like are read out.

- the read current signal may be amplified by a certain multiple, and then compared with the reference current to determine the stored logic state. .

- the first electrode and the second electrode are biased with a write voltage in a first direction, and the first direction is a ferroelectric single crystal substrate or a ferroelectric single crystal.

- the polarization direction of the film layer is opposite to the direction of the connection between the first electrode and the second electrode, that is, the first direction is the direction from the first electrode to the second electrode, and the magnitude of the write voltage is at least greater than the correction of the memory cell.

- the coercive voltage causes the polarization of the domain in the memory cell to be completely reversed (relative to the other ferroelectric single crystal substrate or ferroelectric single crystal film layer of the memory cell), as shown in Figure 1-6.

- the dotted arrow in the figure indicates the direction of polarization reversal, which is opposite to the polarization direction in which the ferroelectric single crystal substrate or film is not reversed, so that a conductive domain wall is formed at the interface, and offset writing is performed. After the voltage is removed, the conductive domain wall does not disappear. This process writes the message "1" (ie, the logic state "1").

- the first electrode and the second electrode bias voltage are biased in a second direction opposite to the first direction, and the voltage is at least larger than the memory cell.

- the coercive field voltage, the write voltage in the second direction can cause the domain polarization direction of the memory cell to be all reversed back to the initial state, that is, the initial polarization in the ferroelectric single crystal substrate or the ferroelectric single crystal thin film layer

- the direction is the same, the conductive domain wall formed at the interface disappears, the process is to write "0" information (ie logic state "0");

- the first electrode and the second electrode bias voltage are biased by the read voltage in the first direction, and the read voltage is smaller than the storage cell coercive field voltage.

- the information is read by current, and the read current changes according to the generation or disappearance of the above low-resistance domain wall. By comparing the read current with the reference current circuit, the logic state “0” or “1” can be identified.

- the process is the process of reading information. Since the biased read voltage is small and the polarization direction of the memory cell has been reversed, there is no influence on the polarization state of the memory cell, and non-destructive reading is realized;

- a third electrode may be disposed corresponding to each memory cell; and during a read operation, between the first electrode and the third electrode When the read voltage in the first direction or the read voltage in the first direction is biased between the third electrode and the second electrode, the logic state "0" or "1" is identified by the magnitude of the read current.

- Fig. 7 is a circuit connection diagram showing a crossbar structure of a ferroelectric memory cell according to the embodiment shown in Fig. 1, Fig. 3 or Fig. 5.

- the illustrated ferroelectric memory array includes a plurality of ferroelectric memory cells as shown in Figure 7 arranged in rows and columns, with bit lines BL Arranged in the column direction, the plate line PL (or referred to as a drive line) is arranged in the row direction as an example, and the resistive memory cell of the ferroelectric memory cell is in the vicinity of the intersection point of the bit line BL and the plate line PL in space.

- the bit line BL is connected to the plate line PL.

- the second electrode of the memory cell is connected to the bit line BL0 and the first electrode connection plate line BL0 of the memory cell. Assuming that the address signal bit line BL0 and the board line BL0 are selected and biased corresponding to the read signal or the write signal, a read operation or a write operation can be performed on the corresponding memory cell at the intersection of the bit line BL0 and the board line BL0. Other unselected memory locations will not be read or written.

- each ferroelectric memory cell is mainly formed by one memory cell in the memory cell array, one end of which is connected to the plate line PL and the other end is connected to the bit line BL.

- the bit line BL can be connected to the current comparator SA input by the reference current Ref so that the logic state currently stored by the memory cell can be read.

- a current amplifier is required on the current comparator to amplify the current read on the bit line.

- the memory cell of the ferroelectric memory cell is a resistive ferroelectric memory cell because the ferroelectric memory integrated circuit provided can write data in a bias voltage manner and read data in a manner of reading current.

- the magnitude of the read current reflects the resistance of the memory cell to a certain extent.

- the write operation of the memory cell reflects the change of the resistance of the memory cell to some extent. Therefore, in the embodiment of the present invention, the storage unit can be represented by R.

- the crossbar structure of the embodiment shown in Fig. 7 corresponds to an OT1R structure (T denotes a transistor for strobe).

- FIG. 8-10 illustrate a ferroelectric memory array of a ferroelectric memory integrated circuit according to an embodiment of the present invention, in which the ferroelectric memory array is a 1024 ⁇ 8 memory array, that is, 1024 ⁇ 8 are arranged in rows and columns.

- the plate line PL is connected to the first electrode of the memory cell of the corresponding row of ferroelectric memory cells

- the bit line BL is connected to the second electrode of the memory cell of the corresponding column of ferroelectric memory cells.

- the target memory cell is selected for read and write operations by the board line PL and the bit line BL.

- the memory cell read current has a switching characteristic, that is, a large on-state current is read under the condition that the first electrode and the second electrode bias voltage bias the voltage in the first direction and the conductive domain wall exists.

- the output information is "1", that is, corresponding to the low resistance state; other conditions such as the disappearance of the domain wall, the off-state current is read, and the readout information is "0", that is, the high resistance state is corresponding.

- the memory cell since the memory cell is formed using the ferroelectric single crystal layer, it has a characteristic of a ratio of an on-state current to an off-state current (i.e., a switching ratio) (e.g., an on state).

- the ratio of the current to the off-state current can be greater than 10 6 ), so that during the read operation or the write operation, crosstalk is not generated to the adjacent memory cells of the selected memory cell, and the leakage power consumption is also small. Therefore, each ferroelectric memory cell

- the transistor for strobing can be omitted directly to form a ferroelectric memory cell of a crossbar structure.

- ferroelectric memory cell having a crossbar structure eliminates the need for transistors, the ferroelectric memory cell and the ferroelectric memory array are simple in construction, low in cost, and the peripheral read and write circuits are correspondingly simple.

- the on-state read current can reach, for example, 10 -7 A or more, and the data readability is good.

- FIG. 8 is a view showing a configuration operation of writing storage information "1" to a certain ferroelectric memory cell of the ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 1, Figure 3 or Figure 5.

- the ferroelectric memory cell at address (1022, 6) is selected to perform the operation of writing the storage information "1"; first, the read enable terminal RE is configured to a low level, thereby blocking the bit line and The current comparison circuit is connected; then, the plate line PL1022 is configured to a high voltage V write , the V write value is greater than the coercive field voltage of the memory cell, and the other plate lines are left floating or configured to be a half level V cc /2 while Bit line BL6 is configured to be grounded, and other bit lines are left floating or configured as a half-level V cc /2.

- a write signal V write to the memory cell is biased in the ferroelectric memory cell address (1022,6) of the memory cell ferroelectric domain inversion occurs, successfully written to the storage

- the drive line PL1022 and the bit line BL6 are left floating or arranged at a half level V cc /2.

- FIG. 9 is a view showing a configuration operation of writing information "0" to a ferroelectric memory cell of the ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 1, Figure 3 or Figure 5.

- the ferroelectric memory cell having the address (1022, 6) is selected to perform the operation of writing the storage information "0"; first, the read enable terminal RE is configured to be low, thereby blocking the bit line and The current comparison circuit is connected; then, the bit line BL6 is configured to a high voltage V write , the V write value is greater than the coercive field voltage of the memory cell, and the other bit lines are left floating or configured as a half level V cc /2 while The plate line PL1022 is configured to be grounded, and the other plate lines are left floating or configured to be a half level V cc /2.

- a write signal V write to the memory cell is biased in the ferroelectric memory cell address (1022,6), the electrical domain of the memory cell returns to the original direction of polarization, information

- the drive line PL1022 and the bit line BL6 are left floating or arranged at a half level V cc /2.

- FIG. 10 is a view showing a configuration operation of reading information from a ferroelectric memory cell of a ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 1, Figure 3 or Figure 5.

- the ferroelectric memory cell at address (1022, 6) is selected for read operation; first, the read enable terminal RE is configured to be high, thereby connecting the bit line BL with the current comparison circuit; PL1022 drive line configured to read voltage V read, V read correction value is less than the coercive field voltage of the memory cell, the floating or other drive line configured to half the high level V cc / 2, at the same time, the bit line BL6 configured to ground, The other bit lines are left floating or configured as a half high level V cc /2.

- the sense current is compared to the reference current by the input current comparator to determine the logic state stored by the ferroelectric memory cell at address (1022, 6).

- the drive line PL1022 and the bit line BL6 are left floating or arranged at a half level V cc /2.

- FIG 11 is a circuit connection diagram of a 1T1R structure of a ferroelectric memory cell in accordance with the embodiment shown in Figure 2, Figure 4 or Figure 6.

- the illustrated ferroelectric memory array includes a plurality of ferroelectric memory cells as shown in Figure 11 arranged in rows and columns, with bit lines BL And the plate line PL (or referred to as a drive line) are arranged in the column direction, the word line WL is arranged in the row direction as an example, the resistive memory cell R of the ferroelectric memory cell and the transistor T are spatially in the bit line BL and the plate line PL

- the bit line BL is connected to the plate line PL in the vicinity of the intersection point.

- the first electrode connection plate line BL0 of the memory cell and the second electrode of the memory cell are connected to the transistor T and further pass.

- the transistor T is connected to the bit line BL0

- the transistor T of the memory cell is connected to the word line WL0.

- the corresponding bit line BL0, the board line BL0, and the word line WL0 are selected and biased corresponding to the read signal or the write signal based on the address signal, the selected memory cell can be read or written, and the other unselected The memory unit does not read or write.

- each ferroelectric memory cell is mainly formed by one memory cell R and one transistor T in the memory cell array, that is, a 1T1R structure is formed, one end of the memory cell is connected to the plate line (PL0), and the other end is connected.

- the gate of the transistor T is connected to the word line (WL0), and the other end of the source and the drain of the transistor T is connected to the bit line (BL0).

- the bit line BL can be connected to the current comparator SA input by the reference current Ref so that the logic state currently stored by the memory cell can be read.

- FIG. 12-14 illustrate a ferroelectric memory array of a ferroelectric memory integrated circuit according to still another embodiment of the present invention, wherein the ferroelectric memory array is a 1024 ⁇ 16 memory array, that is, 1024 ⁇ 16 arranged in rows and columns.

- the plate line PL is connected to the first electrode of the memory cell of the corresponding column of the ferroelectric memory cell

- the bit line BL is connected to the source or the drain of the transistor of the corresponding column of the ferroelectric memory cell

- the word line WL The gate of the transistor of the corresponding column of the ferroelectric memory cell is connected, and the target memory cell can be selected through the plate line PL, the bit line BL and the word line WL, thereby performing read and write operations on the selected target memory cell.

- ferroelectric memory cell of 1T1R structure is used, although the ferroelectric memory cell structurally opposite to the crossbar structure is structurally complex, but it is reduced in the array It has beneficial characteristics in terms of crosstalk and leakage current, and is relatively more suitable for larger ferroelectric memory integrated circuits.

- FIG. 12 is a diagram showing the configuration operation of writing storage information "1" to a certain ferroelectric memory cell of the ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 2, Figure 4 or Figure 6.

- FIG. 12 shows an expanded circuit of the ferroelectric memory cell shown in FIG. 11, that is, a ferroelectric memory array. As shown in FIG. 8, the ferroelectric memory cell at address (1022, 14) is selected to be written to store information. 1" operation.

- the read enable terminal RE is configured to be low, thereby blocking the connection of the bit line to the current comparison circuit; then, the configuration plate line PL14 is high voltage V write , and the V write value is greater than the coercive field voltage of the memory cell,

- the other board line PL is left floating or configured as a half-level V cc /2;

- the configuration bit line BL14 is grounded, and the other bit lines BL are left floating or configured as a half-level V cc /2.

- a write signal V write to the memory cell is biased in the ferroelectric memory cell address (1022,14), and the memory cell ferroelectric domain inversion occurs, successfully written to the storage information "1."

- the plate line PL14 and the bit line BL14 are suspended or arranged to be a half-level Vcc/2, and the word line W1022 is also suspended or arranged at a low level.

- FIG. 13 is a view showing the configuration operation of writing information "0" to a certain ferroelectric memory cell of the ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 2, Figure 4 or Figure 6.

- the ferroelectric memory cell having the address (1022, 14) is selected to perform the operation of writing the storage information "0".

- the read enable terminal RE is configured to be low, thereby blocking the connection of the bit line to the current comparison circuit; then, the plate line PL14 is configured to be grounded, and the other plate line PL is suspended or configured as a half level V cc / 2; the bit lines BL14 configured for high voltage V write, V write the memory cell is greater than the coercive voltage Ec.

- a write signal V write to the memory cell is biased in the ferroelectric memory cell address (1022,14), the electrical domain of the memory cell returns to the original direction of polarization, information stored successfully written "0.”

- the plate line PL14 and the bit line BL14 are suspended or arranged to be a half-level Vcc/2, and the word line W1022 is also suspended or arranged at a low level.

- Figure 14 is a diagram showing the operation of reading information from a ferroelectric memory cell of a ferroelectric memory array of the ferroelectric memory integrated circuit of the embodiment shown in Figure 2, Figure 4 or Figure 6.

- the ferroelectric memory cell at address (1022, 14) is selected for read operation.

- the configuration read enable terminal RE is high, so as to connect the bit line BL and the current comparator circuit; then, the plate lines PL14 configured as a voltage V read, V read memory cell is less than the coercive field voltage, the other plate

- the line PL is left floating or configured as a half-level V cc /2; the bit line BL14 is configured to be grounded, and the other bit lines BL are left floating or configured as a half-level V cc /2.

- the sense current is compared to the reference current by the current comparator to determine the logic state stored by the ferroelectric memory cell at address (1022, 6).

- the drive line PL14 and the bit line BL14 are left floating or arranged to be a half-level V cc /2, and the word line W1022 is also left floating or configured as a low level.

- Figure 15 is a SEM image of a sample of a ferroelectric memory array of a ferroelectric memory cell having a crossbar structure in accordance with an embodiment of the present invention.

- a LiNbO 3 ferroelectric single crystal substrate doped with MgO mol of 5% was used, the height of each memory cell was about 70 nm, and the thickness of the first electrode and the second electrode was about 30.

- Nano having a width of about 100 nm, the first electrode is connected to the plate line PL, and a layer of about 200 nm thick silicon dioxide insulating layer is deposited between the plate line PL and the bit line BL, and the bit line BL is passed through the silicon dioxide insulating layer.

- the contact hole is connected to the second electrode and is tested by being led out from the bit line BL and the plate line PL.

- Figure 16 is an I-V test diagram of 12 memory cells randomly sampled in the sample of the embodiment of Figure 15, i.e., an I-V curve of a ferroelectric memory cell; wherein the ordinate is in logarithmic form.

- the voltage is forward-biased for scanning.

- the scan voltage ranges from 0 to 10V. Since the memory cell does not form a domain-wall conductive channel at the beginning, the current after the bias voltage is small, the memory cell is in a high-resistance state, and the scan voltage increases.

- the memory cell After exceeding the coercive field voltage of the memory cell, the memory cell forms a domain wall conductive path, and the current suddenly increases at a bias voltage of, for example, 6-7V, and the current suddenly increases by nearly 4 orders of magnitude; when the scan voltage is reversed from 10V At 0V, the memory cell is in a low resistance state and the current is large.

- This I-V scanning process completes the information writing process of the memory cell, that is, the formation process of the domain wall conductive channel.

- the ferroelectric memory array of the embodiment of the present invention has a crossbar structure, and the ratio of the on-state current to the off-state current of the ferroelectric memory cell measured in the array can be greater than 10 4 , and the ferroelectric memory The crosstalk in the array is small.

- Figure 17 is an IV test diagram of 12 memory cells randomly sampled in the sample of the embodiment of Figure 15, scanning from -10V to +10V, and then scanning from +10V to -10V, as can be seen from Figure 15

- the memory cell of the example has obvious switching characteristics. When the scanning voltage is taken in the negative direction, the stored cell cannot be turned on, that is, the low resistance state cannot be read. It can be seen that the memory cell has a unidirectional conduction characteristic. For example, after a low resistance state in which a domain wall conductive path is formed by forward programming, if the memory cell is biased with a negative voltage, the low resistance state cannot be read. The memory cell can be rendered in a low resistance state only if the same forward voltage is used to bias the memory cell.

- the ferroelectric memory cell of the crossbar structure of the embodiment of the present invention when applied to a ferroelectric memory array, the unidirectional conduction characteristic of the memory cell naturally contributes to avoiding the surrounding ferroelectric memory cells and surrounding ferroelectrics in the array.

- Current crosstalk between memory cells As shown in the example of FIG. 10, when the high resistance state of the memory cell R H is read, since the surrounding memory cells R L1 , R L2 , and R L3 are all in a low resistance state, even if the current tends to pass the b path (see FIG. 10).

- the negative resistance is programmed to form a low resistance state with domain wall conduction paths, if the memory cell is biased with a positive voltage, the low resistance state cannot be read, only if the same negative voltage is used. In the case of biasing the memory cell, the memory cell can be turned on in a low resistance state.

- FIG. 18 is a flow chart showing a method of fabricating the ferroelectric memory integrated circuit of the first embodiment shown in FIG. Referring to FIG. 1 and FIG. 18, first, in step S181, a ferroelectric single crystal substrate or a ferroelectric thin film is provided.

- the ferroelectric material may be selected from one or more of the following materials: lithium tantalate salt LiTaO 3 , tannic acid Lithium salt LiNbO 3 , BiFeO 3 or lithium niobate LiTaO 3 doped with MgO, Mn 2 O 5 or Fe 2 O 3 , lithium niobate LiNbO 3 , BiFeO 3 ferrite, and the like.

- a memory cell array is formed.

- the array pattern can be formed by optical exposure, electron beam exposure, etc., and then the array pattern can be transferred to the surface of the ferroelectric single crystal substrate or the ferroelectric film by wet etching or dry etching. Thereby a bump array, that is to say a memory cell array, is formed.

- the first and second electrodes and the plate line are formed.

- the electrode pattern is formed by optical exposure, electron beam exposure, or the like, and then the electrode film material is grown, and the electrode pattern is transferred to the memory cell array by a process such as lift-off; or a long electrode film material is passed through Optical exposure, electron beam exposure and the like form a pattern of electrode patterns, and the electrode patterns are transferred to the memory array by etching methods such as wet or dry etching.

- the first and second electrodes and the plate line (or plate line) PL may be made of the same material and may be formed simultaneously.

- an insulating layer is formed.

- an insulating layer is grown on the ferroelectric single crystal substrate, and the insulating layer material may be silicon dioxide (SiO 2 ), aluminum oxide (Al 2 O 3 ), hafnium oxide (HfO 2 ), An insulating material such as magnesium oxide (MgO), however, it should be understood herein that the insulating layer material is not limited to the insulating material type exemplified above.

- the method of growing the insulating layer material may be, but not limited to, physical vapor deposition, chemical vapor deposition, atomic layer deposition, molecular beam epitaxy, laser pulse deposition, and the like.

- the silicon thin film material is bonded or grown.

- a silicon thin film layer is formed over the insulating layer by an SOI process.

- the process of bonding the silicon thin film material includes ion implantation of the Si/SiO 2 sheet, bonding it to the ferroelectric single wafer, Strip the remaining silicon, chemical mechanical polishing and other steps.

- a silicon thin film material may also be formed over the insulating layer by an epitaxial growth method. It should be noted that the bonded or grown silicon material used above is only one example of a silicon-based material, and it will be understood that the silicon-based material may also be various semiconductors suitable for large-scale preparation of peripheral circuits of a memory.

- Materials are suitable for use in large scale integrated circuit processes to fabricate semiconductor materials including devices such as MOS transistors, such as GaAs, SiC, InP, etc., and, as advances in semiconductor material technology, various types of memory suitable for preparing memories may emerge. New semiconductor materials for peripheral circuits.

- a contact hole is formed in the insulating layer.

- the pattern of the contact hole is formed by optical exposure, electron beam exposure, or the like, and the contact hole pattern is transferred to the insulating layer by wet or dry etching (reactive ion etching), thereby being the upper layer.

- the circuit formed in the silicon film and the memory cell formed in the lower layer provide interconnection channels.

- a bit line and a read/write circuit are formed.

- the electrode pattern is transferred to the ferroelectric memory array by forming a pattern of the electrode pattern, the material of the growth electrode film, peeling, or the like by optical exposure, electron beam exposure, or the like; or a long electrode

- the film material is formed into a pattern by optical exposure, electron beam exposure, etc., and the electrode pattern is transferred to the ferroelectric memory array by wet or dry etching, and the formed bit lines are passed through the contact holes and the corresponding column memory cells. connection.

- the read/write circuit can be prepared through a standard CMOS process to form a silicon-based read/write circuit; the read/write circuit can include, but is not limited to, a read current amplifying circuit, a reference current output circuit, an output current comparator, and an addressing circuit.

- FIG. 19 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the second embodiment shown in FIG. 2 and FIG. 19, the preparation method shown in FIG. 19 is substantially similar to the preparation method illustrated in FIG. 18.

- the main difference in the preparation method shown in FIG. 19 is that it further includes step S196 in the silicon-based film layer.

- Forming a transistor T thereon that is, forming an array of transistors T on the silicon-based thin film layer before forming the read/write circuit and the bit line; specifically, forming a transistor having a voltage gate-controlled switch on the silicon thin film formed on step S195

- the array has one end of the source and the drain of each transistor electrically connected to the bit line and the other end electrically connected to one end of the lower memory cell.

- Step S191, step S192, step S193, step S194, step S195, step S197, step S198 in the preparation method shown in Fig. 19 may be combined with step S181, step S182, step S183, and step in the preparation method shown in Fig. 18.

- S184, step S185, step S186, and step S187 are respectively the same or similar, and a description thereof will be omitted herein.

- Figure 20 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the third embodiment shown in Figure 3. As shown in Fig. 20 and Fig. 3, a silicon single crystal wafer is used as a silicon-based substrate in this embodiment to form a peripheral read/write circuit or the like.

- step S201 a silicon single wafer is provided, that is, a single crystal silicon substrate is provided.

- a bit line and a silicon-based read/write circuit are formed on a silicon single wafer by using, for example, a standard CMOS process, wherein the silicon-based read/write circuit includes but is not limited to a read current amplifying circuit, a reference current output circuit, and an output current comparison. And addressing circuits, etc.

- an insulating layer is formed.

- an insulating layer may be grown on the silicon-based read/write circuit and the bit line, and the insulating layer material may be selected from silicon dioxide (SiO 2 ), aluminum oxide (Al 2 O 3 ), and antimony oxide ( Insulating materials such as HfO 2 ) and magnesium oxide (MgO), and methods for growing the insulating material include, but are not limited to, physical vapor deposition, chemical vapor deposition, atomic layer deposition, molecular beam epitaxy, laser pulse deposition, and the like.

- a ferroelectric single crystal thin film layer is bonded or grown on the insulating layer.

- the ferroelectric single crystal thin film layer used as the ferroelectric single crystal layer is formed by bonding over the insulating layer by an SOI process; specifically, bonding to form a ferroelectric single crystal thin film layer includes: The surface of the electric single wafer is implanted with ions (H ions or He ions), the ferroelectric single crystal is bonded to the insulating layer of the silicon single wafer, and the ferroelectric single crystal thin film layer bonded to the insulating layer is peeled off, and finally the chemical is performed. Mechanical polishing, etc.

- a ferroelectric single crystal thin film layer serving as a ferroelectric single crystal layer is grown over the insulating layer by an epitaxial growth method.

- a memory cell array is formed on the surface of the ferroelectric single crystal thin film layer.

- the array pattern can be formed by optical exposure, electron beam exposure, or the like, and then the array pattern can be transferred to the surface of the ferroelectric single crystal substrate or the ferroelectric thin film by wet etching or dry etching, thereby forming a convex shape.

- a block array that is, a memory cell array.

- a contact hole is formed.

- the pattern of the contact hole is formed by optical exposure, electron beam exposure, etc., and the contact hole pattern is transferred to the device by wet or dry (reactive ion) etching to provide mutual memory between the upper memory cell and the lower silicon film circuit.

- the pattern of the contact hole is formed by optical exposure, electron beam exposure, etc., and the contact hole pattern is transferred to the insulating layer by wet or dry etching (reactive ion etching), thereby An interconnection channel is provided for the memory cell formed by the upper layer and the bit line BL formed on the underlying silicon single wafer.

- the first and second electrodes and the plate line are formed.

- the engraved electrode pattern is formed by optical exposure, electron beam exposure, or the like, and then the electrode film material is grown, and the electrode pattern is transferred to the memory cell array by a process such as peeling; or a long electrode film material is passed through

- Optical exposure, electron beam exposure and the like form a pattern of electrode patterns, and the electrode patterns are transferred to the memory array by etching methods such as wet or dry etching.

- the first and second electrodes and the plate line (or plate line) PL may be of the same material and may be formed simultaneously, wherein one of the first and second electrodes passes through the contact hole and the silicon single Bit lines on the wafer are connected.

- FIG. 21 is a flow chart showing a method of fabricating the ferroelectric memory integrated circuit of the fourth embodiment shown in FIG. 4 and FIG. 21, the preparation method shown in FIG. 21 is substantially similar to the preparation method illustrated in FIG. 20, and the main difference in the preparation method shown in FIG. 19 is that it further includes step S212 on the silicon single wafer.

- Step S211, step S213, step S214, step S215, step S216, step S217, step S218 in the preparation method shown in FIG. 21 may be combined with step S201, step S203, step S204, and step in the preparation method shown in FIG. S205, step S206, and step S207 are the same or similar, respectively, and a description thereof will be omitted herein.

- FIGS. 22 and 23 The fabrication method illustrated in Figures 18-22 above illustrates the basic fabrication process of an in-plane ferroelectric memory integrated circuit.

- the basic preparation process of the out-of-plane ferroelectric memory integrated circuit will be exemplified below based on FIGS. 22 and 23.

- Figure 22 is a flow chart showing a method of fabricating a ferroelectric memory integrated circuit corresponding to the fifth embodiment shown in Figure 5. Referring to Figures 5 and 22, first,

- step S221 a silicon single wafer is provided, that is, a single crystal silicon substrate is provided.

- a bit line, a silicon-based read/write circuit is formed on a silicon single wafer by, for example, a standard CMOS process, and a contact hole 503 is formed in the insulating layer 504A, wherein the silicon-based read/write circuit includes but is not limited to reading A current amplifying circuit, a reference current output circuit, an output current comparator, an addressing circuit, and the like.

- step S223 an insulating layer such as 504B is deposited.

- This step is the same as or similar to step S203 of the example shown in FIG.

- the second 506B is electrically connected to the corresponding bit line 502 through the contact hole 503.

- step S224 a ferroelectric single crystal thin film layer is bonded or grown on the insulating layer. This step is the same as or similar to step S204 of the example shown in Fig. 20.

- a first electrode (plate line) is formed on the polished surface of the ferroelectric single crystal thin film layer, that is, the first electrode and the plate line are integrally formed.

- a portion of the ferroelectric single crystal thin film layer between the first electrode 506A and the second electrode 506B constitutes a memory cell.

- Figure 23 is a flow chart showing the method of fabricating the ferroelectric memory integrated circuit of the sixth embodiment shown in Figure 6. 6 and FIG. 23, the preparation method shown in FIG. 23 is substantially similar to the preparation method illustrated in FIG. 22, and the main difference in the preparation method shown in FIG. 23 is that, in step S232, it is also formed on a silicon single wafer.

- Step S231, step S233, step S234, and step S235 in the preparation method shown in FIG. 23 may be the same as or similar to step S221, step S223, step S224, and step S225 in the preparation method shown in FIG. 22, and are omitted here. A description of them.

- ferroelectric memory integrated circuits of the embodiments shown in Figs. 1-6 are basically formed, respectively.

- the method for fabricating the ferroelectric memory integrated circuit of the embodiment of the present invention has fewer process steps, is not complicated in the preparation process, and is compatible with the CMOS process, compared to the conventional method of fabricating the FRAM of the ferroelectric capacitor structure.

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019504796A JP7079769B2 (ja) | 2017-09-06 | 2018-02-28 | 強誘電体メモリ集積回路及びその操作方法並びに製造方法 |

| CN201880003413.1A CN109791785B (zh) | 2017-09-06 | 2018-02-28 | 铁电存储集成电路及其操作方法和制备方法 |

| US16/322,032 US11145664B2 (en) | 2017-09-06 | 2018-02-28 | Ferroelectric memory IC as well as method of operating the same and method of preparing the same |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201710793719.9 | 2017-09-06 | ||

| CN201710793719.9A CN107481751B (zh) | 2017-09-06 | 2017-09-06 | 一种铁电存储集成电路 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2019047489A1 true WO2019047489A1 (zh) | 2019-03-14 |

Family

ID=60583540

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/CN2018/077485 Ceased WO2019047489A1 (zh) | 2017-09-06 | 2018-02-28 | 铁电存储集成电路及其操作方法和制备方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US11145664B2 (enExample) |

| JP (1) | JP7079769B2 (enExample) |

| CN (2) | CN107481751B (enExample) |

| WO (1) | WO2019047489A1 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11348943B2 (en) | 2019-07-31 | 2022-05-31 | Fudan University | Non-volatile ferroelectric memory and method of preparing the same |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107481751B (zh) | 2017-09-06 | 2020-01-10 | 复旦大学 | 一种铁电存储集成电路 |

| CN108417574B (zh) * | 2018-03-12 | 2020-05-12 | 复旦大学 | 基于soi的铁电存储器的制造方法 |

| CN109378313B (zh) * | 2018-09-23 | 2020-10-30 | 复旦大学 | 一种低功耗三维非易失性存储器及其制备方法 |

| US11646374B2 (en) * | 2018-12-26 | 2023-05-09 | Intel Corporation | Ferroelectric transistors to store multiple states of resistances for memory cells |

| CN114342075A (zh) * | 2019-09-26 | 2022-04-12 | 华为技术有限公司 | 一种存储器、存储器阵列以及存储器的数据读写方法 |

| WO2021184205A1 (zh) * | 2020-03-17 | 2021-09-23 | 华为技术有限公司 | 平面存储器、立体存储器以及电子设备 |

| US11398568B2 (en) * | 2020-06-17 | 2022-07-26 | Globalfoundries Dresden Module One Limited Liability Company & Co. Kg | Ferroelectric based transistors |

| WO2022104742A1 (zh) * | 2020-11-20 | 2022-05-27 | 华为技术有限公司 | 一种铁电存储器及电子设备 |

| CN112635665B (zh) * | 2020-12-22 | 2024-07-12 | 上海复存信息科技有限公司 | 一种基于多层掩膜套刻的面内岛状铁电阻变存储器单元结构及其制备方法 |

| CN118136073B (zh) * | 2024-03-20 | 2025-01-07 | 北京超弦存储器研究院 | 存储装置及其数据读取方法、电子设备 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105256376A (zh) * | 2015-11-18 | 2016-01-20 | 中国科学技术大学 | 一种控制铁电单晶电致形变取向的方法 |

| CN107481751A (zh) * | 2017-09-06 | 2017-12-15 | 复旦大学 | 铁电存储集成电路设计及其制造方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100289975B1 (ko) * | 1996-07-09 | 2001-06-01 | 니시무로 타이죠 | 반도체장치의제조방법및반도체장치 |

| JP2002324892A (ja) * | 2001-04-25 | 2002-11-08 | Hitachi Ltd | 強誘電体メモリ |

| JP2004165351A (ja) * | 2002-11-12 | 2004-06-10 | Fujitsu Ltd | 半導体装置の製造方法 |

| JP4256670B2 (ja) * | 2002-12-10 | 2009-04-22 | 富士通株式会社 | 容量素子、半導体装置およびその製造方法 |

| WO2004107466A1 (ja) * | 2003-05-08 | 2004-12-09 | Matsushita Electric Industrial Co. Ltd. | 電気スイッチおよびそれを用いた記憶素子 |

| JP4015968B2 (ja) * | 2003-06-09 | 2007-11-28 | 株式会社東芝 | 強誘電体メモリ |

| JP4171908B2 (ja) * | 2004-01-20 | 2008-10-29 | セイコーエプソン株式会社 | 強誘電体膜、強誘電体メモリ、及び圧電素子 |

| KR20080059391A (ko) * | 2005-10-19 | 2008-06-27 | 가부시키가이샤 야마즈 세라믹스 | 강유전체 단결정, 그것을 이용한 탄성 표면파 필터 및 그제조방법 |

| JP2009212448A (ja) * | 2008-03-06 | 2009-09-17 | Toshiba Corp | 半導体記憶装置およびその製造方法 |

| JP5487625B2 (ja) * | 2009-01-22 | 2014-05-07 | ソニー株式会社 | 半導体装置 |

| CN104637948B (zh) * | 2015-01-24 | 2017-11-17 | 复旦大学 | 非破坏性读出铁电存储器及其制备方法和读/写操作方法 |

| CN104637949B (zh) * | 2015-01-24 | 2017-11-17 | 复旦大学 | 非破坏性读出铁电存储器及其制备方法和操作方法 |

| CN105655342B (zh) * | 2016-02-23 | 2019-07-23 | 复旦大学 | 非易失性铁电存储器及其制备方法和读/写操作方法 |

| CN108475523B (zh) * | 2016-04-12 | 2021-10-19 | 复旦大学 | 大电流读出铁电单晶薄膜存储器及其制备方法和操作方法 |

| CN107123648B (zh) * | 2017-04-12 | 2020-09-01 | 复旦大学 | 一种面内读/写操作铁电忆阻器及其制备方法 |

-

2017

- 2017-09-06 CN CN201710793719.9A patent/CN107481751B/zh active Active

-

2018

- 2018-02-28 US US16/322,032 patent/US11145664B2/en active Active

- 2018-02-28 WO PCT/CN2018/077485 patent/WO2019047489A1/zh not_active Ceased

- 2018-02-28 JP JP2019504796A patent/JP7079769B2/ja active Active

- 2018-02-28 CN CN201880003413.1A patent/CN109791785B/zh active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105256376A (zh) * | 2015-11-18 | 2016-01-20 | 中国科学技术大学 | 一种控制铁电单晶电致形变取向的方法 |

| CN107481751A (zh) * | 2017-09-06 | 2017-12-15 | 复旦大学 | 铁电存储集成电路设计及其制造方法 |

Non-Patent Citations (2)

| Title |

|---|