WO2015025499A1 - 酸化物半導体基板及びショットキーバリアダイオード - Google Patents

酸化物半導体基板及びショットキーバリアダイオード Download PDFInfo

- Publication number

- WO2015025499A1 WO2015025499A1 PCT/JP2014/004153 JP2014004153W WO2015025499A1 WO 2015025499 A1 WO2015025499 A1 WO 2015025499A1 JP 2014004153 W JP2014004153 W JP 2014004153W WO 2015025499 A1 WO2015025499 A1 WO 2015025499A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- oxide semiconductor

- diode element

- barrier diode

- schottky barrier

- semiconductor layer

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 163

- 239000000758 substrate Substances 0.000 title claims abstract description 96

- 230000004888 barrier function Effects 0.000 title claims abstract description 88

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 43

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims abstract description 35

- 239000010703 silicon Substances 0.000 claims abstract description 35

- 239000010408 film Substances 0.000 claims description 65

- 229910052751 metal Inorganic materials 0.000 claims description 39

- 239000002184 metal Substances 0.000 claims description 26

- 239000010409 thin film Substances 0.000 claims description 23

- 229910052738 indium Inorganic materials 0.000 claims description 19

- 239000000203 mixture Substances 0.000 claims description 16

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 13

- 229910052725 zinc Inorganic materials 0.000 claims description 10

- 229910052782 aluminium Inorganic materials 0.000 claims description 8

- 229910052733 gallium Inorganic materials 0.000 claims description 7

- 229910052718 tin Inorganic materials 0.000 claims description 7

- 229910052726 zirconium Inorganic materials 0.000 claims description 7

- 229910052719 titanium Inorganic materials 0.000 claims description 6

- 229910052684 Cerium Inorganic materials 0.000 claims description 5

- 229910052772 Samarium Inorganic materials 0.000 claims description 5

- 229910052735 hafnium Inorganic materials 0.000 claims description 3

- 238000010030 laminating Methods 0.000 claims description 3

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims description 3

- 229910021424 microcrystalline silicon Inorganic materials 0.000 claims description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 2

- 238000000034 method Methods 0.000 description 27

- 230000015556 catabolic process Effects 0.000 description 24

- 238000004544 sputter deposition Methods 0.000 description 23

- 230000005684 electric field Effects 0.000 description 14

- 239000013078 crystal Substances 0.000 description 13

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 12

- 239000000463 material Substances 0.000 description 10

- 238000000137 annealing Methods 0.000 description 8

- 230000000052 comparative effect Effects 0.000 description 8

- 238000005477 sputtering target Methods 0.000 description 8

- 230000000694 effects Effects 0.000 description 7

- 235000012431 wafers Nutrition 0.000 description 7

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 6

- 239000013081 microcrystal Substances 0.000 description 6

- 229910052763 palladium Inorganic materials 0.000 description 6

- 238000011084 recovery Methods 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 229910052737 gold Inorganic materials 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 229910052697 platinum Inorganic materials 0.000 description 5

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 4

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 4

- 238000002441 X-ray diffraction Methods 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 230000020169 heat generation Effects 0.000 description 4

- 229910003437 indium oxide Inorganic materials 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 239000000654 additive Substances 0.000 description 3

- 230000000996 additive effect Effects 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 230000017525 heat dissipation Effects 0.000 description 3

- 229910052741 iridium Inorganic materials 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 3

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N Magnesium oxide Chemical compound [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- 229910010038 TiAl Inorganic materials 0.000 description 2

- 229910010413 TiO 2 Inorganic materials 0.000 description 2

- 239000003513 alkali Substances 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 238000011088 calibration curve Methods 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 238000002484 cyclic voltammetry Methods 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- -1 lanthanum aluminate Chemical class 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 238000004445 quantitative analysis Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- QHGNHLZPVBIIPX-UHFFFAOYSA-N tin(II) oxide Inorganic materials [Sn]=O QHGNHLZPVBIIPX-UHFFFAOYSA-N 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- VZSRBBMJRBPUNF-UHFFFAOYSA-N 2-(2,3-dihydro-1H-inden-2-ylamino)-N-[3-oxo-3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propyl]pyrimidine-5-carboxamide Chemical compound C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C(=O)NCCC(N1CC2=C(CC1)NN=N2)=O VZSRBBMJRBPUNF-UHFFFAOYSA-N 0.000 description 1

- 241000792177 Cicadetta radiator Species 0.000 description 1

- 239000004695 Polyether sulfone Substances 0.000 description 1

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 238000010306 acid treatment Methods 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 239000000443 aerosol Substances 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 230000008033 biological extinction Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000007606 doctor blade method Methods 0.000 description 1

- 238000004070 electrodeposition Methods 0.000 description 1

- 238000005868 electrolysis reaction Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000001125 extrusion Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000009616 inductively coupled plasma Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000007733 ion plating Methods 0.000 description 1

- 238000001659 ion-beam spectroscopy Methods 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000001755 magnetron sputter deposition Methods 0.000 description 1

- 150000001247 metal acetylides Chemical class 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 239000000693 micelle Substances 0.000 description 1

- 239000003595 mist Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920001230 polyarylate Polymers 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920006393 polyether sulfone Polymers 0.000 description 1

- 229920000139 polyethylene terephthalate Polymers 0.000 description 1

- 239000005020 polyethylene terephthalate Substances 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 238000005036 potential barrier Methods 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 238000000985 reflectance spectrum Methods 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 1

- 238000005245 sintering Methods 0.000 description 1

- 239000005361 soda-lime glass Substances 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 239000006104 solid solution Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/872—Schottky diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/24—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only semiconductor materials not provided for in groups H01L29/16, H01L29/18, H01L29/20, H01L29/22

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/24—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only semiconductor materials not provided for in groups H01L29/16, H01L29/18, H01L29/20, H01L29/22

- H01L29/247—Amorphous materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/26—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, elements provided for in two or more of the groups H01L29/16, H01L29/18, H01L29/20, H01L29/22, H01L29/24, e.g. alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/47—Schottky barrier electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

Definitions

- the present invention relates to a Schottky barrier diode element, and an electric circuit, an electric device, an electronic device, and a vehicle including the same.

- the present invention also relates to a structure, an oxide semiconductor substrate including the structure, a power semiconductor element including the structure, a diode element and a Schottky barrier diode element, and an electric circuit, an electric device, an electronic device, and a vehicle including the structure.

- a Schottky barrier diode is a diode that has a rectifying action by using a potential barrier formed at a junction surface between a metal and a semiconductor.

- Si is most commonly used as a semiconductor (for example, Patent Document 1).

- Si-based Schottky diodes are used for high-speed switching elements, transmission / reception mixers in the frequency band of several GHz, or frequency conversion elements.

- GaAs Schottky diodes are capable of higher-speed switching elements and are used in microwave converters and mixers.

- SiC is expected to be applied to higher-voltage electric vehicles, railways, power transmission, and the like by taking advantage of the wide band gap.

- a Schottky barrier diode using Si is widely used at a relatively low cost.

- the band gap is as small as 1.1 eV, it is necessary to increase the size of the element in order to provide pressure resistance.

- the band gap of GaAs is 1.4 eV, which is superior to that of Si, but it is difficult to epitaxially grow on the Si substrate, and it is difficult to obtain a crystal with few dislocations.

- SiC has a wide band gap of 3.3 eV, and therefore has a high dielectric breakdown electric field, and is the material with the highest performance.

- both substrate fabrication and epitaxial growth are subject to high-temperature processes, so there are problems in mass productivity and cost. .

- JP 2009-164237 A JP-A-5-36975 JP-A-8-97441

- the present invention has been made in view of such problems, and a Schottky barrier having excellent current-voltage characteristics by forming a compound semiconductor having a wide band gap on a Si substrate by a method that is inexpensive and excellent in mass productivity.

- An object is to provide a diode element.

- Another object of the present invention is to provide an oxide semiconductor substrate suitable for a Schottky barrier diode element, a diode element, and a power semiconductor element.

- the atomic composition percentage of indium with respect to all metal elements contained in the oxide semiconductor layer ([In] / ([In] + [all metal elements other than In]) ⁇ 100) is 1 to 3 at 30 to 100 atm%

- the Schottky barrier diode element according to any one of 1 to 4 wherein the oxide semiconductor layer is formed on the silicon substrate, and the Schottky electrode layer is formed on the oxide semiconductor layer. 6).

- the Schottky barrier diode element according to any one of 1 to 4 wherein the Schottky electrode layer is formed on the silicon substrate, and the oxide semiconductor layer is formed on the Schottky electrode layer. 7).

- 9. The Schottky barrier diode element according to any one of 1 to 8, which is covered with an insulating film so that an end portion of the oxide semiconductor layer is not exposed. 10.

- a vehicle including the Schottky barrier diode element according to any one of 1 to 9. 14 Including an oxide semiconductor layer and a metal thin film,

- the oxide semiconductor layer includes a polycrystalline and / or amorphous oxide semiconductor having a band gap of 3.0 eV or more and 5.6 eV or less; A structure including a region where the oxide semiconductor layer and the metal thin film are in electrical contact. 15.

- the oxide semiconductor is crystalline; In the oxide semiconductor, at least one element selected from Al, Si, Ce, Ga, Hf, Zr and Sm is contained in a ratio of 3 at% to 30 at% in all metal elements.

- the structure in any one of. 18.

- 27. An electric circuit including the power semiconductor element according to 27.23, the diode element according to 24, or the Schottky barrier diode element according to 25 or 26.

- 28. An electric device including the electric circuit according to 28.27.

- Electronic equipment including the electric circuit according to 29.27.

- a vehicle including the electric circuit according to 30.27.

- a Schottky barrier diode element having excellent current-voltage characteristics by forming a compound semiconductor having a wide band gap on a Si substrate by a method that is inexpensive and excellent in mass productivity.

- an oxide semiconductor substrate suitable for a Schottky barrier diode element, a diode element, or a power semiconductor element can be provided.

- a Schottky barrier diode element of the present invention is a Schottky barrier diode element having a silicon (Si) substrate, an oxide semiconductor layer, and a Schottky electrode layer, wherein the oxide semiconductor layer is , 3.0 eV or more and 5.6 eV or less of a polycrystalline and / or amorphous oxide semiconductor.

- a polycrystalline and / or amorphous oxide semiconductor having a wide band gap it is possible to provide a Schottky barrier diode element having excellent current-voltage characteristics, particularly a high breakdown electric field.

- a material having a wide band gap it is possible to use a polycrystalline and / or amorphous material instead of a single crystal which is expensive to manufacture such as crystal growth.

- Examples of the oxide semiconductor having a band gap of 3.0 eV or more and 5.6 eV or less include an oxide containing one or more selected from the group consisting of In, Ti, Zn, Ga, and Sn. 2 O 3, TiO 2, ZnO , Ga 2 O 3, SnO , and the like.

- the oxide semiconductor included in the oxide semiconductor layer is preferably at least one selected from the group consisting of In 2 O 3 , TiO 2 , ZnO, Ga 2 O 3, and SnO.

- In 2 O 3 A solid solution of Ti, Zn, Ga, or Sn, a composite oxide of In and Ti, Zn, Ga, or Sn, and an amorphous oxide containing these elements at a predetermined atomic ratio are also included.

- the band gap can be calculated by the following method. That is, first, an oxide semiconductor thin film is formed by sputtering on a transparent substrate such as glass with a film thickness of 300 nm, and a range of 250 nm to 1000 nm using a UV-VIS measuring apparatus (for example, UV-3100 manufactured by Shimadzu Corporation). Measure the transmittance. Next, with respect to the obtained transmittance, h ⁇ [eV] is plotted on the x-axis and ( ⁇ h ⁇ ) 1/2 [(eV 1/2 ) (cm ⁇ 1/2 )] is plotted (Tauc plot) on the y-axis.

- a UV-VIS measuring apparatus for example, UV-3100 manufactured by Shimadzu Corporation

- h is the Planck constant [J ⁇ s]

- ⁇ is the frequency [s ⁇ 1 ]

- ⁇ is the extinction coefficient [cm ⁇ 1 ]

- the outer portion of the straight line is placed on the x axis, and the intersection is obtained to obtain the oxidation point.

- the band gap of the physical semiconductor thin film can be obtained.

- an oxide thin film exists on a colored substrate or in a diode substrate, it can be calculated in the same manner by evaluating the reflectance spectrum after exposing the film surface.

- the elemental composition ratio of the oxide semiconductor layer can be obtained by quantitative analysis by secondary ion mass spectrometry (SIMS). Specifically, the surface of the semiconductor layer is exposed by a method such as polishing, and then quantified by a calibration curve method using a standard sample having a known concentration.

- SIMS secondary ion mass spectrometry

- a preferable addition concentration of an element other than indium differs depending on whether it is used as a crystalline semiconductor or an amorphous semiconductor.

- a crystalline semiconductor for an indium oxide crystal, Al, Si, Ga, Hf, Zr, Ce, and Sm are all metal elements including 3 at% to 30 at% and Zn is all metal elements including In. It is 5 at% or more and 40 at% or less.

- Sn is effective for reducing the resistance of the target, and is preferably 500 ppm or more and 3 at% or less in all metal elements including In. Since Sn acts as a donor for crystalline indium oxide, it is preferable not to exceed 3 at%.

- a conventionally known composition may be a three-component system such as IGZO111, ITZO, IZZrO, or IZAlO, or a two-component system such as IGO, IZO, or ITO.

- the concentration of In is preferably less than 90%, and the annealing temperature is preferably suppressed to 300 ° C. or lower.

- silicon (Si) substrate either an n-type silicon substrate or a p-type silicon substrate can be used.

- a conventionally known substrate having excellent surface smoothness such as a silicon single crystal substrate, a silicon polycrystalline substrate, or a silicon microcrystal substrate can be used.

- One form of polycrystal is a microcrystal.

- Polycrystals are single crystal aggregates, where there are distinct grain boundaries and often affect electrical properties. Among them, the microcrystals have a grain size of submicron or less, and no clear grain boundary exists. For this reason, there is an advantage that there is little variation in electrical characteristics due to grain boundary scattering.

- an oxide semiconductor layer is formed on a silicon substrate, and a Schottky electrode layer is formed on the oxide semiconductor layer.

- an oxide semiconductor layer is stacked on the surface side of the substrate, and an electrode layer (Pt, Au, Pd, Ni, etc.) for forming a Schottky is further disposed thereon.

- an electrode layer such as Ti that forms an ohmic junction with n-type silicon is laminated.

- a good conductor such as Au is laminated on the back surface side with Ni interposed therebetween. Ni has an effect of preventing diffusion of Au.

- a Schottky electrode layer is formed on a silicon substrate, and an oxide semiconductor layer is formed on the Schottky electrode layer.

- a Schottky electrode layer such as Pt, Au, Pd, or Ni is first laminated on the surface side of the substrate, and an oxide semiconductor layer is formed thereon by a sputtering method.

- the Schottky barrier is formed at the interface between a metal such as Pt, Au, Pd, and Ni and the oxide semiconductor layer.

- the surface of the Schottky electrode layer is oxidized with oxygen plasma, UV ozone, or the like before forming the oxide semiconductor layer, better diode characteristics can be obtained.

- a metal such as Ti that forms an ohmic junction with the oxide semiconductor is stacked on the oxide semiconductor layer.

- a good conductor such as Au may be further stacked with Ni interposed therebetween.

- an electrode having excellent adhesion for assisting conduction is laminated on the back side of the p-type silicon wafer.

- the Schottky barrier diode element of the present invention may be provided with a conventionally known guard ring structure.

- the guard ring is stacked between the oxide semiconductor layer and the Schottky electrode layer, and has an effect of improving the withstand voltage. Since an electric field concentrates on the end portion (edge portion) of the oxide semiconductor layer and dielectric breakdown easily occurs. When an insulating film such as SiO 2 is laminated so as to cover this end portion, the withstand voltage (dielectric breakdown voltage) is further increased. Can be raised.

- the Schottky barrier diode element of the present invention is preferably covered with an insulating film so that the end of the oxide semiconductor layer is not exposed.

- the oxide semiconductor may be crystallized by annealing. By crystallizing the oxide semiconductor, the on-resistance can be reduced.

- the conditions for the annealing treatment are not particularly limited. For example, after forming the oxide semiconductor layer, the oxide state is treated in air at 300 ° C. for 2 hours to stabilize the oxidation state, and then the electrode layer is formed, and then in the air. And treatment at 200 ° C. for 1 hour. Crystallization of the oxide semiconductor can be confirmed by X-ray diffraction (XRD) measurement.

- XRD X-ray diffraction

- the Schottky barrier diode element of the present invention has a high breakdown electric field.

- the breakdown electric field of the Schottky barrier diode element of the present invention is preferably 0.5 MV / cm or more, more preferably 0.7 MV / cm or more. Thereby, since the diode can be designed to be thin, the element can be made small, and a heat dissipation measure is advantageous.

- the n value of the Schottky barrier diode element of the present invention is preferably 2 or less, more preferably 1.5 or less. Thereby, on-resistance becomes small and heat generation can be suppressed.

- the dielectric breakdown electric field and the n value are measured and calculated by the method described in the examples.

- the Schottky barrier diode element of the present invention is suitably used for electric circuits, electric devices, electronic devices, vehicles, and electric vehicles.

- the structure of the present invention includes an oxide semiconductor layer and a metal thin film, and includes a region where the oxide semiconductor layer and the metal thin film are in electrical contact.

- the oxide semiconductor layer includes a polycrystalline and / or amorphous oxide semiconductor having a band gap of 3.0 eV or more and 5.6 eV or less.

- the oxide semiconductor layer and the metal thin film are in electrical contact means that the metal thin film and the oxide semiconductor layer form a junction so that the Fermi energies of the two coincide with each other. This means a contact state in which electrons can freely diffuse.

- the “electrically contacting region” specifically includes a region that is directly bonded without using an insulating film or the like.

- the carrier concentration is preferably 10 20 cm ⁇ 3 or more.

- the carrier concentration is lower than this, when the oxide semiconductor containing In as a main component is stacked, the depletion layer expands, which causes internal resistance and is disadvantageous for high-speed switching characteristics.

- a preferable metal thin film material is Au, Ir, Ni, Pd, or W for stacking with an oxide semiconductor containing In as a main component.

- These materials may be added with a trace amount of metal to the extent that the work function is not reduced in order to improve the workability.

- the material of the metal thin film is Au, an alloy added with Ag and Cu can be used, and if it is Pd, an alloy added with Ag and Cu can be used.

- the work function is measured using a photoelectron spectrometer (for example, AC-3, manufactured by Riken Keiki Co., Ltd.).

- the work function varies depending on the surface treatment of acid, alkali, etc., UV cleaning, and the like.

- the work function described in the present invention refers to a value measured as it is without performing treatment after film formation.

- the above oxide semiconductor preferably contains In as a main component. “Mainly containing In” is as described in the above Schottky barrier diode element of the present invention.

- the band gap is the same as that of the above Schottky barrier diode element.

- the oxide semiconductor is polycrystalline or amorphous, or may be a mixture of polycrystalline and amorphous, and is preferably crystalline.

- the oxide semiconductor preferably contains at least one element selected from Al, Si, Ce, Ga, Hf, Zr, and Sm.

- the content of the oxide semiconductor includes all metal elements of the oxide semiconductor. Among these, 3 at% or more and 30 at% or less are preferable.

- the above oxide semiconductor preferably has a carrier concentration of 1 ⁇ 10 14 cm ⁇ 3 or more and 1 ⁇ 10 17 cm ⁇ 3 or less at room temperature (298 K).

- the carrier concentration is more preferably 1 ⁇ 10 15 cm ⁇ 3 or more and 5 ⁇ 10 16 cm ⁇ 3 or less.

- the carrier concentration is less than 1 ⁇ 10 14 cm ⁇ 3 , when used as a diode element, the on-resistance becomes too high, and heat may be generated during operation, which is not preferable.

- the carrier concentration exceeds 1 ⁇ 10 17 cm ⁇ 3 , the resistance becomes too low, and the leakage current at the time of reverse bias may increase.

- thermal CVD method As for thin film formation technology, thermal CVD method, CAT-CVD method, photo CVD method, mist CVD method, CVD method such as MO-CVD, plasma CVD, atomic level control film forming method such as MBE, ALD, ion plating, etc.

- PVD methods such as ion beam sputtering and magnetron sputtering, doctor blade method, injection method, extrusion method, hot press method, sol-gel method, aerosol deposition method, etc., methods using conventional ceramic processes, coating methods, spin coating Methods, printing methods, spraying methods, electrodeposition methods, plating methods, wet methods such as micelle electrolysis, and the like can be used.

- the dielectric breakdown electric field of the structure of the present invention is 0.5 to 3 MV / cm, which is very superior to conventional silicon diodes.

- the required breakdown voltage varies depending on the application and purpose, and it is necessary to be 0.2 ⁇ m to 1.2 ⁇ m for a 60 V breakdown voltage and 2 ⁇ m to 12 ⁇ m for a 600 V breakdown voltage.

- a film thickness of 2 ⁇ m or more it is more advantageous in the production process to use the CVD method or the wet method than the PVD method.

- a preferable film thickness of the oxide semiconductor is 50 nm or more and 20 ⁇ m or less.

- the withstand voltage is about 10 V, which is insufficient as a dielectric breakdown voltage for many applications.

- the film thickness exceeds 20 ⁇ m, the withstand voltage can be realized at 5000 V, but the On resistance becomes high, causing a problem of heat generation during switching.

- a more preferable range of the film thickness is 200 nm or more and 12 ⁇ m or less.

- these film thicknesses can be measured with a stylus type step gauge such as a surf coder or DEKTAK, or an electron microscope such as TEM or SEM.

- the structure body of the present invention can be preferably used as an oxide semiconductor substrate by being stacked over a conductive substrate or an electrically insulating substrate.

- the oxide semiconductor substrate of the present invention has a rectifying property and can be suitably used for manufacturing a Schottky barrier diode element, a power semiconductor element, and a diode element, that is, a useful intermediate.

- the metal thin film functions as a Schottky electrode layer, and the oxide semiconductor layer in electrical contact with the metal thin film functions as an oxide semiconductor layer.

- the structure body may be stacked on either a conductive or electrically insulating substrate, but using a conductive substrate is superior in terms of heat dissipation.

- a conductive substrate a conventionally known substrate having excellent surface smoothness such as a silicon single crystal substrate, a silicon polycrystalline substrate, or a silicon microcrystal substrate can be used.

- One form of polycrystal is a microcrystal.

- Polycrystals are single crystal aggregates, where there are distinct grain boundaries and often affect electrical properties. Among them, the microcrystals have a grain size of submicron or less, and no clear grain boundary exists. For this reason, there is an advantage that there is little variation in electrical characteristics due to grain boundary scattering.

- the characteristic required for the oxide semiconductor substrate of the present invention is surface smoothness, and conductivity is also required particularly when used in the vertical direction. Although it is a silicon substrate that can realize this condition at a low cost, it is not indispensable. Can also be used. In particular, if a metal material having high thermal conductivity is used, a heat dissipation effect can be expected, and a heat sink structure may be used as necessary.

- compound single crystal wafers such as GaAs and InP, Al 2 O 3 , ZnO, MgO, SrTiO 3 , YSZ, lanthanum aluminate, Y 3 Al 5 O 12 , NdGaO 3 , sapphire, AlN, GaN, SiC, non-alkali Substrates such as various oxides, nitrides and carbides such as glass and soda lime glass can also be used.

- the substrate may be insulative. Note that the vertical direction means that a current is applied in a direction perpendicular to the oxide semiconductor film surface, and the horizontal direction means that a current is supplied in a horizontal direction relative to the oxide semiconductor film surface.

- a resin substrate such as polycarbonate, polyarylate, polyethylene terephthalate, polyethersulfone, polyimide, or phenol resin can be used. Since the structure of the present invention does not require a high-temperature process, a power supply unit of a circuit for driving a display such as a liquid crystal display or an organic EL can be mounted on the same substrate as the display.

- the oxide semiconductor substrate of the present invention is suitably used for each of a power semiconductor element, a diode element, and a Schottky barrier diode element, and an electric circuit including at least one of the power semiconductor element, the diode element, and the Schottky barrier diode element is It is suitably used for electric devices, electronic devices, and electric vehicles.

- the present invention provides a suitable laminate as a member constituting a power semiconductor element, specifically, a diode element, an IGBT (Insulated Gate Bipolar Transistor) element, a MOSFET (Metal Oxide Semiconductor Field Effect Transistor).

- a diode element specifically, an IGBT (Insulated Gate Bipolar Transistor) element, a MOSFET (Metal Oxide Semiconductor Field Effect Transistor).

- a Schottky barrier diode element, a PN diode element, or a PIN diode element can be suitably provided.

- the inverter circuit is required to have a high operating frequency and a short recovery time when switching.

- the film thickness is small and it is unipolar, so that the recovery time can be extremely reduced. Therefore, the higher the operating frequency, the more the characteristics of the diode of the present invention can be utilized.

- GTO Gate Turn-Off thyristor

- a GTO Gate Turn-Off thyristor

- the frequency is about 500 Hz, and noise at the time of starting has been a problem. Therefore, in recent vehicles and EVs, an example of mounting an IGBT is increasing.

- the switching speed of the IGBT can be increased to several tens of kHz, so that noise can be suppressed and peripheral members can be downsized.

- the diode of the present invention having a reverse leakage current smaller than that of a conventional Si diode is particularly effective as a fast recovery diode used in an IGBT inverter.

- the cooling mechanism can be further simplified. For example, in the case of EV, there is an effect that a plurality of cooling mechanisms that have been conventionally required can be integrated with a 110 ° C. radiator.

- a 300 nm thick oxide film (IGO film) 12 containing indium and gallium was formed.

- the substrate 11 also functions as a contact electrode.

- this IGO film was patterned by photolithography to form a desired pattern, and then annealed in air at 300 ° C. for 2 hours to crystallize the IGO film.

- the crystal state of the IGO film was confirmed by XRD measurement and found to be a polycrystal.

- This Si substrate with a polycrystalline IGO film was again mounted on a sputtering apparatus, and a sputtering film was formed using a Pt target, and a Pt electrode 13 was formed on the polycrystalline IGO film to obtain a Schottky junction.

- the substrate is dipped again in dilute hydrofluoric acid to remove the natural oxide film on the back side where the polycrystalline IGO film is not formed, and the Ti layer 14, Ni layer 15 and Au layer 16 are sputtered in this order.

- an ohmic electrode was formed.

- the laminated body obtained by forming this ohmic electrode was annealed in air at 200 ° C. for 1 hour to obtain a Schottky barrier diode element 10.

- ⁇ represents the dielectric constant [F / cm] of the semiconductor

- W represents the depletion layer width [cm].

- ⁇ is the built-in potential [V]

- N represents the contact potential difference between the Pt electrode and the IGO film.

- n value is a parameter indicating the characteristics of the Schottky barrier diode element as shown by the following formula (1). As n approaches 1, ideal element characteristics are obtained.

- I I 0 [exp (eV / nkT)] (1)

- I Total current density [A / cm 2 ] flowing from the oxide film toward the Si substrate side e: charge of electrons, 1.60 ⁇ 10 ⁇ 19 [C]

- V voltage applied to the device [V]

- k Boltzmann constant, 1.38 ⁇ 10 ⁇ 23 [J / K]

- T Temperature [K]

- the n value was 1.3 and the reverse breakdown voltage was 20V.

- This reverse breakdown voltage corresponds to a dielectric breakdown electric field of 0.67 MV / cm, which is about twice as high as that of a conventional Schottky barrier diode using single crystal Si.

- the reverse breakdown voltage and the dielectric breakdown electric field have the following relationship.

- Reverse breakdown voltage (V) dielectric breakdown electric field (V / cm) x semiconductor film thickness (cm)

- the results are shown in Table 1.

- the “forward voltage” in the table is a voltage necessary for a current of 0.1 mA / cm 2 to flow through the element, and the “On current density” is a current density when 10 V is applied to the element.

- Example 2 to Example 9 Hereinafter, as shown in Table 1, a Schottky barrier diode element was fabricated and evaluated in the same manner as in Example 1 using the sputtering method while appropriately changing the composition of the Schottky electrode and the semiconductor. The results are shown in Table 1.

- FIG. 2 is a cross-sectional view schematically showing the Schottky barrier diode element obtained in Example 10.

- a p-type silicon substrate 21 having a resistivity of 0.02 ⁇ ⁇ cm was prepared, the natural oxide film was removed with dilute hydrofluoric acid, and then a Pd target was formed by sputtering to form a Pd electrode 22.

- the IGO film 23 was formed by sputtering in the same manner as in Example 1.

- an ohmic electrode was formed by sputtering a Ti layer 24, a Ni layer 25, and an Au layer 26 in this order on the IGO film.

- a TiAl film 27 was formed by sputtering using a TiAl alloy as a target. . Finally, annealing was performed in air at 200 ° C. for 1 hour to obtain a Schottky barrier diode element 20.

- the polarity of this diode is opposite to that of the diodes of Examples 1 to 9, and the forward direction is obtained when the p-type silicon wafer side is connected to the positive side, and the reverse direction when the p-type silicon wafer side is connected to the negative side.

- the obtained device was evaluated in the same manner as in Example 1. The results are shown in Table 1.

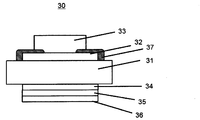

- FIG. 3 is a cross-sectional view schematically showing the Schottky barrier diode element obtained in Example 11.

- an IGO film 32 of an oxide semiconductor was sputtered on an n-type silicon substrate 31 and annealed in air at 300 ° C. for 1 hour, and then a negative resist manufactured by AZ Materials was spin-coated. Was applied.

- a pattern dug in a ring shape was formed at the edge (end portion) of the IGO film by pre-baking, exposure, development, and post-baking.

- Example 12 An n-type silicon (Si) substrate having a resistivity of 0.02 ⁇ ⁇ cm was prepared and treated with dilute hydrofluoric acid to remove the natural oxide film formed on the surface of the substrate. This Si substrate was mounted on a sputtering apparatus (manufactured by Shimadzu Corporation: HSM552), and Ti was first formed as an ohmic electrode.

- Si n-type silicon

- this IGO film was annealed in air at 300 ° C. for 1 hour, patterned by photolithography to form a desired pattern, and then annealed in air at 300 ° C. for 1 hour.

- the substrate with the amorphous IGO film was mounted on the sputtering apparatus again, and sputtering film formation was performed using a Ni target, and a Ni electrode was formed on the amorphous IGO film to obtain a Schottky junction. Further, Au was sputtered on the Ni electrode to obtain a Schottky barrier diode element having a simple configuration.

- the device obtained in the same manner as in Example 1 was evaluated. The results are shown in Table 2.

- Examples 13-20 A Schottky barrier diode element was fabricated and evaluated in the same manner as in Example 1 while appropriately changing the composition of the oxide semiconductor. The results are shown in Table 2. “4H—SiC” means a hexagonal SiC substrate having a four-layer repeating structure, and “YSZ” means an yttria-stabilized zirconia substrate. In Examples 13, 16, 18, 19, and 20, since a high-resistance substrate was used, electrical measurement was performed by placing terminals on the ohmic electrode and the Schottky electrode.

- Comparative Example 1 An n-type silicon (Si) substrate having a resistivity of 0.02 ⁇ ⁇ cm was prepared and treated with dilute hydrofluoric acid to remove the natural oxide film formed on the surface of the substrate. This Si substrate was mounted on a sputtering apparatus (manufactured by Shimadzu Corporation: HSM552), and Ti was first formed as an ohmic electrode. Next, a SiC target (manufactured by Sumitomo Osaka Cement Co., Ltd.) was used as a sputtering target, and sputter discharge was performed under the condition of RF 100 W to form a SiC film having a thickness of 1 ⁇ m on the Ti layer on the Ti-attached Si substrate.

- a SiC target manufactured by Sumitomo Osaka Cement Co., Ltd.

- this SiC film was patterned by photolithography to form a desired pattern, and then annealed in air at 300 ° C. for 1 hour. As a result of confirming the SiC film by XRD and SEM, it was polycrystalline.

- This substrate with polycrystalline SiC was again mounted on the sputtering apparatus, and sputtering film formation was performed using a Ni target, and a Ni electrode was formed on the polycrystalline SiC to obtain a Schottky junction. Further, Au was sputtered on the Ni electrode to obtain a Schottky barrier diode element having a simple configuration.

- the obtained device was evaluated in the same manner as in Example 1. The results are shown in Table 2.

- the device obtained in Comparative Example 1 showed a carrier concentration of 5 ⁇ 10 15 cm ⁇ 3 , but the n value exceeded 10 and did not show satisfactory diode characteristics. Also, the dielectric breakdown electric field remained at 0.1 MV / cm.

- Comparative Example 2 A Schottky barrier diode made of polycrystalline GaN was fabricated and evaluated in the same manner as in Comparative Example 1 except that single crystal GaN was used as the target instead of the SiC target. The results are shown in Table 2. The element obtained in Comparative Example 2 had an n value of more than 10 and did not exhibit satisfactory diode characteristics, and the dielectric breakdown electric field remained at 0.1 MV / cm.

- a Schottky barrier diode was fabricated and evaluated in the same manner as described above. The results are shown in Table 2.

- the device obtained in Comparative Example 3 had a very wide band gap of 5.8 eV or more, but the carrier concentration was very low, less than 10 13 cm ⁇ 3 , and a sufficient forward current could not be obtained.

- the Schottky barrier diode element of the present invention can be suitably used for an electric circuit, an electric device, an electronic device, an electric vehicle and the like that require high speed operation and switching characteristics.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

また、本発明は、ショットキーバリアダイオード素子、ダイオード素子、パワー半導体素子に好適な酸化物半導体基板を提供することを目的とする。

1.シリコン(Si)基板と、酸化物半導体層と、ショットキー電極層とを有するショットキーバリアダイオード素子であって、前記酸化物半導体層が、3.0eV以上、5.6eV以下のバンドギャップを有する多結晶及び/又は非晶質の酸化物半導体を含むショットキーバリアダイオード素子。

2.前記酸化物半導体が、In、Ti、Zn、Ga及びSnからなる群から選択される1種以上を含む1記載のショットキーバリアダイオード素子。

3.前記酸化物半導体層がインジウム(In)を主成分として含む1又は2に記載のショットキーバリアダイオード素子。

4.前記酸化物半導体層中に含まれる全金属元素に対するインジウムの原子組成百分率([In]/([In]+[In以外の全金属元素])×100)が30~100atm%である1~3のいずれかに記載のショットキーバリアダイオード素子。

5.前記シリコン基板上に前記酸化物半導体層が形成され、前記酸化物半導体層上に前記ショットキー電極層が形成された1~4のいずれかに記載のショットキーバリアダイオード素子。

6.前記シリコン基板上に前記ショットキー電極層が形成され、前記ショットキー電極層上に前記酸化物半導体層が形成された1~4のいずれかに記載のショットキーバリアダイオード素子。

7.前記酸化物半導体層が、さらに、Al、Si、Zn、Ga、Hf、Zr、Ce、Sm、及びSnから選ばれる1種以上の元素を含む2~6のいずれかに記載のショットキーバリアダイオード素子。

8.前記酸化物半導体層の室温におけるキャリア濃度が1×1014cm-3以上、1×1017cm-3以下である1~7のいずれかに記載のショットキーバリアダイオード素子。

9.前記酸化物半導体層の端部が露出しないように絶縁膜により被覆されている1~8のいずれかに記載のショットキーバリアダイオード素子。

10.1~9のいずれかに記載のショットキーバリアダイオード素子を含む電気回路。

11.1~9のいずれかに記載のショットキーバリアダイオード素子を含む電気機器。

12.1~9のいずれかに記載のショットキーバリアダイオード素子を含む電子機器。

13.1~9のいずれかに記載のショットキーバリアダイオード素子を含む車両。

14.酸化物半導体層と金属薄膜を含み、

前記酸化物半導体層が、3.0eV以上、5.6eV以下のバンドギャップを有する多結晶及び/又は非晶質の酸化物半導体を含み、

前記酸化物半導体層と前記金属薄膜とが電気的に接触する領域を含む

構造体。

15.前記酸化物半導体がInを主成分とする14に記載の構造体。

16.前記金属薄膜の仕事関数が4.7eV以上である14又は15に記載の構造体。

17.前記酸化物半導体が結晶質であり、

前記酸化物半導体中に、Al,Si,Ce、Ga、Hf、Zr及びSmから選ばれる少なくとも1種類の元素が全金属元素中3at%以上、30at%以下の割合で含まれている14~16のいずれかに記載の構造体。

18.前記酸化物半導体の室温におけるキャリア濃度が1×1014cm-3以上、1×1017cm-3以下である14~17のいずれかに記載の構造体。

19.前記酸化物半導体層の膜厚が50nm~20μmである14~18のいずれかに記載の構造体。

20.14~19のいずれかに記載の構造体が導電性基板上に積層してなる酸化物半導体基板。

21.前記導電性基板が単結晶シリコン、多結晶シリコン及び微結晶シリコンから選ばれる1以上から構成される20に記載の酸化物半導体基板。

22.14~19のいずれかに記載の構造体が電気絶縁性基板上に積層してなる酸化物半導体基板。

23.20~22のいずれかに記載の酸化物半導体基板を用いたパワー半導体素子。

24.20~22のいずれかに記載の酸化物半導体基板を用いたダイオード素子。

25.20~22のいずれかに記載の酸化物半導体基板を用いたショットキーバリアダイオード素子。

26.前記金属薄膜をショットキー電極層とする25に記載のショットキーバリアダイオード素子。

27.23に記載のパワー半導体素子、24に記載のダイオード素子、又は25もしくは26に記載のショットキーバリアダイオード素子を含む電気回路。

28.27に記載の電気回路を含む電気機器。

29.27に記載の電気回路を含む電子機器。

30.27に記載の電気回路を含む車両。

また、本発明によれば、ショットキーバリアダイオード素子、ダイオード素子、パワー半導体素子に好適な酸化物半導体基板を提供することができる。

本発明のショットキーバリアダイオード素子は、シリコン(Si)基板と、酸化物半導体層と、ショットキー電極層とを有するショットキーバリアダイオード素子であって、前記酸化物半導体層が、3.0eV以上、5.6eV以下のバンドギャップを有する多結晶及び/又は非晶質の酸化物半導体を含む。バンドギャップの広い多結晶及び/又は非晶質の酸化物半導体を用いることで、優れた電流-電圧特性、特に高い絶縁破壊電界を有するショットキーバリアダイオード素子を提供することができる。

また、バンドギャップの広い材料を用いることで、結晶成長等、製造にコストのかかる単結晶ではなく、多結晶及び/又は非晶質の材料を使用することが可能となる。

酸化物半導体層に含まれる酸化物半導体は、In2O3、TiO2、ZnO、Ga2O3及びSnOからなる群から選択される1種以上であると好ましく、例えば、In2O3にTi、Zn、Ga又はSnが固溶したもの、InとTi、Zn、Ga又はSnとの複合酸化物、及びこれらの元素を所定の原子比で含有する非晶質酸化物も含まれる。また、酸化物半導体は、適宜不純物をドーピングして、導電性を調整してもよい。例えば、酸化物半導体層を形成する際に用いるスパッタリングターゲットの性能(焼結密度、抗折強度等)の観点からは、酸化物半導体はIn2O3を主成分とすることが好ましい。

これらの酸化物半導体は、多結晶であるか、非晶質であるか、又は多結晶と非晶質が混在していてもよい。

ここで、hはプランク定数[J・s]、νは振動数[s-1]、αは吸光係数[cm-1]、次いで、直線部分をx軸に外層し、交点を求めることで酸化物半導体薄膜のバンドギャップが得られる。

尚、着色基板上や、ダイオード基板中に酸化物薄膜が存在する場合は、膜面を面出しした後、反射率のスペクトルを評価することで、同様に計算することができる。

本発明において「酸化物半導体層がインジウム(In)を主成分として含む」とは、酸化物半導体層中に含まれる全金属元素に対するインジウムの原子組成百分率([In]/([In]+[In以外の全金属元素])×100)が30~100atm%であることを意味する。バンドギャップの広い酸化インジウム系の材料を用いることで、優れた電流-電圧特性、特に高い絶縁破壊電界を有するショットキーバリアダイオード素子を提供することができる。

酸化物半導体層中のインジウムの含有割合は、例えばスパッタリングターゲットにおけるインジウムの含有割合を変更することによって調整することができる。他の元素についても同様である。

スパッタリングターゲットの元素組成比は、誘導結合プラズマ発光分光分析装置(ICP-AES)により定量分析して求める。具体的に、スパッタリングターゲットを酸処理により溶解させた溶液試料を、濃度が既知の標準試料を用いて検量線法により定量する。そして、得られた溶液中の濃度をターゲット中のat%に換算することでターゲットの元素組成比が得られる。

添加元素は、好ましくは、Al、Si、Zn、Ga、Hf、Ce、Sm、及びSnから選ばれる1種以上の元素である。

酸化物半導体層は、単結晶である必要はなく、非晶質であっても、多結晶であってもよい。

但し、良好なダイオード特性を示すためには、酸化物半導体層の室温(298K)におけるキャリア濃度は1×1014cm-3以上、1×1017cm-3以下であることが好ましい。キャリア濃度が1×1014cm-3未満の場合、オン抵抗が高くなりすぎ、動作時に発熱を招くおそれがあり、好ましくない。キャリア濃度が1×1017cm-3を超えた場合、抵抗が低くなりすぎ、逆バイアス時のリーク電流が上昇するおそれがある。

キャリア濃度は、1×1015cm-3以上、5×1016cm-3以下であるとより好ましい。

キャリア濃度は、実施例に記載の方法で測定する。

また、非晶質半導体の場合、従来公知の組成として、IGZO111、ITZO、IZZrO、IZAlO等の3成分系や、IGO、IZO、ITO等の2成分系を使用することができる。尚、この場合のInの濃度は90%未満とし、アニール温度を300℃以下に抑えると好ましい。

この場合もキャリア濃度を1×1014cm-3以上、1×1017cm-3の範囲となるように、酸化雰囲気下でアニールして調整することが好ましい。

尚、多結晶の一つの形態が微結晶である。多結晶は単結晶の集合体であり、明確な粒界が存在し、しばしば電気特性に影響を与える。この中で微結晶は、粒径のサイズがサブミクロン以下であり、明解な粒界が存在しない。このため、粒界散乱による電気特性のバラツキが少ないという長所がある。

一方、オーミック電極層に使用される金属の仕事関数は、シリコンウェハーの不純物濃度にもよるが、4.1eV程度が好ましく、密着性も考慮するとTiやMoが好ましい。

仕事関数の測定は、後述する方法により行うことができる。

n型シリコンウェハーを用いた場合、基板の表面側に酸化物半導体層が積層され、さらにその上に、ショットキーを形成する電極層(Pt、Au、Pd、Ni等)が配置される。基板の裏面側にはTi等の、n型シリコンとオーミック接合を形成する電極層が積層される。また、導通を確保するため、裏面側は、Niを挟んでAu等の良導体を積層すると好ましい。尚、NiはAuの拡散を防止する効果がある。

p型シリコンウェハーを用いた場合、基板の表面側は、最初にPt、Au、Pd、Ni等のショットキー電極層が積層され、その上に、酸化物半導体層がスパッタ法により形成される。この場合もショットキー障壁は、Pt、Au、Pd、Ni等の金属と、酸化物半導体層の界面に形成される。また、酸化物半導体層を形成する前に、ショットキー電極層表面を酸素プラズマやUVオゾン等で酸化処理すると、より良好なダイオード特性を得ることができる。

本発明のショットキーバリアダイオード素子は、酸化物半導体層の端部が露出しないように絶縁膜により被覆されていることが好ましい。

酸化物半導体層の膜厚は、後述する本発明の構造体における酸化物半導体層と同じである。

また、ショットキー電極を形成する電極層と酸化物半導体層の界面は、ショットキー電極スパッタ工程で酸素を導入して反応性スパッタを行い、10nm以下の薄い酸化膜を積層してもよい。

本発明のショットキーバリアダイオード素子のn値は、好ましくは2以下であり、より好ましくは1.5以下である。これにより、オン抵抗が小さくなり、発熱を抑制することができる。

絶縁破壊電界、n値は実施例に記載の方法により測定、算出する。

本発明の構造体は、酸化物半導体層と金属薄膜を含み、酸化物半導体層と金属薄膜とが電気的に接触する領域を含む。酸化物半導体層は、3.0eV以上、5.6eV以下のバンドギャップを有する多結晶及び/又は非晶質の酸化物半導体を含む。

仕事関数が4.7eV以上の金属薄膜とは、Au,Cr,Cu,Fe,Ir,Mo,Nb,Ni,Pd,Pt,Re,Ru,W等の金属やIn2O3,ITO,IZO等の金属酸化物等が挙げられる。尚、仕事関数はより大きく、キャリア濃度の高い金属を用いた方が、明確な整流特性を得る上で有利である。仕事関数のより好ましい範囲は4.8eV以上であり、5.0eV以上であることがさらに好ましい。上限値は特に限定されないが、好ましくは5.6eV以下である。

また、酸化物半導体中に、Al,Si,Ce、Ga、Hf、Zr及びSmから選ばれる少なくとも1種類の元素が含まれていると好ましく、その含有量としては、酸化物半導体の全金属元素中、3at%以上30at%以下が好ましい。

キャリア濃度が1×1014cm-3未満の場合、ダイオード素子として用いた場合、オン抵抗が高くなりすぎ、動作時に発熱を招くおそれがあり、好ましくない。キャリア濃度が1×1017cm-3を超えた場合、抵抗が低くなりすぎ、逆バイアス時のリーク電流が上昇するおそれがある。

本発明の構造体の絶縁破壊電界は0.5~3MV/cmと、従来のシリコン系ダイオードと比較して非常に優れた性能を有する。求められる耐圧は用途と目的に応じて異なり、60V耐圧では0.2μm~1.2μm、600V耐圧では2μm~12μmが必要となる。特に2μm以上の膜厚が必要な場合はPVD法よりもCVD法や湿式法を用いる方が生産工程上有利である。

また、これらの膜厚は、サーフコーダやDEKTAK等の触針式段差計や、TEMやSEM等の電子顕微鏡で測定することができる。

本発明の酸化物半導体基板は整流特性を有し、ショットキーバリアダイオード素子、パワー半導体素子、ダイオード素子を製造するのに好適に用いることができ、即ち、有用な中間体である。

ショットキーバリアダイオード素子として用いる場合、本発明の構造体は、前記金属薄膜がショットキー電極層として機能し、金属薄膜と電気的に接触する酸化物半導体層が酸化物半導体層として機能する。

導電性基板としては、シリコン単結晶基板、シリコン多結晶基板、シリコン微結晶基板等、従来公知の表面平滑性に優れた基板を用いることができる。

尚、多結晶の一つの形態が微結晶である。多結晶は単結晶の集合体であり、明確な粒界が存在し、しばしば電気特性に影響を与える。この中で微結晶は、粒径のサイズがサブミクロン以下であり、明解な粒界が存在しない。このため、粒界散乱による電気特性のバラツキが少ないという長所がある。

尚、縦方向とは、酸化物半導体の膜面に対して垂直方向に通電することを意味し、横方向とは、酸化物半導体の膜面に対して水平方向に通電することを意味する。

実施例1

図1は、実施例1により得られたショットキーバリアダイオード素子を模式的に示した断面図である。

まず、抵抗率0.02Ω・cmのn型シリコン(Si)基板11を用意し、希フッ酸で処理して、基板の表面に形成されていた自然酸化膜を除去した。このSi基板をスパッタリング装置(島津製作所製:HSM552)に装着した。In2O3:Ga2O3=95:5(wt%)の組成を有する焼結体をスパッタリングターゲットとして用い、RF100Wの条件でスパッタ放電して、Si基板の酸化膜を除去した面上に、インジウム及びガリウムを含む厚さ300nmの酸化物膜(IGO膜)12を形成した。

尚、基板11はコンタクト電極としても機能する。

この多結晶IGO膜付きSi基板を再びスパッタリング装置に装着し、Ptターゲットを用いてスパッタリング成膜を行い、多結晶IGO膜上にPt電極13を形成して、ショットキー接合を得た。

CV測定を取得したのち、C-2-V特性をプロットし、傾きからドーピング濃度(=キャリア濃度)Nを求めることができる。その結果、スパッタリング成膜した後のIGO膜は抵抗が低く、空乏層が広がらなかったが、空気中、300℃、2時間の条件でアニールした後ではCV測定が可能であり、C-2-Vの傾きから計算した結果、キャリア濃度は5×1015cm-3であった。

I=I0[exp(eV/nkT)]・・・(1)

I:酸化物膜からSi基板側に向かって流れる全電流密度[A/cm2]

e:電子の電荷、1.60×10-19[C]

V:素子に印加される電圧[V]

I0:素子に印加される電圧V=0Vの時の電流密度[A/cm2]

k:ボルツマン定数、1.38×10-23[J/K]

T:温度[K]

逆耐圧(V)=絶縁破壊電界(V/cm)×半導体膜厚(cm)

以上の結果を表1に示す。尚、表中の「順方向電圧」は、素子に0.1mA/cm2の電流流すのに必要な電圧であり、「On電流密度」は、素子に10V印加したときの電流密度である。

以下、表1に示すように、ショットキー電極と半導体の組成を適宜変更しながら、いずれもスパッタリング法を用いて、実施例1と同様にショットキーバリアダイオード素子を作製し、評価した。結果を表1に示す。

図2は、実施例10により得られたショットキーバリアダイオード素子を模式的に示した断面図である。

まず、抵抗率0.02Ω・cmのp型シリコン基板21を用意し、自然酸化膜を希フッ酸で除去した後、Pdターゲットを用いてスパッタ成膜してPd電極22を形成した。次に、このPd電極の表面をUVオゾンで酸化処理した後、実施例1と同様にIGO膜23をスパッタ成膜した。空気中、300℃、1時間の条件でアニールした後、IGO膜上に、Ti層24、Ni層25、Au層26の順にスパッタ成膜してオーミック電極とした。

さらに、p型シリコン基板の裏面側(Pd電極を形成した面と反対の面側)についても希フッ酸にて自然酸化膜を除去した後、TiAl合金をターゲットとしてTiAl膜27をスパッタ成膜した。最後に空気中、200℃、1時間の条件でアニールして、ショットキーバリアダイオード素子20を得た。このダイオードは、実施例1~9のダイオードとは極性が逆であり、p型シリコンウェハー側をプラスに接続すると順方向、マイナスに接続すると逆方向となる。

得られた素子について実施例1と同様にして評価した。結果を表1に示す。

図3は、実施例11により得られたショットキーバリアダイオード素子を模式的に示した断面図である。

実施例1と同様にしてn型シリコン基板31に酸化物半導体のIGO膜32をスパッタし、空気中、300℃、1時間の条件でアニールした後、AZマテリアル社製のネガレジストをスピンコート法により塗布した。プリベーク、露光、現像、ポストベークにより、IGO膜のエッジ(端部)部分にリング状に掘れたパターンを形成した。次に、スパッタ装置に装着し、SiO2をターゲットとして、RF100W、50分の条件でスパッタ成膜して、厚さ50nmのSiO2膜を形成した。次いで、レジスト剥離液に浸漬して、不要部分のレジストをIGO膜ごと剥離した。このようにして、IGO膜のガードリング37を形成した。以後、実施例1と同様にして、Pt電極33と、Ti34、Ni35、Au36のオーミック電極を作製し、ガードリング付のショットキーバリアダイオード素子30を作製した。

得られた素子について実施例1と同様にして評価した。結果を表1に示す。このショットキーバリアダイオードは、ガードリングの効果により、実施例1と比較してさらに良好な耐圧特性を示した。

抵抗率0.02Ω・cmのn型シリコン(Si)基板を用意し、希フッ酸で処理して、基板の表面に形成されていた自然酸化膜を除去した。このSi基板をスパッタリング装置(島津製作所製:HSM552)に装着し、最初にオーミック電極としてTiを成膜した。次に、In2O3:Ga2O3=78:22(wt%)の組成を有する焼結体をスパッタリングターゲットとして用い、RF100Wの条件でスパッタ放電して、Ti付Si基板上のTi層の上に、厚さ1μmのインジウム及びガリウムを含む酸化物膜(IGO膜)を形成した。

この非晶質IGO膜付き基板を再びスパッタリング装置に装着し、Niターゲットを用いてスパッタリング成膜を行い、非晶質IGO膜上にNi電極を形成して、ショットキー接合を得た。さらに、このNi電極上にAuをスパッタ成膜して単純な構成のショットキーバリアダイオード素子を得た。実施例1と同様にして得られた素子を評価した。結果を表2に示す。

酸化物半導体の組成等を適宜変更しながら、実施例1と同様にショットキーバリアダイオード素子を作製し、評価した。結果を表2に示す。

尚、「4H-SiC」とは4層繰り返し構造を有する六方晶SiC基板を意味し、「YSZ」とはイットリア安定化ジルコニア基板を意味する。

また、実施例13、16、18、19、20においては高抵抗の基板を用いているため、電気測定はオーミック電極とショットキー電極に端子を当てて行った。

抵抗率0.02Ω・cmのn型シリコン(Si)基板を用意し、希フッ酸で処理して、基板の表面に形成されていた自然酸化膜を除去した。このSi基板をスパッタリング装置(島津製作所製:HSM552)に装着し、最初にオーミック電極としてTiを成膜した。次に、SiCターゲット(住友大阪セメント社製)をスパッタリングターゲットとして用い、RF100Wの条件でスパッタ放電して、Ti付Si基板上のTi層の上に、厚さ1μmのSiC膜を形成した。

この多結晶SiC付き基板を再びスパッタリング装置に装着し、Niターゲットを用いてスパッタリング成膜を行い、多結晶SiC上にNi電極を形成して、ショットキー接合を得た。さらに、このNi電極上にAuをスパッタ成膜して単純な構成のショットキーバリアダイオード素子を得た。

比較例1で得られた素子は、キャリア濃度は5×1015cm-3を示したが、n値は10超であり満足なダイオード特性を示さなかった。また、絶縁破壊電界も0.1MV/cmに留まった。

SiCターゲットの替わりに、ターゲットとして単結晶GaNを用いてスパッタした他は、比較例1と同様にして多結晶GaNからなるショットキーバリアダイオードを作製し、評価した。結果を表2に示す。

比較例2で得られた素子は、n値が10超であり満足なダイオード特性を示さず、絶縁破壊電界も0.1MV/cmに留まった。

SiCターゲットの替わりに、ターゲットとしてIn2O3:Al2O3=20:80wt%の組成割合からなる酸化物材料を用い、半導体成膜後のアニールを150℃とした以外は、比較例1と同様にしてショットキーバリアダイオードを作製し、評価した。結果を表2に示す。

比較例3で得られた素子は、バンドギャップが5.8eV以上と非常に広いが、キャリア濃度は1013cm-3未満と非常に少なく、十分な順方向電流を得ることができなかった。

本願のパリ優先の基礎となる日本出願明細書の内容を全てここに援用する。

Claims (30)

- シリコン(Si)基板と、酸化物半導体層と、ショットキー電極層とを有するショットキーバリアダイオード素子であって、前記酸化物半導体層が、3.0eV以上、5.6eV以下のバンドギャップを有する多結晶及び/又は非晶質の酸化物半導体を含むショットキーバリアダイオード素子。

- 前記酸化物半導体が、In、Ti、Zn、Ga及びSnからなる群から選択される1種以上を含む請求項1記載のショットキーバリアダイオード素子。

- 前記酸化物半導体層がインジウム(In)を主成分として含む請求項1又は2に記載のショットキーバリアダイオード素子。

- 前記酸化物半導体層中に含まれる全金属元素に対するインジウムの原子組成百分率([In]/([In]+[In以外の全金属元素])×100)が30~100atm%である請求項1~3のいずれかに記載のショットキーバリアダイオード素子。

- 前記シリコン基板上に前記酸化物半導体層が形成され、前記酸化物半導体層上に前記ショットキー電極層が形成された請求項1~4のいずれかに記載のショットキーバリアダイオード素子。

- 前記シリコン基板上に前記ショットキー電極層が形成され、前記ショットキー電極層上に前記酸化物半導体層が形成された請求項1~4のいずれかに記載のショットキーバリアダイオード素子。

- 前記酸化物半導体層が、さらに、Al、Si、Zn、Ga、Hf、Zr、Ce、Sm、及びSnから選ばれる1種以上の元素を含む請求項2~6のいずれかに記載のショットキーバリアダイオード素子。

- 前記酸化物半導体層の室温におけるキャリア濃度が1×1014cm-3以上、1×1017cm-3以下である請求項1~7のいずれかに記載のショットキーバリアダイオード素子。

- 前記酸化物半導体層の端部が露出しないように絶縁膜により被覆されている請求項1~8のいずれかに記載のショットキーバリアダイオード素子。

- 請求項1~9のいずれかに記載のショットキーバリアダイオード素子を含む電気回路。

- 請求項1~9のいずれかに記載のショットキーバリアダイオード素子を含む電気機器。

- 請求項1~9のいずれかに記載のショットキーバリアダイオード素子を含む電子機器。

- 請求項1~9のいずれかに記載のショットキーバリアダイオード素子を含む車両。

- 酸化物半導体層と金属薄膜を含み、

前記酸化物半導体層が、3.0eV以上、5.6eV以下のバンドギャップを有する多結晶及び/又は非晶質の酸化物半導体を含み、

前記酸化物半導体層と前記金属薄膜とが電気的に接触する領域を含む

構造体。 - 前記酸化物半導体がInを主成分とする請求項14に記載の構造体。

- 前記金属薄膜の仕事関数が4.7eV以上である請求項14又は15に記載の構造体。

- 前記酸化物半導体が結晶質であり、

前記酸化物半導体中に、Al,Si,Ce、Ga、Hf、Zr及びSmから選ばれる少なくとも1種類の元素が全金属元素中3at%以上、30at%以下の割合で含まれている請求項14~16のいずれかに記載の構造体。 - 前記酸化物半導体の室温におけるキャリア濃度が1×1014cm-3以上、1×1017cm-3以下である請求項14~17のいずれかに記載の構造体。

- 前記酸化物半導体層の膜厚が50nm~20μmである請求項14~18のいずれかに記載の構造体。

- 請求項14~19のいずれかに記載の構造体が導電性基板上に積層してなる酸化物半導体基板。

- 前記導電性基板が単結晶シリコン、多結晶シリコン及び微結晶シリコンから選ばれる1以上から構成される請求項20に記載の酸化物半導体基板。

- 請求項14~19のいずれかに記載の構造体が電気絶縁性基板上に積層してなる酸化物半導体基板。

- 請求項20~22のいずれかに記載の酸化物半導体基板を用いたパワー半導体素子。

- 請求項20~22のいずれかに記載の酸化物半導体基板を用いたダイオード素子。

- 請求項20~22のいずれかに記載の酸化物半導体基板を用いたショットキーバリアダイオード素子。

- 前記金属薄膜をショットキー電極層とする請求項25に記載のショットキーバリアダイオード素子。

- 請求項23に記載のパワー半導体素子、請求項24に記載のダイオード素子、又は請求項25もしくは26に記載のショットキーバリアダイオード素子を含む電気回路。

- 請求項27に記載の電気回路を含む電気機器。

- 請求項27に記載の電気回路を含む電子機器。

- 請求項27に記載の電気回路を含む車両。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020167004121A KR102226985B1 (ko) | 2013-08-19 | 2014-08-08 | 산화물 반도체 기판 및 쇼트키 배리어 다이오드 |

| CN202010532733.5A CN111668315B (zh) | 2013-08-19 | 2014-08-08 | 氧化物半导体基板及肖特基势垒二极管元件 |

| JP2015532701A JPWO2015025499A1 (ja) | 2013-08-19 | 2014-08-08 | 酸化物半導体基板及びショットキーバリアダイオード |

| US14/912,815 US9691910B2 (en) | 2013-08-19 | 2014-08-08 | Oxide semiconductor substrate and schottky barrier diode |

| CN201480045490.5A CN105453272B (zh) | 2013-08-19 | 2014-08-08 | 氧化物半导体基板及肖特基势垒二极管元件 |

| US15/605,779 US11769840B2 (en) | 2013-08-19 | 2017-05-25 | Oxide semiconductor substrate and schottky barrier diode |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013169966 | 2013-08-19 | ||

| JP2013-169966 | 2013-08-19 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US14/912,815 A-371-Of-International US9691910B2 (en) | 2013-08-19 | 2014-08-08 | Oxide semiconductor substrate and schottky barrier diode |

| US15/605,779 Continuation US11769840B2 (en) | 2013-08-19 | 2017-05-25 | Oxide semiconductor substrate and schottky barrier diode |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2015025499A1 true WO2015025499A1 (ja) | 2015-02-26 |

Family

ID=52483294

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2014/004153 WO2015025499A1 (ja) | 2013-08-19 | 2014-08-08 | 酸化物半導体基板及びショットキーバリアダイオード |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US9691910B2 (ja) |

| JP (3) | JPWO2015025499A1 (ja) |

| KR (1) | KR102226985B1 (ja) |

| CN (2) | CN111668315B (ja) |

| TW (1) | TWI615984B (ja) |

| WO (1) | WO2015025499A1 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2017111174A1 (ja) * | 2015-12-25 | 2017-06-29 | 出光興産株式会社 | 積層体 |

| WO2017111173A1 (ja) * | 2015-12-25 | 2017-06-29 | 出光興産株式会社 | 積層体 |

| JP2017120878A (ja) * | 2015-12-25 | 2017-07-06 | 出光興産株式会社 | 半導体素子及びそれを用いた電気機器 |

| JP2017201659A (ja) * | 2016-05-02 | 2017-11-09 | ローム株式会社 | 電子部品およびその製造方法 |

| KR20190057318A (ko) | 2016-10-11 | 2019-05-28 | 이데미쓰 고산 가부시키가이샤 | 구조물, 그 제조 방법, 반도체 소자 및 전자 회로 |

| CN110870079A (zh) * | 2017-07-08 | 2020-03-06 | 株式会社Flosfia | 半导体装置 |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2017110940A1 (ja) * | 2015-12-25 | 2017-06-29 | 出光興産株式会社 | 半導体素子及びそれを用いた電気機器 |

| CN107039439B (zh) * | 2016-02-04 | 2020-03-10 | 中芯国际集成电路制造(上海)有限公司 | 存储器及其形成方法 |

| US20180097073A1 (en) * | 2016-10-03 | 2018-04-05 | Flosfia Inc. | Semiconductor device and semiconductor system including semiconductor device |

| JP2018137394A (ja) * | 2017-02-23 | 2018-08-30 | トヨタ自動車株式会社 | 半導体装置の製造方法 |

| JP6977465B2 (ja) * | 2017-10-06 | 2021-12-08 | 株式会社デンソー | 半導体装置の製造方法 |

| GB2569196B (en) | 2017-12-11 | 2022-04-20 | Pragmatic Printing Ltd | Schottky diode |

| DE102020132743A1 (de) * | 2019-12-13 | 2021-06-17 | Denso Corporation | Elektret |

| JP2022149875A (ja) | 2021-03-25 | 2022-10-07 | エヌ・ティ・ティ・コミュニケーションズ株式会社 | 医療システム及びコンピュータープログラム |

| CN117954504A (zh) * | 2022-10-19 | 2024-04-30 | 广州华瑞升阳投资有限公司 | 一种肖特基势垒二极管 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008021689A (ja) * | 2006-07-11 | 2008-01-31 | Fuji Electric Device Technology Co Ltd | 半導体装置 |

| WO2008096768A1 (ja) * | 2007-02-09 | 2008-08-14 | Idemitsu Kosan Co., Ltd. | 薄膜トランジスタの製造方法、薄膜トランジスタ、薄膜トランジスタ基板及び画像表示装置と、画像表示装置と、半導体デバイス |

| JP2009194225A (ja) * | 2008-02-15 | 2009-08-27 | Sumitomo Electric Ind Ltd | ショットキバリアダイオード、及びショットキバリアダイオードを作製する方法 |

| JP2012138552A (ja) * | 2010-12-28 | 2012-07-19 | Taiyo Yuden Co Ltd | ショットキーダイオードおよびその製造方法 |

Family Cites Families (64)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4358782A (en) * | 1980-01-17 | 1982-11-09 | Asahi Kasei Kogyo Kabushiki Kaisha | Semiconductor device |

| US4782302A (en) * | 1986-10-31 | 1988-11-01 | The United States Of America As Represented By The United States Department Of Energy | Detector and energy analyzer for energetic-hydrogen in beams and plasmas |

| JP2702279B2 (ja) * | 1990-11-30 | 1998-01-21 | 新コスモス電機株式会社 | ガス検知素子 |

| JPH0536975A (ja) | 1991-03-07 | 1993-02-12 | Sumitomo Metal Ind Ltd | シヨツトキーバリアダイオード素子 |

| JPH04302173A (ja) * | 1991-03-29 | 1992-10-26 | Japan Synthetic Rubber Co Ltd | 薄膜ダイオード |

| JPH0897441A (ja) | 1994-09-26 | 1996-04-12 | Fuji Electric Co Ltd | 炭化けい素ショットキーダイオードの製造方法 |

| US20020179957A1 (en) * | 2001-05-29 | 2002-12-05 | Motorola, Inc. | Structure and method for fabricating high Q varactor diodes |

| JP2004022878A (ja) | 2002-06-18 | 2004-01-22 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| JP2005072367A (ja) * | 2003-08-26 | 2005-03-17 | Nippon Oil Corp | 光電変換素子 |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| CN101057339B (zh) * | 2004-11-10 | 2012-12-26 | 佳能株式会社 | 无定形氧化物和场效应晶体管 |

| JP5053537B2 (ja) * | 2004-11-10 | 2012-10-17 | キヤノン株式会社 | 非晶質酸化物を利用した半導体デバイス |

| US20090090914A1 (en) * | 2005-11-18 | 2009-04-09 | Koki Yano | Semiconductor thin film, method for producing the same, and thin film transistor |

| KR100723420B1 (ko) * | 2006-02-20 | 2007-05-30 | 삼성전자주식회사 | 비정질 합금 산화층을 포함하는 비휘발성 메모리 소자 |

| JP2007243080A (ja) * | 2006-03-13 | 2007-09-20 | Fuji Electric Holdings Co Ltd | 半導体装置およびその製造方法 |

| US7389675B1 (en) * | 2006-05-12 | 2008-06-24 | The United States Of America As Represented By The National Aeronautics And Space Administration | Miniaturized metal (metal alloy)/ PdOx/SiC hydrogen and hydrocarbon gas sensors |

| JP5164357B2 (ja) * | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP5261923B2 (ja) * | 2006-10-17 | 2013-08-14 | サンケン電気株式会社 | 化合物半導体素子 |

| JP4362635B2 (ja) * | 2007-02-02 | 2009-11-11 | ローム株式会社 | ZnO系半導体素子 |

| US8748879B2 (en) | 2007-05-08 | 2014-06-10 | Idemitsu Kosan Co., Ltd. | Semiconductor device, thin film transistor and a method for producing the same |

| JPWO2009034953A1 (ja) * | 2007-09-10 | 2010-12-24 | 出光興産株式会社 | 薄膜トランジスタ |

| JP2009164237A (ja) | 2007-12-28 | 2009-07-23 | Panasonic Corp | ショットキーバリアダイオード |

| US8076699B2 (en) * | 2008-04-02 | 2011-12-13 | The Hong Kong Univ. Of Science And Technology | Integrated HEMT and lateral field-effect rectifier combinations, methods, and systems |

| JP5382763B2 (ja) | 2008-04-09 | 2014-01-08 | 独立行政法人産業技術総合研究所 | 半導体素子及びその製造方法と、該半導体素子を備えた電子デバイス |

| JP5198146B2 (ja) * | 2008-05-22 | 2013-05-15 | 株式会社東芝 | 不揮発性記憶装置 |

| JP2010040552A (ja) * | 2008-07-31 | 2010-02-18 | Idemitsu Kosan Co Ltd | 薄膜トランジスタ及びその製造方法 |

| JP4803241B2 (ja) * | 2008-11-27 | 2011-10-26 | 三菱電機株式会社 | 半導体モジュール |

| JP5606682B2 (ja) * | 2009-01-29 | 2014-10-15 | 富士フイルム株式会社 | 薄膜トランジスタ、多結晶酸化物半導体薄膜の製造方法、及び薄膜トランジスタの製造方法 |

| JP2010182852A (ja) * | 2009-02-05 | 2010-08-19 | Konica Minolta Holdings Inc | 金属酸化物半導体、その製造方法及び薄膜トランジスタ |

| US20100224878A1 (en) * | 2009-03-05 | 2010-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8461582B2 (en) * | 2009-03-05 | 2013-06-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP5453867B2 (ja) * | 2009-03-24 | 2014-03-26 | 株式会社デンソー | ショットキーバリアダイオードを備えた炭化珪素半導体装置およびその製造方法 |

| US8441047B2 (en) | 2009-04-10 | 2013-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| WO2010147073A1 (ja) | 2009-06-15 | 2010-12-23 | 株式会社村田製作所 | 抵抗スイッチング・メモリー素子 |

| JP2011029238A (ja) * | 2009-07-21 | 2011-02-10 | Fujifilm Corp | 結晶性ホモロガス化合物層を含む積層体の製造方法及び電界効果型トランジスタ |

| WO2011052437A1 (en) * | 2009-10-30 | 2011-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Non-linear element, display device including non-linear element, and electronic device including display device |

| WO2011065210A1 (en) * | 2009-11-28 | 2011-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Stacked oxide material, semiconductor device, and method for manufacturing the semiconductor device |

| CN104992962B (zh) * | 2009-12-04 | 2018-12-25 | 株式会社半导体能源研究所 | 半导体器件及其制造方法 |

| KR101636998B1 (ko) * | 2010-02-12 | 2016-07-08 | 삼성디스플레이 주식회사 | 박막 트랜지스터 및 그 제조 방법 |

| CN105336744B (zh) * | 2010-02-12 | 2018-12-21 | 株式会社半导体能源研究所 | 半导体装置及其驱动方法 |

| US8835917B2 (en) | 2010-09-13 | 2014-09-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, power diode, and rectifier |

| JP5780902B2 (ja) * | 2010-10-12 | 2015-09-16 | 出光興産株式会社 | 半導体薄膜、薄膜トランジスタ及びその製造方法 |

| US20130320326A1 (en) * | 2011-02-18 | 2013-12-05 | Idemitsu Kosan Co., Ltd. | Insulating material forming composition for electronic devices, insulating material for electronic devices, electronic devices and thin film transistor |

| JP5800291B2 (ja) * | 2011-04-13 | 2015-10-28 | ローム株式会社 | ZnO系半導体素子およびその製造方法 |

| US8546879B2 (en) * | 2011-08-18 | 2013-10-01 | Monolithic Power Systems, Inc. | High density lateral DMOS with recessed source contact |

| JP5894393B2 (ja) * | 2011-08-19 | 2016-03-30 | 出光興産株式会社 | 酸化物粒子分散液 |

| JP5866727B2 (ja) * | 2011-09-08 | 2016-02-17 | 株式会社タムラ製作所 | β−Ga2O3単結晶膜の製造方法及び結晶積層構造体 |

| US8902082B2 (en) | 2011-10-11 | 2014-12-02 | Bruce B. Roesner | Communicating statuses of vehicles |

| CN102332474A (zh) * | 2011-10-18 | 2012-01-25 | 北京工业大学 | 一种铟镓锌氧化物肖特基二极管器件及其制备方法 |

| JP2013102081A (ja) * | 2011-11-09 | 2013-05-23 | Tamura Seisakusho Co Ltd | ショットキーバリアダイオード |

| JP5984505B2 (ja) * | 2012-05-22 | 2016-09-06 | 株式会社日立製作所 | 半導体ガスセンサおよびその製造方法 |

| CN103426910B (zh) * | 2012-05-24 | 2016-01-20 | 杰力科技股份有限公司 | 功率半导体元件及其边缘终端结构 |

| US8952470B2 (en) * | 2012-09-10 | 2015-02-10 | James John Lupino | Low cost high density nonvolatile memory array device employing thin film transistors and back to back Schottky diodes |

| JP5777586B2 (ja) * | 2012-09-20 | 2015-09-09 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP6071569B2 (ja) * | 2013-01-17 | 2017-02-01 | キヤノン株式会社 | 有機発光素子 |

| JP6222931B2 (ja) * | 2013-01-21 | 2017-11-01 | キヤノン株式会社 | 有機発光素子 |

| JP6581765B2 (ja) * | 2013-10-02 | 2019-09-25 | 株式会社半導体エネルギー研究所 | ブートストラップ回路、およびブートストラップ回路を有する半導体装置 |

| US9300292B2 (en) * | 2014-01-10 | 2016-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Circuit including transistor |

| JP6541360B2 (ja) * | 2014-02-07 | 2019-07-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9842842B2 (en) * | 2014-03-19 | 2017-12-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor memory device and semiconductor device and electronic device having the same |

| JP6587497B2 (ja) * | 2014-10-31 | 2019-10-09 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI688211B (zh) * | 2015-01-29 | 2020-03-11 | 日商半導體能源研究所股份有限公司 | 半導體裝置、電子組件及電子裝置 |

| WO2016128853A1 (en) * | 2015-02-09 | 2016-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic component, and electronic device |

| US9489988B2 (en) * | 2015-02-20 | 2016-11-08 | Semiconductor Energy Laboratory Co., Ltd. | Memory device |

-

2014

- 2014-08-08 KR KR1020167004121A patent/KR102226985B1/ko active IP Right Grant

- 2014-08-08 JP JP2015532701A patent/JPWO2015025499A1/ja active Pending

- 2014-08-08 US US14/912,815 patent/US9691910B2/en active Active

- 2014-08-08 WO PCT/JP2014/004153 patent/WO2015025499A1/ja active Application Filing

- 2014-08-08 CN CN202010532733.5A patent/CN111668315B/zh active Active

- 2014-08-08 CN CN201480045490.5A patent/CN105453272B/zh active Active

- 2014-08-15 TW TW103128165A patent/TWI615984B/zh active

-

2017

- 2017-05-25 US US15/605,779 patent/US11769840B2/en active Active

-

2019

- 2019-02-22 JP JP2019031008A patent/JP6989545B2/ja active Active

-

2020

- 2020-12-15 JP JP2020207470A patent/JP7084465B2/ja active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008021689A (ja) * | 2006-07-11 | 2008-01-31 | Fuji Electric Device Technology Co Ltd | 半導体装置 |

| WO2008096768A1 (ja) * | 2007-02-09 | 2008-08-14 | Idemitsu Kosan Co., Ltd. | 薄膜トランジスタの製造方法、薄膜トランジスタ、薄膜トランジスタ基板及び画像表示装置と、画像表示装置と、半導体デバイス |

| JP2009194225A (ja) * | 2008-02-15 | 2009-08-27 | Sumitomo Electric Ind Ltd | ショットキバリアダイオード、及びショットキバリアダイオードを作製する方法 |

| JP2012138552A (ja) * | 2010-12-28 | 2012-07-19 | Taiyo Yuden Co Ltd | ショットキーダイオードおよびその製造方法 |

Cited By (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021010031A (ja) * | 2015-12-25 | 2021-01-28 | 出光興産株式会社 | 半導体素子及びそれを用いた電気機器 |

| JP2017120878A (ja) * | 2015-12-25 | 2017-07-06 | 出光興産株式会社 | 半導体素子及びそれを用いた電気機器 |