KR100854162B1 - 반도체 장치 및 그 제조 방법 - Google Patents

반도체 장치 및 그 제조 방법 Download PDFInfo

- Publication number

- KR100854162B1 KR100854162B1 KR1020070071083A KR20070071083A KR100854162B1 KR 100854162 B1 KR100854162 B1 KR 100854162B1 KR 1020070071083 A KR1020070071083 A KR 1020070071083A KR 20070071083 A KR20070071083 A KR 20070071083A KR 100854162 B1 KR100854162 B1 KR 100854162B1

- Authority

- KR

- South Korea

- Prior art keywords

- hard mask

- film

- mask

- etching

- sidewall

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0334—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/0337—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/266—Bombardment with radiation with high-energy radiation producing ion implantation using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32139—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/105—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including field-effect components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- High Energy & Nuclear Physics (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Drying Of Semiconductors (AREA)

- Semiconductor Memories (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

Abstract

피에칭 부재인 폴리실리콘막 상에 제1 하드 마스크가 형성되고, 이 위에 아몰퍼스 실리콘으로 이루어지는 제2 하드 마스크가 더 형성된다. 제2 하드 마스크의 원하는 일부에 붕소 등의 이온 주입을 행한 후, 제2 하드 마스크를 마스크로 하여 제1 하드 마스크를 에칭한다. 웨트 에칭에 의해 제2 하드 마스크의 이온 주입되지 않은 부분을 에칭 제거한다. 제1 하드 마스크의 측벽에 측벽막을 형성한 후, 제2 하드 마스크에 덮이지 않아 상부가 노출되어 있는 제1 하드 마스크를 선택적으로 에칭 제거한다.

폴리실리콘막, 하드 마스크, 측벽막, 웨트 에칭, 이온 주입

Description

<관련 출원>

본 출원은 2006년 7월 18일 출원된 일본 특허 출원 번호 제2006-195757호에 기초한 것으로 그 우선권을 주장하며, 그 전체 내용이 참조로서 본 명세서에 원용된다.

본 발명은, 반도체 장치 및 그 제조 방법에 관한 것으로, 특히, 소위 측벽 전사 프로세스를 이용하여 피에칭 부재를 에칭하는 반도체 장치 및 그 제조 방법에 관한 것이다.

반도체 제조 프로세스에서 배선 패턴(라인 앤드 스페이스)을 형성하는 경우, 포토리소그래피 마스크를 이용하여 레지스트를 현상함으로써 레지스트에 패턴을 전사한 후, 이것을 마스크로 하여 피에칭재를 에칭하여 에칭 처리를 행하는 것이 일반적이다.

반도체 장치의 미세화의 요구에 의해, 리소그래피의 해상 한계 이하의 배선 패턴의 형성이 필요해져 오고 있는데, 이것을 실현하는 방법으로서, 소위 레지스트 슬리밍 방법이 알려져 있다(예를 들면, 일본 특개2001-265011호 공보(단락0008, 도 6 등) 참조). 이 방법은, 레지스트의 현상 후, 레지스트, 또는 레지스트를 마스크로 하여 에칭된 희생막 등에 등방성 에칭을 실시함으로써, 리소그래피의 해상 한계 이하의 패턴을 형성하는 것이다.

다른 방법으로서, 소위 측벽 전사 프로세스가 알려져 있다. 이 방법은, 배선 재료 상에 하드 마스크 또한 레지스트를 형성한 후 레지스트 슬리밍을 실시하고, 그 후 하드 마스크를 레지스트 마스크로 하여 에칭한다. 레지스트를 박리한 후, 하드 마스크 측벽에 측벽막으로 되는 박막을 퇴적시키고, 이방성 에칭 등을 이용함으로써 하드 마스크 측벽에 측벽막을 형성한다. 그리고, 이방성 에칭 혹은 등방성 에칭으로부터 선택적으로 하드 마스크만을 제거하고 측벽막은 남기도록 한다. 그리고, 이 측벽막을 마스크로 하여 배선 재료를 가공한다. 이 방법에 따르면, 리소그래피의 해상 한계의 제한을 받는 하드 마스크의 치수보다도 작은 폭을 갖는 라인 앤드 스페이스를 형성하는 것이 가능하게 된다.

그러나, 이 측벽 전사 프로세스에서는, 모두 측벽막으로 형성된 배선 패턴으로 되기 때문에, 임의의 치수의 배선이나, 컨택트를 취하기 위하여 배선 도중에서 넓어진 패턴 등을 용이하게 형성할 수 없다. 예를 들면, NAND형 플래시 메모리 등을 예로 들면, 메모리 셀 어레이에서는 리소그래피의 해상 한계 이하의 미세한 배선 패턴을 형성하고, 주변 회로 등에서는 리소그래피의 해상도에 따른 통상의 배선 패턴을 형성하는 것이 요구된다. 따라서, 측벽 전사 프로세스에 의해 미세 패턴을 형성하는 영역과, 레지스트 패턴을 따른 전사를 행하는 영역에서, 별개의 리소그래피를 실행할 필요가 생긴다. 예를 들면 미국 특허 제6475891호 공보에서는, 임의의 치수의 배선이나 컨택트를 취하기 위한 방법을 개시하고 있는데, 이 방법으로는, 그러한 배선을 별도로 독립된 포토리소그래피에 의해 형성하기 때문에, 공정수가 증가하여 제조 코스트의 증가를 초래할 우려가 있음과 함께, 그러한 별도로 독립된 포토리소그래피의 위치 정렬도 곤란하다고 하는 문제가 있다. 이와 같이, 리소그래피의 해상 한계 이하의 배선 패턴과, 그 이외의 임의의 치수의 배선 패턴 혹은 컨택트를 간이하게 형성할 방법이 없어, 제조 코스트의 증가 등의 문제를 초래하였다.

본 발명의 일 양태에 따른 반도체 장치의 제조 방법은, 피에칭 부재 상에 제1 하드 마스크를 형성하는 공정과, 상기 제1 하드 마스크 상에 제2 하드 마스크를 형성하는 공정과, 상기 제2 하드 마스크의 일부에 이온 주입을 행하고 이온 주입이 되지 않은 부분과의 비교에서 웨트 에칭에 대한 에칭 레이트를 변화시키기 위한 개질을 행하는 공정과, 상기 제2 하드 마스크를 마스크로 하여 상기 제1 하드 마스크를 에칭하는 공정과, 웨트 에칭에 의해 이온 주입되지 않은 상기 제2 하드 마스크만 선택적으로 에칭 제거하는 공정과, 상기 제1 하드 마스크의 측벽에 측벽막을 형성하는 공정과, 상기 제2 하드 마스크에 덮이지 않아 상부가 노출되어 있는 제1 하드 마스크를 선택적으로 에칭 제거하는 공정과, 상기 측벽막 및 상기 제1 하드 마 스크를 마스크로 하여 상기 피에칭 부재를 에칭 제거하는 공정을 구비한 것을 특징으로 한다.

또한, 본 발명의 다른 일 양태에 따른 반도체 장치의 제조 방법은, 피에칭 부재 상에 제1 하드 마스크를 형성하는 공정과, 상기 제1 하드 마스크 상에 제2 하드 마스크를 형성하는 공정과, 상기 제2 하드 마스크의 일부에 이온 주입을 행하고 이온 주입이 되지 않은 부분과의 비교에서 웨트 에칭에 대한 에칭 레이트를 변화시키기 위한 개질을 행하는 공정과, 상기 제2 하드 마스크의 측벽에 측벽막을 형성하는 공정과, 웨트 에칭에 의해 이온 주입되지 않은 상기 제2 하드 마스크만 선택적으로 에칭 제거하는 공정과, 상기 제2 하드 마스크 및 상기 측벽막을 마스크로 하여 상기 제1 하드 마스크를 에칭하는 공정과, 상기 제1 하드 마스크를 마스크로 하여 상기 피에칭 부재를 에칭 제거하는 공정을 구비한 것을 특징으로 한다.

또한, 본 발명의 일 양태에 따른 반도체 장치는, 하드 마스크의 측벽을 따른 폐 루프 형상의 측벽막을 형성함과 함께, 마스크를 이용하여 상기 하드 마스크의 일부에 대하여 이온 주입을 행한 후 상기 일부를 제외한 상기 하드 마스크를 에칭 제거하고, 상기 일부 및 상기 측벽막을 마스크로 하여 피에칭 부재를 에칭하여 이루어지는 배선층을 구비하고, 상기 배선층은, 상기 일부 및 상기 측벽막에 유래하여 형성되는 광폭부와, 상기 측벽막에만 유래하여 형성되는 배선부를 갖고, 상기 배선부는, 그 윤곽의 변동의 크기가, 상기 폭의 변동의 크기보다도 크고, 상기 광폭부의 윤곽과, 상기 배선부의 윤곽은, 그 상기 폐 루프 형상의 내주에서, 수직 또는 둔각으로 교차하고, 상기 배선부의 상기 폐 루프 형상에 따른 외주는, 상기 일 부의 경계 부근도 포함하여 동일 직선 형상으로 형성되어 있는 것을 특징으로 한다.

이와 같이, 본 발명에 따르면, 아몰퍼스 실리콘으로 이루어지는 제2 하드 마스크의 원하는 일부에 붕소 등의 불순물 이온이 이온 주입됨으로써, 리소그래피의 해상 한계 이하의 배선 패턴과, 그 이외의 임의의 폭의 배선 패턴을, 동일한 리소그래피에 의해 형성 가능하여, 종래에 비하면 현저히 리소그래피의 난이도를 저감할 수 있다.

다음으로, 본 발명의 실시 형태를, 도면을 참조하여 상세하게 설명한다.

구체적인 실시 형태의 설명에 앞서, 본 발명의 실시 형태의 개념을 도 26∼도 35의 공정도를 참조하여 설명한다. 일례로서, 반도체 기판(10) 상에 실리콘 산화막(20)을 개재하여 형성된 폴리실리콘막(25)을 피에칭 부재로서 에칭하는 것으로 한다. 그리고, 영역1(도 26)에서는, 측벽 전사 프로세스를 이용하여 리소그래피의 해상 한계 이하의 배선 패턴을 폴리실리콘막(25)에 의해 형성하고, 영역2에서는, 그 이외의 임의의 폭의 배선 패턴을 동시에 폴리실리콘막(25)에 의해 형성하는 것으로 한다.

우선, 도 26에 도시한 바와 같이, 피에칭 부재로서의 폴리실리콘막(25) 상에, 이것을 에칭하기 위하여 이용하는 제1 하드 마스크(30)를 퇴적한다. 이 제1 하드 마스크(30) 상에, 아몰퍼스 실리콘이나 폴리실리콘 등, 이온 주입에 의해 웨 트 에칭에 대한 에칭 레이트가 변화되는 성질을 갖는 재료로 이루어지는 제2 하드 마스크(40)가 더 형성된다. 이 제2 하드 마스크(40)는, 제1 하드 마스크(30)를 원하는 패턴으로 에칭하기 위해 형성되는 것이다.

다음에 도 27에 도시한 바와 같이, 이 제2 하드 마스크(40)의 전체면에 레지스트를 도포한 후, 포토리소그래피법에 의해, 원하는 패턴으로 레지스트를 현상하여, 원하는 패턴 형상을 갖는 레지스트(50)를 형성한다. 일례로서, 영역1에서는 레지스트(50)는 리소그래피의 해상 한계인 최소 선폭 W의 라인 앤드 스페이스를 갖고, 라인과 스페이스의 간격 W는 거의 동일한 것으로 한다.

계속하여 도 28에 도시한 바와 같이, 등방성 에칭에 의해, 이 레지스트(50)를 슬리밍 처리하여, 포토리소그래피의 해상 한계 이하의 폭까지 레지스트(50)를 세화시킨다. 계속하여 도 29에 도시한 바와 같이, 슬리밍 처리된 레지스트(50)를 마스크로 한 이방성 에칭에 의해, 제2 하드 마스크(40)를 에칭한다. 에칭 후에는, 레지스트(50)는 박리된다.

그리고, 도 30에 도시한 바와 같이, 제2 하드 마스크(40) 중 측벽 전사 프로세스에 의해 리소그래피의 해상 한계 이하의 라인 앤드 스페이스 패턴을 형성하고자 하는 영역(여기서는 영역1로 함)에만 레지스트(60)를 형성하고, 이 레지스트(60)를 마스크로 하여 불순물 이온(붕소(B), 인(P), 비소(As) 또는 이불화 붕소(BF2)가 바람직함)을 제2 하드 마스크(4O)에 주입한다. 이에 의해, 레지스트(60)에 의해 덮이지 않고 이온 주입을 받은 제2 하드 마스크(40B)는, 레지스트(60)에 의해 덮이어 이온 주입을 받지 않은 제2 하드 마스크(40)에 비하여 알칼리계 용액을 이용한 웨트 에칭에 대한 에칭 레이트가 작은 것으로 된다.

계속해서, 이 레지스트(60)를 박리한 후, 도 31에 도시한 바와 같이, 제2 하드 마스크(40, 40B)를 마스크로 한 이방성 에칭에 의해, 제1 하드 마스크(30)를 에칭한다. 그 후, 도 32에 도시한 바와 같이, 알칼리계 용액을 이용한 웨트 에칭에 의해, 이온 주입이 되지 않은 제2 하드 마스크(40)를 선택적으로 제거하고, 이온 주입으로 된 제2 하드 마스크(40B)는 잔존시킨다.

그 후, 제1 하드 마스크(30)의 상면, 측벽도 포함시킨 전체면에, 측벽 재료막을 CVD법 등에 의해 퇴적시킨다. 그 후 이방성 에칭에 의해, 제1 하드 마스크(30) 및 잔존한 제2 하드 마스크(40B)의 측벽에만 측벽 재료막이 남도록 에칭하고, 이 잔존된 막이 도 33에 도시한 바와 같이 측벽막(70)으로 된다. 계속해서, 도 34에 도시한 바와 같이, 웨트 에칭을 이용하여, 영역1에서 측벽막(70)의 사이에 끼워져 있고 상부가 노출된 제1 하드 마스크(30)를 에칭 제거한다. 한편, 영역2에서 제2 하드 마스크(40B)에 의해 덮인 제1 하드 마스크(30)는 에칭되지 않고 잔존한다. 이에 의해, 영역1에서는, 측벽막(70)만이 잔존한다. 도 35에 도시한 바와 같이, 이 측벽막(70)을 마스크로 한 에칭에 의해 피에칭 부재로서의 폴리실리콘막(25)이 에칭되어, 리소그래피의 해상 한계 이하의 배선 패턴이 영역1에 형성된다. 한편, 영역2에서는, 제1 하드 마스크(30)가 에칭되지 않고 잔존되어, 이것이 측벽막(70)과 함께 에칭 마스크로 된다. 따라서, 영역2에서는 임의의 폭의 배선 패턴 및 컨택트 프린지 영역을 메모리 셀 어레이 영역에서의 측벽 전사 프로세스에 의한 배선 패턴(리소그래피의 해상 한계 이하의 배선 패턴)과 동일한 공정에서 형성할 수 있다.

[제1 실시 형태]

본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법을, 도 1a∼도 6b를 참조하여 설명한다. 이하의 예에서는, 반도체 기판(10) 상에 실리콘 산화막(20)을 개재하여 형성된 폴리실리콘막(25)을 피에칭 부재로 하여 에칭하는 것으로 한다. 그리고, 메모리 셀 어레이 영역에서는 측벽 전사 프로세스를 이용하여 리소그래피의 해상 한계 이하의 배선 패턴을 폴리실리콘막(25)에 의해 형성하고, 주변 회로 부분에는, 그 이외의 임의의 폭의 배선 패턴 또는 컨택트 프린지 영역을 동시에 폴리실리콘막(25)에 의해 형성하는 것으로 한다.

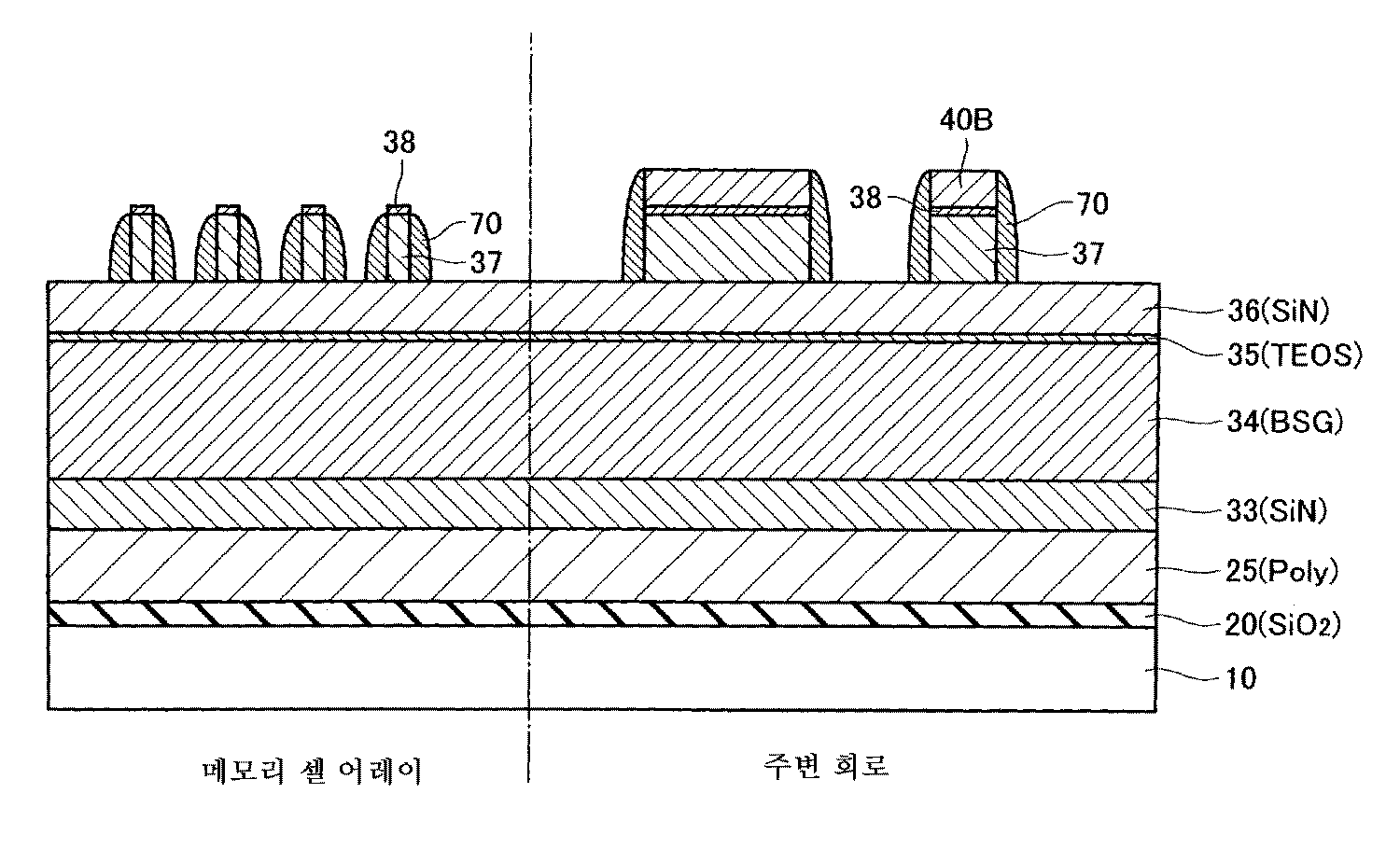

우선, 도 1a에 도시한 바와 같이, 피에칭 부재로서의 폴리실리콘막(25) 상에, 이것을 에칭하기 위하여 이용하는 제1 하드 마스크(30)를 퇴적한다. 제1 하드 마스크(30)는, 이 예에서는, 아래부터 순서대로 실리콘 질화막(SiN)(33), BSG막(34), TEOS막(35), 실리콘 질화막(36), BSG막(37), TEOS막(38)을 퇴적함으로써 형성되는 것으로 한다. 이것은 어디까지나 일례이며, 에칭 조건이나 마스크 재료 등을 고려하여, 다양한 형식(층수, 각 층의 두께, 재료 등)의 것이 이용될 수 있다.

제1 하드 마스크(30) 중,BSG막(37), TEOS막(38)은, 후술하는 바와 같이, 측벽막을 형성하기 위한 측벽 형성막으로서 기능하는 것이다. 이 제1 하드 마스크(30) 상에, 아몰퍼스 실리콘으로 이루어지는 제2 하드 마스크(40)가 더 형성된 다. 이 제2 하드 마스크(40)는, BSG막(37) 및 TEOS막(38)(측벽 형성막)을 포함하는 제1 하드 마스크(30)를 원하는 패턴으로 에칭하기 위해 형성되는 것이다. 측벽 형성막은, 여기에서는 BSG막(37) 및 TEOS막(38)으로 했지만, 본 발명은 이것에 한정되는 것은 아니며, 동일한 효과가 얻어지는 범위에서 여러가지로 변경이 가능하다. 또한, 제2 하드 마스크(40)로서는, 아몰퍼스 실리콘 대신에, 폴리실리콘 등 이온 주입에 의해 웨트 에칭에 대한 에칭 레이트가 변화되는 성질을 갖는 재료에 의해 측벽막(70)을 형성하는 것도 가능하며, 이것은, 이후의 실시 형태에서 마찬가지이다.

다음에 도 1b에 도시한 바와 같이, 이 제2 하드 마스크(40)의 전체면에 반사 방지막(도시하지 않음)과 레지스트를 도포한 후, 포토리소그래피법에 의해, 원하는 패턴으로 레지스트를 현상하여, 원하는 패턴 형상을 갖는 레지스트(50)를 형성한다. 이 예에서는, 메모리 셀 어레이 영역에서는 레지스트(50)는 최소 선폭 W의 라인 앤드 스페이스를 갖고, 라인과 스페이스의 간격 W는 거의 동일한 것으로 한다.

계속해서 도 1c에 도시한 바와 같이, 등방성 에칭에 의해, 도시하지 않은 반사 방지막을 에칭함과 동시에 레지스트(50)를 슬리밍 처리하여, 포토리소그래피의 해상 한계 이하의 폭까지 레지스트(50)를 세화시킨다. 여기에서는 예를 들면, 메모리 셀 어레이 부분에서의 라인 폭이 1/2W, 스페이스 폭이 3/2W로 되도록 한다. 또한, 주변 회로 부분에서의 레지스트(50)의 치수도 세화된다. 계속하여 도 1d에 도시한 바와 같이, 슬리밍 처리된 레지스트(50)를 마스크로 한 이방성 에칭에 의해, 제2 하드 마스크(40)를 에칭한다. 에칭 후에는, 레지스트(50)는 박리된다.

그리고, 도 2a에 도시한 바와 같이, 제2 하드 마스크(40) 중 측벽 전사 프로세스에 의해 리소그래피의 해상 한계 이하의 라인 앤드 스페이스 패턴을 형성하고자 하는 영역(여기서는 메모리 셀 어레이의 부분)에만 레지스트(60)를 형성하고, 이 레지스트(60)를 마스크로 하여 불순물 이온(붕소(B), 인(P), 비소(As) 또는 이불화 붕소(BF2)가 바람직함)을 제2 하드 마스크(40)에 주입한다. 일례로서, 이온 주입이 되는 하드 마스크(40B)에서의 불순물 농도가 1×1020㎝-3로 되도록 이온 주입 조건을 조정한다. 이에 의해, 레지스트(60)에 의해 덮이지 않고 이온 주입을 받은 제2 하드 마스크(40B)는, 레지스트(60)에 의해 덮이어 이온 주입을 받지 않은 제2 하드 마스크(40)에 비교하여, 알칼리계 용액을 이용한 웨트 에칭에 대한 에칭 레이트가 낮은 것으로 된다.

계속해서, 이 레지스트(60)를 박리한 후, 도 2b에 도시한 바와 같이, 제2 하드 마스크(40, 40B)를 마스크로 한 이방성 에칭에 의해, 제1 하드 마스크(30) 중, 측벽 형성막으로 되는 TEOS막(38) 및 BSG막(37)을 에칭한다. 그 후, 도 2c에 도시한 바와 같이, 알칼리계 용액을 이용한 웨트 에칭에 의해, 이온 주입이 되지 않은 제2 하드 마스크(40)를 선택적으로 제거하고, 이온 주입이 된 제2 하드 마스크(40B)는 잔존시킨다. 알칼리계 용액에 의한 웨트 에칭에서는, 산화막, 질화막에 대한 선택비도 높기 때문에, 측벽 형성재인 TEOS막(38), 및 BSG막(37), 및 기초층의 실리콘 질화막(36)에는 아무런 악영향을 끼치지 않는다. 이 방법에 의해, 메모리 셀 어레이의 제2 하드 마스크(40)만을 용이하게 또한, 다른 것에의 부작용을 생 기게 하지 않고 제거할 수 있다.

그 후, 제1 하드 마스크(30) 상의 전체면에, 에칭된 TEOS막(38) 및 BSG막(37)의 측벽, 및 제2 하드 마스크(40B)의 상면도 포함하여, 아몰퍼스 실리콘막을 CVD법에 의해 퇴적시킨다. 그 후 이방성 에칭에 의해, TEOS막(38) 및 BSG막(37)의 측벽, 제2 하드 마스크(40B)의 측벽에만 아몰퍼스 실리콘막이 남도록 에칭하여, 이 잔존된 막이 도 3에 도시한 바와 같이 측벽막(70)(아몰퍼스 실리콘막)으로 된다. 측벽막(70)은, 주변 회로 영역에서,TEOS막(38) 및 BSG막(37)이 다음 공정(도 4)에서 에칭되는 것을 방지하기 위해, 제2 하드 마스크(40B)의 측벽에까지 도달해 있는 것이 바람직하다.

메모리 셀 어레이 영역에서 TEOS막(38) 및 BSG막(37)은 해상 한계에 따르는 최소 선폭 W의 절반인 1/2W 정도의 폭으로 에칭되고 있다. 따라서 여기에서는, 측벽막(70)의 폭이 1/2W 정도로 되도록, 아몰퍼스 실리콘의 퇴적 두께, 에칭 조건 등을 설정한다.

계속해서, 도 4에 도시한 바와 같이, 희불산 등의 웨트 에칭을 이용하여, 메모리 셀 어레이 영역에서 측벽막(70)의 사이에 끼워져 있고 상부가 노출된 TEOS막(38) 및 BSG막(37)을 에칭 제거한다. 한편, 주변 회로 영역에서 제2 하드 마스크(40B)에 의해 덮인 TEOS막(38) 및 BSG막(37)은 에칭되지 않고 잔존한다. 이에 의해, 메모리 셀 어레이 영역에서는,1/2W의 폭의 측벽막(70)만이 스페이스 폭 1/2W로 실리콘 질화막(36) 상에 잔존한다. 이와 같은 측벽막(70)만을 마스크로 한 에칭에 의해, 라인 폭 1/2W, 스페이스 폭 1/2W의 리소그래피의 해상 한계 이하의 배선 패턴이 메모리 셀 어레이 영역에 형성된다. 한편, 주변 회로 영역에서는, 제2 하드 마스크(40B) 및 측벽막(70)에 의해 덮인 TEOS막(38) 및 BSG막(37)이 에칭되지 않고 잔존되고, 이것이 측벽막(70)과 함께 에칭 마스크로 된다. 따라서, 레지스트(50)(도 1c)에서 임의의 폭을 설정함으로써, 주변 회로 영역에서는 임의의 폭의 배선 패턴 및 컨택트 프린지 영역을 메모리 셀 어레이 영역에서의 측벽 전사 프로세스에 의한 배선 패턴(리소그래피의 해상 한계 이하의 배선 패턴)과 동일한 공정에서 형성할 수 있다.

그 후, 도 5a에 도시한 바와 같이, 아몰퍼스 실리콘으로 이루어지는 측벽막(70), 및 마찬가지로 아몰퍼스 실리콘으로 이루어지는 제2 하드 마스크(40B)를 마스크로 한 이방성 에칭에 의해, 실리콘 질화막(36)을 에칭한다. 이 때 제2 하드 마스크(40B)도 에칭 제거되어 없어지는 막 두께로 제2 하드 마스크(40B)를 설정해 두는 것이 바람직하다.

또한 측벽막(70)을 마스크로 하여 에칭을 계속하고, 도 5b에 도시한 바와 같이 TEOS막(35) 및 BSG막(34)의 에칭을 행한다. 주변 회로 영역에서는, 제2 하드 마스크(40B)가 제거된 기초층의 TEOS막(38), BSG막(37) 및 실리콘 질화막(36)도 에칭되지만, 완전하게 실리콘 질화막(36)이 에칭되지 않는 막 두께 설정 및 에칭 조건의 설정을 행해 두는 것이 바람직하다.

계속해서, 도 5c에 도시한 바와 같이, 피에칭 부재인 폴리실리콘막(25) 상의 실리콘 질화막(33)을 에칭한다. 이 시점에서는, 적어도 주변 회로 영역에서 제1 하드 마스크(30)로서 남아 있는 막은, 실리콘 질화막(33), BSG막(34), 및 TEOS 막(35)뿐이다. 단,TEOS막(35)이 제거되고, BSG막(34)만이 실리콘 질화막(33) 상에 잔존하도록 에칭 조건 등을 선정하는 것이 바람직하다.

다음으로, 도 6a에 도시한 바와 같이, BSG막(34)을 마스크로 피에칭 부재인 폴리실리콘막(25)을 에칭하고, 또한 도 6b에 도시한 바와 같이, 불산 베이퍼 처리등 실리콘 산화막(20)에 대하여 선택비가 높은 조건에서 BSG막(34)만 제거한다. 이에 의해, 실리콘 질화막(33)을 캡층으로 한 폴리실리콘막(25)이 형성된다.

이와 같이, 본 실시 형태에 따르면, 아몰퍼스 실리콘으로 이루어지는 제2 하드 마스크(40)의 원하는 일부에 붕소 등의 불순물 이온이 이온 주입됨으로써, 리소그래피의 해상 한계 이하의 배선 패턴과, 그 이외의 임의의 폭의 배선 패턴을, 동일한 리소그래피에 의해 형성 가능하여, 종래에 비하면 현저히 리소그래피의 난이도를 저감할 수 있다.

[제2 실시 형태]

다음으로, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법을, 도 7∼도 13b를 참조하여 설명한다. 제1 실시 형태와 동일한 구성 요소에 대해서는 동일한 부호를 붙이고, 중복되는 설명은 이하에서는 생략한다. 또한,이하의 설명에서는, 제1 실시 형태와 마찬가지로, 반도체 기판(10) 상에 실리콘 산화막(20)을 개재하여 형성된 폴리실리콘막(25)을 피에칭 부재로 하여 에칭한다. 그리고, 메모리 셀 어레이 영역에서는 측벽 전사 프로세스를 이용하여 리소그래피의 해상 한계 이하의 배선 패턴을 형성하고, 주변 회로 부분에는, 그 이외의 임의의 크기의 배선 패턴 또는 컨택트 프린지 영역을 동시에 형성하는 것으로 한다.

우선, 도 7에 도시한 바와 같이, 제1 실시 형태와 마찬가지로, 폴리실리콘막(25) 상에, 아래부터 순서대로 실리콘 질화막(SiN)(33), BSG막(34), TEOS막(35), 실리콘 질화막(36), BSG막(37), TEOS막(38)으로 이루어지는 제1 하드 마스크(30)를 퇴적하고, 이 제1 하드 마스크(30) 상에, 아몰퍼스 실리콘으로 이루어지는 제2 하드 마스크(40)를 더 퇴적한다. 또한, 제2 하드 마스크(40)는, 폴리실리콘을 퇴적 시킨 것이어도 된다.

다음으로, 도 8에 도시한 바와 같이, 레지스트(80)를 메모리 셀 어레이 영역에만 형성하고, 레지스트(80)를 마스크로 하여, 불순물 이온(붕소(B), 인(P), 비소(As) 또는 이불화 붕소(BF2)가 바람직함)을 주변 회로 영역에 존재하는 제2 하드 마스크(40)(40B)에 주입한다. 이와 같이 본 실시 형태에서는, 제2 하드 마스크(40)를 원하는 패턴으로 패터닝하기 전에 이온 주입 공정을 실시하는 점에서, 제1 실시 형태가 패터닝 후에 이온 주입을 행하는 것과 상이하다(도 2a). 이 경우, 제1 실시 형태와 달리 패턴에 의한 요철이 없는 상태에서의 리소그래피로 되기 때문에, 기초층(TEOS막(38) 등)에의 데미지도 작아, 이상적인 상황에서 리소그래피를 실행하는 것이 가능하게 된다. 이온 주입이 되는 하드 마스크(40B)에서의 불순물 농도가 1×1020㎝-3로 되도록 이온 주입 조건을 조정하는 점은, 제1 실시 형태와 마찬가지이다.

그 후, 제2 하드 마스크(40, 40B)에 원하는 패턴 형상을 갖는 레지스트(50)를 형성한 후(도 9a), 슬리밍 처리하는 것(도 9b) 등은, 제1 실시 형태(도 1b, 도 1c)와 거의 마찬가지이다.

그 후의 공정(도 9b∼도 13)은, 도 1d, 도 2b∼도 6b와 거의 마찬가지이다. 즉, 계속하여 도 9b에 도시한 바와 같이, 슬리밍 처리된 레지스트(50)를 마스크로 한 이방성 에칭에 의해, 도 9c에 도시한 바와 같이, 제2 하드 마스크(40, 40B)를 에칭한다.

계속하여, 도 9d에 도시한 바와 같이, 제2 하드 마스크(40, 40B)를 마스크로 한 이방성 에칭에 의해, 제1 하드 마스크(30)의 측벽 형성막으로 되는 TEOS막(38) 및 BSG막(37)을 에칭한다. 그 후, 도 10에 도시한 바와 같이, 알칼리계 용액을 이용한 웨트 에칭에 의해, 이온 주입이 되지 않은 제2 하드 마스크(40)를 선택적으로 제거하고, 이온 주입이 된 제2 하드 마스크(40B)는 잔존시킨다. 알칼리계 용액에 의한 웨트 에칭에서는, 산화막, 질화막에 대한 선택비도 높기 때문에, 측벽 형성재인 TEOS막(38), 및 BSG막(37), 및 기초층의 실리콘 질화막(36)에는 아무런 악영향을 끼치지 않는다. 이 방법에 의해, 메모리 셀 어레이의 제2 하드 마스크(40)만을 용이하게 또한, 부작용없이 제거할 수 있다.

그 후, 측벽막(70)을 제1 실시 형태와 마찬가지로 형성하고(도 11a), 메모리 셀 어레이 영역에서 측벽막(70)의 사이에 끼워진 TEOS막(38) 및 BSG막(37)을 에칭 제거하고(도 11b), 이후 잔존된 측벽막(70) 및 제1 하드 마스크(30)를 마스크로 하여 피에칭 부재로서의 폴리실리콘막(25)을 에칭한다(도 12a∼도 13b). 이들의 상세는 제1 실시 형태의 도 5a∼도 6b과 거의 마찬가지이므로, 상세한 설명은 생략한다. 이와 같이, 이 제2 실시 형태에 의해서도, 리소그래피의 해상 한계 이하의 배 선 패턴과, 그 이외의 임의의 폭의 배선 패턴을, 동일한 리소그래피에 의해 형성 가능하여, 종래에 비하면 현저히 리소그래피의 난이도를 저감할 수 있다.

[제3 실시 형태]

다음으로, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법을, 도 14∼도 19b를 참조하여 설명한다. 상기한 실시 형태와 동일한 구성 요소에 대해서는 동일한 부호를 붙이고, 중복되는 설명은 이하에서는 생략한다.

이 실시 형태에서도, 제1 실시 형태와 마찬가지로, 반도체 기판(10) 상에 실리콘 산화막(20)을 개재하여 형성된 폴리실리콘막(25)을 에칭하여, 메모리 셀 어레이 영역에는 리소그래피의 해상 한계 이하의 배선 패턴을 형성하고, 주변 회로 부분에는, 그 이외의 임의의 큰 배선 패턴 또는 컨택트 프린지 영역을 동시에 형성 하는 것으로 한다(주변 회로 부분은, 도 14∼도 19b에서는 도시를 생략함). 단 이 실시 형태에서는, 메모리 셀 어레이 영역뿐만 아니라, 메모리 셀 어레이 배선에 직접 접속하는 임의 폭의 배선 패턴을 형성한다. 이 메모리 셀 어레이에 직접 연결되는 임의 폭의 부분은, 메모리 셀 어레이 배선의 컨택트 프린지 영역으로서 기능시킬 수 있다. 즉 이 실시 형태에서는, 도 14에 도시한 바와 같이, 피에칭 부재인 폴리실리콘막(25) 상에, 아래부터 순서대로 실리콘 질화막(SiN)(33), BSG막(34), TEOS막(35), 실리콘 질화막(36), BSG막(37), TEOS막(38)으로 이루어지는 제1 하드 마스크(30)를 퇴적하고, 이 제1 하드 마스크(30) 상에, 아몰퍼스 실리콘(또는 폴리실리콘)으로 이루어지는 제2 하드 마스크(40)를 더 퇴적하고, 원하는 패턴으로 패터닝한 후 슬리밍 처리하는 점은, 상기한 제1 실시 형태와 마찬가지이다. 인출 프 린지 영역에서는, 최소폭 W가 아닌 임의의 크기의 제2 하드 마스크(40)가 형성되어 있다(도 14∼도 19b에서, 그 우측위 부근에는, 인출 프린지 영역의 표면에 나타나는 제2 하드 마스크(40) 그 외의 평면도를 도시하고 있음).

단, 이 실시 형태에서는, 도 15에 도시한 바와 같이, 이온 주입 시의 마스크로 되는 레지스트(60)를 메모리 셀 어레이 영역뿐만 아니라 인출 프린지 영역의 제2 하드 마스크(40)의 일부에도 걸치도록 형성하고, 이 레지스트(60)를 마스크로 하여 불순물 이온(붕소(B), 인(P), 비소(As) 또는 이불화 붕소(BF2)가 바람직함)을 제2 하드 마스크(40B)에 주입한다. 즉, 이온 주입이 행해지는 영역과 행해지지 않는 영역의 경계가, 인출 프린지 영역 내에 있는 점에서, 본 실시 형태는 상기한 다른 실시 형태와 상이한 것이다.

계속해서, 이 레지스트(60)를 박리하고, 도 16에 도시한 바와 같이, 제2 하드 마스크(40, 40B)를 마스크로 한 이방성 에칭에 의해, 제1 하드 마스크(30)의 측벽 형성막으로 되는 TEOS막(38) 및 BSG막(37)을 에칭한다.

그 후, 알칼리계 용액을 이용한 웨트 에칭에 의해, 이온 주입이 되지 않은 제2 하드 마스크(40)(메모리 셀 어레이 영역, 및 인출 프린지 영역의 일부)를 선택적으로 제거하고, 이온 주입이 된 제2 하드 마스크(40B)는 잔존시킨다. 제2 하드 마스크(40B)는, 에칭에 의해 인출 프린지 영역 내에서 잔존된 TEOS막(38) 및 BSG막(37) 상의 일부(레지스트(60)가 형성되지 않은 부분)에 잔존하고, 그 밖의 위에서는 에칭 제거된다.

그 후, 제1 하드 디스크(30) 상의 전체면에, 에칭된 TEOS막(38) 및 BSG막(37)의 측벽, 및 제2 하드 마스크(40B)의 상면도 포함하여, 아몰퍼스 실리콘막을 CVD법에 의해 퇴적시킨다. 그 후 이방성 에칭에 의해, 제2 하드 마스크(40B), TEOS막(38) 및 BSG막(37)의 측벽에만 아몰퍼스 실리콘막이 남도록 하고, 이것이 도 17a에 도시한 바와 같이 측벽막(70)(아몰퍼스 실리콘막)으로 된다(도 17a의 우측 상에 도시한 바와 같이, 폐 루프 형상으로 남음). 측벽막(70)의 폭은, 상기한 실시 형태와 마찬가지로 1/2W 정도로 설정한다.

그 후 이방성 에칭에 의해, TEOS막(38) 및 BSG막(37)을 제거하면, 도 17b의 상태로 된다. 메모리 셀 어레이 영역에서는, 상기한 실시 형태와 마찬가지로, 측벽막(70)만이 잔존하고, 이것이 리소그래피의 해상 한계 이하(예를 들면 1/2W)의 배선 패턴 형성을 위한 마스크로 된다.

한편, 인출 프린지 영역에서는, 노출된 TEOS막(38) 및 BSG막(37)은 잔존한 제2 하드 마스크(40B)의 바로 아래에도 잡입하는 형태(제2 하드 마스크(40B)가 「차양」과 같은 형상으로서 잔존함)로 에칭 제거된다. 이 에칭 제거된 TEOS막(38) 및 BSG막(37)의 측벽에 형성되어 있던 측벽막(70)은 잔존하고, 이것이 인출 프린지 영역에서, 메모리 셀 어레이 영역의 배선 패턴으로 접속되는 리소그래피의 해상 한계 이하의 배선 패턴으로 된다.

이후, 제1 실시 형태와 거의 마찬가지로 하여, 에칭된 TEOS막(38), BSG막(37), 및 측벽막(70)을 마스크로 하여, 도 18a∼도 19b와 같이 폴리실리콘막(25)이 에칭되어 배선 패턴으로 된다. 메모리 셀 어레이 영역에는 리소그래피의 해상 한계 이하의 배선 패턴이 형성된다. 한편 인출 프린지 영역에는, 도 19b 우측위에 도시한 바와 같이, 리소그래피의 해상 한계 이하의 배선 패턴(25a), 및 그 이외의 임의의 폭이 넓은 배선 패턴(광폭부(25q))이 형성된다. 즉, 광폭부(25q)는, 잔존된 제2 하드 마스크(40B)와 그 주위의 측벽막(70)에 유래하여 형성되고, 리소그래피의 해상 한계 이하의 배선 패턴(25p)은, 측벽막(70)에만 유래하여 형성되고, 이 배선 패턴(25p)과 광폭부(25q)가 연속적으로 접속되어 형성된다.

본 실시 형태의 방법에 의해 형성되는 배선 패턴(25p)과 광폭부(25q)는, 형태 상 다음 3가지의 특징을 갖는다.

제1 특징은, 광폭부(25q)의 윤곽과, 상기 배선 패턴(25p)의 윤곽은, 그 폐 루프 형상의 내주에서, 거의 수직 또는 둔각으로 교차하는 것이다. 광폭부(25q)가 도 15에 도시한 바와 같은 큰 마스크에 따르는 이온 주입에 의해 규정되기 때문이다. 도 19a에 도시한 바와 같은 배선 패턴(25p) 및 광폭부(25q)를, 배선 패턴(25p) 형성을 위한 측벽 전사 프로세스와, 광폭부(25q) 형성을 위하여 배선 패턴(25p)의 위치에 맞춘 포토리소그래피에 의해 형성하는 경우, 레지스트의 현상 시의 왜곡에 의해, 광폭부(25q)의 윤곽과, 상기 배선 패턴(25p)의 윤곽은, 그 내주에서, 본 실시 형태와 달리 예각으로 교차한다.

제2 특징은, 배선 패턴(25p)의 폐 루프 형상에 따른 외주의 직선은, 광폭부(25q)의 외주의 직선과 거의 동일 직선 형상으로 배열하도록 형성되는 것이다. 광폭부(25q)는, 전술한 바와 같이 잔존된 제2 하드 마스크(40B)와 그 주위의 측벽막(70)에 유래하여 형성되기 때문이다.

제3 특징은, 배선 패턴(25p)은, 그 윤곽의 변동의 크기(LER : Line Edge Roughness)가, 폭의 변동(LWR : Line Width Rohghness)의 크기보다도 큰(LER>LWR)것이다(도 19c 참조). 측벽 전사 프로세스로부터 배선 패턴(25p)을 형성하는 경우, 측벽막이 전사되는 하드 마스크는 LWR>LER의 관계로 되어 있지만, 하드 마스크의 측벽에 형성된 측벽막(70)은, 측벽재의 퇴적막 두께만이 변동의 요인으로 되어, 거의 폭이 일정한 배선으로 되기 때문이다. 이것에 대하여, 통상적인 포토리소그래피에 의해 배선 패턴을 형성하는 경우, 레지스트 기인의 윤곽(엣지)의 위치의 변동은, 배선 패턴(25p)의 좌우 양측의 윤곽에서 각각 독립적으로 발생한다. 이 때문에, LWR>LER로 된다(도 19d 참조). 또한, 이 제3 특징은, 본 실시 형태의 경우에 한정되는 것은 아니며, 일반적으로 측벽 전사 프로세스의 측벽막에서 얻어진 배선 패턴에도 나타나는 특징이다.

[제4 실시 형태]

다음으로, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법을, 도 20a∼도 25c를 참조하여 설명한다. 상기한 실시 형태와 동일한 구성 요소에 대해서는 동일한 부호를 붙이고, 중복되는 설명은 이하에서는 생략한다.

상기한 제1∼제3 실시 형태에서는, 제2 하드 마스크(40)에 의해 에칭된 제1 하드 마스크(30)(구체적으로는 측벽 형성막인 TEOS막(38) 및 BSG막(37))의 측벽에, 아몰퍼스 실리콘으로 이루어지는 측벽막(70)을 형성하였다. 이것에 대하여, 본 실시 형태에서는, 제1 하드 마스크(30)의 측벽이 아니라, 제2 하드 마스크(40)의 측벽에 실리콘 질화막으로 이루어지는 측벽막(70a)을 형성하고, 이것을 이용하여 리 소그래피의 해상 한계 이하의 배선 패턴을 형성한다. 이하, 이 제조 방법을 도면을 참조하여 설명한다.

우선, 도 20a에 도시한 바와 같이, 반도체 기판(10) 상에 실리콘 산화막(20)을 개재하여 피에칭 부재로서의 폴리실리콘막(25)을 형성하고, 그 위에 실리콘 질화막(33), BSG막(37), 및 TEOS막(38)의 3층으로 이루어지는 제1 하드 마스크(30)를 형성한다. 이 제1 하드 마스크(30) 상에, 아몰퍼스 실리콘(또는 폴리실리콘)으로 이루어지는 제2 하드 마스크(40)를 형성한다.

다음으로, 도 20b에 도시한 바와 같이, 이 제2 하드 마스크(40) 상에 레지스트(50)를 형성하고, 이것을 마스크로 하여 제2 하드 마스크(40)를 에칭한다. 또한, 인출 프린지 영역에서는, 인출 프린지는 폭이 넓은 컨택트 프린지와, 이것에 이어지는 리소그래피의 해상 한계 이하의 배선 패턴(메모리 셀 어레이 영역에 접속되어 있음)을 갖고 있다.

다음으로, 도 20c에 도시한 바와 같이, 형성된 제2 하드 마스크(40)를 슬리밍 처리한다. 제2 하드 마스크(40)를 슬리밍 처리하는 대신에, 상기한 실시 형태 와 마찬가지로 레지스트(50)를 슬리밍 처리하는 것이어도 된다.

슬리밍 처리 후, 도 21에 도시한 바와 같이, 리소그래피의 해상 한계 이하의 배선을 형성하고자 하는 영역에, 레지스트(60)를 형성하고, 이것을 마스크로 하여 그 이외의 부분에 존재하는 제2 하드 마스크(40B)에 불순물 이온((붕소(B), 인(P), 비소(As) 또는 이불화 붕소(BF2)가 바람직함)을 주입한다. 주변 회로 영역 및 인출 프린지 형성 영역에서는, 도 21 우측위에 도시하는 평면도와 같이, 인출 프린지 영역의 일부 및 주변 회로 영역을 개구로 하도록 하는 레지스트(60)를 형성하여, 인출 프린지 영역의 일부 및 주변 회로 영역의 제2 하드 마스크(40B)에만 불순물 이온이 주입되도록 한다.

다음으로, 도 22에 도시한 바와 같이, 레지스트(60)를 박리한 후, 제2 하드 마스크(40, 40B)의 측벽에, 실리콘 질화막으로 이루어지는 측벽막(70A)을 형성한다. 상기한 실시 형태에서는, 아몰퍼스 실리콘을 재료로 하여 측벽막(70)을 형성하였다. 이것에 대하여 이 실시 형태에서는, 아몰퍼스 실리콘으로 이루어지는 제2 하드 마스크에 측벽막(70A)을 형성한다. 이 때문에, 측벽막(70A)에는 아몰퍼스 실리콘에 대하여 알칼리계 용액에 의한 웨트 에칭에서 높은 선택비를 갖는 실리콘 질화막을 이용한다.

계속해서, 도 23에 도시한 바와 같이, 알칼리계 용액에 의한 웨트 에칭에 의해, 이온 주입이 되지 않은 제2 하드 마스크(40)를 선택적으로 제거하고, 이온 주입이 된 제2 하드 마스크(40B)는 잔존시킨다. 알칼리계 용액에 의한 웨트 에칭에서는, 산화막, 질화막에 대한 선택비도 높기 때문에, 측벽막(70A) 및 기초층의 TEOS막(38)에는 아무런 악영향을 끼치지 않는다. 메모리 셀 어레이 영역에서는, 상기한 실시 형태와 마찬가지로 1/2W의 라인 폭 및 스페이스 폭으로 측벽막(70A)이 잔존하여 리소그래피의 해상 한계 이하의 배선 패턴이 형성 가능하게 된다. 한편, 주변 회로 영역에서는, 임의 폭의 굵은 배선 패턴도 형성 가능하게 되는 한편, 인출 프린지 영역에서는, 리소그래피의 해상 한계 이하의 배선 패턴과, 이에 접속되 는 굵은 배선 패턴이 형성 가능하게 된다. 이 굵은 배선 패턴은, 미세 배선 패턴의 컨택트 프린지로서 이용할 수 있다.

이 후, 도 24에 도시한 바와 같이, 잔존된 제2 하드 마스크(40B), 및 측벽막(70A)을 마스크로 하여, TEOS막(38), 및 BSG막(37)이 에칭된다. 계속해서, 도 25a에 도시한 바와 같이, 그 하층의 실리콘 질화막(34)이, 측벽막(70A)과 함께 에칭 제거된다. 또한, 이 잔존된 제1 하드 마스크(30)를 마스크로 하여 피에칭 부재인 폴리실리콘막(25)이 도 25b와 같이 에칭된다. 마지막으로, 도 25c에 도시한 바와 같이, 불산 베이퍼 처리 등 실리콘 산화막(20)에 대하여 선택비가 높은 조건에서 BSG막(34)만 제거함으로써, 실리콘 질화막(33)을 캡층으로 한 폴리실리콘막(25)으로 이루어지는 배선층이 형성된다.

이상, 발명의 실시 형태를 설명했지만, 본 발명은 이들에 한정되는 것은 아니며, 발명의 취지를 일탈하지 않는 범위 내에서, 다양한 변경, 추가 등이 가능하다. 예를 들면, 상기 실시 형태에서는, 측벽막(70, 70A)으로서 아몰퍼스 실리콘막 또는 실리콘 질화막으로 형성하는 예를 설명했지만, 에칭 조건 등에 따라서는, 이 이외의 재료, 예를 들면 실리콘 산화막 등을 재료로 하는 것도 가능하다.

도 1a는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 1b는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 1c는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 1d는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 2a는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 2b는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 2c는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 3은, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 4는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 5a는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공 정을 도시하는 도면.

도 5b는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 5c는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 6a는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 6b는, 본 발명의 제1 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 7은, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 8은, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 9a는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 9b는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 9c는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 9d는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공 정을 도시하는 도면.

도 10은, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 11a는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 11b는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 12a는, 본 발명의 .제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 12b는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 12c는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 13a는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 13b는, 본 발명의 제2 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 14는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 15는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공 정을 도시하는 도면.

도 16은, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 17a는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 17b는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 18a는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 18b는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 18c는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 19a는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 19b는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 나타낸다.

도 19c는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 형태 상의 특징도.

도 19d는, 본 발명의 제3 실시 형태에 따른 반도체 장치의 형태 상의 특징 도.

도 20a는, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 20b는, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 20c는, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 21은, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 22는, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 23은, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 24는, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 25a는, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 25b는, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 25c는, 본 발명의 제4 실시 형태에 따른 반도체 장치의 제조 방법의 일 공정을 도시하는 도면.

도 26은, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 27은, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 28은, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 29는, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 30은, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 31은, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 32는, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 33은, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 34는, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설명하는 공정도.

도 35는, 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법의 개념을 설 명하는 공정도.

<도면의 주요 부분에 대한 부호의 설명>

25 : 폴리실리콘막

30 : 제1 하드 마스크

37 : BSG막

38 : TEOS막

40, 40B : 제2 하드 마스크

50 : 레지스트

70 : 측벽막

Claims (18)

- 에칭 부재 상에 제1 하드 마스크를 형성하는 공정과,상기 제1 하드 마스크 상에 제2 하드 마스크를 형성하는 공정과,상기 제2 하드 마스크의 일부에 이온 주입을 행하고 이온 주입이 되지 않은 부분과의 비교에서 웨트 에칭에 대한 에칭 레이트를 변화시키기 위한 개질을 행하는 공정과,상기 제2 하드 마스크를 마스크로 하여 상기 제1 하드 마스크를 에칭하는 공정과,웨트 에칭에 의해 이온 주입되지 않은 상기 제2 하드 마스크만 선택적으로 에칭 제거하는 공정과,상기 제1 하드 마스크의 측벽에 측벽막을 형성하는 공정과,상기 제2 하드 마스크에 덮이지 않아 상부가 노출되어 있는 제1 하드 마스크를 선택적으로 에칭 제거하는 공정과,상기 측벽막 및 상기 제1 하드 마스크를 마스크로 하여 상기 피에칭 부재를 에칭 제거하는 공정을 구비한 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제1항에 있어서,상기 측벽막은, 상기 에칭 제거하는 공정에서 에칭되지 않고 잔존한 상기 제 2 하드 마스크의 측벽에도 형성되는 반도체 장치의 제조 방법.

- 제1항에 있어서,상기 이온 주입을 행하는 공정은, 상기 제2 하드 마스크를 패터닝한 후에, 상기 일부 이외의 부분에 마스크를 형성하여 실행되는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제1항에 있어서,상기 제2 하드 마스크는, 아몰퍼스 실리콘 혹은 폴리실리콘인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제4항에 있어서,상기 이온 주입에 이용되는 불순물 이온은, 붕소(B), 인(P), 비소(As) 또는 이불화 붕소(BF2) 중 어느 하나인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제1항에 있어서,상기 제1 하드 마스크는, 아래부터 순서대로 실리콘 질화막(SiN), BSG막, TEOS막, 실리콘 질화막, BSG막, TEOS막을 퇴적함으로써 형성되는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제6항에 있어서,상기 측벽막은, 아몰퍼스 실리콘인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제1항에 있어서,상기 제1 하드 마스크는, 상기 제2 하드 마스크에 대하여 알칼리계 용액에 의한 웨트 에칭에서 높은 선택비를 갖는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제1항에 있어서,상기 제1 하드 마스크는, 아래부터 순서대로 실리콘 질화막(SiN), BSG막, TEOS막, 실리콘 질화막, BSG막, TEOS막을 퇴적함으로써 형성되고,상기 제2 하드 마스크는, 아몰퍼스 실리콘 혹은 폴리실리콘인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제9항에 있어서,상기 측벽막은, 아몰퍼스 실리콘인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제1항에 있어서,상기 제2 하드 마스크 상에 리소그래피의 해상 한계인 최소 선폭의 라인 앤드 스페이스를 갖는 레지스트를 형성하는 공정과,상기 레지스트를 포토리소그래피의 해상 한계 이하의 폭까지 세화하는 공정과,상기 세화된 레지스트를 마스크로 한 이방성 에칭을 상기 제2 하드 마스크에 대하여 행하는 공정을 더 구비한 것을 특징으로 하는 반도체 장치의 제조 방법.

- 피에칭 부재 상에 제1 하드 마스크를 형성하는 공정과,상기 제1 하드 마스크 상에 제2 하드 마스크를 형성하는 공정과,상기 제2 하드 마스크의 일부에 이온 주입을 행하고 이온 주입이 되지 않은 부분과의 비교에서 웨트 에칭에 대한 에칭 레이트를 변화시키기 위한 개질을 행하는 공정과,상기 제2 하드 마스크의 측벽에 측벽막을 형성하는 공정과,웨트 에칭에 의해, 이온 주입되지 않은 상기 제2 하드 마스크만 선택적으로 에칭 제거하는 공정과,상기 제2 하드 마스크 및 상기 측벽막을 마스크로 하여 상기 제1 하드 마스크를 에칭하는 공정과,상기 제1 하드 마스크를 마스크로 하여 상기 피에칭 부재를 에칭 제거하는 공정을 구비한 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제12항에 있어서,상기 제2 하드 마스크는, 아몰퍼스 실리콘 혹은 폴리실리콘인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제13항에 있어서,상기 이온 주입에 이용되는 불순물 이온은, 붕소(B), 인(P), 비소(As) 또는 이불화 붕소(BF2) 중 어느 하나인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제13항에 있어서,상기 측벽막은, 실리콘 질화막인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제12항에 있어서,상기 측벽막은, 상기 제2 하드 마스크에 대하여 알칼리계 용액에 의한 웨트 에칭에서 높은 선택비를 갖는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제12항에 있어서,상기 제2 하드 마스크 상에 리소그래피의 해상 한계인 최소 선폭의 라인 앤드 스페이스를 갖는 레지스트를 형성하는 공정과,상기 레지스트를 포토리소그래피의 해상 한계 이하의 폭까지 세화하는 공정과,상기 세화된 레지스트를 마스크로 한 이방성 에칭을 상기 제2 하드 마스크에 대하여 행하는 공정을 더 구비한 것을 특징으로 하는 반도체 장치의 제조 방법.

- 하드 마스크의 측벽을 따른 폐 루프 형상의 측벽막을 형성함과 함께, 마스크를 이용하여 상기 하드 마스크의 일부에 대하여 이온 주입을 행한 후 상기 일부를 제외한 상기 하드 마스크를 에칭 제거하고, 상기 일부 및 상기 측벽막을 마스크로 하여 피에칭 부재를 에칭하여 이루어지는 배선층을 구비하고,상기 배선층은, 상기 일부 및 상기 측벽막에 유래하여 형성되는 광폭부와, 상기 측벽막에만 유래하여 형성되는 배선부를 갖고,상기 배선부는, 그 윤곽의 변동의 크기가, 상기 폭의 변동의 크기보다도 크고,상기 광폭부의 윤곽과, 상기 배선부의 윤곽은, 그 상기 폐 루프 형상의 내주에서, 수직 또는 둔각으로 교차하고,상기 배선부의 상기 폐 루프 형상에 따른 외주는, 상기 일부의 경계 부근도 포함하여 동일 직선 형상으로 형성되어 있는 것을 특징으로 하는 반도체 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2006-00195757 | 2006-07-18 | ||

| JP2006195757A JP4996155B2 (ja) | 2006-07-18 | 2006-07-18 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20080008257A KR20080008257A (ko) | 2008-01-23 |

| KR100854162B1 true KR100854162B1 (ko) | 2008-08-26 |

Family

ID=38970673

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020070071083A KR100854162B1 (ko) | 2006-07-18 | 2007-07-16 | 반도체 장치 및 그 제조 방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20080017992A1 (ko) |

| JP (1) | JP4996155B2 (ko) |

| KR (1) | KR100854162B1 (ko) |

| CN (1) | CN101114571B (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101532012B1 (ko) * | 2008-12-24 | 2015-06-30 | 삼성전자주식회사 | 반도체 소자 및 반도체 소자의 패턴 형성 방법 |

Families Citing this family (48)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4950702B2 (ja) | 2007-03-01 | 2012-06-13 | 株式会社東芝 | 半導体記憶装置の製造方法 |

| JP4384199B2 (ja) | 2007-04-04 | 2009-12-16 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2009049338A (ja) * | 2007-08-23 | 2009-03-05 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2009130035A (ja) * | 2007-11-21 | 2009-06-11 | Toshiba Corp | 半導体装置の製造方法 |

| US8304174B2 (en) | 2007-12-28 | 2012-11-06 | Hynix Semiconductor Inc. | Method for fabricating semiconductor device |

| KR100966976B1 (ko) * | 2007-12-28 | 2010-06-30 | 주식회사 하이닉스반도체 | 반도체 소자의 제조 방법 |

| JP5160302B2 (ja) * | 2008-05-19 | 2013-03-13 | 株式会社東芝 | 半導体装置の製造方法 |

| KR101468028B1 (ko) * | 2008-06-17 | 2014-12-02 | 삼성전자주식회사 | 반도체 소자의 미세 패턴 형성 방법 |

| KR101435520B1 (ko) | 2008-08-11 | 2014-09-01 | 삼성전자주식회사 | 반도체 소자 및 반도체 소자의 패턴 형성 방법 |

| JP2010080942A (ja) | 2008-08-25 | 2010-04-08 | Elpida Memory Inc | 半導体装置の製造方法 |

| US7709396B2 (en) * | 2008-09-19 | 2010-05-04 | Applied Materials, Inc. | Integral patterning of large features along with array using spacer mask patterning process flow |

| JP5236716B2 (ja) * | 2008-09-29 | 2013-07-17 | 東京エレクトロン株式会社 | マスクパターンの形成方法、微細パターンの形成方法及び成膜装置 |

| JP2010087298A (ja) * | 2008-09-30 | 2010-04-15 | Toshiba Corp | 半導体装置の製造方法 |

| JP2010087300A (ja) * | 2008-09-30 | 2010-04-15 | Toshiba Corp | 半導体装置の製造方法 |

| JP5214393B2 (ja) * | 2008-10-08 | 2013-06-19 | 株式会社東芝 | 半導体記憶装置 |

| KR101540083B1 (ko) | 2008-10-22 | 2015-07-30 | 삼성전자주식회사 | 반도체 소자의 패턴 형성 방법 |

| KR101045090B1 (ko) * | 2008-11-13 | 2011-06-29 | 주식회사 하이닉스반도체 | 반도체 소자의 미세 패턴 형성방법 |

| KR101565796B1 (ko) * | 2008-12-24 | 2015-11-06 | 삼성전자주식회사 | 반도체 소자 및 반도체 소자의 패턴 형성 방법 |

| JP5532611B2 (ja) * | 2009-01-23 | 2014-06-25 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法及び設計支援装置 |

| JP4871368B2 (ja) | 2009-03-16 | 2012-02-08 | 株式会社東芝 | 半導体記憶装置 |

| JP5390337B2 (ja) * | 2009-10-26 | 2014-01-15 | 株式会社東芝 | 半導体記憶装置 |

| JP2011176150A (ja) | 2010-02-24 | 2011-09-08 | Elpida Memory Inc | 半導体装置の製造方法 |

| JP2011249585A (ja) | 2010-05-27 | 2011-12-08 | Elpida Memory Inc | 半導体装置の製造方法 |

| JP5622512B2 (ja) * | 2010-10-06 | 2014-11-12 | 株式会社東芝 | 半導体装置の製造方法 |

| US8507346B2 (en) * | 2010-11-18 | 2013-08-13 | International Business Machines Corporation | Method of forming a semiconductor device having a cut-way hole to expose a portion of a hardmask layer |

| KR101732936B1 (ko) * | 2011-02-14 | 2017-05-08 | 삼성전자주식회사 | 반도체 소자의 미세 패턴 형성 방법 |

| JP5289479B2 (ja) * | 2011-02-14 | 2013-09-11 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2012204652A (ja) | 2011-03-25 | 2012-10-22 | Toshiba Corp | 半導体装置の製造方法 |

| JP5579136B2 (ja) * | 2011-08-17 | 2014-08-27 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP5615311B2 (ja) * | 2012-03-16 | 2014-10-29 | 株式会社東芝 | テンプレートの製造方法 |

| CN104425220A (zh) * | 2013-08-20 | 2015-03-18 | 中芯国际集成电路制造(上海)有限公司 | 图案的形成方法 |

| JP6384040B2 (ja) * | 2013-11-11 | 2018-09-05 | 大日本印刷株式会社 | パターン形成方法とこれを用いたインプリントモールドの製造方法およびそれらに用いるインプリントモールド |

| US20150255563A1 (en) * | 2014-03-04 | 2015-09-10 | United Microelectronics Corp. | Method for manufacturing a semiconductor device having multi-layer hard mask |

| TWI546846B (zh) * | 2014-05-16 | 2016-08-21 | 旺宏電子股份有限公司 | 圖案化的方法與圖案化的裝置 |

| KR102323456B1 (ko) | 2014-12-26 | 2021-11-10 | 삼성전자주식회사 | 반도체 소자 및 반도체 소자의 제조 방법 |

| JP6565415B2 (ja) * | 2015-07-22 | 2019-08-28 | 大日本印刷株式会社 | インプリントモールド製造用の基板およびインプリントモールドの製造方法 |

| CN109494149B (zh) | 2017-09-13 | 2020-10-23 | 联华电子股份有限公司 | 半导体结构的制作方法 |

| US20190115392A1 (en) * | 2017-10-16 | 2019-04-18 | International Business Machines Corporation | Access device and phase change memory combination structure in backend of line (beol) |

| US10269576B1 (en) * | 2017-11-15 | 2019-04-23 | Taiwan Semiconductor Manufacturing Co., Ltd. | Etching and structures formed thereby |

| KR102374206B1 (ko) * | 2017-12-05 | 2022-03-14 | 삼성전자주식회사 | 반도체 장치 제조 방법 |

| CN110021560A (zh) * | 2018-01-10 | 2019-07-16 | 中芯国际集成电路制造(上海)有限公司 | 半导体器件及其形成方法 |

| CN110391138A (zh) * | 2018-04-18 | 2019-10-29 | 上海格易电子有限公司 | 一种存储器的离子注入方法 |

| US11437238B2 (en) * | 2018-07-09 | 2022-09-06 | Applied Materials, Inc. | Patterning scheme to improve EUV resist and hard mask selectivity |

| JP2019054235A (ja) * | 2018-08-09 | 2019-04-04 | 大日本印刷株式会社 | パターン形成方法とこれを用いたインプリントモールドの製造方法およびそれらに用いるインプリントモールド |

| KR20200039073A (ko) | 2018-10-04 | 2020-04-16 | 삼성전자주식회사 | 반도체 장치의 제조 방법 |

| CN109950141A (zh) * | 2019-04-18 | 2019-06-28 | 上海华力微电子有限公司 | 一种半导体结构的形成方法 |

| JP2022542170A (ja) | 2019-08-01 | 2022-09-29 | アプライド マテリアルズ インコーポレイテッド | パターニングされた金属酸化物フォトレジストの線量減少 |

| TWI774007B (zh) * | 2020-06-16 | 2022-08-11 | 華邦電子股份有限公司 | 圖案化的方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6055631A (ja) | 1983-09-07 | 1985-03-30 | Oki Electric Ind Co Ltd | 半導体装置の製造方法 |

| JPS6484640A (en) * | 1987-09-28 | 1989-03-29 | Hitachi Ltd | Formation of pattern of polycrystalline silicon film |

| KR20050088779A (ko) * | 2004-03-03 | 2005-09-07 | 주식회사 하이닉스반도체 | 반도체 소자 제조 방법 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0855920A (ja) * | 1994-08-15 | 1996-02-27 | Toshiba Corp | 半導体装置の製造方法 |

| JPH0855908A (ja) * | 1994-08-17 | 1996-02-27 | Toshiba Corp | 半導体装置 |

| KR100354440B1 (ko) * | 2000-12-04 | 2002-09-28 | 삼성전자 주식회사 | 반도체 장치의 패턴 형성 방법 |

| JP2002208646A (ja) * | 2001-01-10 | 2002-07-26 | Toshiba Corp | 半導体装置、半導体装置の製造方法 |

| JP2005116969A (ja) * | 2003-10-10 | 2005-04-28 | Toshiba Corp | 半導体装置及びその製造方法 |

| US7151040B2 (en) * | 2004-08-31 | 2006-12-19 | Micron Technology, Inc. | Methods for increasing photo alignment margins |

| JP4936659B2 (ja) * | 2004-12-27 | 2012-05-23 | 株式会社東芝 | 半導体装置の製造方法 |

| JP4921723B2 (ja) * | 2005-04-18 | 2012-04-25 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2006351861A (ja) * | 2005-06-16 | 2006-12-28 | Toshiba Corp | 半導体装置の製造方法 |

| US7696101B2 (en) * | 2005-11-01 | 2010-04-13 | Micron Technology, Inc. | Process for increasing feature density during the manufacture of a semiconductor device |

| US8158333B2 (en) * | 2006-04-11 | 2012-04-17 | Kabushiki Kaisha Toshiba | Manufacturing method of semiconductor device |

| JP4271243B2 (ja) * | 2006-04-11 | 2009-06-03 | 株式会社東芝 | 集積回路パターンの形成方法 |

-

2006

- 2006-07-18 JP JP2006195757A patent/JP4996155B2/ja active Active

-

2007

- 2007-07-13 US US11/826,224 patent/US20080017992A1/en not_active Abandoned

- 2007-07-16 KR KR1020070071083A patent/KR100854162B1/ko not_active IP Right Cessation

- 2007-07-18 CN CN200710136666.XA patent/CN101114571B/zh not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6055631A (ja) | 1983-09-07 | 1985-03-30 | Oki Electric Ind Co Ltd | 半導体装置の製造方法 |

| JPS6484640A (en) * | 1987-09-28 | 1989-03-29 | Hitachi Ltd | Formation of pattern of polycrystalline silicon film |

| KR20050088779A (ko) * | 2004-03-03 | 2005-09-07 | 주식회사 하이닉스반도체 | 반도체 소자 제조 방법 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101532012B1 (ko) * | 2008-12-24 | 2015-06-30 | 삼성전자주식회사 | 반도체 소자 및 반도체 소자의 패턴 형성 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008027978A (ja) | 2008-02-07 |

| CN101114571B (zh) | 2012-03-14 |

| US20080017992A1 (en) | 2008-01-24 |

| KR20080008257A (ko) | 2008-01-23 |

| CN101114571A (zh) | 2008-01-30 |

| JP4996155B2 (ja) | 2012-08-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100854162B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US7914973B2 (en) | Method of forming a pattern in a semiconductor device and method of forming a gate using the same | |

| US6579757B2 (en) | Method for fabricating semiconductor device which prevents gates of a peripheral region from being oxidized | |

| US9581900B2 (en) | Self aligned patterning with multiple resist layers | |

| US10269581B2 (en) | Method of fabricating a semiconductor structure | |

| CN109585279B (zh) | 一种自对准双层图形的形成方法 | |

| US7687403B2 (en) | Method of manufacturing flash memory device | |

| TW201913226A (zh) | 半導體裝置的形成方法 | |

| JP2010087300A (ja) | 半導体装置の製造方法 | |

| KR100843899B1 (ko) | 반도체 소자의 제조방법 | |

| KR20060079353A (ko) | 사이드 로브 현상을 이용한 실린더형 커패시터 형성 방법 | |

| TWI449085B (zh) | 半導體元件的製程方法 | |

| US6949795B2 (en) | Structure and method of fabricating a transistor having a trench gate | |

| US20080146030A1 (en) | System and method for direct etching | |

| US20090102022A1 (en) | Method for manufacturing semiconductor device | |

| US6281092B1 (en) | Method for manufacturing a metal-to-metal capacitor utilizing only one masking step | |

| KR100302616B1 (ko) | 모스 트랜지스터 제조방법 | |

| KR0148611B1 (ko) | 반도체 소자의 소자분리막 형성방법 | |

| US6790743B1 (en) | [Method to relax alignment accuracy requirement in fabrication for integrated circuit] | |

| CN113140500A (zh) | 半导体结构的制作方法 | |

| KR100218727B1 (ko) | 반도체 소자의 콘택홀 형성방법 | |

| TWI518743B (zh) | 半導體裝置圖案化結構之製作方法 | |

| CN113496941A (zh) | 一种半导体结构的形成方法 | |

| JP2010087298A (ja) | 半導体装置の製造方法 | |

| KR20030002702A (ko) | 반도체 소자의 소자 분리막 형성 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20110720 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20120802 Year of fee payment: 5 |

|

| LAPS | Lapse due to unpaid annual fee |