KR100538181B1 - 액티브매트릭스형표시장치,반도체장치및반도체표시장치 - Google Patents

액티브매트릭스형표시장치,반도체장치및반도체표시장치 Download PDFInfo

- Publication number

- KR100538181B1 KR100538181B1 KR1019970045637A KR19970045637A KR100538181B1 KR 100538181 B1 KR100538181 B1 KR 100538181B1 KR 1019970045637 A KR1019970045637 A KR 1019970045637A KR 19970045637 A KR19970045637 A KR 19970045637A KR 100538181 B1 KR100538181 B1 KR 100538181B1

- Authority

- KR

- South Korea

- Prior art keywords

- electrode pattern

- display device

- pixel electrode

- active matrix

- electrode

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136227—Through-hole connection of the pixel electrode to the active element through an insulation layer

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B66—HOISTING; LIFTING; HAULING

- B66C—CRANES; LOAD-ENGAGING ELEMENTS OR DEVICES FOR CRANES, CAPSTANS, WINCHES, OR TACKLES

- B66C1/00—Load-engaging elements or devices attached to lifting or lowering gear of cranes or adapted for connection therewith for transmitting lifting forces to articles or groups of articles

- B66C1/04—Load-engaging elements or devices attached to lifting or lowering gear of cranes or adapted for connection therewith for transmitting lifting forces to articles or groups of articles by magnetic means

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B66—HOISTING; LIFTING; HAULING

- B66C—CRANES; LOAD-ENGAGING ELEMENTS OR DEVICES FOR CRANES, CAPSTANS, WINCHES, OR TACKLES

- B66C13/00—Other constructional features or details

- B66C13/04—Auxiliary devices for controlling movements of suspended loads, or preventing cable slack

- B66C13/06—Auxiliary devices for controlling movements of suspended loads, or preventing cable slack for minimising or preventing longitudinal or transverse swinging of loads

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B66—HOISTING; LIFTING; HAULING

- B66C—CRANES; LOAD-ENGAGING ELEMENTS OR DEVICES FOR CRANES, CAPSTANS, WINCHES, OR TACKLES

- B66C9/00—Travelling gear incorporated in or fitted to trolleys or cranes

- B66C9/08—Runners; Runner bearings

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136209—Light shielding layers, e.g. black matrix, incorporated in the active matrix substrate, e.g. structurally associated with the switching element

Abstract

본 발명은 높은 개구율과 필요로 하는 보조 용량을 가진 액티브 매트릭스형 표시장치를 제공한다. 소스 선 및 게이트 선과 화소 전극의 일부가 겹친 상태로 한다. 이 겹친 영역이 블랙 매트릭스가 된다. 또한, 화소 전극과 동일한 재료로 된 전극 패턴이 배치되어, 화소 전극을 이용하여 보조 용량을 형성한다. 이것에 의해, 개구율을 낮추지 않고 요구되는 보조 용량 값이 얻어질 수 있다. 또한, 전극 패턴이 소스 선 및 게이트 선과 화소 전극 사이의 크로스토크를 억제하기 위한 전기적 차폐막으로서 기능할 수 있다.

Description

본 발명은 액정 표시장치의 구성 및 그의 제작방법에 관한 것이다.

액정 표시장치로 대표되는 플랫 패널형 표시장치가 알려져 있다. 액정 패널을 투과한 광을 그 액정 패널에 의해 광학적으로 변조하는 형식을 가지는 투과형 액정 표시장치에서는, 화소의 윤곽을 명확하게 하기 위해 블랙 매트릭스로 불리는 차광수단이 필요하게 된다. 구체적으로는, 화소 전극의 주변부를 차광 프레임에 의해 덮는 것이 필요하다. 그러한 블랙 매트릭스는 특히 미세한 동화상을 표시하는데 있어서 중요한 역할을 한다.

그러나, 블랙 매트릭스는, 화소의 유효 면적(이 비율을 개구율이라 부른다)을 감소시키고 화면을 어둡게 하는 단점을 가진다.

최근, 휴대형 비디오 카메라나 휴대형 정보단말장치와 같은 저소비전력형 휴대 장치에 플랫 패널형 표시장치를 이용하는 것이 시도되고 있다.

여기서 문제로 되는 것은 그러한 휴대 장치에 요구되는 저소비전력 특성이다. 즉, 화면 표시에 사용되는 전력소비를 감소시키는 것이 필요하다.

투과형 액정 표시장치의 경우, 액정 패널의 뒤쪽으로부터 광을 조사(照射)하는 백라이트에 의해 소비되는 전력을 어떻게 감소시키는지가 문제로 된다. 백라이트의 전력소비는 화소의 개구율을 증가시켜 백라이트의 밝기를 작게 함으로써 감소될 수 있다.

한편, 액정 표시장치의 경우, 각 화소에서 액정이 가지는 용량을 보충하기 위해 보조 용량으로 불리는 커패시터를 배치하는 것이 필요하다. 이러한 보조 용량은, 화소 전극에 기입되고 소정의 시간 간격으로 재기입되는 정보(전하량에 대응함)를 다음 번 재기입될 때까지 보유하는 기능을 가진다. 보조 용량의 값이 작으면 표시의 플릭커 또는 컬러의 불균일(특히 컬러를 표시할 때 실현된다)이 일어난다.

그러나, 각 화소에 보조 용량을 배치하는 것은 또한, 블랙 매트릭스를 배치하는 경우와 마찬가지로 화소의 개구율을 감소시키는 원인이 된다.

상기한 바와 같이, 화질을 높이기 위해 블랙 매트릭스나 보조 용량을 배치하는 것은 화소의 개구율을 저하시키는 원인이 된다. 개구율의 저하는 다른 의미에서는 화질의 저하를 초래한다.

즉, 명확한 화상 표시를 구하는 것(블랙 매트릭스의 작용에 의해)과 밝은 화상을 얻는 것(개구율을 증가시키는 것에 의해)은 모순되는 요구사항이 된다.

또한, 표시의 플릭커와 컬러의 불균일을 억제하는 것(보조 용량의 작용에 의해)과 밝은 화상을 얻는 것(개구율을 증가시키는 것에 의해)도 모순되는 요구사항이 된다.

따라서, 본 발명의 목적은 상기한 모순되는 요구사항을 해결하는 기술을 제공하는데 있다.

본 발명의 일 양태에 따르면, 소스 선 및 게이트 선과 화소 전극 사이에 배치된 도전성 막으로 된 전극 패턴과; 그 전극 패턴과 화소 전극 사이에 형성된 보조 용량을 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시장치가 제공된다.

본 발명의 다른 양태에 따르면, 소스 선 및 게이트 선과 화소 전극 사이에 배치된 도전성 막으로 된 전극 패턴과; 그 전극 패턴과 화소 전극 사이에 형성된 보조 용량을 포함하고; 상기 화소 전극의 가장자리는 상기 소스 선 및 게이트 선과 겹치도록 배치되는 것을 특징으로 하는 액티브 매트릭스형 표시장치가 제공된다.

상기한 양 구성에서, 도전성 막으로 된 전극 패턴이 화소 전극으로부터 소스 선 및 게이트 선을 전기적으로 차폐하는 차폐막으로 기능한다.

본 발명의 또 다른 양태에 따르면, 도전성 막으로 된 전극 패턴이 소스 선 및 게이트 선을 덮도록 배치되는 것을 특징으로 하는 액티브 매트릭스형 표시장치가 제공된다.

상기한 구성에서, 도전성 막으로 된 전극 패턴이 화소 전극과 부분적으로 겹쳐 보조 용량을 형성한다. 또한, 도전성 막으로 된 전극 패턴은 화소 전극으로부터 소스 선 및 게이트 선을 전기적으로 차폐하는 차폐막으로 기능한다.

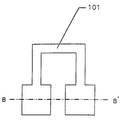

본 발명의 한가지 구체적인 예는, 도 1에 도시된 화소 구조에서와 같이, 화소 전극(107)과 동일한 재료로 된 전극 패턴(106)이 소스 선(105) 및 게이트 선(104)과 화소 전극(107) 사이에 배치되어, 전극 패턴(106)과 화소 전극(107) 사이에 보조 용량을 형성하는 것을 특징으로 한다.

[실시예 1]

도 1∼도 3에 본 실시예의 구성이 나타내어져 있다. 도 1∼도 3은 액티브 매트릭스형 액정 표시장치의 하나의 화소의 일부를 나타내는 확대 평면도이다.

도 1∼도 3은 동일한 부분을 나타낸다. 먼저, 도 1을 참조하여 그의 구성을 설명한다. 도 1에서, 부호 101로 나타낸 것이 박막트랜지스터의 활성층을 구성하는 패턴이다. 그 활성층(101)은 결정성 규소막으로 구성되어 있다.

부호 102는 활성층(101)의 일부로서, 드레인 영역으로 불리는 영역을 나타내고, 부호 103은 소스 영역으로 불리는 영역을 나타낸다. 이들 영역은 N채널형의 경우에는 N형을 가지고, P채널형의 경우에는 P형을 가지고 있다.

부호 104로 나타낸 것은 게이트 선의 패턴이다. 이 게이트 선(104)이 활성층(101)과 겹치는 부분에 있어서의 활성층(101)내의 영역이 채널 영역이 된다. 또한, 게이트 선(104)이 활성층(101)과 겹치는 영역이 게이트 전극으로 기능한다.

소스 선(105)은 콘택트부(111)를 통해 소스 영역(103)과 접촉하여 있다.

활성층(101)과 게이트 선(104)의 상하방향 위치관계는 다음과 같다. 즉, 활성층(101) 위에 게이트 절연막(도시되지 않음)이 형성되고, 그 위에 게이트 선(104)이 형성되어 있다.

그리고, 게이트 선(104) 위에 층간절연막(도시되지 않음)이 형성되고, 그 위에 소스 선(105)이 형성되어 있다.

부호 106으로 나타낸 빗금 영역은 커패시터를 형성하기 위한 ITO로 된 전극 패턴이다. 이 전극 패턴은 전체 액티브 매트릭스 영역에서 볼 때 격자 구조로 되어 있다. 커패시터를 형성하기 위한 ITO로 된 전극 패턴(106)은 적절한 일정 전위(기준 전위)로 유지되도록 구성되어 있다. 구체적으로는, 그 전극 패턴(106)은 액티브 매트릭스 회로(도시되지 않음)의 가장자리에서 대향 기판의 전극(이 전극은 대향 전극에 접속되어 있다)과 접촉하도록 구성되어 있다. 그리하여, 그의 전위가 대향 전극과 같게 유지되도록 배치된다.

보조 용량을 형성하기 위한 전극 패턴(106)의 형상은 도 1에 도시된 것에 한정되는 것은 아니다. 그 전극 패턴(106)이 ITO(또는 적절한 투명 도전성 막)로 되어 있기 때문에, 큰 자유도를 가지고 형성될 수 있다.

ITO로 된 패턴(107)이 화소 전극을 구성한다. 이 패턴(107)의 가장자리가 점선(108)으로 나타내어져 있다. 즉, 화소 전극(107)의 가장자리는 그의 일부가 소스 선(105) 및 게이트 선(104)과 겹치는 것으로 되어 있다.

도 2는 화소 전극(107)의 패턴이 빗금 부분으로서 강조된 도면을 나타낸다. 즉, 도 2에서 빗금으로 나타낸 영역이 화소 전극(107)이다.

이 화소 전극(107)은 커패시터를 형성하기 위한 ITO로 된 전극 패턴(106) 위에 형성된 제2 층간절연막(도시되지 않음) 위에 형성되어 있다.

도 1에 도시된 바와 같이, 화소 전극(107)은 콘택트부(110)를 통해 활성층(101)의 드레인 영역(102)과 접촉하여 있다.

도 1 및 도 2로부터(특히 도 2로부터) 명백한 바와 같이, 화소 전극(107)은 그의 가장자리가 게이트 선(104) 및 소스 선(105)과 겹치도록 배치되어 있다. 화소 전극(107)이 게이트 선(104) 및 소스 선(105)과 겹친 영역이 화소 전극의 가장자리를 차광하는 블랙 매트릭스가 된다.

커패시터를 형성하기 위한 전극 패턴(106)(도 1에서 빗금으로 나타낸)도 또한, 도 3의 빗금 부분(109)으로 나타낸 영역에서 도 2에서 빗금으로 나타낸 화소 전극(107)과 겹쳐 있다.

이들 2개의 ITO 전극 패턴들이 겹친 영역에 보조 용량이 형성된다. 즉, 액정과 대향 전극 사이에 형성된 커패시터와 병렬로 접속된 커패시터(보조 용량으로 불린다)가 형성된다.

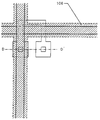

도 4 이하의 도면은 제작공정을 나타내는, 도 1의 A-A'선에 따른 단면을 나타낸다. 또한, 도 9A∼도 9D 및 도 10은 대응하는 제작공정들을 나타내는 단면도이다.

먼저, 도 9A에 도시된 바와 같이, 유리 기판(또는 석영 기판)(901)상에 하지막(下地膜)으로서 산화규소막(902)을 스퍼터링법에 의해 3000 Å의 두께로 성막한다. 도 4의 B-B'선에 따른 단면이 도 9A의 단면에 대응한다.

다음에, 비정질 규소막(도시되지 않음)을 LPCVD법에 의해 500 Å의 두께로 성막한다. 이 비정질 규소막은 후에 박막트랜지스터의 활성층을 형성하기 위한 출발막이 된다.

비정질 규소막(도시되지 않음)을 성막한 후, 레이저광을 조사(照射)한다. 레이저광 조사에 의해, 비정질 규소막이 결정화되어 결정성 규소막이 얻어진다. 또한, 비정질 규소막이 가열에 의해 결정화될 수도 있다.

그 다음, 그렇게 하여 얻어진 결정성 규소막을 패터닝하여 활성층(101)을 형성한다(그 활성층의 패턴이 도 4 및 도 9A에 도시되어 있다). 후의 공정에서, 그 활성층 내에 소스/드레인 영역 및 채널 영역이 형성된다.

그리하여, 도 4 및 도 9A에 도시된 상태가 얻어진다. 그 다음, 도 9B에 도시된 바와 같이(도 4에는 도시되지 않음), 게이트 절연막으로 기능하는 산화규소막(903)을 플라즈마 CVD법에 의해 1000 Å의 두께로 성막한다.

그 다음, 도 5에 도시된 바와 같이, 게이트 선(104)을 형성한다. 이 게이트 선은 알루미늄으로 형성되어 있다. 그리고, 도면들에서는 명확하지 않지만, 그 알루미늄의 표면에 보호막으로서 양극산화막이 형성된다. 게이트 선(104)이 도 9에는 도시되어 있지 않다(즉, 도 9의 단면에는 게이트 선이 존재하지 않는다).

여기서, 게이트 선(104)이 활성층(101)과 겹치는 활성층의 영역이 채널 영역이 된다. 즉, 도 5에서 부호 501, 502로 나타낸 영역들이 채널 영역이다. 본 실시예의 경우에는, 2개의 채널 영역이 존재한다 이 구성은 2개의 박막트랜지스터가 직렬로 등가적으로 접속된 구조가 된다.

그러한 구성은, 하나의 박막트랜지스터에 인가되는 전압이 각각의 트랜지스터부로 분할되기 때문에 역방향 누설전류 및 열화(劣化) 정도를 감소시킬 수 있다.

게이트 선(104)을 형성한 후, 도 5에 도시된 상태에서 불순물을 도핑한다. 여기서는, N채널형 박막트랜지스터를 제작하기 위해, 플라즈마 도핑법에 의해 P(인) 원소가 도핑되었다.

이 불순물 도핑 공정에서, 게이트 선(104)이 마스크가 되고, 소스 영역(103) 및 드레인 영역(102)이 자기정합적으로 형성된다. 또한, 2개의 채널 영역(501, 502)의 위치도 자기정합적으로 결정된다.

불순물 도핑의 완료 후, 레이저광을 조사하여, 도핑된 원소를 활성화하고, 그 도핑 중에 야기되는 활성층의 손상을 어닐한다. 이 활성화는 램프광의 조사 또는 가열처리에 의해서도 행해질 수 있다.

게이트 선(104)을 형성한 후, 질화규소막(904)과 폴리이미드막(905)으로 된 적층 막을 형성한다. 이 적층 막은 제1층간절연막으로서 기능한다. 그리하여, 도 9B에 도시된 상태가 얻어진다.

층간절연막으로서 폴리이미드와 같은 수지 막을 이용한 경우, 그의 표면이 평탄화될 수 있다.

다음에, 도 9C에 도시된 바와 같이, 적층 막(904, 905)으로 된 제1 층간절연막을 관통하여 콘택트 홀(111)을 형성한 다음, 도 6 및 도 9C에 도시된 바와 같이, 소스 선(105)을 형성한다.

소스 선(105)은 콘택트 홀(111)을 통하여 소스 영역(103)과 접촉하는 상태가 된다. 도 6의 C-C'선에 따른 단면이 도 9C에 도시된 것에 대응한다.

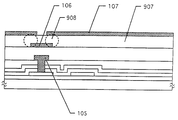

그 다음, 도 9D 및 도 7에 도시된 바와 같이, 제2 층간절연막으로서 폴리이미드막(906)을 형성한다.

그리고, ITO로 된 패턴(106)(보조 용량을 형성하기 위한 패턴)을 형성한다. 여기서, 도 7의 D-D'선에 따른 단면이 도 9D에 도시된 것에 대응한다.

그 다음, 도 8 및 도 10에 도시된 바와 같이, 제3 층간절연막으로서 폴리이미드막(907)을 형성한 다음, 그 위에 ITO로 된 화소 전극(107)을 형성한다.

여기서, 전술한 바와 같이, 화소 전극(107)이 소스 선(105)(및 게이트 선)과 겹친 영역이 블랙 매트릭스로 기능한다. 또한, ITO로 된 패턴(106)이 화소 전극(107)과 겹친 영역(908)이 보조 용량으로 기능한다.

도 10에 도시된 바와 같은 단면 구조를 형성함으로써, 하기의 유의성이 얻어질 수 있다.

(1) 화소 전극(107)의 가장자리를 소스 선 및 게이트 선과 겹치게 함으로써, 그 겹침 영역이 블랙 매트릭스로서 기능한다. 그리하여, 개구율이 최대로 증대될 수 있다.

(2) ITO로 된 패턴(106)과 화소 전극(107) 사이에 보조 용량(908)을 형성함으로써, 필요로 하는 용량 값을 개구율의 저하 없이 얻을 수 있다. 특히, 화소 전극과 겹쳐 형성되는 ITO 패턴의 자유도가 증가되어, 필요로 하는 용량을 얻을 수 있다.

(3) 도 10으로부터 명백한 바와 같이, 보조 용량을 형성하기 위한 ITO 패턴(106)이 소스 선(105)보다 큰 면적을 가지는 패턴으로 되고, 적절한 기준 전위로 유지된다. 그리하여, ITO 패턴(106)이 소스 선(105)으로부터 화소 전극(107)을 전기적으로 차폐하는 차폐막으로도 기능할 수 있게 된다. 그래서, 소스 선(105)과 화소 전극(107) 사이의 크로스토크(cross-talk)가 억제될 수 있다. 이러한 효과는 화소 전극과 게이트 선 사이에서도 마찬가지로 얻어질 수 있다.

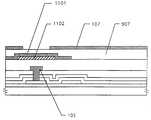

[실시예 2]

본 실시예는 실시예 1에 나타낸 것으로부터 변형된 구성에 관한 것이다. 실시예 1에 나타낸 구성에서는, 소스 선 및 게이트 선이 화소 전극과 겹쳐 있고, 그 겹침 영역이 블랙 매트릭스로서 기능하도록 되어 있다. 실시예 1에 나타낸 구성은 개구율을 최대로 증대시키는데 유용한 구성이다. 그러나, 요구되는 화질 또는 표시방법에 따라서는 블랙 매트릭스의 면적을 증가시키는 것이 필요한 경우도 있다.

본 실시예는 그러한 경우에 이용될 수 있는 구성에 관한 것이다. 도 11은 본 실시예에 따른 화소 부분의 단면을 나타낸다. 도 11은 도 10에 대응하기 때문에, 도 10에서의 것과 동일한 부호가 도 11의 동일 구성요소를 나타낸다.

본 실시에에서는, 티탄 막 또는 크롬 막(또는 적절한 금속 막)으로 되어 있고 블랙 매트릭스를 구성하는 막(1102)의 일부가 ITO로 된 화소 전극(107)의 가장자리와 겹쳐 있다.

ITO 패턴(1101)이 블랙 매트릭스(1102)를 덮기 위해 블랙 매트릭스보다 큰 면적을 가지고 있어, 보조 용량의 값을 더욱 증가시킨다 보조 용량을 형성하기 위한 ITO 패턴(1101)은 그의 면적이 증가하여도 개구율을 저하시키지 않는다.

본 발명에 의하면, 화소의 개구율을 저하시키지 않고 블랙 매트릭스가 제공될 수 있다. 또한, 필요로 하는 보조 용량이 화소의 개구율의 저하 없이 제공될 수 있다. 또한, 화소 전극과 함께 보조 용량을 형성하는 전극 패턴에 의해 소스 선 및 게이트 선과 화소 전극 사이의 크로스토크가 억제될 수 있다.

도 1은 실시예 1에 따른 액티브 매트릭스 회로의 일부를 나타내는 평면도.

도 2는 실시예 1에 따른 액티브 매트릭스 회로의 일부를 나타내는 평면도.

도 3은 실시예 1에 따른 액티브 매트릭스 회로의 일부를 나타내는 평면도.

도 4는 실시예 1에 따른 액티브 매트릭스 회로의 제작공정을 나타내는 평면도.

도 5는 실시예 1에 따른 액티브 매트릭스 회로의 제작공정을 나타내는 평면도.

도 6은 실시예 1에 따른 액티브 매트릭스 회로의 제작공정을 나타내는 평면도.

도 7은 실시예 1에 따른 액티브 매트릭스 회로의 제작공정을 나타내는 평면도.

도 8은 실시예 1에 따른 액티브 매트릭스 회로의 제작공정을 나타내는 평면도.

도 9A∼도 9D는 실시예 1에 따른 액티브 매트릭스 회로의 제작공정을 나타내는 단면도.

도 10은 실시예 1에 따른 액티브 매트릭스 회로의 제작공정을 나타내는 단면도.

도 11은 실시예 2에 따른 액티브 매트릭스 회로의 제작공정을 나타내는 단면도.

* 도면의 주요 부분에 대한 부호의 설명

101: 활성층 102: 드레인 영역 103: 소스 영역

104: 게이트 선 105: 소스 선 106: ITO 전극

107: 화소 전극 110, 111: 콘택트부 901: 유리 기판

902: 산화규소막 903: 게이트 절연막 904: 질화규소막

905∼907: 폴리이미드막 908: 보조 용량 형성부 1101: ITO 전극

1102: 블랙 매트릭스

Claims (74)

- 화소 전극;그 화소 전극에 접속된 적어도 하나의 스위칭 소자;소스 선 및 게이트 선과 상기 화소 전극 사이에 배치된 투명 도전성 막으로 된 전극 패턴; 및그 전극 패턴과 상기 화소 전극 사이에 형성된 보조 용량을 포함하고;상기 전극 패턴이 상기 소스 선의 적어도 일부 위에서 연장하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 1 항에 있어서, 투명 도전성 막으로 된 상기 전극 패턴이, 상기 화소 전극으로부터 상기 소스 선 및 게이트 선을 전기적으로 차폐하는 차폐막으로서 기능하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 1 항에 있어서, 상기 스위칭 소자가 박막트랜지스터인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 1 항에 있어서, 상기 전극 패턴의 재료가 ITO인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 화소 전극;그 화소 전극에 접속된 적어도 하나의 스위칭 소자;소스 선 및 게이트 선과 상기 화소 전극 사이에 배치된 투명 도전성 막으로 된 전극 패턴; 및투명 도전성 막으로 된 상기 전극 패턴과 상기 화소 전극 사이에 형성된 보조 용량을 포함하고;상기 화소 전극의 가장자리가 상기 소스 선 및 게이트 선과 겹치도록 배치되어 있는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 5 항에 있어서, 투명 도전성 막으로 된 상기 전극 패턴이, 상기 화소 전극으로부터 상기 소스 선 및 게이트 선을 전기적으로 차폐하는 차폐막으로서 기능하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 5 항에 있어서, 상기 스위칭 소자가 박막트랜지스터인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 5 항에 있어서, 상기 전극 패턴의 재료가 ITO인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 투명 화소 전극;그 투명 화소 전극에 접속된 적어도 하나의 스위칭 소자; 및;소스 선 및 게이트 선을 덮도록 상기 스위칭 소자와 상기 투명 화소 전극 사이에 배치된 투명 도전성 막으로 된 전극 패턴을 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 9 항에 있어서, 투명 도전성 막으로 된 상기 전극 패턴이 상기 화소 전극과 부분적으로 겹쳐 보조 용량을 형성하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 9 항에 있어서, 투명 도전성 막으로 된 상기 전극 패턴이, 상기 화소 전극으로부터 상기 소스 선 및 게이트 선을 전기적으로 차폐하는 차폐막으로서 기능하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 9 항에 있어서, 상기 스위칭 소자가 박막트랜지스터인 것과 동일한 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 9 항에 있어서, 상기 전극 패턴의 재료가 ITO인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 절연 표면을 가진 기판 위에 형성된 반도체막;그 반도체막 위에 형성된 게이트 절연막;그 게이트 절연막 위에 형성된 제1 층간절연막;그 제1 층간절연막 상에 형성되고 콘택트를 통하여 상기 반도체막에 접속된 배선;그 배선과 상기 제1 층간절연막 위에 형성된 제2 층간절연막;상기 배선을 덮도록 상기 제2 층간절연막 상에 형성된 전극 패턴;그 전극 패턴과 상기 제2 층간절연막 위에 형성된 제3 층간절연막; 및상기 전극 패턴과 부분적으로 겹치도록 상기 제3 층간절연막 상에 형성된 화소 전극을 포함하고;상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 14 항에 있어서, 상기 전극 패턴의 재료가 투명성인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 14 항에 있어서, 상기 제1 층간절연막이 질화규소막과 폴리이미드막으로 이루어진 적층 막인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 14 항에 있어서, 상기 제2 및 제3 층간절연막이 폴리이미드로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 절연 표면을 가진 기판 위에 형성된 반도체막;그 반도체막 위에 형성된 게이트 절연막;그 게이트 절연막 위에 형성된 제1 층간절연막;그 제1 층간절연막 상에 형성되고 콘택트를 통하여 상기 반도체막에 접속된 배선;그 배선과 상기 제1 층간절연막 위에 형성된 제2 층간절연막;상기 배선을 덮도록 상기 제2 층간절연막 상에 형성된 블랙 매트릭스;상기 배선과 상기 블랙 매트릭스를 덮도록 상기 블랙 매트릭스와 상기 제2 층간절연막 위에 형성된 전극 패턴;그 전극 패턴과 상기 제2 층간절연막 위에 형성된 제3 층간절연막; 및상기 전극 패턴과 부분적으로 겹치도록 상기 제3 층간절연막 상에 형성된 화소 전극을 포함하고;상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 18 항에 있어서, 상기 블랙 매트릭스가 티탄과 크롬으로부터 선택된 금속으로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 18 항에 있어서, 상기 전극 패턴과 상기 화소 전극의 재료가 투명성인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 18 항에 있어서, 상기 제1 층간절연막이 질화규소막과 폴리이미드막으로 이루어진 적층 막인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 18 항에 있어서, 상기 제2 및 제3 층간절연막이 폴리이미드로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 절연 표면을 가진 기판 위에 형성된 반도체막;게이트 절연막을 사이에 두고 상기 반도체막에 인접하여 있는 게이트 전극;상기 반도체막에 각각 접속된 소스 배선 및 드레인 배선;그 소스 배선의 적어도 일부를 덮도록 형성된 투명 전극 패턴;그 투명 전극 패턴 위에 형성된 층간절연막; 및그 층간절연막 상에 형성된 화소 전극을 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 23 항에 있어서, 상기 전극 패턴이 ITO로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 23 항에 있어서, 상기 소스 배선 및 드레인 배선이, 적어도 규소와 질소를 포함하는 절연막을 통과하여 상기 반도체막에 접속된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 23 항에 있어서, 상기 층간절연막이 폴리이미드로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 절연 표면을 가진 기판 위에 형성된 반도체막;게이트 절연막을 사이에 두고 상기 반도체막에 인접하여 있는 게이트 전극;상기 반도체막과 상기 게이트 전극 위에 형성된 절연막;그 절연막의 콘택트 홀들을 통하여 상기 반도체막에 접속된 소스 배선 및 드레인 배선;적어도 상기 소스 배선에 인접하여 있는 블랙 매트릭스;적어도 상기 소스 배선 위에 형성된 투명 전극 패턴;그 투명 전극 패턴 위에 형성된 층간절연막; 및그 층간절연막 위에 형성된 화소 전극을 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 27 항에 있어서, 상기 블랙 매트릭스가 티탄과 크롬으로부터 선택된 금속으로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 27 항에 있어서, 상기 전극 패턴과 상기 화소 전극이 ITO로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 27 항에 있어서, 상기 절연막이 적어도 규소와 질소를 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 27 항에 있어서, 상기 층간절연막이 폴리이미드로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- U자형 활성층을 가진 적어도 하나의 박막트랜지스터;소스 선 및 게이트 선과 화소 전극 사이에 배치된 도전성 막으로 된 전극 패턴; 및그 전극 패턴과 상기 화소 전극 사이에 형성된 보조 용량을 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 32 항에 있어서, 도전성 막으로 된 상기 전극 패턴이, 상기 화소 전극으로부터 상기 소스 선 및 게이트 선을 전기적으로 차폐하는 차폐막으로서 기능하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 32 항에 있어서, 상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 32 항에 있어서, 상기 전극 패턴의 재료가 투명성인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 다수의 채널 영역을 가진 반도체 활성층을 가지고, 화소 전극에 접속된 적어도 하나의 박막트랜지스터;그 박막트랜지스터에 접속된 소스 선 및 게이트 선;적어도 상기 소스 선 위에 배치된 도전성 막으로 된 전극 패턴; 및그 전극 패턴과 상기 화소 전극 사이에 형성된 보조 용량을 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 36 항에 있어서, 도전성 막으로 된 상기 전극 패턴이, 상기 화소 전극으로부터 상기 소스 선 및 게이트 선을 전기적으로 차폐하는 차폐막으로서 기능하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 36 항에 있어서, 상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 36 항에 있어서, 상기 전극 패턴의 재료가 투명성인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 절연 표면을 가진 기판 위에 형성되고, 적어도 하나의 굴곡부를 가진 적어도 하나의 반도체 섬;그 반도체 섬에 인접하여 있는 게이트 전극;상기 반도체 섬에 접속된 배선;그 배선 위에 형성된 절연막;상기 배선의 적어도 일부를 덮는 전극 패턴;그 전극 패턴 위에 형성된 층간절연막; 및상기 전극 패턴의 적어도 일부와 겹치도록 상기 층간절연막 상에 형성된 화소 전극을 포함하고;상기 반도체 섬이 다수의 채널 영역을 가지는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 40 항에 있어서, 상기 전극 패턴과 상기 화소 전극이 투명성인 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 40 항에 있어서, 상기 전극 패턴과 상기 화소 전극이 ITO로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 40 항에 있어서, 상기 층간절연막이 폴리이미드로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 기판 위에 형성되고, 적어도 채널 영역, 소스 영역 및 드레인 영역을 포함하는 활성층을 가진 적어도 하나의 박막트랜지스터;서로 교차하고 상기 박막트랜지스터에 접속된 소스 선 및 게이트 선;그 소스 선 및 게이트 선을 덮고 그 소스 선 및 게이트 선을 따라 연장하며, 투명 재료로 된 전극 패턴; 및그 전극 패턴 위에 형성되고, 상기 박막트랜지스터의 상기 드레인 영역에 접속되며, 주변부가 상기 전극 패턴을 사이에 두고 상기 소스 선 및 게이트 선과 겹쳐 있는 화소 전극을 포함하고;상기 소스 선이 상기 박막트랜지스터의 상기 소스 영역의 콘택트부와 겹쳐 있는 것을 특징으로 하는 반도체장치.

- 제 44 항에 있어서, 상기 전극 패턴이 ITO로 된 것을 특징으로 하는 반도체장치.

- 제 44 항에 있어서, 상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 반도체장치.

- 제 44 항에 있어서, 상기 전극 패턴과 상기 화소 전극 사이에 보조 용량이 형성된 것을 특징으로 하는 반도체장치.

- 제 44 항에 있어서, 상기 화소 전극이 투명 재료로 된 것을 특징으로 하는 반도체장치.

- 제 44 항에 있어서, 상기 박막트랜지스터가 적어도 2개의 채널 영역을 포함하는 것을 특징으로 하는 반도체장치.

- 기판 위에 형성되고, 적어도 채널 영역, 소스 영역 및 드레인 영역을 포함하는 활성층을 가진 적어도 하나의 박막트랜지스터;서로 교차하고 상기 박막트랜지스터에 접속된 소스 선 및 게이트 선;그 소스 선 및 게이트 선을 덮고 그 소스 선 및 게이트 선을 따라 연장하며, 투명 재료로 된 전극 패턴; 및상기 박막트랜지스터의 상기 드레인 영역에 접속되고, 주변부가 상기 전극 패턴을 사이에 두고 상기 소스 선 및 게이트 선과 겹쳐 있는 화소 전극을 포함하고,상기 소스 영역의 콘택트부가 상기 화소 전극과 겹치지 않는 것을 특징으로 하는 반도체 표시장치.

- 제 50 항에 있어서, 상기 전극 패턴이 ITO로 된 것을 특징으로 하는 반도체 표시장치.

- 제 50 항에 있어서, 상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 반도체 표시장치.

- 제 50 항에 있어서, 상기 전극 패턴과 상기 화소 전극 사이에 보조 용량이 형성된 것을 특징으로 하는 반도체 표시장치.

- 제 50 항에 있어서, 상기 화소 전극이 투명 재료로 된 것을 특징으로 하는 반도체 표시장치.

- 제 50 항에 있어서, 상기 박막트랜지스터가 적어도 2개의 채널 영역을 포함하는 것을 특징으로 하는 반도체 표시장치.

- 기판 위에 형성되고, 적어도 채널 영역, 소스 영역 및 드레인 영역을 포함하는 활성층을 가진 적어도 하나의 박막트랜지스터;서로 교차하고 상기 박막트랜지스터에 접속된 소스 선 및 게이트 선;그 소스 선 및 게이트 선을 덮고 그 소스 선 및 게이트 선을 따라 연장하며, 투명 재료로 된 전극 패턴; 및상기 박막트랜지스터의 상기 드레인 영역에 직접 접속되고, 주변부가 상기 전극 패턴을 사이에 두고 상기 소스 선 및 게이트 선과 겹쳐 있는 화소 전극을 포함하고;상기 전극 패턴이 상기 소스 선과 상기 게이트 선의 교차부를 덮는 것을 특징으로 하는 반도체 표시장치.

- 제 56 항에 있어서, 상기 전극 패턴이 ITO로 된 것을 특징으로 하는 반도체 표시장치.

- 제 56 항에 있어서, 상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 반도체 표시장치.

- 제 56 항에 있어서, 상기 전극 패턴과 상기 화소 전극 사이에 보조 용량이 형성된 것을 특징으로 하는 반도체 표시장치.

- 제 56 항에 있어서, 상기 화소 전극이 투명 재료로 된 것을 특징으로 하는 반도체 표시장치.

- 제 56 항에 있어서, 상기 박막트랜지스터가 적어도 2개의 채널 영역을 포함하는 것을 특징으로 하는 반도체 표시장치.

- 기판 위에 형성된 적어도 하나의 박막트랜지스터;서로 교차하고, 상기 박막트랜지스터에 접속된 소스 선 및 게이트 선;그 소스 선 및 게이트 선을 덮고 그 소스 선 및 게이트 선을 따라 연장하며, 투명 재료로 된 전극 패턴; 및그 전극 패턴 위에 형성되고, 주변부가 상기 전극 패턴을 사이에 두고 상기 소스 선 및 게이트 선과 겹쳐 있는 화소 전극을 포함하고;상기 전극 패턴이, 상기 화소 전극으로부터 상기 소스 선 및 게이트 선을 전기적으로 차폐하는 차폐막으로서 기능하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 62 항에 있어서, 상기 전극 패턴이 ITO로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 62 항에 있어서, 상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 62 항에 있어서, 상기 전극 패턴과 상기 화소 전극 사이에 보조 용량이 형성된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 62 항에 있어서, 상기 화소 전극이 투명 재료로 된 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 제 62 항에 있어서, 상기 박막트랜지스터가 적어도 2개의 채널 영역을 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시장치.

- 기판 위에 형성되고, 적어도 채널 영역, 소스 영역 및 드레인 영역을 포함하는 활성층을 가진 적어도 하나의 박막트랜지스터;서로 교차하고 상기 박막트랜지스터에 접속된 소스 선 및 게이트 선;그 소스 선 및 게이트 선을 덮고 그 소스 선 및 게이트 선을 따라 연장하며, 제1 층과 제2 층으로 이루어진 전극 패턴; 및그 전극 패턴 위에 형성되고, 상기 박막트랜지스터의 상기 드레인 영역에 접속되며, 주변부가 상기 소스 선 및 게이트 선과 겹쳐 있는 화소 전극을 포함하고;상기 소스 선이 상기 박막트랜지스터의 상기 소스 영역의 콘택트부와 겹쳐 있고, 상기 제1 층이 금속으로 되어 있고, 상기 제2 층이 투명 재료로 된 것을 특징으로 하는 반도체장치.

- 제 68 항에 있어서, 상기 제1 층이 Ti 또는 Cr을 포함하는 것을 특징으로 하는 반도체장치.

- 제 68 항에 있어서, 상기 제2 층이 ITO로 된 것을 특징으로 하는 반도체장치.

- 제 68 항에 있어서, 상기 전극 패턴의 재료가 상기 화소 전극의 재료와 동일한 것을 특징으로 하는 반도체장치.

- 제 68 항에 있어서, 상기 전극 패턴과 상기 화소 전극 사이에 보조 용량이 형성된 것을 특징으로 하는 반도체장치.

- 제 68 항에 있어서, 상기 화소 전극이 투명 재료로 된 것을 특징으로 하는 반도체장치.

- 제 68 항에 있어서, 상기 박막트랜지스터가 적어도 2개의 채널 영역을 포함하는 것을 특징으로 하는 반도체장치.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050008463A KR100653409B1 (ko) | 1996-09-04 | 2005-01-31 | 반도체장치 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP8-253817 | 1996-09-04 | ||

| JP25381796A JP3634089B2 (ja) | 1996-09-04 | 1996-09-04 | 表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020050008463A Division KR100653409B1 (ko) | 1996-09-04 | 2005-01-31 | 반도체장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980024306A KR19980024306A (ko) | 1998-07-06 |

| KR100538181B1 true KR100538181B1 (ko) | 2006-04-28 |

Family

ID=17256555

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970045637A KR100538181B1 (ko) | 1996-09-04 | 1997-09-03 | 액티브매트릭스형표시장치,반도체장치및반도체표시장치 |

| KR1020050008463A KR100653409B1 (ko) | 1996-09-04 | 2005-01-31 | 반도체장치 |

| KR1020050053385A KR100700485B1 (ko) | 1996-09-04 | 2005-06-21 | 반도체장치 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020050008463A KR100653409B1 (ko) | 1996-09-04 | 2005-01-31 | 반도체장치 |

| KR1020050053385A KR100700485B1 (ko) | 1996-09-04 | 2005-06-21 | 반도체장치 |

Country Status (3)

| Country | Link |

|---|---|

| US (8) | US6115088A (ko) |

| JP (1) | JP3634089B2 (ko) |

| KR (3) | KR100538181B1 (ko) |

Families Citing this family (53)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3634089B2 (ja) * | 1996-09-04 | 2005-03-30 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US6088070A (en) | 1997-01-17 | 2000-07-11 | Semiconductor Energy Laboratory Co., Ltd. | Active matrix liquid crystal with capacitor between light blocking film and pixel connecting electrode |

| JP3784491B2 (ja) * | 1997-03-28 | 2006-06-14 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型の表示装置 |

| KR100322965B1 (ko) * | 1998-03-27 | 2002-06-20 | 주식회사 현대 디스플레이 테크놀로지 | 액정표시소자의 제조방법 |

| JP3980167B2 (ja) * | 1998-04-07 | 2007-09-26 | 株式会社日立製作所 | Tft電極基板 |

| US6493048B1 (en) * | 1998-10-21 | 2002-12-10 | Samsung Electronics Co., Ltd. | Thin film transistor array panel for a liquid crystal display and a method for manufacturing the same |

| US6617644B1 (en) | 1998-11-09 | 2003-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the same |

| KR100474003B1 (ko) * | 1998-11-27 | 2005-09-16 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 |

| US6576926B1 (en) | 1999-02-23 | 2003-06-10 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and fabrication method thereof |

| TW478014B (en) | 1999-08-31 | 2002-03-01 | Semiconductor Energy Lab | Semiconductor device and method of manufacturing thereof |

| US6646287B1 (en) | 1999-11-19 | 2003-11-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with tapered gate and insulating film |

| JP2001228457A (ja) * | 1999-12-08 | 2001-08-24 | Sharp Corp | 液晶表示装置 |

| US7023021B2 (en) * | 2000-02-22 | 2006-04-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the same |

| US6789910B2 (en) | 2000-04-12 | 2004-09-14 | Semiconductor Energy Laboratory, Co., Ltd. | Illumination apparatus |

| JP4689851B2 (ja) * | 2001-02-23 | 2011-05-25 | Nec液晶テクノロジー株式会社 | アクティブマトリクス型液晶表示装置 |

| JP2002258320A (ja) * | 2001-02-28 | 2002-09-11 | Nec Corp | 液晶表示装置 |

| KR100620847B1 (ko) * | 2001-06-05 | 2006-09-13 | 엘지.필립스 엘시디 주식회사 | 액정표시장치의 어레이기판 및 그의 제조방법 |

| KR100807582B1 (ko) * | 2001-07-30 | 2008-02-28 | 엘지.필립스 엘시디 주식회사 | 스토리지 커패시터 및 이를 구비한 액정 표시장치 |

| DE60230314D1 (de) * | 2001-11-13 | 2009-01-22 | Ibm | System und verfahren zum auswählen eines elektronischen dokuments aus einem physikalischen dokument und zum anzeigen dieses elektronischen dokuments über dieses physikalische dokument |

| KR20030042221A (ko) * | 2001-11-22 | 2003-05-28 | 삼성전자주식회사 | 액정 표시 장치용 박막 트랜지스터 기판 |

| US7079210B2 (en) * | 2001-11-22 | 2006-07-18 | Samsung Electronics Co., Ltd. | Liquid crystal display and thin film transistor array panel |

| KR100857132B1 (ko) * | 2001-12-06 | 2008-09-05 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그의 제조 방법 |

| US20030117378A1 (en) | 2001-12-21 | 2003-06-26 | International Business Machines Corporation | Device and system for retrieving and displaying handwritten annotations |

| JP2003207794A (ja) * | 2002-01-11 | 2003-07-25 | Sanyo Electric Co Ltd | アクティブマトリクス型表示装置 |

| JP4216092B2 (ja) * | 2002-03-08 | 2009-01-28 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| KR100498544B1 (ko) * | 2002-11-27 | 2005-07-01 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 및 그 제조방법 |

| US7310779B2 (en) | 2003-06-26 | 2007-12-18 | International Business Machines Corporation | Method for creating and selecting active regions on physical documents |

| KR100527195B1 (ko) * | 2003-07-25 | 2005-11-08 | 삼성에스디아이 주식회사 | 유기전계 발광표시장치 |

| TWI226712B (en) * | 2003-12-05 | 2005-01-11 | Au Optronics Corp | Pixel structure and fabricating method thereof |

| CN100399168C (zh) * | 2003-12-16 | 2008-07-02 | 友达光电股份有限公司 | 画素结构及其制造方法 |

| US7532899B2 (en) * | 2004-04-15 | 2009-05-12 | At&T Mobility Ii Llc | System for providing location-based services in a wireless network, such as locating sets of desired locations |

| US7540451B2 (en) * | 2006-09-05 | 2009-06-02 | Se-Kure Controls, Inc. | System for securing a cable to a portable article |

| JP5042662B2 (ja) * | 2007-02-21 | 2012-10-03 | 三菱電機株式会社 | 液晶表示装置及びその製造方法 |

| JP2009226115A (ja) * | 2008-03-25 | 2009-10-08 | Sri Sports Ltd | ゴルフボール |

| KR101515382B1 (ko) | 2008-08-26 | 2015-04-27 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 |

| JP5347412B2 (ja) * | 2008-10-01 | 2013-11-20 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP5589359B2 (ja) | 2009-01-05 | 2014-09-17 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| KR101643835B1 (ko) | 2009-07-10 | 2016-07-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| KR101835748B1 (ko) | 2009-10-09 | 2018-03-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 발광 표시 장치 및 이를 포함한 전자 기기 |

| US20130088660A1 (en) * | 2010-06-15 | 2013-04-11 | Sharp Kabushiki Kaisha | Thin film transistor substrate and liquid crystal display device |

| CN103137616B (zh) | 2011-11-25 | 2017-04-26 | 上海天马微电子有限公司 | Tft阵列基板及其形成方法、显示面板 |

| WO2014021356A1 (en) | 2012-08-03 | 2014-02-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| DE102013216824A1 (de) | 2012-08-28 | 2014-03-06 | Semiconductor Energy Laboratory Co., Ltd. | Halbleitervorrichtung |

| TWI611511B (zh) | 2012-08-31 | 2018-01-11 | 半導體能源研究所股份有限公司 | 半導體裝置 |

| US20140063419A1 (en) * | 2012-09-04 | 2014-03-06 | Shenzhen China Star Optoelectronics Technology Co. Ltd. | Display Panel and Liquid Crystal Display Device |

| CN111477634B (zh) | 2012-09-13 | 2023-11-14 | 株式会社半导体能源研究所 | 半导体装置 |

| KR20220145922A (ko) | 2012-12-25 | 2022-10-31 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US9905585B2 (en) | 2012-12-25 | 2018-02-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising capacitor |

| US9231002B2 (en) | 2013-05-03 | 2016-01-05 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| TWI809474B (zh) | 2013-05-16 | 2023-07-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| JP6577224B2 (ja) | 2015-04-23 | 2019-09-18 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN205789971U (zh) * | 2016-05-16 | 2016-12-07 | 京东方科技集团股份有限公司 | 薄膜晶体管阵列基板及应用其的显示装置 |

| WO2020059125A1 (ja) * | 2018-09-21 | 2020-03-26 | シャープ株式会社 | 表示装置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04278927A (ja) * | 1991-03-07 | 1992-10-05 | Sharp Corp | アクティブマトリクス表示装置 |

| JPH05142570A (ja) * | 1991-11-20 | 1993-06-11 | Sharp Corp | アクテイブマトリクス基板 |

| JPH06130418A (ja) * | 1992-10-21 | 1994-05-13 | Seiko Epson Corp | アクティブマトリクス基板 |

| KR960702117A (ko) * | 1994-02-17 | 1996-03-28 | 야즈카와 히데아키 | 액티브 매트릭스 기판 및 칼러 액정 표시 장치(Active matrix substrate and color liquid crystal display) |

Family Cites Families (68)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3307150B2 (ja) | 1995-03-20 | 2002-07-24 | ソニー株式会社 | アクティブマトリクス型表示装置 |

| FR2284984A1 (fr) * | 1974-09-13 | 1976-04-09 | Commissariat Energie Atomique | Procede de realisation de transistors m.o.s. sur isolant pour la detection de rayonnements |

| US4239346A (en) * | 1979-05-23 | 1980-12-16 | Hughes Aircraft Company | Compact liquid crystal display system |

| JPS6045219A (ja) * | 1983-08-23 | 1985-03-11 | Toshiba Corp | アクテイブマトリクス型表示装置 |

| JPS60213062A (ja) | 1984-04-09 | 1985-10-25 | Hosiden Electronics Co Ltd | 薄膜トランジスタの製造方法 |

| US4598305A (en) * | 1984-06-18 | 1986-07-01 | Xerox Corporation | Depletion mode thin film semiconductor photodetectors |

| JPS6329924A (ja) * | 1986-07-23 | 1988-02-08 | Komatsu Ltd | 半導体装置の製造方法 |

| JP2702117B2 (ja) | 1987-01-28 | 1998-01-21 | 日本電気株式会社 | 音声二重通信装置 |

| US5327001A (en) | 1987-09-09 | 1994-07-05 | Casio Computer Co., Ltd. | Thin film transistor array having single light shield layer over transistors and gate and drain lines |

| JPH01183628A (ja) | 1988-01-18 | 1989-07-21 | Matsushita Electric Ind Co Ltd | アクティブマトリックスアレイ |

| JPH0210877A (ja) * | 1988-06-29 | 1990-01-16 | Matsushita Electric Ind Co Ltd | 光学的パターン検出装置の製造方法 |

| JPH02181419A (ja) * | 1989-01-06 | 1990-07-16 | Hitachi Ltd | レーザアニール方法 |

| US5051570A (en) * | 1989-01-20 | 1991-09-24 | Nec Corporation | Liquid crystal light valve showing an improved display contrast |

| JPH02245742A (ja) * | 1989-03-17 | 1990-10-01 | Matsushita Electric Ind Co Ltd | 反射型液晶表示デバイス |

| JPH039562A (ja) * | 1989-06-07 | 1991-01-17 | Sharp Corp | 半導体装置 |

| JPH0323671A (ja) * | 1989-06-21 | 1991-01-31 | Nippon Sheet Glass Co Ltd | 集積化機能デバイス及びその製造方法並びにこのデバイスを用いた機能モジュール |

| JP2538086B2 (ja) * | 1990-01-11 | 1996-09-25 | 松下電器産業株式会社 | 液晶表示デバイスおよびその製造方法 |

| JP2622183B2 (ja) * | 1990-04-05 | 1997-06-18 | シャープ株式会社 | アクティブマトリクス表示装置 |

| US5162933A (en) * | 1990-05-16 | 1992-11-10 | Nippon Telegraph And Telephone Corporation | Active matrix structure for liquid crystal display elements wherein each of the gate/data lines includes at least a molybdenum-base alloy layer containing 0.5 to 10 wt. % of chromium |

| EP0459763B1 (en) * | 1990-05-29 | 1997-05-02 | Semiconductor Energy Laboratory Co., Ltd. | Thin-film transistors |

| US5273910A (en) * | 1990-08-08 | 1993-12-28 | Minnesota Mining And Manufacturing Company | Method of making a solid state electromagnetic radiation detector |

| US5221365A (en) * | 1990-10-22 | 1993-06-22 | Sanyo Electric Co., Ltd. | Photovoltaic cell and method of manufacturing polycrystalline semiconductive film |

| JP2772405B2 (ja) | 1990-11-22 | 1998-07-02 | 株式会社日立製作所 | 液晶表示装置 |

| KR960010723B1 (ko) * | 1990-12-20 | 1996-08-07 | 가부시끼가이샤 한도오따이 에네루기 겐큐쇼 | 전기광학장치 |

| US5289030A (en) * | 1991-03-06 | 1994-02-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with oxide layer |

| JP3277548B2 (ja) * | 1991-05-08 | 2002-04-22 | セイコーエプソン株式会社 | ディスプレイ基板 |

| US6849872B1 (en) * | 1991-08-26 | 2005-02-01 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor |

| KR940004322B1 (ko) | 1991-09-05 | 1994-05-19 | 삼성전자 주식회사 | 액정표시장치 및 그 제조방법 |

| US5191832A (en) * | 1991-09-05 | 1993-03-09 | Tsay Shih C | Tubular stuffing apparatus |

| US5317433A (en) * | 1991-12-02 | 1994-05-31 | Canon Kabushiki Kaisha | Image display device with a transistor on one side of insulating layer and liquid crystal on the other side |

| JPH05249478A (ja) * | 1991-12-25 | 1993-09-28 | Toshiba Corp | 液晶表示装置 |

| US5459595A (en) * | 1992-02-07 | 1995-10-17 | Sharp Kabushiki Kaisha | Active matrix liquid crystal display |

| US5254480A (en) * | 1992-02-20 | 1993-10-19 | Minnesota Mining And Manufacturing Company | Process for producing a large area solid state radiation detector |

| NL194848C (nl) * | 1992-06-01 | 2003-04-03 | Samsung Electronics Co Ltd | Vloeibaar-kristalindicatorinrichting. |

| US5459596A (en) * | 1992-09-14 | 1995-10-17 | Kabushiki Kaisha Toshiba | Active matrix liquid crystal display with supplemental capacitor line which overlaps signal line |

| JP2924506B2 (ja) * | 1992-10-27 | 1999-07-26 | 日本電気株式会社 | アクティブマトリックス型液晶表示装置の画素構造 |

| JP2950061B2 (ja) | 1992-11-13 | 1999-09-20 | 日本電気株式会社 | 液晶表示素子 |

| EP0598394A3 (en) * | 1992-11-16 | 1997-07-16 | Tokyo Electron Ltd | Method and apparatus for manufacturing a liquid crystal display substrate, and apparatus and method for evaluating semiconductor crystals. |

| KR960001847B1 (ko) | 1992-12-21 | 1996-02-06 | 주식회사유공 | 에틸렌-알파올레핀계 공중합체 고무의 제조방법 |

| DE69332142T2 (de) * | 1992-12-25 | 2003-03-06 | Sony Corp | Substrat mit aktiver Matrix |

| EP0642179B1 (en) * | 1993-03-23 | 1999-02-03 | TDK Corporation | Solid state imaging device and process for production thereof |

| US5719065A (en) * | 1993-10-01 | 1998-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device with removable spacers |

| US5822026A (en) * | 1994-02-17 | 1998-10-13 | Seiko Epson Corporation | Active matrix substrate and color liquid crystal display |

| JPH07302912A (ja) | 1994-04-29 | 1995-11-14 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| CN1146056C (zh) * | 1994-06-02 | 2004-04-14 | 株式会社半导体能源研究所 | 有源矩阵显示器 |

| TW289097B (ko) * | 1994-08-24 | 1996-10-21 | Hitachi Ltd | |

| JP3238020B2 (ja) | 1994-09-16 | 2001-12-10 | 株式会社東芝 | アクティブマトリクス表示装置の製造方法 |

| JPH08122768A (ja) | 1994-10-19 | 1996-05-17 | Sony Corp | 表示装置 |

| JP3081474B2 (ja) * | 1994-11-11 | 2000-08-28 | 三洋電機株式会社 | 液晶表示装置 |

| GB9424598D0 (en) * | 1994-12-06 | 1995-01-25 | Philips Electronics Uk Ltd | Semiconductor memory with non-volatile memory transistor |

| KR0169385B1 (ko) | 1995-03-10 | 1999-03-20 | 김광호 | 블랙 매트릭스 구조가 가능한 액정용 박막 트랜지스터 기판 및 그 제조방법 |

| JPH08306926A (ja) | 1995-05-07 | 1996-11-22 | Semiconductor Energy Lab Co Ltd | 液晶電気光学装置 |

| JPH0926603A (ja) * | 1995-05-08 | 1997-01-28 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| US6372534B1 (en) * | 1995-06-06 | 2002-04-16 | Lg. Philips Lcd Co., Ltd | Method of making a TFT array with photo-imageable insulating layer over address lines |

| JP3200552B2 (ja) | 1995-10-26 | 2001-08-20 | 株式会社日立製作所 | アクティブマトリクス型液晶表示装置 |

| KR0158260B1 (ko) * | 1995-11-25 | 1998-12-15 | 구자홍 | 엑티브 매트릭스 액정표시장치의 매트릭스 어레이 및 제조방법 |

| TW309633B (ko) * | 1995-12-14 | 1997-07-01 | Handotai Energy Kenkyusho Kk | |

| JPH09298305A (ja) * | 1996-05-08 | 1997-11-18 | Semiconductor Energy Lab Co Ltd | 薄膜トランジスタおよびかかる薄膜トランジスタを有する液晶表示装置 |

| JP3433779B2 (ja) | 1996-06-19 | 2003-08-04 | シャープ株式会社 | アクティブマトリクス基板およびその製造方法 |

| JP3126661B2 (ja) * | 1996-06-25 | 2001-01-22 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JPH1039333A (ja) * | 1996-07-19 | 1998-02-13 | Sharp Corp | アクティブマトリクス型表示装置およびその欠陥修正方法 |

| KR100209620B1 (ko) * | 1996-08-31 | 1999-07-15 | 구자홍 | 액정 표시 장치 및 그 제조방법 |

| JP3634089B2 (ja) * | 1996-09-04 | 2005-03-30 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP3813280B2 (ja) | 1997-01-08 | 2006-08-23 | エルジー フィリップス エルシーディー カンパニー リミテッド | 液晶表示装置および電子機器 |

| JP3784491B2 (ja) * | 1997-03-28 | 2006-06-14 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型の表示装置 |

| JPH1123671A (ja) | 1997-06-30 | 1999-01-29 | Ando Electric Co Ltd | 半導体検査装置の冷却方式 |

| CN1139837C (zh) * | 1998-10-01 | 2004-02-25 | 三星电子株式会社 | 液晶显示器用薄膜晶体管阵列基板及其制造方法 |

| KR100961847B1 (ko) | 2008-02-11 | 2010-06-08 | 이승균 | 에어 컴프레서 |

-

1996

- 1996-09-04 JP JP25381796A patent/JP3634089B2/ja not_active Expired - Fee Related

-

1997

- 1997-09-03 KR KR1019970045637A patent/KR100538181B1/ko not_active IP Right Cessation

- 1997-09-03 US US08/922,951 patent/US6115088A/en not_active Expired - Lifetime

-

2000

- 2000-04-07 US US09/546,636 patent/US6421101B1/en not_active Expired - Lifetime

-

2002

- 2002-07-15 US US10/196,878 patent/US7046313B2/en not_active Expired - Fee Related

-

2005

- 2005-01-31 KR KR1020050008463A patent/KR100653409B1/ko not_active IP Right Cessation

- 2005-03-03 US US11/069,982 patent/US7023502B2/en not_active Expired - Fee Related

- 2005-06-21 KR KR1020050053385A patent/KR100700485B1/ko not_active IP Right Cessation

-

2006

- 2006-05-09 US US11/382,412 patent/US7646022B2/en not_active Expired - Fee Related

-

2009

- 2009-11-02 US US12/610,450 patent/US7863618B2/en not_active Expired - Fee Related

-

2010

- 2010-12-30 US US12/982,255 patent/US8586985B2/en not_active Expired - Fee Related

-

2012

- 2012-08-17 US US13/587,958 patent/US8536577B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04278927A (ja) * | 1991-03-07 | 1992-10-05 | Sharp Corp | アクティブマトリクス表示装置 |

| JPH05142570A (ja) * | 1991-11-20 | 1993-06-11 | Sharp Corp | アクテイブマトリクス基板 |

| JPH06130418A (ja) * | 1992-10-21 | 1994-05-13 | Seiko Epson Corp | アクティブマトリクス基板 |

| KR960702117A (ko) * | 1994-02-17 | 1996-03-28 | 야즈카와 히데아키 | 액티브 매트릭스 기판 및 칼러 액정 표시 장치(Active matrix substrate and color liquid crystal display) |

Also Published As

| Publication number | Publication date |

|---|---|

| US7046313B2 (en) | 2006-05-16 |

| US20050151891A1 (en) | 2005-07-14 |

| KR20060086783A (ko) | 2006-08-01 |

| US7646022B2 (en) | 2010-01-12 |

| US8586985B2 (en) | 2013-11-19 |

| KR100700485B1 (ko) | 2007-03-28 |

| US8536577B2 (en) | 2013-09-17 |

| US6421101B1 (en) | 2002-07-16 |

| US20060192201A1 (en) | 2006-08-31 |

| JP3634089B2 (ja) | 2005-03-30 |

| US20110163315A1 (en) | 2011-07-07 |

| US6115088A (en) | 2000-09-05 |

| US7863618B2 (en) | 2011-01-04 |

| KR100653409B1 (ko) | 2006-12-05 |

| JPH1078593A (ja) | 1998-03-24 |

| US7023502B2 (en) | 2006-04-04 |

| US20020171780A1 (en) | 2002-11-21 |

| KR19980024306A (ko) | 1998-07-06 |

| KR20060087987A (ko) | 2006-08-03 |

| US20120305927A1 (en) | 2012-12-06 |

| US20100044714A1 (en) | 2010-02-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100538181B1 (ko) | 액티브매트릭스형표시장치,반도체장치및반도체표시장치 | |

| US5182620A (en) | Active matrix display device | |

| US5966193A (en) | LCD device having coupling capacitances and shielding films | |

| KR100501128B1 (ko) | 각 화소에 보조 용량을 구비하는 액티브 매트릭스형 표시장치 | |

| KR100305275B1 (ko) | 액티브매트릭스형표시장치 | |

| KR100250093B1 (ko) | 액티브 매트릭스 기판 및 그 제조 방법 | |

| US7379139B2 (en) | Liquid crystal display and electro-optical devices with a function element | |

| KR20050077808A (ko) | 액정 표시 장치 | |

| JPH11112002A (ja) | 半導体装置およびその製造方法 | |

| KR100471954B1 (ko) | 캐패시터, 반도체 장치, 전기 광학 장치, 캐패시터의 제조방법, 반도체 장치의 제조 방법, 전자 기기 | |

| JPH08328036A (ja) | 液晶表示装置 | |

| JPH04283729A (ja) | アクティブマトリクス表示装置 | |

| JP3830213B2 (ja) | スイッチング素子を備えた基板及び液晶表示パネル並びにそれを用いた電子機器 | |

| JP3662350B2 (ja) | 表示装置 | |

| US7354700B2 (en) | Method for manufacturing insulating resin layer, substrate for electro-optical devices, method for manufacturing electro-optical device, and electro-optical device | |

| JP2002297060A (ja) | アクティブマトリクス型表示装置 | |

| JP4411825B2 (ja) | 電気光学装置の製造方法 | |

| JPH05167072A (ja) | 薄膜トランジスタ | |

| JPH08220558A (ja) | 薄膜トランジスタ及びそれを用いたアクティブマトリクス型液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| A107 | Divisional application of patent | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20121119 Year of fee payment: 8 |

|

| FPAY | Annual fee payment |

Payment date: 20131119 Year of fee payment: 9 |

|

| FPAY | Annual fee payment |

Payment date: 20141120 Year of fee payment: 10 |

|

| LAPS | Lapse due to unpaid annual fee |