KR100516248B1 - 액티브매트릭스형 액정표시장치 및 액정표시장치 - Google Patents

액티브매트릭스형 액정표시장치 및 액정표시장치 Download PDFInfo

- Publication number

- KR100516248B1 KR100516248B1 KR1019970057605A KR19970057605A KR100516248B1 KR 100516248 B1 KR100516248 B1 KR 100516248B1 KR 1019970057605 A KR1019970057605 A KR 1019970057605A KR 19970057605 A KR19970057605 A KR 19970057605A KR 100516248 B1 KR100516248 B1 KR 100516248B1

- Authority

- KR

- South Korea

- Prior art keywords

- generating means

- film

- liquid crystal

- scanning

- line

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13452—Conductors connecting driver circuitry and terminals of panels

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13458—Terminal pads

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

- G02F1/13629—Multilayer wirings

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/09—Use of materials for the conductive, e.g. metallic pattern

Abstract

본 발명은, 액정표시장치에 관하여, 특히, 박막트랜지스터(TFT)를 사용한 액티브매트릭스형 액정표시장치에 관한 것으로서, 신호의 전송로를 형성하는 요소와의 접속부의 콘택트저항을 낮게 할 수 있는 액티브매트릭스형 액정표시장치를 제공하는 것을 목적으로 한 것이며, 그 구성에 있어서, 복수의 화소를 구성하는 액정을 함유한 액정층과, 액정층을 사이에 두고 상대향해서 배치되어서 적어도 한쪽이 투명한 1쌍의 기판과, 주사펄스를 발생하는 주사펄스발생수단과, 화상데이터를 발생하는 화상데이터발생수단과, 1쌍의 기판 중 한쪽의 기판에 분산해서 배치되어서 주사펄스발생수단에 접속된 복수의 주사선과, 복수의 주사선과 매트릭스형상으로 교차하도록 배치되어서 화상데이터발생수단에 접속된 복수의 데이터신호선을 구비하고 있는 동시에, 복수의 주사선과 복수의 데이터신호선에 의해 둘러싸인 복수의 표시영역에, 1쌍의 기판중 한쪽의 기판쪽에 배치된 투명화소전극과, 액정층을 사이에 두고 투명화소전극과 상대향해서 배치되어서 액정구동전압이 인가되는 대향전극과, 주사선과 데이터신호선 및 투명화소전극에 접속된 화소구동용 반도체능동소자와, 각 주사선과 각 데이터신호선 및 화소구동용 반도체능동소자를 각각 피복하는 절연막을 구비하고 있으며, 상기 주사선과 상기 데이터신호선에 관련되는 신호전송로를 구성하는 요소와 요소와의 접속부중 적어도 한쪽의 요소의 재료는, Nb, Mo, Ta, W 중에서 선택한 적어도 하나의 원소와 Cr과의 합금이고, 주사선과 주사펄스발생수단과는 절연막에 형성된 제 1개구부를 개재해서 접속되고, 데이터신호선과 화상데이터발생수단과는 절연막에 형성된 제 2개구부를 개재해서 접속되고, 제 1개구부에는 주사펄스발생수단에 접속된 다결정박막이 삽입되고, 제 2개구부에는 화상데이터발생수단에 접속된 다결정박막이 삽입되고, 상기 다결정박막은, 산화인듐을 주체로해서 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비저항이 6x10-4Ωcm이하인 것을 특징으로 하는 액티브매트릭스형 액정표시장치이다.

Description

본 발명은, 액정표시장치에 관한 것으로서, 특히, 박막트랜지스터(TFT)를 사용한 액티브매트릭스형 액정표시장치 및 액정표시장치에 관한 것이다.

액티브매트릭스형 액정표시장치에는 반도체능동소자(스위칭소자)로서, TFT(Thin Film Transistor)가 사용되고 있다. 이 TFT의 구조는, 일반적으로 역스태거구조가 채용되고 있으며, 기판위에 게이트전극이 형성되고, 그 위에 신호선이나 다른 전극이 형성되도록 되어 있다. 구체적으로는, 투명절연기판위에 주사신호선(게이트라인, 게이트전극과 동일) 그 상부에 게이트절연막, 이 게이트절연막상부에 반도체층, 반도체층위에 드레인전극(데이터라인) 및 소스전극이 형성되어 있고, 소스전극에는 투명한 화소전극이 접속되어 있다. 그리고 드레인전극(데이터라인)에는 영상신호전압이 공급되도록 되어 있다. 이와 같은 TFT구조를 채용한 것으로는, 예를 들면 일본국 특개평 2-48639호 공보가 알려져 있다.

한편, 액정표시장치의 기판주변부에 구동회로등을 실장하는데 있어서는, TCP(Tape Carrier Package)와 COG(Chip On Glass)의 2종류의 실장방식이 채용되고 있다. 이들의 방식중, 종래 TCP방식이 많이 채용되고 있었으나, 최근, 저코스트화, 파인피치화 등의 점에서 우위성이 유망하다고 보는 COG방식으로 이행해가고 있다.

COG방식에서는, 구동회로칩의 입력쪽단자와 기판과의 접속, 구동회로칩의 출력쪽단자와 기판과의 접속 및 기판과 외부회로에 접속된 FPC(Flexible Printed Cable)와의 접속의 합계 3종류의 접속이 있다. 그리고 각 접속부에는 이방성도전막ACF(Anisotropic Conductive Film)가 삽입되고, 이방성도전막을 개재해서 접속되도록 되어 있다. 이 경우, 접속의 신뢰성을 확보하기 위하여, 기판쪽의 배선재료에는 산화인듐을 주체로해서 산화주석이 첨가된 산화인듐주석(ITO)막이 사용되고 있다.

TFT를 사용한 액정표시장치는 액티브구동이 가능하기 때문에 표시품질이 높다고 하는 특징을 구비하고 있다. 그러나, 기판위에 TFT를 형성하는 공정이 복잡하며, 적어도 6회이상의 사진평판공정을 필요로한다. 그 이유는 TFT를 구성하는 기본요소(막)가, 주사신호선(게이트라인), 게이트절연막, 반도체층, 드레인전극(데이터라인, 통상 소스전극과 동일), 투명화소전극 및 보호성절연막의 6종류가 있으며, 각각의 막을 사진평판에 의해 패터닝하기 위해서이다. 또 어느막도 두께가 수백nm이고, 또한 패터닝된 배선의 폭은 10㎛의 오더와 미세하기 때문에, 제조공정 중에 이물이 혼입하거나 밑바탕 단차타고넘기부에 있어서의 배선(특히, 데이터라인 및 투명화소전극)에 절단등이 발생하기 쉽고, 사진평판공정에서 패턴이 정밀하게 전사되지 않으면 전극배선사이에 단락이 발생한다. 또, 공정중에 표면오염이 가해지면, 소스전극과 투명화소전극과의 사이, 기판주변의 단자부에 있어서의 게이트라인, 데이터라인과 투명화소전극과의 사이의 전기적콘택트저항이 현저하게 증대한다. 이들의 현상이 발생하면, 액정표시장치로서의 표시결함을 야기하게 된다. 즉, 기판의 수율이 저하하고, 제조코스트의 증가를 초래한다.

수율을 향상시키는 하나의 방법으로서, 종래기술에서는, TFT의 소스전극 및 드레인전극위에 층간절연막(보호성절연막)을 형성하고, 이 층간절연막속에 형성된 개구부를 개재해서 소스전극 및 드레인전극과 화소전극을 접속하는 구조가 제안되어 있다. 이 구조에 의하면, 소스전극 및 드레인전극과 투명화소전극이 동일평면 상에 있을 경우에 발생하기 쉬운 양전극간의 단락을 방지할 수 있다.

그러나, 종래기술에서는, 액정표시장치의 기판위에 구동회로나 TFT를 실장할 때에, 전기신호가 흐르는 전송로를 구성하는 각요소의 접속부의 콘택트저항을 낮게 하는 것에 대해서 충분히 배려되어 있지않고, 특히 단자접속부의 수율이 낮다고 하는 문제점이 있다. 즉, 종래기술에서는, 구동회로칩과 드레인배선을 접속하는 데 있어서, 드레인배선을 Cr로 구성하고, 구동회로칩쪽에 ITO막을 배치하고, 양자를 거의 전체면에 걸쳐서 접촉시키고, 접촉면적을 크게해서 콘택트저항을 작게하도록 하고 있다. 한편, 표시패널의 표시영역이외의 영역(주변영역)의 면적을 작게하는 것이 요구되고 있다. 이 요구에 대처하기 위하여, 콘택트부의 면적을 작게하면, ITO와 Cr과의 비(比)콘택트저항(단위면적당의 콘택트저항)이 높기 때문에, 콘택트저항을 작게할 수 없게된다. 또 콘택트부분이 증대하면, 밀봉수지중의 핀홀등의 결함을 통해서 수분이 침입하고, 또한 접합부의 열악화를 초래하기 쉽게된다.

본 발명의 목적은, 신호의 전송로를 형성하는 요소와 요소와의 접속부의 콘택트저항을 낮게할 수 있는 액티브매트릭스형 액정표시장치를 제공하는 데 있다.

본 발명의 액티브매트릭스형 액정표시장치에 의하면, 복수의 화소를 구성하는 액정을 함유한 액정층과, 액정층을 사이에 두고 상대향해서 배치되어서 적어도 한쪽이 투명한 1쌍의 기판과, 주사펄스를 발생하는 주사펄스발생수단과, 화상데이터를 발생하는 화상데이터발생수단과, 1쌍의 기판의 한쪽의 기판에 분산해서 배치되어서 주사펄스발생수단에 접속된 복수의 주사선과, 복수의 주사선과 매트릭스형상으로 교차하도록 배치되어서 화상데이터발생수단에 접속된 복수의 데이터신호선을 구비하고 있는 동시에,

복수의 주사선과 복수의 데이터신호선에 의해 둘러싸인 복수의 표시영역에,

한쌍의 기판중 한쪽의 기판측에 배치된 투명화소전극과,

액정층을 사이에 두고 투명화소전극과 상대향해서 배치되어서 액정구동전압이 인가되는 대향전극과,

주사선과 데이터신호선 및 투명화소전극에 접속된 화소구동용 반도체능동소자와, 각 주사선과 각 데이터신호선 및 화소구동용 반도체능동소자를 각각 피복하는 절연막을 구비하고 있으며,

상기 주사선과 상기 데이터신호선에 관련되는 신호전송로를 구성하는 요소와 요소와의 접속부중 적어도 한쪽의 요소의 재료는, Nb, Mo, Ta, W중에서 선택한 적어도 하나의 원소와 Cr과의 합금이고,

주사선과 주사펄스발생수단과의 절연막에 형성된 제 1개구부를 개재해서 접속되고, 데이터신호선과 화상데이터발생수단과는 절연막에 형성된 제 2개구부를 개재해서 접속되고, 제 1개구부에는 주사펄스발생수단에 접속된 다결정박막이 삽입되고, 제 2개구부에는 화상데이터발생수단에 접속된 다결정박막이 삽입되고, 상기 다결정박막은, 산화인듐을 주체로해서 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비(比)저항이 6×10-4Ωcm이하이다.

또, 본 발명의 다른 액티브매트릭스형 액정표시장치에 의하면, 복수의 화소를 구성하는 액정을 함유한 액정층과, 액정층을 사이에 두고 상대향해서 배치되어서 적어도 한쪽이 투명한 1쌍의 기판과, 주사펄스를 발생하는 주사펄스발생수단과, 화상데이터를 발생하는 화상데이터발생수단과, 1쌍의 기판의 한쪽의 기판에 분산해서 배치되어서 주사펄스발생수단에 접속된 복수의 주사선과, 복수의 주사선과 매트릭스형상으로 교차하도록 배치되어서 화상데이터발생수단에 접속된 복수의 데이터신호선을 구비하고 있는 동시에,

복수의 주사선과 복수의 데이터신호선에 의해 둘러싸인 복수의 표시영역에,

1쌍의 기판중 한쪽의 기판측에 배치된 투명화소전극과,

액정층을 사이에 두고 투명화소전극과 상대향해서 배치되어서 액정구동전압이 인가되는 대향전극과,

주사선과 데이터신호선 및 투명화소전극에 접속된 화소구동용 반도체능동소자와, 각 주사선과 각 데이터신호선 및 화소구동용 반도체능동소자를 각각 피복하는 절연막을 구비하고 있으며,

상기 주사선과, 상기 데이터신호선 및 상기 화소구동용 반도체능동소자의 전극을 구성하는 것중 적어도 하나의 재료는, Nb, Mo, Ta, W중에서 선택한 적어도 하나의 원소와 Cr과의 합금이고,

주사선과 주사펄스발생수단과는 절연막에 형성된 제 1개구부를 개재해서 접속되고, 데이터신호선과 화상데이터발생수단과는 절연막에 형성된 제 2개구부를 개재해서 접속되고, 화소구동용 반도체능동소자의 전극과 투명화소전극과는 제 3개구부를 개재해서 접속되고, 제 1개구부에는 주사펄스발생수단에 접속된 다결정박막이삽입되고, 제 2개구부에는 화상데이터를 발생수단에 접속된 다결정박막이 삽입되고, 제 3개구부에는 투명화소전극에 접속된 다결정박막이 삽입되어 있으며, 상기 다결정박막은, 산화인듐을 주체로해서 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비저항이 6×10-4Ωcm이하이다.

상기 각 액정표시장치를 구성하는 데 있어서는, 이하의 요소를 부가할 수 있다.

(1) Cr과의 합금막을 형성하는 원소의 조성은 20∼80중량%이다.

(2) 주사선과 주사펄스발생수단과는 주사선을 따라서 형성된 복수의 제1 개구부를 개재해서 형성되고, 데이터신호선과 화상데이터발생수단과는 데이터신호선을 따라서 형성된 복수의 제 2개구부를 개재해서 접속되어 있다.

(3) 제 1개구부와 제 2개구부 및 제 3개구부에 있어서의 다결정박막과 합금과의 비콘택트저항은 1×10-4Ω㎛2이하이다.

(4) 주사펄스발생수단에 속하는 선으로서 표시영역밖의 기판위에 배치되어서 주사펄스를 전송하는 주사펄스전송용 배선과 다른 부재와는 이방성도전막을 개재해서 접속되고, 화상데이터발생수단에 속하는 선으로서 표시영역밖의 기판위에 배치되어서 화상데이터를 전송하는 화상데이터전송용 배선은 다른 부재와 이방성도전막을 개재해서 접속되어 있으며, 주사펄스전송용 배선의 다른부재와의 접속면 및 화상데이터전송용 배선의 다른부재와의 접속면에는 다결정박막이 형성되고, 이 다결정박막은, 산화인듐을 주체로해서 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비저항이 6×10-4Ωcm이하이다.

상기한 수단에 의하면, 신호전송로를 구성하는 요소와 요소와의 접속부중 한쪽의 요소는, Nb, Mo, Ta, W중에서 선택한 적어도 하나의 원소와 Cr과의 합금에 의해 구성되어 있기 때문에, 접속부의 콘택트저항을 작게할 수 있고, 회로소자의 실장면적을 좁게해도, 수율의 향상을 도모할 수 있다.

이하, 본 발명의 일실시형태를 도면에 의거해서 설명한다.

(실시형태 1)

도 1은 본 발명의 제 1실시형태를 표시한 액티브매트릭스형 액정표시장치의 드레인단자부의 단면도이다. 도 1에 있어서, 투명절연기판(1))은 표시패널의 일 구성요소로서 거의 평판위에 형성되어 있으며, 이 투명절연기판(10)의 중앙부에는 표시영역(12)이 형성되고, 단부주변부에는 드레인단자부(14)가 형성되어 있다. 투명절연기판(10)의 표시영역(1)위에는 밀봉제(16)를 개재해서 컬러필터기판(18)이 장착되어 있고, 투명절연기판(10)위에는 데이터신호선으로서의 드레인배선(20)이 복수개 분산해서 실장되어 있다. 그리고 각 드레인배선(20)과 매트릭스형상으로 교차하도록 복수의 주사선(도시생략)이 절연층을 개재해서 실장되어 있으며, 각 드레인배선(20)과 신호선에 의해 둘러싸인 복수의 표시영역에는 화소에 대응해서, 투명화소전극, 대향전극, 화소구동용 반도체능동소자로서의 TFT(박막트랜지스터)등이 실장되어 있다. 또 기판(10)과 컬러기판(18)과의 사이에는 화소를 형성하는 액정을 함유한 액정층이 형성되어 있다.

한편, 드레인단자부(14)에는 COG방식에 의해, 구동회로칩(22), 단자배선(24), FPC(Flexible Printed Cable)(26)가 실장되어 있다. 구동회로칩(20)에는 시프트레지스터등의 회로소자를 구비하고, 화상데이터를 발생하는 화상데이터발생수단의 일요소로서 구성되어 있다. 그리고 구동회로칩(22)의 바닥부양쪽에 금제의 범프가 형성되어 있고, 한쪽의 범프가 이방성도전막(ACF)(28)을 개재해서 드레인배선(20)의 패드부(30)에 접속되고, 다른쪽의 범프가 이방성도전막(32)을 개재해서 단자배선(24)의 패드부(34)에 접속되어 있다. 이방성도전막(28),(32)중에는 니켈과 금이 이 순서로 도금된 플라스틱입자가 분산하고 있으며, 금의 범프와 패드부(30),(34)사이에 압력 및 열을 가하면 입자가 찌부러져, 금의 범프와 패드부(30),(34)가 전기적으로 접속되도록 되어 있다. 즉 이방성도전막(28),(32)는 수직방향으로는 도전성을 표시하고, 수평방향으로는 절연성을 표시하도록 되어있다. FPC(26)는 외부의 전원이라 타이밍회로에 접속되어 있고, FPC(26)는 바닥부에 형성된 구리의 배선패턴이 이방성도전막(28)을 개재해서 단자배선(24)의 패드부(38)에 접속되어 있다. 그리고 패드부(34),(38)의 주위에는 밀봉수지(40)가 도포되어서 외기로부터 차단되어 있다.

패드부(30)는, 도 2에 표시한 바와 같이, 산화인듐주석막(이하, ITO막이라고 칭함)(42), 보호막(44)을 구비하고 있으며, 드레인배선(20)을 피복하는 보호막(42)의 단부에 형성된 개구부(45)를 개재해서 ITO막(42)과 드레인배선(20)이 접속되어 있다. 드레인배선(20)은, 후술한 바와 같이, Cr과 Mo와의 합금에 의해 형성되어 있고, 이 합금에 의한 드레인배선(20)과 ITO막(42)을 접속하므로서, 신호전송로를 구성하는 요소와 요소와의 접속부의 콘택트저항을 작게할 수 있다. 이 ITO막(42)의 단부는 이방성도전막(28)을 개재해서 구동회로칩(22)의 범프에 접속된다. 또 ITO막(42)은, 도 3에 표시한 바와 같이, TFT소자와 함께 형성되는 투명화소전극(46)과 동일한 재료로 동일한 공정에 의해 형성되도록 되어 있다. TFT소자는 투명절연기판(10)위에 형성된 게이트전극(48), 드레인전극(50), 소스전극(52)을 구비하고 있으며, 게이트전극(48)위에 게이트절연막(54)이 형성되고, 게이트절연막(54)위에 비정질실리콘(a-Si)반도체층(56)이 형성되어 있다. 비정질실리콘반도체층(56) 위에는 비정질실리콘에 인(P)을 고농도로 도핑한 n+, a-Si층(58)이 형성되어 있고, 비정질실리콘반도체층(56)이 n+, a-Si층(58)을 개재해서 드레인전극(50)과 소스전극(52)에 접합되어 있다. 또 드레인전극(50)과 소스전극(52)은 보호막(44)에 의해 분리되어 있으며, 소스전극(52)은, 보호막(44)에 형성된 개구부(60)를 개재해서 투명화상전극(46)과 접속되어 있다. 그리고 게이트전극(48)에 인가되는 주사펄스신호에 의해서 TFT가 동작하면, 드레인전극(50)에 공급되는 화상데이터에 의한 펄스신호가 투명화소전극(46)에 인가되고, 액정에 전계가 인가되도록 되어 있다. 그리고 액정에 전계가 인가되므로써 화소부분의 투과율이 변화하고, 화상데이터에 따른 화상이 표시되도록 되어 있다.

한편, 단자배선(24)의 패드부(34),(38)는, 도 4에 표시한 바와 같이, FPC(26)로부터 타이밍신호등의 고주파신호가 입력되기 때문에, 2중구조가 채용되고 있다. 즉, 단자배선(24)는 드레인배선(20)과 동일한 재료 및 동일한 공정에 의해 형성되는 합금막(62)과, 투명화소전극(46)과 동일한 공정에 의해 형성되는 ITO막(42)으로 구성되어 있다. 합금막(62)는 Cr과 Mo와의 합금에 의해 투명절연기판(10)위에 형성되어 있고, 이 합금막(62)은 보호막(44)에 의해 피복되어 있다. 그리고 합금막(62)양쪽의 보호막(44)에는 개구부(64),(66)가 형성되어 있으며, 개구부(64),(66)에는 보호막(44)위에 적층된 ITO막(42)의 일부가 삽입되고, ITO막(42)과 합금막(62)이 개구부(64),(66)에서 접합되어 있다. 개구부(64)에 있어서의 ITO막(42)은 이방성도전막(28)을 개재해서 구동회로칩(22)의 금의 범프에 접속되고, 개구부(66)에 있어서의 ITO막(42)은 이방성도전막(36)을 개재해서 FPC(26)의 배선패턴에 접속되어 있다. 합금막(62)은 Cr과 Mo와의 합금에 이해 구성되어 있기 때문에, 합금막(62)과 ITO막(42)과의 접합부에 있어서의 콘택트저항을 작게할 수 있다. 또 합금막(62)은 개구부(64),(66)을 개재해서만 ITO막(42)과 접합되고, 그 이외의 부분은 보호막(44)에 의해 덮여지고 있기 때문에, 단자배선(24)주위를 밀봉수지에 의해 도포하므로서 수분의 침입을 2중으로 방지할 수 있다. 또 합금막(62)의 단부가 보호막(44)에 의해 피복되고, ITO막(42)과는 개구부(64),(66)를 개재해서만 접합되어 있기 때문에, 수분이 원인이 되어서 합금막(62)과 ITO막(42)과의 사이에 전지반응(부식)이 발생해서, 콘택트저항이 높아지거나, 단자배선(24)이 파단하거나 하는 것을 방지할 수 있고, 신뢰성을 높일 수 있다.

본 실시형태에 의하면, 드레인배선(20)을, Cr과 Mo와의 합금에 의해 형성하고, 드레인밴선(20)과 ITO막(42)을 접속하도록 했으므로, 회상데이터를 전송하는 신호전송로중 드레인배선(20)과 ITO막(420과의 접속부의 콘택트저항을 작게할 수 있다.

상기 실시형태에 있어서는 화상데이터를 전송하는 신호전송로를 구성하는 요소와 요소와의 접합부에 대해서 설명했으나, 주사펄스발생수단으로부터의 주사펄스를 전송하는 전송로를 구성하는 요소와 요소와의 접합부에 대해서도 상기 실시형태와 마찬가지의 구조를 채용할 수 있다. 이 경우에도 접속부의 콘택트저항을 낮게 할 수 있다.

(실시형태 2)

다음에, 드레인배선(20)과 단자배선(24)을 구성하는 막의 작성방법에 대해서 설명한다.

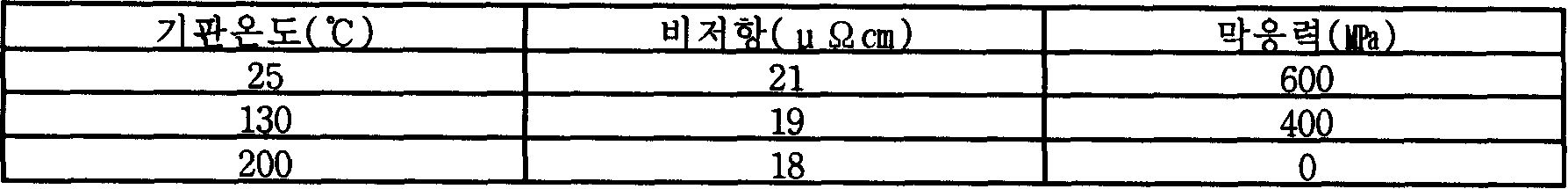

먼저, 종래형의 DC마그네트론스퍼터장치를 사용한 드레인배선(20), 단자배선(24)을 퇴적하고, 막특성을 평가했던바, 게이트배선 및 드레인배선으로서 널리사용되고 있는 Cr막에 비해서, Cr에 Mo를 첨가한 합금에서는, 막의 비저항과 막응력을 대폭적으로 저감할 수 있는 것을 알게되었다. 이어서, Cr에 Mo를 첨가한 합금과 ITO와의 콘택트특성을 평가했던바, 이 콘택트특성은, Cr막과 ITO와의 콘택트특성에 비해서 특성이 크게 향상되는 것이 발견되었다.

다음에, 이들의 식견에 의거해서, 최근 TFT용의 양산(量産)라인에서 널리 가동하게 된 클러스터타입(cluster type)DC마그네트론스퍼터장치를 사용하고, Cr-Mo 합금막을 양산품과 동일사이즈의 무알칼리봉규산유리(370mm×470mm×0.7mm(두께)위에 형성하였다. Cr-Mo합금타겟의 Mo조성은 50wt(중량)%로 하였다. 이 타겟은 50wt%Cr과 Mo분말을 혼합한 후, 캔(罐)에 봉입하여, HIP(Hot Isostatic Press)법에 의해 고형화하고, 기계가공에 의해 260mm×243mm×6mm의 크기로 성형하고, 그들 6매를 구리제뒷받침판(bcking plate)위에 맞붙인 것이다. 또 스퍼터장치의 파워는 9.6kw, 아르곤가스의 압력은 0.4Pa로 Cr-Mo합금막을 퇴적하고, 막두께를 20nm로 하였다. 또, 4점탐침법(4-point Probe method)에 의해 시트저항을 측정하고, 촉침식( 針式)프로파이러(stylus type profiler)를 사용해서 막두께를 측정하여, 이들의 측정치를 사용해서 비저항을 구했다. 또 Si웨이퍼위에 막을 작성하여, 웨이퍼의 휘어짐량을 구하고, 막응력을 계산하였다. 얻어진 결과를 다음의 표 1에 표시하였다.

또한, Cr-Mo합금막의 결과(표 1)와의 비교를 위해, 종래사용되었던 100%Cr막에 대해서 마찬가지의 실험을 행했던바, 다음의 표 2에 표시한 바와 같은 결과를 얻을 수 있었다.

표 1로부터, Cr-Mo합금막을 사용했을때에는, 기판온도의 상승에 따라서 비저항, 막응력이 함께 감소하고, 기판온도 200℃(TFT의 생성공정에 있어서의 온도에 상당)에서는 막응력이 거의 0으로 되는 것을 알 수 있다. 또 표 2에 표시한 Cr막과의 결과와 비교해도, 비저항이 낮고, 막응력이 각별히 작은 것을 알 수 있다. 또 기판온도 130℃의 경우에 대해서 더욱 검토를 진행한 결과, Cr막에서는 특성향상은 이루어지지 않았으나, Cr-Mo합금막의 경우에는, 스퍼터파워 및 압력의 최적화에 의해 비저항 18μ Ωcm, 막응력 180MPa까지 저감할 수 있었다.

다음에, 얻어진 막의 구조를 관찰하기 위하여, 기판온도를 200℃로 해서, Cr-Mo합금막과 Cr막을 주사형 전자현미경(SEM)에 의해 관찰하였다. 이 결과, Cr-Mo합금막에서는 50∼100nm의 크기의 서브그레인(Subgrain)으로 이루어진 입자직경 약 500nm의 큰 도메인(domain)구조가 인정되었다. 이 도베인구조는 하나하나가 결정입자 1개로서 행동한다고 생각된다. 또 막의 단면을 관찰한 결과, 결정입자경계가 확실하게는 인정되지 않고, 큰 결정입자가 치밀하게 충전되어 있는 것을 알 수 있다. 더욱 막의 절단면이 갈가리찢어지도록 되어 있으며, 막이 부드럽고, 바꿔말하면, 연성(延性)에 뛰어나 있는 것을 알 수 있었다. 이에 대해서, Cr막에서는, 결정입자직경은 50nm이하로 작고, 단면의 관찰로부터 결정입자경계가 확실하게 인정되었다. 따라서, Cr막에서는 작은 결정입자가 비교적 조잡하게 충전되어 있고, 연성도 작다고 판단할 수 있다.

(실시형태 3)

다음에, 실시형태 2에서 작성한 Cr-50wt%Mo합금막의 패터닝특성에 대해서 설명한다.

먼저 사진평판공정에 의해 레지스트의 배선패턴을 형성한 후, Cr용의 에칭액인 질산제2세륨암모늄15%수용액을 사용해서 에칭가고하였다. 이 에칭에는 샤워방식의 장치를 사용하였다.

다음에 형성한 Cr-Mo합금막패턴의 단면을 주사형 전자현미경에 의해 관찰하였다. 이 결과, Cr막에서는 패턴면이 거의 수직으로 서 있는데 대해서, Cr-Mo합금막에서는 테이퍼형상으로 되어 있으며, 이 테이퍼의 각도는 약 50°인 것을 알게 되었다. 또, 상세히 이 테이퍼각과 작성프로세스조건의 관계를 조사했던바, 테이퍼는, 포토레지스트의 베이킹조건과 샤워에칭의 분출압력에 의존하는 것을 알게되고, 이들을 적절히 조절하므로써, 패턴단부에 재현성좋게 테이퍼를 부여하는 것이실증되었다. 또한, Cr막의 경우에는, 테이퍼가 잘 형성할 수 없는 이유는, Cr막과 레지스트와의 밀착성이 너무 강하여, 양자의 계면에 에칭면이 침투하기 어렵다고 생각된다. Cr-Mo합금막에 있어서의 테이퍼는, 에칭액이 막과 레지스트와의 사이에 침입하고, 횡방향(막두께와 직각방향)에도 등방(等方)으로 에칭이 진행하므로써 달성된다.

(실시형태 4)

다음에, Cr막과 ITO막과의 콘택트특성 및 Cr-Mo합금막과 ITO막과의 콘택트특성에 대해서 설명한다.

먼저, 잘 세정한 유리기판위에 Cr막과 Cr-(50wt%)Mo합금막을 클러스터타입DC 마그네트론스퍼터법에 의해 퇴적한다. 이때 기판온도를 200℃ 막두께를 200nm로 하였다. 이 막을 사진평판에 의해서 다수의 배선패턴으로 가공하여, 선폭을 30㎛로하고, 선단부에는 측정용 점탐침을 세우기위한 패드를 형성하였다. Cr막과 Cr-(50wt%)Mo합금막과도 질산제2세륨암모늄수용액을 사용한 웨트(wet)에칭법에 의해서 가공하였다. 그리고 레지스트를 박리한 후, 금속배선패턴위에 층간절연막의 SiN막을 플라즈마CVD법에 의해서 형성하였다. 이때 기판온도를 300℃, 막두께를 350nm로 하였다. 다음에, 사진평판에 의해서, 금속배선위의 SiN막에 관통구멍패턴을 형성하였다. SiN막의 관통구멍은 CF4와 02의 혼합가스를 사용한 드라이에칭법에 의해서 가공하였다. 다음에 레지스트를 박리한 후, ITO막을 DC마그네트론스퍼터법(본공정에서는 종래형의 인라인식을 이용)에 의해 퇴적하였다.

다음에, 기판온도를 200℃로하고, 스퍼터가스에 Ar과 02의 혼합가스를 사용한 경우와, 기판온도를 실온으로하고, 스퍼터가스에 Ar과 H20의 혼합가스를 사용한 경우의 2종류에 대해서 검토하였다. 전자의 경우는, 퇴적한 상태에서 다결정의 ITO막(이하, P-ITO라고 칭한다), 후자의 경우에는, 퇴적한 상태에서는 비정질(amorphous)의 ITO막(이하 a-ITO라고 칭함)으로 되어 있다. 비정질의 경우에는, 나중의 공정에서 최고 240℃정도의 열이 가해지기 때문에, 결정화해서 최종적으로는 다결정이 된다. 또 막두께는 어느 경우에도 140nm로 하였다. 이어서, 사진평판에 의해서, ITO막을 패터닝하고, SiN막의 관통구멍을 개재해서 금속배선막과 +자위에 교차하는 콘택트저항의 평가패턴을 작성하였다. 그리고 Cr로부터 ITO에 대해서 전류를 흐르게 하고, 4점탐침법에 의해서, Cr막과 ITO막과의 콘택트부와, Cr-Mo합금막과 ITO막과의 콘택트부에 있어서의 전압강하V를 각각 측정하고, 이 측정결과로부터 비콘택트저항을 구했다. 이 결과를 다음의 표 3에 표시한다.

표 3으로부터, 금속막으로서 Cr-Mo합금막을 사용한 경우에는, ITO가 다결정, 비정질에 의하지 않고 비콘택트저항이 Cr의 경우보다도 낮은 것을 알 수 있다. 후술하지만, 패드부(30),(34),(38)에 있어서의 콘택트부에서는 비콘택트저항이 1×105Ω㎛2이하일 필요를 알게되었다. 따라서, Cr막의 경우에는, 콘택트특성이 불충분한 것을 알 수 있다.

또한, 상기한 비콘택트저항은, ITO막자체의 저항치에 의존하는 것을 알게 되었다. 즉, ITO막의 비저항이 6×10-4Ωm보다 큰경우에는, Cr-Mo합금막에서도, 비콘택트저항치를 1×105Ω㎛2이하로 할 수 없다. 또한, ITO막의 비저항은 ITO막의 스퍼터조건에 의해서 변화하고, 예를 들면, P-IOT의 경우에는, O2의 첨가량이 너무 많으면 상승하고, a-ITO의 경우에는, H2O의 첨가량이 너무 많으면 상승한다. 그리고 H2O의 첨가량은 Ar에 대해서 2%이하이면, 비콘택트저항을 1×105Ω㎛2이하로 할 수 있다.

(실시형태 5)

상기한 실시형태로 확립한 기술을 사용해서 액정표시장치(TFT-LCD)를 작성한 때의 표시부의 구성에 대해서 설명한다.

도 5는 액정표시장치의 표시부의 하나의 화소의 평면도이다. 또한, 작성한 디바이스의 TFT부의 구조는 도 3과 마찬가지이고, 드레인단자부는 도 2 및 도 4에 표시한 구조와 마찬가지이다. 도 5에 있어서, 드레인배선(20)과 게이트배선(68)에 의해 둘러싸인 표시영역에는 화소전극(46)이 형성되어 있는 동시에 TFT가 형성되어 있다. TFT중 소스전극(52)과 화소전극(46)과는 보호막(44)에 개구된 콘택트호올CN1을 개재해서 전기적으로 접속되어 있다. 이와 같은 구조를 채용하므로써, 다음과 같은 효과를 얻을 수 있다.

① 드레인배선(20)과 화소전극(46)을 이층화(異層化)하고 있으므로, 양자의 사이에서 단락이 발생하는 확률을 현저하게 감소시킬 수 있고, 그에 의거한 불량을 방지할 수 있다.

② 게이트전극(48), 게이트배선(68)을 사용해서 차광막(70)을 구성하고, 또한 화소전극(46)을 이위에 덮도록 형성하므로써, 드레인배선(20)과 화소전극(46)사이로부터의 광누설을 없앨 수 있다. 따라서, 투명절연기판(10)과 대향하는 컬러필터기판(18)에 형성하고 있는 블랙매트릭스를 생략할 수 있다. 이것은 투명절연기판(10)과 컬러필터기판(18)과의 위치조정(alighment)어긋남을 억제할 수 있고, 나아가서는 화소부의 개구율의 향상이 가능하게 된다.

③ ②와 마찬가지의 이유에서, 화소전극(46)과 게이트배선(68)을 평면적으로 포개므로써, 부가용량 Cadd를 형성할 수 있다(다른쪽은 게이트배선(68)과 소스전극(62)과의 포개짐에 의한 기생(寄生)용량Cgs가 된다). 이 때문에, 이부분으로부터의 광누설을 없앨 수 있고, 개구율의 향상을 도모할 수 있다.

④ 드레인배선(20)과 화소전극(46)간은, 도 3에 표시한 바와 같이, 게이트절연막(54)과 게이트절연막(54)/보호막(44)의 적층절연막이 차광막(70)을 개재해서 용량결합하게 되므로, 양전극간의 기생용량을 저감할 수 있다.

본 실시형태에 있어서의 구조를 채용했을때의 포토마스크수는, ① 게이트전극, ② n+, a-Si층(58)/비정질실리콘반도체층(56), ③ 게이트절연막(54), ④ 소스전극(52) · 드레인전극(50), ⑤ 보호막(44)(전극단자, 화소전극부에 관통구멍형성), ⑥ 화소전극(46)의 6이지만, ③을 생략하고, 이것을 ⑤의 마스크패턴을 사용해서 동시에 가공할 수도 있다. 이 경우, 포토마스크수가 5로 적어지므로, 제조패털수의 증대, 즉, 시스템효율(throughput)의 향상을 실현할 수 있다. 또, 이상에서는, TFT소자부분을 염두에 두고 설명했으나, 단자부분이 동일프로세스(하등의 부가 공정없음)에 의해 작성할 수 있는 것은 말할것도 없고, 그점이 본 발명의 특징이기도 하다.

여기서, 포토마스크수를 5로해서 작성한 TFT패널의 드레인단자부(14)의 구조를 도 6에 표시한다. 도 6에 표시한 드레인단자부(14)의 경우에는, 포토마스크수가 6인경우와 비하면 드레인배선(20)의 아래에 게이트절연막(54)이 있는 것, 또 게이트절연막(54)과 보호막(44)의 단부면이 일치하고 있는 것이다. 이들은, 상기한 바와 같이, 포토마스크를 사용한 게이트절연막의 가공을 생략하고, 게이트절열막과 보호막(44)을 동일포토마스크에 의해 일괄해서 가공하는 것에 의하고 있다.

다음에, 상기한 방법에 의해서 TFT기판을 작성하였다. 또한, ITO막(42)에는 기판온도를 200℃로하는 P-ITO막을 사용하였다. 여기서, 비교하기 위하여, 다음의 3종류를 각각 10매씩 작성하였다.

(a)에서 게이트전극: Cr-50wt%Mo합금막/소스전극·드레인전극:Cr-50wt%Mo함금막

(b)에서 게이트전극: Cr-50wt%Mo합금막/소스전극·드레인전극:Cr의 막

(c)에서 게이트전극:Cr막/소스전극·드레인전극:Cr-50wt%Mo합금막

상기 어느 금속막도 실시형태 2에 표시한 기판온도 200℃의 조건에서 퇴적하였다. 또, 실시형태 3에서 설명한 방법에 의해 에칭을 행하였다. 따라서, (a),(b)의 게이트전극에는 테이퍼가 형성되어 있고, (c)에서는 거의 수직의 패턴단부가 형성되어 있다. 이와 같은 패널작성을 진행시키는 중에, (c)에 의한 구조의 전극막퇴적시, 클러스트스퍼터장치내에서 기판의 휘어짐에 의한다고 볼 수 있는 반송트러블이 발생하였다. 그래서 주의깊게반송하므로써 기판갈라짐은 방지할 수 있었으나, 작성에는 장시간을 요했다. 이것은 Cr막의 응력이 높은 것에 기인하고 있으며, 양산에서는 시스템효율의 저하를 야기하게 된다. 이 점에서도, Cr-Mo합금막이 뛰어나고 있는 것이 표시되어 있다.

다음에, 얻어진 패널의 결함을 조사해서 결과를 다음의 표 4에 표시한다.

표 4로부터, (a)의 구조에서는, 드레인배선(20)에 단선이 있는 패널이 1매발생했으나, 이것은, 조사한 결과 CVD막속에 이물이 존재한 경우이고, 드레인배선(20)에는 문제가 없는 것이 명백하게 되었다. (b)의 구조에서는, 모든 패널에서 드레인 배선의 단선이 발생하였다. 이 소자의 단면구조를 조사한 결과, 게이트배선을 드레인배선이 타고넘는 부분에서 드레인배선의 Cr이 단선되어 있는 것을 알게 되었다. 이 이유는, Cr막에 1000MPa정도의 큰 응력이 발생하고 있으며, 그 응력의 방향이 인장이기 때문에, 단차 타고넘기부에서 배선이 절단된 것으로 생각된다. (c)의 구조에서는, 게이트배선의 단선의 발생이 2매 인정되었다. 이 원일을 조사한 결과, 유리기판에 미소한 흠이 존재하고, Cr배선의 에칭시에, 이 부분에 에칭액이 침투하여, Cr이 절단한 것으로 추정된다. Cr-Mo합금배선을 사용한 패널에서도 마찬가지의 홈이 존재하고 있으나, Cr-Mo합금막은 결정입자직경이 Cr막에 비해서 각별히 큰 것, 막의 연성(延性)이 Cr막에 비해서 큰 것이 원인으로서, 에칭시에 단선되기 어렵다고 볼 수 있다. 또 표 4로부터 (c)의 구조에서는, 게이트배선에 테이퍼가 형성되어 있지 않은데도 불구하고, 드레인배선에 단선이 발생하고 있지 않은 것을 알 수 있다. 이 일로부터, Cr-Mo합금막을 배선에 사용하므로써, 프로세스마진이 확대되는 효과를 기대할 수 있다.

이어서, 단선결함이 없었던 패널전부와 결함이 있었던 패널의 일부를 LCD공정으로 옮기고, LCD장치를 작성하였다. 즉, 컬러필터 및 공통투명전극을 가진 대향기판과 TFT패널에 각각 배향막을 형성하고, 그 표면을 러빙처리한 후, 비드를 분산한다. 그리고 밀봉제를 도포한 후, 양자를 맞붙이고, 주위를 밀봉한다. 그리고 셀로 절단후 맞붙이고, 양자의 사이에 액정을 봉입하고, 봉입구를 밀봉한다. 계속해서, 단자부의 유리를 절단한다. 그 유리표면에 편광판을 장착한다. 이렇게해서, LCD장치를 완성한 후, 백라이트를 설치해서 점등상태를 조사하였다. 그 결과, 드레인배선(20)에 Cr-Mo합금막을 사용한 패널에서는, 화소가 결락하는 점결함 및 선형상결함은 인정되지 않고, 양호한 상태인 것이 확인되었다. 점결함이 발생하지 않는 것은, 도 3 및 도 5에 있어서의 콘택트호울CN1(개구부(60))에서 소스전극(52)과 투명화소전극(46)이 전기적으로 양호한 접합상태에 있는 것을 표시하고 있다.

다음에, 패널의 단자부에 구동회로칩(22), FPC(26)를 사용해서 외부신호회로를 실장한 후, 패널을 구동하였다. 그 결과, 드레인배선에 Cr을 사용한 것에서는, 표시불균일이 발생하는 것을 알게되었다. 이 결과를 조사했던바, 단자배선부에서의 ITO/Cr의 콘택트가 불충분하고, 이 비콘택트저항이 높은 것이 원인인 것이 판명되었다. 또, 패널의 외주부에 설치한 콘택트저항평가소자를 사용해서, 표시불균일이 발생하는 임계치를 조사한 결과, 비콘택트저항이 대략 1×105Ω㎛2이하이면, 이와 같은 표시불균일이 발생하지 않는 것이 명백하게 되었다. 그리고 배선Cr-Mo합금막을 사용했을 때에는, 표시불균일이 전혀 발생하지 않았던 것은 말할 것도 없다.

다음에, 패널의 평가후, 고온고습시험에 패널을 옮기고, 여기서의 신뢰성을 평가하였다. 이 결과, 배선Cr-Mo합금막을 사용한 패널에서는, 전혀 표시품질이 저하하지 않는 것이 실증되었다.

다음에, 단자부구조의 변형예를 도 7에 표시한다. 도 7에 표시한 단자부의 구조는, 드레인배선(20)과 ITO막(42)이 거의 전체면에 걸쳐서 접합되어 있다. 단 드레인배선(20)의 양단부는 보호막(44)에 의해 피복되어 있다. 이와 같은 구조를 채용하므로써, 예를 들면 ITO막(42)의 표면에 까지 미봉수지를 통해서 외부로부터 물이 침입했다고 해도, ITO막(42)과 드레인배선(22)의 계면에 까지 물이 침입하는 것을 억제할 수 있다.

본 발명에 의한 효과를 얻을려면, 신호전송로를 구성하는 요소와 요소와의 접속부중 한쪽의 재료를, Cr과 Mo와의 합금으로하므로써, 접합부의 콘택트저항을 낮게하는 것이 기본이다. 따라서 다른 변형예로서, 게이트배선 또는/ 및 드레인배선을 적층막에 의해 구성하고, 그 최상층만, 바꿔말하면 개구부표면에만 본합금을 적용해도 효과가 달성되는 것은 말할 것도 없다. 구체적으로는, 최상층의 CrMo합금의 막두께를 20nm이상으로 형성하면, 콘택트저항이 저감되고 본 발명의 효과를 달성할 수 있는 것을 확인하였다. 또한, 후술하는 바와 같이, Cr과 Mo와의 합금 대신에, Nb, Mo, Ta, W중에서 선택한 적어도 하나의 원소와 Cr과의 합금에 의해 구성하도록 하면, 접합부의 비콘택트저항을 1×10-4Ω㎛2이하의 값으로 낮게할 수 있다.

또 Cr-Mo합금막쪽이 Cr막보다도 콘택트저항이 각별히 낮은 이유는, 막표면을 광전자분광법에 의해 조사한 결과, Cr-Mo합금막표면에 생성하는 산화막의 두께가 Cr막표면의 경우보다도 얇은 것 및 구조가 Cr막표면과는 다르기 때문이라고 추정된다.

이상의 일로부터, Cr-Mo합금막을 TFT패널의 배선막으로 사용하므로써, 공정 중 및 신뢰성시험에 있어서도 높은 수율을 실현할 수 있고, 액정표시장치의 저코스트화를 촉진할 수 있다.

(실시형태 6)

다음에, 다른 합금막의 적용에 대해서 설명한다. Cr-Mo합금막이외의 합금막을 사용하기 위하여, Cr막에, Nb, Ta 및 W를 각각 5, 10, 20, 30, 50wt%첨가한 합금막을 제작하고, 이들 합금막의 비저항과 막응력을 측정하였다. 합금막의 제작방법은 실시형태 2에서 설명한 방법과 마찬가지이다. 이들 합금막의 측정결과 중, 막응력에 대해서는, Nb의 경우, 실시형태 2에 표시한 Mo의 경우와 거의 마찬가지의 경향을 표시하였다. Ta 및 W의 경우에는, Mo보다는 적은 첨가량, 즉 10wt%정도로부터 응력의 저하가 인정되었다. 이들의 일로부터, 어느 원소라도 Cr과 합금화함으로써, Cr-Mo합금막과 마찬가지의 효과를 얻을 수 있는 것으로 판단된다. 비저항에 관해서는, 여기서 실시한 Nb, Ta 및 W의 첨가에서는, Cr-Mo합금막보다도 높게 되어버리는 것을 판명하였다. 따라서, Cr과의 합금막을 형성하는 원소로서, Nb, Ta 및 W는 매우 유효하나, 막응력과 비저항의 양쪽의 결과를 고려하면, Mo의 첨가가 가장 뛰어나 있다고 판단된다.

또한, Cr-Mo합금막의 Mo조성은, 주로 50wt%의 경우에 대해서 설명했으나, 비콘택트저항을 낮게하는 경우에는, Mo조성이 20∼80wt%의 넓은 범위의 것을 사용할 수 있다. 단, Mo조성이 증대함에 따라서, 질산제2세륨암모늄수용액을 사용한 에칭의 속도가 감소하는 것 및 Mo조성이 감소함에 따라서 막응력이 증대하는 것의 이유에 의해서, 30∼55wt%의 범위의 것을 사용하는 것이 바람직하다.

이상 설명한 바와 같이, 본 발명에 의하면, 신호전송로를 구성하는 요소와 요소와의 접속부중 한쪽의 재료를 Nb, Mo, Ta, W중에서 선택한 적어도 하나의 원소와 Cr과의 합금에 의해 구성하도록 했기 때문에, 접합부의 콘택트저항을 낮게할 수 있고, 수율의 향상에 기여할 수 있다.

도 1은 본 발명의 일실시형태를 표시한 액정표시장치의 드레인단자부의 단면도

도 2는 단자접속부의 단면도

도 3은 TFT소자의 단면도

도 4는 단자배선의 단면도

도 5는 TFT패널의 화소부의 평면도

도 6은 포토마스크수를 5로 했을때의 드레인단자의 단면도

도 7은 드레인단자부의 다른 변형예를 표시한 단면도

〈도면의 주요부분에 대한 부호의 설명〉

10: 투명절연기판 12: 표시영역

14: 드레인단자부 16: 밀봉제

18: 컬러필터기판 20: 드레인배선

22: 구동회로칩 24: 단자배선

26: FPC(Flexible Printed Cable) 28, 32, 36: 이방성도전막(ACF)

30, 34, 38: 패드부 40: 밀봉수지

42: 산화인듐주석막(ITO막) 44: 보호막

45, 60, 64, 66: 개구부 46: 투명화소전극

48: 게이트전극 50: 드레인전극

52: 소스전극 54: 게이트절연막

56: 비정질실리콘반도체층 58: n+, a-Si층

62: 합금막 68: 게이트배선

70: 차광막

Claims (23)

- 적어도 한쪽이 투명한 한 쌍의 기판과;상기 한 쌍의 기판 사이에 개재된 액정층과;주사펄스발생수단과;화상데이터발생수단과:한 쌍의 기판중 한쪽의 기판위에 분산하여 배치되고 주사펄스발생수단에 접속된 복수의 주사선과;복수의 주사선과 매트릭스형상으로 교차하도록 배치되어 화상데이터발생수단에 접속된 복수의 데이터신호선을 구비하고 있고,복수의 주사선과 복수의 데이터신호선에 의해 둘러싸인 복수의 화소에는,한 쌍의 기판중 한쪽의 기판위에 배치된 투명화소전극과;액정층을 사이에 두고 투명화소전극과 대향하여 배치되어 액정구동전압이 인가되는 대향전극과;주사선, 데이터신호선 및 투명화소전극에 접속된 각각의 화소구동용 반도체능동소자, 각각의 주사선 및 각각의 데이터신호선을 피복하는 절연막과;를 부가하여 구비하고 있는 액티브매트릭스형 액정표시장치에 있어서,주사선과 주사펄스발생수단이 접속되고, 데이터신호선과 화상데이터발생수단이 접속하는 재료형성부분은, Nb, Mo, Ta 및 W로 이루어진 군으로부터 선택된 적어도 하나의 화학원소를 함유하는 Cr 합금과 대략 유사한 조성물이며,주사선과 주사펄스발생수단과는 절연막에 형성된 제 1개구부를 개재해서 서로 접속되고, 데이터신호선과 화상데이터발생수단과는 절연막에 형성된 제 2개구부를 개재해서 서로 접속되고, 주사펄스발생수단에 접속된 다결정박막이 제 1개구부에 삽입되고, 화상데이터발생수단에 접속된 다결정박막이 제 2개구부에 삽입되고, 상기 다결정박막은 산화인듐을 주성분으로 이루어지고 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비저항이 0Ωcm보다 크고 6 x 10-4Ωcm이하인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 1항에 있어서,주사선과 주사펄스발생수단은 상기 주사선을 따라서 형성된 복수의 제 1개구부를 개재해서 접속되고,상기 데이터신호선과 상기 화상데이터발생수단은 상기 데이터신호선을 따라서 형성된 복수의 제 2개구부를 개재해서 접속되어 있는 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 1항에 있어서,제 1개구부와 제 2개구부에 있어서의 다결정박막과 합금과의 비콘택트저항은 1 x 103Ω㎛2이상 1 x 105Ω㎛2이하 인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 1항에 있어서,Cr과의 합금을 형성하는 화학원소는 20 ∼ 80중량%의 범위내에 있는 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 1항에 있어서,주사펄스발생수단에 속하는 선으로서 화소의 바깥쪽의 기판위에 배치되어서 주사펄스를 전송하는 선은, 이방성도전막을 개재해서 제 1부재와 접속하고,화상데이터발생수단에 속하는 선으로서 화소의 바깥쪽의 기판위에 배치되어 화상데이터를 전송하는 선은, 이방성도전막을 개재해서 제 2부재와 접속하고,상기 주사펄스전송용 선과 제 1부재와의 접속면 및 상기 화상데이터전송용 선과 제 2부재와의 접속면에서 각각 다결정박막이 형성되고,상기 다결정박막은, 산화인듐을 주성분으로 이루어지고 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비저항이 0Ωcm보다 크고 6 x 10-4Ωcm이하인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 1항에 있어서,상기 주사선과 데이터신호선중 적어도 하나는, 접속부 이외의 영역에서 접속부의 재료와 다른 재료로 형성되는 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 6항에 있어서,상기 다결정막은 주성분으로서의 산화인듐과 첨가물로서의 산화주석으로 구성된 ITO로 이루어진 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 6항에 있어서,상기 신호선의 일부를 형성하는 상기 다결정막은, 상기 접속부에서 상기 Cr-Mo 합금막위에 형성되는 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 6항에 있어서,상기 다결정막과 상기 Cr-Mo합금막 사이의 비콘택트저항은 1 x 103Ω㎛2이상 1 x 105Ωcm2 이하인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 적어도 한쪽이 투명한 한 쌍의 기판과;상기 한 쌍의 기판 사이에 개재된 액정층과;주사펄스발생수단과;화상데이터발생수단과;한 쌍의 기판중 한쪽의 기판위에 분산하여 배치되고 주사펄스생성수단에 접속된 복수의 주사선과;복수의 주사선과 매트릭스헝상으로 교차하도록 배치되어 화상데이터생성수단에 접속된 복수의 데이터신호선을 구비하고 있고,복수의 주사선과 복수의 데이터신호선에 의해 둘러싸인 복수의 화소에는,한 쌍의 기판중 한쪽의 기판위에 배치된 투명화소전극과;액정층을 사이에 두고 투명화소전극과 대향하여 배치되어 액정구동전압이 인가되는 대향전극과;주사선, 데이터신호선 및 투명화소전극에 접속된 각각의 화소구동용 반도체능동소자, 각각의 주사선 및 각각의 데이터신호선을 피복하는 절연막과:를 부가하여 구비하고 있는 액티브매트릭스형 액정표시장치에 있어서,주사선과 주사펄스생성수단을 접속하는 적어도 하나의 부분, 데이터신호선과 화상데이터발생수단을 접속하는 적어도 하나의 부분 및 화소구동용 상기 반도체 액티브소자로 구성된 전극과 투명화소전극을 접속하는 적어도 하나의 부분에 형성된 물질은, Nb, Mo, Ta 및 W로 이루어진 군으로부터 선택된 적어도 하나의 화학원소를 함유하는 Cr 합금과 유사한 조성물을 가지며,주사선과 주사펄스발생수단과는 절연막에 형성된 제 1개구부를 개재해서 서로 접속되고, 데이터신호선과 화상데이터발생수단과는 절연막에 형성된 제 2개구부를 개재해서 서로 접속되고, 화소구동용 반도체능동소자의 전극과 투명화소전극과는 절연막에 형성된 제 3개구를 개재해서 서로 접속하고, 주사펄스발생수단에 접속하는 다결정막은 제 1개구에 삽입되고, 화상데이터발생수단에 접속하는 다결정막은 제 2개구에 삽입되고, 투명화소전극에 접속하는 다결정박막은 제 3개구에 삽입되고, 상기 다결정박막은 산화인듐을 주성분으로 이루어지고 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비저항이 0Ωcm보다 크고 6 x 10-4Ωcm이하 인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 10항에 있어서,상기 주사선과 상기 주사펄스발생수단은 상기 주사선을 따라서 형성된 복수의 제 1개구를 개재해서 접속되고, 상기 데이터선과 상기 화상데이터발생수단은 상기 데이터선을 따라서 형성된 복수의 제 2개구를 개재하여 접속되는 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 10항에 있어서,제 1개구부와 제 2개구부에서 다결정박막과 합금과의 비콘택트저항은, 1 x 103Ω㎛2 이상 1 x 105㎛2이하 인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 10항에 있어서,제 1개구부, 제 2개구부 및 제 3개구부에서 다결정박막과 합금과의 비콘택트저항은, 1 x 103Ω㎛2 이상 1 x 105Ω㎛2 이하인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 10항에 있어서,Cr과 합금을 형성하는 화학원소는 20∼80중량%의 범위내에 있는 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 10항에 있어서,주사펄스발생수단에 속하는 선으로서 화소의 바깥쪽에 배치된 주사펄스를 전송하는 선은 이방성 도전막을 개재해서 제 1부재에 접속되고;화상데이터생성수단에 속하는 선으로서 화소의 바깥쪽에 배치된 화상데이터를 전송하는 선은 이방성도전막을 개재해서 제 2부재에 접속되고;다결정박막은, 주사펄스전송용 상기 선과 제 1부재와의 접속면 및 상기 화상데이터전송용 선과 제 2부재와의 접속면에 각각 형성되고;상기 다결정박막은, 산화인듐을 주성분으로 이루어지고 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비저항이 0Ωcm보다 크고 6 x 10-4Ω㎛이하인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 10항에 있어서,상기 주사선과 데이터신호선중 적어도 하나는, 접속부 이외의 영역에서 그 접속부의 구성하는 재료 이외의 재료로 형성되는 것을 특징으로 하는 액티브매트릭스형 액정표시장장치.

- 제 16항에 있어서,상기 ITO는 0Ωcm보다 크고 6 x 10-4Ωcm이하의 비저항을 갖는 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 적어도 한쪽이 투명한 한 쌍의 기판과;상기 한 쌍의 기판 사이에 개재된 액정층과;주사펄스발생수단과;화상데이터발생수단과;한 쌍의 기판중 한쪽의 기판위에 분산하여 배치되고 주사펄스발생수단에 접속된 복수의 주사선과;복수의 주사선과 매트릭스형상으로 교차하도록 배치되어 화상데이터발생수단에 접속된 복수의 데이터신호선을 구비하고,복수의 주사선과 복수의 데이터신호선에 의해 둘러싸인 복수의 화소에는,화소전극과 대향전극을 구비하는 한쌍의 전극과;주사선, 데이터신호선, 및 화소전극에 접속하는 각각의 화소구동용 반도체 능동소자와, 각각의 주사선 및 각각의 데이터신호선을 피복하는 절연막과;주사선과 주사펄스발생수단을 접속하고 데이터신호선과 화상데이터발생수단을 접속하는 부분을 형성하고, Nb, Mo, Ta, W로 이루어진 군으로부터 선택된 적어도 하나의 화학원소를 함유하는 Cr 합금과 대략 유사한 조성물을 가지는 물질과를 부가하여 구비하는 액티브매트릭스형 액정표시장치에 있어서,주사선과 주사펄스발생수단과는 절연막에 형성된 제 1개구부를 개재해서 서로 접속되고, 데이터신호선과 화상데이터발생수단과는 절연막에 형성된 제 2개구부를 개재해서 서로 접속되고, 주사펄스발생수단에 접속된 다결정박막은 제 1개구부에 삽입되고, 화상데이터발생수단에 접속된 다결정박막은 제 2개구부에 삽입되고, 상기 다결정박막은 산화인듐을 주성분으로 이루어지고 산화주석이 첨가된 산화인듐주석에 의해 구성되고, 비저항이 0Ωcm보다 크고 6 x 10-4Ωcm이하인 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- 제 18항에 있어서,상기 주사선과 데이터신호선 중 적어도 하나는 접속부이외의 영역에서 접속부의 재료와 상이한 재료로 형성되는 것을 특징으로 하는 액티브매트릭스형 액정표시장치.

- Cr-Mo합금막은 다결정막으로 이루어진 투명화소전극의 한쪽 단부와 트랜지스터의 소스전극을 접속하는 부분에 형성되고,다결정막으로 이루어진 신호선은 이방성 도전성막을 개재하여 기판위에 배치된 구동회로칩에 접속하는 것을 특징으로 하는 액정표시장치.

- 한 쌍의 기판과,한 쌍의 기판 사이에 개재된 액정층과,적어도 트랜지스터, 투명화소전극, 신호선 및 한 쌍의 기판 중 적어도 한쪽에 형성된 구동회로칩으로 이루어진 액정표시장치에 있어서,Cr-Mo합금막은 다결정막으로 이루어진 투명화소전극 중의 한쪽 단부와 트랜지스터의 소스전극을 접속하는 부분에 형성되고,다결정막으로 이루어진 신호선은 이방성 도전성막을 개재하여 한 쌍의 기판 중 한 쪽 기판위에 배치된 구동회로침에 접속하는 것을 특징으로 하는 액정표시장치.

- Cr-Mo합금막은 다결정막으로 이루어진 투명화소전극 중의 한쪽 단부와 트랜지스터의 소스전극을 접속하는 부분 및 다결정막으로 이루어진 데이터신호선의 한쪽 단부와 신호전극을 접속하는 부분에 형성하고,다결정막으로 이루어진 신호선은 이방성 도전성막을 개재하여 기판위에 배치된 구동회로칩에 접속하는 것을 특징으로 하는 액정표시장치.

- Cr-Mo합금막은 다결정박막으로 이루어진 투명화소전극의 한쪽 단부와 트랜지스터의 소스전극을 접속하는 부분 및 다결정막으로 이루어진 주사선의 한쪽 단부와 신호전극을 접속하는 부분에 형성되고,다결정막으로 이루어진 주사선은, 이방성 도전성막을 개재하여 기판위에 배치된 구동회로칩에 접속하는 것을 특징으로 하는 액정표시장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP96-291899 | 1996-11-01 | ||

| JP8291899A JPH10133216A (ja) | 1996-11-01 | 1996-11-01 | アクティブマトリクス型液晶表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980042033A KR19980042033A (ko) | 1998-08-17 |

| KR100516248B1 true KR100516248B1 (ko) | 2005-11-29 |

Family

ID=17774908

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970057605A KR100516248B1 (ko) | 1996-11-01 | 1997-11-01 | 액티브매트릭스형 액정표시장치 및 액정표시장치 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6226060B1 (ko) |

| JP (1) | JPH10133216A (ko) |

| KR (1) | KR100516248B1 (ko) |

| TW (1) | TW374121B (ko) |

Families Citing this family (49)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3255942B2 (ja) * | 1991-06-19 | 2002-02-12 | 株式会社半導体エネルギー研究所 | 逆スタガ薄膜トランジスタの作製方法 |

| JP3866783B2 (ja) | 1995-07-25 | 2007-01-10 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| JP2985124B2 (ja) * | 1997-06-12 | 1999-11-29 | 株式会社日立製作所 | 液晶表示装置 |

| JP4004672B2 (ja) * | 1998-12-28 | 2007-11-07 | シャープ株式会社 | 液晶表示装置用基板及びその製造方法 |

| TWI255957B (en) * | 1999-03-26 | 2006-06-01 | Hitachi Ltd | Liquid crystal display device and method of manufacturing the same |

| JP4627843B2 (ja) * | 1999-07-22 | 2011-02-09 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2001053283A (ja) | 1999-08-12 | 2001-02-23 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| KR20010080327A (ko) * | 1999-09-08 | 2001-08-22 | 모리시타 요이찌 | 표시장치 및 그 제조방법 |

| JP3670577B2 (ja) * | 2000-01-26 | 2005-07-13 | シャープ株式会社 | 液晶表示装置およびその製造方法 |

| JP2002148659A (ja) * | 2000-11-10 | 2002-05-22 | Hitachi Ltd | 液晶表示装置 |

| JP2002245947A (ja) * | 2000-12-15 | 2002-08-30 | Canon Inc | 細線を有する基板及びその製造方法及び電子源基板及び画像表示装置 |

| TW512536B (en) * | 2001-02-21 | 2002-12-01 | Au Optronics Corp | Reflective TFT-LCD having pixel electrode with coarse diffuser |

| JP2002296609A (ja) | 2001-03-29 | 2002-10-09 | Nec Corp | 液晶表示装置及びその製造方法 |

| KR100796749B1 (ko) | 2001-05-16 | 2008-01-22 | 삼성전자주식회사 | 액정 표시 장치용 박막 트랜지스터 어레이 기판 |

| KR100900536B1 (ko) * | 2001-07-16 | 2009-06-02 | 삼성전자주식회사 | 박막 트랜지스터 기판 및 그의 제조 방법 |

| JP2003098543A (ja) * | 2001-09-21 | 2003-04-03 | Seiko Epson Corp | 電気光学パネル、その製造方法および電子機器 |

| JP3603890B2 (ja) * | 2002-03-06 | 2004-12-22 | セイコーエプソン株式会社 | 電子デバイス及びその製造方法並びに電子機器 |

| JP2004219712A (ja) * | 2003-01-15 | 2004-08-05 | Toshiba Matsushita Display Technology Co Ltd | 表示パネル用配線構造 |

| JP2004247373A (ja) * | 2003-02-12 | 2004-09-02 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2004317924A (ja) | 2003-04-18 | 2004-11-11 | Advanced Display Inc | 表示装置および表示装置の製造方法 |

| US7372528B2 (en) * | 2003-06-09 | 2008-05-13 | Samsung Electronics Co., Ltd. | Array substrate, method of manufacturing the same and liquid crystal display apparatus having the same |

| KR100905662B1 (ko) * | 2003-06-26 | 2009-06-30 | 엘지디스플레이 주식회사 | 액정표시장치 제조 방법 및 배선 구조 |

| US8937580B2 (en) * | 2003-08-08 | 2015-01-20 | Semiconductor Energy Laboratory Co., Ltd. | Driving method of light emitting device and light emitting device |

| KR101006438B1 (ko) | 2003-11-12 | 2011-01-06 | 삼성전자주식회사 | 액정 표시 장치 |

| JP4202300B2 (ja) * | 2004-06-24 | 2008-12-24 | 三菱電機株式会社 | 液晶表示装置及び液晶表示装置の検査方法 |

| JP2006047827A (ja) * | 2004-08-06 | 2006-02-16 | Mitsubishi Electric Corp | 液晶表示装置およびその製造方法 |

| JP2006066676A (ja) * | 2004-08-27 | 2006-03-09 | Seiko Epson Corp | 電気光学装置及び電子機器 |

| KR101085451B1 (ko) * | 2005-02-11 | 2011-11-21 | 삼성전자주식회사 | 표시장치용 박막트랜지스터 기판과 그 제조방법 |

| JP2006309028A (ja) * | 2005-04-28 | 2006-11-09 | Sanyo Epson Imaging Devices Corp | 表示装置および表示装置の製造方法 |

| JP2005301311A (ja) * | 2005-06-27 | 2005-10-27 | Hitachi Ltd | 液晶表示装置 |

| JP4662350B2 (ja) * | 2005-07-21 | 2011-03-30 | エプソンイメージングデバイス株式会社 | 液晶表示装置及びその製造方法 |

| US8747387B2 (en) * | 2005-10-11 | 2014-06-10 | Covidien Lp | IV catheter with in-line valve and methods related thereto |

| JP4894477B2 (ja) * | 2005-12-15 | 2012-03-14 | ソニー株式会社 | 電気光学装置、実装構造体及び電子機器 |

| JP5057321B2 (ja) * | 2006-03-14 | 2012-10-24 | 株式会社ジャパンディスプレイウェスト | 表示装置の製造方法 |

| JP4952425B2 (ja) * | 2006-08-21 | 2012-06-13 | ソニー株式会社 | 液晶装置および電子機器 |

| US20090079057A1 (en) * | 2007-09-24 | 2009-03-26 | Infineon Technologies Ag | Integrated circuit device |

| JP5299768B2 (ja) * | 2009-01-26 | 2013-09-25 | Nltテクノロジー株式会社 | 薄膜トランジスタアレイ基板及びその製造方法並びに液晶表示装置 |

| JP2013029532A (ja) * | 2009-11-20 | 2013-02-07 | Sharp Corp | 液晶表示装置および液晶表示装置の製造方法 |

| JP2012073341A (ja) * | 2010-09-28 | 2012-04-12 | Hitachi Displays Ltd | 液晶表示装置 |

| CN103632972A (zh) * | 2012-08-23 | 2014-03-12 | 中国科学院微电子研究所 | 一种半导体结构及其制造方法 |

| US20140069696A1 (en) * | 2012-09-11 | 2014-03-13 | Apple Inc. | Methods and apparatus for attaching multi-layer flex circuits to substrates |

| KR102253391B1 (ko) * | 2013-11-28 | 2021-05-20 | 엘지디스플레이 주식회사 | 전자 수용체를 구비한 퀀텀로드 화합물과 이를 이용한 퀀텀로드 표시장치 |

| US9228717B2 (en) * | 2013-11-28 | 2016-01-05 | Lg Display Co., Ltd. | Quantum rod compound including electron acceptor and quantum rod luminescent display device including the same |

| JP2015129863A (ja) * | 2014-01-08 | 2015-07-16 | パナソニック液晶ディスプレイ株式会社 | 液晶表示装置及びその製造方法 |

| US9933812B2 (en) * | 2014-09-05 | 2018-04-03 | Semiconductor Energy Laboratory Co., Ltd. | Display panel, input/output device, and data processor |

| CN105304646A (zh) * | 2015-10-19 | 2016-02-03 | 京东方科技集团股份有限公司 | 阵列基板及其制造方法、显示面板、显示装置 |

| AT15220U1 (de) * | 2016-03-07 | 2017-03-15 | Ceratizit Austria Gmbh | Verfahren zur Herstellung einer Hartstoffschicht auf einem Substrat, Hartstoffschicht, Zerspanwerkzeug sowie Beschichtungsquelle |

| US9960151B2 (en) * | 2016-08-02 | 2018-05-01 | Novatek Microelectronics Corp. | Semiconductor device, display panel assembly, semiconductor structure |

| JP6729658B2 (ja) * | 2018-10-16 | 2020-07-22 | セイコーエプソン株式会社 | 液晶装置および電子機器 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5162933A (en) * | 1990-05-16 | 1992-11-10 | Nippon Telegraph And Telephone Corporation | Active matrix structure for liquid crystal display elements wherein each of the gate/data lines includes at least a molybdenum-base alloy layer containing 0.5 to 10 wt. % of chromium |

| JPH08146446A (ja) * | 1994-11-18 | 1996-06-07 | Hitachi Ltd | アクティブマトリクス型液晶表示装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4666252A (en) * | 1984-06-29 | 1987-05-19 | Energy Conversion Devices, Inc. | High yield liquid crystal display and method of making same |

| US5187604A (en) * | 1989-01-18 | 1993-02-16 | Hitachi, Ltd. | Multi-layer external terminals of liquid crystal displays with thin-film transistors |

| US5071800A (en) * | 1989-02-28 | 1991-12-10 | Tosoh Corporation | Oxide powder, sintered body, process for preparation thereof and targe composed thereof |

| JP2794499B2 (ja) * | 1991-03-26 | 1998-09-03 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| EP0534467B1 (en) * | 1991-09-26 | 1997-03-12 | Kabushiki Kaisha Toshiba | Electrode structure of a liquid crystal display device and method of manufacturing the liquid crystal display device |

| JPH05249478A (ja) * | 1991-12-25 | 1993-09-28 | Toshiba Corp | 液晶表示装置 |

| DE69303126T2 (de) * | 1992-08-19 | 1996-11-28 | Tosoh Corp | Verfahren zur Herstellung eines Indiumoxidpulvers verwendbar für einen ITO-Sinterkörper mit hoher Dichte |

| JP3098345B2 (ja) * | 1992-12-28 | 2000-10-16 | 富士通株式会社 | 薄膜トランジスタマトリクス装置及びその製造方法 |

| JPH08291899A (ja) | 1995-04-20 | 1996-11-05 | Chubu Electric Power Co Inc | 液化天然ガスの気化装置及びその冷却待機保持方法 |

| US5777710A (en) * | 1995-04-28 | 1998-07-07 | Canon Kabushiki Kaisha | Electrode substrate, making the same, liquid crystal device provided therewith, and making the same |

| US5835177A (en) * | 1995-10-05 | 1998-11-10 | Kabushiki Kaisha Toshiba | Array substrate with bus lines takeout/terminal sections having multiple conductive layers |

-

1996

- 1996-11-01 JP JP8291899A patent/JPH10133216A/ja active Pending

-

1997

- 1997-10-20 TW TW086115459A patent/TW374121B/zh not_active IP Right Cessation

- 1997-10-27 US US08/958,672 patent/US6226060B1/en not_active Expired - Lifetime

- 1997-11-01 KR KR1019970057605A patent/KR100516248B1/ko not_active IP Right Cessation

-

2001

- 2001-01-18 US US09/761,187 patent/US6587164B2/en not_active Expired - Lifetime

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5162933A (en) * | 1990-05-16 | 1992-11-10 | Nippon Telegraph And Telephone Corporation | Active matrix structure for liquid crystal display elements wherein each of the gate/data lines includes at least a molybdenum-base alloy layer containing 0.5 to 10 wt. % of chromium |

| JPH08146446A (ja) * | 1994-11-18 | 1996-06-07 | Hitachi Ltd | アクティブマトリクス型液晶表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US6587164B2 (en) | 2003-07-01 |

| US6226060B1 (en) | 2001-05-01 |

| US20010002855A1 (en) | 2001-06-07 |

| KR19980042033A (ko) | 1998-08-17 |

| JPH10133216A (ja) | 1998-05-22 |

| TW374121B (en) | 1999-11-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100516248B1 (ko) | 액티브매트릭스형 액정표시장치 및 액정표시장치 | |

| KR101002521B1 (ko) | Al합금막을 이용한 저접촉 전기 저항형 전극 및 그 제조방법 및 표시 장치 | |

| US6624864B1 (en) | Liquid crystal display device, matrix array substrate, and method for manufacturing matrix array substrate | |

| KR100375435B1 (ko) | 박막트랜지스터의제조방법및이것을이용한액정표시장치 | |

| KR101065130B1 (ko) | 표시 장치 | |

| US6184966B1 (en) | Semiconductor device and method for producing the same | |

| US6731364B2 (en) | Liquid crystal display device | |

| KR100792982B1 (ko) | 전기광학소자의 제조방법 | |

| US8039852B2 (en) | Thin film transistor for a liquid crystal device in which a sealing pattern is electrically connected to a common electrode wiring | |

| US7027043B2 (en) | Wiring substrate connected structure, and display device | |

| US6621537B1 (en) | Active matrix liquid crystal display and manufacturing method of the same | |

| EP0411726B1 (en) | A method of manufacturing flat panel display backplanes | |

| US20060275618A1 (en) | Display device | |

| KR100481344B1 (ko) | 액정 표시 장치 | |

| KR20090126052A (ko) | 박막 트랜지스터 기판 및 이를 표함하는 표시 장치 | |

| US9252161B2 (en) | Thin film transistor array substrate and manufacturing method thereof, and liquid crystal display device and manufacturing method thereof | |

| US20030112382A1 (en) | Liquid crystal display device | |

| KR20010110181A (ko) | 액정 표시 장치 | |

| US7872698B2 (en) | Liquid crystal display with structure resistant to exfoliation during fabrication | |

| KR100430744B1 (ko) | 고집적도대면적lcd디스플레이용tft패널과그제조방법및액정표시장치 | |

| KR100298239B1 (ko) | 표시장치의어레이기판,어레이기판을구비한액정표시장치및어레이기판제조방법 | |

| JPH04232922A (ja) | 液晶表示装置の製造方法 | |

| JP3484307B2 (ja) | 液晶表示装置 | |

| JPH0764109A (ja) | 液晶表示装置 | |

| JP4252126B2 (ja) | 液晶表示装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20120821 Year of fee payment: 8 |

|

| FPAY | Annual fee payment |

Payment date: 20130822 Year of fee payment: 9 |

|

| FPAY | Annual fee payment |

Payment date: 20140825 Year of fee payment: 10 |

|

| FPAY | Annual fee payment |

Payment date: 20150730 Year of fee payment: 11 |

|

| FPAY | Annual fee payment |

Payment date: 20160818 Year of fee payment: 12 |

|

| LAPS | Lapse due to unpaid annual fee |