KR100272941B1 - 반도체장치및그제조방법 - Google Patents

반도체장치및그제조방법 Download PDFInfo

- Publication number

- KR100272941B1 KR100272941B1 KR1019970023763A KR19970023763A KR100272941B1 KR 100272941 B1 KR100272941 B1 KR 100272941B1 KR 1019970023763 A KR1019970023763 A KR 1019970023763A KR 19970023763 A KR19970023763 A KR 19970023763A KR 100272941 B1 KR100272941 B1 KR 100272941B1

- Authority

- KR

- South Korea

- Prior art keywords

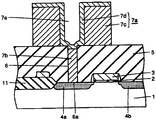

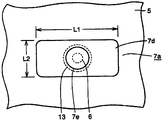

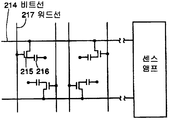

- conductive layer

- conductor portion

- insulating film

- contact hole

- opening

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

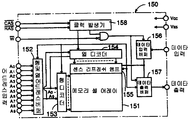

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP8343351A JPH10189898A (ja) | 1996-12-24 | 1996-12-24 | 半導体装置およびその製造方法 |

| JP96-343351 | 1996-12-24 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980063330A KR19980063330A (ko) | 1998-10-07 |

| KR100272941B1 true KR100272941B1 (ko) | 2000-11-15 |

Family

ID=18360855

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970023763A Expired - Fee Related KR100272941B1 (ko) | 1996-12-24 | 1997-06-10 | 반도체장치및그제조방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6188099B1 (enExample) |

| JP (1) | JPH10189898A (enExample) |

| KR (1) | KR100272941B1 (enExample) |

| CN (1) | CN1118874C (enExample) |

| DE (1) | DE19726069B4 (enExample) |

| TW (1) | TW365703B (enExample) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3998373B2 (ja) * | 1999-07-01 | 2007-10-24 | 株式会社ルネサステクノロジ | 半導体集積回路装置の製造方法 |

| KR100359163B1 (ko) | 1999-12-31 | 2002-10-31 | 주식회사 하이닉스반도체 | 반도체소자의 캐패시터 형성방법 |

| US6329291B1 (en) * | 2000-01-28 | 2001-12-11 | United Microelectronics Corp. | Method of forming a lower storage node of a capacitor for dynamic random access memory |

| KR100533969B1 (ko) * | 2000-10-04 | 2005-12-07 | 주식회사 하이닉스반도체 | 이너 캐패시터의 전하저장 전극 형성방법 |

| JP2003243535A (ja) * | 2002-02-15 | 2003-08-29 | Mitsubishi Electric Corp | 半導体記憶装置 |

| TWI271872B (en) * | 2002-12-30 | 2007-01-21 | Hynix Semiconductor Inc | Capacitor and method for fabricating the same |

| US20070052021A1 (en) * | 2005-08-23 | 2007-03-08 | Semiconductor Energy Laboratory Co., Ltd. | Transistor, and display device, electronic device, and semiconductor device using the same |

| JP4483896B2 (ja) * | 2007-05-16 | 2010-06-16 | ソニー株式会社 | 半導体装置及びその製造方法 |

| KR20130106151A (ko) | 2012-03-19 | 2013-09-27 | 에스케이하이닉스 주식회사 | 고종횡비 캐패시터 제조 방법 |

| JP2015028990A (ja) * | 2013-07-30 | 2015-02-12 | 株式会社東芝 | 不揮発性記憶装置 |

| TWI723848B (zh) * | 2020-04-17 | 2021-04-01 | 華邦電子股份有限公司 | 記憶體結構及其製造方法 |

| CN113555363B (zh) * | 2020-04-24 | 2023-11-07 | 华邦电子股份有限公司 | 存储器结构及其制造方法 |

| US11342332B2 (en) * | 2020-06-23 | 2022-05-24 | Winbond Electronics Corp. | Memory structure and manufacturing method therefor |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05304267A (ja) * | 1992-04-27 | 1993-11-16 | Nec Yamaguchi Ltd | 半導体集積回路装置の製造方法 |

| JPH0774325A (ja) * | 1993-06-29 | 1995-03-17 | Mitsubishi Electric Corp | 半導体記憶装置およびその製造方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5235199A (en) * | 1988-03-25 | 1993-08-10 | Kabushiki Kaisha Toshiba | Semiconductor memory with pad electrode and bit line under stacked capacitor |

| US5130885A (en) | 1991-07-10 | 1992-07-14 | Micron Technology, Inc. | Dram cell in which a silicon-germanium alloy layer having a rough surface morphology is utilized for a capacitive surface |

| JPH0555505A (ja) | 1991-08-29 | 1993-03-05 | Nec Corp | 半導体メモリセルとその形成方法 |

| JP2848135B2 (ja) | 1992-07-03 | 1999-01-20 | 日本電気株式会社 | 半導体記憶装置の製造方法 |

| US5539612A (en) | 1992-09-08 | 1996-07-23 | Texas Instruments Incorporated | Intermediate structure for forming a storage capacitor |

| JP3172321B2 (ja) | 1993-04-26 | 2001-06-04 | 三洋電機株式会社 | 半導体記憶装置の製造方法 |

| KR960011664B1 (ko) * | 1993-05-21 | 1996-08-24 | 현대전자산업 주식회사 | 반도체 장치의 캐패시터 형성방법 |

| JPH0730077A (ja) | 1993-06-23 | 1995-01-31 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP3319869B2 (ja) * | 1993-06-24 | 2002-09-03 | 三菱電機株式会社 | 半導体記憶装置およびその製造方法 |

| KR950021644A (ko) * | 1993-12-31 | 1995-07-26 | 김주용 | 반도체 기억장치 및 그 제조방법 |

| JPH07235612A (ja) * | 1994-02-23 | 1995-09-05 | Mitsubishi Electric Corp | 半導体装置のメモリセル構造 |

| US5418180A (en) * | 1994-06-14 | 1995-05-23 | Micron Semiconductor, Inc. | Process for fabricating storage capacitor structures using CVD tin on hemispherical grain silicon |

| JP2679671B2 (ja) * | 1995-03-30 | 1997-11-19 | 日本電気株式会社 | 半導体記憶装置の容量素子の製造方法 |

| US5602051A (en) * | 1995-10-06 | 1997-02-11 | International Business Machines Corporation | Method of making stacked electrical device having regions of electrical isolation and electrical connection on a given stack level |

| US5940713A (en) * | 1996-03-01 | 1999-08-17 | Micron Technology, Inc. | Method for constructing multiple container capacitor |

| US5811331A (en) * | 1996-09-24 | 1998-09-22 | Taiwan Semiconductor Manufacturing Company Ltd. | Formation of a stacked cylindrical capacitor module in the DRAM technology |

| US5668038A (en) * | 1996-10-09 | 1997-09-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | One step smooth cylinder surface formation process in stacked cylindrical DRAM products |

| US5748521A (en) * | 1996-11-06 | 1998-05-05 | Samsung Electronics Co., Ltd. | Metal plug capacitor structures for integrated circuit devices and related methods |

-

1996

- 1996-12-24 JP JP8343351A patent/JPH10189898A/ja active Pending

-

1997

- 1997-04-18 TW TW086105031A patent/TW365703B/zh active

- 1997-05-14 US US08/856,482 patent/US6188099B1/en not_active Expired - Fee Related

- 1997-06-10 KR KR1019970023763A patent/KR100272941B1/ko not_active Expired - Fee Related

- 1997-06-19 DE DE19726069A patent/DE19726069B4/de not_active Expired - Fee Related

- 1997-08-08 CN CN97116176A patent/CN1118874C/zh not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05304267A (ja) * | 1992-04-27 | 1993-11-16 | Nec Yamaguchi Ltd | 半導体集積回路装置の製造方法 |

| JPH0774325A (ja) * | 1993-06-29 | 1995-03-17 | Mitsubishi Electric Corp | 半導体記憶装置およびその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR19980063330A (ko) | 1998-10-07 |

| US6188099B1 (en) | 2001-02-13 |

| JPH10189898A (ja) | 1998-07-21 |

| DE19726069A1 (de) | 1998-07-02 |

| TW365703B (en) | 1999-08-01 |

| CN1186343A (zh) | 1998-07-01 |

| DE19726069B4 (de) | 2004-11-04 |

| CN1118874C (zh) | 2003-08-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5216266A (en) | Semiconductor memory device having memory cells formed in trench and manufacturing method therefor | |

| US5218219A (en) | Semiconductor memory device having a peripheral wall at the boundary region of a memory cell array region and a peripheral circuit region | |

| KR0123260B1 (ko) | 스택형 커패시터를 갖는 반도체 장치와 그의 제조방법 | |

| US6255684B1 (en) | DRAM cell configuration and method for its production | |

| KR930010823B1 (ko) | 반도체 기억장치 | |

| KR100272941B1 (ko) | 반도체장치및그제조방법 | |

| JP2689031B2 (ja) | 半導体記憶装置およびその製造方法 | |

| KR100251217B1 (ko) | 동적 램과 그의 제조 공정 | |

| JP2769664B2 (ja) | 半導体記憶装置およびその製造方法 | |

| JP2818964B2 (ja) | 積層構造の電荷蓄積部を有する半導体記憶装置の製造方法 | |

| US5225699A (en) | Dram having a large dielectric breakdown voltage between an adjacent conductive layer and a capacitor electrode and method of manufacture thereof | |

| US5272103A (en) | DRAM having a large dielectric breakdown voltage between an adjacent conductive layer and a capacitor electrode and method of manufacture thereof | |

| US6181014B1 (en) | Integrated circuit memory devices having highly integrated SOI memory cells therein | |

| JPH01143254A (ja) | 半導体記憶装置 | |

| US5180683A (en) | Method of manufacturing stacked capacitor type semiconductor memory device | |

| US5698878A (en) | Plate potential applying structure of trench capacitor cell | |

| US5867362A (en) | Storage capacitor for DRAM memory cell | |

| JP2715012B2 (ja) | 半導体記憶装置およびその製造方法 | |

| JP3070537B2 (ja) | 半導体装置およびその製造方法 | |

| JP3382005B2 (ja) | 半導体記憶装置及びその製造方法 | |

| JPH10284700A (ja) | 半導体集積回路装置の製造方法および半導体集積回路装置 | |

| JP2996409B2 (ja) | 半導体装置およびその製造方法 | |

| JP2827377B2 (ja) | 半導体集積回路 | |

| JPH0834299B2 (ja) | 半導体記憶装置 | |

| JPH08274276A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| T11-X000 | Administrative time limit extension requested |

St.27 status event code: U-3-3-T10-T11-oth-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20040823 Year of fee payment: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20050901 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20050901 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |