JP6798293B2 - 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 - Google Patents

炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 Download PDFInfo

- Publication number

- JP6798293B2 JP6798293B2 JP2016238507A JP2016238507A JP6798293B2 JP 6798293 B2 JP6798293 B2 JP 6798293B2 JP 2016238507 A JP2016238507 A JP 2016238507A JP 2016238507 A JP2016238507 A JP 2016238507A JP 6798293 B2 JP6798293 B2 JP 6798293B2

- Authority

- JP

- Japan

- Prior art keywords

- silicon carbide

- main surface

- dislocation

- epitaxial substrate

- single crystal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 229910010271 silicon carbide Inorganic materials 0.000 title claims description 227

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 title claims description 225

- 239000000758 substrate Substances 0.000 title claims description 140

- 238000004519 manufacturing process Methods 0.000 title claims description 31

- 238000000034 method Methods 0.000 title claims description 27

- 239000004065 semiconductor Substances 0.000 title claims description 23

- 239000013078 crystal Substances 0.000 claims description 68

- 230000002093 peripheral effect Effects 0.000 claims description 16

- 238000003491 array Methods 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 79

- 239000007789 gas Substances 0.000 description 41

- 238000006243 chemical reaction Methods 0.000 description 29

- 238000001816 cooling Methods 0.000 description 22

- 238000010438 heat treatment Methods 0.000 description 16

- KWYUFKZDYYNOTN-UHFFFAOYSA-M Potassium hydroxide Chemical compound [OH-].[K+] KWYUFKZDYYNOTN-UHFFFAOYSA-M 0.000 description 12

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 11

- 239000002994 raw material Substances 0.000 description 10

- 239000012159 carrier gas Substances 0.000 description 9

- 239000012535 impurity Substances 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 8

- 230000007246 mechanism Effects 0.000 description 8

- 230000008569 process Effects 0.000 description 8

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 7

- 230000007423 decrease Effects 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 6

- 238000005468 ion implantation Methods 0.000 description 6

- 230000004913 activation Effects 0.000 description 5

- 238000000137 annealing Methods 0.000 description 5

- 210000000746 body region Anatomy 0.000 description 5

- 235000012239 silicon dioxide Nutrition 0.000 description 5

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 4

- ATUOYWHBWRKTHZ-UHFFFAOYSA-N Propane Chemical compound CCC ATUOYWHBWRKTHZ-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 239000012298 atmosphere Substances 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 230000006698 induction Effects 0.000 description 4

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 3

- 239000002019 doping agent Substances 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 238000002360 preparation method Methods 0.000 description 3

- 239000010453 quartz Substances 0.000 description 3

- 229910000077 silane Inorganic materials 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 239000012300 argon atmosphere Substances 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910052739 hydrogen Inorganic materials 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 239000001294 propane Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 229910005883 NiSi Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- -1 for example Substances 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012774 insulation material Substances 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000005092 sublimation method Methods 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B29/00—Single crystals or homogeneous polycrystalline material with defined structure characterised by the material or by their shape

- C30B29/10—Inorganic compounds or compositions

- C30B29/36—Carbides

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

- C30B25/18—Epitaxial-layer growth characterised by the substrate

- C30B25/186—Epitaxial-layer growth characterised by the substrate being specially pre-treated by, e.g. chemical or physical means

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

- C30B25/18—Epitaxial-layer growth characterised by the substrate

- C30B25/20—Epitaxial-layer growth characterised by the substrate the substrate being of the same materials as the epitaxial layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02373—Group 14 semiconducting materials

- H01L21/02378—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/02428—Structure

- H01L21/0243—Surface structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/02433—Crystal orientation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02529—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/0257—Doping during depositing

- H01L21/02573—Conductivity type

- H01L21/02576—N-type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02609—Crystal orientation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/0445—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising crystalline silicon carbide

- H01L21/0455—Making n or p doped regions or layers, e.g. using diffusion

- H01L21/046—Making n or p doped regions or layers, e.g. using diffusion using ion implantation

- H01L21/047—Making n or p doped regions or layers, e.g. using diffusion using ion implantation characterised by the angle between the ion beam and the crystal planes or the main crystal surface

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Materials Engineering (AREA)

- Organic Chemistry (AREA)

- Metallurgy (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Inorganic Chemistry (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

- Formation Of Insulating Films (AREA)

- Recrystallisation Techniques (AREA)

Description

本開示の目的は、オフ方向に対して垂直な直線に沿って並ぶハーフループの転位列を低減可能な炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法を提供することである。

本開示によれば、オフ方向に対して垂直な直線に沿って並ぶハーフループの転位列を低減可能な炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法を提供することができる。

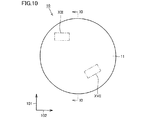

(1)本開示に係る炭化珪素エピタキシャル基板100は、炭化珪素単結晶基板10と、炭化珪素層20とを備える。炭化珪素単結晶基板10は、第1主面11を有する。炭化珪素層20は、第1主面11上にある。炭化珪素層20は、炭化珪素単結晶基板10と接する面14と反対側の第2主面30を含む。第2主面30は、{0001}面がオフ方向に傾斜した面である。第2主面30の最大径111は、100mm以上である。第2主面30は、第2主面30の外縁54から3mm以内の外周領域52と、外周領域52に取り囲まれた中央領域53とを有する。中央領域53には、オフ方向に対して垂直な直線に沿って並ぶ第1ハーフループ1の第1転位列2がある。第1ハーフループ1は、第2主面30に露出する一対の貫通刃状転位を含む。中央領域53における第1転位列2の面密度は、10本/cm2以下である。

以下、本開示の一実施形態(以下「本実施形態」とも記す)について説明する。ただし本実施形態はこれらに限定されるものではない。

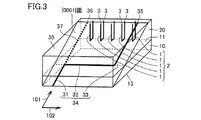

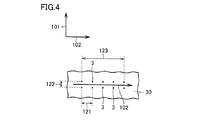

図1および図2に示されるように、本実施形態に係る炭化珪素エピタキシャル基板100は、炭化珪素単結晶基板10と、炭化珪素層20とを有している。炭化珪素単結晶基板10は、第1主面11と、第1主面11と反対側の第3主面13とを含む。炭化珪素層20は、炭化珪素単結晶基板10と接する第4主面14と、第4主面14と反対側の第2主面30を含む。炭化珪素エピタキシャル基板100は、第1方向101に延在する第1フラット(図示せず)と、第2方向102に延在する第2フラット(図示せず)を有していてもよい。第1方向101は、たとえば<11−20>方向である。第2方向102は、たとえば<1−100>方向である。

図1および図3に示されるように、中央領域53には、オフ方向に対して垂直な直線に沿って並ぶ第1ハーフループ1の第1転位列2がある。第1転位列2は、複数の第1ハーフループ1から構成されている。オフ方向が第1方向101の場合、オフ方向に対して垂直な方向は第2方向102である。第1ハーフループ1は、第2主面30に露出する一対の貫通刃状転位を含む。中央領域53における第1転位列2の面密度は、10本/cm2以下である。好ましくは、中央領域53における第1転位列2の面密度は、8本/cm2以下であり、より好ましくは5本/cm2以下である。

まず、溶融KOH(水酸化カリウム)で中央領域53がエッチングされることにより、中央領域53にエッチピットが形成される。溶融KOHの温度は、たとえば515℃である。溶融KOHによるエッチング時間は、たとえば8分である。次に、光学顕微鏡を用いて中央領域53に形成されたエッチピットが観察される。中央領域53が、たとえば格子状に1cm×1cmの正方形領域に分割される。全ての正方形領域において転位列の面密度が測定される。中央領域53における第1転位列2の面密度は、10本/cm2以下であるとは、全ての正方形領域において第1転位列2の面密度が10本/cm2以下であることを意味する。なお、中央領域53の外周付近は、ラウンド状であるため正方形の領域に分割できない。転位列の面密度の計算に際して、このような正方形の領域に分割できない領域における面密度は考慮しない。

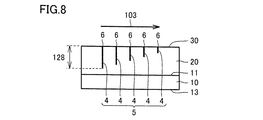

図1および図6に示されるように、中央領域53には、オフ方向に対して傾斜する直線に沿って並ぶ第2ハーフループ4の第2転位列5があってもよい。第2転位列5は、複数の第2ハーフループ4から構成されている。第2ハーフループ4は、第1方向101および第2方向102の双方に対して傾斜する直線に平行な第3方向103に沿って並んでいる。第2ハーフループ4は、第2主面30に露出する一対の貫通刃状転位を含む。中央領域53おいて、第1転位列2の面密度は、第2転位列5の面密度よりも低くてもよい。中央領域53における第2転位列5の面密度は、10本/cm2よりも高くてもよい。第1転位列2は、外周領域52の近くに多く存在し、第2転位列5は、中央領域53の中心付近に多く存在する傾向がある。

次に、本実施形態に係る炭化珪素エピタキシャル基板100の製造方法で使用される製造装置200の構成について説明する。

次に、本実施形態に係る炭化珪素エピタキシャル基板の製造方法について説明する。

図12に示されるように、成長工程終了後、冷却工程が実施される。第3時点(T3)から第7時点(T7)までが冷却工程である。冷却工程において、炭化珪素単結晶基板10と炭化珪素層20とを含む炭化珪素エピタキシャル基板100が冷却される。たとえば、第3時点(T3)から第6時点(T6)にかけて、炭化珪素エピタキシャル基板100の温度は、第1温度(A1)から第2温度(A2)まで低下する。第3時点(T3)から第6時点(T6)までの時間は、たとえば60分である。第1温度(A1)は、たとえば1600℃であり、第2温度(A2)は、たとえば100℃である。つまり、炭化珪素エピタキシャル基板100の冷却速度は、たとえば(1600−100)℃/1h=1500℃/hである。第1温度(A1)から第2温度(A2)までの冷却速度は、1500℃/h以下であってもよいし、1300℃/h以下であってもよいし、1000℃/h以下であってもよい。

次に、本実施形態に係る炭化珪素半導体装置300の製造方法について説明する。

Claims (6)

- 第1主面を有する炭化珪素単結晶基板と、

前記第1主面上の炭化珪素層とを備え、

前記炭化珪素層は、前記炭化珪素単結晶基板と接する面と反対側の第2主面を含み、

前記第2主面は、{0001}面がオフ方向に傾斜した面であり、

前記第2主面の最大径は、100mm以上であり、

前記第2主面は、前記第2主面の外縁から3mm以内の外周領域と、前記外周領域に取り囲まれた中央領域とを有し、

前記中央領域には、前記オフ方向に対して垂直な直線に沿って並ぶ第1ハーフループの第1転位列があり、

前記第1ハーフループは、前記第2主面に露出する一対の貫通刃状転位を含み、

前記中央領域における前記第1転位列の面密度は、8本/cm2以下であり、

前記中央領域には、前記オフ方向に対して傾斜する直線に沿って並ぶ第2ハーフループの第2転位列があり、

前記第2ハーフループは、前記第2主面に露出する一対の貫通刃状転位を含み、

前記中央領域おいて、前記第1転位列の面密度は、前記第2転位列の面密度よりも低い、炭化珪素エピタキシャル基板。 - 前記最大径は、150mm以上である、請求項1に記載の炭化珪素エピタキシャル基板。

- 前記オフ方向は、<11−20>方向である、請求項1または請求項2に記載の炭化珪素エピタキシャル基板。

- 前記第2主面は、(0001)面が4°以下傾斜した面である、請求項1〜請求項3のいずれか1項に記載の炭化珪素エピタキシャル基板。

- 前記第2主面は、(000−1)面が4°以下傾斜した面である、請求項1〜請求項3のいずれか1項に記載の炭化珪素エピタキシャル基板。

- 請求項1〜請求項5のいずれか1項に記載の炭化珪素エピタキシャル基板を準備する工程と、

前記炭化珪素エピタキシャル基板を加工する工程とを備える、炭化珪素半導体装置の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015199565 | 2015-10-07 | ||

| JP2015199565 | 2015-10-07 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016560603A Division JP6061060B1 (ja) | 2015-10-07 | 2016-07-04 | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020191406A Division JP7052851B2 (ja) | 2015-10-07 | 2020-11-18 | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017071551A JP2017071551A (ja) | 2017-04-13 |

| JP2017071551A5 JP2017071551A5 (ja) | 2019-07-04 |

| JP6798293B2 true JP6798293B2 (ja) | 2020-12-09 |

Family

ID=58487499

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016238507A Active JP6798293B2 (ja) | 2015-10-07 | 2016-12-08 | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 |

| JP2020191406A Active JP7052851B2 (ja) | 2015-10-07 | 2020-11-18 | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020191406A Active JP7052851B2 (ja) | 2015-10-07 | 2020-11-18 | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20170275779A1 (ja) |

| JP (2) | JP6798293B2 (ja) |

| CN (1) | CN108138360B (ja) |

| DE (1) | DE112016004600T5 (ja) |

| WO (1) | WO2017061154A1 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001189692A (ja) * | 1999-12-28 | 2001-07-10 | Matsushita Electric Ind Co Ltd | 受信装置及び利得制御方法 |

| US20170275779A1 (en) * | 2015-10-07 | 2017-09-28 | Sumitomo Electric Industries, Ltd. | Silicon carbide epitaxial substrate and method for manufacturing silicon carbide semiconductor device |

| WO2019049525A1 (ja) * | 2017-09-08 | 2019-03-14 | 住友電気工業株式会社 | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 |

| DE102018106967B3 (de) * | 2018-03-23 | 2019-05-23 | Infineon Technologies Ag | SILIZIUMCARBID HALBLEITERBAUELEMENT und Halbleiterdiode |

| CN112470255B (zh) * | 2018-07-20 | 2024-03-19 | 住友电气工业株式会社 | 碳化硅外延衬底和碳化硅半导体器件的制造方法 |

| WO2020144900A1 (ja) * | 2019-01-08 | 2020-07-16 | 住友電気工業株式会社 | 炭化珪素再生基板および炭化珪素半導体装置の製造方法 |

| JP7393900B2 (ja) * | 2019-09-24 | 2023-12-07 | 一般財団法人電力中央研究所 | 炭化珪素単結晶ウェハ及び炭化珪素単結晶インゴットの製造方法 |

| JP7319502B2 (ja) * | 2020-01-09 | 2023-08-02 | 株式会社東芝 | 炭化珪素基体の製造方法、半導体装置の製造方法、炭化珪素基体、及び、半導体装置 |

| EP3943645A1 (en) * | 2020-07-21 | 2022-01-26 | SiCrystal GmbH | Sic crystalline substrates with an optimal orientation of lattice planes for fissure reduction and method of producing same |

| EP3943644A1 (en) * | 2020-07-21 | 2022-01-26 | SiCrystal GmbH | Sic crystals with an optimal orientation of lattice planes for fissure reduction and method of producing same |

Family Cites Families (60)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US93518A (en) * | 1869-08-10 | Improvement in stuffing-boxes | ||

| US53517A (en) * | 1866-03-27 | Improvement in sealing boxes | ||

| US123502A (en) * | 1872-02-06 | Improvement in hoes | ||

| US40103A (en) * | 1863-09-29 | Improvement in quartz-crushers | ||

| US81910A (en) * | 1868-09-08 | keltum | ||

| US33503A (en) * | 1861-10-15 | Improvement in railroad-rails | ||

| US51301A (en) * | 1865-12-05 | Improvement in mowing-machines | ||

| US71301A (en) * | 1867-11-26 | Improvement in gang-ploughs | ||

| US5679153A (en) * | 1994-11-30 | 1997-10-21 | Cree Research, Inc. | Method for reducing micropipe formation in the epitaxial growth of silicon carbide and resulting silicon carbide structures |

| US6508880B2 (en) * | 2000-02-15 | 2003-01-21 | The Fox Group, Inc. | Apparatus for growing low defect density silicon carbide |

| US6863728B2 (en) * | 2001-02-14 | 2005-03-08 | The Fox Group, Inc. | Apparatus for growing low defect density silicon carbide |

| DE10247017B4 (de) * | 2001-10-12 | 2009-06-10 | Denso Corp., Kariya-shi | SiC-Einkristall, Verfahren zur Herstellung eines SiC-Einkristalls, SiC-Wafer mit einem Epitaxiefilm und Verfahren zur Herstellung eines SiC-Wafers, der einen Epitaxiefilm aufweist |

| EP1491662B1 (en) * | 2002-03-19 | 2012-02-22 | Central Research Institute of Electric Power Industry | METHOD FOR PREPARING SiC CRYSTAL |

| US6869480B1 (en) * | 2002-07-17 | 2005-03-22 | The United States Of America As Represented By The United States National Aeronautics And Space Administration | Method for the production of nanometer scale step height reference specimens |

| JP3764462B2 (ja) * | 2003-04-10 | 2006-04-05 | 株式会社豊田中央研究所 | 炭化ケイ素単結晶の製造方法 |

| US7230274B2 (en) * | 2004-03-01 | 2007-06-12 | Cree, Inc | Reduction of carrot defects in silicon carbide epitaxy |

| EP1739726A4 (en) * | 2004-03-26 | 2009-08-26 | Kansai Electric Power Co | BIPOLAR SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING SAME |

| DE102005017814B4 (de) * | 2004-04-19 | 2016-08-11 | Denso Corporation | Siliziumkarbid-Halbleiterbauelement und Verfahren zu dessen Herstellung |

| EP1619276B1 (en) * | 2004-07-19 | 2017-01-11 | Norstel AB | Homoepitaxial growth of SiC on low off-axis SiC wafers |

| US7314520B2 (en) * | 2004-10-04 | 2008-01-01 | Cree, Inc. | Low 1c screw dislocation 3 inch silicon carbide wafer |

| JP5011493B2 (ja) * | 2005-09-14 | 2012-08-29 | 関西電力株式会社 | 炭化珪素半導体素子の製造方法 |

| JP5070691B2 (ja) * | 2005-10-03 | 2012-11-14 | 住友電気工業株式会社 | 炭化珪素基板および縦型半導体装置 |

| US8455269B2 (en) * | 2006-08-04 | 2013-06-04 | Central Research Institute Of Electric Power Industry | Method for recovering an on-state forward voltage and, shrinking stacking faults in bipolar semiconductor devices, and the bipolar semiconductor devices |

| JP5273741B2 (ja) * | 2007-09-12 | 2013-08-28 | 昭和電工株式会社 | エピタキシャルSiC単結晶基板及びエピタキシャルSiC単結晶基板の製造方法 |

| US8652255B2 (en) * | 2007-10-12 | 2014-02-18 | The United States Of America, As Represented By The Secretary Of The Navy | Method of producing epitaxial layers with low basal plane dislocation concentrations |

| JP5504597B2 (ja) * | 2007-12-11 | 2014-05-28 | 住友電気工業株式会社 | 炭化ケイ素半導体装置およびその製造方法 |

| JP2010184833A (ja) * | 2009-02-12 | 2010-08-26 | Denso Corp | 炭化珪素単結晶基板および炭化珪素単結晶エピタキシャルウェハ |

| JP4978637B2 (ja) * | 2009-02-12 | 2012-07-18 | 株式会社デンソー | 炭化珪素単結晶の製造方法 |

| EP2432004A1 (en) * | 2009-05-11 | 2012-03-21 | Sumitomo Electric Industries, Ltd. | Semiconductor device |

| US9464366B2 (en) * | 2009-08-20 | 2016-10-11 | The United States Of America, As Represented By The Secretary Of The Navy | Reduction of basal plane dislocations in epitaxial SiC |

| US10256090B2 (en) * | 2009-08-20 | 2019-04-09 | The United States Of America, As Represented By The Secretary Of The Navy | Reduction of basal plane dislocations in epitaxial SiC using an in-situ etch process |

| US10256094B2 (en) * | 2009-08-20 | 2019-04-09 | The Government Of The United States Of America, As Represented By The Secretary Of The Navy | Reduction of basal plane dislocations in epitaxial SiC using an in-situ etch process |

| JP4959763B2 (ja) * | 2009-08-28 | 2012-06-27 | 昭和電工株式会社 | SiCエピタキシャルウェハ及びその製造方法 |

| JP4887418B2 (ja) * | 2009-12-14 | 2012-02-29 | 昭和電工株式会社 | SiCエピタキシャルウェハの製造方法 |

| JP4850960B2 (ja) * | 2010-04-07 | 2012-01-11 | 新日本製鐵株式会社 | エピタキシャル炭化珪素単結晶基板の製造方法 |

| WO2011142074A1 (ja) * | 2010-05-10 | 2011-11-17 | 三菱電機株式会社 | 炭化珪素エピタキシャルウエハ及びその製造方法、エピタキシャル成長用炭化珪素バルク基板及びその製造方法並びに熱処理装置 |

| JP4880052B2 (ja) * | 2010-05-11 | 2012-02-22 | 新日本製鐵株式会社 | エピタキシャル炭化珪素単結晶基板及びその製造方法 |

| JP5276068B2 (ja) * | 2010-08-26 | 2013-08-28 | 株式会社豊田中央研究所 | SiC単結晶の製造方法 |

| SE1051137A1 (sv) * | 2010-10-29 | 2012-04-30 | Fairchild Semiconductor | Förfarande för tillverkning av en kiselkarbid bipolär transistor och kiselkarbid bipolär transistor därav |

| FR2969815B1 (fr) * | 2010-12-27 | 2013-11-22 | Soitec Silicon On Insulator Tech | Procédé de fabrication d'un dispositif semi-conducteur |

| CN103370454B (zh) * | 2011-04-21 | 2015-09-09 | 新日铁住金株式会社 | 外延碳化硅单晶基板及其制造方法 |

| JP6025306B2 (ja) * | 2011-05-16 | 2016-11-16 | 株式会社豊田中央研究所 | SiC単結晶、SiCウェハ及び半導体デバイス |

| JP5958949B2 (ja) * | 2011-05-26 | 2016-08-02 | 一般財団法人電力中央研究所 | 炭化珪素基板、炭化珪素ウェハ、炭化珪素ウェハの製造方法及び炭化珪素半導体素子 |

| EP2752508A4 (en) * | 2011-08-29 | 2015-02-25 | Nippon Steel & Sumitomo Metal Corp | SILICON CARBIDE CRYSTAL WAFERS AND MANUFACTURING METHOD THEREFOR |

| JP5961357B2 (ja) * | 2011-09-09 | 2016-08-02 | 昭和電工株式会社 | SiCエピタキシャルウェハ及びその製造方法 |

| US9885124B2 (en) * | 2011-11-23 | 2018-02-06 | University Of South Carolina | Method of growing high quality, thick SiC epitaxial films by eliminating silicon gas phase nucleation and suppressing parasitic deposition |

| JP5750363B2 (ja) * | 2011-12-02 | 2015-07-22 | 株式会社豊田中央研究所 | SiC単結晶、SiCウェハ及び半導体デバイス |

| US8860040B2 (en) * | 2012-09-11 | 2014-10-14 | Dow Corning Corporation | High voltage power semiconductor devices on SiC |

| JP2014146748A (ja) * | 2013-01-30 | 2014-08-14 | Toshiba Corp | 半導体装置及びその製造方法並びに半導体基板 |

| JP6090998B2 (ja) * | 2013-01-31 | 2017-03-08 | 一般財団法人電力中央研究所 | 六方晶単結晶の製造方法、六方晶単結晶ウエハの製造方法 |

| JP2014175412A (ja) * | 2013-03-07 | 2014-09-22 | Toshiba Corp | 半導体基板及び半導体装置 |

| US8940614B2 (en) * | 2013-03-15 | 2015-01-27 | Dow Corning Corporation | SiC substrate with SiC epitaxial film |

| CN103280502B (zh) * | 2013-05-23 | 2016-12-28 | 安徽三安光电有限公司 | 发光器件及其制作方法 |

| JP6183010B2 (ja) * | 2013-07-03 | 2017-08-23 | 住友電気工業株式会社 | 炭化珪素単結晶基板およびその製造方法 |

| JP6311384B2 (ja) * | 2014-03-24 | 2018-04-18 | 三菱電機株式会社 | 炭化珪素半導体装置の製造方法 |

| JP2015199565A (ja) | 2014-04-07 | 2015-11-12 | 株式会社小森コーポレーション | シート検出装置 |

| US9425262B2 (en) * | 2014-05-29 | 2016-08-23 | Fairchild Semiconductor Corporation | Configuration of portions of a power device within a silicon carbide crystal |

| JP2016166112A (ja) * | 2015-03-10 | 2016-09-15 | 株式会社東芝 | 半導体基板及び半導体装置 |

| JP6584253B2 (ja) * | 2015-09-16 | 2019-10-02 | ローム株式会社 | SiCエピタキシャルウェハ、SiCエピタキシャルウェハの製造装置、SiCエピタキシャルウェハの製造方法、および半導体装置 |

| US20170275779A1 (en) | 2015-10-07 | 2017-09-28 | Sumitomo Electric Industries, Ltd. | Silicon carbide epitaxial substrate and method for manufacturing silicon carbide semiconductor device |

-

2016

- 2016-07-04 US US15/503,919 patent/US20170275779A1/en not_active Abandoned

- 2016-07-04 DE DE112016004600.6T patent/DE112016004600T5/de active Pending

- 2016-07-04 CN CN201680057722.8A patent/CN108138360B/zh active Active

- 2016-07-04 WO PCT/JP2016/069801 patent/WO2017061154A1/ja active Application Filing

- 2016-12-08 JP JP2016238507A patent/JP6798293B2/ja active Active

-

2020

- 2020-11-18 JP JP2020191406A patent/JP7052851B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017071551A (ja) | 2017-04-13 |

| CN108138360B (zh) | 2020-12-08 |

| US20170275779A1 (en) | 2017-09-28 |

| DE112016004600T5 (de) | 2018-06-21 |

| JP2021035905A (ja) | 2021-03-04 |

| CN108138360A (zh) | 2018-06-08 |

| JP7052851B2 (ja) | 2022-04-12 |

| WO2017061154A1 (ja) | 2017-04-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7052851B2 (ja) | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 | |

| US10697086B2 (en) | Method for manufacturing silicon carbide epitaxial substrate, method for manufacturing silicon carbide semiconductor device, and apparatus for manufacturing silicon carbide epitaxial substrate | |

| WO2017138247A1 (ja) | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 | |

| JP6856156B2 (ja) | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 | |

| JP6891758B2 (ja) | 炭化珪素エピタキシャル基板及び炭化珪素半導体装置の製造方法 | |

| JP6954316B2 (ja) | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 | |

| JP7415558B2 (ja) | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 | |

| WO2020039684A1 (ja) | 炭化珪素エピタキシャル基板の製造方法および炭化珪素半導体装置の製造方法 | |

| JP6090552B1 (ja) | 炭化珪素エピタキシャル基板の製造方法、炭化珪素半導体装置の製造方法および炭化珪素エピタキシャル基板の製造装置 | |

| JP6233555B1 (ja) | 炭化珪素エピタキシャル基板及び炭化珪素半導体装置の製造方法 | |

| JP6791348B2 (ja) | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 | |

| JP7371632B2 (ja) | 炭化珪素エピタキシャル基板の製造方法および炭化珪素半導体装置の製造方法 | |

| JP6061060B1 (ja) | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 | |

| WO2017051611A1 (ja) | 炭化珪素エピタキシャル基板の製造方法、炭化珪素半導体装置の製造方法および炭化珪素エピタキシャル基板の製造装置 | |

| JP6973600B2 (ja) | 炭化珪素エピタキシャル基板および炭化珪素半導体装置の製造方法 | |

| JP2020009941A (ja) | 炭化珪素エピタキシャル基板の製造方法および炭化珪素半導体装置の製造方法 | |

| JP2020009940A (ja) | 炭化珪素エピタキシャル基板の製造方法および炭化珪素半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190529 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190529 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200526 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200623 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20201020 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20201102 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6798293 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |