JP5665263B2 - 半導体記憶装置、及び該半導体記憶装置のテスト方法 - Google Patents

半導体記憶装置、及び該半導体記憶装置のテスト方法 Download PDFInfo

- Publication number

- JP5665263B2 JP5665263B2 JP2008143580A JP2008143580A JP5665263B2 JP 5665263 B2 JP5665263 B2 JP 5665263B2 JP 2008143580 A JP2008143580 A JP 2008143580A JP 2008143580 A JP2008143580 A JP 2008143580A JP 5665263 B2 JP5665263 B2 JP 5665263B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- input

- memory device

- semiconductor memory

- test

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/1201—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details comprising I/O circuitry

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/56—External testing equipment for static stores, e.g. automatic test equipment [ATE]; Interfaces therefor

- G11C2029/5602—Interface to device under test

Description

テスター90は、半導体記憶装置91にクロック信号、アドレス信号及び読み出しや書き込み等の動作を示すコマンド信号を含む制御信号を出力し、32個の入出力ピンを用いて半導体記憶装置91のデータ入出力端子とデータの入出力を行う。

例えば、256個の入出力端子を備えるテスターは、4ビット幅のデータ入出力端子を備える半導体記憶装置を64個同時にテストを行える。しかし、32ビット幅のデータ入出力端子を備える半導体記憶装置をテストする場合、同時にテストできる個数は8個となり、8分の1になってしまう。

テスター90は、半導体記憶装置93にクロック信号及びデータの読み出しを示す制御信号を出力する。半導体記憶装置93において、制御回路931は、入力されるクロック信号及びデータの読み出しを示す制御信号に基づいて、メモリ部932に記憶されているデータをシリアル・パラレル変換回路933に出力させる。

また、制御回路931は、シリアル・パラレル変換回路933に入力されたデータ信号を比較回路934に出力させる。

このように、半導体記憶装置93とテスター90との間で実動作速度、例えば、533MHzや666MHzのように高速なデータの入出力を行わずとも、メモリ部932の入出力データが経由するシリアル・パラレル変換回路933を、実動作速度など、でテストを行うことができる。

(1)また、本発明は、データを記憶するメモリ部と、n(n≧2)個のデータ入出力端子を介してnビット幅のデータを前記メモリ部に クロック信号に同期して入出力する手段(制御回路11、21、31及びループバック回路14、24、34)と、前記n個のデータ入出力端子のうちの予め選択されたm(m≦n)個のデータ入出力端子を介して前記メモリ部にデータを入出力する手段(制御回路11、21、31及びループバック回路14、24、34)と、前記メモリ部の任意の記憶領域から順次前記nビット幅でデータを読み出し、読み出した該nビット幅のデータを前記記憶領域とは異なる記憶領域に記憶させるループバック回路と、を備えることを特徴とする半導体記憶装置である。

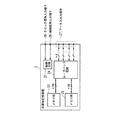

図1は、第1実施形態における半導体記憶装置1の構成を示す概略ブロック図である。半導体記憶装置1は、制御回路11、メモリ部12、ループバック回路14、クロック信号が入力されるクロック信号入力端子15、制御信号が入力される制御信号入力端子16及び32ビット幅のデータ入出力端子17を有している。

また、ループバック回路14は、メモリ部12からクロック信号の立下りに同期して入力される64ビット幅のデータを2つの32ビット幅のデータに分け、分けたデータの一方をクロックの立上がりに同期してデータ入出力端子17に出力し、分けたデータの他方をクロック信号の立下りに同期してデータ入出力端子17に出力する。

また、ループバック回路14は、メモリ部12から入力される64ビット幅のデータをメモリ部12へ出力するループバックを行う。このループバック回路14の動作は、制御回路11が選択する。また、ループバック回路14は、半導体記憶装置1の故障検出を行う動作テストモードの読み出し動作において、メモリ部12から入力される64ビット幅のデータから順に4ビットのデータを選択し、選択した4ビットのデータをデータ入出力端子17のうちの予め選択された4つの端子から出力する。

また、ループバック回路14は、動作テストのテストデータの書き込み及び読み出しの際に用いる64ビット幅のバッファ・レジスタを有している。

ループバック・ブロック100は、制御部101、バッファ102、103、ラッチ104、フリップ・フロップ105、106、108、109、プログラマブル遅延素子107、セレクタ110、クロック信号入力端子111、データ入出力端子112、制御信号端子113、内部データ入出力端子114、115を有している。

制御信号端子113には、読み出し動作及び書き込み動作を示す信号、及びプログラマブル遅延素子107の遅延時間を選択する信号を含む制御信号が入力される。

データ入出力端子112は、32ビット幅のデータが入出力される端子であり、データ入出力端子17に接続される。

クロック信号入力端子111は、クロック信号入力端子15に接続される。

フリップ・フロップ108は、入力されたクロック信号の立下りに同期して、内部データ入出力端子114から入力される32ビットのデータを記憶する。

フリップ・フロップ105は、データ入出力端子112又はセレクタ110から入力される32ビットのデータを遅延クロックの立上がりに同期して記憶する。

バッファ103は、メモリ部12にデータを記憶させる書き込み動作において、フリップ・フロップ106から入力されるデータを内部データ出力端子115に出力する。また、制御部101は、メモリ部12が記憶するデータを出力する読み出し期間において、バッファ103の出力をハイ・インピーダンス状態にする。バッファ103の動作の切替えは、制御部101により行われる。

制御部101は、制御信号端子113を介して制御回路11から入力される読み出し動作及び書き込み動作を示す信号に基づいて、セレクタ110及びバッファ102、103の出力を制御する。

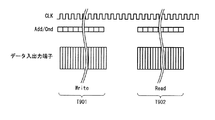

まず、時刻t0において、制御回路11は、データを書き込む領域を示すアドレス信号を含む書き込みコマンド(Write)が、制御信号入力端子16(Add/Cmdと図示)を介して入力されると、入力された書き込みコマンドをデコードした信号を制御信号端子113に出力する。制御部101は、制御信号端子113から入力される信号をデコードして、セレクタ110の出力をハイ・インピーダンスにする。

フリップ・フロップ106は、データ入出力端子112から入力されているデータDw2を遅延クロック信号の立下りに同期して記憶する。また、フリップ・フロップ106は、記憶したデータをバッファ103に出力する。バッファ103は、入力された信号を内部データ出力信号端子115(RWbus)に出力する。

まず、時刻t0において、制御回路11は、読み出すデータが記憶されている領域を示すアドレス信号を含む読み出しコマンド(Read)が、制御信号入力端子16(Add/Cmdと図示)から入力されると、入力された読み出しコマンドをデコードした信号を制御信号端子113に出力する。制御部101は、制御信号端子113から入力される信号をデコードして、バッファ102、103の出力をハイ・インピーダンスにする。

まず、時刻t0において、制御回路11は、読み出すデータが記憶されている領域を示すアドレス信号を含む読み出しコマンド(Read)が、制御信号入力端子16(Add/Cmdと図示)から入力されると、入力された読み出しコマンドをデコードした信号を制御信号端子113に出力する。制御部101は、制御信号端子113から入力される信号をデコードして、バッファ102、103の出力をハイ・インピーダンスにする。

次に、時刻t3において、制御回路11は、データを書き込む領域を示すアドレス信号を含む書き込みコマンド(Write)が、制御信号入力端子16(Add/Cmdと図示)を介して入力されると、入力された書き込みコマンドをデコードした信号を制御信号端子113に出力する。

フリップ・フロップ106は、遅延クロック信号の立下りに同期して、セレクタ110が出力するデータDr1を記憶する。

時刻t8において、ラッチ104は、遅延クロックの立上がりに同期してフリップ・フロップ105から入力されているデータDr1をラッチする。

マンドのCLと書き込みコマンドのデータを入力するタイミング(レイテンシ)に基づいて定められる。

図4(a)は、半導体記憶装置1が、データ入出力端子17のうち予め選択された4個の端子であるテスト兼用端子を介してデータの入出力を行う動作テストにおける動作を示している。データ入出力端子17とループバック回路14との間の破線は、有効なデータが入出力されていないことを示している。実線で接続されているテスト兼用端子を介した4ビット幅のデータによる読み出し及び書き込みは、例えば、次のようにして行う。

なお、図6(b)に示すように、T111で図示される半導体記憶装置1にテストデータを書き込む際の書き込みコマンド、及びT113で図示される半導体記憶装置1からテストデータを読み出す際の読み出しコマンドを、半導体記憶装置1の実動作速度よりも遅いクロック周波数を用いて行ってもよい。この場合、高速にデータの入出力が行えるI/O端子を有する高精度のテスターを用いることなく、半導体記憶装置1の実動作速度でのテストを行うことが可能となる。

上述したように、データ入出力端子17からテスター90との接続に用いる端子の選択は、クロック信号を分配するクロックツリーの構成に基づいて行う。

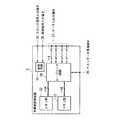

図8は、第2実施形態における半導体記憶装置2の構成を示す概略ブロック図である。半導体記憶装置2は、制御回路21、メモリ部22、23、ループバック回路24、クロック信号が入力されるクロック信号入力端子25、制御信号が入力される制御信号入力端子26及び32ビット幅のデータ入出力端子27を有している。

また、ループバック回路24は、メモリ部22、23からクロック信号の立下りに同期して入力される64ビット幅のデータを2つの32ビット幅のデータに分け、分けたデータの一方をクロックの立上がりに同期してデータ入出力端子27に出力し、分けたデータの他方をクロック信号の立下りに同期してデータ入出力端子27に出力する。

図9(a)は、半導体記憶装置2が、データ入出力端子27のうち予め選択された4個の端子であるテスト兼用端子を介してデータの入出力を行う動作テストにおける動作を示している。データ入出力端子27とループバック回路24との間の破線は、有効なデータが入出力されていないことを示している。

なお、半導体記憶装置2は、メモリ部23から64ビット幅のデータを読み出し、読み出した64ビット幅のデータをメモリ部22に書き込む動作テストも行う。

図11は、第3実施形態における半導体記憶装置3の構成を示す概略ブロック図である。半導体記憶装置3は、制御回路31、メモリ部32、33、ループバック回路34、クロック信号が入力されるクロック信号入力端子35、制御信号が入力される制御信号入力端子36、32ビット幅のデータ入出力端子37、及びテストデータ専用端子39を有している。

また、ループバック回路34は、メモリ部32、33からクロック信号の立下りに同期して入力される64ビット幅のデータを2つの32ビット幅のデータに分け、分けたデータの一方をクロックの立上がりに同期してデータ入出力端子37に出力し、分けたデータの他方をクロック信号の立下りに同期してデータ入出力端子37に出力する。

更に、ループバック回路34は、テストデータ専用端子39と接続され、動作テストのテストデータの入出力をテストデータ専用端子39を介して行う。

また、ループバック回路34は、メモリ部32、33から入力される64ビット幅のデータをメモリ部32、33へ出力するループバックを行う。このループバック回路34の動作は、制御回路31が選択する。

また、半導体記憶装置3は、第2実施形態の半導体記憶装置2と比べ、テストデータの入出力をデータ入出力端子37を用いずに、テストデータ専用端子39を用いて行う構成となっている。

また、テスターと半導体記憶装置との間で実動作速度のような高速なデータ転送を行わずとも、半導体記憶装置のメモリ部に対してデータの読み出し及び書き込みを行う実動作速度による高速な動作テストを行うことが可能になる。

この結果、テスターが目的とする動作テストの周波数でデータの入出力は行えなくとも、目的の周波数のクロック信号が出力できれば、高速に動作する半導体記憶装置の故障検出のための動作テストを行うことが可能となる。このようなテスターは、高速にデータの入出力が行えるテスターに比べ安価であるため半導体記憶装置のコストの削減に効果的である。

11、21、31・・・制御回路

12、13、22、23、32、33・・・メモリ部

14、24、34・・・ループバック回路

15、25、35・・・クロック信号入力端子

16、26、36・・・制御信号入力端子

17、27、37・・・データ入出力端子

39・・・テストデータ専用端子

90・・・テスター

100・・・ループバック・ブロック

101・・・制御部、102、103…バッファ、104…ラッチ

105、106、108、109・・・フリップ・フロップ

107・・・プログラマブル遅延素子

110・・・セレクタ、

111・・・クロック信号入力端子、112…データ入出力端子

113・・・制御信号端子

114、115・・・内部データ入出力端子

Claims (11)

- 第1メモリ部と、

第1ビット数からなる第1データと、

前記第1ビット数より小さい第2ビット数からなる第2データと、

制御回路と、を備え、

前記制御回路は、複数の前記第2データに基づいて前記第1データを生成し、前記生成された第1データを前記第1メモリ部に並列して書き込み、

さらに、第2メモリ部と、を備え、

前記制御回路は、

前記第1メモリ部に書き込まれた前記第1データのビットを前記第1メモリ部から並列して読み出し、

前記第1メモリ部から読み出された前記第1データに基づいて前記第1ビット数を有する第3データを生成し、

前記生成された第3データのビットを前記第2メモリ部に並列して書き込む、ことを特徴とする半導体記憶装置。 - 前記第2ビット数と同数のビット数からなる第4データと、を備え、

前記制御回路は、

前記第2メモリ部に書き込まれた前記第3データのビットを前記第2メモリ部から読み出し、

前記読み出された第3データに基づいて複数の前記第4データを生成し、

さらに、前記半導体記憶装置の故障検出テストとして前記第4データを所定のデータと一致するか否かをテストするテスターに、前記生成された複数の前記第4データをそれぞれ出力する、ことを特徴とする請求項1に記載の半導体記憶装置。 - 前記第2データ又は前記第4データを前記半導体記憶装置へ入出力するように構成した入出力端子を含み、

前記第1メモリ部は、前記第1データを第1メモリ部へ入出力するように構成した第1内部端子を含み、

前記第2メモリ部は、前記第3データを第2メモリ部へ入出力するように構成した第2内部端子を含み、

前記第1内部端子及び前記第2内部端子の数は、前記入出力端子の数より大きいことを特徴とする請求項2に記載の半導体記憶装置。 - 前記半導体記憶装置に供給されるリードコマンド及びライトコマンドを備え、

前記リードコマンドが前記半導体記憶装置に供給された後に前記ライトコマンドが前記半導体記憶装置に供給される場合に、

前記制御回路は、

前記ライトコマンドが前記半導体記憶装置に供給された後に、前記半導体記憶装置に供給されたリードコマンドを受け取るのに応じて前記第1メモリ部から前記第1データのビットを読み出し、

前記読み出しの後、前記半導体記憶装置に供給されたライトコマンドを受け取るのに応じて前記第2メモリ部へ前記第3データのビットを書き込むことを特徴とする請求項3に記載の半導体記憶装置。 - 前記第1データの前記第1ビット数は、複数の前記第2データの総ビット数と同数であることを特徴とする請求項4に記載の半導体記憶装置。

- データを記憶するメモリ部と、

n(n≧2)個のデータ入出力端子を介してnビット幅のデータを前記メモリ部にクロック信号に同期して入出力する手段と、

前記n個のデータ入出力端子のうちの予め選択されたm(m≦n)個のデータ入出力端子を介して前記メモリ部にデータを入出力する手段と、

前記メモリ部の任意の記憶領域から順次前記nビット幅でデータを読み出し、前記読み出した該nビット幅のデータを前記記憶領域とは異なる記憶領域に記憶させるループバック回路と、

を備えることを特徴とする半導体記憶装置。 - 前記メモリ部は、前記nビット幅のデータの読み出し及び書き込みを独立に行うメモリブロックを複数有し、

前記ループバック回路は、前記メモリブロックから入力されるnビット幅のデータを異なる前記メモリブロックへ出力する

ことを特徴とする請求項6に記載の半導体記憶装置。 - 前記半導体記憶装置は、

書き込みコマンドが読み出しコマンド入力後予め定められたクロックサイクル経過後に入力されると、前記読み出しコマンドで指定される前記メモリ部の記憶領域から前記nビット幅のデータを読み出すと共に、前記ループバック回路を使用して読み出した該データを前記書き込みコマンドで指定される前記メモリ部の記憶領域に記憶させる

ことを特徴とする請求項7に記載の半導体記憶装置。 - 前記データ入出力端子は、データの入出力を行うデータ端子と共に、前記半導体記憶装置の故障検出テスト用データの入出力のみを行うテストデータ専用端子とを含み、

前記nビット幅のデータは、前記テストデータ専用端子を介して入力されたデータである

ことを特徴とする請求項8に記載の半導体記憶装置。 - 半導体記憶装置におけるテスト方法であって、

テスターからのテストデータの入出力としてはテストデータ専用端子のみ使用し、

前記テスターが、前記テストデータ専用端子から前記テストデータを入力し、メモリ部の第1の記憶領域に記憶させるテストデータ入力過程と、

前記メモリ部の前記第1の記憶領域から前記テストデータを読み出すと共に、ループバック回路を使用して読み出した該テストデータを前記メモリ部の前記第1の記憶領域とは異なる第2の記憶領域に記憶させる動作テスト過程と、

前記テスターが、前記メモリ部の前記第2の記憶領域から前記テストデータを前記テストデータ専用端子から読み出し、読み出した該テストデータが予め定めたデータと一致するか否かにより前記半導体記憶装置の故障を検出するテストデータ出力過程と

を有することを特徴とするテスト方法。 - 前記テストデータ入力過程又は前記テストデータ出力過程における前記半導体記憶装置に入力されるクロック信号の周波数は、前記動作テスト過程における前記半導体記憶装置に入力されるクロック周波数より遅い

ことを特徴とする請求項10に記載のテスト方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008143580A JP5665263B2 (ja) | 2008-05-30 | 2008-05-30 | 半導体記憶装置、及び該半導体記憶装置のテスト方法 |

| US12/260,842 US7911861B2 (en) | 2008-05-30 | 2008-10-29 | Semiconductor memory device and method of testing semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008143580A JP5665263B2 (ja) | 2008-05-30 | 2008-05-30 | 半導体記憶装置、及び該半導体記憶装置のテスト方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009289374A JP2009289374A (ja) | 2009-12-10 |

| JP2009289374A5 JP2009289374A5 (ja) | 2011-03-17 |

| JP5665263B2 true JP5665263B2 (ja) | 2015-02-04 |

Family

ID=41379626

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008143580A Expired - Fee Related JP5665263B2 (ja) | 2008-05-30 | 2008-05-30 | 半導体記憶装置、及び該半導体記憶装置のテスト方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7911861B2 (ja) |

| JP (1) | JP5665263B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009301612A (ja) * | 2008-06-10 | 2009-12-24 | Elpida Memory Inc | 半導体記憶装置 |

| JP5579972B2 (ja) * | 2008-08-01 | 2014-08-27 | ピーエスフォー ルクスコ エスエイアールエル | 半導体記憶装置及び半導体記憶装置のテスト方法 |

| US8607104B2 (en) * | 2010-12-20 | 2013-12-10 | Advanced Micro Devices, Inc. | Memory diagnostics system and method with hardware-based read/write patterns |

| US9568546B2 (en) * | 2011-02-24 | 2017-02-14 | Rambus Inc. | Delay fault testing for chip I/O |

| JP2013196713A (ja) * | 2012-03-16 | 2013-09-30 | Fujitsu Semiconductor Ltd | 半導体装置の試験方法 |

| JP2015008025A (ja) * | 2013-06-25 | 2015-01-15 | マイクロン テクノロジー, インク. | 半導体装置 |

| KR102077072B1 (ko) * | 2013-07-05 | 2020-02-14 | 에스케이하이닉스 주식회사 | 병렬 테스트 장치 및 방법 |

| US9767868B2 (en) * | 2014-01-24 | 2017-09-19 | Qualcomm Incorporated | Providing memory training of dynamic random access memory (DRAM) systems using port-to-port loopbacks, and related methods, systems, and apparatuses |

| US10134482B2 (en) | 2017-01-17 | 2018-11-20 | Micron Technology, Inc. | Apparatuses and methods for high speed writing test mode for memories |

| KR102477268B1 (ko) * | 2018-01-26 | 2022-12-13 | 삼성전자주식회사 | 메모리 모듈의 정보를 실시간으로 모니터링하는 방법 및 시스템 |

| CN114566205A (zh) * | 2022-03-02 | 2022-05-31 | 长鑫存储技术有限公司 | 存储芯片的测试方法、装置、存储介质与电子设备 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58205992A (ja) * | 1982-05-25 | 1983-12-01 | Fujitsu Ltd | Lsi内蔵メモリの試験方法 |

| JPH01251400A (ja) * | 1988-03-30 | 1989-10-06 | Toshiba Corp | Ramのチェック方法 |

| JPH0362245A (ja) * | 1989-07-31 | 1991-03-18 | Nec Corp | 半導体集積回路 |

| JPH04275654A (ja) * | 1991-03-01 | 1992-10-01 | Nec Corp | 情報処理装置の記憶部診断方式 |

| JPH04373047A (ja) * | 1991-06-24 | 1992-12-25 | Nec Corp | メモリ診断方式 |

| JPH10207787A (ja) * | 1997-01-28 | 1998-08-07 | Nec Commun Syst Ltd | 記憶装置試験システム |

| JP3948141B2 (ja) * | 1998-09-24 | 2007-07-25 | 富士通株式会社 | 半導体記憶装置及びその制御方法 |

| JP2000156078A (ja) * | 1998-11-16 | 2000-06-06 | Toshiba Microelectronics Corp | 半導体記憶装置 |

| JP3180317B2 (ja) * | 1999-02-09 | 2001-06-25 | 日本電気株式会社 | 半導体記憶装置 |

| JP2000331498A (ja) * | 1999-05-17 | 2000-11-30 | Nec Corp | 半導体記憶装置 |

| JP4282170B2 (ja) * | 1999-07-29 | 2009-06-17 | 株式会社ルネサステクノロジ | 半導体装置 |

| JP4878215B2 (ja) | 2006-05-26 | 2012-02-15 | ルネサスエレクトロニクス株式会社 | インタフェース回路及びメモリ制御装置 |

| JP5125028B2 (ja) * | 2006-08-18 | 2013-01-23 | 富士通セミコンダクター株式会社 | 集積回路 |

-

2008

- 2008-05-30 JP JP2008143580A patent/JP5665263B2/ja not_active Expired - Fee Related

- 2008-10-29 US US12/260,842 patent/US7911861B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009289374A (ja) | 2009-12-10 |

| US20090296504A1 (en) | 2009-12-03 |

| US7911861B2 (en) | 2011-03-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5665263B2 (ja) | 半導体記憶装置、及び該半導体記憶装置のテスト方法 | |

| KR100782495B1 (ko) | 반도체 메모리 장치 및 이 장치의 데이터 라이트 및 리드방법 | |

| JP5579972B2 (ja) | 半導体記憶装置及び半導体記憶装置のテスト方法 | |

| US6510530B1 (en) | At-speed built-in self testing of multi-port compact sRAMs | |

| JP4229652B2 (ja) | 半導体回路装置 | |

| JP4216405B2 (ja) | ビルト−インパラレルテスト回路を備えた半導体メモリ装置 | |

| US20100182857A1 (en) | Tester for semiconductor device and semiconductor device | |

| KR20120068620A (ko) | 반도체 메모리 장치 및 그 테스트 방법 | |

| JPH10170607A (ja) | 半導体デバイスのテスト装置 | |

| JP2004046927A (ja) | 半導体記憶装置 | |

| JP4558648B2 (ja) | 試験装置 | |

| KR100914329B1 (ko) | 반도체 메모리 장치 및 그 테스트 방법 | |

| KR100850204B1 (ko) | 고속 반도체 메모리 장치를 테스트하기 위한 고주파 커맨드 신호 및 어드레스 신호 생성 방법 및 장치 | |

| US7948912B2 (en) | Semiconductor integrated circuit with test mode | |

| US20090303806A1 (en) | Synchronous semiconductor memory device | |

| JP2010040092A (ja) | 半導体集積回路 | |

| JP2003297096A (ja) | メモリ装置及びメモリ装置の試験方法 | |

| US20070088993A1 (en) | Memory tester having master/slave configuration | |

| US20100223514A1 (en) | Semiconductor memory device | |

| KR101287863B1 (ko) | 반도체 메모리 장치의 입력회로, 및 이를 구비한 테스트시스템 | |

| JP4836724B2 (ja) | 位相調整回路およびテスト装置 | |

| JP3060580B2 (ja) | メモリ搭載パッケージの検査装置 | |

| JP2004512630A (ja) | at−speedでのマルチポートCsRAMの組み込み自己検査 | |

| JP2006208190A (ja) | 集積回路およびその試験方法 | |

| JP3165131B2 (ja) | 半導体集積回路のテスト方法及びテスト回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110128 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110309 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130731 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20130801 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130905 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20131030 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131129 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20131213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140121 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140414 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141111 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141209 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5665263 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |