JP4993754B2 - Pga型配線基板及びその製造方法 - Google Patents

Pga型配線基板及びその製造方法 Download PDFInfo

- Publication number

- JP4993754B2 JP4993754B2 JP2008041441A JP2008041441A JP4993754B2 JP 4993754 B2 JP4993754 B2 JP 4993754B2 JP 2008041441 A JP2008041441 A JP 2008041441A JP 2008041441 A JP2008041441 A JP 2008041441A JP 4993754 B2 JP4993754 B2 JP 4993754B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring board

- pin

- fixing plate

- hole

- pin fixing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistors

- H05K3/303—Assembling printed circuits with electric components, e.g. with resistors with surface mounted components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10227—Other objects, e.g. metallic pieces

- H05K2201/1031—Surface mounted metallic connector elements

- H05K2201/10318—Surface mounted metallic pins

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10227—Other objects, e.g. metallic pieces

- H05K2201/10424—Frame holders

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10954—Other details of electrical connections

- H05K2201/10977—Encapsulated connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

- H05K3/284—Applying non-metallic protective coatings for encapsulating mounted components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistors

- H05K3/303—Assembling printed circuits with electric components, e.g. with resistors with surface mounted components

- H05K3/305—Affixing by adhesive

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistors

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistors electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistors electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3421—Leaded components

- H05K3/3426—Leaded components characterised by the leads

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49128—Assembling formed circuit to base

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Lead Frames For Integrated Circuits (AREA)

Description

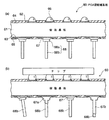

図1は本発明の第1の実施形態に係るPGA型配線基板10の構成を断面図の形態で示したものである。

図3は本発明の第2の実施形態に係るPGA型配線基板10aの構成を断面図の形態で示したものである。

図4は本発明の第3の実施形態に係るPGA型配線基板10bの構成を断面図の形態で示したものである。

図5は本発明の第4の実施形態に係るPGA型配線基板10cの構成を断面図の形態で示したものである。

図6は本発明の第5の実施形態に係るPGA型配線基板10dの構成を断面図の形態で示したものである。

次に、上述した各実施形態に係るPGA型配線基板を製造する方法について説明する。基本となる工程は各製造方法とも実質的に同じであるので、代表として、第2の実施形態に係るPGA型配線基板10a(図3)を製造する方法について説明する。図7及び図8はその製造工程の一例を示したものである。

11…樹脂基板(配線基板本体)、

12,13…配線層(パッド部)、

14,15…ソルダレジスト層(保護膜/絶縁層)、

16,17…はんだ、

18…ピン(外部接続端子)、

18a,18c…(ピンの)ヘッド部、

18b…(ピンの)軸部、

19,19a,19b,19c,19d,19e,19f,30…接着剤(層)、

20,20a,21,22…ピン固定用板、

DP…ダム部、

FR…接着剤の流れ出しのエリア、

GH…ガス抜き孔、

TH,TH1,TH2…貫通孔。

Claims (18)

- 表面にパッド部が形成された配線基板と、

ヘッド部及び該ヘッド部に接合された軸部を有するピンと、

貫通孔が形成されたピン固定用板とを備え、

前記ピンのヘッド部が、導電性材料を介して前記パッド部に接合され、

前記ピン固定用板が、接着剤層を介して前記配線基板の表面に接着され、

前記貫通孔に前記ピンの軸部が挿通されると共に、前記接着剤層の接着剤が、前記貫通孔と前記軸部との隙間に充填され、且つ前記軸部上を前記貫通孔の外まで這い上がっていることを特徴とするPGA型配線基板。 - 前記配線基板の表面に前記パッド部を露出させてソルダレジスト層が設けられ、

前記ピン固定用板が、前記接着剤層を介して前記ソルダレジスト層に接着され、

前記貫通孔に前記ピンの軸部が挿通されると共に、前記ソルダレジスト層の表面から突出する前記ヘッド部の部分が、前記貫通孔内に収容されていることを特徴とする請求項1に記載のPGA型配線基板。 - 前記貫通孔は、断面的に見て一定の大きさで形成されていることを特徴とする請求項1又は2に記載のPGA型配線基板。

- 前記貫通孔は、断面的に見て段差状に2段構成で形成されていることを特徴とする請求項1又は2に記載のPGA型配線基板。

- 前記貫通孔は、断面的に見てテーパ状に傾斜した部分を含む形状に形成されていることを特徴とする請求項1又は2に記載のPGA型配線基板。

- 前記ピン固定用板は、その周辺部に対応する箇所にダム部を有することを特徴とする請求項1又は2に記載のPGA型配線基板。

- 前記ピン固定用板は、ガス抜き孔を有することを特徴とする請求項1又は2に記載のPGA型配線基板。

- 前記接着剤層は、前記配線基板の端部から内部の方向に後退させて設けられていることを特徴とする請求項1又は2に記載のPGA型配線基板。

- 表面にパッド部が形成され、該パッド部にピンのヘッド部が導電性材料を介して接合された配線基板を用意する工程と、

貫通孔が形成されたピン固定用板を作製する工程と、

前記ピン固定用板の一方の面に未硬化状態の接着剤層を形成する工程と、

前記配線基板の前記ピンが接合されている側の面に前記ピン固定用板の前記接着剤層が形成されている側の面を対向させ、当該ピンのヘッド部に接合された軸部を前記貫通孔に挿通させて対向する両面を当接させる工程と、

前記接着剤層を、その接着剤が前記貫通孔と前記軸部との隙間を充填し、且つ前記軸部上を前記貫通孔の外まで這い上がるように硬化させて、前記配線基板に前記ピン固定用板を接着する工程とを含むことを特徴とするPGA型配線基板の製造方法。 - 前記配線基板を用意する工程において、前記配線基板の表面に前記パッド部を露出させてソルダレジスト層を形成し、また、前記ピンのヘッド部の部分を前記ソルダレジスト層の表面から突出させて前記パッド部に接合させ、

前記配線基板に前記ピン固定用板を接着する工程において、該ピン固定用板を前記接着剤層を介して前記ソルダレジスト層に接着すると共に、前記ピンのヘッド部の部分を前記貫通孔内に収容することを特徴とする請求項9に記載のPGA型配線基板の製造方法。 - 前記ピン固定用板を作製する工程は、前記ピンの配列に合わせた位置に一定の大きさで貫通孔を形成する工程を含むことを特徴とする請求項9又は10に記載のPGA型配線基板の製造方法。

- 前記ピン固定用板を作製する工程は、前記ピンの配列に合わせた位置に一定の径で貫通孔を形成する工程と、該貫通孔よりも大きな一定の径をもって該貫通孔の途中の部分までを開口する工程とを含むことを特徴とする請求項9又は10に記載のPGA型配線基板の製造方法。

- 前記ピン固定用板を作製する工程は、前記ピンの配列に合わせた位置に一定の径で貫通孔を形成する工程と、該貫通孔よりも大きな径をもってテーパ状に該貫通孔の途中の部分までを開口する工程とを含むことを特徴とする請求項9又は10に記載のPGA型配線基板の製造方法。

- 前記ピン固定用板を作製する工程において、該ピン固定用板の周辺部に対応する箇所にダム状に隆起させた部分を形成することを特徴とする請求項9又は10に記載のPGA型配線基板の製造方法。

- 前記ピン固定用板を作製する工程において、該ピン固定用板にガス抜き孔を形成することを特徴とする請求項9又は10に記載のPGA型配線基板の製造方法。

- 前記ピン固定用板の一方の面に未硬化状態の接着剤層を形成する工程において、該接着剤層を、該ピン固定用板の周辺部に対応する箇所を除いて形成することを特徴とする請求項9又は10に記載のPGA型配線基板の製造方法。

- 前記配線基板に前記ピン固定用板を接着する工程において、前記接着剤の使用量を調整することにより這い上がり量を調整することを特徴とする請求項9に記載のPGA型配線基板の製造方法。

- 前記配線基板に前記ピン固定用板を接着する工程において、該ピン固定用板及び該ピン固定用板に被着された未硬化の接着剤層を加圧し、加熱して接着することを特徴とする請求項9に記載のPGA型配線基板の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008041441A JP4993754B2 (ja) | 2008-02-22 | 2008-02-22 | Pga型配線基板及びその製造方法 |

| US12/372,870 US20090211798A1 (en) | 2008-02-22 | 2009-02-18 | Pga type wiring board and method of manufacturing the same |

| KR1020090014481A KR101521485B1 (ko) | 2008-02-22 | 2009-02-20 | Pga형 배선 기판 및 그 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008041441A JP4993754B2 (ja) | 2008-02-22 | 2008-02-22 | Pga型配線基板及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009200313A JP2009200313A (ja) | 2009-09-03 |

| JP2009200313A5 JP2009200313A5 (ja) | 2011-03-31 |

| JP4993754B2 true JP4993754B2 (ja) | 2012-08-08 |

Family

ID=40997206

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008041441A Expired - Fee Related JP4993754B2 (ja) | 2008-02-22 | 2008-02-22 | Pga型配線基板及びその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20090211798A1 (ja) |

| JP (1) | JP4993754B2 (ja) |

| KR (1) | KR101521485B1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5290017B2 (ja) * | 2008-03-28 | 2013-09-18 | 日本特殊陶業株式会社 | 多層配線基板及びその製造方法 |

| JP5079646B2 (ja) * | 2008-08-26 | 2012-11-21 | 新光電気工業株式会社 | 半導体パッケージ及びその製造方法と半導体装置 |

| US20110147069A1 (en) * | 2009-12-18 | 2011-06-23 | International Business Machines Corporation | Multi-tiered Circuit Board and Method of Manufacture |

| JP2012164965A (ja) * | 2011-01-21 | 2012-08-30 | Ngk Spark Plug Co Ltd | 配線基板及びその製造方法 |

| JP2012169591A (ja) * | 2011-01-24 | 2012-09-06 | Ngk Spark Plug Co Ltd | 多層配線基板 |

| JP6008582B2 (ja) * | 2012-05-28 | 2016-10-19 | 新光電気工業株式会社 | 半導体パッケージ、放熱板及びその製造方法 |

| TW201432961A (zh) * | 2013-02-05 | 2014-08-16 | Lextar Electronics Corp | 基板結構 |

| CN106211629B (zh) * | 2016-08-30 | 2018-10-02 | 无锡市同步电子制造有限公司 | 印刷电路板加工中进行高温焊接的方法 |

| US11808787B2 (en) * | 2020-08-28 | 2023-11-07 | Unimicron Technology Corp. | Probe card testing device |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01313969A (ja) * | 1988-06-13 | 1989-12-19 | Hitachi Ltd | 半導体装置 |

| US5103292A (en) * | 1989-11-29 | 1992-04-07 | Olin Corporation | Metal pin grid array package |

| US5261157A (en) * | 1991-01-22 | 1993-11-16 | Olin Corporation | Assembly of electronic packages by vacuum lamination |

| JP2658672B2 (ja) * | 1991-10-11 | 1997-09-30 | 日本電気株式会社 | I/oピンの修理構造および修理方法 |

| JPH05183019A (ja) * | 1991-12-27 | 1993-07-23 | Hitachi Ltd | 半導体装置およびその製造方法 |

| US6835898B2 (en) * | 1993-11-16 | 2004-12-28 | Formfactor, Inc. | Electrical contact structures formed by configuring a flexible wire to have a springable shape and overcoating the wire with at least one layer of a resilient conductive material, methods of mounting the contact structures to electronic components, and applications for employing the contact structures |

| JPH09102560A (ja) * | 1995-10-05 | 1997-04-15 | Sumitomo Kinzoku Electro Device:Kk | 低温焼成セラミック基板の外部リードピン接合構造 |

| JP3037885B2 (ja) * | 1995-10-31 | 2000-05-08 | 日本特殊陶業株式会社 | Pga型電子部品用基板 |

| JPH09213836A (ja) * | 1996-02-07 | 1997-08-15 | Sumitomo Kinzoku Electro Device:Kk | 低温焼成セラミックパッケージ |

| US5952716A (en) * | 1997-04-16 | 1999-09-14 | International Business Machines Corporation | Pin attach structure for an electronic package |

| JP4046854B2 (ja) * | 1998-06-29 | 2008-02-13 | イビデン株式会社 | ピン付きプリント配線板の製造方法 |

| JP2000058736A (ja) * | 1998-08-07 | 2000-02-25 | Sumitomo Kinzoku Electro Device:Kk | 樹脂基板へのピン接続方法 |

| KR100882173B1 (ko) * | 1998-12-16 | 2009-02-06 | 이비덴 가부시키가이샤 | 도전성접속핀 및 패키지기판 |

| US20020019168A1 (en) * | 1999-01-12 | 2002-02-14 | Robert W. Hooley | Pin array header with floating surface mount interconnects |

| US6217346B1 (en) * | 1999-05-11 | 2001-04-17 | Illinois Tool Works Inc. | Solderless pin connection |

| US6830460B1 (en) * | 1999-08-02 | 2004-12-14 | Gryphics, Inc. | Controlled compliance fine pitch interconnect |

| US6974765B2 (en) * | 2001-09-27 | 2005-12-13 | Intel Corporation | Encapsulation of pin solder for maintaining accuracy in pin position |

| DE60329478D1 (de) * | 2002-03-20 | 2009-11-12 | Andrew Llc | Stifte und buchse zum zwischenverbinden von zwei leiterplatten, sowie verfahren zum einbau in eine leiterplatte |

| JP4054269B2 (ja) * | 2003-03-20 | 2008-02-27 | Tdk株式会社 | 電子部品の製造方法および電子部品 |

| CN101160694A (zh) * | 2005-08-25 | 2008-04-09 | 住友电气工业株式会社 | 各向异性导电片及其制造方法、连接方法以及检测方法 |

| TWI298613B (en) * | 2006-05-19 | 2008-07-01 | Foxconn Advanced Tech Inc | Method for manufacturing via holes used in printed circuit boards |

| US20080192446A1 (en) * | 2007-02-09 | 2008-08-14 | Johannes Hankofer | Protection For Circuit Boards |

-

2008

- 2008-02-22 JP JP2008041441A patent/JP4993754B2/ja not_active Expired - Fee Related

-

2009

- 2009-02-18 US US12/372,870 patent/US20090211798A1/en not_active Abandoned

- 2009-02-20 KR KR1020090014481A patent/KR101521485B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR101521485B1 (ko) | 2015-05-20 |

| JP2009200313A (ja) | 2009-09-03 |

| KR20090091070A (ko) | 2009-08-26 |

| US20090211798A1 (en) | 2009-08-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4993754B2 (ja) | Pga型配線基板及びその製造方法 | |

| JP3875077B2 (ja) | 電子デバイス及びデバイス接続方法 | |

| JP5113114B2 (ja) | 配線基板の製造方法及び配線基板 | |

| JP4928945B2 (ja) | バンプ−オン−リードフリップチップ相互接続 | |

| TWI492677B (zh) | 配線基板及其製造方法 | |

| US20040235287A1 (en) | Method of manufacturing semiconductor package and method of manufacturing semiconductor device | |

| KR20030067590A (ko) | 반도체소자와 그 제조방법 및 반도체장치와 그 제조방법 | |

| US8779300B2 (en) | Packaging substrate with conductive structure | |

| CN102446776A (zh) | 电子装置的制造方法及电子装置 | |

| JP2006005322A (ja) | 部品実装配線基板および配線基板への部品の実装方法 | |

| JP4051570B2 (ja) | 半導体装置の製造方法 | |

| WO2007080863A1 (ja) | 半導体装置、該半導体装置を実装するプリント配線基板、及びそれらの接続構造 | |

| JP4835629B2 (ja) | 半導体装置の製造方法 | |

| JP2019021752A (ja) | 配線基板、電子機器、配線基板の製造方法及び電子機器の製造方法 | |

| JP4429435B2 (ja) | バンプ付き二層回路テープキャリアおよびその製造方法 | |

| JP4918780B2 (ja) | 多層配線基板の製造方法、ならびに半導体装置 | |

| JP2016127066A (ja) | バンプ付きプリント配線板およびその製造方法 | |

| JP4045708B2 (ja) | 半導体装置、電子回路装置および製造方法 | |

| JP4065264B2 (ja) | 中継基板付き基板及びその製造方法 | |

| JP3742732B2 (ja) | 実装基板及び実装構造体 | |

| JP2004200608A (ja) | プリント配線基板およびその製造方法 | |

| US12185470B2 (en) | Embedded printed circuit board | |

| JP2011238843A (ja) | 突起電極付き配線基板及び突起電極付き配線基板の製造方法 | |

| TWI550738B (zh) | 表面安裝積體電路組件 | |

| JP2007266640A (ja) | 半導体装置及びその製造方法、回路基板並びに電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110208 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111020 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111025 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111205 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120501 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120507 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150518 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4993754 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |