JP5079646B2 - 半導体パッケージ及びその製造方法と半導体装置 - Google Patents

半導体パッケージ及びその製造方法と半導体装置 Download PDFInfo

- Publication number

- JP5079646B2 JP5079646B2 JP2008242066A JP2008242066A JP5079646B2 JP 5079646 B2 JP5079646 B2 JP 5079646B2 JP 2008242066 A JP2008242066 A JP 2008242066A JP 2008242066 A JP2008242066 A JP 2008242066A JP 5079646 B2 JP5079646 B2 JP 5079646B2

- Authority

- JP

- Japan

- Prior art keywords

- lead pin

- resin

- solder

- resin layer

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

- H05K3/284—Applying non-metallic protective coatings for encapsulating mounted components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4853—Connection or disconnection of other leads to or from a metallisation, e.g. pins, wires, bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49822—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49866—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers characterised by the materials

- H01L23/49894—Materials of the insulating layers or coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00011—Not relevant to the scope of the group, the symbol of which is combined with the symbol of this group

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0102—Calcium [Ca]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/146—Mixed devices

- H01L2924/1461—MEMS

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15172—Fan-out arrangement of the internal vias

- H01L2924/15174—Fan-out arrangement of the internal vias in different layers of the multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15312—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a pin array, e.g. PGA

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09009—Substrate related

- H05K2201/091—Locally and permanently deformed areas including dielectric material

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10227—Other objects, e.g. metallic pieces

- H05K2201/1031—Surface mounted metallic connector elements

- H05K2201/10318—Surface mounted metallic pins

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10954—Other details of electrical connections

- H05K2201/10977—Encapsulated connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4682—Manufacture of core-less build-up multilayer circuits on a temporary carrier or on a metal foil

Description

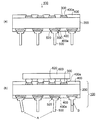

図2〜図6は本発明の第1実施形態の半導体パッケージの製造方法を示す断面図である。

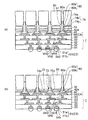

図12〜図15は本発明の第2実施形態の半導体パッケージの製造方法を示す断面図である。前述した第1実施形態では、補強樹脂層70をエポキシ樹脂などの単層の樹脂フィルム70xから形成している。半導体パッケージではリードピン側の面に難燃性をもたせる場合があるが、エポキシ樹脂単体では難燃性を得ることは困難である。

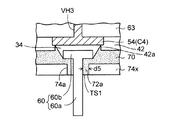

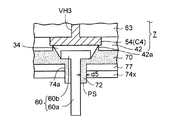

図19及び図20は本発明の第3実施形態の半導体パッケージのリードピンの周りを示す部分断面図である。第3実施形態と第2実施形態との違いは、リードピンの周りの補強樹脂層の形状にあり、その他の要素は第2実施形態の図15と同一である。このため、リードピンの周りの部分断面図を参照して説明する。

図21及び図22は本発明の第4実施形態の半導体パッケージのリードピンの周りを示す部分断面図である。第4実施形態と第2実施形態との違いは、難燃性フィルム74xと補強樹脂層70との間に他の層をさらに形成することにある。その他の要素は第2実施形態の図15と同一であるので、リードピンの周りの部分断面図を参照して説明する。

Claims (8)

- 配線基板と、

前記配線基板の一方の面側の接続パッドにはんだによって固着されたリードピンと、

前記配線基板の前記リードピンが設けられた面の全面に形成され、前記リードピンの周りで局所的に突出して前記リードピンの基部側の側面を被覆する突起状樹脂部を備えた補強樹脂層と、

前記補強樹脂層の外面側に形成されて、前記リードピンの径より大きな径の開口部を備え、前記開口部に前記リードピンが挿通した状態で配置された絶縁フィルムと、

前記補強樹脂層と前記絶縁フィルムとの間に形成され、前記リードピンの径より大きな径の開口部を備え、前記開口部に前記リードピンが挿通した状態で配置された中間樹脂層とを有し、

前記突起状樹脂部は、前記リードピンと前記絶縁フィルム及び前記中間樹脂層の開口部の側面との隙間に充填されて前記リードピンの先端側に突出しており、かつ、

前記補強樹脂層、前記中間樹脂層、及び前記絶縁フィルムの順にそれらの弾性率が高くなるように設定されていることを特徴とする半導体パッケージ。 - 前記突起状樹脂部は、前記リードピンの外周部から外側に延在する頂上面と、前記頂上面と非同一面となる側面とを備えていることを特徴とする請求項1に記載の半導体パッケージ。

- 前記突起状樹脂部を備えた補強樹脂層は、エポキシ樹脂、ポリイミド樹脂、アクリル樹脂、エポキシ樹脂とアクリル樹脂との混合樹脂、又は、下から順に、エポキシ樹脂/ポリイミド樹脂の2層構造からなることを特徴とする請求項1又は2に記載の半導体パッケージ。

- 前記はんだは鉛フリーはんだであることを特徴とする請求項1乃至3のいずれか一項に記載の半導体パッケージ。

- 前記絶縁フィルムは、ポリイミド、エンジニアリングプラスチック、ポリフェニレンサルファイド、及びテフロン(登録商標)のいずれかからなることを特徴とする1乃至3のいずれか一項に記載の半導体パッケージ。

- 請求項1乃至5のいずれかの半導体パッケージと、

前記配線基板の他方の面側の接続パッドにはんだによって実装された半導体チップとを有することを特徴とする半導体装置。 - 前記リードピンを固着するはんだと前記半導体チップを実装するはんだは共に鉛フリーはんだであり、

前記半導体チップは前記はんだをリフロー加熱することによって実装され、

前記リードピンを固着するはんだの融点は、前記半導体チップを実装する際の前記リフロー加熱の温度と同等又はそれより低いことを特徴とする請求項6に記載の半導体装置。 - 配線基板の一方の面側の接続パッドにはんだによってリードピンを固着する工程と、

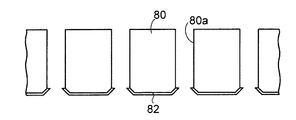

下から順に、未硬化の補強樹脂層、未硬化の中間樹脂層、及び絶縁フィルムが積層されて、前記リードピンの径より大きな径の開口部を備えた樹脂付きフィルムの前記開口部に前記リードピンを挿通させ、押圧治具で前記樹脂付きフィルムを押圧しながら熱処理して硬化させることにより、前記補強樹脂層、前記中間樹脂層及び前記絶縁フィルムを得ると共に、リードピンと前記絶縁フィルム及び前記中間樹脂層の開口部の側面との隙間に、前記補強樹脂層に繋がって充填された突起状樹脂部を前記リードピンの先端側に突出させて形成する工程とを有し、

前記補強樹脂層、前記中間樹脂層、及び前記絶縁フィルムの順にそれらの弾性率が高くなるように設定されていることを特徴とする半導体パッケージの製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008242066A JP5079646B2 (ja) | 2008-08-26 | 2008-09-22 | 半導体パッケージ及びその製造方法と半導体装置 |

| US12/512,277 US8120166B2 (en) | 2008-08-26 | 2009-07-30 | Semiconductor package and method of manufacturing the same, and semiconductor device and method of manufacturing the same |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008216325 | 2008-08-26 | ||

| JP2008216325 | 2008-08-26 | ||

| JP2008242066A JP5079646B2 (ja) | 2008-08-26 | 2008-09-22 | 半導体パッケージ及びその製造方法と半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010080457A JP2010080457A (ja) | 2010-04-08 |

| JP2010080457A5 JP2010080457A5 (ja) | 2011-08-18 |

| JP5079646B2 true JP5079646B2 (ja) | 2012-11-21 |

Family

ID=41724089

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008242066A Active JP5079646B2 (ja) | 2008-08-26 | 2008-09-22 | 半導体パッケージ及びその製造方法と半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8120166B2 (ja) |

| JP (1) | JP5079646B2 (ja) |

Families Citing this family (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7688237B2 (en) * | 2006-12-21 | 2010-03-30 | Broadcom Corporation | Apparatus and method for analog-to-digital converter calibration |

| KR20110058938A (ko) * | 2009-11-27 | 2011-06-02 | 삼성전기주식회사 | 반도체 패키지용 리드핀 및 반도체 패키지 |

| JP5590985B2 (ja) * | 2010-06-21 | 2014-09-17 | 新光電気工業株式会社 | 半導体装置及びその製造方法 |

| JP2012009586A (ja) * | 2010-06-24 | 2012-01-12 | Shinko Electric Ind Co Ltd | 配線基板、半導体装置及び配線基板の製造方法 |

| JP5548062B2 (ja) * | 2010-08-11 | 2014-07-16 | 株式会社日立製作所 | 配管用モジュール向け仮設部材の施工方法及び配管モジュールの搬送方法 |

| JP2012164965A (ja) | 2011-01-21 | 2012-08-30 | Ngk Spark Plug Co Ltd | 配線基板及びその製造方法 |

| JP2012169591A (ja) * | 2011-01-24 | 2012-09-06 | Ngk Spark Plug Co Ltd | 多層配線基板 |

| US8952540B2 (en) * | 2011-06-30 | 2015-02-10 | Intel Corporation | In situ-built pin-grid arrays for coreless substrates, and methods of making same |

| US8872358B2 (en) * | 2012-02-07 | 2014-10-28 | Shin-Etsu Chemical Co., Ltd. | Sealant laminated composite, sealed semiconductor devices mounting substrate, sealed semiconductor devices forming wafer, semiconductor apparatus, and method for manufacturing semiconductor apparatus |

| US9354748B2 (en) | 2012-02-13 | 2016-05-31 | Microsoft Technology Licensing, Llc | Optical stylus interaction |

| US8873227B2 (en) | 2012-03-02 | 2014-10-28 | Microsoft Corporation | Flexible hinge support layer |

| US9064654B2 (en) * | 2012-03-02 | 2015-06-23 | Microsoft Technology Licensing, Llc | Method of manufacturing an input device |

| US9426905B2 (en) | 2012-03-02 | 2016-08-23 | Microsoft Technology Licensing, Llc | Connection device for computing devices |

| US9298236B2 (en) | 2012-03-02 | 2016-03-29 | Microsoft Technology Licensing, Llc | Multi-stage power adapter configured to provide a first power level upon initial connection of the power adapter to the host device and a second power level thereafter upon notification from the host device to the power adapter |

| US9360893B2 (en) | 2012-03-02 | 2016-06-07 | Microsoft Technology Licensing, Llc | Input device writing surface |

| USRE48963E1 (en) | 2012-03-02 | 2022-03-08 | Microsoft Technology Licensing, Llc | Connection device for computing devices |

| US9870066B2 (en) * | 2012-03-02 | 2018-01-16 | Microsoft Technology Licensing, Llc | Method of manufacturing an input device |

| US9460029B2 (en) | 2012-03-02 | 2016-10-04 | Microsoft Technology Licensing, Llc | Pressure sensitive keys |

| US9075566B2 (en) | 2012-03-02 | 2015-07-07 | Microsoft Technoogy Licensing, LLC | Flexible hinge spine |

| US20130300590A1 (en) | 2012-05-14 | 2013-11-14 | Paul Henry Dietz | Audio Feedback |

| US10031556B2 (en) | 2012-06-08 | 2018-07-24 | Microsoft Technology Licensing, Llc | User experience adaptation |

| US9019615B2 (en) | 2012-06-12 | 2015-04-28 | Microsoft Technology Licensing, Llc | Wide field-of-view virtual image projector |

| US9073123B2 (en) | 2012-06-13 | 2015-07-07 | Microsoft Technology Licensing, Llc | Housing vents |

| US8964379B2 (en) | 2012-08-20 | 2015-02-24 | Microsoft Corporation | Switchable magnetic lock |

| US8654030B1 (en) | 2012-10-16 | 2014-02-18 | Microsoft Corporation | Antenna placement |

| WO2014059618A1 (en) | 2012-10-17 | 2014-04-24 | Microsoft Corporation | Graphic formation via material ablation |

| CN104870123B (zh) | 2012-10-17 | 2016-12-14 | 微软技术许可有限责任公司 | 金属合金注射成型突起 |

| WO2014059625A1 (en) | 2012-10-17 | 2014-04-24 | Microsoft Corporation | Metal alloy injection molding overflows |

| JP2014103176A (ja) * | 2012-11-16 | 2014-06-05 | Shin Etsu Chem Co Ltd | 支持基材付封止材、封止後半導体素子搭載基板、封止後半導体素子形成ウエハ、半導体装置、及び半導体装置の製造方法 |

| US8946884B2 (en) * | 2013-03-08 | 2015-02-03 | Xilinx, Inc. | Substrate-less interposer technology for a stacked silicon interconnect technology (SSIT) product |

| US9304549B2 (en) | 2013-03-28 | 2016-04-05 | Microsoft Technology Licensing, Llc | Hinge mechanism for rotatable component attachment |

| US10120420B2 (en) | 2014-03-21 | 2018-11-06 | Microsoft Technology Licensing, Llc | Lockable display and techniques enabling use of lockable displays |

| US10324733B2 (en) | 2014-07-30 | 2019-06-18 | Microsoft Technology Licensing, Llc | Shutdown notifications |

| JP6358431B2 (ja) * | 2014-08-25 | 2018-07-18 | 新光電気工業株式会社 | 電子部品装置及びその製造方法 |

| US9424048B2 (en) | 2014-09-15 | 2016-08-23 | Microsoft Technology Licensing, Llc | Inductive peripheral retention device |

| JP7107120B2 (ja) * | 2018-09-14 | 2022-07-27 | 富士電機株式会社 | 半導体装置、半導体装置の製造方法 |

| US11427466B2 (en) * | 2019-07-19 | 2022-08-30 | Advanced Semiconductor Engineering, Inc. | Semiconductor package structure and method for manufacturing the same |

| EP3859776A1 (en) | 2020-01-31 | 2021-08-04 | Infineon Technologies AG | Power semiconductor device and method for fabricating a power semiconductor device |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01100958A (ja) | 1987-10-14 | 1989-04-19 | Hitachi Ltd | 樹脂被覆セラミック配線基板 |

| JP2000058736A (ja) * | 1998-08-07 | 2000-02-25 | Sumitomo Kinzoku Electro Device:Kk | 樹脂基板へのピン接続方法 |

| JP2001148441A (ja) | 1999-11-19 | 2001-05-29 | Shinko Electric Ind Co Ltd | 半導体パッケージ及びその製造方法 |

| JP2006216631A (ja) * | 2005-02-02 | 2006-08-17 | Ngk Spark Plug Co Ltd | 配線基板およびその製造方法 |

| JP4993754B2 (ja) * | 2008-02-22 | 2012-08-08 | 新光電気工業株式会社 | Pga型配線基板及びその製造方法 |

-

2008

- 2008-09-22 JP JP2008242066A patent/JP5079646B2/ja active Active

-

2009

- 2009-07-30 US US12/512,277 patent/US8120166B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010080457A (ja) | 2010-04-08 |

| US8120166B2 (en) | 2012-02-21 |

| US20100052153A1 (en) | 2010-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5079646B2 (ja) | 半導体パッケージ及びその製造方法と半導体装置 | |

| USRE44377E1 (en) | Bump-on-lead flip chip interconnection | |

| US20100212939A1 (en) | Module, circuit board, and module manufacturing method | |

| US20080251942A1 (en) | Semiconductor Device and Manufacturing Method Thereof | |

| JP4729963B2 (ja) | 電子部品接続用突起電極とそれを用いた電子部品実装体およびそれらの製造方法 | |

| US7901983B2 (en) | Bump-on-lead flip chip interconnection | |

| JP2006302930A (ja) | 配線基板とそれを用いた電子部品実装体およびそれらの製造方法 | |

| US7969028B2 (en) | Semiconductor device mounting structure, manufacturing method, and removal method of semiconductor device | |

| US20090211798A1 (en) | Pga type wiring board and method of manufacturing the same | |

| KR20120033973A (ko) | 전자 장치의 제조 방법 및 전자 장치 | |

| JP2008288489A (ja) | チップ内蔵基板の製造方法 | |

| JP5569676B2 (ja) | 電子部品の実装方法 | |

| US6657313B1 (en) | Dielectric interposer for chip to substrate soldering | |

| WO2011102101A1 (en) | Stacked semiconductor device | |

| JP4051570B2 (ja) | 半導体装置の製造方法 | |

| KR20020044577A (ko) | 개선된 플립-칩 결합 패키지 | |

| JP5061668B2 (ja) | 2種類の配線板を有するハイブリッド基板、それを有する電子装置、及び、ハイブリッド基板の製造方法 | |

| JP4835406B2 (ja) | 実装構造体とその製造方法および半導体装置とその製造方法 | |

| JP4065264B2 (ja) | 中継基板付き基板及びその製造方法 | |

| JP3742732B2 (ja) | 実装基板及び実装構造体 | |

| KR100746362B1 (ko) | 패키지 온 패키지 기판 및 그 제조방법 | |

| JPH10116927A (ja) | 接続端子及びその形成方法 | |

| JP2002057242A (ja) | エリアアレイ型半導体パッケージ | |

| US20100038123A1 (en) | Board unit and manufacturing method for the same | |

| JP2006121008A (ja) | 半導体部品実装体及び半導体部品実装体の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110705 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110705 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120413 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120508 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120625 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120828 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120829 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150907 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5079646 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |