JP4045708B2 - 半導体装置、電子回路装置および製造方法 - Google Patents

半導体装置、電子回路装置および製造方法 Download PDFInfo

- Publication number

- JP4045708B2 JP4045708B2 JP34910399A JP34910399A JP4045708B2 JP 4045708 B2 JP4045708 B2 JP 4045708B2 JP 34910399 A JP34910399 A JP 34910399A JP 34910399 A JP34910399 A JP 34910399A JP 4045708 B2 JP4045708 B2 JP 4045708B2

- Authority

- JP

- Japan

- Prior art keywords

- hole

- substrate

- semiconductor

- wiring pattern

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/15—Encapsulations, e.g. protective coatings characterised by their shape or disposition on active surfaces of flip-chip devices, e.g. underfills

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/731—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors

- H10W90/734—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

本発明は、高速化、多ピン化、小型化および高密度実装化に対応した半導体装置、電子回路装置および製造方法に関し、特に、半導体チップと絶縁基板との接合部分のはんだバンプの応力が低減され、接続信頼性が向上された半導体装置、電子回路装置および製造方法に関する。

【0002】

【従来の技術】

近年、半導体デバイスの高集積化・高速化に伴い、半導体パッケージも従来のQFP(quad flat package)から、より小型化・多ピン化されたBGA(ball grid array)が多く採用されるようになってきている。BGAは半導体チップを実装した絶縁基板の底面側に、接続端子であるはんだボールが二次元的に配列された表面実装型のパッケージである。したがって、多ピン化された場合にもピン間隔の狭ピッチ化を避けられ、パッケージ寸法を縮小できるという利点を有する。さらに、従来の表面実装部品と同様に、一括リフローによる基板実装が可能であるという利点も有する。

【0003】

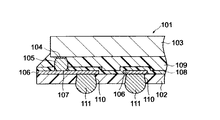

従来のBGA型半導体パッケージの例について、図11を参照して説明する。図11に示す半導体装置101は、絶縁基板(実装基板)102に半導体チップ103の表面が電極パッド104およびはんだバンプ105を介して実装されている。絶縁基板102の表面には配線パターン106が形成されている。配線パターン106の一部はランド107となり、ランド107において配線パターン106とはんだバンプ105が接続する。配線パターン106は絶縁膜からなるオーバーコート108により被覆され、絶縁基板102と半導体チップ103との間には封止樹脂109が形成されている。

絶縁基板102にはスルーホール110が二次元的に配列されて形成されており、スルーホール110内には外部端子および配線パターン106に接続する外部端子用はんだバンプ111が形成されている。

【0004】

図11に示すような従来のBGA型半導体パッケージにおいては、クリームはんだをスキージを用いてスルーホール110内に充填し、その上にあらかじめほぼ球状に形成されたはんだボールを移載してから、一括リフローにより溶融させる方法が一般的に用いられている。ここで、スルーホール110内に充填されたクリームはんだにより、配線パターン106とはんだボールとが接続される。はんだボールを溶融させると、表面張力によって球形を維持しようとする力が作用する。したがって、クリームはんだをスルーホール110に充填しない場合には、配線パターン106とはんだボールとの間に隙間ができ、接続不良となる。

【0005】

以上のように、従来のBGA型半導体パッケージによれば、スルーホール内にクリームはんだを充填させる必要があり、生産性の向上やコスト低減の妨げとなっていた。

【0006】

一方、BGA型半導体パッケージにおいて、クリームはんだを用いない方法もいくつか提案されている。例えば、特開平10−50883号公報にはスルーホール内に突起ができるように配線パターンの一部を突出させ、配線パターンとはんだボールとを接合させる方法が記載されている。また、配線パターンに突起を設けることにより、はんだボールにかかる応力を低減できるとしている。

【0007】

また、特開平9−232373号公報(特許第2842361号公報)には、外部端子用はんだバンプを囲むように樹脂を塗布することにより、樹脂補強部材が形成された半導体装置が記載されている。はんだバンプ接合部には絶縁基板(実装基板)と半導体チップとの熱膨張率差に起因した強い応力がかかるため、温度サイクル試験を行うとはんだバンプ接合部において破断する。上記の特開平9−232373号公報に記載の半導体装置によれば、はんだバンプ接合部が補強されるため、半導体装置の温度サイクル寿命を向上させることができる。

【0008】

【発明が解決しようとする課題】

上記のように、従来のBGA型半導体パッケージにおいては、はんだバンプ接合部にクリームはんだを充填する必要があり、生産性の向上やコスト低減の妨げとなっていた。クリームはんだを用いない方法も提案されているが、特開平10−50883号公報に記載のように、スルーホール内に突起ができるように配線パターンを突出させる場合には、配線を変形させるための作業をスルーホールごとに行う必要があり、生産性の点で問題がある。

【0009】

また、スルーホール内に突起ができるように配線を変形させることにより、配線に断線が生じる可能性があるため、形成できる突起の大きさには限界がある。スルーホール内にはんだバンプが形成された構造の場合、絶縁基板とはんだバンプとの接合部分にひずみエネルギーが集中し、はんだに疲労によるクラックが発生する(第8回マイクロエレクトロニクスシンポジウム論文集(1998年12月)p.37−40)。特開平10−50883号公報に記載された半導体装置によれば、絶縁基板とはんだバンプとの接合部分に形成できる突起の大きさが制限されるため、突起がはんだバンプ接合部分の応力を緩和する能力にも限界がある。

【0010】

一方、特開平9−232373号公報に記載の半導体装置の製造方法によれば、外部端子用はんだバンプを形成してから樹脂のコーティングが行われ、その後、絶縁基板に半導体チップが実装される。したがって、外部端子用はんだバンプの表面に樹脂が残存することがあり、その場合には、絶縁基板に実装した際に接続不良が発生することになる。

【0011】

以上のように、BGA型半導体パッケージにおいてスルーホール内にはんだボールを形成する場合には、クリームはんだを用いる必要があったり、クリームはんだを用いずに配線パターンを変形させて突起を形成する場合であっても限定的な効果が得られるのみであった。また、外部端子用はんだバンプを形成後、はんだバンプを補強する樹脂をコーティングする場合には、はんだバンプの接合部への樹脂の付着を防止するのが困難であった。

【0012】

本発明は上記の問題点に鑑みてなされたものであり、したがって本発明は、外部端子用はんだバンプにかかる応力を低減し、はんだバンプ接合部におけるクラックの発生が防止された半導体装置、電子回路装置および製造方法を提供することを目的とする。

【0013】

【課題を解決するための手段】

上記の目的を達成するため、本発明の半導体装置は、半導体基板と、前記半導体基板の一方の面である第1面側に形成された半導体素子と、前記半導体基板を搭載する絶縁基板と、前記半導体基板と前記絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、前記絶縁基板に形成され、前記配線パターンに達するスルーホールと、前記スルーホール内の側面を被覆する絶縁層と、前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有することを特徴とする。

【0014】

本発明の半導体装置は、好適には、前記スルーホール埋め込み部は、前記はんだバンプに比較して機械的強度が大きい金属からなることを特徴とする。

本発明の半導体装置は、好適には、前記絶縁層は、前記絶縁基板に比較して低弾性率の絶縁性樹脂からなり、前記スルーホール埋め込み部と前記配線パターンとの接合部で発生する応力を緩和することを特徴とする。

本発明の半導体装置は、好適には、前記スルーホール埋め込み部と前記はんだバンプとの接合部は、前記絶縁基板の表面よりも突出していることを特徴とする。

【0015】

本発明の半導体装置は、好適には、前記絶縁層は、前記スルーホール内の側面と前記スルーホール近傍の絶縁基板表面とを被覆することを特徴とする。本発明の半導体装置は、さらに好適には、前記スルーホール埋め込み部と前記はんだバンプとの接合部は、前記スルーホール近傍の前記絶縁層の表面よりも突出していることを特徴とする。

本発明の半導体装置は、好適には、隣接するスルーホールに形成された前記絶縁層は、相互に分離されていることを特徴とする。あるいは、本発明の半導体装置は、好適には、隣接するスルーホールに形成された前記絶縁層は、一体化されていることを特徴とする。

本発明の半導体装置は、好適には、前記絶縁基板は可撓性絶縁基板であることを特徴とする。

【0016】

これにより、絶縁基板に形成されたスルーホールを埋め込む導電体にクラックが発生するのを防止することができる。本発明の半導体装置によれば、スルーホール内に応力を低減する絶縁性樹脂を介して、機械的強度の大きい金属が埋め込まれる。したがって、接続部のクラックの発生が防止され、半導体装置の長期的な接続信頼性が改善される。

【0017】

上記の目的を達成するため、本発明の半導体装置は、半導体基板と、前記半導体基板の一方の面である第1面側に形成された半導体素子と、前記半導体基板を、前記第1面を介して搭載する可撓性絶縁基板と、前記半導体基板と前記可撓性絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、前記配線パターンと前記半導体素子とを接続する接続部と、前記配線パターンと前記半導体基板の前記第1面との間に形成された封止樹脂層と、前記可撓性絶縁基板に形成され、前記配線パターンに達するスルーホールと、前記スルーホール内の側面を被覆する絶縁層と、前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有することを特徴とする。

本発明の半導体装置は、好適には、前記接続部ははんだバンプであることを特徴とする。

【0018】

これにより、表面実装型のパッケージにおいて、絶縁基板に形成されたスルーホールの接続信頼性を向上させることができる。本発明の半導体装置によれば、スルーホール内に応力を低減する絶縁性樹脂を介して、機械的強度の大きい導電性材料を埋め込むことにより、接続部におけるクラックの発生が防止され、長期的な接続信頼性を改善することができる。

【0019】

上記の目的を達成するため、本発明の半導体装置は、半導体基板と、前記半導体基板の一方の面である第1面側に形成された半導体素子と、前記半導体基板を、前記第1面の裏面である第2面を介して搭載する可撓性絶縁基板と、前記半導体基板と前記可撓性絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、前記半導体基板の外部に形成され、前記配線パターンと前記半導体素子とを接続するボンディングワイヤーと、前記半導体基板および前記ボンディングワイヤーを被覆する封止樹脂層と、前記可撓性絶縁基板に形成され、前記配線パターンに達するスルーホールと、前記スルーホール内の側面を被覆する絶縁層と、前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有することを特徴とする。

【0020】

これにより、ワイヤーボンディング法により形成されたパッケージにおいて、絶縁基板に形成されたスルーホールの接続信頼性を向上させることができる。本発明の半導体装置によれば、スルーホール内に応力を低減する絶縁性樹脂を介して、機械的強度の大きい導電性材料を埋め込むことにより、接続部におけるクラックの発生が防止され、半導体装置の長期的な接続信頼性を改善することができる。

【0021】

上記の目的を達成するため、本発明の半導体装置は、半導体基板と、前記半導体基板の一方の面である第1面側に形成された半導体素子と、前記半導体基板を、前記第1面を介して搭載する可撓性絶縁基板と、前記半導体基板と前記可撓性絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、前記配線パターンと前記半導体素子とを接続する接続部と、前記配線パターンと前記半導体基板の前記第1面との間に形成された封止樹脂層と、前記可撓性絶縁基板に形成され、前記配線パターンに達するスルーホールと、前記スルーホール内の側面を被覆する絶縁層と、前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、前記スルーホール埋め込み部に接続する電極部を表面に有し、前記可撓性絶縁基板を介して前記半導体基板を搭載する実装基板とを有することを特徴とする。

【0022】

これにより、LGA(land grid array)型のパッケージにおいて、絶縁基板に形成されたスルーホールの接続信頼性を向上させることができる。本発明の半導体装置によれば、スルーホール内に応力を低減する絶縁性樹脂を介して、機械的強度の大きい導電性材料を埋め込むことにより、接続部におけるクラックの発生が防止され、半導体装置の長期的な接続信頼性を改善することができる。

さらに、従来のLGA型の半導体装置のようにはんだバンプを形成しないことにより、接続高さを低減させ、半導体装置を小型化することが可能となる。

【0023】

上記の目的を達成するため、本発明の半導体装置は、半導体基板と、前記半導体基板の一方の面である第1面側に形成された半導体素子と、前記半導体基板を搭載する絶縁基板と、前記半導体基板と前記絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、前記絶縁基板に形成され、前記配線パターンに達するスルーホールと、前記スルーホール内の少なくとも側面を被覆する導電性樹脂層と、前記スルーホール内に前記導電性樹脂層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有し、前記導電性樹脂層は、前記絶縁基板に比較して低弾性率の材料からなり、前記スルーホール埋め込み部と前記配線パターンとの接合部で発生する応力を緩和する。

【0024】

これにより、絶縁基板に形成されたスルーホールを埋め込む導電体にクラックが発生するのを防止することができる。本発明の半導体装置によれば、スルーホール内に応力を低減する導電性樹脂を介して、機械的強度の大きい金属が埋め込まれる。したがって、接続部のクラックの発生が防止され、半導体装置の長期的な接続信頼性が改善される。

【0025】

上記の目的を達成するため、本発明の電子回路装置は、第1の基板と、前記第1の基板の一方の面である第1面側に形成された電子回路素子と、前記第1の基板を搭載する第2の基板と、前記第1の基板と前記第2の基板との層間に形成され、前記電子回路素子に電気的に導通する配線パターンと、前記第2の基板に形成され、前記配線パターンに達するスルーホールと、前記スルーホール内の側面を被覆する絶縁層と、前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有することを特徴とする。

【0026】

これにより、基板に形成されたスルーホールを埋め込む導電体にクラックが発生するのを防止することができる。本発明の電子回路装置によれば、スルーホール内に応力を低減する絶縁性樹脂を介して、機械的強度の大きい金属が埋め込まれる。したがって、接続部のクラックの発生が防止され、電子回路装置の長期的な接続信頼性が改善される。

【0027】

上記の目的を達成するため、本発明の半導体装置の製造方法は、半導体基板の一方の面である第1面側に半導体素子を形成する工程と、絶縁基板の表面に配線パターンを形成する工程と、前記絶縁基板に、前記配線パターンに達するスルーホールを形成する工程と、前記スルーホール内の側面に絶縁層を形成する工程と、前記スルーホール内に前記絶縁層を介して、導電体からなるスルーホール埋め込み部を形成する工程と、前記配線パターンと前記半導体素子とが接続するように、前記絶縁基板に前記半導体基板を搭載する工程と、前記スルーホール埋め込み部の表面に、外部端子となるはんだバンプを形成する工程とを有することを特徴とする。

【0028】

本発明の半導体装置の製造方法は、好適には、前記スルーホール埋め込み部を形成する工程は、前記はんだバンプに比較して機械的強度が大きい金属を材料に用いることを特徴とする。

本発明の半導体装置の製造方法は、好適には、前記絶縁層を形成する工程は、前記スルーホール埋め込み部と前記配線パターンとの接合部で発生する応力を緩和させる、前記絶縁基板に比較して低弾性率の絶縁性樹脂を材料に用いることを特徴とする。

【0029】

本発明の半導体装置の製造方法は、好適には、前記スルーホール埋め込み部を形成する工程は、前記配線パターンに通電して電解めっきを行う工程であることを特徴とする。

本発明の半導体装置の製造方法は、好適には、前記スルーホール埋め込み部を形成する工程は、前記導電体が前記絶縁基板の表面よりも突出するまで電解めっきを行う工程であることを特徴とする。

【0030】

本発明の半導体装置の製造方法は、好適には、前記絶縁層を形成する工程は、前記スルーホール内の側面と前記絶縁基板表面とを被覆するように前記絶縁層を形成する工程であることを特徴とする。

本発明の半導体装置の製造方法は、さらに好適には、前記スルーホール埋め込み部を形成する工程は、前記導電体が前記絶縁基板を被覆する前記絶縁層の表面よりも突出するまで電解めっきを行う工程であることを特徴とする。

本発明の半導体装置の製造方法は、好適には、隣接するスルーホール間の前記基板表面に形成された前記絶縁層の一部を除去し、前記絶縁層を分断する工程を有することを特徴とする。

【0031】

本発明の半導体装置の製造方法は、好適には、前記はんだバンプを形成する工程は、ほぼ球状のはんだボールを形成する工程と、前記はんだボールを前記スルーホール埋め込み部の表面に移載する工程と、加熱して前記はんだボールを溶融させ、前記スルーホール埋め込み部の表面を被覆する前記はんだバンプを形成する工程とを有することを特徴とする。

本発明の半導体装置の製造方法は、好適には、前記絶縁基板は可撓性絶縁基板であることを特徴とする。

【0032】

本発明の半導体装置の製造方法は、好適には、前記絶縁基板に前記半導体基板を搭載する工程は、前記配線パターンの表面に接続部を形成する工程と、前記半導体素子が前記接続部に接するように、前記半導体基板を前記第1面を介して前記絶縁基板に搭載する工程と、前記配線パターンと前記半導体基板の前記第1面との間に封止樹脂層を形成する工程とを有することを特徴とする。

本発明の半導体装置の製造方法は、好適には、前記接続部を形成する工程は、はんだバンプを形成する工程であることを特徴とする。

【0033】

あるいは、本発明の半導体装置の製造方法は、好適には、前記絶縁基板に前記半導体基板を搭載する工程は、前記半導体基板を、前記第1面の裏面である第2面を介して前記絶縁基板に搭載する工程であり、前記絶縁基板に前記半導体基板を搭載した後、前記半導体基板の外部に、前記配線パターンと前記半導体素子とを接続するボンディングワイヤーを形成する工程と、前記半導体基板および前記ボンディングワイヤーを被覆する封止樹脂層を形成する工程とを有することを特徴とする。

【0034】

これにより、半導体チップを搭載する絶縁基板を、他の基板等に接続・実装するためのスルーホール内に、簡略な工程で導電体を埋め込むことが可能となる。本発明の半導体装置の製造方法によれば、好適には電解めっきによりスルーホール内に金属材料を埋め込むため、従来の製造方法の場合のように、クリームはんだを充填する工程や、はんだボールを形成し、はんだボールをリフローさせる工程が不要となる。また、はんだバンプを形成するためのリフロー工程が不要であることから、材料を低融点金属に限定する必要がなく、機械的強度の大きい金属を使用することができる。したがって、スルーホールの接続部におけるクラックの発生を防止することができる。

【0035】

【発明の実施の形態】

以下に、本発明の半導体装置およびその製造方法の実施の形態について、図面を参照して説明する。

(実施形態1)

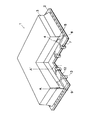

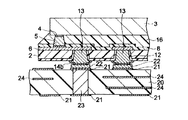

図1は本実施形態の半導体装置の斜視図であり、図2は図1のA−A’に対応する断面図である。

図1および図2に示す半導体装置1は、可撓性の絶縁基板2の上面に半導体チップ3が主面(図示しない半導体集積回路が形成された面)を下向きにして搭載されている。半導体チップ3の主面には、半導体チップ3に形成された半導体集積回路に接続する電極パッド4が形成されている。電極パッド4とはんだバンプ5との間にはバンプ下地金属(不図示)が形成されている。

【0036】

はんだバンプ5は可撓性絶縁基板2上の配線パターン6に設けられたランド7に接続する。絶縁基板2の配線パターン6はオーバーコート8により被覆されており、オーバーコート8の開口部がランド7となっている。配線パターン6は半導体装置1の端部まで延在し、後述する電解めっき工程においてめっきリード9としても利用される。配線パターン6の他端は外部端子用ランド10に接続する。外部端子用ランド10部分の絶縁基板2にはスルーホール11が形成され、スルーホール11には絶縁性樹脂層12を介してスルーホール埋め込み部13が形成されている。スルーホール埋め込み部13は外部端子用ランド10に接続している。スルーホール埋め込み部13の表面に酸化防止層14bを介して外部端子用はんだバンプ17が形成されている。

【0037】

本実施形態の半導体装置によれば、スルーホール11内がスルーホール埋め込み部13により埋め込まれるため、スルーホール内をはんだバンプで埋め込む場合のようにクリームはんだを充填する必要がない。また、スルーホール11内に絶縁性樹脂層12が形成されていることにより、スルーホール11内の金属と配線パターン6との接合部における応力が低減され、長期的な接続信頼性が改善される。

【0038】

次に、上記の本実施形態の半導体装置の製造方法について説明する。

まず、図3(a)に示すように、例えば銅箔6aなどの金属薄膜に絶縁性樹脂2aを塗布する。銅箔6aは配線パターン6になり、絶縁性樹脂2aは絶縁基板2となる。絶縁性樹脂2aとしては例えばポリイミドやエポキシ樹脂等を用いることができる。

【0039】

次に、図3(b)に示すように、絶縁基板2をパターニングすることによりスルーホール11を形成する。絶縁性樹脂2aとして例えば感光性の熱硬化性ポリイミドを使用する場合には、所定のパターンが形成されたフォトマスクを用いて紫外線を露光し、その後、現像液を用いた現像と熱硬化を行うことによりスルーホール11が形成される。

あるいは、絶縁性樹脂2aとして非感光性の熱硬化性ポリイミドを使用する場合には、ポリイミドを銅箔6aに塗布しベーキングを行った後、ポリイミド上にフォトレジストをラミネートし、レジストのパターニングを行う。このフォトレジストをマスクとしてポリイミドをエッチングし、スルーホール11を形成する。

【0040】

また、絶縁性樹脂2aとして紫外線硬化型のエポキシ樹脂を使用する場合には、エポキシ樹脂を塗布後、フォトマスクを用いて露光し、現像することによりスルーホール11が形成される。

絶縁性樹脂2aとして熱硬化型のエポキシ樹脂を使用する場合には、スルーホール11の形成部分を被覆するパターンが形成されたメッシュスクリーンを用いて、銅箔6a上にエポキシ樹脂をスクリーン印刷する。樹脂を印刷後、熱硬化させることによりスルーホール11以外の部分に絶縁基板2が形成される。

【0041】

上記のような方法によりスルーホール11を形成する以外に、金型を用いた打ち抜きやレーザ加工等によってスルーホール11を形成してもよい。また、上記のように銅箔6aに絶縁性樹脂2aを塗布する以外に、絶縁性樹脂からなるフィルムに接着剤を用いて銅箔6aをラミネートしてもよい。

上記の銅箔6aの厚さは例えば12〜18μm、絶縁性樹脂2aの厚さは例えば20〜50μmとする。また、スルーホール11のピッチは例えば0.5mm、スルーホール11の口径は例えば240μmとする。

【0042】

続いて、図3(c)に示すように、レジスト(不図示)をマスクとして銅箔6aにエッチングを行い、配線パターン6を形成する。

次に、図3(d)に示すように、絶縁性樹脂をスルーホール11が形成された側の反対側の面に塗布することにより、オーバーコート8を形成する。オーバーコート8をパターニングして開口を設け、ランド7を形成する。オーバーコート8としては上記の絶縁性樹脂2aと同様の樹脂を用いることができる。オーバーコート8のランド7部分を開口するには、上記の絶縁性樹脂2aにスルーホール11を形成する場合と同様に行うことができる。オーバーコート8の厚さは例えば10〜30μmとする。

【0043】

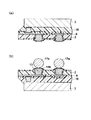

次に、図4(a)に示すように、スルーホール11が形成された側に絶縁性樹脂12を塗布、成膜する。絶縁性樹脂12には上記の絶縁性樹脂2aおよびオーバーコート8と同様の樹脂を用いることができる。絶縁性樹脂12としては、スルーホール11内のスルーホール埋め込み部13にかかる熱応力を低減させる目的で、弾性率の低い材料を用いることが好ましく、例えば、弾性率を0.1〜5GPaとする。絶縁性樹脂12の厚さは例えば20μmとする。

【0044】

次に、図4(b)に示すように、スルーホール11内の配線パターン6に接続する部分の絶縁性樹脂12を除去する。絶縁性樹脂12の一部を選択的に除去するには、上記の絶縁性樹脂2aにスルーホール11を形成する場合、あるいはオーバーコート8のランド7部分を除去する場合と同様に行うことができる。

【0045】

次に、図4(c)に示すように、配線パターン6の端部をめっきリード9として電解を行い、スルーホール11内にスルーホール埋め込み部13を形成する。スルーホール埋め込み部13としては例えば銅を用いることができる。絶縁性樹脂12の厚さが例えば20μmである場合、スルーホール埋め込み部13のめっき厚は23μm程度とし、表面がスルーホール11から突出した形状の埋め込み部13を形成する。

【0046】

さらに、図4(d)に示すように、ランド7とスルーホール埋め込み部13の表面にそれぞれ酸化防止層14a、14bを形成する。酸化防止層14a、14bはめっきリード9を用いた電解めっきか、あるいは無電解めっきにより形成することができる。酸化防止層14a、14bとしては例えば、厚さ3μmのニッケルめっきと厚さ0.03〜0.05μmのフラッシュ金めっきとの積層膜を用いることができる。

【0047】

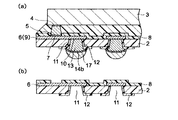

次に、図5(a)に示すように、半導体チップ3の主面に電極パッド4を介してはんだバンプ5を形成する。はんだバンプ5を絶縁基板2上のランド7に位置合わせし、半導体チップ3を絶縁基板2に搭載する。半導体チップ3の主面に形成された電極パッド4のピッチは例えば150μm、電極パッド4の大きさは例えば一辺の長さを110μmとする。

電極パッド4とはんだバンプ5の間のバンプ下地金属(不図示)は、半導体チップ3とはんだバンプ5との密着性を高めるため、あるいは半導体チップ3の電極材料とはんだバンプ5の材料との相互拡散を防止する目的で設けられる。バンプ下地金属としては例えば、厚さ5μmのニッケルめっきと厚さ0.05μmの金めっきとの積層膜を用いることができる。その他にもクロム、銅あるいはチタン、タングステンの積層膜などをバンプ下地金属として用いることができる。

【0048】

はんだバンプ5としてはSn−Pbの共晶はんだの他に、Sn−Ag系、Sn−Ag−Cu系、Sn−Ag−Bi系、Sn−Zn系などの鉛レスはんだを用いることもできる。はんだバンプ5の高さは例えば60μmとする。

絶縁基板2に半導体チップ3を搭載する前に、あらかじめ、絶縁基板2のランド7にフラックス(例えばロジン系樹脂、有機酸、ワックスおよび高沸点グリコールの混合物)15を塗布しておく。あるいは、はんだバンプ5のランド7に接合する部分にフラックス15を塗布しておく。

その後、図5(b)に示すように、半導体チップ3を加熱してはんだバンプ5を溶融させ、はんだバンプ5を電極パッド4およびランド7に接合させる。はんだ付けの温度は通常220〜240℃で行う。

【0049】

次に、図6(a)に示すように、フラックス15の残渣を洗浄してから、可撓性絶縁基板2と半導体チップ3との間の空間を封止樹脂16により封止する。

続いて、図6(b)に示すように、スルーホール11内のスルーホール埋め込み部13の表面に形成された酸化防止層14bにフラックス(不図示)を供給する。ここで、図6(b)は図2〜図6(a)と上下を反転させて表示してある。酸化防止層14b上にフラックスを介して、はんだボール17aを形成する。はんだボール17aの直径は例えば、スルーホール11のピッチが0.5mmである場合に0.3〜0.4mmとする。

【0050】

次に、図2に示すように、リフロー装置等を用いてはんだボール17aを溶融させ、外部端子用はんだバンプ17を形成する。リフローの際に生じるフラックス残渣を、必要に応じて洗浄・除去する。

その後、ウェハ上に一括形成された複数の半導体装置1を、個々の半導体装置に個片化するための切断を行う。この個片化は、例えば金型を用いた打ち抜き、レーザ加工、ルーター加工、回転ブレードを用いたダイシング等により行うことができる。

以上の工程により、図1および図2に示す半導体装置1が得られる。

【0051】

上記の本実施形態の半導体装置の製造方法によれば、電解めっきによりスルーホール内を埋め込むため、クリームはんだを充填したり、スルーホールにはんだボールを移載し、リフローする工程が不要となる。したがって、簡略な工程で接続信頼性の高い半導体装置を形成することができる。

【0052】

(実施形態2)

図7(a)に本実施形態の半導体装置の断面図を示す。図7に示す半導体装置においては実施形態1の半導体装置1と同様に、可撓性の絶縁基板2の上面に半導体チップ3が主面(図示しない半導体集積回路が形成された面)を下向きにして搭載されている。半導体チップ3の主面には、半導体チップ3に形成された半導体集積回路に接続する電極パッド4が形成されている。電極パッド4とはんだバンプ5との間にはバンプ下地金属(不図示)が形成されている。

【0053】

はんだバンプ5は可撓性絶縁基板2上の配線パターン6に設けられたランド7に接続する。絶縁基板2の配線パターン6はオーバーコート8により被覆されており、オーバーコート8の開口部がランド7となっている。配線パターン6は外部端子用ランド10に接続し、外部端子用ランド10部分の絶縁基板2にはスルーホール11が形成されている。スルーホール11には絶縁性樹脂12を介してスルーホール埋め込み部13が形成されている。スルーホール埋め込み部13は外部端子用ランド10に接続している。

【0054】

実施形態1の半導体装置(図2参照)においては、絶縁性樹脂12がスルーホール11以外の部分の絶縁基板2を被覆するように形成されているが、本実施形態の半導体装置においては、絶縁性樹脂12はスルーホール11内の側壁と、スルーホール11周囲のみを被覆するように形成されている。

本実施形態の半導体装置のように、スルーホール11近傍にのみ絶縁性樹脂12が形成された構造とすることにより、絶縁性樹脂12の分断箇所で応力が緩和されることになる。したがって、実施形態1の半導体装置に比較して、さらに外部端子用はんだバンプ17にかかる応力を低減させることができる。

【0055】

上記の本実施形態の半導体装置は、実施形態1の図2〜図6に示す工程にほぼ沿って形成することができる。まず、絶縁基板2と銅箔6aとを一体化させてから、絶縁基板2にスルーホール11を形成する。スルーホール11内を含む絶縁基板2の表面に絶縁性樹脂12を成膜する。銅箔6aの表面にオーバーコート8を形成してから、ランド7上のオーバーコート8に開口部を設ける。

【0056】

次に、図7(b)に示すように、スルーホール11内の絶縁性樹脂12が配線パターン6に接続する部分を除去する。また、隣接するスルーホール11間に形成された絶縁性樹脂12の一部を除去し、スルーホール11間で絶縁基板2が露出した状態とする。

その後、実施形態1の製造方法と同様にして、スルーホール11内に例えば銅からなるスルーホール埋め込み部13を形成する。また、ランド7とスルーホール埋め込み部13の表面にそれぞれ、例えばニッケルめっきとフラッシュ金めっきとの積層膜からなる酸化防止層14a、14bを形成する。さらに、半導体チップ3の主面に電極パッド4を介してはんだバンプ5を形成し、はんだバンプ5を絶縁基板2上のランド7に位置合わせして、半導体チップ3を絶縁基板2に搭載する。

【0057】

半導体チップ3を加熱してはんだバンプ5を溶融させ、はんだバンプ5を電極パッド4およびランド7に接合させる。また、絶縁基板2と半導体チップ3との間の空間を封止樹脂16により封止する。続いて、スルーホール埋め込み部13の表面に酸化防止層14bおよびフラックス(不図示)を介して、はんだボール17aを形成する。さらに、はんだボール17aを溶融させて外部端子用はんだバンプ17を形成する。その後、ウェハ上に一括形成されている複数の半導体装置を切断して個片化する。

以上の工程により、図7(a)に示す半導体装置が得られる。

【0058】

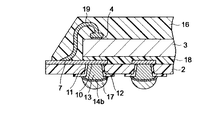

(実施形態3)

図8に本実施形態の半導体装置の断面図を示す。本実施形態の半導体装置においては、絶縁基板2と半導体チップとがダイボンディング材18を介して接合されており、実施形態1あるいは2に示されるはんだバンプ5は形成されない。半導体チップ3は主面(図示しない半導体集積回路が形成された面)を上向きにして搭載され、半導体チップ3の表面に形成された電極パッド4とランド7とがボンディングワイヤー19を介して接続されている。半導体チップ3の上部および側面とボンディングワイヤー19は封止樹脂16により封止されている。

【0059】

本実施形態は、ワイヤーボンディング法により絶縁基板2と半導体チップ3とが接続された半導体装置において、絶縁基板2のスルーホール11内に絶縁性樹脂12を介してスルーホール埋め込み部13が形成されたものである。図8は実施形態2と同様に絶縁性樹脂12がスルーホール間で分断されている例を示すが、絶縁性樹脂12は実施形態1と同様にスルーホール間の絶縁基板2を連続して被覆する形状であってもよい。

上記の本実施形態の半導体装置によれば、ワイヤーボンディング法により絶縁基板2と半導体チップ3とが接続された半導体装置においても、絶縁基板に形成された外部端子用はんだバンプにかかる応力を低減させることができる。したがって、半導体装置の長期信頼性を向上させることができる。

【0060】

上記の本実施形態の半導体装置を形成するには、まず、実施形態1の図3(a)〜図4(a)に示す工程と同様にして、絶縁基板2と銅箔6aとを一体化させ、絶縁基板2にスルーホール11を形成する。スルーホール11内を含む絶縁基板2の表面に絶縁性樹脂12を成膜する。

次に、配線パターンに接続する部分の絶縁性樹脂12(スルーホール11の底面の絶縁性樹脂12)を除去する。図8に示すように、スルーホール間で絶縁性樹脂12が分断された構造とする場合には、隣接するスルーホール11間に形成された絶縁性樹脂12の一部を除去し、スルーホール11間で絶縁基板2が露出した状態とする。

【0061】

次に、実施形態1の製造方法と同様にして、スルーホール11内に例えば銅からなるスルーホール埋め込み部13を形成する。また、スルーホール埋め込み部13の表面に、例えばニッケルめっきとフラッシュ金めっきとの積層膜からなる酸化防止層14bを形成する。

続いて、絶縁基板2の配線パターン6が形成された側にダイボンディング材18を塗布する。ダイボンディング材18としては例えば熱硬化性樹脂が用いられる。その後、絶縁基板2上にダイボンディング材18を介して半導体チップ3を載置し、ダイボンディング材18を加熱硬化させる。

【0062】

次に、配線パターン6のランド7と半導体チップ3の電極パッド4との間を、例えばAlまたはAuからなるボンディングワイヤー19を用いて接続する(ワイヤーボンディング工程)。

その後、熱硬化性樹脂からなる封止樹脂16を用いて半導体チップ3およびボンディングワイヤー19を封止する。続いて、スルーホール埋め込み部13の表面に酸化防止層14およびフラックス(不図示)を介して、はんだボールを形成する。さらに、はんだボールを溶融させて外部端子用はんだバンプ17を形成する。その後、ウェハ上に一括形成されている複数の半導体装置を切断して個片化する。

以上の工程により、図8に示す半導体装置が得られる。

【0063】

(実施形態4)

本実施形態の半導体装置の断面図を図9に示す。本実施形態の半導体装置によれば、実施形態1あるいは2に示す半導体装置と同様にスルーホール11内の側壁を被覆する絶縁性樹脂12が形成されるが、外部端子用はんだバンプ17は形成されない。図9に、スルーホール埋め込み部13をプリント配線板(ボード)20のパッド21に、クリームはんだ22を介して接続させたLGA(landgrid array)型のCSP(chip size packageまたはchip scale package)の例を示す。

【0064】

LGAはBGA同様に、半導体チップを実装した絶縁基板の底面側に接続端子が二次元的に配列された表面実装型のパッケージであり、多ピン化された場合にもピン間隔の狭ピッチ化を避けられ、パッケージ寸法を縮小できるという利点を有する。LGAは接続部分にリードがなくパッドしか形成されないパッケージであり、半導体チップは絶縁基板の底面に形成されたコネクタを介してプリント配線板に実装される。

LGA型のCSPにおいてはコネクタの接続信頼性と、コネクタの付加による実質的なサイズの増大とを改善することが課題となっている。従来、はんだ接続高さを高くして応力を分散させ、コネクタの接続信頼性の改善が図られていたが、その場合には実質的サイズが増大するという問題があった。

【0065】

本実施形態の半導体装置によれば、スルーホール11内に絶縁性樹脂12が形成されていることによりスルーホール11の界面における応力が低減され、クリームはんだ22のみでスルーホール埋め込み部13をプリント配線板20に接続させることができる。スルーホール埋め込み部13は、上記の従来のLGA型CSPにおけるコネクタに相当する。スルーホール埋め込み部13の表面に外部端子用はんだバンプを形成する必要がないため、プリント配線板に実装された半導体チップの取り付け高さを低くすることができ、半導体装置を用いた電子製品の実質的サイズを小型化させることが可能となる。

【0066】

上記の本実施形態の半導体装置は、実施形態1あるいは2と同様の方法にしたがって形成することができるが、スルーホール埋め込み部13の表面にはんだボールを形成する工程と、はんだボールをリフローさせる加熱工程が不要となる。したがって、上記の本発明の半導体装置は、簡略化された工程で製造することが可能であり、かつ、実装されるプリント配線板との接続信頼性が向上される。

【0067】

(実施形態5)

本実施形態の半導体装置の断面図を図10に示す。図10に示すように、スルーホール11内に絶縁層12(実施形態1〜4参照)のかわりに導電性樹脂層25を形成することにより、外部端子用はんだバンプにかかる応力を低減させることもできる。本実施形態に示すように、スルーホール内に低弾性率の導電性樹脂層25を形成する場合、ランド10に接続する部分の導電性樹脂層25を除去する必要はない。但し、隣接するスルーホール間のショートを防止するため、図10に示すようにスルーホール間の導電性樹脂層25は分断させる。

【0068】

本発明の半導体装置、電子回路装置および製造方法の実施形態は、上記の説明に限定されない。例えば、スルーホール内に形成される絶縁性樹脂の厚さは、スルーホール埋め込み部の応力が低減される範囲で適宜変更することが可能である。その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

【0069】

【発明の効果】

本発明の半導体装置によれば、半導体チップが搭載された絶縁基板を他の基板等に接続・実装するためのスルーホールにおいて、接合部の応力を低減してクラックの発生を防止し、接続信頼性を向上させることができる。

本発明の電子回路装置によれば、基板を他の基板等に接続・実装するためのスルーホールにおいて、接合部の応力を低減してクラックの発生を防止し、接続信頼性を向上させることができる。

本発明の半導体装置の製造方法によれば、半導体チップが搭載された絶縁基板を他の基板等に実装するためのスルーホール内に、簡略な工程で接合部の応力を低減してクラックの発生を防止できる導電体を形成することができる。

【図面の簡単な説明】

【図1】本発明の実施形態1にかかる半導体装置の斜視図である。

【図2】本発明に実施形態1にかかる半導体装置の断面図であり、図1のA−A’における断面図である。

【図3】(a)〜(d)は本発明の実施形態1にかかる半導体装置の製造方法の製造工程を示す断面図であり、配線パターンのオーバーコートを形成する工程までを示す。

【図4】(a)〜(d)は本発明の実施形態1にかかる半導体装置の製造方法の製造工程を示す断面図であり、スルーホール埋め込み部の表面に酸化防止層を形成する工程までを示す。

【図5】(a)および(b)は本発明の実施形態1にかかる半導体装置の製造方法の製造工程を示す断面図であり、半導体チップと絶縁基板を接続するはんだバンプを形成する工程までを示す。

【図6】(a)および(b)は本発明の実施形態1にかかる半導体装置の製造方法の製造工程を示す断面図であり、スルーホール埋め込み部の表面にはんだボールを形成する工程までを示す。

【図7】(a)は本発明の実施形態2にかかる半導体装置の断面図であり、(b)は本発明の実施形態2にかかる半導体装置の製造方法の製造工程を示す断面図である。

【図8】本発明の実施形態3にかかる半導体装置の断面図である。

【図9】本発明の実施形態4にかかる半導体装置の断面図である。

【図10】本発明の実施形態5にかかる半導体装置の断面図である。

【図11】従来の半導体装置の断面図である。

【符号の説明】

1、101…半導体装置、2、102…絶縁基板(実装基板)、2a…絶縁性樹脂、3、103…半導体チップ、4、104…電極パッド、5、105…はんだバンプ、6、106…配線パターン、6a…銅箔、7、107…ランド、8、108…オーバーコート、9…めっきリード、10…外部端子用ランド、11、110…スルーホール、12…絶縁性樹脂層、13…スルーホール埋め込み部、14a、14b…酸化防止層、15…フラックス、16、109…封止樹脂、17…外部端子用はんだバンプ、17a…はんだボール、18…ダイボンディング材、19…ボンディングワイヤー、20…プリント配線板、21…パッド、22…クリームはんだ、23…コンタクトホール、24…導電層、25…導電性樹脂層。

Claims (28)

- 半導体基板と、

前記半導体基板の一方の面である第1面側に形成された半導体素子と、

前記半導体基板を搭載する絶縁基板と、

前記半導体基板と前記絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、

前記絶縁基板に形成され、前記配線パターンに達するスルーホールと、

前記スルーホール内の側面を被覆する絶縁層と、

前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、

前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有する

半導体装置。 - 前記スルーホール埋め込み部は、前記はんだバンプに比較して機械的強度が大きい金属からなる

請求項1記載の半導体装置。 - 前記絶縁層は、前記絶縁基板に比較して低弾性率の絶縁性樹脂からなり、前記スルーホール埋め込み部と前記配線パターンとの接合部で発生する応力を緩和する

請求項1記載の半導体装置。 - 前記スルーホール埋め込み部と前記はんだバンプとの接合部は、前記絶縁基板の表面よりも突出している

請求項1記載の半導体装置。 - 前記絶縁層は、前記スルーホール内の側面と前記スルーホール近傍の絶縁基板表面とを連続的に被覆する

請求項1記載の半導体装置。 - 前記スルーホール埋め込み部と前記はんだバンプとの接合部は、前記スルーホール近傍の前記絶縁層の表面よりも突出している

請求項5記載の半導体装置。 - 隣接するスルーホールに形成された前記絶縁層は、相互に分離されている

請求項5記載の半導体装置。 - 隣接するスルーホールに形成された前記絶縁層は、一体化されている

請求項5記載の半導体装置。 - 前記絶縁基板は可撓性絶縁基板である

請求項1記載の半導体装置。 - 半導体基板と、

前記半導体基板の一方の面である第1面側に形成された半導体素子と、

前記半導体基板を、前記第1面を介して搭載する可撓性絶縁基板と、

前記半導体基板と前記可撓性絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、

前記配線パターンと前記半導体素子とを接続する接続部と、

前記配線パターンと前記半導体基板の前記第1面との間に形成された封止樹脂層と、

前記可撓性絶縁基板に形成され、前記配線パターンに達するスルーホールと、

前記スルーホール内の側面を被覆する絶縁層と、

前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、

前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有する

半導体装置。 - 前記接続部は、はんだバンプである

請求項10記載の半導体装置。 - 半導体基板と、

前記半導体基板の一方の面である第1面側に形成された半導体素子と、

前記半導体基板を、前記第1面の裏面である第2面を介して搭載する可撓性絶縁基板と、

前記半導体基板と前記可撓性絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、

前記半導体基板の外部に形成され、前記配線パターンと前記半導体素子とを接続するボンディングワイヤーと、

前記半導体基板および前記ボンディングワイヤーを被覆する封止樹脂層と、

前記可撓性絶縁基板に形成され、前記配線パターンに達するスルーホールと、

前記スルーホール内の側面を被覆する絶縁層と、

前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、

前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有する

半導体装置。 - 半導体基板と、

前記半導体基板の一方の面である第1面側に形成された半導体素子と、

前記半導体基板を、前記第1面を介して搭載する可撓性絶縁基板と、

前記半導体基板と前記可撓性絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、

前記配線パターンと前記半導体素子とを接続する接続部と、

前記配線パターンと前記半導体基板の前記第1面との間に形成された封止樹脂層と、

前記可撓性絶縁基板に形成され、前記配線パターンに達するスルーホールと、

前記スルーホール内の側面を被覆する絶縁層と、

前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、

前記スルーホール埋め込み部に接続する電極部を表面に有し、前記可撓性絶縁基板を介して前記半導体基板を搭載する実装基板とを有する

半導体装置。 - 半導体基板と、

前記半導体基板の一方の面である第1面側に形成された半導体素子と、

前記半導体基板を搭載する絶縁基板と、

前記半導体基板と前記絶縁基板との層間に形成され、前記半導体素子に電気的に導通する配線パターンと、

前記絶縁基板に形成され、前記配線パターンに達するスルーホールと、

前記スルーホール内の少なくとも側面を被覆する導電性樹脂層と、

前記スルーホール内に前記導電性樹脂層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、

前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有し、

前記導電性樹脂層は、前記絶縁基板に比較して低弾性率の材料からなり、前記スルーホール埋め込み部と前記配線パターンとの接合部で発生する応力を緩和する

半導体装置。 - 第1の基板と、

前記第1の基板の一方の面である第1面側に形成された電子回路素子と、

前記第1の基板を搭載する第2の基板と、

前記第1の基板と前記第2の基板との層間に形成され、前記電子回路素子に電気的に導通する配線パターンと、

前記第2の基板に形成され、前記配線パターンに達するスルーホールと、

前記スルーホール内の側面を被覆する絶縁層と、

前記スルーホール内に前記絶縁層を介して形成され、前記配線パターンに接続し、導電体からなるスルーホール埋め込み部と、

前記スルーホール埋め込み部に接続し、外部端子となるはんだバンプとを有する

電子回路装置。 - 半導体基板の一方の面である第1面側に半導体素子を形成する工程と、

絶縁基板の表面に配線パターンを形成する工程と、

前記絶縁基板に、前記配線パターンに達するスルーホールを形成する工程と、

前記スルーホール内の側面に絶縁層を形成する工程と、

前記スルーホール内に前記絶縁層を介して、導電体からなるスルーホール埋め込み部を形成する工程と、

前記配線パターンと前記半導体素子とが接続するように、前記絶縁基板に前記半導体基板を搭載する工程と、

前記スルーホール埋め込み部の表面に、外部端子となるはんだバンプを形成する工程とを有する

半導体装置の製造方法。 - 前記スルーホール埋め込み部を形成する工程は、前記はんだバンプに比較して機械的強度が大きい金属を材料に用いる

請求項16記載の半導体装置の製造方法。 - 前記絶縁層を形成する工程は、前記スルーホール埋め込み部と前記配線パターンとの接合部で発生する応力を緩和させる、前記絶縁基板に比較して低弾性率の絶縁性樹脂を材料に用いる

請求項16記載の半導体装置の製造方法。 - 前記スルーホール埋め込み部を形成する工程は、前記配線パターンに通電して電解めっきを行う工程である

請求項16記載の半導体装置の製造方法。 - 前記スルーホール埋め込み部を形成する工程は、前記導電体が前記絶縁基板の表面よりも突出するまで電解めっきを行う工程である

請求項19記載の半導体装置の製造方法。 - 前記絶縁層を形成する工程は、前記スルーホール内の側面と前記絶縁基板表面とを被覆するように前記絶縁層を形成する工程である

請求項16記載の半導体装置の製造方法。 - 前記スルーホール埋め込み部を形成する工程は、前記導電体が前記絶縁基板を被覆する前記絶縁層の表面よりも突出するまで電解めっきを行う工程である

請求項21記載の半導体装置の製造方法。 - 隣接するスルーホール間の前記基板表面に形成された前記絶縁層の一部を除去し、前記絶縁層を分断する工程を有する

請求項22記載の半導体装置の製造方法。 - 前記はんだバンプを形成する工程は、ほぼ球状のはんだボールを形成する工程と、

前記はんだボールを前記スルーホール埋め込み部の表面に移載する工程と、

加熱して前記はんだボールを溶融させ、前記スルーホール埋め込み部の表面を被覆する前記はんだバンプを形成する工程とを有する

請求項16記載の半導体装置の製造方法。 - 前記絶縁基板は可撓性絶縁基板である

請求項16記載の半導体装置の製造方法。 - 前記絶縁基板に前記半導体基板を搭載する工程は、前記配線パターンの表面に接続部を形成する工程と、

前記半導体素子が前記接続部に接するように、前記半導体基板を前記第1面を介して前記絶縁基板に搭載する工程と、

前記配線パターンと前記半導体基板の前記第1面との間に封止樹脂層を形成する工程とを有する

請求項16記載の半導体装置の製造方法。 - 前記接続部を形成する工程は、はんだバンプを形成する工程である

請求項26記載の半導体装置の製造方法。 - 前記絶縁基板に前記半導体基板を搭載する工程は、前記半導体基板を、前記第1面の裏面である第2面を介して前記絶縁基板に搭載する工程であり、

前記絶縁基板に前記半導体基板を搭載した後、前記半導体基板の外部に、前記配線パターンと前記半導体素子とを接続するボンディングワイヤーを形成する工程と、

前記半導体基板および前記ボンディングワイヤーを被覆する封止樹脂層を形成する工程とを有する

請求項16記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP34910399A JP4045708B2 (ja) | 1999-12-08 | 1999-12-08 | 半導体装置、電子回路装置および製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP34910399A JP4045708B2 (ja) | 1999-12-08 | 1999-12-08 | 半導体装置、電子回路装置および製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001168224A JP2001168224A (ja) | 2001-06-22 |

| JP4045708B2 true JP4045708B2 (ja) | 2008-02-13 |

Family

ID=18401521

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP34910399A Expired - Fee Related JP4045708B2 (ja) | 1999-12-08 | 1999-12-08 | 半導体装置、電子回路装置および製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4045708B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4695796B2 (ja) * | 2001-09-27 | 2011-06-08 | 富士通セミコンダクター株式会社 | 半導体装置、半導体装置ユニットおよびその製造方法 |

| JP4599121B2 (ja) * | 2004-09-08 | 2010-12-15 | イビデン株式会社 | 電気中継板 |

| KR100833209B1 (ko) | 2006-11-28 | 2008-05-28 | 삼성전자주식회사 | 열팽창에 의한 미스매치를 해결할 수 있는 원주형 회전결합체 및 이를 포함하는 반도체 소자 |

| JP6705718B2 (ja) * | 2016-08-09 | 2020-06-03 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| JP2022161250A (ja) * | 2021-04-08 | 2022-10-21 | イビデン株式会社 | プリント配線板およびプリント配線板の製造方法 |

-

1999

- 1999-12-08 JP JP34910399A patent/JP4045708B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001168224A (ja) | 2001-06-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN103066051B (zh) | 封装基板及其制作工艺、半导体元件封装结构及制作工艺 | |

| US6441500B1 (en) | Semiconductor device having resin members provided separately corresponding to externally connecting electrodes | |

| JP3450236B2 (ja) | 半導体装置及びその製造方法 | |

| JP3277997B2 (ja) | ボールグリッドアレイパッケージとその製造方法 | |

| US6887778B2 (en) | Semiconductor device and manufacturing method | |

| JPH1167968A (ja) | ボールグリッドアレーパッケージ用印刷回路基板及びボールグリッドアレーパッケージ並びにそれらの製造方法 | |

| JP2000022027A (ja) | 半導体装置、その製造方法およびパッケージ用基板 | |

| KR20020096985A (ko) | 회로 장치 및 그 제조 방법 | |

| JP2003007916A (ja) | 回路装置の製造方法 | |

| JP3732378B2 (ja) | 半導体装置の製造方法 | |

| JP4045708B2 (ja) | 半導体装置、電子回路装置および製造方法 | |

| JP2009164493A (ja) | 配線基板及びその製造方法並びに電子部品装置及びその製造方法 | |

| KR100843705B1 (ko) | 금속 범프를 갖는 반도체 칩 패키지 및 그 제조방법 | |

| JPH10321750A (ja) | 半導体装置および半導体チップを搭載する配線基板の製造方法 | |

| JP4626063B2 (ja) | 半導体装置の製造方法 | |

| JP3084648B2 (ja) | 半導体装置 | |

| JP4525148B2 (ja) | 半導体装置およびその製造方法 | |

| US7671477B2 (en) | Technique for moderating stresses cause by a difference in thermal expansion coeffiecients between a substrate and an electronic component | |

| JP3417292B2 (ja) | 半導体装置 | |

| JPH1022440A (ja) | 半導体装置及びその製造方法 | |

| JP2006351950A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP3889311B2 (ja) | プリント配線板 | |

| KR100343454B1 (ko) | 웨이퍼 레벨 패키지 | |

| JP4322903B2 (ja) | 半導体装置、および半導体装置の製造方法 | |

| JPH08330472A (ja) | 半導体装置とその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060315 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070803 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070814 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071009 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071030 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071112 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101130 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111130 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121130 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |