JP4443728B2 - クロック発生回路 - Google Patents

クロック発生回路 Download PDFInfo

- Publication number

- JP4443728B2 JP4443728B2 JP2000173475A JP2000173475A JP4443728B2 JP 4443728 B2 JP4443728 B2 JP 4443728B2 JP 2000173475 A JP2000173475 A JP 2000173475A JP 2000173475 A JP2000173475 A JP 2000173475A JP 4443728 B2 JP4443728 B2 JP 4443728B2

- Authority

- JP

- Japan

- Prior art keywords

- clock

- circuit

- internal

- external

- potential

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/0805—Details of the phase-locked loop the loop being adapted to provide an additional control signal for use outside the loop

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/10—Distribution of clock signals, e.g. skew

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

- G11C7/222—Clock generating, synchronizing or distributing circuits within memory device

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/133—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals using a chain of active delay devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/135—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals by the use of time reference signals, e.g. clock signals

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/07—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop using several loops, e.g. for redundant clock signal generation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0814—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the phase shifting device being digitally controlled

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0816—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the controlled phase shifter and the frequency- or phase-detection arrangement being connected to a common input

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/087—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using at least two phase detectors or a frequency and phase detector in the loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/091—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector using a sampling device

Description

【発明の属する技術分野】

この発明は、半導体記憶装置に使用されるクロック発生回路に関し、より特定的には、外部クロックに同期した内部クロックを発生するクロック発生回路に関する。

【0002】

【従来の技術】

SDRAM(Synchronous Dynamic Random Access Memory)に代表される、外部クロックに同期して動作する半導体デバイスにおいては、半導体デバイスの内部にクロック発生回路を具備し、外部クロックに同期した内部クロック信号をクロック発生回路によって生成し、半導体デバイスの内部回路は、この内部クロックを用いて制御されるのが一般的である。

【0003】

すなわち、半導体デバイスが外部との間でデータを授受するためのデータ入出力インタフェースを制御する回路も、このような内部クロックを用いて制御される。このため、データ入出力のタイミングは、内部クロックの位相精度の影響を大きく受ける。以下においては、代表例としてSDRAMのデータ出力のタイミングについて説明する。

【0004】

図22は、SDRAMにおけるデータ出力タイミングを説明するタイミングチャートである。

【0005】

図22を参照して、外部クロックEXT./CLKの立上りエッジが、基準電位VREFを超えたタイミング(時刻t0)において、クロック入力回路は外部クロックEXT.CLKの入力を認識する。クロック入力回路は、時刻t0からtD1経過後の時刻t1において、内部クロックCLKIを活性化する。この遅延tD1は、クロック入力回路で生じる位相遅延に相当する。

【0006】

内部クロックCLKIをトリガとしてデータ出力動作が開始され、時刻t1からtD2経過後の時刻t2において、出力データDOUTが出力される。したがって、外部クロックEXT.CLKが基準電位VREFを超えてから、出力データDOUTが出力ターミネートレベルである電位VTTを超えるまでの時間で定義されるアクセス時間tACは、クロック入力回路において生じる遅延tD1と、データ出力動作時に生じる遅延tD2との和となる。通常のSDRAMにおいて、このアクセス時間tACの規格値は、3nsec〜6nsecと厳しく、クロック入力回路において生じる遅延tD1がアクセスタイムtACに大きな影響を及ぼす。

【0007】

一方、半導体デバイスの高周波動作化の要求に伴って、外部クロックエッジと半導体デバイスに対する入出力タイミングとの位相差を小さくすることが要求されている。半導体デバイスの動作の基準となる外部クロックの周波数が高くなるにつれて、外部クロックエッジとデータ入出力タイミングとの位相のずれが外部クロックの周期に対して相対的に大きくなり、無視できなくなるためである。すなわち、半導体デバイスに対するコマンドおよびデータの授受を外部クロックエッジを基準として正確に実行するには、クロックエッジと入出力インタフェースの動作タイミングとの間の位相差をできるだけ小さくする必要がある。

【0008】

図23は、DDR−SDRAM(Double Data Rate−SDRAM)のデータ出力タイミングを示すタイミングチャートである。

【0009】

図23を参照して、DDR−SDRAMにおいては、アクセスタイムtACは、外部クロックEXT.CLKとその反転クロックであるEXT./CLKとの電位レベルの交点に相当する時刻t0から、出力データDOUTが出力ターミネートレベル電位VTTを超える時刻t1までの間の経過時間で示される。

【0010】

外部クロックの立上り/立下りエッジの両方に同期してデータを入出力するDDR−SDRAMにおいては、必然的にアクセスタイムtACは小さい値となることが要求され、一般的なアクセスタイムtACのスペックは±0.75nsec程度である。このようなアクセスタイムのスペックを満足するためには、外部クロックEXT.CLKと内部クロックCLKIとの間の位相差、すなわち外部クロックに基づく内部クロック生成時に生じる位相遅延tD1を制御できるクロック発生回路を内部に具備する必要がある。このようなクロック発生回路として、通常、可変遅延回路と位相比較器から構成されるDLL(Delay Locked Loop)、もしくはPLL(Phase Locked Loop)といった回路が適用されていた。

【0011】

次に、従来DDR−SDRAMに適用されていたDLLを用いたクロック発生回路の構成を説明する。

【0012】

図24は、DLLを用いた従来の技術のクロック発生回路500の構成を示すブロック図である。

【0013】

図24を参照して、クロック発生回路500は、クロック入力回路125と、可変遅延回路130と、レプリカ回路140,160と、位相比較器200と、遅延制御回路150とを備える。

【0014】

クロック入力回路125は、相補クロックを形成する、外部クロックEXT.CLKおよびその反転クロックEXT./CLKの電位レベルの交点を検出し、内部クロックCLK1を生成する。クロック入力回路125で内部クロックCLK1の生成に要する時間をtD1と表記すれば、内部クロックCLK1は、この時点で相補クロックの電位レベルの交点から既に遅延tD1だけ位相が遅れている。

【0015】

可変遅延回路130は、内部クロックCLK1をさらに遅延して、内部動作クロックCLK2を生成する。データ出力制御回路50は、内部動作クロックCLK2に応答して動作し、データDOUTをデータ入出力端子EXT.DQに出力する。

【0016】

ここで、外部クロックEXT.CLKの周期をtCLKとし、内部動作クロックCLK2が活性化されてからデータDOUTが出力されるまでの所要時間をtD2とすると、遅延制御回路150によって、可変遅延回路130の遅延時間を“tCLK−(tD1+tD2)”と設定することによって、アクセスタイムtACを、外部クロック周期tCLKと等しくすることができる。この場合、半導体デバイス外部から、データ出力インタフェースを見ると、アクセスタイムtACは等価的に0となり、外部クロックエッジに同期したタイミングで、データ出力が実行されることになる。

【0017】

可変遅延回路130の遅延値を、上述したように“tCLK−(tD1+tD2)”とするために、内部動作クロックCLK2は、2個のレプリカ回路140,160によってさらに遅延されて、リターンクロックRCLKとして位相比較器200に入力される。ここで、レプリカ回路140は、データ出力制御回路50で生じる遅延量tD2に相当する遅延を、内部動作クロックCLK2に対して模擬的に付与する回路である。同様に、レプリカ回路160は、クロック入力回路125で生じる遅延量tD1に相当する遅延を、レプリカ回路140の出力に対して模擬的に付与する回路である。

【0018】

位相比較器200は、レプリカ回路160が出力するリターンクロックRCLKと、1サイクル後の内部クロックCLK1との位相比較を実行し、その位相差に基づいて、可変遅延回路130の遅延量を増/減するための制御信号UP/DOWNを生成する。

【0019】

遅延制御回路150は、制御信号UPおよびDOWNに基づいて、遅延制御信号CTRLを生成し、可変遅延回路130の遅延量を調節する。内部クロックCLK1とリターンクロックRCLKとの位相が一致した場合には、遅延制御信号CTRLはある固定値となり、可変遅延回路130の遅延量は固定される。この状態で、内部クロックCLK1とリターンクロックRCLKとの位相は一致している。以下においては、この状態を「ロック状態」とも称する。

【0020】

したがって、内部動作クロックCLK2は、クロック入力回路125が出力する内部クロックCLK1よりも、レプリカ回路140および160で与えられる遅延量だけ位相が早い信号となる。このため、レプリカ回路140および160の遅延量の和が、正確に(tD2+tD1)と一致した場合には、可変遅延回路130の遅延値は“tCLK−(tD1+tD2)”となるため、見かけ上のアクセスタイムtACは、上述したように0となる。

【0021】

図25は、DDR−SDRAMに用いられるクロック発生回路の他の構成を示すブロック図である。

【0022】

図25を参照して、クロック発生回路510は、外部クロックEXT.CLKの立上りエッジと立下りエッジとの両方にそれぞれ対応して、内部動作クロックFCLK2およびBCLK2を生成する。

【0023】

すなわち、クロック発生回路510は、外部クロックEXT.CLKの立上りエッジに応答して内部クロックFCLK1を生成するクロック入力回路125aと、外部クロックEXT.CLKの立下りエッジに応答して内部クロックBCLK1を生成するクロック入力回路125bとを備える。クロック発生回路510は、内部クロックFCLK1およびBCLK1それぞれに対応して、可変遅延回路130aおよび130bを有する、いわゆるデュアルディレイライン構成を有している。

【0024】

可変遅延回路130aは、内部クロックFCLK1を遅延して内部動作クロックFCLK2を生成し可変遅延回路130bは、内部クロックBLCK1を遅延して、内部動作クロックBCLK2を生成する。データ出力制御回路50は、内部動作クロックFCLK2およびBCLK2の両方に応答してデータ出力を実行する。

【0025】

可変遅延回路130a、レプリカ回路140,160、位相比較器200、および遅延制御回路150によって形成される、クロック発生回路500と同様のDLL経路が、内部クロックFCLK1に対して設けられ、内部動作クロックFCLK2に応答したデータ出力タイミングを外部クロックEXT.CLKの立上りエッジと同期させることができる。

【0026】

また、EXT.CLKの立下りエッジに応答して生成される内部クロックBCLK1についても、可変遅延回路130aと同一の遅延量が可変遅延回路130bによって付与されるため、内部動作クロックFCLK2とBCLK2とを一定周期で交互に活性化することができる。

【0027】

この結果、半導体デバイス外部から見れば、外部クロックEXT.CLKの立上りエッジと立下りエッジとの両方に同期して、等価的にアクセスタイムtAC=0の状態で、データ出力が実行される。

【0028】

【発明が解決しようとする課題】

DLLを用いた従来のクロック発生回路の問題点を、タイミングチャートを用いて説明する。

【0029】

図26は、従来のクロック発生回路500の動作を示すタイミングチャートである。

【0030】

図26(a)は、正常のタイミングでデータ出力を行なう場合を示している。図26(a)を参照して、外部クロックEXT.CLKおよび反転クロックEXT./CLKの電位レベルが等しくなる時刻t0からクロック入力回路による遅延tD1経過後の時刻t1において、内部クロックCLK1が活性化される。

【0031】

DLL動作によって、リターンクロックRCLKは、内部クロックCLK1と位相が一致する。内部動作クロックCLK2は、内部クロックCLK1より、レプリカ回路140および160による遅延時間の和“tR2+tR1”だけ早い位相で発生する。出力データDoutは、出力トリガ信号CLK2の活性化タイミングよりtD2遅延した時刻t0において出力される。

【0032】

ここで、レプリカ回路160および140で設定される遅延量が、クロック入力回路125における遅延量tD1およびデータ出力制御回路150における遅延量tD2とそれぞれ等しいため、アクセスタイムtACは等価的に0となる。

【0033】

図26(b)には、外部クロックEXT.CLKおよび反転クロックEXT./CLKの立上りおよび立下りのスルーレートが小さく、立上り/立下り時間が大きい場合が示される。この場合には、クロック入力回路125で発生する遅延時間tD1が図26(a)の場合より大きくなってしまう。このため、クロック入力回路の実際の遅延時間tD1が、レプリカ回路160で設定される遅延時間tR1よりも大きくなってしまい、これに対応して、出力データDOUTの出力タイミングは、外部クロックEXT.CLKと同期しなくなり、アクセスタイムtACがプラス側に発生してしまう。

【0034】

反対に、図26(c)に示されるように、外部クロックEXT.CLKおよび反転クロックEXT./CLKの立上りおよび立下りのスルーレートが大きく、立上り/立下り時間が小さい場合には、クロック入力回路125の実際の遅延時間tD1が、図26(b)の場合とは反対に、レプリカ回路160に設定される遅延時間tR1よりも小さくなってしまう。この結果、外部クロックEXT.CLKとデータ出力タイミングとは同期しなくなり、アクセスタイムtACがマイナス側に発生してしまう。

【0035】

以上述べたように、クロック入力回路で生じる遅延を予め予測して、これをDLL内に設けられたレプリカ回路によって補償する従来のクロック発生回路の構成では、外部クロックのスルーレートの変動に応じてアクセス時間tACが変動してしまう。

【0036】

さらに、アクセスタイムtACは、外部クロックEXT.CLKおよび反転クロックEXT./CLKの交点の電位レベルの変動によっても生じる。さらに、外部クロックの波形の変動のみならず、電源電圧、電源ノイズ、温度条件およびプロセス変動などによって、レプリカ回路およびクロック入力回路で実際に生じる遅延量が、所定の設計値からずれることによっても、アクセスタイムtACは変動してしまう。これらの要因によってアクセスタイムtACの変動が大きくなると、データ出力タイミングの規格を満たすことができず、半導体デバイスとして正常に動作することができない。

【0037】

この発明は、このような問題点を解決するためになされたものであって、この発明の目的は、クロック入力回路で生じる遅延量の変動の影響を受けることなく、外部クロックに対する位相差の変動の小さい内部クロックを生成することが可能なクロック発生回路を提供することである。

【0038】

【課題を解決するための手段】

請求項1記載のクロック発生回路は、所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、外部クロックおよび外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、第1の内部クロックは、外部クロックおよび外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、第1の内部クロックを遅延して、動作クロックとして内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、第2の内部クロックを内部回路における所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、外部クロックおよび外部基準クロックの電位レベルが交差する位相と、第3の内部クロックの位相とを比較する第1の位相比較器と、第1の位相比較器の位相比較結果に基づいて、第1の可変遅延回路の遅延量を制御する第1の遅延制御回路と、第3の内部クロックを第1のクロック入力回路で生じる遅延に相当する第2の所定時間さらに遅延して、第4の内部クロックを生成する第2の模擬遅延回路と、第1の内部クロックと第4の内部クロックとの位相を比較する第2の位相比較器とを備える。第1の遅延制御回路は、第1および第2の位相比較器の位相比較結果に基づいて、第1の可変遅延回路の遅延量を制御する。

【0040】

請求項2記載のクロック発生回路は、所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、外部クロックおよび外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、第1の内部クロックは、外部クロックおよび外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、第1の内部クロックを遅延して、動作クロックとして内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、第2の内部クロックを内部回路における所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、外部クロックおよび外部基準クロックの電位レベルが交差する位相と、第3の内部クロックの位相とを比較する第1の位相比較器と、第1の位相比較器の位相比較結果に基づいて、第1の可変遅延回路の遅延量を制御する第1の遅延制御回路と、外部クロックおよび外部基準クロックを受けて、第1の内部クロックと相補の第1の内部サブクロックを生成する第2のクロック入力回路と、第1の内部サブクロックを遅延して、動作クロックとして内部回路に供給される第2の内部サブクロックを生成する第2の可変遅延回路と、第3の内部クロックを第1のクロック入力回路で生じる遅延に相当する第2の所定時間さらに遅延して、第4の内部クロックを生成する第2の模擬遅延回路と、第1の内部クロックと第4の内部クロックとの位相を比較する第2の位相比較器とを備える。第1の遅延制御回路は、第1および第2の位相比較器の位相比較結果に基づいて、第1および第2の可変遅延回路の遅延量を共通に制御する。

【0041】

請求項3記載のクロック発生回路は、所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、外部クロックおよび外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、第1の内部クロックは、外部クロックおよび外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、第1の内部クロックを遅延して、動作クロックとして内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、第2の内部クロックを内部回路における所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、外部クロックおよび外部基準クロックの電位レベルが交差する位相と、第3の内部クロックの位相とを比較する第1の位相比較器と、第1の位相比較器の位相比較結果に基づいて、第1の可変遅延回路の遅延量を制御する第1の遅延制御回路と、外部クロックおよび外部基準クロックを受けて、第1の内部クロックと相補の第1の内部サブクロックを生成する第2のクロック入力回路と、第1の内部サブクロックを遅延して、動作クロックとして内部回路に供給される第2の内部サブクロックを生成する第2の可変遅延回路と、第2の内部クロックおよび第2の内部サブクロックを受けて、一定の選択周期に基づいていずれか一方を第1の模擬遅延回路に送出するクロック選択回路とを備える。第1の模擬遅延回路は、クロック選択回路が送出するクロックを第1の所定時間さらに遅延して、第3の内部クロックを生成する。クロック発生回路は、第1の位相比較器の位相比較結果に基づいて、第1の遅延制御回路とは独立に第2の可変遅延回路の遅延量を制御する第2の遅延制御回路をさらに備える。

【0042】

請求項4記載のクロック発生回路は、所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、外部クロックおよび外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、第1の内部クロックは、外部クロックおよび外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、第1の内部クロックを遅延して、動作クロックとして内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、第2の内部クロックを内部回路における所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、外部クロックおよび外部基準クロックの電位レベルが交差する位相と、第3の内部クロックの位相とを比較する第1の位相比較器と、第1の位相比較器の位相比較結果に基づいて、第1の可変遅延回路の遅延量を制御する第1の遅延制御回路と、外部クロックおよび外部基準クロックを受けて、第1の内部クロックと相補の第1の内部サブクロックを生成する第2のクロック入力回路と、第1の内部サブクロックを遅延して、動作クロックとして内部回路に供給される第2の内部サブクロックを生成する第2の可変遅延回路と、第2の内部サブクロックを第1の所定時間さらに遅延して、第3の内部サブクロックを生成する第2の模擬遅延回路と、外部クロックおよび外部基準クロックの電位レベルが交差する位相と、第3の内部サブクロックの位相とを比較する第2の位相比較器と、第2の位相比較器の位相比較結果に基づいて、第2の可変遅延回路の遅延量を制御する第2の遅延制御回路とを備える。

【0043】

請求項5記載のクロック発生回路は、所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、外部クロックおよび外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、第1の内部クロックは、外部クロックおよび外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、第1の内部クロックを遅延して、動作クロックとして内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、第2の内部クロックを内部回路における所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、外部クロックおよび外部基準クロックの電位レベルが交差する位相と、第3の内部クロックの位相とを比較する第1の位相比較器と、第1の位相比較器の位相比較結果に基づいて、第1の可変遅延回路の遅延量を制御する第1の遅延制御回路とを備える。第1の位相比較器は、第3の内部クロックの電位レベルに応じて、外部クロックおよび外部基準クロックの電位レベル差を第1および第2の内部ノード間の電位レベル差に変換する電位差変換回路と、第1および第2の内部ノードの電位レベル差を増幅して増幅結果を保持する差動増幅回路とを含み、電位差変換回路は、第1の内部ノードと電気的に結合され、外部クロックをゲートに受ける第1のトランジスタと、第2の内部ノードと電気的に結合され、外部基準クロックをゲートに受ける第2のトランジスタと、第3の内部クロックの電位レベルに応じてオンして、電位差変換回路および差動増幅回路に動作電流を供給するための電流供給トランジスタとを有する。差動増幅回路は、増幅結果に基づいて、第1の可変遅延回路の遅延量を増加するための第1の制御信号および、第1の可変遅延回路の遅延量を減少するための第2の制御信号のいずれか一方を活性化する。

【0044】

請求項6記載のクロック発生回路は、請求項5記載のクロック発生回路であって、差動増幅回路は、第1および第2の内部ノードのいずれか一方と電気的に結合されるゲートを有し、第2の電位を供給するノードと第1および第2の内部ノードとの間にそれぞれ設けられる第3および第4のトランジスタと、第1および第2の内部ノードの電位レベルに応じて、第1および第2の制御信号の信号レベルを設定するフリップフロップ回路とを有する。

【0045】

請求項7記載のクロック発生回路は、請求項5記載のクロック発生回路であって、差動増幅回路は、第3の内部ノードと電気的に結合されるゲートを有し、第2のノードと第4のノードとの間に電気的に結合される第3のトランジスタと、第4の内部ノードと電気的に結合されるゲートを有し、第1のノードと第3のノードとの間に電気的に結合される第4のトランジスタと、第2の電位を供給する電位供給ノードと第3の内部ノードとの間に電気的に結合され、第4の内部ノードと電気的に結合されるゲートを有する第5のトランジスタと、電位供給ノードと第4の内部ノードとの間に電気的に結合され、第3の内部ノードと電気的に結合されるゲートを有する第6のトランジスタと、電流供給トランジスタと相補的にオンして、電位供給ノードと第3および第4の内部ノードとをそれぞれ電気的に結合する第7および第8のトランジスタと、第3および第4の内部ノードの電位レベルにそれぞれ応じて、第1および第2の制御信号をそれぞれ生成する第1および第2の論理ゲートとを有する。

【0046】

請求項8記載のクロック発生回路は、所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、外部クロックおよび外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、第1の内部クロックは、外部クロックおよび外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、第1の内部クロックを遅延して、動作クロックとして内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、第2の内部クロックを内部回路における所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、外部クロックおよび外部基準クロックの電位レベルが交差する位相と、第3の内部クロックの位相とを比較する第1の位相比較器と、第1の位相比較器の位相比較結果に基づいて、第1の可変遅延回路の遅延量を制御する第1の遅延制御回路とを備える。第1の位相比較器は、第1のタイミング信号の活性化に応答して、外部クロックおよび外部基準クロックの電位レベル差を第1および第2の内部ノード間の電位レベル差に変換する電位差変換回路と、第1および第2の内部ノードの電位レベル差を増幅して、第1および第2の内部ノードのそれぞれ電位レベルを第1および第2の電位のいずれか一方ずつに設定する増幅結果を保持する差動増幅回路と、第2のタイミング信号の活性化に応答して、電位差変換回路に動作電流を供給する第1の電流供給回路と、第3のタイミング信号の活性化に応答して、差動増幅回路に動作電流を供給する第2の電流供給回路とを含み、第1および第2のタイミング信号は、第3の内部クロックが第1の電位から第2の電位に遷移する遷移タイミングよりも先に活性化され、第2のタイミング信号は、第3の内部クロックの遷移タイミングよりも後に非活性化され、第3のタイミング信号は、第2のタイミング信号の非活性化後に活性化され、第1および第3のタイミング信号は、第3の内部クロックが第2の電位から第1の電位に遷移するタイミングにおいて非活性化され、差動増幅回路は、第1および第2の内部ノードの電位レベルに応じて、第1の可変遅延回路の遅延量を増加するための第1の制御信号および、第1の可変遅延回路の遅延量を減少するための第2の制御信号のいずれか一方を活性化する。

【0047】

請求項9記載のクロック発生回路は、所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、外部クロックおよび外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、第1の内部クロックは、外部クロックおよび外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、第1の内部クロックを遅延して、動作クロックとして内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、第2の内部クロックを内部回路における所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、外部クロックおよび外部基準クロックの電位レベルが交差する位相と、第3の内部クロックの位相とを比較する第1の位相比較器と、第1の位相比較器の位相比較結果に基づいて、第1の可変遅延回路の遅延量を制御する第1の遅延制御回路とを備える。第1の位相比較器は、第3の内部クロックの電位レベルに応じて動作し、外部クロックを第1のノードに伝達するための第1の信号伝達ゲートと、第1の信号伝達ゲートと同一のタイミングで動作し、外部基準クロックを第1のノードに伝達するための第2の信号伝達ゲートと、第1および第2の内部ノードの電位レベル差を増幅して、増幅結果を保持する差動増幅回路と、第3の内部クロックの電位レベルに応じて動作し、差動増幅回路に動作電流を供給する電流供給回路とを含み、第1および第2の信号伝達ゲートと電流供給回路とは、相補的にオン/オフし、差動増幅回路は、増幅結果に基づいて、第1の可変遅延回路の遅延量を所定量増加するための第1の制御信号および、第1の可変遅延回路の遅延量を所定量減少するための第2の制御信号のいずれか一方を活性化する。

【0048】

請求項10記載のクロック発生回路は、請求項9記載のクロック発生回路であって、差動増幅回路は、第1および第2の内部ノードの電位レベル差を増幅して、第1および第2の内部ノードの電位レベルを第1および第2の電位のいずれか一方ずつに設定する交差結合型アンプを含み、電流供給回路は、第1の電位を供給する第1の電位供給ノードと差動増幅回路との間に電気的に結合される第1のトランジスタと、第2の電位を供給する第2の電位供給ノードと差動増幅回路との間に電気的に結合される第2のトランジスタとを有し、第1および第2のトランジスタは、第1および第2の信号伝達ゲートと相補的にオン/オフする。

【0054】

【発明の実施の形態】

以下において、本発明の実施の形態について図面を参照して詳しく説明する。なお、図中における同一符号は同一または相当部分を示し、その説明は繰返さない。

【0055】

[実施の形態1]

図1は、本発明の実施の形態1に従うクロック発生回路を具備する半導体記憶装置10の構成を示す概略ブロック図である。

【0056】

図1を参照して、半導体記憶装置10は、アドレス端子12と、コマンド制御端子14と、クロック端子16と、データ入力端子18と、データ出力端子19と、コントロール回路20と、メモリコア30と、データ入力ラッチ回路40と、データ出力制御回路50と、クロック発生回路100とを備える。図1においては、半導体記憶装置の全体構成のうち、データ入出力に関する主要部分のみが代表的に示される。

【0057】

アドレス端子12は、アドレスビットA0〜Ai(i:自然数)からなる(i+1)ビットのアドレス信号の入力を受ける。コマンド制御端子14は、ロウアドレスストローブ信号/RAS、コラムアドレスストローブ信号/CAS、ライトイネーブル信号/WEおよびチップセレクト信号/CS等のコマンド制御信号の入力を受ける。クロック端子16は、外部クロックEXT.CLKの入力を受ける。外部クロックとしては、EXT.CLKと相補の反転クロックEXT./CLKやEXT.CLKの立上りエッジを規定するための基準電位VREFも合わせて入力される。

【0058】

コントロール回路20は、外部クロックEXT.CLKに同期したタイミングで、アドレス信号およびコマンド制御信号を取込み、取り込んだアドレス信号およびコマンド制御信号に応答して、メモリコア30に対するコマンドCMDおよびアドレス信号ADDを生成する。メモリコア30は、コマンドCMDおよびアドレス信号ADDに応答した動作を実行し、データの読出および書込を実行する。

【0059】

クロック発生回路100は、外部クロックEXT.CLKに同期した内部動作クロックCLK2を生成する。データ入力ラッチ回路40およびデータ出力制御回路50は、内部動作クロックCLK2に応答して動作し、データ入力端子18における入力データDINのラッチおよび、データ出力端子19における出力データDOUTの出力をそれぞれ実行する。

【0060】

図2は、実施の形態1に従うクロック発生回路100の構成を示すブロック図である。

【0061】

図2を参照して、クロック発生回路100は、クロック入力回路120と、可変遅延回路130と、レプリカ回路140と、位相比較器200と、遅延制御回路150とを備える。

【0062】

クロック入力回路120は、外部クロックEXT.CLKに基づいて内部クロックCLK1を生成する。可変遅延回路130は、内部クロックCLK1を遅延して、内部動作クロックCLK2を生成する。データ出力制御回路50は、内部動作クロックCLK2に応答して、データ出力端子19に対するデータ出力動作を開始する。データ出力制御回路50で生じる遅延はtD2で示される。

【0063】

レプリカ回路140は、内部動作クロックCLK2を、所定時間遅延してリターンクロックRCLKを出力する。レプリカ回路140の遅延量は、データ出力制御回路50で生じる遅延時間tD2と等しくなるように設計される。位相比較器200は、リターンクロックRCLKおよび外部クロックEXT.CLKの位相を直接比較し、位相比較結果に基づいて、可変遅延回路130の遅延量の増加および減少をそれぞれ指示するための制御信号UPおよびDOWN生成する。

【0064】

遅延制御回路150は、制御信号UPおよびDOWNに基づいて、可変遅延回路130の遅延量を制御する遅延制御信号CTRLの値を変化させる。可変遅延回路130が、デジタル的に遅延量を設定する構成である場合には、遅延制御信号CTRLは、遅延量を指示するための複数ビットのデジタル信号である。また、可変遅延回路130が、アナログ的に遅延量を設定する構成である場合には、遅延制御信号CTRLは、遅延量を指示するための電圧レベルを有するアナログ信号である。可変遅延回路130は、制御遅延信号CTRLに基づいて遅延量を設定する。

【0065】

このような構成とすることにより、位相比較器200が、リターンクロックRCLKの位相を直接外部クロックEXT.CLKの位相と直接比較するため、リターンクロックRCLKは、クロック入力回路で生ずる遅延を補償するためのレプリカ回路を通る必要がない。したがって、この半導体記憶装置におけるアクセスタイムtACは、外部クロック波形、電源電圧、電源ノイズ、温度条件、およびプロセス等の変動によって生じるクロック入力回路および、クロック入力回路で生じる遅延を補償するためのレプリカ回路における遅延量の変動の影響を受けることがなく、安定した値を保つことができる。

【0066】

なお、図2においては、位相比較器に対して、リターンクロックRCLKを直接入力する構成を示しているが、位相比較器への入力は、リターンクロックRCLKそのものではなく、リターンクロックの状態遷移タイミングに応答したタイミングで信号レベルが変化する制御信号(以下においては、このようなリターンクロックRCLKに派生する制御信号を総称して制御信号RCとも表す)でもよい。

【0067】

[実施の形態2]

図3は、実施の形態2に従うクロック発生回路101の構成を示すブロック図である。

【0068】

図3を参照して、クロック発生回路101は、互いに相補の外部クロックEXT.CLKおよびEXT./CLKを受けて、内部動作クロックCLK2を生成する。クロック発生回路101は、クロック入力回路125と、可変遅延回路130と、レプリカ回路140と、位相比較器210と、遅延制御回路150とを備える。

【0069】

クロック入力回路125は、互いに相補の外部クロックEXT.CLKおよびEXT./CLKを受けて、これらの電位レベル差に基づいて、内部クロックCLK1を生成する。可変遅延回路130は、内部クロックCLK1を遅延して内部動作クロックCLK2を生成する。レプリカ回路140は、図1の場合と同様に、内部動作クロックCLK2をデータ出力制御回路50で生じる遅延tD2に相当する所定時間さらに遅延させて、リターンクロックRCLKを生成する。

【0070】

位相比較器210は、互いに相補の外部クロックEXT.CLKおよびEXT./CLKと、リターンクロックRCLKとを受けて、外部クロックEXT.CLKおよびEXT./CLKの電位レベルが交差する位相と、リターンクロックRCLKの位相(状態遷移タイミング)とを直接位相比較し、位相比較結果に基づいて制御信号UPおよびDOWNを生成する。なお、位相比較器210に対しても、リターンクロックRCLKを直接入力せずに、制御信号RCを入力してもよい。

【0071】

遅延制御回路150は、制御信号UPおよびDOWNに基づいて、遅延制御信号CTRLを変化させる。可変遅延回路130は、遅延制御信号CTRLに基づいて遅延量を調節する。なお、制御信号UP,DOWNおよび遅延制御信号CTRLについては、すでに実施の形態1で説明したのと同様であるので、詳細な説明は繰り返さない。

【0072】

図4は、位相比較器210の構成例を示すブロック図である。

図4を参照して、位相比較器210は、ノードN1およびN2の電位差を増幅してラッチする差動増幅ラッチ回路215と、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベル差をノードN1およびN2の電位レベル差に変換する電位レベル差変換回路205とを含む。

【0073】

電位レベル差変換回路205は、ノードN1とノードNsとの間に電気的に結合されるN型MOSトランジスタT1と、ノードN2とノードNsとの間に電気的に結合されるN型MOSトランジスタT2と、ノードNsと接地電圧Vssとの間に電気的に結合されるN型MOSトランジスタT3とを含む。トランジスタT1およびT2のゲートには、互いに相補の外部クロックEXT.CLKおよびEXT./CLKがそれぞれ入力される。トランジスタT3のゲートには、制御信号RCが入力される。リターンクロックRCLKに応答する制御信号RCをトリガとして、ノードN1〜Ns間およびノードN2〜Ns間に電流経路が形成され、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの間の電位レベル差がノードN1およびN2に出力される。

【0074】

差動増幅ラッチ回路215は、ノードN1およびN2の電位差を増幅しラッチする。差動増幅ラッチ回路215にラッチされた情報が、制御信号UPもしくはDOWNに反映される。

【0075】

このように、外部の相補クロックEXT.CLKおよびEXT./CLKのそれぞれを直接差動ゲートで受け、かつ差動増幅のトリガをリターンクロックに応答する制御信号RCで行なうことによって、制御信号RCの電位レベルがLレベルからHレベルに遷移する状態遷移(活性化)のタイミングにおける、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベル差を増幅して、ノードN1およびN2に出力できる。したがって、制御信号RCの活性化タイミングが、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが交差するタイミングに対して早いか遅いかの判定結果を、制御信号UP,DOWNに反映して出力することが可能となる。

【0076】

図5は、位相比較器210の他の構成例を示すブロック図である。

図5を参照して、位相比較器210は、図4の構成例と同様に、差動増幅ラッチ回路215と電位レベル差変換回路205とを含む。

【0077】

電位差レベル変換回路205は、図4の構成例と異なり、N型MOSトランジスタT1およびT2と接地電位Vssとの間にそれぞれN型MOSトランジスタT3aおよびT3bを有する。トランジスタT3aおよびT3bのゲートには、リターンクロックRCLKに関連する制御信号RCが共通に入力される。

【0078】

このような構成とすることによっても、リターンクロックに関連する制御信号RCをトリガとして互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベル差がノードN1およびN2に出力されるので、図4に示される構成例と同様に、制御信号RCの活性化タイミングが、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが交差するタイミングに対して早いか遅いかの判定結果を制御信号UP,DOWNとして出力することが可能である。

【0079】

このような構成とすることにより、クロック発生回路101は、クロック発生回路100と同様に、外部クロック波形、電源電圧、電源ノイズ、温度条件、およびプロセス等の変動によって生じるクロック入力回路および、クロック入力回路で生じる遅延を補償するためのレプリカ回路における遅延量の変動がアクセスタイムtACに及ぼす影響を排除することができる。この結果、リターンクロックRCLKの位相と相補の外部クロックとの間において位相誤差の小さい正確なロック状態を確保できる内部動作クロックを用いて、半導体記憶装置のアクセスタイムtACを安定的に維持できる。

【0080】

[実施の形態3]

図6は、本発明の実施の形態3に従うクロック発生回路102の構成を示すブロック図である。

【0081】

図6を参照して、互いに相補の外部クロックEXT.CLKおよびEXT./CLKを受けて、データ出力のトリガ信号となる内部動作クロックCLK2を生成する。クロック発生回路102は、図3に示されるクロック発生回路101と比較して、位相比較器を2個備える点で異なる。

【0082】

クロック発生回路102は、図2に示されるクロック発生回路100と同様のDLLを形成する、クロック入力回路125、可変遅延回路130、レプリカ回路140、位相比較器210a、および遅延制御回路150を備える。このDLLの構成および動作は、すでに説明したのと同様であるので、説明は繰り返さない。

【0083】

クロック発生回路102は、さらにレプリカ回路140が出力するリターンクロックRCLK1をさらに遅延してリターンクロックRCLK2を生成するためのレプリカ回路160と、内部クロックCLK1とリターンクロックRCLK2との位相を比較する位相比較器210bとをさらに備える。

【0084】

レプリカ回路160の遅延量は、クロック入力回路125の遅延量tD1に対応して設定される。位相比較器210bは、内部クロックCLK1とリターンクロックRCLK2との位相を比較して、位相比較結果に基づいて可変遅延回路130の遅延量の増加および減少を指示するための制御信号UPbおよびDOWNb信号を生成する。

【0085】

位相比較器210aは、図3に示される位相比較器210と同様に、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが交差する位相と、レプリカ回路140が出力するリターンクロックRCLK1との位相を直接比較し、比較結果に基づいて、制御信号UPaおよびDOWNaを生成する。

【0086】

遅延制御回路150は、位相比較器210bが生成するUPb信号およびDOWNb信号に基づいて、遅延制御信号CTRLを変更する。可変遅延回路130の遅延量は、制御信号CTRLに応じて調整される。

【0087】

その後、可変遅延回路130の遅延量は、位相比較器210aが生成するUPa信号およびDOWNa信号に基づいて、さらに高い精度で調整される。

【0088】

このように、外部クロックの1周期に対応して、位相比較器210bによる粗い遅延調整および、位相比較器210aによる精密な遅延調整の両方を実行できるので、実施の形態1および2で示した、位相比較器によって外部クロックとの間で位相比較を直接実行することによる効果を享受しつつ、ロック状態に至るまでの所要時間を短縮し、位相調整を高速化できる。さらに、位相を合せ込むべきクロックエッジ(立上りエッジ/立下りエッジ)を取り違えることがなくなるので、ロック可能な周波数範囲を広く取ることができる。

【0089】

なお、図6においては、位相比較器210aおよび210bに、レプリカ回路が出力するリターンクロックRCLK1,RCLK2をそれぞれ直接入力する構成を示したが、位相比較器210aおよび210bのそれぞれへの入力は、リターンクロックRCLK1およびRCLK2そのものではなく、これらのリターンクロックの状態遷移タイミングに応答したタイミングで信号レベルが変化する制御信号であってもよい。

【0090】

[実施の形態4]

図7は、本発明の実施の形態4に従うクロック発生回路103の構成を示すブロック図である。

【0091】

図7を参照して、クロック発生回路103は、図25で示したクロック発生回路510の問題点を改善するためのものであり、可変遅延回路130aおよび130bを有するデュアルディレイライン構成となっている。

【0092】

図7を参照して、クロック発生回路103は、図6に示されるクロック発生回路102と比較して、外部クロックEXT.CLKの立下りエッジに応答して内部クロックBCLK1を生成するためのクロック入力回路125bと、クロック入力回路125bからの内部クロックBCLK1を遅延して内部動作クロックBCLK2を生成する可変遅延回路130bとをさらに備える点で異なる。クロック入力回路125aおよび可変遅延回路130aは、クロック発生回路102中のクロック入力回路125および可変遅延回路130に相当し、クロック入力回路125a、可変遅延回路130a、レプリカ回路140,160、および位相比較器210a、210bによって形成されるDLLの構成および動作は、クロック発生回路102と同様であるので説明は繰り返さない。

【0093】

可変遅延回路130bの遅延量は、遅延制御信号CTRLに応じて可変遅延回路130aと同一値が設定される。データ出力制御回路50は、内部動作クロックFCLK2およびBCLK2に応答して、出力データDOUTをデータ出力端子19に出力する。データ出力制御回路50は、外部クロックEXT.CLKの立上りエッジと立下りエッジとの両方に応答して、いわゆるダブルデータレートでデータ出力を実行する。

【0094】

クロック発生回路103は、図6に示すクロック発生回路102と同様に、ロック状態に至るまでの可変遅延回路130a,130bの遅延調整に要する時間を短縮して位相調整を高速化できる。また、位相合せのためのDLLは、外部クロックEXT.CLKの立上りエッジに応答した内部クロックFCLK1のみに対して設けられており、外部クロックEXT.CLKの立下りエッジに応答して生成される内部クロックBCLK1に対応して設けられる可変遅延回路130bの遅延量を可変遅延回路130aと同一値としているので、安定的なロック状態を得ることができるとともに、内部動作クロックFCLK2とBCLK2との活性化タイミングを等間隔化することができる。

【0095】

[実施の形態5]

図8は、本発明の実施の形態5に従うクロック発生回路104の構成を示すブロック図である。

【0096】

図8を参照して、クロック発生回路104は、図3に示されるクロック発生回路101の構成に加えて、外部クロックEXT.CLKの立下りエッジに応答して内部クロックBCLK1を生成するクロック入力回路125bと、内部クロックBCLK1を遅延して内部動作クロックBCLK2を生成する可変遅延回路1130bと、内部動作クロックFCLK2およびBCLK2のいずれか一方を選択してフィードバッククロックFBCLKとして出力するクロックセレクタ170と、位相比較器210の位相比較結果に基づいて可変遅延回路130bの遅延量を調整する遅延制御回路150bとをさらに備える。レプリカ回路140は、クロックセレクタ170からのフィードバッククロックFBCLKを遅延してリターンクロックRCLK1を位相比較器210に送出する。

【0097】

クロック入力回路125a、可変遅延回路130a、および遅延制御回路150aは、クロック発生回路101中のクロック入力回路125、可変遅延回路130、および遅延制御回路150に相当するので、構成および動作についての説明は繰り返さない。

【0098】

クロックセレクタ170は、内部動作クロックFCLK2およびBCLK2を受けて、いずれか一方をフィードバッククロックFBCLKとしてレプリカ回路140に送出する。クロックセレクタ170による内部動作クロックの選択周期は、内部動作クロックFCLK2およびBCLKを1:1に交互に選択しても、内部動作クロックFCLK2とBCLK2との選択比率を、n:1もしくは1:n(nは2以上の自然数)としてもよい。ここでは、リターンクロックRCLK1に対して、内部動作クロックFCLK2およびBCLK2のそれぞれの立上りエッジが混在して反映されることが必要である。

【0099】

レプリカ回路140は、このようにして選択されたフィードバックトリガ信号FBCLKを遅延して、リターンクロックRCLK1を生成する。したがって、リターンクロックRCLK1には、内部動作クロックFCLK1の位相を基準とするものと、内部動作クロックBCLK1の位相を基準とするものとが混在している。

【0100】

位相比較器210は、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが交差する位相と、リターンクロックRCLK1の位相を直接比較し、位相比較結果に基づいて、クロック発生回路101の場合と同様に、制御信号UPおよびDOWNを生成する。したがって、制御信号UPおよびDOWNにも、内部動作クロックFCLK1に基づく位相比較結果と、内部動作クロックBCLK1に基づく位相比較結果とが混在して出力される。

【0101】

遅延制御回路150aおよび150bは、制御信号UPおよびDOWNに基づいて、可変遅延回路150aおよび150bの遅延量をそれぞれ制御するための遅延制御信号CTRL1およびCTRL2をそれぞれ生成する。可変遅延回路130aおよび130bにそれぞれ対応する遅延制御信号CTRL1およびCTRL2は独立に設定されるので、可変遅延回路130aおよび130bの遅延量を異なるものとすることも可能である。

【0102】

したがって、外部クロックEXT.CLKの立上りエッジおよび立下りエッジにそえぞれ応答して生成される2個の内部動作トリガ信号の位相を独立に調整することが可能であるため、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの間のスキューを独立に調整でき、より正確な位相の合わせ込みが可能となる。

【0103】

[実施の形態6]

図9は、実施の形態6に従うクロック発生回路105の構成を示すブロック図である。

【0104】

図9を参照して、クロック発生回路105は、図8に示されるクロック発生回路104と比較して、クロックセレクタ170を具備しない点および、外部クロックEXT.CLKの立上り/立下りエッジにそれぞれ応答する内部クロックFCLK1およびBCLK1の各々に対応して、DLL構成を有する点が異なる。

【0105】

クロック発生回路105は、外部クロックEXT.CLKの立上りエッジに応答して内部クロックFCLK1を生成するクロック入力回路125aと、内部クロックFCLK1についてのDLLを構成する、可変遅延回路130a、レプリカ回路140a、位相比較器210a、および遅延制御回路150aとを備える。

【0106】

クロック発生回路105は、さらに、外部クロックEXT.CLKの立下りエッジに応答して内部クロックBCLK1を生成するクロック入力回路125bと、内部クロックBCLK1についてのDLLを構成する、可変遅延回路130b、レプリカ回路140b、位相比較器210b、および遅延制御回路150bとを備える。

【0107】

各DLLの構成および動作は、図3に示されるクロック発生回路101中の可変遅延回路130、レプリカ回路140、位相比較器210、および遅延制御回路150で構成されるDLLと同様であるので、詳細な説明は繰り返さない。すなわち、位相比較器210aおよび210bは、対応する内部クロックのそれぞれの位相を、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが交差する位相と直接比較する。

【0108】

それぞれのDLLにおける遅延量調整は独立に実行され、遅延制御回路150aは、位相比較器210aの位相比較結果に基づく制御信号UPaおよびDOWNaに応じて、可変遅延回路130aの遅延量を設定するための遅延制御信号CTRL1を生成する。同様に、遅延制御回路150bは、位相比較器210bの位相比較結果に基づく制御信号UPbおよびDOWNbに応じて、可変遅延回路130bの遅延量を設定するための遅延制御信号CTRL2を生成する。

【0109】

したがって、実施の形態5に従うクロック発生回路104と同様に、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの間のスキューを独立に調整できるため、より正確な位相の合せ込みが可能となる。さらに、クロック発生回路105は、図8に示されるようなクロックセレクタ170によって内部動作クロックの選択を実行する必要がないため、制御を簡易化することが可能である。

【0110】

[実施の形態7]

図10は、本発明の実施の形態7に従うクロック発生回路106の構成を示すブロック図である。

【0111】

図10を参照して、クロック発生回路106は、図3に示されるクロック発生回路101と類似の構成を有し、クロック入力回路125の入力が、互いに相補の外部クロックEXT.CLKおよびEXT./CLKに代えて、単一の外部クロックEXT.CLKおよび外部クロックの受付けタイミングを規定するための基準電圧VREFである点が異なる。クロック発生回路106のその他の構成および動作は、クロック発生回路101と同様であるので詳細な説明は繰返さない。

【0112】

クロック発生回路106は、相補クロックでない単一の外部クロックに対応して、実施の形態2に従うクロック発生回路101を適用するものであり、クロック入力回路125は、外部クロックEXT.CLKと基準電圧VREFとの電位レベルの関係に応じて、外部クロックEXT.CLKを受付て、内部クロックCLK1を生成する。基準電圧VREFは、直流電位を有する信号であり、外部から供給しても、半導体記憶装置内部で生成してもよい。

【0113】

このような構成とすることにより、クロック発生回路101と同様の効果を、外部クロックが相補クロックでなく単一のクロックである場合にも、享受することができる。また、図6に示されたクロック発生回路102についても、クロック入力回路125の入力を外部クロックEXT.CLKおよび基準電圧VREFとすることによって、外部クロックが単一のクロックである場合にも、同様の効果を享受することができる。

【0114】

[実施の形態8]

図11は、本発明の実施の形態8に従うクロック発生回路107の構成を示す回路図である。

【0115】

図11を参照して、クロック発生回路107は、互いに相補の外部クロックEXT.CLKおよびEXT./CLKを受けて、データ入力ラッチ回路40の動作トリガとなる内部動作クロックCLK′2を生成する。データ入力ラッチ回路40は、内部動作クロックCLK′2に応答してデータ入力端子18に与えられる入力データDINをラッチする。

【0116】

図11を参照して、クロック発生回路107は、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベル差に応じて内部クロックCLK1を生成するクロック入力回路125と、内部クロックCLK1を遅延して内部動作クロックCLK′2を生成する可変遅延回路130と、内部動作クロックCLK′2を遅延してリターンクロックRCLK1を出力する調整遅延回路180と、互いに相補の外部クロックEXT.CLKおよびEXT./CLKと、リターンクロックRCLK1とを受けて、制御信号UPおよびDOWNを生成する位相比較器210と、位相比較器210の位相比較結果に基づいて可変遅延回路130の遅延量を設定するための遅延制御信号CTRLを生成する遅延制御回路150とを備える。

【0117】

調整遅延回路180は、入力データを取込むタイミングを調整するために必要となる遅延を考慮して設けられる。したがって、このような遅延は、半導体記憶装置の仕様等によっては特に必要でない場合も生じる。この場合には調整遅延回路180は省略される。

【0118】

位相比較器210は、リターンクロックRCLK1の位相と、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが交差する位相とを直接比較して、位相比較結果を反映した制御信号UPおよびDOWNを生成する。遅延制御回路150は、制御信号UPおよびDOWNに基づいて、遅延制御信号CTRLを発生する。可変遅延回路130は、遅延制御信号CTRLに基づいて、遅延量を調節する。

【0119】

なお、クロック発生回路107においても、位相比較器210に対する入力は、リターンクロックRCLKそのものではなく、リターンクロックの状態遷移タイミングに応答したタイミングで信号レベルが変化する制御信号RCでもよい。

【0120】

クロック発生回路107は、実施の形態2に従うクロック発生回路101と同様の構成を有しており、リターンクロックの位相を外部クロックの位相と直接比較することによって、位相誤差の小さい正確なロック状態を確保することが可能である。

【0121】

したがって、クロック発生回路107が生成する内部動作クロックに応答してデータ入力ラッチ回路40を動作させることにより、半導体記憶装置の入力データ取込みタイミングは、外部クロック波形、電源電圧、電源ノイズ、温度条件、およびプロセス等の変動によって生じるクロック入力回路および、クロック入力回路で生じる遅延を補償するためのレプリカ回路における遅延量の変動の影響を受けることがなく、安定したデータ入力を実行することができる。

【0122】

[実施の形態9]

実施の形態1〜8においては、DLL構成を用いてクロック発生回路を構成したが、実施の形態9においては、PLLを用いる本願発明のクロック発生回路の構成について説明する。

【0123】

図12は、本発明の実施の形態9に従うクロック発生回路108の構成を示すブロック図である。

【0124】

図12を参照して、クロック発生回路108は、互いに相補の外部クロックEXT.CLKおよびEXT./CLKに応答して、内部動作クロックCLK2を生成する。

【0125】

クロック発生回路108は、閉ループを形成して、内部クロックCLK1および内部動作クロックCLK2をそれぞれ生成する、制御回路190および可変遅延回路130と、内部動作クロックCLK2を遅延してリターンクロックRCLK1を生成する調整遅延回路180と、互いに相補の外部クロックEXT.CLKおよびEXT./CLKとリターンクロックRCLK1とを受けて位相比較を行なう位相比較器210と、位相比較器210の位相比較結果に応じて、可変遅延回路130の遅延量を設定するための遅延制御信号CTRLを生成する遅延制御回路150とを備える。

【0126】

可変遅延回路130は、内部クロックCLK1を遅延して内部動作クロックCLK2を生成する。内部動作クロックCLK2は、たとえば半導体記憶装置内部の制御クロックもしくは入出力インタフェースのトリガ信号として使用することができる。

【0127】

調整遅延回路180は、内部動作クロックCLK2を遅延してリターンクロックRCLK1を出力する。調整遅延回路180で設定される遅延量は、内部動作クロックCLK2が供給される内部回路の動作に対応して定められ、特に遅延が必要でない場合には調整遅延回路180は省略される構成としてもよい。

【0128】

位相比較器210は、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが交差する位相と、リターンクロックRCLK1の位相とを直接比較して、位相比較結果を反映した制御信号UPおよびDOWNを生成する。遅延制御回路150は、制御信号UPおよびDOWNに応答して共通制御信号CTRLを変化させ、可変遅延回路130の遅延量を調整する。

【0129】

このように、内部のリターンクロックと外部クロックとの位相を直接比較するように位相比較器を設けることによって、PLLを用いて内部動作クロックを発生する場合においても、外部クロック波形、電源電圧、電源ノイズ、温度条件、およびプロセス等の変動によって生じるクロック入力回路および、クロック入力回路で生じる遅延を補償するためのレプリカ回路における遅延量の変動の影響をを排除して、位相誤差の小さい正確なロック状態を確保することが可能である。

【0130】

なお、クロック発生回路108においても、位相比較器210への入力は、リターンクロックRCLK1そのものに限られるわけではなく、リターンクロックの状態遷移タイミングに応答したタイミングで信号レベルが変化する制御信号RCであってもよい。

【0131】

[実施の形態10]

実施の形態10においては、内部のリターンクロックと外部クロックとの位相を直接比較するための位相比較器の具体的な構成のバリエーションについて説明する。

【0132】

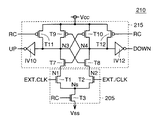

図13は、位相比較器210の第1の構成例を示す回路図である。

図13に示される第1の構成例に従う位相比較器210の回路図は、図4に示したブロック図の回路構成例を詳細に示したものである。

【0133】

図13を参照して、位相比較器210は、ノードN1およびN2の電位差を増幅してラッチする差動増幅ラッチ回路215と、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベル差をノードN1およびN2の電位レベル差に変換する電位レベル差変換回路205とを含む。電位レベル差変換回路205の構成は、図4および図5で示したのと同様であるので、説明は繰り返さない。

【0134】

差動増幅ラッチ回路215は、フリップフロップ222を形成する論理ゲートLG10およびLG12と、電源電位VccとノードN1およびN2との間にそれぞれ電気的に結合されるP型MOSトランジスタT5およびT6とを含む。トランジスタT5およびT6のゲートは、ノードN1と結合され、トランジスタT1,T2,T5,T6は、相補クロックEXT.CLKおよびEXT./CLKの電位レベル差を増幅してノードN1およびN2に出力するカレントミラー回路を構成する。

【0135】

トランジスタT1,T2,T5,T6で構成されるカレントミラー回路の差動増幅動作は、リターンクロックの状態遷移タイミングに応答したタイミングで信号レベルが変化する制御信号RCをトリガとして実行される。すなわち、制御信号RCの活性化に応じて、トランジスタT3が導通して、カレントミラー回路204に電流が供給され、相補クロックEXT.CLKおよびEXT./CLKの間の電位レベル差の増幅動作が開始される。ノードN1およびN2の電位レベルは、セット入力およびリセット入力としてフリップフロップ222に入力される。

【0136】

このような構成とすることにより、増幅動作が開始される制御信号RCの活性化時点において、外部クロックEXT.CLKの電位レベルがすでに反転クロックEXT./CLKよりも大きい場合、すなわちリターンクロックの位相が外部クロックよりも遅れている場合には、ノードN1およびN2の電位レベルは、それぞれLレベル(接地電位Vss)およびHレベル(電源電位Vcc)となるので、これに応じて、可変遅延回路の遅延量を減少させるための制御信号DOWNが活性化(Hレベル)される。

【0137】

反対に、制御信号RCの活性化時点において、反転クロックEXT./CLKの電位レベルが未だ外部クロックEXT.CLKよりも大きい場合、すなわちリターンクロックの位相が外部クロックよりも進んでいる場合には、ノードN1およびN2の電位レベルは、それぞれHレベル(電源電位Vcc)およびLレベル(接地電位Vss)となるので、これに応じて、可変遅延回路の遅延量を増加させるための制御信号UPが活性化(Hレベル)される。

【0138】

制御信号UPおよびDOWNは、フリップフロップの出力とされるので、制御信号RCの活性化タイミングにおける、外部クロックEXT.CLKと制御信号RC(すなわちリターンクロック)との位相の関係が逆転するまでは、制御信号UPおよびDOWNの信号レベルは維持される。

【0139】

したがって、このように構成された位相比較器210を用いて、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが等しくなるタイミングで規定される外部クロックの位相と、制御信号RCすなわちリターンクロックの位相とを比較して、位相比較結果を制御信号UPおよびDOWNに反映して出力することが可能である。

【0140】

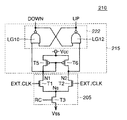

図14は、位相比較器210の第2の構成例を示す回路図である。

図14を参照して、第2の構成例に従う位相比較器210は、図4に示したブロック図の他の回路構成例を詳細に示したものである。

【0141】

第2の構成例に従う位相比較器210は、ノードN1およびN2の電位差を増幅してラッチする差動増幅ラッチ回路215と、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベル差をノードN1およびN2の電位レベル差に変換する電位レベル差変換回路205とを含む。電位レベル差変換回路205の構成は、図4および図5で示したのと同様であるので、説明は繰り返さない。

【0142】

差動増幅ラッチ回路215は、ノードN3およびN1の間に電気的に結合されるN型MOSトランジスタT7と、ノードN4およびN2の間に電気的に結合されるN型MOSトランジスタT8と、電源電位VccとノードN3およびN4との間にそれぞれ結合されるP型MOSトランジスタT9およびT10と、ノードN3およびN4の電位レベルに応じて制御信号UPおよびDOWNをそれぞれ生成するインバータIV10およびIV12とを含む。トランジスタT7〜T10は、交差結合型アンプを構成する。

【0143】

差動増幅ラッチ回路215は、さらに、制御信号RCの非活性化時、すなわち差動増幅ラッチ回路215に動作電流が供給されない期間において、ノードN3およびN4を電源電位VccにそれぞれプリチャージするためのP型MOSトランジスタT11およびT12を含む。トランジスタT11およびT12は、電源電位VccとノードN3およびN4との間にそれぞれ電気的に結合され、ゲートに制御信号RCを受ける。したがって、トランジスタT11およびT12は、トランジスタT3と相補的にオン/オフする。

【0144】

このような構成とすることにより、差動増幅ラッチ回路215の動作前においては、ノードN3およびN4の電位レベルはHレベル(電源電位Vcc)に固定され、制御信号UPおよびDOWNは、いずれも非活性化(Lレベル)される。一方、制御信号RCが活性化(Hレベル)されるタイミングにおいて、ノードN3およびN4は電源電位Vccと切り離され、さらにトランジスタT3がオンすることによって、差動増幅ラッチ回路215に動作電流が供給される。

【0145】

これに応じて、互いに相補の外部クロックEXT.CLKとEXT./CLKとの電位差は、ノードN1およびN2の電位差に変換され、さらに増幅されてノードN3およびN4にラッチされる。制御信号RCの活性化タイミングにおける互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルの関係と、位相比較結果を示す制御信号UPおよびDOWNの信号レベルとの関係は、図13で説明した内容と同一であるので、説明は繰り返さない。

【0146】

図15は、位相比較器210の第3の構成例を示す回路図である。

図15を参照して、第3の構成例に従う位相比較器210は、図14に示される位相比較器と類似の構成を有し、トランジスタT1およびT2に接地電位Vssを供給するために、N型MOSトランジスタT3に代えてN型MOSトランジスタT3aおよびT3bを含む点で異なる。トランジスタT3aおよびT3bのゲートには、共通の制御信号RCが与えられる。

【0147】

このような構成とすることによって、N型MOSトランジスタT1およびT2のソースへの接地電位Vssの供給を、独立のトランジスタによって実行することが可能となる。その他の部分の構成および動作については、図13の場合と同様であるので説明は繰返さない。

【0148】

図16は、位相比較器210の第4の構成例を示す回路図である。

図16を参照して、第4の構成例に従う位相比較器210は、制御信号RCの活性化に応答して動作し、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベル差をノードN1およびN2の電位レベル差に変換する電位レベル差変換回路206と、ノードN1およびN2の電位差を増幅してラッチする差動増幅ラッチ回路216と、ノードN1の電位レベルに応じて制御信号UPを生成するインバータIV10と、ノードN2の電位レベルに応じて制御信号DOWNを生成するインバータIV12とを含む。

【0149】

電位レベル差変換回路206は、ノードN1および電源電位Vccの間に電気的に結合されるP型MOSトランジスタT11と、ノードN5およびN1の間に電気的に結合されるN型MOSトランジスタT1と、ノードN2および電源電位Vccの間に電気的に結合されるP型MOSトランジスタT12と、ノードN5およびN2の間に電気的に結合されるN型MOSトランジスタT2とを有する。トランジスタT1およびT2のゲートには、互いに相補の外部クロックEXT.CLKおよびEXT./CLKがそれぞれ入力される。トランジスタT11およびT12のゲートには、リターンクロックに応答する制御信号RC0が共通に与えられる。

【0150】

差動増幅ラッチ回路216は、ノードN1およびN2の信号レベルを増幅してラッチするための交差結合型アンプを構成するN型MOSトランジスタT7,T8およびP型MOSトランジスタT9,T10を有する。トランジスタT9およびT10は、電源電位VccとノードN1およびN2の間にそれぞれ電気的に結合される。トランジスタT7およびT8は、ノードN6とノードN1およびN2との間にそれぞれ電気的に結合される。トランジスタT7およびT9のゲートはノードN2と電気的に結合され、トランジスタT8およびT10のゲートはノードN1と電気的に結合される。

【0151】

第4の構成例に従う位相比較器210は、さらに、ノードN5と接地電位Vssとの間に電気的に結合され、電位レベル差変換回路206の動作電流を供給するためのN型MOSトランジスタT3と、ノードN6と接地電位Vssとの間に電気的に結合され、差動増幅ラッチ回路216の動作電流を供給するためのN型MOSトランジスタT13とを含む。トランジスタT3およびT13のゲートには、制御信号RC1およびRC2がそれぞれ入力される。

【0152】

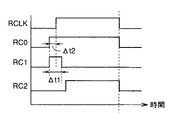

図17は、制御信号RC0、RC1およびRC2の活性化タイミングを説明するタイミングチャートである。

【0153】

図17を参照して、制御信号RC0〜RC2の活性化タイミングは、リターンクロックRCLKの活性化タイミングに対応して定められる。

【0154】

制御信号RC0は、リターンクロックRCLKの活性化(Hレベルへ)タイミングよりΔt2早く活性化され、リターンクロックRCLKが活性化される間、活性状態(Hレベル)を維持する。制御信号RC1は、制御信号RC0と同時に活性化(Hレベルへ)され、期間Δt1の間活性状態(Hレベル)を維持した後に、リターンクロックRCLKが活性化(Hレベルへ)された後に非活性化(Lレベルへ)される。制御信号RC2は、制御信号RC1が非活性化(Lレベルへ)されるタイミングより後に活性化(Hレベルへ)され、リターンクロック信号RCLKと同時に非活性化(Lレベルへ)される。

【0155】

再び図16を参照して、制御信号RC0が非活性状態(Lレベル)である間は、ノードN1およびN2の電位レベルはHレベル(電源電位Vcc)にプリチャージされる。これに応じて、制御信号UPおよびDOWNはいずれも非活性化(Lレベル)される。

【0156】

制御信号RC0が活性化されると、ノードN1およびN2は、電源電位Vccと切り離される。また、同時に制御信号RC1が活性化(Hレベル)されるので、ノードN1(Vccプリチャージ)〜トランジスタT1〜トランジスタT3〜接地電位Vssおよび、ノードN2(Vccプリチャージ)〜トランジスタT2〜トランジスタT13〜接地電位Vssに電流経路が形成される。したがって、トランジスタT1およびT2のゲートにそれぞれ入力される相補クロックEXT.CLKおよびEXT./CLKの電位レベルが、ノードN1およびN2の電位レベル差に反映されて現れる。ノードN1およびN2の間の電位レベル差は、トランジスタT7〜T10で増幅される。

【0157】

さらに、制御信号RC1が非活性化(Lレベルへ)されて、信号RC2が活性化(Hレベルへ)されると、増幅されたノードN1およびN2の電位レベルは、トランジスタT7〜T10で構成される交差結合型アンプによってラッチされる。ノードN1およびN2の電位レベルと、位相比較結果を示す制御信号UPおよびDOWNの信号レベルとの関係は、図13で説明した内容と同一であるので、説明は繰り返さない。

【0158】

このような構成とすることによって、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの間の電位レベル差の増幅動作を、制御信号RC1が活性化されるΔt1の期間のみで実行することができる。制御信号RC1の活性化期間(Hレベル)の中央を、リターンクロックRCLKの活性化エッジと合せることによって、特定のウインドウ期間においてのみ相補の外部クロックの電位レベル差の増幅動作を実行することになるので、リターンクロックRCLKを外部クロックとの位相とさらに正確に比較することができる。

【0159】

図18は、位相比較器210の第5の構成例を示す回路図である。

図18を参照して、第5の構成例に従う位相比較器210は、図16に示される位相比較器と類似の構成を有し、トランジスタT2のゲートに入力される信号が、反転クロックEXT./CLKではなく単一の外部クロックEXT.CLKを受付るための基準電圧VREFである点が異なる。

【0160】

このような構成とすることによって、位相比較器210は、リターンクロックRCLKの活性化エッジを中心として設けられる特定の期間において、外部クロックEXT.CLKと基準電圧VREFとの電位レベル差を増幅して、その増幅結果を増幅しかつラッチすることができる。したがって、外部クロックが相補クロックでなく単一のクロックである場合にも、リターンクロックRCLKの位相と外部クロックEXT.CLKとの位相比較を正確に実行することができる。

【0161】

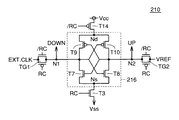

図19は、位相比較器の第6の構成例を示す回路図である。

図19を参照して、第6の構成例に従う位相比較器210は、相補クロックEXT.CLKおよびEXT./CLKをノードN1およびN2に伝達するためのトランスファゲートTG1およびTG2と、ノードN1およびN2の電位差を増幅してラッチする差動増幅ラッチ回路216と、差動増幅ラッチ回路216と電源電位Vccおよび接地電位Vssとの間にそれぞれ電気的に結合されるP型MOSトランジスタT14およびN型MOSトランジスタT3とを含む。差動増幅ラッチ回路216は、制御信号RCをトリガとして、トランジスタT3およびT14を介して動作電流を供給されて、差動増幅動作を開始する。

【0162】

同様に、制御信号RCをトリガとして、トランスファゲートTG1およびTG2はクロックEXT.CLKおよびEXT./CLKのノードN1およびN2への伝達を中止する。したがって、差動増幅ラッチ回路216は、制御信号RCが活性化されたタイミングにおけるクロックEXT.CLKとEXT./CLKとの間の電位レベル差を閉じ込めて増幅かつラッチし、ラッチ情報に基づいて制御信号UPおよびDOWNを生成する。

【0163】

図20は、図19に示される第6の構成例に従う位相比較器の構成を詳細に説明する回路図である。

【0164】

図20を参照して、トランスファゲートTG1およびTG2は、制御信号RCに応答して動作するCMOSゲートで構成される。トランジスタT3は、ノードNsと接地電位Vssとの間に結合され、ゲートに制御信号RCの反転信号/RCを受ける。トランジスタT14は、ゲートに制御信号RCの反転信号/RCを受ける。

【0165】

差動増幅ラッチ回路216は、ノードNdとノードN1およびN2との間にそれぞれ電気的に結合されるP型MOSトランジスタT9およびT10と、ノードNsとN1およびN2との間にそれぞれ電気的に結合されるN型MOSトランジスタT7およびT8とを含む。トランジスタT7およびT9のゲートはノードN2と結合され、トランジスタT8およびT10のゲートはノードN1と結合される。

【0166】

制御信号RCの活性化(Hレベル)をトリガとして、トランジスタT7〜T10で構成される交差結合型アンプが動作して、ノードN1およびN2の間の電位レベル差の増幅が開始される。また、このタイミングにおいて、トランスファゲートTG1およびTG2はオフされて、ノードN1およびN2は、外部クロックEXT.CLKとEXT./CLKとそれぞれ切り離される。

【0167】

したがって、差動増幅ラッチ回路216は、制御信号RCの活性化(Hレベル)タイミングにおける外部クロックEXT.CLKとEXT./CLKの電位レベルを閉じ込めて、閉じ込めた電位レベル差を増幅してノードN1およびN2に出力する。制御信号RCの活性化タイミングにおける互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルの関係と、位相比較結果を示す制御信号UPおよびDOWNの信号レベルとの関係は、図13で説明した内容と同一であるので、説明は繰り返さない。

【0168】

このような構成によっても、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの電位レベルが等しくなるタイミングで規定される外部クロックの位相と、制御信号RCすなわちリターンクロックの位相とを比較して、位相比較結果を制御信号UPおよびDOWNに反映して出力することが可能である。

【0169】

図21は、位相比較器210の第7の構成例を示す回路図である。

図21を参照して、第7の構成例に従う位相比較器210は、図20に示される位相比較器と同様の構成を有するが、トランスファゲートTG2を介してノードN2に伝達される信号が、反転クロックEXT./CLKではなく単一の外部クロックEXT.CLKを受付るための基準電圧VREFである点が異なる。その他の構成および動作については、図20に示される位相比較器210と同様であるので説明は繰返さない。

【0170】

このような構成とすることによって、外部クロックが相補クロックでなく単一のクロックである場合にも、リターンクロックRCLKの位相と外部クロックEXT.CLKとの位相比較を正確に行なうことができる。

【0171】

実施の形態10において説明した種々の構成例に従う位相比較器は、実施の形態1〜9に従うクロック発生回路中に具備される位相比較器210,210a,210bに適宜使用することができる。

【0172】

また、本実施の形態においては、半導体記憶装置におけるデータ入力/出力タイミングを実行するためのトリガ信号となる内部動作クロックの生成について代表的に説明したが、本願発明は、外部クロックに同期して動作する内部回路に対する動作クロックの供給について、一般的に適用することが可能である。この場合には、実施の形態1〜9の構成におけるデータ出力制御回路50もしくはデータ入力ラッチ回路40を、内部回路に置換えて本願発明の構成を適用すればよい。

【0173】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0174】

【発明の効果】

請求項1記載のクロック発生回路は、位相比較器に入力される内部クロックの位相を、互いに相補の外部クロックの電位レベルが交差する位相と直接比較するので、外部クロック波形、電源電圧、電源ノイズ、温度条件、およびプロセス等の変動によって生じる外部クロックを内部クロックに変換する際に生じる遅延時間の変動が、内部クロックの位相精度に悪影響を与えることを防止でき、内部クロックの位相精度を良好に維持できる。さらに、外部クロックの1周期に対応して第1および第2の位相比較器による遅延調整を実行できるので、ロック状態に至るまでの所要時間を短縮して位相調整を高速化できる。さらに、位相を合せ込むべきクロックエッジ(立上りエッジ/立下りエッジ)を取り違えることがなくなるので、ロック可能な周波数範囲を広く取ることができる。

【0176】

請求項2記載のクロック発生回路は、内部クロックの位相精度を良好に維持できる効果に加えて、外部クロックの立上りおよび立下りエッジの両方に応答して内部クロックを生成できる。また、第1および第2の可変遅延回路の遅延量を共通に制御するので、外部クロックの両エッジにそれぞれ対応する内部クロックの活性化を等間隔化することができる。

【0177】

請求項3記載のクロック発生回路は、内部クロックの位相精度を良好に維持できる効果に加えて、外部クロックの立上りおよび立下りエッジの両方に応答して内部クロックを生成できる。さらに、外部クロックの両エッジにそれぞれ応答して生成される内部動作トリガ信号の位相を独立に調整するので、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの間のスキューを独立に調整できる。

【0178】

請求項4記載のクロック発生回路は、内部クロックの位相精度を良好に維持できる効果に加えて、外部クロックの立上りおよび立下りエッジの両方に応答して内部クロックを生成できる。さらに、クロックセレクタを用いない簡易な制御に基づいて、外部クロックの両エッジにそれぞれ応答して生成される内部動作トリガ信号の位相を独立に調整して、互いに相補の外部クロックEXT.CLKおよびEXT./CLKの間のスキューを独立に調整できる。

【0179】

請求項5から10記載のクロック発生回路は、DLLによってフィードバックされる内部クロックの位相と相補の外部クロックの電位が交差する位相とを、位相比較器によって正確に比較することができる。

【図面の簡単な説明】

【図1】 本発明の実施の形態1に従うクロック発生回路を具備する半導体記憶装置10の構成を示す概略ブロック図である。

【図2】 実施の形態1に従うクロック発生回路100の構成を示すブロック図である。

【図3】 実施の形態2に従うクロック発生回路101の構成を示すブロック図である。

【図4】 位相比較器210の構成例を示すブロック図である。

【図5】 位相比較器210の他の構成例を示すブロック図である。

【図6】 本発明の実施の形態3に従うクロック発生回路102の構成を示すブロック図である。

【図7】 本発明の実施の形態4に従うクロック発生回路103の構成を示すブロック図である。

【図8】 本発明の実施の形態5に従うクロック発生回路104の構成を示すブロック図である。

【図9】 本発明の実施の形態6に従うクロック発生回路105の構成を示すブロック図である。

【図10】 本発明の実施の形態7に従うクロック発生回路106の構成を示すブロック図である。

【図11】 本発明の実施の形態8に従うクロック発生回路107の構成を示す回路図である。

【図12】 本発明の実施の形態9に従うクロック発生回路108の構成を示すブロック図である。

【図13】 位相比較器210の第1の構成例を示す回路図である。

【図14】 位相比較器210の第2の構成例を示す回路図である。

【図15】 位相比較器210の第3の構成例を示す回路図である。

【図16】 位相比較器210の第4の構成例を示す回路図である。

【図17】 制御信号RC0、RC1およびRC2の活性化タイミングを説明するタイミングチャートである。

【図18】 位相比較器210の第5の構成例を示す回路図である。

【図19】 位相比較器210の第6の構成例を示す回路図である。

【図20】 第6の構成例に従う位相比較器の構成を詳細に説明する回路図である。

【図21】 位相比較器210の第7の構成例を示す回路図である。

【図22】 SDRAMにおけるデータ出力タイミングを説明するタイミングチャートである。

【図23】 DDR−SDRAMのデータ出力タイミングを示すタイミングチャートである。

【図24】 DLLを用いた従来の技術のクロック発生回路500の構成を示すブロック図である。

【図25】 DDR−SDRAMに用いられる従来の技術のクロック発生回路510の構成を示すブロック図である。

【図26】 従来のクロック発生回路500の動作を示すタイミングチャートである。

【符号の説明】

30 メモリコア、40 データ入力ラッチ回路、50 データ出力制御回路、100,101,102,103,104,105,106,107,108クロック発生回路、120,125,125a,125b クロック入力回路、130,130a,130b 可変遅延回路、140,140a,140b,160 レプリカ回路、150,150a,150b 遅延制御回路、170 クロックセレクタ、180 遅延調整回路、200,210,210a,210b 位相比較器。

Claims (10)

- 所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、

前記外部クロックおよび前記外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、

前記第1の内部クロックは、前記外部クロックおよび前記外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、

前記第1の内部クロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、

前記第2の内部クロックを前記内部回路における前記所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、

前記外部クロックおよび前記外部基準クロックの電位レベルが交差する位相と、前記第3の内部クロックの位相とを比較する第1の位相比較器と、

前記第1の位相比較器の位相比較結果に基づいて、前記第1の可変遅延回路の遅延量を制御する第1の遅延制御回路と、

前記第3の内部クロックを前記第1のクロック入力回路で生じる遅延に相当する第2の所定時間さらに遅延して、第4の内部クロックを生成する第2の模擬遅延回路と、

前記第1の内部クロックと前記第4の内部クロックとの位相を比較する第2の位相比較器とを備え、

前記第1の遅延制御回路は、前記第1および第2の位相比較器の位相比較結果に基づいて、前記第1の可変遅延回路の遅延量を制御する、クロック発生回路。 - 所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、

前記外部クロックおよび前記外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、

前記第1の内部クロックは、前記外部クロックおよび前記外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、

前記第1の内部クロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、

前記第2の内部クロックを前記内部回路における前記所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、

前記外部クロックおよび前記外部基準クロックの電位レベルが交差する位相と、前記第3の内部クロックの位相とを比較する第1の位相比較器と、

前記第1の位相比較器の位相比較結果に基づいて、前記第1の可変遅延回路の遅延量を制御する第1の遅延制御回路と、

前記外部クロックおよび前記外部基準クロックを受けて、前記第1の内部クロックと相補の第1の内部サブクロックを生成する第2のクロック入力回路と、

前記第1の内部サブクロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部サブクロックを生成する第2の可変遅延回路と、

前記第3の内部クロックを前記第1のクロック入力回路で生じる遅延に相当する第2の所定時間さらに遅延して、第4の内部クロックを生成する第2の模擬遅延回路と、

前記第1の内部クロックと前記第4の内部クロックとの位相を比較する第2の位相比較器とを備え、

前記第1の遅延制御回路は、前記第1および第2の位相比較器の位相比較結果に基づいて、前記第1および第2の可変遅延回路の遅延量を共通に制御する、クロック発生回路。 - 所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、

前記外部クロックおよび前記外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、

前記第1の内部クロックは、前記外部クロックおよび前記外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、

前記第1の内部クロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、

前記第2の内部クロックを前記内部回路における前記所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、

前記外部クロックおよび前記外部基準クロックの電位レベルが交差する位相と、前記第3の内部クロックの位相とを比較する第1の位相比較器と、

前記第1の位相比較器の位相比較結果に基づいて、前記第1の可変遅延回路の遅延量を制御する第1の遅延制御回路と、

前記外部クロックおよび前記外部基準クロックを受けて、前記第1の内部クロックと相補の第1の内部サブクロックを生成する第2のクロック入力回路と、

前記第1の内部サブクロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部サブクロックを生成する第2の可変遅延回路と、

前記第2の内部クロックおよび前記第2の内部サブクロックを受けて、一定の選択周期に基づいていずれか一方を前記第1の模擬遅延回路に送出するクロック選択回路とを備え、

前記第1の模擬遅延回路は、前記クロック選択回路が送出するクロックを前記第1の所定時間さらに遅延して、前記第3の内部クロックを生成し、

前記クロック発生回路は、

前記第1の位相比較器の位相比較結果に基づいて、前記第1の遅延制御回路とは独立に前記第2の可変遅延回路の遅延量を制御する第2の遅延制御回路をさらに備える、クロック発生回路。 - 所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、

前記外部クロックおよび前記外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、

前記第1の内部クロックは、前記外部クロックおよび前記外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、

前記第1の内部クロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、

前記第2の内部クロックを前記内部回路における前記所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、

前記外部クロックおよび前記外部基準クロックの電位レベルが交差する位相と、前記第3の内部クロックの位相とを比較する第1の位相比較器と、

前記第1の位相比較器の位相比較結果に基づいて、前記第1の可変遅延回路の遅延量を制御する第1の遅延制御回路と、

前記外部クロックおよび前記外部基準クロックを受けて、前記第1の内部クロックと相補の第1の内部サブクロックを生成する第2のクロック入力回路と、

前記第1の内部サブクロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部サブクロックを生成する第2の可変遅延回路と、

前記第2の内部サブクロックを前記第1の所定時間さらに遅延して、第3の内部サブクロックを生成する第2の模擬遅延回路と、

前記外部クロックおよび前記外部基準クロックの電位レベルが交差する位相と、前記第3の内部サブクロックの位相とを比較する第2の位相比較器と、

前記第2の位相比較器の位相比較結果に基づいて、前記第2の可変遅延回路の遅延量を制御する第2の遅延制御回路とを備える、クロック発生回路。 - 所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、

前記外部クロックおよび前記外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、

前記第1の内部クロックは、前記外部クロックおよび前記外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、

前記第1の内部クロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、

前記第2の内部クロックを前記内部回路における前記所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、

前記外部クロックおよび前記外部基準クロックの電位レベルが交差する位相と、前記第3の内部クロックの位相とを比較する第1の位相比較器と、

前記第1の位相比較器の位相比較結果に基づいて、前記第1の可変遅延回路の遅延量を制御する第1の遅延制御回路とを備え、

前記第1の位相比較器は、前記第3の内部クロックの電位レベルに応じて、前記外部クロックおよび前記外部基準クロックの電位レベル差を第1および第2の内部ノード間の電位レベル差に変換する電位差変換回路と、

前記第1および第2の内部ノードの電位レベル差を増幅して増幅結果を保持する差動増幅回路とを含み、

前記電位差変換回路は、

前記第1の内部ノードと電気的に結合され、前記外部クロックをゲートに受ける第1のトランジスタと、

前記第2の内部ノードと電気的に結合され、前記外部基準クロックをゲートに受ける第2のトランジスタと、

前記第3の内部クロックの電位レベルに応じてオンして、前記電位差変換回路および前記差動増幅回路に動作電流を供給するための電流供給トランジスタとを有し、

前記差動増幅回路は、前記増幅結果に基づいて、前記第1の可変遅延回路の遅延量を増加するための第1の制御信号および、前記第1の可変遅延回路の遅延量を減少するための第2の制御信号のいずれか一方を活性化する、クロック発生回路。 - 前記差動増幅回路は、

前記第1および第2の内部ノードのいずれか一方と電気的に結合されるゲートを有し、前記第2の電位を供給するノードと前記第1および第2の内部ノードとの間にそれぞれ設けられる第3および第4のトランジスタと、

前記第1および第2の内部ノードの電位レベルに応じて、前記第1および第2の制御信号の信号レベルを設定するフリップフロップ回路とを有する、請求項5記載のクロック発生回路。 - 前記差動増幅回路は、

第3の内部ノードと電気的に結合されるゲートを有し、前記第2のノードと第4のノードとの間に電気的に結合される第3のトランジスタと、

前記第4の内部ノードと電気的に結合されるゲートを有し、前記第1のノードと前記第3のノードとの間に電気的に結合される第4のトランジスタと、

前記第2の電位を供給する電位供給ノードと前記第3の内部ノードとの間に電気的に結合され、前記第4の内部ノードと電気的に結合されるゲートを有する第5のトランジスタと、

前記電位供給ノードと前記第4の内部ノードとの間に電気的に結合され、前記第3の内部ノードと電気的に結合されるゲートを有する第6のトランジスタと、

前記電流供給トランジスタと相補的にオンして、前記電位供給ノードと前記第3および第4の内部ノードとをそれぞれ電気的に結合する第7および第8のトランジスタと、

前記第3および第4の内部ノードの電位レベルにそれぞれ応じて、前記第1および第2の制御信号をそれぞれ生成する第1および第2の論理ゲートとを有する、請求項5記載のクロック発生回路。 - 所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、

前記外部クロックおよび前記外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、

前記第1の内部クロックは、前記外部クロックおよび前記外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、

前記第1の内部クロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、

前記第2の内部クロックを前記内部回路における前記所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、

前記外部クロックおよび前記外部基準クロックの電位レベルが交差する位相と、前記第3の内部クロックの位相とを比較する第1の位相比較器と、

前記第1の位相比較器の位相比較結果に基づいて、前記第1の可変遅延回路の遅延量を制御する第1の遅延制御回路とを備え、

前記第1の位相比較器は、

第1のタイミング信号の活性化に応答して、前記外部クロックおよび前記外部基準クロックの電位レベル差を第1および第2の内部ノード間の電位レベル差に変換する電位差変換回路と、

前記第1および第2の内部ノードの電位レベル差を増幅して、前記第1および第2の内部ノードのそれぞれ電位レベルを前記第1および第2の電位のいずれか一方ずつに設定する増幅結果を保持する差動増幅回路と、

第2のタイミング信号の活性化に応答して、前記電位差変換回路に動作電流を供給する第1の電流供給回路と、

第3のタイミング信号の活性化に応答して、前記差動増幅回路に動作電流を供給する第2の電流供給回路とを含み、

前記第1および第2のタイミング信号は、前記第3の内部クロックが前記第1の電位から前記第2の電位に遷移する遷移タイミングよりも先に活性化され、

前記第2のタイミング信号は、前記第3の内部クロックの前記遷移タイミングよりも後に非活性化され、

前記第3のタイミング信号は、前記第2のタイミング信号の非活性化後に活性化され、

前記第1および第3のタイミング信号は、前記第3の内部クロックが第2の電位から第1の電位に遷移するタイミングにおいて非活性化され、

前記差動増幅回路は、前記第1および第2の内部ノードの電位レベルに応じて、前記第1の可変遅延回路の遅延量を増加するための第1の制御信号および、前記第1の可変遅延回路の遅延量を減少するための第2の制御信号のいずれか一方を活性化する、クロック発生回路。 - 所定動作を実行する内部回路に対して、外部クロックに同期した動作クロックを供給するクロック発生回路であって、

前記外部クロックおよび前記外部クロックと相補のクロック信号である外部基準クロックを受けて第1の内部クロックを生成する第1のクロック入力回路を備え、

前記第1の内部クロックは、前記外部クロックおよび前記外部基準クロックの電位レベル差に応じて、第1の電位と第2の電位との間における状態遷移を繰り返し、

前記第1の内部クロックを遅延して、前記動作クロックとして前記内部回路に供給される第2の内部クロックを生成する第1の可変遅延回路と、

前記第2の内部クロックを前記内部回路における前記所定動作の所要時間に相当する第1の所定時間さらに遅延して、第3の内部クロックを生成する第1の模擬遅延回路と、

前記外部クロックおよび前記外部基準クロックの電位レベルが交差する位相と、前記第3の内部クロックの位相とを比較する第1の位相比較器と、

前記第1の位相比較器の位相比較結果に基づいて、前記第1の可変遅延回路の遅延量を制御する第1の遅延制御回路とを備え、

前記第1の位相比較器は、

前記第3の内部クロックの電位レベルに応じて動作し、前記外部クロックを第1のノードに伝達するための第1の信号伝達ゲートと、

前記第1の信号伝達ゲートと同一のタイミングで動作し、前記外部基準クロックを第1のノードに伝達するための第2の信号伝達ゲートと、

前記第1および第2の内部ノードの電位レベル差を増幅して、増幅結果を保持する差動増幅回路と、

前記第3の内部クロックの電位レベルに応じて動作し、前記差動増幅回路に動作電流を供給する電流供給回路とを含み、

前記第1および第2の信号伝達ゲートと前記電流供給回路とは、相補的にオン/オフし、

前記差動増幅回路は、前記増幅結果に基づいて、前記第1の可変遅延回路の遅延量を所定量増加するための第1の制御信号および、前記第1の可変遅延回路の遅延量を所定量減少するための第2の制御信号のいずれか一方を活性化する、クロック発生回路。 - 前記差動増幅回路は、前記第1および第2の内部ノードの電位レベル差を増幅して、前記第1および第2の内部ノードの電位レベルを前記第1および第2の電位のいずれか一方ずつに設定する交差結合型アンプを含み、

前記電流供給回路は、

前記第1の電位を供給する第1の電位供給ノードと前記差動増幅回路との間に電気的に結合される第1のトランジスタと、

前記第2の電位を供給する第2の電位供給ノードと前記差動増幅回路との間に電気的に結合される第2のトランジスタとを有し、

前記第1および第2のトランジスタは、前記第1および第2の信号伝達ゲートと相補的にオン/オフする、請求項9記載のクロック発生回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000173475A JP4443728B2 (ja) | 2000-06-09 | 2000-06-09 | クロック発生回路 |

| US09/793,999 US6417715B2 (en) | 2000-06-09 | 2001-02-28 | Clock generation circuit generating internal clock of small variation in phase difference from external clock, and semiconductor memory device including such clock generation circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000173475A JP4443728B2 (ja) | 2000-06-09 | 2000-06-09 | クロック発生回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001351381A JP2001351381A (ja) | 2001-12-21 |

| JP2001351381A5 JP2001351381A5 (ja) | 2007-07-12 |

| JP4443728B2 true JP4443728B2 (ja) | 2010-03-31 |

Family

ID=18675700

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000173475A Expired - Fee Related JP4443728B2 (ja) | 2000-06-09 | 2000-06-09 | クロック発生回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6417715B2 (ja) |

| JP (1) | JP4443728B2 (ja) |

Families Citing this family (55)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3362705B2 (ja) * | 1999-07-16 | 2003-01-07 | 日本電気株式会社 | 位相調整回路及びこれを内蔵した半導体記憶装置 |

| JP2001068650A (ja) * | 1999-08-30 | 2001-03-16 | Hitachi Ltd | 半導体集積回路装置 |

| US6621882B2 (en) * | 2001-03-02 | 2003-09-16 | General Dynamics Information Systems, Inc. | Method and apparatus for adjusting the clock delay in systems with multiple integrated circuits |

| US7116728B2 (en) * | 2001-05-25 | 2006-10-03 | Matsushita Electric Industrial Co., Ltd. | Quadrature alignment in communications receivers using dual delay lines |

| JP2002352582A (ja) * | 2001-05-28 | 2002-12-06 | Hitachi Ltd | 半導体集積回路装置 |

| US6930524B2 (en) | 2001-10-09 | 2005-08-16 | Micron Technology, Inc. | Dual-phase delay-locked loop circuit and method |

| JP2003163592A (ja) * | 2001-11-26 | 2003-06-06 | Mitsubishi Electric Corp | 位相比較器およびそれを用いたクロック発生回路 |

| US6977529B2 (en) * | 2002-03-01 | 2005-12-20 | Ics Technologies, Inc. | Differential clock signal detection circuit |

| JP4628096B2 (ja) | 2002-06-10 | 2011-02-09 | 株式会社アドバンテスト | 半導体試験装置 |

| US6621316B1 (en) | 2002-06-20 | 2003-09-16 | Micron Technology, Inc. | Synchronous mirror delay (SMD) circuit and method including a counter and reduced size bi-directional delay line |

| US6727740B2 (en) | 2002-08-29 | 2004-04-27 | Micron Technology, Inc. | Synchronous mirror delay (SMD) circuit and method including a ring oscillator for timing coarse and fine delay intervals |

| JP2004145709A (ja) * | 2002-10-25 | 2004-05-20 | Renesas Technology Corp | 半導体装置 |

| DE10330796B4 (de) * | 2002-10-30 | 2023-09-14 | Hynix Semiconductor Inc. | Registergesteuerter Delay Locked Loop mit Beschleunigungsmodus |

| KR100518547B1 (ko) * | 2002-12-28 | 2005-10-04 | 삼성전자주식회사 | 출력 드라이버의 구동력 변화에 따른 내부클락신호의지연을 보상할 수 있는 반도체 메모리 장치의 지연동기루프 |

| KR100564566B1 (ko) * | 2003-04-14 | 2006-03-29 | 삼성전자주식회사 | 외부 클럭 신호가 직접 입력되는 지연 동기 루프 |

| US6839301B2 (en) * | 2003-04-28 | 2005-01-04 | Micron Technology, Inc. | Method and apparatus for improving stability and lock time for synchronous circuits |

| KR100505686B1 (ko) * | 2003-05-26 | 2005-08-03 | 삼성전자주식회사 | 다수의 피시험 소자들을 병렬로 검사하는 테스트 시스템및 테스트 방법 |

| US6937076B2 (en) * | 2003-06-11 | 2005-08-30 | Micron Technology, Inc. | Clock synchronizing apparatus and method using frequency dependent variable delay |

| US6975150B2 (en) * | 2003-06-27 | 2005-12-13 | Intel Corporation | Apparatus and methods to control laser duty cycle |

| KR100578232B1 (ko) * | 2003-10-30 | 2006-05-12 | 주식회사 하이닉스반도체 | 지연 고정 루프 |

| US20050102476A1 (en) * | 2003-11-12 | 2005-05-12 | Infineon Technologies North America Corp. | Random access memory with optional column address strobe latency of one |

| WO2005050844A1 (ja) * | 2003-11-20 | 2005-06-02 | Advantest Corporation | 可変遅延回路 |

| US7098714B2 (en) * | 2003-12-08 | 2006-08-29 | Micron Technology, Inc. | Centralizing the lock point of a synchronous circuit |

| US7177205B2 (en) * | 2004-04-27 | 2007-02-13 | Intel Corporation | Distributed loop components |

| JP4137005B2 (ja) | 2004-05-25 | 2008-08-20 | Necエレクトロニクス株式会社 | 位相同期回路 |

| KR100645461B1 (ko) * | 2004-06-30 | 2006-11-15 | 주식회사 하이닉스반도체 | 듀티 싸이클 교정이 가능한 디지털 지연 고정 루프 및그의 제어 방법 |

| US7245551B2 (en) * | 2004-08-19 | 2007-07-17 | Micron Technology, Inc. | Read command triggered synchronization circuitry |

| KR100630731B1 (ko) * | 2005-01-10 | 2006-10-02 | 삼성전자주식회사 | 클럭 트리에서 온도-전압 변화에 따른 지연시간드리프트를 보상하는 회로를 구비하는 반도체 장치 |

| KR100733471B1 (ko) * | 2005-02-28 | 2007-06-28 | 주식회사 하이닉스반도체 | 반도체 기억 소자의 지연 고정 루프 회로 및 그 제어 방법 |

| KR100672033B1 (ko) * | 2005-10-14 | 2007-01-19 | 삼성전자주식회사 | 두 개의 입력 기준 클럭을 가지는 지연동기루프회로, 이를포함하는 클럭 신호 발생 회로 및 클럭 신호 발생 방법 |

| KR100706836B1 (ko) | 2006-06-07 | 2007-04-13 | 주식회사 하이닉스반도체 | 펄스 발생 장치 및 방법 |

| US7539078B2 (en) * | 2006-08-22 | 2009-05-26 | Atmel Corporation | Circuits to delay a signal from a memory device |

| US7433262B2 (en) * | 2006-08-22 | 2008-10-07 | Atmel Corporation | Circuits to delay a signal from DDR-SDRAM memory device including an automatic phase error correction |

| US20080048731A1 (en) * | 2006-08-25 | 2008-02-28 | Faraday Technology Corp. | Comparator and method for operating thereof |

| KR100854457B1 (ko) | 2006-12-29 | 2008-08-27 | 주식회사 하이닉스반도체 | 지연고정루프 |

| US7548471B2 (en) * | 2007-09-21 | 2009-06-16 | Qimonda North America Corp. | Method and apparatus for adjusting the timing of an electronic circuit |

| JP5574570B2 (ja) * | 2008-02-12 | 2014-08-20 | ピーエスフォー ルクスコ エスエイアールエル | 伝送制御回路及びそれを備えた半導体記憶装置 |

| JP2008211809A (ja) * | 2008-03-10 | 2008-09-11 | Elpida Memory Inc | タイミング調整回路及びそれを備えた半導体装置 |

| KR100985879B1 (ko) | 2008-03-21 | 2010-10-08 | 주식회사 하이닉스반도체 | 지연고정루프회로 |

| KR100937949B1 (ko) * | 2008-04-30 | 2010-01-21 | 주식회사 하이닉스반도체 | 지연 고정 루프 회로 |

| KR100917630B1 (ko) * | 2008-04-30 | 2009-09-17 | 주식회사 하이닉스반도체 | 지연 고정 루프 회로 |

| WO2010013340A1 (ja) | 2008-07-31 | 2010-02-04 | 富士通株式会社 | データ転送装置、データ送信装置、データ受信装置およびデータ転送方法 |

| US7864625B2 (en) * | 2008-10-02 | 2011-01-04 | International Business Machines Corporation | Optimizing SRAM performance over extended voltage or process range using self-timed calibration of local clock generator |

| KR101605463B1 (ko) * | 2009-03-04 | 2016-03-22 | 삼성전자 주식회사 | 피브이티 변동에 둔감한 딜레이 라인을 갖는 지연 고정 루프회로 |

| JP2011044795A (ja) * | 2009-08-19 | 2011-03-03 | Renesas Electronics Corp | 入力インターフェース回路 |

| US8363485B2 (en) * | 2009-09-15 | 2013-01-29 | Qualcomm Incorporated | Delay line that tracks setup time of a latching element over PVT |

| KR101138833B1 (ko) * | 2010-05-27 | 2012-05-11 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그의 구동 방법 |

| JP6051500B2 (ja) * | 2011-03-15 | 2016-12-27 | 株式会社リコー | 画像読取装置及び電子機器 |

| US8823388B2 (en) * | 2011-06-03 | 2014-09-02 | Solid State System Co., Ltd. | Calibration circuit and calibration method |

| US10983554B2 (en) * | 2019-02-15 | 2021-04-20 | Wipro Limited | Method and system for clock synchronization based on time based control |

| JP6751460B1 (ja) * | 2019-05-30 | 2020-09-02 | 華邦電子股▲ふん▼有限公司Winbond Electronics Corp. | 疑似スタティックランダムアクセスメモリ及びそのデータ書き込み方法 |

| CN112102859B (zh) * | 2019-06-17 | 2023-08-15 | 华邦电子股份有限公司 | 伪静态随机存取存储器及其数据写入方法 |

| KR20210126821A (ko) * | 2020-04-10 | 2021-10-21 | 삼성전자주식회사 | 반도체 장치 |

| KR20210141120A (ko) * | 2020-05-15 | 2021-11-23 | 에스케이하이닉스 주식회사 | 위상조절동작을 수행하기 위한 시스템 |

| CN116959518B (zh) * | 2023-07-25 | 2024-03-19 | 合芯科技(苏州)有限公司 | 自定时电路与静态随机存取存储器 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5771264A (en) * | 1996-08-29 | 1998-06-23 | Altera Corporation | Digital delay lock loop for clock signal frequency multiplication |

| US5990714A (en) * | 1996-12-26 | 1999-11-23 | United Microelectronics Corporation | Clock signal generating circuit using variable delay circuit |

| JPH10190448A (ja) | 1996-12-26 | 1998-07-21 | Nippon Steel Corp | 位相比較回路及び信号発生回路 |

| JP3792329B2 (ja) | 1997-01-20 | 2006-07-05 | 聯華電子股▲分▼有限公司 | 内部クロック発生回路 |

| JP2954070B2 (ja) * | 1997-03-26 | 1999-09-27 | 日本電気アイシーマイコンシステム株式会社 | デジタルpll回路 |

| JP3945894B2 (ja) | 1997-04-21 | 2007-07-18 | 富士通株式会社 | 半導体装置及び信号入力状態検出回路 |

| US5969552A (en) * | 1998-01-15 | 1999-10-19 | Silicon Image, Inc. | Dual loop delay-locked loop |

| KR100305646B1 (ko) * | 1998-05-29 | 2001-11-30 | 박종섭 | 클럭보정회로 |

| US6240046B1 (en) * | 1999-02-13 | 2001-05-29 | Integrated Device Technology, Inc. | Integrated circuit random access memory capable of reading either one or more than one data word in a single clock cycle |

-

2000

- 2000-06-09 JP JP2000173475A patent/JP4443728B2/ja not_active Expired - Fee Related

-

2001

- 2001-02-28 US US09/793,999 patent/US6417715B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001351381A (ja) | 2001-12-21 |

| US20010052808A1 (en) | 2001-12-20 |

| US6417715B2 (en) | 2002-07-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4443728B2 (ja) | クロック発生回路 | |

| US10679683B1 (en) | Timing circuit for command path in a memory device | |

| KR100305546B1 (ko) | 반도체장치,반도체시스템및디지탈지연회로 | |

| US6928007B2 (en) | ODT mode conversion circuit and method | |

| US7750699B2 (en) | Delay locked loop circuit | |

| US7501866B2 (en) | Delay locked loop circuit | |

| US8111580B2 (en) | Multi-phase duty-cycle corrected clock signal generator and memory having same | |

| KR100837822B1 (ko) | Dll 회로 및 그 제어 방법 | |

| US6975149B2 (en) | Method and circuit for adjusting the timing of output data based on an operational mode of output drivers | |

| US7227809B2 (en) | Clock generator having a delay locked loop and duty cycle correction circuit in a parallel configuration | |

| US7649390B2 (en) | Delay locked loop for high speed semiconductor memory device | |

| US6757212B2 (en) | Clock synchronous type semiconductor memory device | |

| US6259288B1 (en) | Semiconductor integrated circuit having a DLL circuit and a special power supply circuit for the DLL circuit | |

| US7671647B2 (en) | Apparatus and method for trimming static delay of a synchronizing circuit | |

| US20070001724A1 (en) | Delay locked loop circuit | |

| KR100987359B1 (ko) | 데이터 입출력 회로 | |

| JPH11353878A (ja) | 半導体装置 | |

| JP2015012352A (ja) | 半導体装置 | |

| US7994833B2 (en) | Delay locked loop for high speed semiconductor memory device | |

| KR100753101B1 (ko) | 락킹 페일 방지 위한 지연고정루프 클럭 생성 방법 및 장치 | |

| US7099232B2 (en) | Delay locked loop device | |

| US11025255B2 (en) | Signal generation circuit synchronized with a clock signal and a semiconductor apparatus using the same | |

| US6333875B1 (en) | Semiconductor circuit with adjustment of double data rate data latch timings | |

| US6318707B1 (en) | Semiconductor integrated circuit device | |

| KR100859834B1 (ko) | 지연 고정 루프와 그의 구동 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070524 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070524 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090804 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090930 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100105 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100113 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130122 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130122 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130122 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130122 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140122 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |