JP2011044795A - 入力インターフェース回路 - Google Patents

入力インターフェース回路 Download PDFInfo

- Publication number

- JP2011044795A JP2011044795A JP2009190102A JP2009190102A JP2011044795A JP 2011044795 A JP2011044795 A JP 2011044795A JP 2009190102 A JP2009190102 A JP 2009190102A JP 2009190102 A JP2009190102 A JP 2009190102A JP 2011044795 A JP2011044795 A JP 2011044795A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- clock

- delay

- input

- phase

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0814—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the phase shifting device being digitally controlled

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1078—Data input circuits, e.g. write amplifiers, data input buffers, data input registers, data input level conversion circuits

- G11C7/1087—Data input latches

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1078—Data input circuits, e.g. write amplifiers, data input buffers, data input registers, data input level conversion circuits

- G11C7/1093—Input synchronization

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

- G11C7/222—Clock generating, synchronizing or distributing circuits within memory device

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0816—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the controlled phase shifter and the frequency- or phase-detection arrangement being connected to a common input

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0818—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the controlled phase shifter comprising coarse and fine delay or phase-shifting means

Abstract

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

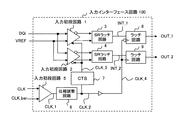

【選択図】図1

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

【選択図】図1

Description

本発明は半導体メモリ装置のインターフェース技術に関し、特に入力インターフェース回路に関する。

高速インターフェース技術の急速な進化に伴い、デバイス間のデータ通信の動作スピードが高速化している。近年では、各デバイスの入出力インターフェース回路間でのデータ通信に関して、その動作スピードは1GHzを超えている。

特に、シンクロナスメモリとCPU間のインターフェースにおいては、シンクロナスメモリは、CPUから出力されるクロック信号とそのクロック信号に同期したデータ信号とを受信し、クロック信号の立ち上がりと立ち下がり信号を用いてデータ信号をラッチするというシステム構成がとられている。

図11に、本発明に関連する一般的な入力回路を示す。図11に示す入力インターフェース回路300は、入力初段回路61、63と、クロックツリー回路(CTS)64、クロックツリーレプリカ回路(CTSレプリカ)62と、ラッチ回路65、66と、を備えている。図11では、DQiから入力されるデータを、ラッチ回路2、3を用いてラッチする構成を示している。尚、図12に、入力初段回路61、63としてのバッファを示す。

図13は、外部から入力されるクロック信号と、データ(DQi信号)と、入力インターフェース回路300における内部信号と、の波形を示す。

DDRインターフェースでは、入力クロック(CLK)に対して位相が90度ずれたデータ(DQi信号)が入力される。また、1つのCLK pinによるクロックで複数のアドレスやデータの入力をラッチするシステムとなっているために、各アドレス及びデータに対してCLKを分配しなくてはならない。

CLKを分配することで、CLKラインにはt6で示すクロック遅延(図11に示したCTS64を通過することで付加される遅延)が付いてしまう。このため、ラッチ回路65、66を用いてデータを正常にラッチするためには、CLKラインに付加される遅延と同等の遅延量(t7で示す遅延)をデータに対しても付加する必要がある(図11に示したCTSレプリカ62を通過することで付加される遅延)。その理由は、ラッチ回路65、66は、CLKの立ち上がり及び立ち下がりエッジに対して、t8で示すセットアップ特性と、t9で示すホールド特性とを十分に確保する必要があるためである。

特許文献1には、シンクロナスメモリのデータ信号をラッチするための、メモリインターフェース回路が開示されている。図14は、特許文献1に記載のメモリインターフェース回路を示すブロック図である。

図14において、211はDDR−SDRAM、212はDQS信号、213a、213bはデータ信号、215は入力バッファ、216は遅延回路、217はデータラッチ、221はメモリインターフェース回路、222はリードクロック発生回路、223はメインステートマシン、257はデータストローブ信号、253はリードクロック、250は発振回路、260は位相比較器、262は制御回路である。

DDR−SDRAM211は、クロックに同期してDQS信号212及びデータ信号213を出力する。メモリインターフェース回路221は、DDR−SDRAM211と接続可能である。遅延回路216は、発振回路250が出力するクロックを遅延してリードクロック253として出力する。位相比較器260は、入力されたデータストローブ信号257とリードクロック253の位相差を測定する。遅延回路216は、測定した位相差に従ってリードクロック253の遅延時間を加減する。データラッチ217は、リードクロック253に同期してデータ信号213を取り込む。これにより、特許文献1に記載のメモリインターフェース回路221は、伝送条件の悪化や不整合がある場合においても、安定した信頼性の高いデータ信号のラッチ動作を可能とするものとである。

しかしながら、図11に示した一般的なDDR入力インターフェースでは、図12に示したバッファを用いてDQiのデータ信号のレベルを増幅した後に、CTS64を通過する際に相当する遅延量をCTSレプリカ62において付加させるという構成をとることで、ラッチ回路65、66でデータをラッチしている。このため、バッファ及びクロック遅延を経由することで、ラッチ回路65、66に必要とされる有効なセットアップ特性及びホールド特性を悪化させてしまうという問題がある。すなわち、理想的な回路であれば、図13においては"t10=t8"及び"t11=t9"となるのが理想であるが、実際の回路では、トランジスタのばらつきや電源変動により、通常は"t10>t8"、"t11>t9"となってしまう。

また、遅延量の付加は、t8及びt9を劣化させる要因を増加することになるため、高周波動作においては、セットアップ特性及びホールド特性の大幅な悪化をもたらすおそれがある。

特許文献1に記載のメモリインターフェース回路221においても、データ信号線213aが入力バッファ215を経由することで、有効なセットアップ特性及びホールド特性を悪化させてしまう。また、内部発信回路250を用いているために、クロック入力信号212や内部発振回路250とは独立してジッタやデューティ崩れが生じてしまい、セットアップ特性及びホールド特性の悪化を招くという問題がある。

本発明に係る入力インターフェース回路は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、前記入力初段回路に含まれるラッチ回路へのラッチタイミング信号とを同位相に調整する位相調整回路と、を備え、前記位相調整回路は、前記クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路を通過して前記ラッチ回路へと供給される前記ラッチタイミング信号の遅延時間を調整するものである。

これにより、遅延回路において発生するジッタやデューティの悪化を抑制することができるため、ラッチ回路に必要となる有効なセットアップ特性及びホールド特性を良好に確保することができる。

本発明にかかる入力インターフェース回路によれば、有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供することができる。

以下、本発明を実施するための最良の形態について、図面を参照しながら詳細に説明する。説明の明確化のため、以下の記載及び図面は、適宜、省略及び簡潔化がなされている。各図面において同一の構成又は機能を有する構成要素及び相当部分には、同一の符号を付し、その説明を省略する。

実施の形態1.

図1は、本発明の実施の形態1に係る入力インターフェース回路を示すブロック図である。入力インターフェース回路100は、DDRメモリ(不図示)と接続され、クロック(CLK)に同期したDQi信号及びデータ信号が入力される。

図1は、本発明の実施の形態1に係る入力インターフェース回路を示すブロック図である。入力インターフェース回路100は、DDRメモリ(不図示)と接続され、クロック(CLK)に同期したDQi信号及びデータ信号が入力される。

入力インターフェース回路100は、入力初段回路1、2と、SRラッチ回路3、4と、入力初段回路5と、位相調整回路6と、クロックツリー回路(CTS)7と、立ち下りエッジでデータをラッチするラッチ回路8、立ち上がりエッジでデータをラッチするラッチ回路9と、を備えている。図1において、ラッチ型入力初段回路が、入力初段回路1、2と、SRラッチ回路3、4と、に相当する。

入力初段回路1は、CLK_3の立ち上がり信号に同期して、外部端子DQiの信号レベルと外部Vref端子の信号レベルとを比較し、比較結果を出力する。入力初段回路1は、CLK_3の立ち上がりエッジにおいて、DQi信号とVREF信号(例えば、DQi信号の振幅レベルの中間電位。)の信号レベルを比較した結果を増幅する。増幅した信号レベルは、CLK_3信号の立ち上がりエッジから次の立ち上がりエッジまでの1サイクルの間、SRラッチ回路3によってラッチされる。

入力初段回路2は、CLK_3の立ち下がり信号に同期して、外部端子DQiの信号レベルと外部Vref端子の信号レベルとを比較し、比較結果を出力する。入力初段回路2は、CLK_3の立ち下がりエッジにおいて、DQi信号とVREF信号の信号レベルを比較した結果を増幅する。増幅した信号レベルは、CLK_3信号の立ち下がりエッジから次の立ち下がりエッジまでの1サイクルの間、SRラッチ回路4によってラッチされる。

SRラッチ回路3、4は、入力初段回路1及び入力初段回路2の出力結果をそれぞれラッチする、SR型のラッチ回路である。入力初段回路5は、CLK用の初段回路であり、CLK信号及びその反転信号(CLK_bar)が入力される。

位相調整回路6は、入力初段回路1及び入力初段回路2に入力されるCLK_3の位相を、外部CLK端子のクロックと同相に調整する。クロックツリー回路(CTS)7は、各データにCLK_3を分配するクロック遅延素子から構成される。

ラッチ回路8、9は、CLK_4を用いて、内部的にデータをラッチする。具体的には、ラッチ回路8は、CLK_4の立ち下がりエッジで、SRラッチ回路3の出力結果(INT_1)をラッチする。また、ラッチ回路9は、CLK_4の立ち上がりエッジで、SRラッチ回路4の出力結果(INT_2)をラッチする。

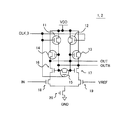

図2は、入力初段回路1、2を示す。図に示すように、入力クロック信号(CLK_3)が、Pchトランジスタ11、12、15のゲートにそれぞれ入力される。入力信号IN及び入力信号VREFが、Nchトランジスタ18、19のそれぞれのゲートに入力される。また、Pchトランジスタ11、12、13、14のソース端子が電源端子VDDに接続され、Nchトランジスタ20のソース端子がGNDに接続される。

出力端子OUTが、Pchトランジスタ12、14、15のドレイン端子と、Pchトランジスタ13及びNchトランジスタ17のゲートと、Nchトランジスタ16のドレインと、に接続される。出力端子OUTBが、Pchトランジスタ11、13のドレイン端子と、Pchトランジスタ15のソース端子と、Pchトランジスタ14と、Nchトランジスタ16のゲートと、Nchトランジスタ17のドレインと、に接続される。

Nchトランジスタ16のソースが、Nchトランジスタ18のドレインと接続される。Nchトランジスタ17のソースが、Nchトランジスタ19のドレインと接続される。Nchトランジスタ20のドレインが、Nchトランジスタ18、19のソースと接続される。

図3は、SRラッチ回路3、4を示す。図に示すように、SRラッチ回路3、4は、入力初段回路1、2の出力結果(OUT、OUTB)を、それぞれIN_1、IN_2として入力する。NAND_1には、IN_1及びO_1が入力され、SRラッチ回路3、4の出力であるOUTを出力する。また、NAND_2には、IN_2及びOUTが入力され、O_1を出力する。

図4は、位相調整回路6の詳細な構成を示すブロック図である。位相調整回路6は、CLK_7の位相がCLK_1の位相に近づくように位相を調整する。位相調整回路6は、インバーター31と、マルチプレクサー32と、遅延調整コントロール回路33と、粗遅延調整回路34と、微遅延調整回路35と、入力初段回路36と、クロックツリー回路(CTSレプリカ)37と、位相比較器38と、を備えている。

位相調整回路6に入力されるCLK_1が、インバーター31と、マルチプレクサー32に入力され、また、インバーター31の出力がマルチプレクサー32に入力される。インバーター31を通過した反転クロックであるCLK_5が、マルチプレクサー32に入力される。

マルチプレクサー32は、遅延調整コントロール回路33からの出力信号M_0によって制御される。すなわち、マルチプレクサー32は、信号M_0に応じて、インバーター31からの出力クロックCLK_5及びCLK_1を選択する。

マルチプレクサー32の出力信号(CLK_6)が、粗遅延調整回路34に入力される。粗遅延調整回路34の出力信号(CLK_8)が、微遅延調整回路35に入力される。微遅延調整回路35の出力信号(CLK_2)が、入力初段回路36に入力されると共に、位相調整回路6の出力信号として出力される。CTSレプリカ37を通過した出力信号(CLK_7)と、CLK_1とが、位相比較器38に入力される。位相比較器38は、CLK_7及びCLK_1の位相を比較し、比較結果信号(OUT_5)を、遅延調整コントロール回路33に出力する。

入力初段回路36は、入力初段回路36を擬似したレプリカ回路である。CTSレプリカ37は、CTS7を擬似したレプリカ回路であり、CTS7と同様のクロック遅延を付加するための、クロック信号レプリカ素子から構成される。すなわち、微遅延調整回路35から出力されるCLK_2が入力初段回路36及びCTSレプリカ37を通過することで得られるCLK_7は、外部CLKが入力初段回路5及びCTS7を通過することで得られるCLK_3と同様の遅延量を有することになる。

遅延調整コントロール回路33は、位相比較結果に基づいて、マルチプレクサー32の制御を行うことで、粗遅延調整回路34及び微遅延調整回路35の遅延を調整する。このため、制御信号として、M_0、N_0[n:0]、N_1[n:0]を出力する。

図5は、粗遅延調整回路34を示す。粗遅延調整回路34は、遅延調整コントロール回路33から入力される入力信号N_0[n:0]の値に応じて、CLK_6に対するCLK_8の遅延を調整することができる。図5に示す例では、各トランジスタのサイズは同一であり、HighにするN_0[n:0]の個数を増加させることで、CLK_6の位相に対するCLK_8の遅延量を増加させることができる。初期状態では、N_00のみをHighとすることで、最小の遅延値が設定される。そして、N_01、N_02、...、N_0nを順次Highとすることで、遅延量を増加させていくことができる。

図6は、微遅延調整回路35を示す。微遅延調整回路35は、遅延調整コントロール回路33から入力される入力信号N_1[n:0]の値に応じて、CLK_8に対するCLK_2の遅延を調整することができる。図6に示す例では、各トランジスタのサイズは同一であり、LowにするN_1[n:0]の個数を増加させることで、CLK_8の位相に対するCLK_2の遅延量を増加させることができる。初期状態では、全てのN_1[n:0]をHighとすることで、最小の遅延値が設定される。そして、N_11、N_12、...、N_1mを順次Lowとすることで、遅延量を増加させていくことができる。

図7は、位相比較器38を示す。位相比較器38は、CLK_1の位相と、遅延回路を経由したCLK7の位相と、を比較する。位相比較器38は、CLK_1の位相に対してCLK_7の位相が180度以上遅れている場合には、OUT_5の出力としてHighを出力し、位相遅れが180より小さい範囲の遅れである場合には、OUT_5の出力としてLowを出力する。

図8は、CLKと、DQiと、入力インターフェース回路100における内部信号と、の波形を示す。DDRインターフェースの入力においては、入力クロック(CLK)に対するデータ(DQi)の入力タイミングは、スペックにより規定されたセットアップ時間(図4においてt4で示す時間)及びホールド時間(図4においてt5で示す時間)が確保されたタイミングで行われる。このため、入力初段回路1、2に入力されるCLK_3信号の位相に関して、位相調整回路6によりt2で示す遅延時間を調整することで、CLK_3がCLKと同位相となるように調整する必要がある。ここでは、入力初段回路5を通過する際にt1で示す遅延時間が付加され、CTS7を通過する際にt3で示す遅延時間が付加される。尚、位相調整回路6による位相調整動作の詳細については後述する。

図8において、DQ0はDQiのうちの一つのデータ波形である。DQ0の波形に含まれる太線で示す部分は、DQ0のうちの有効なData部分に対応する。まず、CLK_3の立ち上がりエッジで、入力初段回路1におけるDQ0とVREFとの比較結果信号であるIN_1及びIN_2が出力される。SRラッチ回路3は、入力初段回路1からのIN_1及びIN_2に基づき、有効Dataをラッチ回路8に出力する。SRラッチ回路8は、有効Dataを、CLK_4の立ち下がりエッジでラッチする。一方で、CLK_3の立ち下がりエッジで、入力初段回路2におけるDQ0とVREFとの比較結果信号であるIN_1及びIN_2が出力される。SRラッチ回路4は、入力初段回路2からのIN_1及びIN_2に基づき、有効Dataをラッチ回路9に出力する。SRラッチ回路9は、有効Dataを、CLK_4の立ち上がりエッジでラッチする。

尚、位相調整回路6が初期状態である場合には、マルチプレクサー32は、CLK_1をそのまま通過させる設定であり、また、粗遅延調整回路34及び微遅延調整回路35には、最小の遅延値が出力される設定がなされているものとする。このため、初期状態では、位相調整回路6における遅延を0であるとした場合(すなわち、t2=0の場合)には、CLK_3の位相はCLK_1の位相に対してt1+t3だけ遅れることになる。

次に、図9を参照して、本発明の実施の形態1に係る位相調整動作について説明する。図9は、遅延調整コントロール回路33による、遅延調整のシーケンスを示す。

SEQ1において、遅延調整コントロール回路33が動作し始めた場合に、まず、初期位相を確認する(S1)。ここでは、位相比較器38は、CLK_1の位相に対してCLK_7の位相が180度以上遅れている場合にはHighを出力し、位相遅れが180度よりも小さい範囲の場合にはLowを出力するものとして説明する。

遅延調整コントロール回路33は、位相確認の結果、CLK_1の位相に対してCLK_7の位相が180度より小さい範囲の遅れである場合(S1においてYESの場合)には、CLK_1の反転信号が出力するようにマルチプレクサー32の制御を行う(S2)(すなわち、マルチプレクサー32がインバーター31からの出力(CLK_5)を選択するようにM_0の値を制御する。)。

本来、CLK_1の位相に対してCLK_7の位相が180度より小さい範囲の遅れである場合には、CLK_7及びCLK_1の位相関係を等しくするためには、180度以上の遅延調整が必要となる。このため、SEQ1において、位相の判定及び反転を行うことで、SEQ2の開始状態において、位相比較器38は、High(CLK_7がCLK_1の位相より、180度以上遅れている。)を必ず出力することになる。

次いで、SEQ2において、位相比較器38による出力結果からCLK_7の位相を検知する(S3)。位相検知の結果、CLK_1の位相に対してCLK_7の位相が180度以上遅れている場合(位相比較器38の出力がHighある場合、すなわち、S3においてNo)である場合には、位相比較器38の出力がLowになるまでの間(S3においてYESとなるまでの間)、粗遅延調整回路34の遅延値を増加させていく。例えば、現在、粗遅延調整回路34のn番目のトランジスタまでの制御信号がHighとなっている場合に、その次のトランジスタのアドレス(n+1番目)の制御信号をHighとする。上述したように、SEQ2の開始状態においては、位相比較器38の出力はHighであるため、この状態から位相比較器38の出力がLowになるまでの間、粗遅延調整回路34の遅延値を増加させていく(S4)。

そして、位相比較器38の出力がLowになった場合には、粗遅延調整回路34の遅延値は、位相比較器38の出力がLowになる1つ手前の遅延値に設定される(S5)。例えば、現在、粗遅延調整回路34のn番目のトランジスタまでの制御信号がHighとなっている場合には、そのn番目のトランジスタの制御信号をLowとすることで、その一つ前のトランジスタのアドレス(n−1番目)までの制御信号がHighであるようにする。尚、SEQ3の開始状態においても、位相比較器38の出力はHighとなる。

次いで、SEQ3において、位相比較器38による出力結果からCLK_7の位相を検知する(S6)。位相検知の結果、CLK_1の位相に対してCLK_7の位相が180度以上遅れている場合(位相比較器38の出力がHighある場合、すなわち、S6においてNo)である場合には、位相比較器38の出力がLowになるまでの間(S6においてYESとなるまでの間)、微遅延調整回路35の遅延値を増加させていく(S7)。例えば、現在、微遅延調整回路35のn番目のトランジスタまでの制御信号がLowとなっている場合に、その次のトランジスタのアドレス(n+1番目)の制御信号をLowとする。

そして、位相比較器38の出力がLowになった時点で、微遅延調整回路35の遅延値は、位相比較器38の出力がLowになる1つ手前の遅延値に設定される(S8)。例えば、現在、微遅延調整回路35のn番目のトランジスタまでの制御信号がLowとなっている場合には、そのn番目のトランジスタの制御信号をHighとすることで、その一つ前のトランジスタのアドレス(n−1番目)までの制御信号がLowであるようにする。

さらに、SEQ4においては、位相比較器38により位相を常時検知しながら、位相の補正を行う(S9、10、11)。SEQ4では、CLK_1の位相に対してCLK_7の位相が追従するように、微遅延調整回路35による遅延の調整が行われる。

以上説明したように、入力インターフェースとしてラッチ型の入力初段回路を備えることで(すなわち、SRラッチ回路3、4を備え、位相調整回路6によって外部CLKとSRラッチ回路3、4へと供給するCLK3とを同相になるように調整することで)、従来、ジッタやデューティを悪化させていた初段回路や初段回路以降の遅延の影響を無視することができる。

さらに、遅延調整コントロール回路33の初期状態において、入力初段回路36を通過したCLK_7が、CLK入力端子のCLK_1に対して180度より進んでいない場合には初期位相を反転し、180度以上進んでいる場合には位相を反転させずにスルーさせることで、位相調整回路6において調整する遅延量を小さくすることができる。

従って、遅延回路において発生するジッタやデューティの悪化を抑制することができるために、ラッチ回路8、9に必要となる有効なセットアップ特性及びホールド特性を良好に確保することができる。

実施の形態2.

図10は、本発明の実施の形態2に係る入力インターフェース回路を示すブロック図である。入力インターフェース回路200は、図1に示した入力インターフェース回路100と比べて、位相調整回路6に換えて、立ち下がりCLK用の位相調整回路(立ち下がりエッジ用位相調整回路)46と、立ち上がりCLK用の位相調整回路(立ち上がりエッジ用位相調整回路)47と、の2つの位相調整回路を備えたことを特徴とする。尚、入力初段回路41、42は図1に示した入力初段回路1、2と、SRラッチ回路43、44はSRラッチ回路3、4と、入力初段回路45は入力初段回路5と、CTS48、49はCTS7と、ラッチ回路50、51はラッチ回路8、9と同様の構成であるため、ここではその説明を省略する。

図10は、本発明の実施の形態2に係る入力インターフェース回路を示すブロック図である。入力インターフェース回路200は、図1に示した入力インターフェース回路100と比べて、位相調整回路6に換えて、立ち下がりCLK用の位相調整回路(立ち下がりエッジ用位相調整回路)46と、立ち上がりCLK用の位相調整回路(立ち上がりエッジ用位相調整回路)47と、の2つの位相調整回路を備えたことを特徴とする。尚、入力初段回路41、42は図1に示した入力初段回路1、2と、SRラッチ回路43、44はSRラッチ回路3、4と、入力初段回路45は入力初段回路5と、CTS48、49はCTS7と、ラッチ回路50、51はラッチ回路8、9と同様の構成であるため、ここではその説明を省略する。

図1に示した入力インターフェース回路100では、位相比較器38が比較する信号は、CLK_1でのCLK_7の立ち上がりエッジのみを検出対象としている。このため、位相調整回路6から出力されるCLK_2の立ち下がりエッジについては、正確に位相の合わせこみを行うことができない。従って、入力初段回路2に入力されるCLK_3の立ち下りエッジの位相は、CLK_1の立ち下がりエッジの位相と比較して、ずれている可能性がある。

これに対して、図10に示す入力インターフェース回路200は、立ち下がりエッジ及び立ち上がりエッジの両エッジの遅延に対して、それぞれ位相調整回路46、47を備えることで、入力初段回路41、42に入力される両方のエッジ(CLK_12のエッジ、CLK_13のエッジ)を、CLK_9の位相に合わせことできる。

尚、本発明は上述した実施の形態のみに限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能であることは勿論である。

100 入力インターフェース回路、

1、2 入力初段回路、 3、4 SRラッチ回路、 5 入力初段回路、

6 位相調整回路、 7 クロックツリー回路(CTS)、 8、9 ラッチ回路、

31 インバーター、 32 マルチプレクサー、

33 遅延調整コントロール回路、 34 粗遅延調整回路、

35 微遅延調整回路、 36 入力初段回路、

37 クロックツリー回路(CTSレプリカ)、 38 位相比較器、

200 入力インターフェース回路、

46 立ち下がりエッジ用位相調整回路、 47 立ち上がりエッジ用位相調整回路、

41、42 入力初段回路、 43、44 SRラッチ回路、 45 入力初段回路、

48、49 CTS、 50、51 ラッチ回路、

300 入力インターフェース回路、

61、63 入力初段回路、

62 クロックツリーレプリカ回路(CTSレプリカ)、

64 クロックツリー回路(CTS)、 65、66 ラッチ回路、

211 DDR−SDRAM、 212 DQS信号、

213a、213b データ信号、 215 入力バッファ、 216 遅延回路、

217 データラッチ、 221 メモリインターフェース回路、

222 リードクロック発生回路、 223 メインステートマシン、

257 データストローブ信号、 253 リードクロック、 250 発振回路、

260 位相比較器、 262 制御回路

1、2 入力初段回路、 3、4 SRラッチ回路、 5 入力初段回路、

6 位相調整回路、 7 クロックツリー回路(CTS)、 8、9 ラッチ回路、

31 インバーター、 32 マルチプレクサー、

33 遅延調整コントロール回路、 34 粗遅延調整回路、

35 微遅延調整回路、 36 入力初段回路、

37 クロックツリー回路(CTSレプリカ)、 38 位相比較器、

200 入力インターフェース回路、

46 立ち下がりエッジ用位相調整回路、 47 立ち上がりエッジ用位相調整回路、

41、42 入力初段回路、 43、44 SRラッチ回路、 45 入力初段回路、

48、49 CTS、 50、51 ラッチ回路、

300 入力インターフェース回路、

61、63 入力初段回路、

62 クロックツリーレプリカ回路(CTSレプリカ)、

64 クロックツリー回路(CTS)、 65、66 ラッチ回路、

211 DDR−SDRAM、 212 DQS信号、

213a、213b データ信号、 215 入力バッファ、 216 遅延回路、

217 データラッチ、 221 メモリインターフェース回路、

222 リードクロック発生回路、 223 メインステートマシン、

257 データストローブ信号、 253 リードクロック、 250 発振回路、

260 位相比較器、 262 制御回路

Claims (5)

- データが外部入力される信号端子に接続される入力初段回路と、

外部入力されるクロックと、前記入力初段回路に含まれるラッチ回路へのラッチタイミング信号とを同位相に調整する位相調整回路と、を備え、

前記位相調整回路は、

前記クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路を通過して前記ラッチ回路へと供給される前記ラッチタイミング信号の遅延時間を調整する

ことを特徴とする入力インターフェース回路。 - 前記位相調整回路は、

前記クロックの遅延時間を調整する遅延調整回路と、

前記遅延調整回路により遅延時間が調整されたクロックが入力され、前記クロックツリー回路を擬似する擬似クロックツリー回路と、

前記擬似クロックツリー回路の出力結果と、前記クロックとの位相を比較する位相比較器と、

前記位相比較器の比較結果に基づいて、前記遅延調整回路の遅延量を調整する遅延調整コントロール回路と、を備える

ことを特徴とする請求項1に記載の入力インターフェース回路。 - 前記遅延調整回路は、

前記クロックの遅延時間を粗調整する粗遅延調整回路と、

前記クロックの遅延時間を微調整する微遅延調整回路と、を備え、

前記遅延調整コントロール回路は、

前記粗遅延調整回路により前記クロックの遅延時間を粗調整した後に、前記微遅延調整回路により前記粗調整したクロックの遅延時間を微調整する

ことを特徴とする請求項1又は2に記載の入力インターフェース回路。 - 前記位相調整回路は、

前記クロックと、当該クロックの反転信号とが入力され、選択した信号を前記遅延調整回路に出力するマルチプレクサーを更に備え、

前記遅延調整コントロール回路は、

前記位相比較器の比較結果に基づいて、前記マルチプレクサーを制御する

ことを特徴とする請求項1乃至3いずれか1項に記載の入力インターフェース回路。 - 前記入力初段回路は、第1及び第2のラッチ回路を備え、

前記位相調整回路は、

前記クロックの立ち上がりエッジと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいて第1のクロックツリー回路を通過して前記第1のラッチ回路へと供給される前記ラッチタイミング信号の遅延時間を調整する第1の位相調整回路と、

前記クロックの立ち下がりエッジと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいて第2のクロックツリー回路を通過して前記第2のラッチ回路へと供給される前記ラッチタイミング信号の遅延時間を調整する第2の位相調整回路と、を備える

ことを特徴とする請求項1乃至4いずれか1項に記載の入力インターフェース回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009190102A JP2011044795A (ja) | 2009-08-19 | 2009-08-19 | 入力インターフェース回路 |

| US12/801,482 US8446196B2 (en) | 2009-08-19 | 2010-06-10 | Input interface circuit |

| CN2010102370931A CN101996674A (zh) | 2009-08-19 | 2010-07-21 | 输入接口电路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009190102A JP2011044795A (ja) | 2009-08-19 | 2009-08-19 | 入力インターフェース回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011044795A true JP2011044795A (ja) | 2011-03-03 |

| JP2011044795A5 JP2011044795A5 (ja) | 2012-04-05 |

Family

ID=43604848

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009190102A Pending JP2011044795A (ja) | 2009-08-19 | 2009-08-19 | 入力インターフェース回路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8446196B2 (ja) |

| JP (1) | JP2011044795A (ja) |

| CN (1) | CN101996674A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8976596B1 (en) | 2013-08-23 | 2015-03-10 | Kabushiki Kaisha Toshiba | Controller |

| JP2018064233A (ja) * | 2016-10-14 | 2018-04-19 | 日本電気株式会社 | スルーレート調整回路、及びスルーレート調整方法 |

| WO2021145109A1 (ja) * | 2020-01-16 | 2021-07-22 | ソニーセミコンダクタソリューションズ株式会社 | 受信回路 |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6051500B2 (ja) | 2011-03-15 | 2016-12-27 | 株式会社リコー | 画像読取装置及び電子機器 |

| EP2774151B1 (en) * | 2011-11-01 | 2019-08-14 | Rambus Inc. | Data transmission using delayed timing signals |

| US9479173B1 (en) * | 2012-01-27 | 2016-10-25 | Altera Corporation | Transition accelerator circuitry |

| US9325542B2 (en) * | 2012-11-21 | 2016-04-26 | Globalfoundries Inc. | Power-scalable skew compensation in source-synchronous parallel interfaces |

| KR20170008077A (ko) * | 2015-07-13 | 2017-01-23 | 에스케이하이닉스 주식회사 | 고속 통신을 위한 인터페이스 회로 및 이를 포함하는 시스템 |

| CN105262464B (zh) * | 2015-11-16 | 2018-05-08 | 西安紫光国芯半导体有限公司 | 减小芯片输入端口所需建立保持时间的电路及方法 |

| CN107591173B (zh) * | 2016-07-06 | 2020-07-03 | 华邦电子股份有限公司 | 半导体存储器装置及其时脉调整方法 |

| US10347307B2 (en) * | 2017-06-29 | 2019-07-09 | SK Hynix Inc. | Skew control circuit and interface circuit including the same |

| US10256795B1 (en) * | 2017-10-11 | 2019-04-09 | Micron Technology, Inc. | Pipelined latches to prevent metastability |

| KR102495361B1 (ko) * | 2018-03-14 | 2023-02-06 | 에스케이하이닉스 주식회사 | 입출력 회로 |

| US10431293B1 (en) * | 2018-07-23 | 2019-10-01 | Micron Technology, Inc. | Systems and methods for controlling data strobe signals during read operations |

| CN110827885B (zh) * | 2018-08-13 | 2023-03-31 | 华邦电子股份有限公司 | 输入接收器电路及自适应反馈方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10336008A (ja) * | 1997-05-30 | 1998-12-18 | Fujitsu Ltd | クロック発生回路及び半導体装置 |

| JP2004342212A (ja) * | 2003-05-15 | 2004-12-02 | Elpida Memory Inc | クロック発生回路およびそれを用いた半導体記憶装置 |

| JP2005044854A (ja) * | 2003-07-23 | 2005-02-17 | Handotai Rikougaku Kenkyu Center:Kk | クロックツリー回路、半導体集積回路装置、半導体集積回路装置の設計方法、および、半導体集積回路の設計プログラムを記録した媒体 |

| JP2007265606A (ja) * | 2007-05-18 | 2007-10-11 | Fujitsu Ltd | 半導体集積回路 |

| JP2008071018A (ja) * | 2006-09-13 | 2008-03-27 | Matsushita Electric Ind Co Ltd | メモリインターフェース回路 |

| JP2009124703A (ja) * | 2007-11-09 | 2009-06-04 | Hynix Semiconductor Inc | データセンタートラッキング回路及びこれを含む半導体集積回路 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4443728B2 (ja) * | 2000-06-09 | 2010-03-31 | 株式会社ルネサステクノロジ | クロック発生回路 |

| KR100812602B1 (ko) * | 2006-09-29 | 2008-03-13 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 및 그 구동방법 |

-

2009

- 2009-08-19 JP JP2009190102A patent/JP2011044795A/ja active Pending

-

2010

- 2010-06-10 US US12/801,482 patent/US8446196B2/en not_active Expired - Fee Related

- 2010-07-21 CN CN2010102370931A patent/CN101996674A/zh active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10336008A (ja) * | 1997-05-30 | 1998-12-18 | Fujitsu Ltd | クロック発生回路及び半導体装置 |

| JP2004342212A (ja) * | 2003-05-15 | 2004-12-02 | Elpida Memory Inc | クロック発生回路およびそれを用いた半導体記憶装置 |

| JP2005044854A (ja) * | 2003-07-23 | 2005-02-17 | Handotai Rikougaku Kenkyu Center:Kk | クロックツリー回路、半導体集積回路装置、半導体集積回路装置の設計方法、および、半導体集積回路の設計プログラムを記録した媒体 |

| JP2008071018A (ja) * | 2006-09-13 | 2008-03-27 | Matsushita Electric Ind Co Ltd | メモリインターフェース回路 |

| JP2007265606A (ja) * | 2007-05-18 | 2007-10-11 | Fujitsu Ltd | 半導体集積回路 |

| JP2009124703A (ja) * | 2007-11-09 | 2009-06-04 | Hynix Semiconductor Inc | データセンタートラッキング回路及びこれを含む半導体集積回路 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8976596B1 (en) | 2013-08-23 | 2015-03-10 | Kabushiki Kaisha Toshiba | Controller |

| JP2018064233A (ja) * | 2016-10-14 | 2018-04-19 | 日本電気株式会社 | スルーレート調整回路、及びスルーレート調整方法 |

| US10374586B2 (en) | 2016-10-14 | 2019-08-06 | Nec Corporation | Slew rate adjusting circuit and slew rate adjusting method |

| WO2021145109A1 (ja) * | 2020-01-16 | 2021-07-22 | ソニーセミコンダクタソリューションズ株式会社 | 受信回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101996674A (zh) | 2011-03-30 |

| US8446196B2 (en) | 2013-05-21 |

| US20110043262A1 (en) | 2011-02-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2011044795A (ja) | 入力インターフェース回路 | |

| KR101013444B1 (ko) | 듀티 사이클 보정 장치 및 이를 포함하는 반도체 집적 회로 | |

| US7368966B2 (en) | Clock generator and clock duty cycle correction method | |

| KR100813554B1 (ko) | 데이터 출력 스트로브 신호 생성 회로 및 이를 포함하는반도체 메모리 장치 | |

| KR100305546B1 (ko) | 반도체장치,반도체시스템및디지탈지연회로 | |

| KR100962026B1 (ko) | 듀티 사이클 보정 장치 및 이를 포함하는 반도체 집적 회로 | |

| US20170309320A1 (en) | Methods and apparatuses including command delay adjustment circuit | |

| KR100956771B1 (ko) | 디엘엘 클럭 생성 회로 | |

| JP2007097182A (ja) | 遅延固定ループ | |

| US7768327B2 (en) | Delay locked loop of semiconductor device and method for driving the same | |

| JP4434858B2 (ja) | デューティ補正電圧発生回路及びデューティ補正電圧発生方法 | |

| US7408394B2 (en) | Measure control delay and method having latching circuit integral with delay circuit | |

| US9209961B1 (en) | Method and apparatus for delay compensation in data transmission | |

| US8264267B2 (en) | Clock pulse generating circuit | |

| KR20080108859A (ko) | 내부 클럭 드라이버 회로 | |

| JP2006333472A (ja) | 遅延ロックループ、および、遅延鎖の設定方法 | |

| KR100632615B1 (ko) | 동기식 메모리 장치의 테스트를 위한 데이터 스트로브신호 생성 회로 | |

| KR100886645B1 (ko) | 클럭 버퍼 회로 및 그를 포함하는 반도체 메모리 장치 | |

| US8164963B2 (en) | Semiconductor memory device | |

| JP2004070800A (ja) | メモリシステム及びメモリモジュール | |

| KR100834397B1 (ko) | 내부클럭을 테스트할 수 있는 반도체 메모리 장치 | |

| KR20070031599A (ko) | Dll의 클럭 버퍼 회로 | |

| KR100600049B1 (ko) | 반도체메모리소자 | |

| KR100513807B1 (ko) | 지연고정루프 회로 | |

| KR20090041006A (ko) | 지연고정루프 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120217 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120217 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130523 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20131008 |