JP4063450B2 - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP4063450B2 JP4063450B2 JP16632099A JP16632099A JP4063450B2 JP 4063450 B2 JP4063450 B2 JP 4063450B2 JP 16632099 A JP16632099 A JP 16632099A JP 16632099 A JP16632099 A JP 16632099A JP 4063450 B2 JP4063450 B2 JP 4063450B2

- Authority

- JP

- Japan

- Prior art keywords

- conductor layer

- integrated circuit

- bit line

- semiconductor integrated

- circuit device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 99

- 239000004020 conductor Substances 0.000 claims description 69

- 239000003990 capacitor Substances 0.000 claims description 40

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 13

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 11

- 239000000758 substrate Substances 0.000 claims description 10

- 244000062793 Sorghum vulgare Species 0.000 claims 1

- 235000019713 millet Nutrition 0.000 claims 1

- 238000004519 manufacturing process Methods 0.000 description 34

- 239000010410 layer Substances 0.000 description 30

- 238000000034 method Methods 0.000 description 29

- 238000010586 diagram Methods 0.000 description 14

- 230000002093 peripheral effect Effects 0.000 description 14

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 13

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 12

- 230000015572 biosynthetic process Effects 0.000 description 11

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 238000002955 isolation Methods 0.000 description 3

- -1 phosphorus ions Chemical class 0.000 description 3

- 230000004913 activation Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 230000002040 relaxant effect Effects 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000002360 explosive Substances 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

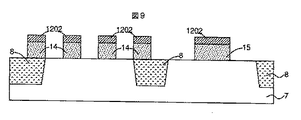

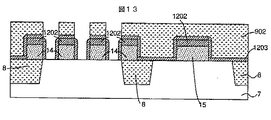

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/09—Manufacture or treatment with simultaneous manufacture of the peripheral circuit region and memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

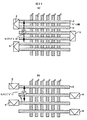

- H10B12/48—Data lines or contacts therefor

- H10B12/482—Bit lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/50—Peripheral circuit region structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/10—Integrated device layouts

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/906—Dram with capacitor electrodes used for accessing, e.g. bit line is capacitor plate

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/907—Folded bit line dram configuration

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/908—Dram configuration with transistors and capacitors of pairs of cells along a straight line between adjacent bit lines

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP16632099A JP4063450B2 (ja) | 1999-06-14 | 1999-06-14 | 半導体集積回路装置 |

| TW089110509A TW473987B (en) | 1999-06-14 | 2000-05-30 | Semiconductor integrated circuit device and manufacture thereof |

| US09/592,648 US6621110B1 (en) | 1999-06-14 | 2000-06-13 | Semiconductor intergrated circuit device and a method of manufacture thereof |

| KR1020000032336A KR100650468B1 (ko) | 1999-06-14 | 2000-06-13 | 반도체 집적 회로 장치 및 그 제조 방법 |

| US10/630,695 US6809364B2 (en) | 1999-06-14 | 2003-07-31 | Semiconductor integrated circuit device and a method of manufacture thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP16632099A JP4063450B2 (ja) | 1999-06-14 | 1999-06-14 | 半導体集積回路装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000353793A JP2000353793A (ja) | 2000-12-19 |

| JP2000353793A5 JP2000353793A5 (enExample) | 2004-09-30 |

| JP4063450B2 true JP4063450B2 (ja) | 2008-03-19 |

Family

ID=15829179

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP16632099A Expired - Fee Related JP4063450B2 (ja) | 1999-06-14 | 1999-06-14 | 半導体集積回路装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6621110B1 (enExample) |

| JP (1) | JP4063450B2 (enExample) |

| KR (1) | KR100650468B1 (enExample) |

| TW (1) | TW473987B (enExample) |

Families Citing this family (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2839581B1 (fr) * | 2002-05-07 | 2005-07-01 | St Microelectronics Sa | Circuit electronique comprenant un condensateur et au moins un composant semiconducteur, et procede de conception d'un tel circuit |

| KR100480601B1 (ko) * | 2002-06-21 | 2005-04-06 | 삼성전자주식회사 | 반도체 메모리 소자 및 그 제조방법 |

| KR100492899B1 (ko) * | 2002-11-18 | 2005-06-02 | 주식회사 하이닉스반도체 | 반도체소자 및 그 제조 방법 |

| DE10259634B4 (de) * | 2002-12-18 | 2008-02-21 | Qimonda Ag | Verfahren zur Herstellung von Kontakten auf einem Wafer |

| KR100502669B1 (ko) * | 2003-01-28 | 2005-07-21 | 주식회사 하이닉스반도체 | 반도체 메모리소자 및 그 제조 방법 |

| JP2004311706A (ja) * | 2003-04-07 | 2004-11-04 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP4342854B2 (ja) * | 2003-07-09 | 2009-10-14 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP4627977B2 (ja) | 2003-10-14 | 2011-02-09 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US7375033B2 (en) | 2003-11-14 | 2008-05-20 | Micron Technology, Inc. | Multi-layer interconnect with isolation layer |

| KR100630683B1 (ko) * | 2004-06-02 | 2006-10-02 | 삼성전자주식회사 | 6f2 레이아웃을 갖는 디램 소자 |

| KR100706233B1 (ko) * | 2004-10-08 | 2007-04-11 | 삼성전자주식회사 | 반도체 기억 소자 및 그 제조방법 |

| KR100604911B1 (ko) | 2004-10-20 | 2006-07-28 | 삼성전자주식회사 | 하부전극 콘택을 갖는 반도체 메모리 소자 및 그 제조방법 |

| KR100593746B1 (ko) * | 2004-12-24 | 2006-06-28 | 삼성전자주식회사 | 디램의 커패시터들 및 그 형성방법들 |

| KR100752644B1 (ko) | 2005-04-12 | 2007-08-29 | 삼성전자주식회사 | 반도체 소자의 셀영역 레이아웃 및 이를 이용한 콘택패드제조방법 |

| KR100693879B1 (ko) * | 2005-06-16 | 2007-03-12 | 삼성전자주식회사 | 비대칭 비트 라인들을 갖는 반도체 장치 및 이를 제조하는방법 |

| KR100654353B1 (ko) * | 2005-06-28 | 2006-12-08 | 삼성전자주식회사 | 커패시터를 구비하는 반도체 집적 회로 장치 및 이의 제조방법 |

| US7557032B2 (en) | 2005-09-01 | 2009-07-07 | Micron Technology, Inc. | Silicided recessed silicon |

| US7687342B2 (en) * | 2005-09-01 | 2010-03-30 | Micron Technology, Inc. | Method of manufacturing a memory device |

| US8716772B2 (en) * | 2005-12-28 | 2014-05-06 | Micron Technology, Inc. | DRAM cell design with folded digitline sense amplifier |

| KR100876881B1 (ko) * | 2006-02-24 | 2008-12-31 | 주식회사 하이닉스반도체 | 반도체 소자의 패드부 |

| US7349232B2 (en) * | 2006-03-15 | 2008-03-25 | Micron Technology, Inc. | 6F2 DRAM cell design with 3F-pitch folded digitline sense amplifier |

| JP2007294618A (ja) * | 2006-04-24 | 2007-11-08 | Elpida Memory Inc | 半導体装置の製造方法及び半導体装置 |

| US20080035956A1 (en) * | 2006-08-14 | 2008-02-14 | Micron Technology, Inc. | Memory device with non-orthogonal word and bit lines |

| US7521763B2 (en) * | 2007-01-03 | 2009-04-21 | International Business Machines Corporation | Dual stress STI |

| KR100898394B1 (ko) * | 2007-04-27 | 2009-05-21 | 삼성전자주식회사 | 반도체 집적 회로 장치 및 그 제조 방법 |

| US7923373B2 (en) | 2007-06-04 | 2011-04-12 | Micron Technology, Inc. | Pitch multiplication using self-assembling materials |

| US8294188B2 (en) * | 2008-10-16 | 2012-10-23 | Qimonda Ag | 4 F2 memory cell array |

| JP2010219139A (ja) * | 2009-03-13 | 2010-09-30 | Elpida Memory Inc | 半導体装置及びその製造方法 |

| JP2010219326A (ja) * | 2009-03-17 | 2010-09-30 | Elpida Memory Inc | 半導体記憶装置及びその製造方法 |

| KR101076888B1 (ko) * | 2009-06-29 | 2011-10-25 | 주식회사 하이닉스반도체 | 반도체 소자의 연결 배선체 및 형성 방법 |

| JP2011023652A (ja) * | 2009-07-17 | 2011-02-03 | Elpida Memory Inc | 半導体記憶装置 |

| US8558320B2 (en) * | 2009-12-15 | 2013-10-15 | Qualcomm Incorporated | Systems and methods employing a physically asymmetric semiconductor device having symmetrical electrical behavior |

| US8686486B2 (en) * | 2011-03-31 | 2014-04-01 | Semiconductor Energy Laboratory Co., Ltd. | Memory device |

| JP5831687B2 (ja) * | 2011-07-22 | 2015-12-09 | ソニー株式会社 | 記憶装置およびその製造方法 |

| CN105905231A (zh) * | 2016-05-19 | 2016-08-31 | 国家海洋局第海洋研究所 | 便携双体船 |

| CN109427787A (zh) | 2017-08-30 | 2019-03-05 | 联华电子股份有限公司 | 半导体存储装置 |

| CN113903740B (zh) * | 2020-07-06 | 2025-05-09 | 华邦电子股份有限公司 | 半导体存储器结构及其形成方法 |

| US11637107B2 (en) | 2021-06-17 | 2023-04-25 | Applied Materials, Inc. | Silicon-containing layer for bit line resistance reduction |

| US11716838B2 (en) * | 2021-08-11 | 2023-08-01 | Micron Technology, Inc. | Semiconductor device and method for forming the wiring structures avoiding short circuit thereof |

| CN115996560B (zh) * | 2021-10-15 | 2025-07-25 | 长鑫存储技术有限公司 | 一种存储器及其制造方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR950003402B1 (ko) * | 1992-09-08 | 1995-04-12 | 삼성전자 주식회사 | 폴디드 비트라인 방식의 디램쎌 어레이 |

| JP3368002B2 (ja) | 1993-08-31 | 2003-01-20 | 三菱電機株式会社 | 半導体記憶装置 |

| TW377495B (en) * | 1996-10-04 | 1999-12-21 | Hitachi Ltd | Method of manufacturing semiconductor memory cells and the same apparatus |

| TW442923B (en) * | 1998-03-20 | 2001-06-23 | Nanya Technology Corp | Manufacturing method of DRAM comprising redundancy circuit region |

| JP3137185B2 (ja) * | 1998-04-09 | 2001-02-19 | 日本電気株式会社 | 半導体記憶装置 |

| KR20010003628A (ko) * | 1999-06-24 | 2001-01-15 | 김영환 | 반도체 메모리셀 구조 및 제조방법 |

-

1999

- 1999-06-14 JP JP16632099A patent/JP4063450B2/ja not_active Expired - Fee Related

-

2000

- 2000-05-30 TW TW089110509A patent/TW473987B/zh not_active IP Right Cessation

- 2000-06-13 KR KR1020000032336A patent/KR100650468B1/ko not_active Expired - Lifetime

- 2000-06-13 US US09/592,648 patent/US6621110B1/en not_active Expired - Lifetime

-

2003

- 2003-07-31 US US10/630,695 patent/US6809364B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| TW473987B (en) | 2002-01-21 |

| KR20010020983A (ko) | 2001-03-15 |

| US6621110B1 (en) | 2003-09-16 |

| KR100650468B1 (ko) | 2006-11-28 |

| JP2000353793A (ja) | 2000-12-19 |

| US20040021159A1 (en) | 2004-02-05 |

| US6809364B2 (en) | 2004-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4063450B2 (ja) | 半導体集積回路装置 | |

| US6130449A (en) | Semiconductor memory device and a method for fabricating the same | |

| KR100579365B1 (ko) | 메모리 어레이 및 지지 트랜지스터의 형성 방법, 및 이중일함수 지지 트랜지스터 및 매립형 dram 어레이를포함하는 반도체 장치 | |

| JP3532325B2 (ja) | 半導体記憶装置 | |

| US9385130B2 (en) | Semiconductor device and method for manufacturing the same | |

| US6555450B2 (en) | Contact forming method for semiconductor device | |

| JP3398649B2 (ja) | 異なる導電タイプのドーパントをゲート導体にドーピングする方法 | |

| US20130062679A1 (en) | Device | |

| US6146994A (en) | Method for forming self-aligned selective silicide layer using chemical mechanical polishing in merged DRAM logic | |

| US20040046195A1 (en) | Semiconductor integrated circuit device and process for manufacturing the same | |

| KR100273987B1 (ko) | 디램 장치 및 제조 방법 | |

| US6281051B1 (en) | Semiconductor device and manufacturing method thereof | |

| US6238961B1 (en) | Semiconductor integrated circuit device and process for manufacturing the same | |

| US8779487B2 (en) | Semiconductor devices including storage node landing pads separated from bit line contact plugs | |

| JPH10163452A (ja) | 半導体記憶装置及びその製造方法 | |

| JP2002261256A (ja) | 半導体装置およびその製造方法 | |

| JP4181284B2 (ja) | 半導体装置の製造方法 | |

| US7015552B2 (en) | Dual work function semiconductor structure with borderless contact and method of fabricating the same | |

| JP3202501B2 (ja) | 半導体記憶装置及びその製造方法 | |

| JP2635429B2 (ja) | 半導体構造体及び半導体記憶装置並びにそれらの製造方法 | |

| KR100349345B1 (ko) | 반도체 장치의 비트라인 및 그 제조방법 | |

| CN120417373A (zh) | 半导体器件 | |

| JPH11330238A (ja) | 半導体装置の製造方法 | |

| KR20010064819A (ko) | 반도체장치의 콘택 형성방법 | |

| JP2005136436A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060322 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20060417 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060522 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20070605 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071010 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071107 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071225 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110111 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110111 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120111 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120111 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130111 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130111 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140111 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |