JP4063450B2 - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP4063450B2 JP4063450B2 JP16632099A JP16632099A JP4063450B2 JP 4063450 B2 JP4063450 B2 JP 4063450B2 JP 16632099 A JP16632099 A JP 16632099A JP 16632099 A JP16632099 A JP 16632099A JP 4063450 B2 JP4063450 B2 JP 4063450B2

- Authority

- JP

- Japan

- Prior art keywords

- conductor layer

- integrated circuit

- bit line

- semiconductor integrated

- circuit device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 99

- 239000004020 conductor Substances 0.000 claims description 69

- 239000003990 capacitor Substances 0.000 claims description 40

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 13

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 11

- 239000000758 substrate Substances 0.000 claims description 10

- 244000062793 Sorghum vulgare Species 0.000 claims 1

- 235000019713 millet Nutrition 0.000 claims 1

- 238000004519 manufacturing process Methods 0.000 description 34

- 239000010410 layer Substances 0.000 description 30

- 238000000034 method Methods 0.000 description 29

- 238000010586 diagram Methods 0.000 description 14

- 230000002093 peripheral effect Effects 0.000 description 14

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 13

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 12

- 230000015572 biosynthetic process Effects 0.000 description 11

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 238000002955 isolation Methods 0.000 description 3

- -1 phosphorus ions Chemical class 0.000 description 3

- 230000004913 activation Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 230000002040 relaxant effect Effects 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000002360 explosive Substances 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/09—Manufacture or treatment with simultaneous manufacture of the peripheral circuit region and memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/482—Bit lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/50—Peripheral circuit region structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/906—Dram with capacitor electrodes used for accessing, e.g. bit line is capacitor plate

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/907—Folded bit line dram configuration

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/908—Dram configuration with transistors and capacitors of pairs of cells along a straight line between adjacent bit lines

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

本発明は、微細であってかつ蓄積容量が大きな半導体記憶装置に関する。特に、高集積化に好適なダイナミックランダムアクセスメモリ(DRAM)に関する。

【0002】

【従来の技術】

これまで、3年に4倍のペースで集積化の向上を実現してきたダイナミックランダムアクセスメモリ(DRAM:Dynamic Random Access Memory)は、近年のパーソナルコンピュータの爆発的な売上に牽引されて、その需要はますます高まりつつある。

【0003】

DRAMのメモリセルの配列には、折り返しビット線配置と開放型ビット線配置、の2つがある。図1には代表的な折り返しビット線配置構造を有するDRAMのメモリセルレイアウトを示している。メモリセル面積を最小にする為に、ワード線及びビット線は最小寸法をFとして、線幅=F、ピッチ=2Fでレイアウトされている。横長のアクティブ領域に2つのメモリセルが形成され、縦長のビット線コンタクトがそれら2つのセルに共用されている。一方、図2には'1993 Symposium on VLSI circuits P.91'に記された、代表的な開放型ビット線配置の場合のメモリセルレイアウトを示す。この場合、ワード線は線幅=F、ピッチ=2Fとなるが、ビット線は線幅=F、ピッチ=3Fとなる。さて、これら2つのビット線配置構造に対して、データ読出し工程を考える。1本のワード線がオンした場合を考えると、折り返しビット線構造の場合、ビット線からは一本おきにデータが出てくる。即ち、図3(a)に示したように、1つのセンスアンプに繋がるペアのビット線が、同一マットの中の隣り合う2つのビット線となる。こうしたことから、折り返しビット線構造と呼ばれる。一方、開放型ビット線配置の場合は、全てのビット線からデータが出てくるので、ペアとなるビット線は図3(b)に示したように、別マットに開放的に存在することになる。即ち、ペアビット線とカップルする駆動ワードが、折り返しビット線配置では共通であるのに対し、開放型では共通ではない。これは、雑音という観点で言い換えるならば、ワード線駆動雑音が、折り返しビット線配置ではペアビット線間でキャンセルするのに対し、開放型ではキャンセルしない、ということであり、折り返しビット線構造がノイズに強いということを意味する。このように、開放型ビット線配置はノイズに対して弱いが、その最大の特長は、その小さいセル面積にある。折り返しビット線配置においては、図1に示したように8F2であるのに対し、開放型では図2のように6F2である。

【0004】

量産ということを考えると、製品コストを下げる為には、チップ面積の縮小、即ちメモリセル面積の縮小が極めて効果的である。この観点からすると、開放型ビット線配置の方が、折り返し線配置よりも望ましい。課題は耐ノイズ性能をいかにして向上するかである。

【0005】

実際の製品では、16Kの世代までは開放型ビット線配置が用いられていたが、以降はノイズに対して強い、折り返しビット線配置が用いられており、現在に至っている。

【0006】

開放型ビット線配置を有するDRAMに関して、図2に類似した構造の提案は、特開平07−066299にもある。この場合、原理的なセルレイアウトは図2に示したものに極めて類似しているが、ビット線ピッチが4Fに緩和されており、その結果として、隣接キャパシタ下部電極コンタクトの間隔を広げ、セル間リーク電流を低減させている。

【0007】

【発明が解決しようとする課題】

上述した従来技術には次に示すような課題がある。

【0008】

まず、上述の'1993 Symposium on VLSI circuits'に記された実施例においては、次のような問題点がある。図2から明らかなように、キャパシタ下部電極コンタクト(5)がビット線(3)に近接したレイアウトになっており、ビット線(3)と接することなく、キャパシタ下部電極コンタクト(5)を開口する為には、所謂自己整合コンタクト技術が必須である。自己整合コンタクト技術とは以下のようなものである。図2のAA方向の断面に着目してビット線形成以降のプロセスを説明する。図4に示すように、ビット線コンタクトプラグ(10)形成後、ビット線となるタングステン及びシリコンナイトライドの積層膜を堆積する。次にリソグラフィ、ドライエッチ工程を経てビット線(11)を形成して、図5のようになる。更に、シリコンナイトライド(1201)を堆積し、図6のようになる。続いて、シリコン酸化膜からなる層間膜(901)を堆積平坦化した後に、シリコンナイトライドに対して高選択性を有する酸化膜エッチングにより、キャパシタ下部電極コンタクトを開口する。更に、プラグ(13)を形成して、図7のようになる。このように、自己整合コンタクト開口技術を用いることによって、ビット線(11)に短絡することなく、下部電極コンタクトを開口できる。本技術により、余裕が十分に無いときにも、面積を増大することなく、コンタクト開口が可能である。しかし、自己整合コンタクト開口技術には次のような問題点がある。シリコンナイトライドの誘電率はシリコン酸化膜の約2倍である。自己整合コンタクト技術では、図7に示したように、ビット線(11)をシリコンナイトライド(12,1201)で囲む構造となり、しかも下部電極プラグとビット線の間がシリコンナイトライドで絶縁されることになるので、ビット線容量が増大することを意味する。すでに述べたように、開放型ビット線配置は折り返し配置よりもノイズに対して弱いので、こうした構造ではビット線容量を低減することが極めて重要である。この点で、開放型ビット線配置を有するDRAMにおいて、自己整合コンタクト形成プロセスを用いることは、適切ではない。

【0009】

また、特開平07−066299では、図2に類似したレイアウトで、ビット線ピッチを広げることにより、キャパシタ下部電極コンタクトの間隔を広げている。しかし、これでは、セル面積が増大してしまい、開放型ビット線配置の最大の特長を活かしていない。

【0010】

本発明は、上記課題を同時に解決するものである。即ち、ビット線容量が小さい結果ノイズ耐性に優れ、しかもセル面積の小さい、開放型ビット線配置を有するDRAMのレイアウト並びに製造方法を提案するものである。

【0011】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0012】

すなわち、請求項1に記載の発明は、第1方向に延びる複数のワード線と、前記第1方向に交差する第2方向に延びる複数のビット線と、それぞれの前記ワード線とビット線の交点に配置された1つのトランジスタと1つの容量素子とを有する複数のメモリセルと、複数のビット線のうち交差するワード線が異なる2本のビット線が夫々接続される複数のセンスアンプとを備え、前記ビット線上に前記容量素子を配置した半導体集積回路装置であって、半導体基板上において、前記複数のワード線中の隣接する第1、第2ワード線及び前記複数のビット線中の第1ビット線と交差し、前記第1及び第2方向と異なる第3方向に延び、前記第3方向に対して直交する第4方向に所定の幅を有する活性領域と、前記活性領域内に形成され、前記トランジスタのソース、ドレインとして機能する第1及び第2半導体領域と、前記容量素子を構成する第1及び第2電極と、前記第1及び第2電極間に位置する誘電体膜と、前記ビット線と前記第1電極との間に位置する第1絶縁膜と、前記第1絶縁膜に形成された第1開孔内に形成され、前記第1及び第2半導体領域の一方と、前記第1電極とを電気的に接続するための第1導体層と、前記ビット線と前記第1及び第2半導体領域の他方を前記ビット線と前記活性領域の交点において接続する第3導体層とからなり、前記第1導体層は前記ワード線とビット線によって囲まれた領域の各々に配置され、前記第1導体層の中心は、前記第3方向に沿う前記活性領域の中心線から対応する前記第3導体層が接続されるビット線から離れる方向にずれている半導体集積回路装置構造とするものである。

【0013】

また、請求項8に記載の発明は、交差するワード線が異なる2本のビット線が夫々接続される複数のセンスアンプを備える半導体集積回路装置であって、各々が第1方向に延び、互いに隣接する第1、第2ワード線と、前記第1ワード線に隣接し前記第2ワード線と反対側に配置された第3ワード線と、前記第2ワード線に隣接し前記第1ワード線と反対側に配置された第4ワード線と、前記第1方向に交差する第2方向に延び、連続的に隣接する第1、第2及び第3ビット線と、前記第1及び第2方向と交差する第3方向に延びる活性領域と、前記活性領域内であって、前記第1、第2ワード線間に位置する第1半導体領域と、前記活性領域内であって、前記第1、第3ワード線間及び第2、第4ワード線間に位置する第2半導体領域と、第1、第2及び第3ビット線上に第1絶縁膜を介して形成された第1電極および第2電極と、前記第1及び第2電極間に位置する誘電体膜から構成される容量素子と、前記第2半導体領域と前記第1電極とを電気的に接続する前記第1絶縁膜内に形成された複数の第1導体層とを有し、前記第1導体層は、前記ワード線と前記ビット線で囲まれた領域の各々に配置され、前記第1、第3ワード線間に配置された第1導体層の中心と、前記第2、第4ワード線間に配置された第1導体層の中心とを結ぶ直線が前記第1方向に対してなす角度は、前記第3方向が前記第1方向に対してなす角度よりも小である半導体集積回路装置構造とするものである。

【0014】

また、請求項9に記載の発明は、第1方向に延びる複数のワード線と、前記第1方向に交差する第2方向に延びる複数のビット線と、前記ワード線とビット線の交点に配置されたそれぞれが1つのトランジスタと1つの容量素子とを有する複数のメモリセルと、前記複数のビット線のうち交差する複数のワード線が異なる2本のビット線が夫々接続される複数のセンスアンプとを備え、前記ビット線上に前記容量素子を配置した半導体集積回路装置であって、半導体基板上において2つのワード線及び1つのビット線と交差し、前記第1及び第2方向と異なる第3方向に延びる活性領域と、前記活性領域内に形成され、前記トランジスタのソース、ドレインとして機能する第1及び第2半導体領域と、前記容量素子を構成する第1及び第2電極と、前記第1及び第2電極間に位置する誘電体膜と、前記ビット線と前記第1電極との間に位置する第1絶縁膜と、前記第1絶縁膜に設けられた第1開孔内に形成され、前記第1及び第2半導体領域の一方と、前記第1電極とを電気的に接続するための第1導体層と、前記ビット線と前記第1及び第2半導体領域の他方を前記ビット線と前記活性領域の交点において接続する第3導体層とからなり、前記第1導体層は、前記ワード線とビット線で囲まれた領域の各々に配置され、前記第1導体層の前記第2方向における幅は、前記ワード線の幅よりも小である半導体集積回路装置構造とするものである。

【0015】

また、請求項14に記載の発明は、第1方向に延びる複数のワード線と、前記第1方向に交差する第2方向に延びる複数のビット線と、前記ワード線とビット線の交点に配置されたそれぞれが1つのトランジスタと1つの容量素子とを有する複数のメモリセルと、前記複数のビット線のうち交差するワード線が異なる2本のビット線が夫々接続される複数のセンスアンプとを備え、前記ビット線上に前記容量素子を配置した半導体集積回路装置であって、半導体基板上に形成された前記容量素子を構成する第1及び第2電極と、前記第1及び第2電極間に位置する誘電体膜と、前記ビット線と前記第1電極との間に位置する第1絶縁膜と、前記第1絶縁膜に形成された第1開孔内に形成され、前記トランジスタと、前記第1電極とを電気的に接続するための第1導体層とからなり、前記第1導体層は前記ワード線とビット線によって囲まれた領域の各々に配置され、前記第1導体層と前記第1及び第2半導体領域の一方との間に配置された第2導体層を有し、前記第1方向において、前記第2の導体層の幅は、前記第1導体層の幅よりも大であり、前記第1方向において隣接する第2導体層の中心間距離は、前記第2導体層の上に配置された前記第1導体層の中心間距離よりも小である半導体集積回路装置構造とするものである。

【0018】

上記半導体集積回路装置の構造により、ビット線容量が小さくできてノイズ耐性に優れた、しかもセル面積の小さい半導体集積回路装置を提供できるものであります。

【0019】

【発明の実施の形態】

(実施例1)

以下、本発明の実施例を、レイアウト図及びプロセスフロー断面図を用いて説明する。

【0020】

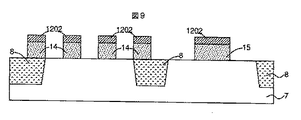

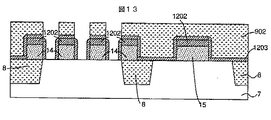

まず始めに、半導体基板(7)を用意して、図8に示すような浅溝素子分離領域(8)を形成する。続いて、ウエル及びパンチスルーストッパ領域を形成する為に、不純物イオンを打ち込む。ゲート酸化膜を形成した後に、50nmのノンドープのポリシリコンを公知のCVD(Chemical Vapor Deposition)法を用いて堆積する。2極性ゲート形成の為に、Nゲート領域にはリンイオンをエネルギー5keV、ドーズ量2e15cm−2の条件で打ち込み、Pゲート領域にはボロンイオンをエネルギー2keV、ドーズ量2e15cm−2の条件で打ち込む。勿論、リンの代わりにヒソを、ボロンの代わりにBF2を用いても構わない。続いて、ワード線抵抗を低減する為にTiNを10nm、Wを80nmスパッタする。TiNはポリシリコンとWの間のシリサイド化反応を抑える為であり、WNを代わりに用いることもできる。さらに、自己整合コンタクト用として、CVD法を用いてSiNを100nm堆積する。つづいて、公知のドライエッチ法を用いて、SiN/W/TiN/poly−Siを加工し、ゲート電極(14)を形成して図9のようになった。ワード線(2)レイアウトは図10に示すようになる。次に、周辺MOSFETの拡散層形成の為に、レジストマスクを用いて、N型MOSFETにはヒソイオンをエネルギー20keV、ドーズ量1e14cm−2の条件で、P型のMOSFETにはBF2イオンをエネルギー20keV、ドーズ量1e14cm−2の条件で、打ち込む。さらにCVD法を用いてSiN(1203)を30nm堆積し、図11のようになる。続いて、ゲート側壁膜を形成するために、周辺回路領域のSiNをエッチバックし、レジストをマスクに拡散層抵抗低減を目的にイオン打ち込みを行う。先ず、P型拡散層領域をレジストで開口し、BF2イオンをエネルギー20keV、ドーズ量2e15cm−2の条件で打ち込む。続いて、レジストを除去した後、N型拡散層領域をレジストで開口し、ヒソイオンをエネルギー15keV、ドーズ量2e15cm−2で打ち込む。

【0021】

次に、350nmの酸化膜をCVD法を用いて堆積し平坦化を行い、レジストをマスクにメモリアレー内において、ビット線やキャパシタ電極用の直径約0.2ミクロンのプラグ穴を開口し、下地SiNを露出させる。ゲート電極はSiNで完全に覆われているので、酸化膜加工の際にゲート電極が露出することはなかった。この時の、プラグのレイアウトパタン(16)を図12に示す。続いて、30nmのSiNドライエッチを行い、基板に形成された拡散層表面を露出させて図13のようになる。続いて、メモリセルトランジスタの電界緩和を目的として、リンをエネルギー25keV、ドーズ量6e12cm−2の条件で打ち込む。次に、メモリセルプラグとなるポリシリコンを500nm堆積する。勿論、このポリシリコンにはリンを4e20cm−3の濃度でドープされている。次にポリシリコンの平坦化を行い、図14のようにメモリセル下部電極プラグ(16)が形成された。

【0022】

続いて、CVDによりシリコン酸化膜(903)を50nm堆積した後に、図15のように直径0.18ミクロンのメモリセルアレー部のビット線コンタクトと、周辺回路のコンタクトを開口する。この時の、ビット線コンタクトのレイアウトパタン(17)を図16に示す。次に、TiNプラグの形成を行う。CVDにより100nmのTiN(18)を堆積し、さらにTiNエッチバック工程を行い、TiNプラグ(18,19)を形成し図17を得る。本実施例ではTiNプラグを用いたが、プラグ材料としてW/TiN積層膜を用いても構わない。

【0023】

次にビット線に用いるWを50nmスパッタする。続いて、レジストをマスクにWをドライエッチし、メモリセルアレー部ではビット線(20)、周辺回路部ではインターコネクト配線(21)が図18のように形成される。尚、図19にはメモリセルアレーにおけるビット線(20)レイアウトを示している。ビット線ピッチは、ワード線ピッチを2Fとして、3Fである。

【0024】

この時、後のキャパシタ下部電極コンタクト開口の際に、ビット線との短絡を防ぐ為に、ビット線をレジストアッシングにより約50nm細線化し、80nmとした。更に、層間絶縁膜として酸化膜(904)を200nm堆積し、エッチバック工程により平坦化した。次に、キャパシタ下部電極コンタクトを形成する。自己整合プロセスを用いることなく、コンタクトを開口する目的で、キャパシタ下部電極コンタクト(22)は図20に示したように、下部電極プラグに対してビット線から離れる方向にオフセットし、しかも、その直径を下地プラグよりも小さくしている。メモリセルコンタクトのレイアウトの特徴を言い換えると次のようになる。まず、ワード線方向に関しては、隣接上部キャパシタ電極プラグ(22)の中心距離が、隣接下部キャパシタ電極プラグ(16)の中心距離よりも大きい。またビット線方向に関しては、隣接上部キャパシタ電極プラグ(22)の中心距離が、隣接下部キャパシタ電極プラグ(16)の中心距離よりも小さくなっている。この結果、自己整合コンタクト形成技術を用いること無く、ビット線との短絡を防止することが可能になる。また、下部キャパシタ電極プラグ(16)が大きく開口されている結果、たとえ上部キャパシタ下部電極プラグ(22)がオフセットされていても、必要十分なプラグの重なりが確保されている。続いて、リンを高濃度に含む多結晶シリコンを300nm堆積し、エッチバック工程により平坦化し、プラグ(22)を形成して、図20中のBB方向の断面図は図21のようになった。

【0025】

続いて、公知の製造方法を用いて、メモリキャパシタ(23)及び配線2(26)の形成を行い、図22に示す所望の半導体記憶装置を得た。勿論、必要に応じて配線層を増やすことは可能である。

【0026】

以上述べたように本実施例によれば、キャパシタ下部電極プラグを下地プラグからオフセットさせ、しかもその径を下地プラグよりも小さくすることによって、セル面積を増大させることなく、自己整合プロセスを用いずに開放型ビット線配置のDRAMを形成できた。また、本実施例には以下のような特長もある。即ち、開放型ビット線配置を有するDRAMにおいては、寄生抵抗及び容量の低減が、ノイズの観点からは極めて重要である。本実施例では、ワードにポリシリコンとタングステンの積層膜、ビット線にタングステンを用いることによって、ワード線とビット線の低抵抗化を達成し、その結果ノイズに対して強い構造となっている。

【0027】

(実施例2)

本実施例の目的は、実施例1と同様に、ノイズに対して強く、セル面積の小さい開放型ビット線配置を有するDRAMの製造方法を提案するものである。実施例1との違いは製造工程の簡略化、即ちマスク枚数の削減にある。具体的には、実施例1においては、キャパシタ下部電極プラグが積層プラグ構造になっていたが、本実施例では、単一プラグ構造としている。その製造工程を以下、図面を用いて説明する。

【0028】

図11に示したワード線形成までは実施例1と同様である。続いて、層間絶縁膜(902)を堆積し、ビット線コンタクト及び、周辺回路コンタクトを開口する。次に、プラグ電極(18,19)を形成し、タングステンから成るビット線(20)及びローカルインタコネクト配線(21)を形成して、図23のようになった。この時、実施例1と同様にビット線は細線化され、その幅は約80nmであった。さらに、層間絶縁膜として、シリコン酸化膜(904)を堆積平坦化し、キャパシタ電極プラグコンタクト(22)を開口する。この時の、平面レイアウトを図24に示す。この特長は、キャパシタプラグコンタクトが下地の素子形成領域に対して、ビット線との短絡余裕を増大させる方向にオフセットされている点である。尚、キャパシタプラグコンタクトの直径は約100nmである。この結果、ビット線間隔を広げることなく、ビット線との短絡を回避して、図25に示すようにキャパシタ下部電極プラグコンタクトを開口し、プラグ電極(22)を形成できた。この実施例には、プラグと素子形成領域の重なりが減少する結果、コンタクト抵抗が増大するという懸念がある。しかし、実際にはメモリセルの特性を劣化させる程のコンタクト抵抗の増大は観測されなかった。以降のキャパシタ形成及び配線工程は実施例1と同様である。こうして、所望の半導体記憶装置を得た。

【0029】

以上述べたように、本実施例においては、キャパシタ下部電極と基板活性化領域をつなぐプラグを単一構造とし、プラグのレイアウトをワード線が走る方向に、ビット線との距離を増大させる向きにオフセットさせ、かつその直径を100nmにすることによって、セル面積を増大することなく、しかも自己整合プロセスを用いない結果ビット線容量の小さい開放型ビット線配置のDRAMを形成できた。

【0030】

(実施例3)

本実施例は、開放型ビット線配置を有するDRAMにおいて、特に、実施例1のプロセスフローに関して、メモリセル周りの合わせ余裕を増大させるものである。

【0031】

実施例1においては、次のような順序でメモリセルプラグを形成している。即ち、まず、ビット線及びキャパシタの下部プラグ(16)を形成(図26)、ビット線上部プラグ(18)を形成(図27)、ビット線(20)を形成し、キャパシタ電極の上部プラグ(22)を形成(図28)、の順となっている。これに対して、本実施例では次のようなフローで形成した。まず、図29に示したように、多結晶Siからなるキャパシタ下部電極プラグ(16)を形成する。次に、図30に示したように、層間膜を堆積した後に、ビット線コンタクトを開口し、多結晶Siからなるビット線プラグを形成する。続いて、ビット線プラグをエッチバックすることによりくぼませ、その中に、W/TiNプラグ(18)を形成し図31のようになる。この時、同時に、周辺回路コンタクトプラグ(19)も形成する。続いて、Wからなるビット線(20)を形成し、さらにキャパシタ下部プラグ(22)を形成し、図32を得る。本実施例においては、プラグと拡散層の接触部にはすべて多結晶Siを用いたが、工程簡略化の観点から、W/TiN等のメタル材料を用いることも勿論可能である。

【0032】

本実施例においては、ビット線上部コンタクトプラグ(18)を実効的に、ビット線下部コンタクトプラグ(16)に対して自己整合的に形成することになる。この結果、実施例1よりもメモリセルのプラグ形成プロセスにおいて、合わせマージンを大きく確保することに成功した。

【0033】

(実施例4)

本実施例は、開放型ビット線配置を有するDRAMにおいて、周辺回路の高性能化を実現する手法に関するものである。実施例1に示したように、フィーチャーサイズ0.13umを有するDRAMにおいては、メモリセルプラグの拡散層とのコンタクト面積確保の観点から、メモリセルにおいては側壁膜は30nm程度に制限される。工程簡略化の観点からは、これを周辺回路の側壁膜として使用するのが望ましい。しかし、トランジスタの高性能化と信頼性両立の為には、側壁膜は100nm程度必要である。そこで、本実施例においては、メモリセルトランジスタと周辺回路トランジスタの側壁膜の膜厚を異なるものとした。具体的には、図33に示したように、メモリセルにおいては、側壁膜として30nmのシリコンナイトライド(1203)を、周辺回路においては、シリコンナイトライド30nm(1203)とシリコン酸化膜40nm(27)の積層膜とした。

【0034】

こうして、本実施例においては、周辺回路トランジスタの側壁膜をメモリセルトランジスタのそれよりも厚く形成することにより、高性能化と信頼性の両立を可能にした。

【0035】

(実施例5)

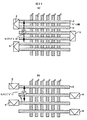

本実施例は開放型ビット線配置を有するDRAMのセンスアンプレイアウトに関するものである。従来の折り返しビット線配置を有するDRAMにおいては、センスアンプは図34(a)に示したように、ビット線ピッチを2Fとして、8F内に収めればよい。この場合の典型的なセンスアンプのレイアウトを図35(a)に示す。しかし、開放型ビット線配置を有するDRAMにおいては、セル面積を増大させない為には、図34(b)に示したように、6Fの範囲に入れる必要がある。即ち、センスアンプの短辺方向の長さを短縮する必要がある。そこで、センスアンプを形成するトランジスタに関しては、ゲート電極とコンタクトの間隔を縮小できる、自己整合コンタクトプロセスを適用した。この時のレイアウトを図35(b)に示す。この結果、所望のピッチの中にセンスアンプを配置することができた。従来は、センスアンプにおいて技術的に難度の高い自己整合コンタクト技術を用いることはなかった。

【0036】

このように、本実施例においては、開放型ビット線配置を有するDRAMのセンスアンプにおいて、ゲートに対する自己整合コンタクト開口プロセスを適用することによって、6Fのピッチの中でのレイアウトを可能にした。この結果、ビット線ピッチを緩和することなく、所望の半導体記憶装置を実現できた。

【0037】

(実施例6)

本実施例は開放型ビット線配置を有するDRAMのメモリセルレイアウトに関するものである。実施例1や2におけるレイアウトでは、ワード線とビット線が互いに直交し、それらに対して素子形成領域が斜めに交差していた。本実施例では、ワード線と素子形成領域が互いに直交し、ビット線がそれらに対して斜めに交差するレイアウトを提案する。

【0038】

図36に本実施例におけるメモリセルの1レイアウト図を示す。セル面積は実施例1と同様、にフィーチャーサイズをFとして、6F2である。実施例1と同様の製造工程を経て、所望の半導体記憶装置を得た。また、図37には、別のメモリセルレイアウトを示す。この場合、実施例2と同様の製造工程を経て、所望の半導体記憶装置を得た。図36と図37のレイアウトの違いは、キャパシタ下部電極に繋がるプラグが図36の場合は積層構造であるのに対し、図37の場合は単層構造である点である。いずれの場合も、キャパシタ下部電極プラグをビット線から離す方向にオフセットすることにより、セル面積を増大させることなく、ノイズに対して強い、開放型ビット線配置を有する、半導体記憶装置を実現できた。また本実施例には、素子形成領域の分離幅を実施例1や2よりも大きく確保でき、その結果として、メモリセル間のリークを低減できるという特長をも有する。

【0039】

【発明の効果】

本発明には、開放型ビット線配置を有するDRAMにおいて、ノイズに対する耐性を向上し、しかも同時にセル面積の縮小を可能にする、という効果がある。

【図面の簡単な説明】

【図1】従来の折り返しビット線配置構造を有するDRAMのメモリセルレイアウト。

【図2】従来の開放型ビット線配置を有するDRAMのメモリセルレイアウト。

【図3】 (a)折り返しビット線配置構造の原理図。 (b)開放型ビット線配置構造の原理図。

【図4】自己整合コンタクトプロセスの説明図。

【図5】自己整合コンタクトプロセスの説明図。

【図6】自己整合コンタクトプロセスの説明図。

【図7】自己整合コンタクトプロセスの説明図。

【図8】本発明の半導体記憶装置の1製造工程における断面図。

【図9】本発明の半導体記憶装置の1製造工程における断面図。

【図10】本発明の半導体記憶装置の1製造工程におけるレイアウト図。

【図11】本発明の半導体記憶装置の1製造工程における断面図。

【図12】本発明の半導体記憶装置の1製造工程におけるレイアウト図。

【図13】本発明の半導体記憶装置の1製造工程における断面図。

【図14】本発明の半導体記憶装置の1製造工程における断面図。

【図15】本発明の半導体記憶装置の1製造工程における断面図。

【図16】本発明の半導体記憶装置の1製造工程におけるレイアウト図。

【図17】本発明の半導体記憶装置の1製造工程における断面図。

【図18】本発明の半導体記憶装置の1製造工程における断面図。

【図19】本発明の半導体記憶装置の1製造工程におけるレイアウト図。

【図20】本発明の半導体記憶装置の1製造工程におけるレイアウト図。

【図21】本発明の半導体記憶装置の1製造工程における断面図。

【図22】本発明の半導体記憶装置の1製造工程における断面図。

【図23】本発明の半導体記憶装置の1製造工程における断面図。

【図24】本発明の半導体記憶装置の1製造工程におけるレイアウト図。

【図25】本発明の半導体記憶装置の1製造工程における断面図。

【図26】本発明の半導体記憶装置の1製造工程における断面図。

【図27】本発明の半導体記憶装置の1製造工程における断面図。

【図28】本発明の半導体記憶装置の1製造工程における断面図。

【図29】本発明の半導体記憶装置の1製造工程における断面図。

【図30】本発明の半導体記憶装置の1製造工程における断面図。

【図31】本発明の半導体記憶装置の1製造工程における断面図。

【図32】本発明の半導体記憶装置の1製造工程における断面図。

【図33】本発明の半導体記憶装置の1製造工程における断面図。

【図34】 (a)折り返しビット線構造におけるセンスアンプ配置。 (b)開放型ビット線構造におけるセンスアンプ配置。

【図35】 (a)従来のセンスアンプレイアウト。 (b)本発明の1実施例におけるセンスアンプレイアウト。

【図36】本発明の半導体記憶装置の1実施例におけるメモリレイアウト。

【図37】本発明の半導体記憶装置の1実施例におけるメモリレイアウト。

【符号の説明】

1…活性化領域、2…ワード線、3…ビット線、4…ビット線コンタクト、5…キャパシタ下部電極コンタクト1、6…センスアンプ、7…メモリセル、7…Si基板、8…素子分離領域、9,901,902,903,904,905,906…層間絶縁膜、10…ビット線コンタクトプラグ、11…タングステン、12,1201,1202,1203…シリコンナイトライド、13…キャパシタ下部電極コンタクトプラグ、14…ワード線(W/TiN/ポリシリコン)、15…ゲート電極(周辺回路)、16…メモリセルプラグ、17…ビット線コンタクト、18…ビット線コンタクトプラグ、19…周辺トランジスタコンタクトプラグ、20…ビット線、21…配線1、22…キャパシタ下部電極コンタクト2、23…キャパシタ下部電極、24…プレート電極、25…周辺回路配線接続プラグ、26…配線2、27…側壁酸化膜、28…Y選択ゲート、29…プリチャージ回路、30…センスアンプNMOS、31…センスアンプPMOS、32…N型ウエル領域。

Claims (15)

- 第1方向に延びる複数のワード線と、前記第1方向に交差する第2方向に延びる複数のビット線と、それぞれの前記ワード線とビット線の交点に配置された1つのトランジスタと1つの容量素子とを有する複数のメモリセルと、複数のビット線のうち交差するワード線が異なる2本のビット線が夫々接続される複数のセンスアンプとを備え、前記ビット線上に前記容量素子を配置した半導体集積回路装置であって、

半導体基板上において、前記複数のワード線中の隣接する第1、第2ワード線及び前記複数のビット線中の第1ビット線と交差し、前記第1及び第2方向と異なる第3方向に延び、前記第3方向に対して直交する第4方向に所定の幅を有する活性領域と、

前記活性領域内に形成され、前記トランジスタのソース、ドレインとして機能する第1及び第2半導体領域と、

前記容量素子を構成する第1及び第2電極と、前記第1及び第2電極間に位置する誘電体膜と、

前記ビット線と前記第1電極との間に位置する第1絶縁膜と、

前記第1絶縁膜に形成された第1開孔内に形成され、前記第1及び第2半導体領域の一方と、前記第1電極とを電気的に接続するための第1導体層と、

前記ビット線と前記第1及び第2半導体領域の他方を前記ビット線と前記活性領域の交点において接続する第3導体層とからなり、

前記第1導体層は前記ワード線とビット線によって囲まれた領域の各々に配置され、前記第1導体層の中心は、前記第3方向に沿う前記活性領域の中心線から対応する前記第3導体層が接続されるビット線から離れる方向にずれていることを特徴とする半導体集積回路装置。 - 請求項1に記載の半導体集積回路装置において、更に前記第1導体層と前記第1及び第2半導体領域の一方との間に配置された第2導体層を有し、前記第1方向において、前記第2導体層の幅は、前記第1導体層の幅よりも大であることを特徴とする半導体集積回路装置。

- 請求項2記載の半導体集積回路装置において、

前記第1方向において隣接する第2導体層の中心間距離は、前記第2導体層の上に配置された前記第1導体層の中心間距離よりも小であることを特徴とする半導体集積回路装置。 - 請求項2記載の半導体集積回路装置において、

前記第2方向において隣接する第2導体層の中心間距離は、前記第2導体層の上に配置された前記第1導体層の中心間距離よりも大であることを特徴とする半導体集積回路装置。 - 請求項2記載の半導体集積回路装置において、

前記ワード線と前記第2導体層間には窒化珪素膜が存在し、前記ビット線と前記第1導体層間には窒化珪素膜は存在しないことを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記第2方向において、前記第1導体層の幅は、前記ワード線の幅よりも小であることを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記ビット線の幅は、前記ワード線の幅よりも小であることを特徴とする半導体集積回路装置。 - 交差するワード線が異なる2本のビット線が夫々接続される複数のセンスアンプとを備える半導体集積回路装置であって、

各々が第1方向に延び、互いに隣接する第1、第2ワード線と、前記第1ワード線に隣接し前記第2ワード線と反対側に配置された第3ワード線と、前記第2ワード線に隣接し前記第1ワード線と反対側に配置された第4ワード線と、

前記第1方向に交差する第2方向に延び、連続的に隣接する第1,第2及び第3ビット線と、

前記第1及び第2方向と交差する第3方向に延びる活性領域と、

前記活性領域内であって、前記第1、第2ワード線間に位置する第1半導体領域と、前記活性領域内であって、前記第1、第3ワード線間及び第2、第4ワード線間に位置する第2半導体領域と、

第1,第2及び第3ビット線上に第1絶縁膜を介して形成された第1電極及び第2電極と、前記第1及び第2電極間に位置する誘電体膜から構成される容量素子と、

前記第2半導体領域と前記第1電極とを電気的に接続する前記第1絶縁膜内に形成された複数の第1導体層とを有し、

前記第1導体層は、前記ワード線と前記ビット線で囲まれた領域の各々に配置され、前記第1、第3ワード線間に配置された第1導体層の中心と、前記第2、第4ワード線間に配置された第1導体層の中心とを結ぶ直線が前記第1方向に対してなす角度は、前記第3方向が前記第1方向に対してなす角度よりも小であることを特徴とする半導体集積回路装置。 - 第1方向に延びる複数のワード線と、前記第1方向に交差する第2方向に延びる複数のビット線と、前記ワード線とビット線の交点に配置されたそれぞれが1つのトランジスタと1つの容量素子とを有する複数のメモリセルと、前記複数のビット線のうち交差する複数のワード線が異なる2本のビット線が夫々接続される複数のセンスアンプとを備え、前記ビット線上に前記容量素子を配置した半導体集積回路装置であって、

半導体基板上において2つのワード線及び1つのビット線と交差し、前記第1及び第2方向と異なる第3方向に延びる活性領域と、

前記活性領域内に形成され、前記トランジスタのソース、ドレインとして機能する第1及び第2半導体領域と、

前記容量素子を構成する第1及び第2電極と、前記第1及び第2電極間に位置する誘電体膜と、

前記ビット線と前記第1電極との間に位置する第1絶縁膜と、

前記第1絶縁膜に設けられた第1開孔内に形成され、前記第1及び第2半導体領域の一方と、前記第1電極とを電気的に接続するための第1導体層と、

前記ビット線と前記第1及び第2半導体領域の他方を前記第ビット線と前記活性領域の交点において接続する第3導体層とからなり、 前記第1導体層は、前記ワード線とビット線で囲まれた領域の各々に配置され、 前記第1導体層の前記第2方向における幅は、前記ワード線の幅よりも小であることを特徴とする半導体集積回路装置。 - 請求項9記載の半導体集積回路装置において、更に前記第1導体層と前記第1及び第2半導体領域の一方との間に配置された第2導体層を有し、前記第1方向において、前記第2導体層の幅は、前記第1導体層の幅よりも大であることを特徴とする半導体集積回路装置。

- 請求項10記載の半導体集積回路装置において、

前記第1方向において隣接する第2導体層の中心間距離は、前記第2導体層の上に配置された前記第1導体層の中心間距離よりも小であることを特徴とする半導体集積回路装置。 - 請求項10記載の半導体集積回路装置において、

前記第2方向において隣接する第2導体層の中心間距離は、前記第2導体層の上に配置された前記第1導体層の中心間距離よりも大であることを特徴とする半導体集積回路装置。 - 請求項9において、

前記ビット線の幅は、前記ワード線の幅よりも小であることを特徴とする半導体集積回路装置。 - 第1方向に延びる複数のワード線と、前記第1方向に交差する第2方向に延びる複数のビット線と、前記ワード線とビット線の交点に配置されたそれぞれが1つのトランジスタと1つの容量素子とを有する複数のメモリセルと、前記複数のビット線うち交差するワード線が異なる2本のビット線が夫々接続される複数のセンスアンプとを備え、前記ビット線上に前記容量素子を配置した半導体集積回路装置であって、

半導体基板上に形成された前記容量素子を構成する第1及び第2電極と、前記第1及び第2電極間に位置する誘電体膜と、

前記ビット線と前記第1電極との間に位置する第1絶縁膜と、

前記第1絶縁膜に形成された第1開孔内に形成され、前記トランジスタと、前記第1電極とを電気的に接続するための第1導体層とからなり、

前記第1導体層は前記ワード線とビット線によって囲まれた領域の各々に配置され、前記第1導体層と前記第1及び第2半導体領域の一方との間に配置された第2導体層を有し、前記第1方向において、前記第2導体層の幅は、前記第1導体層の幅よりも大であり、前記第1方向において隣接する第2導体層の中心間距離は、前記第2導体層の上に配置された前記第1導体層の中心間距離よりも小であることを特徴とする半導体集積回路装置。 - 請求項14記載の半導体集積回路装置において、

前記第2方向において隣接する第2導体層の中心間距離は、前記第2導体層の上に配置された前記第1導体層の中心間距離よりも大であることを特徴とする半導体集積回路装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP16632099A JP4063450B2 (ja) | 1999-06-14 | 1999-06-14 | 半導体集積回路装置 |

| TW089110509A TW473987B (en) | 1999-06-14 | 2000-05-30 | Semiconductor integrated circuit device and manufacture thereof |

| US09/592,648 US6621110B1 (en) | 1999-06-14 | 2000-06-13 | Semiconductor intergrated circuit device and a method of manufacture thereof |

| KR1020000032336A KR100650468B1 (ko) | 1999-06-14 | 2000-06-13 | 반도체 집적 회로 장치 및 그 제조 방법 |

| US10/630,695 US6809364B2 (en) | 1999-06-14 | 2003-07-31 | Semiconductor integrated circuit device and a method of manufacture thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP16632099A JP4063450B2 (ja) | 1999-06-14 | 1999-06-14 | 半導体集積回路装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000353793A JP2000353793A (ja) | 2000-12-19 |

| JP2000353793A5 JP2000353793A5 (ja) | 2004-09-30 |

| JP4063450B2 true JP4063450B2 (ja) | 2008-03-19 |

Family

ID=15829179

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP16632099A Expired - Fee Related JP4063450B2 (ja) | 1999-06-14 | 1999-06-14 | 半導体集積回路装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6621110B1 (ja) |

| JP (1) | JP4063450B2 (ja) |

| KR (1) | KR100650468B1 (ja) |

| TW (1) | TW473987B (ja) |

Families Citing this family (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2839581B1 (fr) * | 2002-05-07 | 2005-07-01 | St Microelectronics Sa | Circuit electronique comprenant un condensateur et au moins un composant semiconducteur, et procede de conception d'un tel circuit |

| KR100480601B1 (ko) * | 2002-06-21 | 2005-04-06 | 삼성전자주식회사 | 반도체 메모리 소자 및 그 제조방법 |

| KR100492899B1 (ko) * | 2002-11-18 | 2005-06-02 | 주식회사 하이닉스반도체 | 반도체소자 및 그 제조 방법 |

| DE10259634B4 (de) * | 2002-12-18 | 2008-02-21 | Qimonda Ag | Verfahren zur Herstellung von Kontakten auf einem Wafer |

| KR100502669B1 (ko) * | 2003-01-28 | 2005-07-21 | 주식회사 하이닉스반도체 | 반도체 메모리소자 및 그 제조 방법 |

| JP2004311706A (ja) * | 2003-04-07 | 2004-11-04 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP4342854B2 (ja) * | 2003-07-09 | 2009-10-14 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP4627977B2 (ja) | 2003-10-14 | 2011-02-09 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US7375033B2 (en) | 2003-11-14 | 2008-05-20 | Micron Technology, Inc. | Multi-layer interconnect with isolation layer |

| KR100630683B1 (ko) * | 2004-06-02 | 2006-10-02 | 삼성전자주식회사 | 6f2 레이아웃을 갖는 디램 소자 |

| KR100706233B1 (ko) * | 2004-10-08 | 2007-04-11 | 삼성전자주식회사 | 반도체 기억 소자 및 그 제조방법 |

| KR100604911B1 (ko) | 2004-10-20 | 2006-07-28 | 삼성전자주식회사 | 하부전극 콘택을 갖는 반도체 메모리 소자 및 그 제조방법 |

| KR100593746B1 (ko) * | 2004-12-24 | 2006-06-28 | 삼성전자주식회사 | 디램의 커패시터들 및 그 형성방법들 |

| KR100752644B1 (ko) | 2005-04-12 | 2007-08-29 | 삼성전자주식회사 | 반도체 소자의 셀영역 레이아웃 및 이를 이용한 콘택패드제조방법 |

| KR100693879B1 (ko) * | 2005-06-16 | 2007-03-12 | 삼성전자주식회사 | 비대칭 비트 라인들을 갖는 반도체 장치 및 이를 제조하는방법 |

| KR100654353B1 (ko) * | 2005-06-28 | 2006-12-08 | 삼성전자주식회사 | 커패시터를 구비하는 반도체 집적 회로 장치 및 이의 제조방법 |

| US7687342B2 (en) * | 2005-09-01 | 2010-03-30 | Micron Technology, Inc. | Method of manufacturing a memory device |

| US7557032B2 (en) | 2005-09-01 | 2009-07-07 | Micron Technology, Inc. | Silicided recessed silicon |

| US8716772B2 (en) | 2005-12-28 | 2014-05-06 | Micron Technology, Inc. | DRAM cell design with folded digitline sense amplifier |

| KR100876881B1 (ko) * | 2006-02-24 | 2008-12-31 | 주식회사 하이닉스반도체 | 반도체 소자의 패드부 |

| US7349232B2 (en) * | 2006-03-15 | 2008-03-25 | Micron Technology, Inc. | 6F2 DRAM cell design with 3F-pitch folded digitline sense amplifier |

| JP2007294618A (ja) * | 2006-04-24 | 2007-11-08 | Elpida Memory Inc | 半導体装置の製造方法及び半導体装置 |

| US20080035956A1 (en) * | 2006-08-14 | 2008-02-14 | Micron Technology, Inc. | Memory device with non-orthogonal word and bit lines |

| US7521763B2 (en) * | 2007-01-03 | 2009-04-21 | International Business Machines Corporation | Dual stress STI |

| KR100898394B1 (ko) * | 2007-04-27 | 2009-05-21 | 삼성전자주식회사 | 반도체 집적 회로 장치 및 그 제조 방법 |

| US7923373B2 (en) | 2007-06-04 | 2011-04-12 | Micron Technology, Inc. | Pitch multiplication using self-assembling materials |

| US8294188B2 (en) * | 2008-10-16 | 2012-10-23 | Qimonda Ag | 4 F2 memory cell array |

| JP2010219139A (ja) * | 2009-03-13 | 2010-09-30 | Elpida Memory Inc | 半導体装置及びその製造方法 |

| JP2010219326A (ja) * | 2009-03-17 | 2010-09-30 | Elpida Memory Inc | 半導体記憶装置及びその製造方法 |

| KR101076888B1 (ko) * | 2009-06-29 | 2011-10-25 | 주식회사 하이닉스반도체 | 반도체 소자의 연결 배선체 및 형성 방법 |

| JP2011023652A (ja) * | 2009-07-17 | 2011-02-03 | Elpida Memory Inc | 半導体記憶装置 |

| US8558320B2 (en) * | 2009-12-15 | 2013-10-15 | Qualcomm Incorporated | Systems and methods employing a physically asymmetric semiconductor device having symmetrical electrical behavior |

| US8686486B2 (en) * | 2011-03-31 | 2014-04-01 | Semiconductor Energy Laboratory Co., Ltd. | Memory device |

| JP5831687B2 (ja) * | 2011-07-22 | 2015-12-09 | ソニー株式会社 | 記憶装置およびその製造方法 |

| CN105905231A (zh) * | 2016-05-19 | 2016-08-31 | 国家海洋局第海洋研究所 | 便携双体船 |

| CN109427787A (zh) * | 2017-08-30 | 2019-03-05 | 联华电子股份有限公司 | 半导体存储装置 |

| US11637107B2 (en) | 2021-06-17 | 2023-04-25 | Applied Materials, Inc. | Silicon-containing layer for bit line resistance reduction |

| US11716838B2 (en) * | 2021-08-11 | 2023-08-01 | Micron Technology, Inc. | Semiconductor device and method for forming the wiring structures avoiding short circuit thereof |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR950003402B1 (ko) * | 1992-09-08 | 1995-04-12 | 삼성전자 주식회사 | 폴디드 비트라인 방식의 디램쎌 어레이 |

| JP3368002B2 (ja) | 1993-08-31 | 2003-01-20 | 三菱電機株式会社 | 半導体記憶装置 |

| TW377495B (en) * | 1996-10-04 | 1999-12-21 | Hitachi Ltd | Method of manufacturing semiconductor memory cells and the same apparatus |

| TW442923B (en) * | 1998-03-20 | 2001-06-23 | Nanya Technology Corp | Manufacturing method of DRAM comprising redundancy circuit region |

| JP3137185B2 (ja) * | 1998-04-09 | 2001-02-19 | 日本電気株式会社 | 半導体記憶装置 |

| KR20010003628A (ko) * | 1999-06-24 | 2001-01-15 | 김영환 | 반도체 메모리셀 구조 및 제조방법 |

-

1999

- 1999-06-14 JP JP16632099A patent/JP4063450B2/ja not_active Expired - Fee Related

-

2000

- 2000-05-30 TW TW089110509A patent/TW473987B/zh not_active IP Right Cessation

- 2000-06-13 KR KR1020000032336A patent/KR100650468B1/ko active IP Right Grant

- 2000-06-13 US US09/592,648 patent/US6621110B1/en not_active Expired - Lifetime

-

2003

- 2003-07-31 US US10/630,695 patent/US6809364B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000353793A (ja) | 2000-12-19 |

| US6621110B1 (en) | 2003-09-16 |

| US20040021159A1 (en) | 2004-02-05 |

| TW473987B (en) | 2002-01-21 |

| US6809364B2 (en) | 2004-10-26 |

| KR100650468B1 (ko) | 2006-11-28 |

| KR20010020983A (ko) | 2001-03-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4063450B2 (ja) | 半導体集積回路装置 | |

| US6130449A (en) | Semiconductor memory device and a method for fabricating the same | |

| KR100579365B1 (ko) | 메모리 어레이 및 지지 트랜지스터의 형성 방법, 및 이중일함수 지지 트랜지스터 및 매립형 dram 어레이를포함하는 반도체 장치 | |

| JP3532325B2 (ja) | 半導体記憶装置 | |

| US9385130B2 (en) | Semiconductor device and method for manufacturing the same | |

| JP3398649B2 (ja) | 異なる導電タイプのドーパントをゲート導体にドーピングする方法 | |

| US6555450B2 (en) | Contact forming method for semiconductor device | |

| US20130062679A1 (en) | Device | |

| US6146994A (en) | Method for forming self-aligned selective silicide layer using chemical mechanical polishing in merged DRAM logic | |

| US20040046195A1 (en) | Semiconductor integrated circuit device and process for manufacturing the same | |

| JP3857622B2 (ja) | 半導体装置およびその製造方法 | |

| KR100273987B1 (ko) | 디램 장치 및 제조 방법 | |

| US7015552B2 (en) | Dual work function semiconductor structure with borderless contact and method of fabricating the same | |

| US6281051B1 (en) | Semiconductor device and manufacturing method thereof | |

| US6238961B1 (en) | Semiconductor integrated circuit device and process for manufacturing the same | |

| US8779487B2 (en) | Semiconductor devices including storage node landing pads separated from bit line contact plugs | |

| JPH10163452A (ja) | 半導体記憶装置及びその製造方法 | |

| JP2002261256A (ja) | 半導体装置およびその製造方法 | |

| JP4181284B2 (ja) | 半導体装置の製造方法 | |

| JP3202501B2 (ja) | 半導体記憶装置及びその製造方法 | |

| JP2635429B2 (ja) | 半導体構造体及び半導体記憶装置並びにそれらの製造方法 | |

| KR100349345B1 (ko) | 반도체 장치의 비트라인 및 그 제조방법 | |

| JPH11330238A (ja) | 半導体装置の製造方法 | |

| KR20010064819A (ko) | 반도체장치의 콘택 형성방법 | |

| JPH0724285B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060322 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20060417 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060522 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20070605 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071010 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071107 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071225 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110111 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110111 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120111 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120111 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130111 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130111 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140111 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |