JP3959264B2 - 積層型半導体装置 - Google Patents

積層型半導体装置 Download PDFInfo

- Publication number

- JP3959264B2 JP3959264B2 JP2001375022A JP2001375022A JP3959264B2 JP 3959264 B2 JP3959264 B2 JP 3959264B2 JP 2001375022 A JP2001375022 A JP 2001375022A JP 2001375022 A JP2001375022 A JP 2001375022A JP 3959264 B2 JP3959264 B2 JP 3959264B2

- Authority

- JP

- Japan

- Prior art keywords

- chip

- circuit

- chips

- semiconductor device

- stacked

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 57

- 230000010355 oscillation Effects 0.000 description 18

- 238000000034 method Methods 0.000 description 17

- 238000004519 manufacturing process Methods 0.000 description 14

- 238000001514 detection method Methods 0.000 description 13

- 239000000758 substrate Substances 0.000 description 12

- 238000012545 processing Methods 0.000 description 9

- 238000010586 diagram Methods 0.000 description 6

- 101100476722 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) SBA1 gene Proteins 0.000 description 5

- 239000003990 capacitor Substances 0.000 description 5

- 230000002950 deficient Effects 0.000 description 5

- 230000003071 parasitic effect Effects 0.000 description 4

- 239000000470 constituent Substances 0.000 description 3

- 230000000694 effects Effects 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 239000004020 conductor Substances 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000003698 laser cutting Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54433—Marks applied to semiconductor devices or parts containing identification or tracking information

- H01L2223/5444—Marks applied to semiconductor devices or parts containing identification or tracking information for electrical read out

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06517—Bump or bump-like direct electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06572—Auxiliary carrier between devices, the carrier having an electrical connection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06596—Structural arrangements for testing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/544—Marks applied to semiconductor devices or parts, e.g. registration marks, alignment structures, wafer maps

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Integrated Circuits (AREA)

- Read Only Memory (AREA)

- Dram (AREA)

- Static Random-Access Memory (AREA)

Description

【発明の属する技術分野】

本発明は、積層型半導体装置に関する。

【0002】

【従来の技術】

メモリカード等に要求される記憶容量の増大に伴い、メモリチップ等の半導体集積回路チップ(LSIチップ)を積層した積層型半導体装置(マルチチップデバイス)が提案されている。この積層型半導体装置は、複数のチップを縦方向に積層するため、各チップを横方向に配置した半導体装置に比べて小型化(小面積化)をはかることが可能である。

【0003】

積層型半導体装置では、各チップ間の電気的な接続は、例えばチップを貫通するスループラグによって行われる。そのため、積層された同一構造のメモリチップのなかから所望のチップを選択するためには、チップを能動状態(動作可能状態)にするためのチップイネーブルバー(/CE)の端子位置をチップ毎に変えるといった手段を講じる必要がある。そのため、各チップの構造を共通化することができず、製造コストの上昇を招くことになる。

【0004】

このような問題に対して、各チップのスループラグ間を接続するバンプの配置パターンを変えることで、チップセレクトのための各チップのチップイネーブルバー或いはチップアドレス信号が入力される端子の位置を各チップで共通化するという提案がなされている(特開2000−49277)。この提案について、図10を参照して以下説明する。

【0005】

各チップC1〜C4はスループラグPGを備え、スループラグPG間はバンプBPによって接続されている。図中、P1で示した部分は、所望のチップを選択する(能動状態にする)ためのチップアドレス信号(CA0,CA1)が供給される端子部分である。P2で示した部分は、チップを特定するための端子が形成された部分であり、この部分では各チップC1〜C4でバンプBPの配置パターンを異ならせている。すなわち、チップC1では三つのスループラグPGが全て接地電位(Vss)に、チップC2では二つのスループラグPGが接地電位に、チップC3では一つのスループラグPGが接地電位に接続され、チップC4ではいずれのスループラグPGも接地電位には接続されていない。

【0006】

このように、バンプBPの配置によって各チップC1〜C4の接続関係を互いに異ならせることで、所望のチップを選択するためのチップアドレス信号CA0,CA1の端子位置を各チップで共通化することができる。そして、各チップC1〜C4内に、P1及びP2で示した部分の端子(スループラグPG)の論理値を入力とする論理回路を構成することで、チップアドレス信号(CA0,CA1)によって所望のチップを選択することができる。

【0007】

しかしながら、上述した従来技術では、各チップを共通化することは可能であるが、チップ毎にバンプの配置パターンを変える必要がある。そのため、やはり製造工程の共通化を十分にはかることができず、製造コストの上昇を招くことになる。また、図10のP2で示した部分のチップ特定用端子の数は、チップの積層数の増大とともに増加するため、チップの積層数が多い場合には端子数の大幅な増加につながる。

【0008】

【発明が解決しようとする課題】

以上述べたように、従来の積層型半導体装置では、バンプの配置パターンを変えることによって任意のチップを選択するようにしているため、製造工程の共通化が不十分であることに起因する製造コストの上昇といった問題や、積層数の増大にともなうチップ特定用端子数の増加といった問題があった。

【0009】

本発明は上記従来の課題に対してなされたものであり、製造コストの上昇や端子数の増加を抑えることが可能な積層型半導体装置を提供することを目的としている。

【0010】

【課題を解決するための手段】

本発明に係る積層型半導体装置は、複数の半導体集積回路チップが積層された積層型半導体装置であって、前記各半導体集積回路チップは、自己の識別情報が電気的に書き込まれて保持される保持回路を備えることを特徴とする。

【0011】

【発明の実施の形態】

以下、本発明の実施形態を図面を参照して説明する。

【0012】

図1は、本実施形態に係る積層型半導体装置の一構成例を示したものである。

【0013】

ベース基板BS上には、複数の半導体集積回路チップ(LSIチップ)C1〜C4が積層されている。ベース基板BSは、マザーボードとして機能するものであり、端子BTM及び図示しない配線パターンや電源等が設けられている。

【0014】

各半導体集積回路チップC1〜C4は、実質的に同一構造となっており、同一の仕様を有している。すなわち、各チップC1〜C4の形状、端子数及び回路構成等は実質的に同一となっている。実質的に同一であるとしているのは、例えばリダンダンシー等によって回路構成等が厳密には完全に同一とは言えない場合もあるためである。各チップC1〜C4において、少なくともクロック信号や各種制御信号などが入力される対応する端子どうしは共通に接続されている。本例では、チップを貫通する導電材からなるスループラグPGによって端子TMが構成されており、各チップの対応する端子どうしはバンプBPによって全て共通に接続されている。各チップの端子には、電源端子や各種制御信号及びデータ信号の入出力端子等が含まれており、その中には所望のチップを能動状態(動作可能状態)にするチップセレクトのためのチップアドレス(CA0,CA1)を指定する端子も含まれる。

【0015】

各チップC1〜C4の対応する端子どうしが共通に接続されているため、チップアドレスCA0及びCA1を指定するだけでは所望のチップを選択することはできない。そのため、各チップ内には自己を他のチップから識別するための識別データを電気的に保持(記憶)する保持回路(図示せず)が設けられている。この保持回路は、半導体能動素子を含み、保持する情報を電気的に書き込み可能な構造を有しており、例えば不揮発性メモリセルを含む回路によって構成されている。本例では、4層のチップC1〜C4を積層しているため、識別データは2ビットのコードで表すことができ、例えば各チップにはそれぞれ(0,0)(0,1)(1,0)(1,1)の異なるコードが割り当てられる。

【0016】

図2は、本実施形態に係る積層型半導体装置の他の構成例を示したものである。基本的な概念については図1に示した例と同様であり、本例特有の構成について以下説明する。

【0017】

本例では、各半導体集積回路チップC1〜C4は、基板SBA1〜SBA4に搭載されている。各基板SBA1〜SBA4上には、チップの端子TMと後述するスループラグTPとを電気的に接続する配線WRが設けられている。各基板SBA1〜SBA4の間には基板SBB1〜SBB4が介在しており、基板SBB1〜SBB4の中央に設けられた穴(デバイスホール)に対応して各チップC1〜C4が配置されている。各基板SBA1〜SBA4及び各基板SBB1〜SBB4には、各基板を貫通するスループラグTPが設けられており、各スループラグTPどうしはバンプBPによって接続されている。

【0018】

以下の説明では、半導体集積回路チップC1〜C4としてNAND型E2PROM等の不揮発性メモリチップを想定し、自己の識別データを保持する保持回路として不揮発性メモリセルを備えた回路を想定する。また、積層型半導体装置としては、図1に示した構成例を想定する。

【0019】

図3は、各半導体集積回路チップC1〜C4内に設けられた回路の一例を示した図である。

【0020】

各チップC1〜C4内の保持回路11には自己の識別データとして、例えばチップC1には(0,0)、チップC2には(0,1)、チップC3には(1,0)、チップC4には(1,1)が保持されている。電源が投入されると、保持回路11に保持された識別データのうち、下位ビットはラッチ回路12aに、上位ビットはラッチ回路12bにラッチされる。

【0021】

各チップC1〜C4には、チップアドレスを入力する端子13a及び13b(図1に示した端子TMのなかの二つ)が設けられており、端子13aにはチップアドレスの下位ビットCA0が、端子13bにはチップアドレスの上位ビットCA1が外部から入力される。例えば、チップC1を選択する場合には、チップアドレス(CA0,CA1)を(0,0)に設定する。なお、さらに上位のアドレスを入力する端子を設けることにより、チップC1〜C4のいずれも選択していない状態を設定することができる。

【0022】

ラッチ回路12aの出力及び端子13aはエクスクルーシブノア(EXNOR)回路14aに、ラッチ回路12bの出力及び端子13bはエクスクルーシブノア(EXNOR)回路14bに接続されており、エクスクルーシブノア回路14a及び14bの出力はナンド(NAND)回路15に入力している。したがって、チップアドレスCA0とラッチ回路12aのデータが等しく、且つチップアドレスCA1とラッチ回路12bのデータが等しい場合、すなわち端子13a及び13bから入力されるチップアドレスと保持回路11に保持されている識別データが全て等しい場合に限り、ナンド回路15の出力チップイネーブルバー(/CE)はロウレベル(論理値0)となる。/CE信号は主回路16(例えば、不揮発性メモリチップでは、メモリセルアレイ16aやローデコーダ・カラムデコーダ等の周辺回路16b等からなる回路)に供給され、/CE信号がアクティブ(/CE信号がロウレベル)となったチップのみが能動状態となる。

【0023】

以上のように、本実施形態に係る積層型半導体装置は、各チップ内に自己の識別データを電気的に書き込んで電気的に保持する保持回路を備えているため、従来のようにチップセレクトのために各チップの接続関係を異ならせる必要がない。そのため、バンプの配置パターンをチップ毎に変える必要がなく、各チップの製造工程の共通化はもちろんバンプの製造工程の共通化もはかることができる。また、従来のようにチップ特定用の多数の端子を設ける必要がないので、チップの積層数の増大にともなう端子数の大幅な増加を抑えることができる。

【0024】

また、保持回路は電気的に書き換え可能な構造であるため、識別データを書き込んだ後に容易に識別データを変更することができる。例えば、各チップ間のチップセレクトのための手段としてバンプの代わりにヒューズを用い、ヒューズをレーザによって溶断することでチップ内の接続パターンを変えるような場合には、一旦ヒューズを切断した後は接続パターンの変更を行うことができないが、本実施形態では必要に応じてデータの書き換えを行うことが可能である。

【0025】

さらに、電気的な書き込み(書き換え)を行うことから、各チップを積層した後に識別データを書き込むこともでき、例えば電源を投入する度に識別データを書き込むといったことも可能である。

【0026】

次に、本実施形態に係る積層型半導体装置の製造方法の一例について、図4に示したフローチャートを参照して説明する。本例は、各チップの積層前に識別データを書き込む例である。

【0027】

まず、所定の製造工程にしたがって、半導体能動素子や配線等の回路及びスループラグを半導体ウエハに形成し、さらにスループラグ上にパッドを形成する(S11)。続いて、プレダイソートにより不良チップの検出を行い、不良セルの特定と不良セルの救済を行うリダンダンシーを実施する。リダンダンシーはレーザ溶断で行ってもよいし、電気的な切り換えによって行ってもよい。この工程において、保持回路への識別データの書き込みを行う。書き込み方法は、不揮発性メモリセルに対する通常の書き込み方法と同様である(S12)。なお、不良セルの救済のためのリダンダンシー回路内にも、識別データを保持する保持回路と同一の構造、すなわち不揮発性メモリセルを用いれば、リダンダンシー及び識別データの書き込みに当たって、共通の書き込み方法を用いることができ、工程を簡略化するうえで有効となる。

【0028】

続いて、先に形成したパッド上にバンプを形成する(S13)。このバンプ形成工程は、S12の工程の前に行ってもよい。さらに、ファイナルダイソート及びバーンインを行う(S14)。

【0029】

次に、ウエハの裏面から研削処理等を行ってウエハを薄くし、さらにダイシングによってウエハをチップに分離する(S15)。その後、チップの選別を行い(S16)、さらにチップの積層、組み立てを行う(S17)。チップの積層の際には、書き込まれた識別データが互いに異なるチップを積層する。例えば、チップC1では(0,0)、チップC2では(0,1)、チップC3では(1,0)、チップC4では(1,1)というように、各チップの識別データが互いに異なるようにする。

【0030】

なお、本例においては、保持回路への識別データの書き込みは各チップを積層する前であればよく、例えばファイナルダイソート工程の際に書き込み処理を行うようにしてもよい。すなわち、本実施形態の積層型半導体装置は、識別データを保持回路に電気的に書き込んで保持するため、所望の時点で識別データの書き込みを行うことが可能である。

【0031】

次に、本実施形態に係る積層型半導体装置の動作例(電源投入後の動作例)について、図5に示したフローチャートを参照して説明する。

【0032】

積層型半導体装置に電源が投入(パワーオン)されると(S21)、各チップはパワーオンリセットされ(S22)、一定期間の待機状態の後(S23)、各チップのR/B(レディ/ビジー)信号端子がB(ビジー)状態にセットされる(S24)。次に、不良アドレスデータを読み出してセットする初期設定データリード処理(S25)、制御電圧値データを読み出してセットする初期設定データリード処理(S26)、保持回路に保持されている識別データを読み出してセットする初期設定データリード処理(S27)、さらにその他のデータを読み出してセットする初期設定データリード処理(S28)を行う。S27の処理は、図3で示した例では、保持回路11に保持されている識別データをラッチ回路12a及び12bにラッチする処理に対応する。その後、R/B信号端子をR(レディ)状態、すなわち外部からのアクセスが可能なスタンバイ状態にセットする(S29)。

【0033】

以上のようにして初期設定を行った後、図3で示したように、端子13a及び13bに外部からチップアドレス信号CA0及びCA1を入力することで、チップC1〜C4のなかから所望のチップを選択することができる。

【0034】

次に、本実施形態に係る積層型半導体装置の製造方法の他の例について、図6に示したフローチャートを参照して説明する。

【0035】

図6に示したフローチャートと図4に示したフローチャートを比較すればわかるように、本例では、S32のステップで識別データの書き込み処理は行わず、チップC1〜C4を積層した後に、S38のステップで保持回路に識別データの書き込み処理を行うようにしている。その他の基本的な処理(S31、S33〜S37)については図4に示した例と同様である。

【0036】

このように、本実施形態に係る積層型半導体装置では、各チップ内に自己の識別データを電気的に書き込んで保持する保持回路を備えているため、各チップを積層した後でも識別データを保持回路に書き込むことが可能である。以下、各チップ積層後に識別データを書き込む処理の具体例について説明する。

【0037】

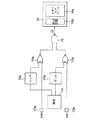

図7は上記処理を行うための識別情報設定回路の構成例を示したブロック図であり、図7に示すような回路が各チップC1〜C4内にそれぞれ同一構成で形成されている。また、以下に述べる各端子も各チップC1〜C4に同一構成で形成されており、各端子は共通に接続されている。

【0038】

端子21には入力制御回路22が接続されており、例えば端子21に外部から制御信号を入力することで、入力制御回路22から発振回路23に発振開始信号が送出される。入力制御回路22には電圧発生回路24も接続されており、電圧発生回路24では入力制御回路22からの信号を受けて所定の電圧を発生する。電圧発生回路24の電圧はキャパシタ(チップ内の寄生容量を用いる)25に徐々に充電され、キャパシタ25の充電電圧は時間の経過とともにしだいに上昇する。キャパシタ25の充電電圧は電圧検出回路26によって検出され、充電電圧が所定値に到達したときに電圧検出回路26から発振回路23に発振終了信号が送出され、発振回路23の発振が停止する。

【0039】

発振回路23にはカウンタ回路27が接続されており、カウンタ回路27では発振回路23からの発振信号をクロック信号としてカウントを行う。すなわち、上述した発振開始信号が生じてから発振終了信号が生じるまでの時間がカウンタ回路27によってカウントされることになる。キャパシタ25の容量や発振回路23の発振周期はチップ毎にばらつくため、カウンタ回路27でのカウント値は通常各チップC1〜C4間で通常異なったものとなる。

【0040】

カウンタ回路28は、端子29を介して外部から供給されるクロック信号によってカウント動作を行う。このクロック信号は、カウンタ回路27でのカウント動作が終了した後、外部から各チップに入力するようにする。カウンタ回路27及び28のカウント値は一致検出回路30に入力しており、一致検出回路30からはカウンタ回路27及び28の両カウント値が一致したときに一致信号が出力される。先に述べたように、カウンタ回路27でのカウント値は各チップC1〜C4間で異なっているため、一致検出回路30から一致信号が出力されるタイミングも各チップC1〜C4間で異なったものとなる。

【0041】

一致検出回路30からの一致信号は、プルアップ抵抗32が接続されたトランジスタ31を介して端子33に出力される。端子33は各チップC1〜C4で共通に接続されているため、あるチップで生じた一致信号は他のチップにも供給されることになる。自己のチップ内で生じた一致信号(トランジスタ31の出力信号)及び他のチップで生じた一致信号(端子33を介して入力する一致信号)は、クロック信号として遅延回路34を介してカウンタ回路(本例では2ビット構成)35に入力する。したがって、カウンタ回路35のカウント値は、各チップで一致信号が生じる毎にカウントアップされる。

【0042】

一致検出回路30からの一致信号はゲート回路36にも入力しており、自己のチップで生じた一致信号によってゲート回路36が導通状態となり、カウンタ回路35のカウント値がゲート回路36を介してラッチ回路37にラッチされる。カウンタ回路35の入力には遅延回路34が接続されていることから、一致信号が生じる前のカウント値がラッチ回路37にラッチされることになる。例えば、チップC1で最初に一致信号が生じた場合には、チップC1のカウンタ回路35のカウント値は“00”であり、この値“00”がチップC1のラッチ回路37にラッチされる。その次にチップC2で一致信号が生じた場合には、チップC2のカウンタ回路35のカウント値は“01”であり、この値“01”がチップC2のラッチ回路37にラッチされる。このようにして、各チップC1〜C4内のラッチ回路37には、それぞれ異なったカウント値“00”“01”“10”及び“11”がラッチされる。

【0043】

各チップC1〜C4内のラッチ回路37にラッチされた値は、各チップC1〜C4内の保持回路(図3の保持回路11に対応)38に書き込まれ、各チップC1〜C4内の保持回路38には互いに異なった値、すなわち互いに異なった識別データが記憶されることになる。

【0044】

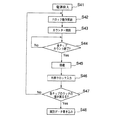

図8は、図7に示した回路の動作の一例を示したフローチャートである。

【0045】

電源投入(S41)の後、端子21に制御信号が入力されると、入力制御回路22からの発振開始信号によって発振回路23での発振動作が開始され(S42)、発振信号をクロックとしてカウンタ27でのカウント動作が開始される(S43)。電圧検出回路26から発振終了信号が出力され、全チップC1〜C4のカウント動作が終了すると(S44)、各チップC1〜C4は一旦待機状態となる(S45)。

【0046】

その後、各チップに端子29から共通の外部クロック信号を入力し、各チップのカウンタ回路28で外部クロック信号をカウントする(S46)。各チップでは、先に述べたように、一致検出回路30での一致検出動作、ラッチ回路37へのカウント値のラッチ動作等が行われる。

【0047】

各チップC1〜C4におけるカウンタ27のカウント値は寄生容量の充電時間のばらつき等により通常は互いに異なったものとなるが、2以上のチップでカウンタ27のカウント値がたまたま等しくなっている場合もある。このような場合には、上記2以上のチップにおいて一致検出回路30から同時に一致信号が生じるため、それらのチップのラッチ回路37にラッチされるカウント値は互いに等しくなる。そこで、ラッチ回路37にラッチされたカウント値が各チップ間で互いに異なっているか否かを判断する(S47)。本例では、ラッチ回路37自体にラッチされているカウント値を比較する代わりに、端子33から出力される一致信号を外部装置でカウントするようにしている。2以上のチップでラッチ回路37のカウント値が等しくなる場合には、それらのチップでは端子33から同時に一致信号が生じているため、外部装置でのカウント値は3以下となる。したがって、外部装置でのカウント値が3以下の場合には、端子21に制御信号を入力してカウンタ27、28及び35のリセット等を行い、各チップのラッチ回路37にラッチされるカウント値が互いに異なった値となるまで(外部装置でのカウント値が4となるまで)、繰り返し上述した処理と同様の処理を行う。

【0048】

各チップのラッチ回路37にラッチされたカウント値が各チップ間で互いに異なっている場合(外部装置でのカウント値が4の場合)には、各チップのラッチ回路37にラッチされたカウント値が、各チップの保持回路38に識別データとして書き込まれる(S48)。

【0049】

なお、各チップのラッチ回路37或いはカウンタ27のカウント値自体を比較して、2以上のチップでカウント値が互いに等しい場合に、上述したのと同様にしてS42からの処理を繰り返すようにしてもよい。

【0050】

以上のように、寄生容量への充電時間等、所定の動作に費やされる時間のチップ間でのばらつきを利用することにより、各チップを積層した後でも各保持回路に互いに異なった識別情報を書き込むことが可能となる。

【0051】

図7及び図8で説明した例では、寄生容量への充電時間等のチップ間でのばらつきを利用して、各チップ内の保持回路に互いに異なる識別データを記憶するようにしたが、その他任意の動作に費やされる時間のチップ間でのばらつきが利用可能であり、例えばメモリセル(メモリセルアレイ内のメモリセル)への書き込み時間のチップ間でのばらつきを利用するようにしてもよい。

【0052】

図9は、このような方法を利用して識別データを記憶する場合の動作を示したフローチャートである。なお、回路構成については図示しないが、図7のカウンタ27への入力までの構成が異なるだけであり、カウンタ27及びそれ以降の構成(参照番号27〜38の構成)については図7の例と同様である。

【0053】

電源投入(S51)及びパワーオンリセット(S52)の後、各チップをテストモードにして(S53)、メモリセルへの書き込み動作を開始し、書き込み開始と同時にカウンタ(図7のカウンタ27に相当)の動作を開始する(S54)。全チップC1〜C4の書き込みが終了してカウント動作が終了すると(S55)、各チップC1〜C4は一旦待機状態となる(S56)。その後の基本的な処理(S57〜S59)については図8に示した例と同様である。

【0054】

このように、本例においても図8に示した例と同様、各チップ積層後に保持回路に識別データを書き込むことが可能である。なお、本例ではメモリセルへの書き込み時間のばらつきを利用したが、消去時間のばらつきを利用してもよく、さらに書き込み時間及び消去時間両者のばらつきを利用してもよい。

【0055】

以上、本発明の実施形態を説明したが、本実施形態は以下のような変更を行うことも可能である。

【0056】

上述した実施形態では保持回路を主回路内のメモリセルアレイとは別に設けたが、メモリセルアレイ内のメモリセルを保持回路のメモリセルとして代用してもよい。

【0057】

また、上述した実施形態では、半導体集積回路チップとして不揮発性メモリチップを、保持回路として不揮発性メモリセルからなる回路を想定して説明を行ったが、これ以外のチップや保持回路を用いることも可能である。例えば、図6〜図9で説明したように、各チップ積層後に保持回路に識別データを書き込む場合には、半導体集積回路チップとしてDRAM等の揮発性メモリチップを、保持回路としてDRAM用の揮発性メモリセルからなる回路を用いるようにしてもよい。例えばDRAMチップでは、電源オフによってメモリセルアレイのデータが消失するため、保持回路に保持されていた識別データが電源オフ時に消失するものの、電源をオンしたときに新たに識別データを保持回路に記憶させるようにすれば問題はない。要するに、保持回路には電源投入前に予め識別データが記憶されていなくてもよく、電源投入の度に保持回路に識別データを記憶させるようにしてもよい。さらに、保持回路としては、電気的に書き換え可能な構造に何ら限定されるものではなく、電気的な書き込みが可能であれば、例えばアンチヒューズ素子などを用いたPROMのように、一旦設定された自己の識別情報がその後書き換えられることなく保持され続けるものであってもよい。

【0058】

以上、本発明の実施形態を説明したが、本発明は上記実施形態に限定されるものではなく、その趣旨を逸脱しない範囲内において種々変形して実施することが可能である。さらに、上記実施形態には種々の段階の発明が含まれており、開示された構成要件を適宜組み合わせることによって種々の発明が抽出され得る。例えば、開示された構成要件からいくつかの構成要件が削除されても、所定の効果が得られるものであれば発明として抽出され得る。

【0059】

【発明の効果】

本発明によれば、各チップ内に自己の識別データを保持する回路を備えていることから、製造工程の共通化や端子数増加の防止等をはかることが可能となり、低コストの積層型半導体装置を得ることが可能となる。

【図面の簡単な説明】

【図1】本発明の実施形態に係る積層型半導体装置の構成の一例を示した図。

【図2】本発明の実施形態に係る積層型半導体装置の構成の他の例を示した図。

【図3】本発明の実施形態に係り、半導体集積回路チップ内に設けられた回路の一例を示した図。

【図4】本発明の実施形態に係る積層型半導体装置の製造方法の一例を示したフローチャート。

【図5】本発明の実施形態に係る積層型半導体装置について電源投入後の動作例を示したフローチャート。

【図6】本発明の実施形態に係る積層型半導体装置の製造方法の他の例を示したフローチャート。

【図7】本発明の実施形態に係り、半導体集積回路チップ内に設けられた識別情報設定回路の構成例を示したブロック図。

【図8】本発明の実施形態に係り、識別情報の設定方法の一例を示したフローチャート。

【図9】本発明の実施形態に係り、識別情報の設定方法の他の例を示したフローチャート。

【図10】従来技術に係る積層型半導体装置の構成例を示した図。

【符号の説明】

BS…ベース基板

C1〜C4…半導体集積回路チップ

BTM、TM…端子

PG…スループラグ

BP…バンプ

CA0、CA1…チップアドレス

SBA1〜SBA4、SBB1〜SBB4…基板

WR…配線

11…保持回路

12a、12b…ラッチ回路

13a、13b…端子

14a、14b…エクスクルーシブノア回路

15…ナンド回路

16…主回路

16a…メモリセルアレイ

16b…周辺回路

21、29、33…端子

22…入力制御回路

23…発振回路

24…電圧発生回路

25…キャパシタ

26…電圧検出回路

27、28、35…カウンタ回路

30…一致検出回路

31…トランジスタ

32…プルアップ抵抗

34…遅延回路

36…ゲート回路

37…ラッチ回路

38…保持回路

Claims (5)

- 複数の半導体集積回路チップが積層された積層型半導体装置であって、

前記各半導体集積回路チップは、

自己の識別情報が電気的に書き込まれて保持される保持回路と、

各半導体集積回路チップが積層された状態で自己の保持回路に自己の識別情報を設定する識別情報設定回路と、

自己の保持回路に自己の識別情報を設定するために用いる少なくとも一つの設定端子と、

を備え、

各半導体集積回路チップの前記少なくとも一つの設定端子は、他の半導体集積回路チップの対応する前記少なくとも一つの設定端子に接続され、

前記識別情報設定回路は、所定の動作に費やされる時間の各半導体集積回路チップ間での相違に基づいて自己の保持回路に自己の識別情報を設定する

ことを特徴とする積層型半導体装置。 - 前記各半導体集積回路チップ内の回路構成は互いに実質的に同一である

ことを特徴とする請求項1に記載の積層型半導体装置。 - 前記各半導体集積回路チップはチップセレクトのための信号が入力される複数の端子を有し、各半導体集積回路チップの対応する前記複数の端子どうしは全て共通に接続されている

ことを特徴とする請求項1に記載の積層型半導体装置。 - 前記保持回路は、保持される情報を電気的に書き換え可能な構造を有する

ことを特徴とする請求項1に記載の積層型半導体装置。 - 前記保持回路は、不揮発性メモリセルを含む

ことを特徴とする請求項1に記載の積層型半導体装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001375022A JP3959264B2 (ja) | 2001-09-29 | 2001-09-29 | 積層型半導体装置 |

| TW091122148A TW564526B (en) | 2001-09-29 | 2002-09-26 | Laminated type semiconductor device |

| US10/255,960 US6791175B2 (en) | 2001-09-29 | 2002-09-27 | Stacked type semiconductor device |

| KR10-2002-0059094A KR100506105B1 (ko) | 2001-09-29 | 2002-09-28 | 적층형 반도체 장치 |

| CNB021440697A CN1224102C (zh) | 2001-09-29 | 2002-09-29 | 层叠型半导体装置 |

| US10/902,291 US6991964B2 (en) | 2001-09-29 | 2004-07-30 | Stacked type semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001375022A JP3959264B2 (ja) | 2001-09-29 | 2001-09-29 | 積層型半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003110086A JP2003110086A (ja) | 2003-04-11 |

| JP2003110086A5 JP2003110086A5 (ja) | 2005-08-11 |

| JP3959264B2 true JP3959264B2 (ja) | 2007-08-15 |

Family

ID=19183475

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001375022A Expired - Fee Related JP3959264B2 (ja) | 2001-09-29 | 2001-09-29 | 積層型半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US6791175B2 (ja) |

| JP (1) | JP3959264B2 (ja) |

| KR (1) | KR100506105B1 (ja) |

| CN (1) | CN1224102C (ja) |

| TW (1) | TW564526B (ja) |

Families Citing this family (72)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7102892B2 (en) * | 2000-03-13 | 2006-09-05 | Legacy Electronics, Inc. | Modular integrated circuit chip carrier |

| US6812726B1 (en) * | 2002-11-27 | 2004-11-02 | Inapac Technology, Inc. | Entering test mode and accessing of a packaged semiconductor device |

| US7240254B2 (en) * | 2000-09-21 | 2007-07-03 | Inapac Technology, Inc | Multiple power levels for a chip within a multi-chip semiconductor package |

| US7444575B2 (en) * | 2000-09-21 | 2008-10-28 | Inapac Technology, Inc. | Architecture and method for testing of an integrated circuit device |

| JP3983996B2 (ja) * | 2001-04-23 | 2007-09-26 | 株式会社ルネサステクノロジ | 半導体集積回路装置 |

| US7313740B2 (en) * | 2002-07-25 | 2007-12-25 | Inapac Technology, Inc. | Internally generating patterns for testing in an integrated circuit device |

| US8001439B2 (en) * | 2001-09-28 | 2011-08-16 | Rambus Inc. | Integrated circuit testing module including signal shaping interface |

| US8286046B2 (en) | 2001-09-28 | 2012-10-09 | Rambus Inc. | Integrated circuit testing module including signal shaping interface |

| US8166361B2 (en) | 2001-09-28 | 2012-04-24 | Rambus Inc. | Integrated circuit testing module configured for set-up and hold time testing |

| TWI237354B (en) * | 2002-01-31 | 2005-08-01 | Advanced Semiconductor Eng | Stacked package structure |

| US20060147719A1 (en) * | 2002-11-22 | 2006-07-06 | Slawomir Rubinsztajn | Curable composition, underfill, and method |

| US20050266263A1 (en) * | 2002-11-22 | 2005-12-01 | General Electric Company | Refractory solid, adhesive composition, and device, and associated method |

| US8063650B2 (en) | 2002-11-27 | 2011-11-22 | Rambus Inc. | Testing fuse configurations in semiconductor devices |

| JP4419049B2 (ja) * | 2003-04-21 | 2010-02-24 | エルピーダメモリ株式会社 | メモリモジュール及びメモリシステム |

| US7098541B2 (en) * | 2003-05-19 | 2006-08-29 | Hewlett-Packard Development Company, L.P. | Interconnect method for directly connected stacked integrated circuits |

| US7145226B2 (en) * | 2003-06-30 | 2006-12-05 | Intel Corporation | Scalable microelectronic package using conductive risers |

| JP2005101356A (ja) * | 2003-09-25 | 2005-04-14 | Toshiba Corp | 無線カード |

| KR100621992B1 (ko) * | 2003-11-19 | 2006-09-13 | 삼성전자주식회사 | 이종 소자들의 웨이퍼 레벨 적층 구조와 방법 및 이를이용한 시스템-인-패키지 |

| JP4399777B2 (ja) | 2004-01-21 | 2010-01-20 | セイコーエプソン株式会社 | 半導体記憶装置、半導体装置、及び電子機器 |

| KR100618838B1 (ko) * | 2004-06-24 | 2006-09-01 | 삼성전자주식회사 | 상하 연결 능력을 개선할 수 있는 스택형 멀티칩 패키지 |

| JP4421957B2 (ja) | 2004-06-29 | 2010-02-24 | 日本電気株式会社 | 3次元半導体装置 |

| JP4865197B2 (ja) | 2004-06-30 | 2012-02-01 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| KR100688518B1 (ko) * | 2005-01-12 | 2007-03-02 | 삼성전자주식회사 | 개별 칩들의 디바이스 정보를 직접 판독할 수 있는시그너처 식별 장치를 갖는 멀티 칩 패키지 |

| US7405246B2 (en) * | 2005-04-05 | 2008-07-29 | Momentive Performance Materials Inc. | Cure system, adhesive system, electronic device |

| US7446136B2 (en) * | 2005-04-05 | 2008-11-04 | Momentive Performance Materials Inc. | Method for producing cure system, adhesive system, and electronic device |

| JP4577688B2 (ja) | 2005-05-09 | 2010-11-10 | エルピーダメモリ株式会社 | 半導体チップ選択方法、半導体チップ及び半導体集積回路装置 |

| DE102005031378B4 (de) * | 2005-07-05 | 2018-05-30 | Rohde & Schwarz Gmbh & Co. Kg | Verfahren zur fälschungssicheren Identifikation individueller elektronischer Baugruppen |

| JP4799157B2 (ja) | 2005-12-06 | 2011-10-26 | エルピーダメモリ株式会社 | 積層型半導体装置 |

| US7352602B2 (en) * | 2005-12-30 | 2008-04-01 | Micron Technology, Inc. | Configurable inputs and outputs for memory stacking system and method |

| US7645675B2 (en) * | 2006-01-13 | 2010-01-12 | International Business Machines Corporation | Integrated parallel plate capacitors |

| JP4753725B2 (ja) * | 2006-01-20 | 2011-08-24 | エルピーダメモリ株式会社 | 積層型半導体装置 |

| JP4693656B2 (ja) * | 2006-03-06 | 2011-06-01 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP4843336B2 (ja) * | 2006-03-06 | 2011-12-21 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR100717285B1 (ko) * | 2006-04-19 | 2007-05-15 | 삼성전자주식회사 | 듀얼 칩 패키지 |

| JP2008091638A (ja) | 2006-10-02 | 2008-04-17 | Nec Electronics Corp | 電子装置およびその製造方法 |

| JP5141005B2 (ja) * | 2006-12-04 | 2013-02-13 | 凸版印刷株式会社 | 半導体メモリ |

| US8018071B2 (en) | 2007-02-07 | 2011-09-13 | Samsung Electronics Co., Ltd. | Stacked structure using semiconductor devices and semiconductor device package including the same |

| JP2009003991A (ja) * | 2007-06-19 | 2009-01-08 | Toshiba Corp | 半導体装置及び半導体メモリテスト装置 |

| US7760533B2 (en) * | 2007-10-02 | 2010-07-20 | Micron Technology, Inc. | Systems, methods and devices for arbitrating die stack position in a multi-bit stack device |

| JP2009129498A (ja) | 2007-11-22 | 2009-06-11 | Toshiba Corp | 半導体記憶装置 |

| US8399973B2 (en) * | 2007-12-20 | 2013-03-19 | Mosaid Technologies Incorporated | Data storage and stackable configurations |

| KR101398633B1 (ko) * | 2008-01-28 | 2014-05-26 | 삼성전자주식회사 | 반도체 메모리 장치 및 이 장치의 칩 식별신호 발생방법 |

| KR100900239B1 (ko) | 2008-02-18 | 2009-06-02 | 주식회사 하이닉스반도체 | 스택 패키지 및 그의 제조방법 |

| KR101571763B1 (ko) * | 2008-07-07 | 2015-12-07 | 삼성전자주식회사 | 적응적 제어 스킴을 가지는 메모리 장치 및 그 동작 방법 |

| US7847626B2 (en) * | 2008-03-04 | 2010-12-07 | Micron Technology, Inc. | Structure and method for coupling signals to and/or from stacked semiconductor dies |

| KR100963593B1 (ko) * | 2008-04-11 | 2010-06-15 | 한국과학기술원 | 관통 웨이퍼 비아를 포함하는 적층 칩 패키지 및 이의 생산방법 |

| KR101001635B1 (ko) | 2008-06-30 | 2010-12-17 | 주식회사 하이닉스반도체 | 반도체 패키지, 이를 갖는 적층 반도체 패키지 및 적층반도체 패키지의 하나의 반도체 칩 선택 방법 |

| JP4982778B2 (ja) | 2008-07-04 | 2012-07-25 | 学校法人慶應義塾 | 電子回路装置 |

| US8130527B2 (en) | 2008-09-11 | 2012-03-06 | Micron Technology, Inc. | Stacked device identification assignment |

| JP5331427B2 (ja) * | 2008-09-29 | 2013-10-30 | 株式会社日立製作所 | 半導体装置 |

| KR101053744B1 (ko) * | 2009-06-29 | 2011-08-02 | 주식회사 하이닉스반도체 | 멀티 칩 메모리 장치 |

| JP2011029535A (ja) * | 2009-07-29 | 2011-02-10 | Elpida Memory Inc | 半導体装置 |

| US9160349B2 (en) * | 2009-08-27 | 2015-10-13 | Micron Technology, Inc. | Die location compensation |

| KR101069710B1 (ko) * | 2009-10-29 | 2011-10-04 | 주식회사 하이닉스반도체 | 반도체 장치 및 이의 칩 선택방법 |

| US8437163B2 (en) * | 2010-02-11 | 2013-05-07 | Micron Technology, Inc. | Memory dies, stacked memories, memory devices and methods |

| KR20110112707A (ko) | 2010-04-07 | 2011-10-13 | 삼성전자주식회사 | 층간 연결 유닛을 갖는 적층 메모리 장치, 이를 포함하는 메모리 시스템, 및 전송선의 지연시간 보상 방법 |

| KR101751045B1 (ko) | 2010-05-25 | 2017-06-27 | 삼성전자 주식회사 | 3d 반도체 장치 |

| JP2011258266A (ja) * | 2010-06-08 | 2011-12-22 | Sony Corp | 半導体装置および集積型半導体装置 |

| TW201203496A (en) * | 2010-07-01 | 2012-01-16 | Nat Univ Tsing Hua | 3D-IC device and decreasing type layer-ID detector for 3D-IC device |

| JP2012033627A (ja) | 2010-07-29 | 2012-02-16 | Sony Corp | 半導体装置および積層半導体装置 |

| KR101251916B1 (ko) * | 2010-08-27 | 2013-04-08 | 에스케이하이닉스 주식회사 | 반도체 집적회로 |

| JP5654855B2 (ja) | 2010-11-30 | 2015-01-14 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | 半導体装置 |

| KR101223540B1 (ko) | 2011-01-14 | 2013-01-21 | 에스케이하이닉스 주식회사 | 반도체 장치, 그의 칩 아이디 부여 방법 및 그의 설정 방법 |

| KR101805146B1 (ko) | 2011-05-03 | 2017-12-05 | 삼성전자주식회사 | 반도체 칩, 메모리 칩, 메모리 제어 칩, 반도체 패키지, 그리고 메모리 시스템 |

| JP5429891B2 (ja) * | 2011-05-09 | 2014-02-26 | Necアクセステクニカ株式会社 | データ書き込み装置およびデータ書き込み方法 |

| JP2013004601A (ja) * | 2011-06-14 | 2013-01-07 | Elpida Memory Inc | 半導体装置 |

| TWI482260B (zh) * | 2012-03-30 | 2015-04-21 | Nat Univ Tsing Hua | 多層三維晶片之層識別電路及其方法 |

| TWI699761B (zh) * | 2015-03-04 | 2020-07-21 | 日商東芝記憶體股份有限公司 | 半導體裝置 |

| US9496042B1 (en) | 2015-05-21 | 2016-11-15 | Kabushiki Kaisha Toshiba | Semiconductor device with control of maximum value of current capable of being supplied |

| US20200066701A1 (en) * | 2016-09-28 | 2020-02-27 | Intel Corporation | Stacked chip package having substrate interposer and wirebonds |

| US10381088B2 (en) * | 2017-03-30 | 2019-08-13 | Silicon Storage Technology, Inc. | System and method for generating random numbers based on non-volatile memory cell array entropy |

| EP3493209A1 (en) * | 2017-11-29 | 2019-06-05 | IMEC vzw | An assembly of integrated circuit modules and method for identifying the modules |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IL96808A (en) * | 1990-04-18 | 1996-03-31 | Rambus Inc | Introductory / Origin Circuit Agreed Using High-Performance Brokerage |

| JP3659981B2 (ja) * | 1992-07-09 | 2005-06-15 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド | ダイ特定情報に特徴付けられるダイ上の集積回路を含む装置 |

| US5262488A (en) * | 1992-08-26 | 1993-11-16 | The Goodyear Tire & Rubber Company | Rubber vulcanization composition with bis-(2,5-polythio-1,3,4 thiadiazole) |

| JPH09504654A (ja) * | 1993-08-13 | 1997-05-06 | イルビン センサーズ コーポレーション | 単一icチップに代わるicチップ積層体 |

| JPH07283375A (ja) | 1994-04-15 | 1995-10-27 | Hitachi Maxell Ltd | 半導体メモリ装置 |

| US5640107A (en) * | 1995-10-24 | 1997-06-17 | Northrop Grumman Corporation | Method for in-circuit programming of a field-programmable gate array configuration memory |

| JPH1097463A (ja) | 1996-09-24 | 1998-04-14 | Hitachi Ltd | セレクトバス機能付き積層型半導体装置 |

| JP3563604B2 (ja) | 1998-07-29 | 2004-09-08 | 株式会社東芝 | マルチチップ半導体装置及びメモリカード |

| KR100308214B1 (ko) | 1998-12-30 | 2001-12-17 | 윤종용 | 듀얼칩반도체집적회로장치 |

| KR20000073345A (ko) * | 1999-05-10 | 2000-12-05 | 윤종용 | 본딩 옵션을 이용한 반도체 집적회로의 스택 패키지 집적회로 |

| JP3980807B2 (ja) | 2000-03-27 | 2007-09-26 | 株式会社東芝 | 半導体装置及び半導体モジュール |

| JP3779524B2 (ja) * | 2000-04-20 | 2006-05-31 | 株式会社東芝 | マルチチップ半導体装置及びメモリカード |

| US6417695B1 (en) * | 2001-03-15 | 2002-07-09 | Micron Technology, Inc. | Antifuse reroute of dies |

| JP2003060053A (ja) * | 2001-08-10 | 2003-02-28 | Fujitsu Ltd | 半導体チップ及びそれを用いた半導体集積回路装置及び半導体チップ選択方法 |

-

2001

- 2001-09-29 JP JP2001375022A patent/JP3959264B2/ja not_active Expired - Fee Related

-

2002

- 2002-09-26 TW TW091122148A patent/TW564526B/zh not_active IP Right Cessation

- 2002-09-27 US US10/255,960 patent/US6791175B2/en not_active Expired - Lifetime

- 2002-09-28 KR KR10-2002-0059094A patent/KR100506105B1/ko not_active IP Right Cessation

- 2002-09-29 CN CNB021440697A patent/CN1224102C/zh not_active Expired - Fee Related

-

2004

- 2004-07-30 US US10/902,291 patent/US6991964B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20030062612A1 (en) | 2003-04-03 |

| US6991964B2 (en) | 2006-01-31 |

| CN1411062A (zh) | 2003-04-16 |

| KR20030028412A (ko) | 2003-04-08 |

| KR100506105B1 (ko) | 2005-08-04 |

| JP2003110086A (ja) | 2003-04-11 |

| CN1224102C (zh) | 2005-10-19 |

| TW564526B (en) | 2003-12-01 |

| US6791175B2 (en) | 2004-09-14 |

| US20050001306A1 (en) | 2005-01-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3959264B2 (ja) | 積層型半導体装置 | |

| US9865359B2 (en) | Semiconductor device including fuse circuit | |

| US9922729B2 (en) | Soft post package repair of memory devices | |

| EP2920787B1 (en) | Three-dimensional flash memory system | |

| US7028234B2 (en) | Method of self-repairing dynamic random access memory | |

| TW506135B (en) | Semiconductor integrated circuit device | |

| TWI503834B (zh) | 儲存修復資料的方法及系統 | |

| CN106548807B (zh) | 修复电路、使用它的半导体装置和半导体系统 | |

| KR20100063770A (ko) | 멀티-다이 적층 장치에서 다이 적층 위치를 조정하는 시스템, 방법 및 장치 | |

| KR20220062104A (ko) | 적층 다이 상에서의 tsv 자동 리페어 스킴 | |

| US20240126692A1 (en) | Memory with post-packaging master die selection | |

| JP2012003797A (ja) | 半導体記憶装置 | |

| CN114694715A (zh) | 存储器装置、存储器系统及控制其存储器装置的方法 | |

| JP2001189082A (ja) | 半導体記憶装置 | |

| Wee et al. | A post-package bit-repair scheme using static latches with bipolar-voltage programmable antifuse circuit for high-density DRAMs | |

| US20050086564A1 (en) | Multi-chip module and method for testing | |

| US11256605B2 (en) | Nonvolatile memory device | |

| JPH0991991A (ja) | メモリモジュール | |

| JP2003123472A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050125 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050125 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061113 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061121 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061227 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070508 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070514 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110518 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110518 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120518 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120518 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130518 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130518 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140518 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |