JP3607033B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP3607033B2 JP3607033B2 JP07975697A JP7975697A JP3607033B2 JP 3607033 B2 JP3607033 B2 JP 3607033B2 JP 07975697 A JP07975697 A JP 07975697A JP 7975697 A JP7975697 A JP 7975697A JP 3607033 B2 JP3607033 B2 JP 3607033B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage side

- voltage

- low

- switching device

- side switching

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/687—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors

- H03K17/6871—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors the output circuit comprising more than one controlled field-effect transistor

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/53—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M7/537—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters

- H02M7/538—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters in a push-pull configuration

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/567—Circuits characterised by the use of more than one type of semiconductor device, e.g. BIMOS, composite devices such as IGBT

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Electronic Switches (AREA)

- Power Conversion In General (AREA)

- Control Of Electrical Variables (AREA)

- Dc-Dc Converters (AREA)

- Inverter Devices (AREA)

- Direct Current Feeding And Distribution (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置におけるパワーデバイスの駆動技術に関するものである。より具体的には、本発明は、ハーフブリッジ構成のパワーデバイスの単電源駆動回路に関する。

【0002】

【従来の技術】

ハーフブリッジ構成のパワーデバイスの単電源駆動回路は、図10に示すように、高圧直流電源1PとグランドGND間に直列に接続した2個のスイッチングデバイスQ2P,Q1Pと、これらのスイッチングデバイスQ2P,Q1Pをそれぞれ駆動する高圧側駆動回路(ゲートドライバ)2P及び低圧側駆動回路(ゲートドライバ)3Pとを備えており、2個のスイッチングデバイスQ1P,Q2Pを上記駆動回路3P,2Pによって交互にオン、オフさせるものである。

【0003】

従来のパワーデバイスの駆動回路においては、一方をグランドGNDに接続した低圧直流電源4Pから、その電圧VCCを低圧側駆動回路3Pに供給し、また低圧直流電源4PからダイオードDiPを通してコンデンサCPに充電した電圧を高圧側駆動回路3Pに供給している。通常、高圧直流電源1PとグランドGND間に直列に接続した2個のスイッチングデバイスQ2P,Q1Pには、それぞれダイオードD2P,D1Pが逆並列接続されている。これらのダイオードD1P,D2Pは、インダクタンスLの負荷時の誘導起電力の回生用として用いられる。

【0004】

図10の従来の駆動回路の動作原理は、次の通りである。即ち、(A)低圧側スイッチングデバイスQ1Pがオン状態の時に、低圧直流電源4Pから、ダイオードDiP、コンデンサCP、低圧側スイッチングデバイスQ1Pまたは、ダイオードD1Pから成る経路L1又はL2でコンデンサCPを充電しておき、(B)高圧側スイッチングデバイスQ2Pがオン状態の時に、ダイオードDiPが逆バイアスとなる結果、コンデンサCPをフローティング状態として、コンデンサCPに充電された電圧を高圧側駆動回路2Pに供給することとしている。

【0005】

【発明が解決しようとする課題】

しかしながら、図10に示した従来の駆動回路では、コンデンサCPの充電経路L1又はL2にそれぞれ低圧側スイッチングデバイスQ1Pまたは、低圧側のダイオードD1Pが存在するため、低圧側スイッチングデバイスQ1Pのオン電圧をVCE、ダイオードD1Pの順方向電圧をVF、ダイオードDiPの順方向電圧をVD、低圧直流電源4Pの電圧をVCCとして表わすと、コンデンサCPの充電VCは、以下の範囲となる。

【0006】

VC=(VCC−VD−VCE)〜(VCC−VD+VF)

このように、インダクタンスLの負荷時には、低圧側スイッチングデバイスQ1Pがオン状態で低圧側スイッチングデバイスQ1Pに電流が流れる時(経路1)と、ダイオードD1Pに電流が流れる時(経路L2)が存在する。

【0007】

通常は、低圧側スイッチングデバイスQ1Pのオン電圧VCEは2V程度であり、ダイオードD1Pの順方向電圧VFも2V程度である。従って、ダイオードDiPの順方向電圧VDを1V程度とするならば、コンデンサCPの充電電圧VCは、

VC=(VCC−3V)〜(VCC+1V)

の範囲で変化することになる。即ち、経路L1で電流が流れてコンデンサCPが充電されるときには、その充電電圧VCは低圧直流電源の電圧VCCよりも3Vも低い値となってしまう。

【0008】

この場合、15V駆動スイッチングデバイス(VCC=15V)では、充電電圧VCの範囲は12V〜16Vとなる。15V駆動時には、高圧側スイッチングデバイスQ1Pのオン時のゲート電圧は最小でも3Vあるので、この程度の充電電圧VCの変動は、使用可能な電圧範囲であると言える。

【0009】

ところが、5V駆動スイッチングデバイス(VCC=5V)では、VC=2V〜6Vとなり、その変動が大きすぎるために、本回路を使用することができないという問題が発生する。即ち、5V駆動時には、高圧側スイッチングデバイスQ1Pのオン時のゲート電圧は0.5〜0.75Vであるため、充電電圧VCがその駆動電圧5Vから3Vも低下するときには、スイッチングデバイスQ1Pがオンしても、オン抵抗が大となってしまい、スイッチングデバイスQ2Pでのロスが大きくなってしまう。それどころか、スイッチングデバイスQ2Pのドライブさえも制御できなくなる事態も生じうる。

【0010】

このように、ハーフブリッジ構成のパワーデバイスの従来の単電源駆動回路は、高圧側スイッチングデバイスの駆動回路に電圧を供給するためのコンデンサの充電経路に低圧側スイッチングデバイスまたは、低圧側スイッチングデバイスに逆並列接続されているダイオードが入っていることに起因して、充電電圧が大きく変化するという問題点を根本的に内包している。このため、従来回路を用いて5V駆動スイッチングデバイスを低圧直流電源電圧5Vで駆動することができないという問題点が生じている。この問題点は、最近のデバイスの低電圧化の傾向にとっては、克服すべき懸案事項と言える。

【0011】

本発明は、コンデンサの充電経路に低圧側スイッチングデバイスまたは、低圧側スイッチングデバイスに逆並列接続されているダイオードが存在していても、コンデンサの充電電圧を変化させない半導体装置の駆動回路技術を提供しようとするものである。

【0012】

また、本発明は、コンデンサの充電経路そのものに低圧側スイッチングデバイスや、低圧側スイッチングデバイスに逆並列接続されているダイオードが入らない回路構成を実現して、コンデンサの充電電圧を変化させないで、5V駆動スイッチングデバイスを低圧直流電源電圧5Vで使用することが可能な、半導体装置の駆動回路技術を、提供しようとするものである。

【0013】

【課題を解決するための手段】

請求項1に係る発明は、高圧直流電源にその第1電極が接続された高圧側スイッチングデバイスと、その第1及び第2端がそれぞれ前記高圧側スイッチングデバイスの制御電極及び第2電極に接続された高圧側駆動回路と、前記高圧側スイッチングデバイスの前記第2電極にその第1電極が接続され、その第2電極がグランドに接続された低圧側スイッチングデバイスと、その第1及び第2端がそれぞれ前記低圧側スイッチングデバイスの制御電極及び前記第2電極に接続された低圧側駆動回路とを備え、前記高圧側スイッチングデバイスと前記低圧側スイッチングデバイスとは、前記高圧側駆動回路と前記低圧側駆動回路とによって交互にその動作をオン、オフするように制御されており、ダイオードと、その一端及び他端がそれぞれ前記ダイオードのアノード及び前記グランドに接続された低圧直流電源と、その第1電極が前記ダイオードを介して前記低圧直流電源の前記一端に接続され且つ前記高圧側駆動回路の第3端にも接続されており、その第2電極が前記高圧側スイッチングデバイスの前記第2電極に接続されたコンデンサと、前記低圧側スイッチングデバイスの動作がオン状態にある間に成される前記コンデンサの充電期間中、前記コンデンサの両端間の電圧値を固定する電圧固定手段とを、更に備えることを特徴とする。

【0014】

しかも、請求項1に係る発明は、上記の半導体装置において、前記電圧固定手段は、そのカソードが前記コンデンサの前記第1電極に接続され、そのアノードが前記コンデンサの前記第2電極に接続された、ツェナーダイオードを備え、前記低圧直流電源の電圧は、前記ツェナーダイオードのツェナー電圧と前記ダイオードの順方向電圧と前記低圧側スイッチングデバイスのオン電圧との和よりも大きく設定されていることを特徴とする。

【0015】

請求項2に係る発明は、請求項1記載の半導体装置において、前記低圧側スイッチングデバイスの前記第1及び第2電極にそのカソード及びアノードがそれぞれ接続された低圧側ダイオードと、前記ダイオードのカソード及び前記コンデンサの前記第1電極にその一端及び他端が接続された抵抗とを、更に備えることを特徴とする。

【0016】

請求項3に係る発明は、高圧直流電源にその第1電極が接続された高圧側スイッチングデバイスと、その第1及び第2端がそれぞれ前記高圧側スイッチングデバイスの制御電極及び第2電極に接続された高圧側駆動回路と、前記高圧側スイッチングデバイスの前記第2電極にその第1電極が接続され、その第2電極がグランドに接続された低圧側スイッチングデバイスと、その第1及び第2端がそれぞれ前記低圧側スイッチングデバイスの制御電極及び前記第2電極に接続された低圧側駆動回路とを備え、前記高圧側スイッチングデバイスと前記低圧側スイッチングデバイスとは、前記高圧側駆動回路と前記低圧側駆動回路とによって交互にその動作をオン、オフするように制御されており、前記低圧側スイッチングデバイスの前記第1及び第2電極にそのカソード及びアノードがそれぞれ接続された低圧側ダイオードと、ダイオードと、その一端及び他端がそれぞれ前記ダイオードのアノード及び前記グランドに接続された低圧直流電源と、前記ダイオードのカソードと前記グランドと前記高圧側駆動回路の第3端とに接続され、前記低圧側スイッチングデバイスの動作がオン状態にある間に、前記低圧側スイッチングデバイスと前記低圧側ダイオードとを介在させることなく、前記低圧直流電源から供給される、前記高圧側スイッチングデバイスを駆動するのに必要な電荷を自ら充電する一方、前記高圧側スイッチングデバイスの動作がオン状態にあるときに前記電荷に対応した充電電圧を前記高圧側駆動回路に供給する充電電圧供給手段とを、更に備えることを特徴とする。

【0017】

請求項4に係る発明は、請求項3記載の半導体装置において、前記ダイオードを第1ダイオードとすると、前記充電電圧供給手段は、前記第1ダイオードの前記カソードにその第1電極が接続された第1コンデンサと、前記第1コンデンサの第2電極と前記グランドとの間に配設され、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオンに制御され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオフに制御される、第1スイッチと、そのアノード及びカソードが前記第1ダイオードの前記カソード及び前記高圧側駆動回路の前記第3端にそれぞれ接続された第2ダイオードと、その第1及び第2電極が前記高圧側駆動回路の前記第3端及び前記第2端にそれぞれ接続された第2コンデンサと、前記第1コンデンサの前記第2電極と前記第2コンデンサの前記第2電極との間に配設され、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオフに制御され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオンに制御される、第2スイッチとを、備えることを特徴とする。

【0018】

請求項5に係る発明は、請求項4記載の半導体装置において、前記第2ダイオードに代えて、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオフに制御され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオンに制御される、第3スイッチを、備えることを特徴とする。

【0019】

請求項6に係る発明は、高圧直流電源にその第1電極が接続された高圧側スイッチングデバイスと、その第1及び第2端がそれぞれ前記高圧側スイッチングデバイスの制御電極及び第2電極に接続された高圧側駆動回路と、前記高圧側スイッチングデバイスの前記第2電極にその第1電極が接続され、その第2電極がグランドに接続された低圧側スイッチングデバイスと、その第1及び第2端がそれぞれ前記低圧側スイッチングデバイスの制御電極及び前記第2電極に接続された低圧側駆動回路とを備え、前記高圧側スイッチングデバイスと前記低圧側スイッチングデバイスとは、前記高圧側駆動回路と前記低圧側駆動回路とによって交互にその動作をオン、オフするように制御されており、前記低圧側スイッチングデバイスの前記第1及び第2電極にそのカソード及びアノードがそれぞれ接続された低圧側ダイオードと、ダイオードと、その一端及び他端がそれぞれ前記ダイオードのアノード及び前記グランドに接続された低圧直流電源と、前記ダイオードのカソードと前記グランドと前記高圧側駆動回路の第3端とに接続され、前記高圧側スイッチングデバイスの動作がオン状態にある間に、前記低圧側スイッチングデバイスと前記低圧側ダイオードとを介在させることなく、前記低圧直流電源から供給される、前記高圧側スイッチングデバイスを駆動するのに必要な電荷を自ら充電する一方、前記低圧側スイッチングデバイスの動作がオン状態にあるときに前記電荷に対応した充電電圧を前記高圧側駆動回路に供給する充電電圧供給手段とを、更に備えることを特徴とする。

【0020】

請求項7に係る発明は、請求項6記載の半導体装置において、前記ダイオードを第1ダイオードとすると、前記充電電圧供給手段は、前記第1ダイオードの前記カソードにその第1電極が接続された第1コンデンサと、前記第1コンデンサの第2電極と前記グランドとの間に配設され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオンに制御され、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオフに制御される、第1スイッチと、そのアノード及びカソードが前記第1ダイオードの前記カソード及び前記高圧側駆動回路の前記第3端にそれぞれ接続された第2ダイオードと、その第1及び第2電極が前記高圧側駆動回路の前記第3端及び前記第2端にそれぞれ接続された第2コンデンサと、前記第1コンデンサの前記第2電極と前記第2コンデンサの前記第2電極との間に配設され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオフに制御され、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオンに制御される、第2スイッチとを、備えることを特徴とする。

【0021】

請求項8に係る発明は、請求項4,5及び7のいずれかに記載の半導体装置において、前記低圧直流電源の電圧を、前記高圧側スイッチングデバイスの駆動電圧に前記第1ダイオードの順方向電圧分だけを加えた値に設定することを特徴とする。

【0022】

請求項9に係る発明は、高圧直流電源にその第1電極が接続された高圧側スイッチングデバイスと、その第1及び第2端がそれぞれ前記高圧側スイッチングデバイスの制御電極及び第2電極に接続された高圧側駆動回路と、前記高圧側スイッチングデバイスの前記第2電極にその第1電極が接続され、その第2電極がグランドに接続された低圧側スイッチングデバイスと、その第1及び第2端がそれぞれ前記低圧側スイッチングデバイスの制御電極及び前記第2電極に接続された低圧側駆動回路と、前記低圧側スイッチングデバイスの前記第1及び第2電極にそのカソード及びアノードがそれぞれ接続された低圧側ダイオードと、前記高圧側駆動回路の第3端及び前記第2端との間に並列に接続されたコンデンサと、低圧直流電源をソースとし、スイッチング手段を備える、前記コンデンサの充電経路とを備え、前記高圧側スイッチングデバイスと前記低圧側スイッチングデバイスとを、前記高圧側駆動回路と前記低圧側駆動回路とによって交互にオン、オフするように制御すると共に、前記高圧側スイッチングデバイス及び前記低圧側スイッチングデバイスの動作状態に応じて前記スイッチング手段の動作をオン、オフに交互に切り換え制御することにより、前記低圧側スイッチングデバイス及び前記低圧側ダイオードを介在させることなく、前記充電経路より、前記高圧側スイッチングデバイスを駆動するのに必要な電圧を前記コンデンサに充電することを特徴とする。

【0023】

【発明の実施の形態】

この発明は、大別して、次の2つの基本的な技術的思想を有している。

【0024】

(I) その第一は、コンデンサに充電したい電圧をツェナーダイオードのツェナー電圧で決定してしまい、コンデンサの充電経路に入っている低圧側スイッチングデバイスまたは、低圧側スイッチングデバイスに逆並列接続されているダイオードの影響による変化分以上だけ、コンデンサの充電電圧よりも高い電圧を有する低圧直流電源を使用する点にある。

【0025】

(II) その第二は、コンデンサの充電経路中に低圧側スイッチングデバイスまたは、低圧側スイッチングデバイスに逆並列接続されているダイオードが含まれることを防止すると共に、他のスイッチ手段を設けて、低圧側スイッチングデバイス及び高圧側スイッチングデバイスのそれぞれのオンのタイミングで上記スイッチ手段をオン、オフすることにより、コンデンサを充電する点にある。この構成を用いるときには、後述するように、コンデンサの充電電圧の変化を従来よりも格段に小さくすることができる。

【0026】

以下に示す実施の形態1〜3の内で、実施の形態1は上記構成(I)に基づくものであり、実施の形態2,3は共に上記構成(II)に立脚するものである。

【0027】

(実施の形態1)

以下、本発明の実施の形態1について、図面を参照しつつ詳細に説明する。

【0028】

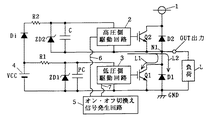

図1は、実施の形態1に係る半導体装置の構成を示す図である。本装置は、ハーフブリッジ構成のパワーデバイスの単電源駆動回路に関する。

【0029】

本装置は、高圧直流電源1とグランドGND間にこの順序で直列に接続された2個のスイッチングデバイスQ2,Q1と、2個のスイッチングデバイスQ2,Q1にそれぞれ逆並列接続されたダイオードD1,D2と、2個のスイッチングデバイスQ2,Q1をそれぞれ駆動するゲートドライバ、即ち、高圧側駆動回路2及び低圧側駆動回路3とを備えている。

【0030】

これらの内で、スイッチングデバイスQ2,Q1をそれぞれ「高圧側スイッチングデバイスないし第2スイッチングデバイス」,「低圧側スイッチングデバイスないし第1スイッチングデバイス」とも称し、又、ダイオードD2,D1をそれぞれ「高圧側ダイオード」、「低圧側ダイオード」とも称す。そして、上記デバイスQ2,D2の端子の内で高圧直流電源1に接続されたものをそれぞれ「第1電極」,「第2電極(カソード)」と定義し、上記デバイスQ2,D2の他方の端子、即ち、デバイスQ2の基準電位ノードN1(出力端子OUT)側の端子を、それぞれ「第2電極」,「第1電極(アノード)」と定義する。又、高圧側駆動回路2の第1端に接続されている上記デバイスQ2の端子を「制御電極」と定義する。以後、上記基準電位ノードN1を、単に「ノードN1」と称す。

【0031】

上記デバイスQ1,D1についても同様に、上記ノードN1に接続された端子をそれぞれ「第1電極」,「第2電極(カソード)」と定義し、グランドGNDに接続された他方の端子をそれぞれ「第2電極」,「第1電極(アノード)」と定義する。両スイッチングデバイスQ1,Q2は、例えばIGBTやパワーMOSトランジスタ等よりなる。

【0032】

尚、記号PCは、パスコンを示す。

【0033】

2個のスイッチングデバイスQ1,Q2の動作は、外部のオン・オフ切替え信号発生回路5が生成・出力するオン・オフ切替信号6,7(信号7は信号6の逆相信号である)に応じて、交互にオン、オフされる。

【0034】

一端をグランドGNDに接続された低圧直流電源4(その電圧値はVCC)から、第1抵抗R1を通して、その第1電極(アノード)がグランドGNDに接続された第1ツェナーダイオード(ないし低圧側ツェナーダイオード)ZD1に電流を流す。その結果発生する、第1ツェナーダイオードZD1の第2電極(カソード)と第1電極間の電圧を低圧側駆動回路3に供給する。

【0035】

他方、低圧直流電源4からダイオードDi、第2抵抗R2を通して、その第1電極(アノード)が高圧側スイッチングデバイスQ2の基準電位(出力)のノードN1に接続された第2ツェナーダイオード(ないし高圧側ツェナーダイオード)ZD2に電流を流し、第2ツェナーダイオードZD2の第2電極(カソード)と第1電極間に生ずる電圧を、第2ツェナーダイオードZD2に並列に接続されたコンデンサCを介して高圧側駆動回路2に供給する。尚、コンデンサCの第1電極と接続された高圧側駆動回路2の端子を「第3端」とし、コンデンサCの第2電極と接続された高圧側駆動回路2の端子を「第2端」と定義する。

【0036】

ここでは、第1及び第2ツェナーダイオードZD1,ZD2とも、そのツェナー電圧が5V程度になるものが用いられる。

【0037】

次に、本装置におけるパワーデバイスの駆動動作について説明する。

【0038】

(A) 低圧側スイッチングデバイスQ1がオン状態にある時:

低圧直流電源4からダイオードDi、第2抵抗R2を通してコンデンサC、低圧側スイッチングデバイスQ1または、低圧側ダイオードD1に至る充電経路(L1,L2)によって、コンデンサCに、第2ツェナーダイオードZD2の両電極間に生ずる電圧(即ち、ツェナー電圧)で定まる電荷を充電する。従って、コンデンサCの充電電圧は一定である。

【0039】

(B) 高圧側スイッチングデバイスQ2がオン状態にある時:

ダイオードDiが逆バイアス状態となるので、コンデンサCはフローティング状態となり、コンデンサCに充電された電圧は高圧側駆動回路2の第3端に供給される。

【0040】

ここで、低圧側スイッチングデバイスQ1のオン電圧をVCE、低圧側ダイオードD1の順方向電圧をVF、ダイオードDiの順方向電圧をVD、第2ツェナーダイオードZD2のツェナー電圧をVZD2、低圧直流電源の電圧をVCCとして表わすと、上記電圧VCCを、

VCC>VZD2+VD+VCE…(1)式

に設定することにより、コンデンサCの充電電圧VCを、常にVC=VZD2に設定することができる。尚、コンデンサCが充電された後は、第2抵抗R2には電流が流れなくなるので、電圧VCCを設定する際の限界点を考えるときには、第2抵抗R2での電圧を0Vとして扱うことができる。第2抵抗R2自体は、低圧側ダイオードD1に電流が流れたときの電圧分を補償する部分である。

【0041】

他方、上記(1)式に基づき、低圧直流電源4の電圧VCCを通常のパワーデバイスの駆動電圧(5V)よりも高い値に設定しているので、低圧側駆動回路3に供給される電圧は、低圧直流電源4から第1抵抗R1を通して第1ツェナーダイオードZD1に至る経路によって供給され、その供給電圧は、第1ツェナーダイオードZD1のツェナー電圧VZD1、従って、VZD1=VZD2となる。即ち、第1抵抗R1の値は、上記供給電圧がツェナー電圧VZD1(=VZD2)となるように設定されている。

【0042】

以上により、高圧側駆動電源のコンデンサCの充電電圧の変動を0Vとすることができ、5V駆動スイッチングデバイスを安定して駆動することが可能となる。

【0043】

なお、第2ツェナーダイオードZD2は、低圧側スイッチングデバイスQ1をオン状態にしてコンデンサCを充電中に、コンデンサの両端間の電圧を固定する手段であると言える。

【0044】

以上より、図1の第2ツェナーダイオードZD2は、低圧側スイッチングデバイスQ1の動作がオン状態にある間に成されるコンデンサCの充電期間中、コンデンサCの両端間の電圧値を固定する電圧固定手段であると言える。

【0045】

(実施の形態2)

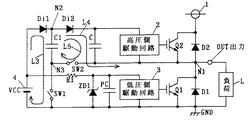

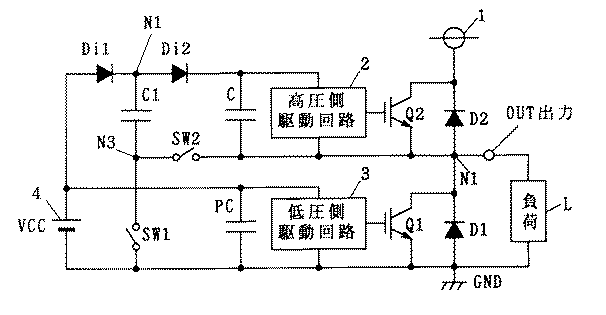

図2は、本発明の実施の形態2に係る半導体装置を示す図である。

【0046】

同図2の装置が図1の装置と異なる点は、第2ツェナーダイオードZD2と第2抵抗R2とに代えて、第1コンデンサC1と、第1及び第2ダイオードDi1,Di2と、第1及び第2スイッチSW1,SW2とを設けた点にある。その他の構成は同じである。即ち、第1ダイオードDi1のカソードと第2ダイオードDi2のアノードとの接続ノードに第1コンデンサC1の第1電極が接続され、第1コンデンサC1の第2電極と第1スイッチSW1の第1端との接続ノードN3に第2スイッチSW2の第1端が接続され、第1及び第2スイッチSW1,SW2の第2端は、それぞれグランドGND及びノードN1に接続されている。ここでは、図1のコンデンサCを、第2コンデンサCと定義する。

【0047】

尚、図2では、図1で図示した外部のオン・オフ切替信号発生回路5の図示化を省略している。以下の他の実施の形態でも、当該回路5の図示化を同様に省略している。

【0048】

低圧直流電源4(その電圧はVCC)から第1抵抗R1を通して第1ツェナーダイオードZD1に印加される電圧、即ちツェナー電圧VZD1(=5V)を、低圧側駆動回路3に供給することとしている。

【0049】

他方、第1スイッチSW1のオン、第2スイッチSW2のオフにより、低圧直流電源4から第1ダイオードDi1を通して第1コンデンサC1と第1スイッチSW1とにより形成される充電経路L3によって第1コンデンサC1を充電し、次に、第2スイッチSW2のオン,第1スイッチSW1のオフにより第1コンデンサC1から第2ダイオードDi2を通して第2コンデンサCに充電し、第2コンデンサCの充電電圧を高圧側駆動回路2に供給するようにしている。

【0050】

以下に、動作について説明する。但し、図2の回路では、駆動方法として2つの方法が考えられるので、それらを方法(A),(B)として順次に説明する。

【0051】

(第1方法A)

第1ダイオードDi1、第2ダイオードDi2の順方向電圧をいずれもVDとして表わし、第1スイッチSW1、第2スイッチSW2のオン電圧をOVであるものとする。

【0052】

(a) 高圧側スイッチングデバイスQ2がオン状態のとき:

第1スイッチSW1をオンに、第2スイッチSW2をオフに制御する。このとき、低圧直流電源4から、各素子Di1,C1,SW1より成る充電経路L3によって、第1コンデンサC1は充電される。その充電電圧VC1は、

VC1=VCC−VD

となる。このとき、第2スイッチSW2がオフであるので、充電経路L3には、低圧側スイッチングデバイスQ1や、低圧側ダイオードD1は、入らない。従って、従来技術のような充電圧VC1の変動は生じない。

【0053】

このタイミングでは、(a)よりも前の(b)の動作によって既に第2コンデンサCに充電されている電圧VCにより、高圧側駆動回路2が動作する。このとき、高圧側スイッチングデバイスQ2がオン状態にあるので、高圧側スイッチングデバイスQ2の出力の電位は高く、第2のコンデンサCはフローティング状態にある。

【0054】

(b) 次に、低圧側スイッチングデバイスQ1がオン状態のとき:

第1スイッチSW1をオフに、第2スイッチSW2をオンに制御する。このときの充電経路は、▲1▼低圧直流電源4から各素子Di1,Di2,Cを経て低圧側スイッチングデバイスQ1または、低圧側ダイオードD1から成る第1の経路L4と、▲2▼第1コンデンサC1から各素子Di2,Cを経て第2スイッチSW2に至る第2の経路L5とがある。それぞれの経路L4,L5での充電電圧VCは、VCE=VF=2V,VD=1Vとすると、次の通りとなる。

【0055】

先ず第1の経路L4では、

VC=(VCC−2*VD−VCE)〜(VCC−2*VD+VF)=(VCC−4V)〜VCC

となる。他方、第2の経路L5では、

VC=VC1−VD=VCC−2*VD=VCC−2V

となる。

【0056】

このとき、第1の経路L4での充電電圧VCが、

VC=(VCC−4V)〜(VCC−2V)

となるときは、第2の経路L5による充電電圧VCの方がその電圧のレベルが高いので、第1ダイオードDi1が逆バイアス状態となり、第1コンデンサC1から上記の第2経路L5を介してのみ、第2コンデンサCは充電されることとなる。その結果、充電電圧VCは、

VC=(VCC−2V)〜VCC…(2)式

となる。

【0057】

したがって、上記(2)式を踏まえて、低圧直流電源4の電圧VCCを予め高圧側スイッチングデバイスQ1の駆動電圧の最適値(例えば5V)よりも1Vだけ高く設定しておけば(上記(2)式のVCCをVCC+1Vに置き換えれば)、高圧側駆動回路2への供給電圧の変動を±1Vにすることができる。つまり、低圧直流電源4の電圧VCCを、高圧側スイッチングデバイスQ2の駆動電圧(5V)に第1ダイオードDi1の順方向電圧VD分だけを加えた値に設定すれば、供給電圧の変動分は±1Vに抑えられる。

【0058】

低圧側駆動回路3への電圧供給は、低圧直流電源2から抵抗R1を介してツェナーダイオードZD1に至る経路によって行われる。この場合、低圧側スイッチングデバイスQ1の駆動電圧の最適値(5V)に等しいツェナー電圧を有するツェナーダイオードZD1が用いられている。従って、VCC=5V+1Vとすれば、抵抗R1での電圧が1Vとなるように、抵抗R1の値が設定される。

【0059】

図3に、上記の動作のタイミングチャートを示す。

【0060】

以上より、ここでは、各素子C1,SW1,Di2,SW2が、ダイオードDi1のカソードとグランドGNDと高圧側駆動回路2の第3端とに接続され、高圧側スイッチングデバイスQ2の動作がオン状態にある間に、低圧側スイッチングデバイスQ1と低圧側ダイオードD1とを介在させることなく、低圧直流電源4から供給される、高圧側スイッチングデバイスQ2を駆動するのに必要な電荷を自ら充電する一方、低圧側スイッチングデバイスQ1の動作がオン状態にあるときに前記電荷に対応した充電電圧を高圧側駆動回路2に供給する、充電電圧供給手段を構成していると言える。

【0061】

(B) 次に、図2の回路の第2の駆動方法による場合の動作について説明する。第1ダイオードDi1、第2ダイオードDi2の順方向電圧をいずれもVDとし、第1スイッチSW1、第2スイッチSW2のオン電圧を共にOVとする。

【0062】

(a) 低圧側スイッチングデバイスQ1がオン状態のとき:

第1スイッチSW1をオンに、第2スイッチSW2をオフにそれぞれ制御する。このとき、低圧直流電源4から各素子Di1,C1,SW1に至る充電経路L3により、第1コンデンサC1は充電され、その充電電圧VC1は、

VC1=VCC−VD

となる。このとき、第2スイッチSW2がオフであるので、充電経路L3に低圧側スイッチングデバイスQ1や、低圧側ダイオードD1は、入らない。従って、充電電圧VC1の変動要因が防止される。

【0063】

このタイミングでは、第2コンデンサCに充電された電圧VCにより、高圧側駆動回路2が動作する。しかし、このときには高圧側スイッチングデバイスQ2がオフ状態にあるので、出力端OUT(ノードN1)の電位は低く、第2コンデンサCは、低圧直流電源4から各素子Di1,Di2,Cを経て低圧側スイッチングデバイスQ1または、低圧側ダイオードD1に至る経路で充電され、その充電電圧VCは、VCE=VF=2V,VD=1Vとすると、

VC=(VCC−2*VD−VCE)〜(VCC−2*VD+VF)=(VCC−4V)〜VCC

となる。充電電圧VCは、最悪のケースでは(VCC−4V)となるが、高圧側スイッチングデバイスQ2がオフ状態にあるので、全く問題は生じない。

【0064】

(b) 高圧側スイッチングデバイスQ2がオン状態のとき:

第1スイッチSW1をオフに、第2スイッチSW2をオンにそれぞれ制御する。このとき、第2コンデンサCは、第1コンデンサC1から各素子Di2,C及びSW2に至る充電経路で充電され、その充電電圧VCは、VD=1Vとすると、

VC=VC1−VD=VCC−2*VD=VCC−2V

となる。このとき、第2コンデンサCの充電電圧VCが、

VC=(VCC−4V)〜(VCC−2V)

の範囲内にあるときにのみ、第1ダイオードDi1が逆バイアスとなり、第1コンデンサC1から各素子Di2,C,SW2に至る充電経路L5によってのみ、第2コンデンサCは充電され、その充電電圧VCは、

VC=(VCC−2V)〜VCC…(3)式

となる。

【0065】

したがって、上記(3)式を踏まえて、低圧直流電源4の電圧VCCを、高圧側スイッチングデバイスQ2の駆動電圧の最適値(例:5V)よりも1Vだけ高く設定すれば(つまり、上記最適値よりも第1ダイオードDi1の順方向電圧VD分だけ高く設定すれば)、高圧側駆動回路2への供給電圧の変動を±1Vにすることができる。

【0066】

上述の動作のタイミングチャートを、図4に示す。

【0067】

本方法(B)では、図2の各素子C1,SW1,Di2,SW2からなる部分は、ダイオードDi1のカソードとグランドGNDと高圧側駆動回路2の第3端とに接続され、低圧側スイッチングデバイスQ1の動作がオン状態にある間に、低圧側スイッチングデバイスQ1と低圧側ダイオードD1とを介在させることなく、低圧直流電源4から供給される、高圧側スイッチングデバイスQ2を駆動するのに必要な電荷を自ら充電する一方、高圧側スイッチングデバイスQ2の動作がオン状態にあるときに前記電荷に対応した充電電圧を高圧側駆動回路2に供給する、充電電圧供給手段を構成していると言える。

【0068】

以上のように、上記(A)の方法では、高圧側スイッチングデバイスQ2の動作状態をオンに制御している間に第1コンデンサC1を充電し、低圧側スイッチングデバイスQ1のオン動作時に、第2コンデンサCを充電して、この充電電圧を、次の高圧側スイッチングデバイスQ2のオン動作時に上記回路2に供給している。他方、上記(B)の方法では、低圧側スイッチングデバイスQ1のオン時に第1コンデンサC1を充電し、高圧側スイッチングデバイスQ2のオン時に、第2コンデンサCの充電、従って、高圧側駆動回路2への充電電圧の供給を実行している。

【0069】

上記(A),(B)のスイッチング制御を、表1,表2に整理して示す。

【0070】

【表1】

【0071】

【表2】

【0072】

なお、低圧側スイッチングデバイスQ1がオン状態のときに、第1スイッチSW1をオンまたはオフに制御すればよいので、低圧側駆動回路3が出力する、低圧側スイッチングデバイスQ1をオンとするための信号を第1スイッチSW1の制御信号に用いることができる。これにより、容易に第1スイッチSW1をオン、オフに制御することができる。又、第2スイッチSW2については、高圧側スイッチングデバイスQ2がオン状態のときに、第2スイッチSW2をオンまたはオフにすればよいので、高圧側駆動回路2が高圧側スイッチングデバイスQ2をオンとするために出力する信号を第2スイッチSW2用の制御信号に用いることで、容易に第2スイッチSW2をオン、オフに制御することができる。

【0073】

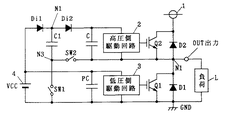

(実施の形態2の変形例)

(1) 図5は、図2の回路の変形例であり、図2の第1抵抗R1を取り除いたものに対応する。即ち、図5の回路は、低圧側駆動回路3への電圧供給を低圧直流電源4より直接に供給したものであり、ここでは、同電源4の供給電圧VCCは高圧側,低圧側スイッチングデバイスQ2,Q1の駆動電圧の最適値(例:5V)よりも1Vだけ高くなるが、実用上、特に問題となることはない。この構成により、回路構成を簡略化することができる。

【0074】

(2) 図6の回路も同じく図2の回路の変形例であり、図2の第1抵抗R1を第3ダイオードDi3に置換したものである。即ち、低圧側駆動回路3への供給電圧VCCを第3ダイオードDi3を通して供給したものであり、第3ダイオードDi3の順方向電圧VDを1Vとすると、低圧側駆動回路3への供給電圧は、

VCC−VD=VCC−1V

となり、高圧側・低圧側スイッチングデバイスQ2,Q1の駆動電圧の最適値(例:5V)を低圧側駆動回路3に供給することができる。

【0075】

(3) 図2、図5、図6に示した実施の形態1の各回路において、第1、第2スイッチSW1,SW2をMOSFETを用いて構成することができる。この場合には、図2、図5、図6で、第1、第2コンデンサC1,C、低圧直流電源4および負荷L以外の部分をモノリシックIC化することができる。また、具体的には、第1、第2スイッチSW1,SW2をNch−MOSFETで構成することで、第1スイッチSW1のNch−MOSFETを、低圧直流電源4の電圧値VCCまたは、低圧側駆動回路3への供給電圧で以て駆動することができ、第2スイッチSW2のNch−MOSFETを第2のコンデンサCの充電電圧により駆動することができる。

【0076】

(実施の形態3)

図7は、本発明の実施の形態3に係る半導体装置の構成を示す図である。図7の回路が図2の回路と相違する点は、図2の第2ダイオードDi2に代えて、第3スイッチSW3を設けた点にある。その他の構成は、図2の場合と同一である。

【0077】

本回路の動作について説明する。ここでは、第1ダイオードDi1の順方向電圧をVDとして表わし、第1スイッチSW1、第2スイッチSW2、及び第3スイッチSW3のオン電圧を全てOVであるものとする。

【0078】

(a) 低圧側スイッチングデバイスQ1がオン状態のとき:

第1スイッチSW1をオンに、第2及び第3スイッチSW2,SW3をオフに、制御する。このとき、低圧直流電源4から各素子Di1,C1,SW1に至る充電経路L6により、第1コンデンサC1は充電され、その充電電圧VC1は、

VC1=VCC−VD=VCC−1V

となる。このとき、第2及び第3スイッチSW2,SW3がオフであるので、充電経路L6に低圧側スイッチングデバイスQ1や、低圧側ダイオードD1は、入らない。

【0079】

このタイミングでは、第2コンデンサCに充電された電圧VCにより高圧側駆動回路2が動作する。しかし、このとき高圧側スイッチングデバイスQ2がオフ状態にあるので、出力端子OUT(ノードN1)の電位は低いが、第2、第3スイッチSW2,SW3が共にオフであるので、高圧側スイッチングデバイスQ2はオフ状態を維持する。

【0080】

(b) 高圧側スイッチングデバイスQ2がオン状態のとき:

第1スイッチSW1をオフに、第2、第3スイッチSW2,SW3を共にオンに制御する。ダイオードDi1は逆バイアス状態となり、このときの充電経路は、第1コンデンサC1から各素子SW3,C,SW2に至る経路L7のみとなる。この場合の充電電圧VCは、VD=1Vとすると、

VC=VC1=VCC−VD=VCC−1V

となる。この第2コンデンサCの充電電圧VCにより、高圧側駆動回路2が動作し、高圧側スイッチングデバイスQ2をオン状態にする。

【0081】

したがって、低圧直流電源4の電圧VCCを高圧側,低圧側スイッチングデバイスQ2,Q1の駆動電圧の最適値(例:5V)よりも1V高く設定することで(つまり、上記最適値よりもダイオードDi1の順方向電圧VD部分だけ高く設定することで)、高圧側駆動回路2への供給電圧を上記最適値に固定することができる。その意味では、各素子C1,SW1,SW2,SW3より成る部分は、高圧側スイッチングデバイスQ2がオンにある間に、第2コンデンサCを充電し、しかも、その充電電圧を一定値にする手段であると言える。

【0082】

又、各素子C1,SW1,SW2,SW3は、ダイオードDi1のカソードとグランドGNDと高圧側駆動回路2の第3端とに接続され、低圧側スイッチングデバイスQ1の動作がオン状態にある間に、低圧側スイッチングデバイスQ1と前記低圧側ダイオードD1とを介在させることなく、低圧直流電源4から供給される、高圧側スイッチングデバイスQ2を駆動するのに必要な電荷を自ら充電する一方、高圧側スイッチングデバイスQ2の動作がオン状態にあるときに前記電荷に対応した充電電圧を高圧側駆動回路2に供給する、充電電圧供給を構成しているとも言える。

【0083】

ここでのスイッチング制御方法を、表3に整理して示す。

【0084】

【表3】

【0085】

低圧側駆動回路3への電圧供給は、低圧直流電源4より抵抗R1を介してツェナーダイオードZD1に至る経路により行われる。両スイッチングデバイスQ1,Q2の駆動電圧の最適値(例:5V)に等しいツェナー電圧VZD1が、上記回路3に供給される。

【0086】

また、第1スイッチSW1については、低圧側スイッチングデバイスQ1がオン状態のときに、第1スイッチSW1をオンにすればよいので、低圧側駆動回路3が出力する、低圧側スイッチングデバイスQ1のオン信号を用いて容易に第1スイッチSW1をオン、オフに制御することができる。

【0087】

第2、第3スイッチSW2,SW3については、高圧側スイッチングデバイスQ2がオン状態のときに、第2、第3スイッチSW2,SW3を共にオンにすればよいので、高圧側駆動回路2が出力する、高圧側スイッチングデバイスQ2をオンとするための信号を用いて、容易に第2、第3スイッチSW2,SW3を共にオン、オフに制御することができる。

【0088】

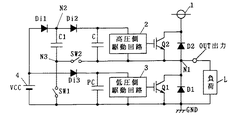

(実施の形態3の変形例)

(1) 図8の回路は、図7の回路に対して、図2の回路から図5の回路への変形と同じ変形を適用して得られたものであり、これにより図7の回路についても図5の回路のもつ特有な利点を発揮させることができる。従って、図8の構成により、回路構成を簡略化することができる。

【0089】

(2) 図9の回路は、図2の回路から図6の回路への変形と同一の変形を図7の回路に適用したものである。従って、ダイオードDi3の順方向電圧VDを1Vとすると、低圧側駆動回路3への供給電圧は、

VCC−VD=VCC−1V

となり、両スイッチングデバイスQ1,Q2の駆動電圧の最適値(例:5V)をダイオード1個で以て供給することができる。

【0090】

(3) 図7、図8、図9の各回路において、第1、第2、及び第3のスイッチSW1,SW2,SW3をMOSFETを用いて構成することができ、第1、第2コンデンサC1,Cと、低圧直流電源4と負荷L以外の部分をモノリシックIC化することが実現できる。

【0091】

また、具体的には第1、第2スイッチSW1,SW2をNch−MOSFETで、第3スイッチSW3をPch−MOSFETでそれぞれ構成することで、第1スイッチSW1のNch−MOSFETは、低圧直流電源4の電圧VCCまたは、低圧側駆動回路3への供給電圧で以て、第2、第3スイッチSW2,SW3のNch−MOSFET、及びPch−MOSFETを第2コンデンサCの充電電圧により、駆動することができる。

【0092】

(まとめ)

以上のように、本発明の実施の形態2,3によれば、高圧側駆動回路2の電源とするコンデンサCを充電するのに、低圧側スイッチングデバイスQ1、低圧側ダイオードD1の経路が介在しなくなるので、又、実施の形態1では充電電圧をツェナー電圧に固定してしまうので、コンデンサCの充電電圧VCの変動を、図1の実施の形態1では0Vに、図2、図5、図6の実施の形態2では±1V内に、図7、図8、図9の実施の形態3では0Vとすることができ、コンデンサCの充電電圧の変動の小さい、又は全く変動のないハーフブリッジ構成のパワーデバイスの単電源駆動回路を実現できる。従って、低圧直流電源の電圧を各実施の形態1〜3に応じて所定の値に設定するならば、5V駆動スイッチングデバイスを低圧直流電源電圧5Vで以て使用することが可能な、ハーフブリッジ構成のパワーデバイスの単電源駆動回路を実現することができる。

【0093】

【発明の効果】

請求項1ないし2の各発明によれば、コンデンサの充電経路中に低圧側スイッチングデバイスが存在していても、それによる影響を受けることなく、充電中、常にコンデンサの両端間の電圧を一定に固定することができる。従って、本装置を、低圧駆動スイッチングデバイスを低圧直流電源で駆動する場合、例えば5V駆動スイッチングデバイスを5Vの低圧直流電源によって駆動するという場合にも、何ら問題なく適用することが可能になる。

【0094】

特に、請求項2の発明では、抵抗を設けることによって、コンデンサの充電経路中に低圧側ダイオードが存在する場合でも、当該低圧側ダイオードで生ずる電圧を上記抵抗で生ずる電圧降下によって補償できるという利点がある。勿論、上記低圧側ダイオードを含む充電経路でコンデンサが充電されているときでも、常にコンデンサの充電電圧を一定にすることができる。

【0095】

請求項3ないし9に記載の各発明によれば、低圧側スイッチングデバイス及び低圧側ダイオードの影響を受けることなく高圧側スイッチングデバイスを駆動するのに必要な電荷を充電することができるので、高圧側駆動回路への供給電圧の変動を、従来よりも格段に小さくすることができる。これにより、5V駆動スイッチングデバイスを5Vの低圧直流電源で以て駆動する場合にも、本発明を適用することが可能となる。

【0096】

特に、請求項4,5,7の各発明によれば、複数のスイッチのオン・オフ動作の組合わせによって、低圧側スイッチングデバイス及び低圧側ダイオードを介在させることなく、安定した第1コンデンサ、従って、第2コンデンサの充電を容易に実現することができる。しかも、各スイッチは例えばMOSFETによって実現可能なので、この点で装置内部の充電経路上の各部の集積化を推進することもできる。

【0097】

特に請求項8の発明によれば、(1)請求項5及び8との関係では、第2コンデンサの充電電圧ないし高圧側駆動回路への供給電圧の変動を±1Vの範囲内に抑制することができ、又、(2)請求項6との関係では、上記供給電圧の変動をなくすことができ、(3)5Vで高圧側スイッチングデバイスを駆動するために、6Vまたは5Vの低圧直流電源を用いることも可能としうる。

【図面の簡単な説明】

【図1】本発明の実施の形態1のハーフブリッジ構成のパワーデバイスの単電源駆動回路を示す図である。

【図2】本発明の実施の形態2のハーフブリッジ構成のパワーデバイスの単電源駆動回路を示す図である。

【図3】方法(A)での充電・駆動のタイミングを示す図である。

【図4】方法(B)での充電・駆動のタイミングを示す図である。

【図5】図2の回路の変形例を示す図である。

【図6】図2の回路の変形例を示す図である。

【図7】本発明の実施の形態3のハーフブリッジ構成のパワーデバイスの単電源駆動回路を示す図である。

【図8】図7の回路の変形例を示す図である。

【図9】図7の回路の変形例を示す図である。

【図10】従来のハーフブリッジ構成のパワーデバイスの単電源駆動回路を示す図である。

【符号の説明】

1 高圧直流電源、2 高圧側駆動回路、3 低圧側駆動回路、4 低圧直流電源、Q1 高圧側スイッチングデバイス、Q2 低圧側スイッチングデバイス、R1 第1抵抗、R2 第2抵抗、SW1 第1スイッチ、SW2 第2スイッチ、SW3 第3スイッチ、C (第2)コンデンサ、C1 第1コンデンサ、ZD1 第1ツェナーダイオード、ZD2 第2ツェナーダイオード。

Claims (9)

- 高圧直流電源にその第1電極が接続された高圧側スイッチングデバイスと、

その第1及び第2端がそれぞれ前記高圧側スイッチングデバイスの制御電極及び第2電極に接続された高圧側駆動回路と、

前記高圧側スイッチングデバイスの前記第2電極にその第1電極が接続され、その第2電極がグランドに接続された低圧側スイッチングデバイスと、

その第1及び第2端がそれぞれ前記低圧側スイッチングデバイスの制御電極及び前記第2電極に接続された低圧側駆動回路とを備え、

前記高圧側スイッチングデバイスと前記低圧側スイッチングデバイスとは、前記高圧側駆動回路と前記低圧側駆動回路とによって交互にその動作をオン、オフするように制御されており、

ダイオードと、

その一端及び他端がそれぞれ前記ダイオードのアノード及び前記グランドに接続された低圧直流電源と、

その第1電極が前記ダイオードを介して前記低圧直流電源の前記一端に接続され且つ前記高圧側駆動回路の第3端にも接続されており、その第2電極が前記高圧側スイッチングデバイスの前記第2電極に接続されたコンデンサと、

前記低圧側スイッチングデバイスの動作がオン状態にある間に成される前記コンデンサの充電期間中、前記コンデンサの両端間の電圧値を固定する電圧固定手段とを、

更に備える半導体装置において、

前記電圧固定手段は、

そのカソードが前記コンデンサの前記第1電極に接続され、そのアノードが前記コンデンサの前記第2電極に接続された、ツェナーダイオードを備え、

前記低圧直流電源の電圧は、前記ツェナーダイオードのツェナー電圧と前記ダイオードの順方向電圧と前記低圧側スイッチングデバイスのオン電圧との和よりも大きく設定されていることを特徴とする、半導体装置。 - 請求項1記載の半導体装置において、

前記低圧側スイッチングデバイスの前記第1及び第2電極にそのカソード及びアノードがそれぞれ接続された低圧側ダイオードと、

前記ダイオードのカソード及び前記コンデンサの前記第1電極にその一端及び他端が接続された抵抗とを、

更に備えることを特徴とする半導体装置。 - 高圧直流電源にその第1電極が接続された高圧側スイッチングデバイスと、

その第1及び第2端がそれぞれ前記高圧側スイッチングデバイスの制御電極及び第2電極に接続された高圧側駆動回路と、

前記高圧側スイッチングデバイスの前記第2電極にその第1電極が接続され、その第2電極がグランドに接続された低圧側スイッチングデバイスと、

その第1及び第2端がそれぞれ前記低圧側スイッチングデバイスの制御電極及び前記第2電極に接続された低圧側駆動回路とを備え、

前記高圧側スイッチングデバイスと前記低圧側スイッチングデバイスとは、前記高圧側駆動回路と前記低圧側駆動回路とによって交互にその動作をオン、オフするように制御されており、

前記低圧側スイッチングデバイスの前記第1及び第2電極にそのカソード及びアノードがそれぞれ接続された低圧側ダイオードと、

ダイオードと、

その一端及び他端がそれぞれ前記ダイオードのアノード及び前記グランドに接続された低圧直流電源と、

前記ダイオードのカソードと前記グランドと前記高圧側駆動回路の第3端とに接続され、前記低圧側スイッチングデバイスの動作がオン状態にある間に、前記低圧側スイッチングデバイスと前記低圧側ダイオードとを介在させることなく、前記低圧直流電源から供給される、前記高圧側スイッチングデバイスを駆動するのに必要な電荷を自ら充電する一方、前記高圧側スイッチングデバイスの動作がオン状態にあるときに前記電荷に対応した充電電圧を前記高圧側駆動回路に供給する充電電圧供給手段とを、

更に備えることを特徴とする半導体装置。 - 請求項3記載の半導体装置において、

前記ダイオードを第1ダイオードとすると、

前記充電電圧供給手段は、

前記第1ダイオードの前記カソードにその第1電極が接続された第1コンデンサと、

前記第1コンデンサの第2電極と前記グランドとの間に配設され、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオンに制御され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオフに制御される、第1スイッチと、

そのアノード及びカソードが前記第1ダイオードの前記カソード及び前記高圧側駆動回路の前記第3端にそれぞれ接続された第2ダイオードと、

その第1及び第2電極が前記高圧側駆動回路の前記第3端及び前記第2端にそれぞれ接続された第2コンデンサと、

前記第1コンデンサの前記第2電極と前記第2コンデンサの前記第2電極との間に配設され、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオフに制御され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオンに制御される、第2スイッチとを、

備えることを特徴とする半導体装置。 - 請求項4記載の半導体装置において、

前記第2ダイオードに代えて、

前記低圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオフに制御され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオンに制御される、第3スイッチを、

備えることを特徴とする半導体装置。 - 高圧直流電源にその第1電極が接続された高圧側スイッチングデバイスと、

その第1及び第2端がそれぞれ前記高圧側スイッチングデバイスの制御電極及び第2電極に接続された高圧側駆動回路と、

前記高圧側スイッチングデバイスの前記第2電極にその第1電極が接続され、その第2電極がグランドに接続された低圧側スイッチングデバイスと、

その第1及び第2端がそれぞれ前記低圧側スイッチングデバイスの制御電極及び前記第2電極に接続された低圧側駆動回路とを備え、

前記高圧側スイッチングデバイスと前記低圧側スイッチングデバイスとは、前記高圧側駆動回路と前記低圧側駆動回路とによって交互にその動作をオン、オフするように制御されており、

前記低圧側スイッチングデバイスの前記第1及び第2電極にそのカソード及びアノードがそれぞれ接続された低圧側ダイオードと、

ダイオードと、

その一端及び他端がそれぞれ前記ダイオードのアノード及び前記グランドに接続された低圧直流電源と、

前記ダイオードのカソードと前記グランドと前記高圧側駆動回路の第3端とに接続され、前記高圧側スイッチングデバイスの動作がオン状態にある間に、前記低圧側スイッチングデバイスと前記低圧側ダイオードとを介在させることなく、前記低圧直流電源から供給される、前記高圧側スイッチングデバイスを駆動するのに必要な電荷を自ら充電する一方、前記低圧側スイッチングデバイスの動作がオン状態にあるときに前記電荷に対応した充電電圧を前記高圧側駆動回路に供給する充電電圧供給手段とを、

更に備えることを特徴とする半導体装置。 - 請求項6記載の半導体装置において、

前記ダイオードを第1ダイオードとすると、

前記充電電圧供給手段は、

前記第1ダイオードの前記カソードにその第1電極が接続された第1コンデンサと、

前記第1コンデンサの第2電極と前記グランドとの間に配設され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオンに制御され、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオフに制御される、第1スイッチと、

そのアノード及びカソードが前記第1ダイオードの前記カソード及び前記高圧側駆動回路の前記第3端にそれぞれ接続された第2ダイオードと、

その第1及び第2電極が前記高圧側駆動回路の前記第3端及び前記第2端にそれぞれ接続された第2コンデンサと、

前記第1コンデンサの前記第2電極と前記第2コンデンサの前記第2電極との間に配設され、前記高圧側スイッチングデバイスの動作がオン状態にあるときには、そのスイッチング動作はオフに制御され、前記低圧側スイッチングデバイスの動作がオン状態にあるときには、前記スイッチング動作はオンに制御される、第2スイッチとを、

備えることを特徴とする半導体装置。 - 請求項4,5及び7のいずれかに記載の半導体装置において、

前記低圧直流電源の電圧を、前記高圧側スイッチングデバイスの駆動電圧に前記第1ダイオードの順方向電圧分だけを加えた値に設定することを特徴とする、

半導体装置。 - 高圧直流電源にその第1電極が接続された高圧側スイッチングデバイスと、

その第1及び第2端がそれぞれ前記高圧側スイッチングデバイスの制御電極及び第2電極に接続された高圧側駆動回路と、

前記高圧側スイッチングデバイスの前記第2電極にその第1電極が接続され、その第2電極がグランドに接続された低圧側スイッチングデバイスと、

その第1及び第2端がそれぞれ前記低圧側スイッチングデバイスの制御電極及び前記第2電極に接続された低圧側駆動回路と、

前記低圧側スイッチングデバイスの前記第1及び第2電極にそのカソード及びアノードがそれぞれ接続された低圧側ダイオードと、

前記高圧側駆動回路の第3端及び前記第2端との間に並列に接続されたコンデンサと、

低圧直流電源をソースとし、スイッチング手段を備える、前記コンデンサの充電経路とを備え、

前記高圧側スイッチングデバイスと前記低圧側スイッチングデバイスとを、前記高圧側駆動回路と前記低圧側駆動回路とによって交互にオン、オフするように制御すると共に、

前記高圧側スイッチングデバイス及び前記低圧側スイッチングデバイスの動作状態に応じて前記スイッチング手段の動作をオン、オフに交互に切り換え制御することにより、前記低圧側スイッチングデバイス及び前記低圧側ダイオードを介在させることなく、前記充電経路より、前記高圧側スイッチングデバイスを駆動するのに必要な電圧を前記コンデンサに充電することを特徴とする、

半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP07975697A JP3607033B2 (ja) | 1997-03-31 | 1997-03-31 | 半導体装置 |

| US08/922,373 US5963066A (en) | 1997-03-31 | 1997-09-03 | Semiconductor device which drives low-voltage driven switching device, using low-voltage direct current power source, a diode and a capacitor |

| DE19750168.0A DE19750168B4 (de) | 1997-03-31 | 1997-11-12 | Drei Spannungsversorgungen für Treiberschaltungen von Leistungs-Halbleiterschaltern |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP07975697A JP3607033B2 (ja) | 1997-03-31 | 1997-03-31 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10285949A JPH10285949A (ja) | 1998-10-23 |

| JP3607033B2 true JP3607033B2 (ja) | 2005-01-05 |

Family

ID=13699076

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP07975697A Expired - Lifetime JP3607033B2 (ja) | 1997-03-31 | 1997-03-31 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US5963066A (ja) |

| JP (1) | JP3607033B2 (ja) |

| DE (1) | DE19750168B4 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20230291176A1 (en) * | 2022-03-10 | 2023-09-14 | Hyundai Motor Company | Laser driver for driving vcsel |

Families Citing this family (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3694843B2 (ja) * | 1996-08-08 | 2005-09-14 | 株式会社安川電機 | インバータ装置 |

| DE19730215C2 (de) * | 1997-07-15 | 2001-01-25 | Dialog Semiconductor Gmbh | Schaltungsanordnung mit einer ersten Steuereinheit und einer zweiten Steuereinheit |

| JP3678891B2 (ja) * | 1997-08-07 | 2005-08-03 | 松下電器産業株式会社 | Pwmインバータ用出力回路 |

| JP4151163B2 (ja) * | 1999-07-08 | 2008-09-17 | 株式会社豊田自動織機 | Mosトランジスタのドライブ回路 |

| US6201717B1 (en) * | 1999-09-04 | 2001-03-13 | Texas Instruments Incorporated | Charge-pump closely coupled to switching converter |

| DE19946025B4 (de) * | 1999-09-25 | 2012-02-23 | Robert Bosch Gmbh | Vorrichtung zur Stromversorgung einer Ansteuerschaltung für ein getaktetes Schaltnetzteil |

| US6392463B1 (en) * | 2000-07-07 | 2002-05-21 | Denso Corporation | Electrical load driving circuit with protection |

| EP1360755A2 (en) * | 2001-02-06 | 2003-11-12 | Koninklijke Philips Electronics N.V. | Synchronous dc-dc converter |

| EP1360756A2 (en) * | 2001-02-06 | 2003-11-12 | Koninklijke Philips Electronics N.V. | Switching fet circuit |

| DE10127868A1 (de) * | 2001-06-08 | 2003-02-20 | Grundfos As | Bootstrap-Spannungsversorgung |

| DE10133204A1 (de) * | 2001-07-07 | 2003-01-23 | Rainer Marquardt | Leistungsauskopplung mit Hilfsspannungserzeugung |

| US6657274B2 (en) | 2001-10-11 | 2003-12-02 | Microsemi Corporation | Apparatus for controlling a high voltage circuit using a low voltage circuit |

| JP2004173460A (ja) * | 2002-11-22 | 2004-06-17 | Fujitsu Ltd | Dc−dcコンバータの制御方法、dc−dcコンバータ、半導体集積回路装置、及び電子機器 |

| JP4349097B2 (ja) * | 2003-11-17 | 2009-10-21 | 株式会社豊田自動織機 | ドライブ回路 |

| JP4313658B2 (ja) * | 2003-11-28 | 2009-08-12 | 三菱電機株式会社 | インバータ回路 |

| US7190208B2 (en) | 2004-04-08 | 2007-03-13 | International Rectifier Corporation | Self-oscillating full bridge driver IC |

| JP4682007B2 (ja) * | 2004-11-10 | 2011-05-11 | 三菱電機株式会社 | 電力用半導体装置 |

| JP3915815B2 (ja) * | 2005-03-23 | 2007-05-16 | サンケン電気株式会社 | レベルシフト回路および電源装置 |

| JP3912417B2 (ja) * | 2005-06-24 | 2007-05-09 | サンケン電気株式会社 | 駆動回路 |

| US20070019450A1 (en) * | 2005-07-13 | 2007-01-25 | Texas Instruments Incorporated | System and method for regulating an output of a switching supply circuit |

| US20070146020A1 (en) * | 2005-11-29 | 2007-06-28 | Advanced Analogic Technologies, Inc | High Frequency Power MESFET Gate Drive Circuits |

| JP4049332B1 (ja) * | 2007-01-29 | 2008-02-20 | 株式会社パワーシステム | 充電制御装置 |

| JP5105070B2 (ja) * | 2008-02-14 | 2012-12-19 | セイコーエプソン株式会社 | 容量性負荷の駆動回路及び液体吐出装置 |

| US8324863B2 (en) * | 2010-04-19 | 2012-12-04 | Tesla Motors, Inc. | Trickle charger for high-energy storage systems |

| DE102011055122A1 (de) * | 2010-12-16 | 2012-06-21 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Widerstandsschaltung, Schaltungsanordnung und Treiber |

| JP5605263B2 (ja) * | 2011-02-23 | 2014-10-15 | 株式会社デンソー | 負荷駆動装置 |

| JP5236822B1 (ja) * | 2012-01-30 | 2013-07-17 | シャープ株式会社 | ドライバ回路 |

| CN104578705A (zh) * | 2013-10-21 | 2015-04-29 | 立锜科技股份有限公司 | 电源转换电路的控制电路及相关的电容充电电路 |

| JP2014033614A (ja) * | 2013-11-18 | 2014-02-20 | National Institute Of Advanced Industrial & Technology | 電力変換装置 |

| CN104953994B (zh) * | 2014-03-29 | 2018-01-09 | 华为技术有限公司 | 一种功率开关管的驱动电路 |

| CN107925345B (zh) * | 2016-02-16 | 2019-12-27 | 富士电机株式会社 | 半导体装置 |

| JP6831713B2 (ja) * | 2017-02-15 | 2021-02-17 | ローム株式会社 | ブートストラップ回路 |

| DE102017130443A1 (de) * | 2017-12-19 | 2019-06-19 | Dr. Ing. H.C. F. Porsche Aktiengesellschaft | Flexibles Bootstrapping für Leistungselektronikschaltungen |

| US10469066B1 (en) * | 2018-07-27 | 2019-11-05 | Texas Instruments Incorporated | Trickle charge control |

| JP2021084337A (ja) * | 2019-11-28 | 2021-06-03 | セイコーエプソン株式会社 | 液体吐出装置、及び駆動回路 |

| WO2024195084A1 (ja) * | 2023-03-23 | 2024-09-26 | サンケン電気株式会社 | スイッチング回路、電源生成回路及び半導体装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3314300A1 (de) * | 1983-04-20 | 1984-10-25 | Siemens AG, 1000 Berlin und 8000 München | Schaltungsanordnung zur ansteuerung von leistungs-mos-fet-gegentaktendstufen |

| US4736121A (en) * | 1985-09-10 | 1988-04-05 | Sos Microelettronica S.p.A. | Charge pump circuit for driving N-channel MOS transistors |

| DE3625091A1 (de) * | 1986-07-24 | 1988-01-28 | Bosch Gmbh Robert | Endstufe in brueckenschaltung |

| JP2758477B2 (ja) * | 1990-03-15 | 1998-05-28 | 株式会社芝浦製作所 | 携帯形情報機器 |

| IT1251097B (it) * | 1991-07-24 | 1995-05-04 | St Microelectronics Srl | Circuito di bootstrap per il pilotaggio di un transistore mos di potenza in configurazione high side driver. |

| US5325258A (en) * | 1992-08-26 | 1994-06-28 | International Rectifier Corporation | Power transistor driver circuit with current sensing and current overprotection and method for protecting power transistor from overcurrent |

| JPH0698560A (ja) * | 1992-09-17 | 1994-04-08 | Toshiba Corp | インバータ装置 |

| US5412309A (en) * | 1993-02-22 | 1995-05-02 | National Semiconductor Corporation | Current amplifiers |

| JP3216764B2 (ja) * | 1994-12-15 | 2001-10-09 | 富士電機株式会社 | インバータの駆動回路 |

| US5796276A (en) * | 1994-12-30 | 1998-08-18 | Sgs-Thomson Microelectronics, Inc. | High-side-driver gate drive circuit |

| EP0751621B1 (en) * | 1995-06-30 | 1998-04-15 | STMicroelectronics S.r.l. | Bootstrap line power supply regulator with no filter capacitor |

-

1997

- 1997-03-31 JP JP07975697A patent/JP3607033B2/ja not_active Expired - Lifetime

- 1997-09-03 US US08/922,373 patent/US5963066A/en not_active Expired - Lifetime

- 1997-11-12 DE DE19750168.0A patent/DE19750168B4/de not_active Expired - Lifetime

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20230291176A1 (en) * | 2022-03-10 | 2023-09-14 | Hyundai Motor Company | Laser driver for driving vcsel |

| US12580365B2 (en) * | 2022-03-10 | 2026-03-17 | Hyundai Motor Company | Laser driver for driving VCSEL |

Also Published As

| Publication number | Publication date |

|---|---|

| US5963066A (en) | 1999-10-05 |

| JPH10285949A (ja) | 1998-10-23 |

| DE19750168B4 (de) | 2014-11-20 |

| DE19750168A1 (de) | 1998-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3607033B2 (ja) | 半導体装置 | |

| JP4113436B2 (ja) | ゲートドライブ装置 | |

| US8072202B2 (en) | Gate driver in buck converters | |

| KR100696719B1 (ko) | 동적 백게이트 바이어싱을 갖는 부트스트랩 다이오드이뮬레이터 | |

| US7692474B2 (en) | Control circuit for a high-side semiconductor switch for switching a supply voltage | |

| US6963498B2 (en) | Bootstrap capacitor refresh circuit | |

| US8013642B2 (en) | Output drive circuit | |

| US8054054B2 (en) | High voltage gate driver IC (HVIC) with internal charge pumping voltage source | |

| WO2000019597A1 (en) | Methods and apparatus for reducing mosfet body diode conduction in a half-bridge configuration | |

| CN101401307A (zh) | 驱动器电路和使用该驱动器电路的半导体装置 | |

| US7688052B2 (en) | Charge pump circuit and method therefor | |

| JP4712519B2 (ja) | ハイサイド駆動回路用チャージポンプ回路及びドライバ駆動電圧回路 | |

| CN117716620A (zh) | 整流电路和使用它的电源 | |

| JP3937354B2 (ja) | ダイナミック・バックゲート・バイアスと短絡保護を伴うブートストラップ・ダイオード・エミュレータ | |

| JP2007336694A (ja) | 絶縁ゲート型半導体素子の駆動回路 | |

| JPH08149796A (ja) | 電圧駆動型スイッチ素子のドライブ回路 | |

| JP3608472B2 (ja) | 出力回路 | |

| US6867574B2 (en) | Switch mode power supply and driving method for efficient RF amplification | |

| KR20190108785A (ko) | 전원 변환기, 스위칭 소자 구동 장치 및 부하 구동 장치 | |

| US20240204777A1 (en) | Semiconductor device | |

| JP3314473B2 (ja) | パワーmosfetの制御装置 | |

| CN115210984A (zh) | 供电控制装置 | |

| JP4443859B2 (ja) | チャージポンプ駆動回路 | |

| JP4319336B2 (ja) | Mosスイッチング回路 | |

| JP6939087B2 (ja) | 集積回路装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040729 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040803 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040903 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20041005 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20041006 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20071015 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081015 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091015 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091015 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101015 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111015 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121015 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131015 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |