JP2011009686A - パッケージ基板及びその製造方法、並びにその基材 - Google Patents

パッケージ基板及びその製造方法、並びにその基材 Download PDFInfo

- Publication number

- JP2011009686A JP2011009686A JP2009263132A JP2009263132A JP2011009686A JP 2011009686 A JP2011009686 A JP 2011009686A JP 2009263132 A JP2009263132 A JP 2009263132A JP 2009263132 A JP2009263132 A JP 2009263132A JP 2011009686 A JP2011009686 A JP 2011009686A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- metal

- layers

- auxiliary dielectric

- dielectric layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K13/00—Apparatus or processes specially adapted for manufacturing or adjusting assemblages of electric components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4682—Manufacture of core-less build-up multilayer circuits on a temporary carrier or on a metal foil

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05568—Disposition the whole external layer protruding from the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05573—Single external layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15172—Fan-out arrangement of the internal vias

- H01L2924/15174—Fan-out arrangement of the internal vias in different layers of the multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/01—Tools for processing; Objects used during processing

- H05K2203/0147—Carriers and holders

- H05K2203/0152—Temporary metallic carrier, e.g. for transferring material

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/15—Position of the PCB during processing

- H05K2203/1536—Temporarily stacked PCBs

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0097—Processing two or more printed circuits simultaneously, e.g. made from a common substrate, or temporarily stacked circuit boards

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T156/00—Adhesive bonding and miscellaneous chemical manufacture

- Y10T156/10—Methods of surface bonding and/or assembly therefor

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Abstract

【解決手段】本発明に係るパッケージ基板の製造方法は、先ず、二つの金属層を相互にラミネートし、誘電体層で二つの金属層を覆い、次に、誘電体層の両側にビルドアップ構造をそれぞれ形成し、最後に二つの金属層の界面に沿って両側のビルドアップ構造を分離させることにより、二つのパッケージ基板を形成する。本発明は最初に誘電体層の粘着特性によって中間層である二つの金属層をビルドアップ構造の形成過程にて分離させず、最後に二つの金属層の周囲の誘電体層部分を切断することにより、二つの金属層を円滑に分離させることで、プロセスを簡略化することができる。又、中間層である二つの金属層をパターニングすることにより、回路層、金属バンプ、又は支持構造を形成することができるため、資源の無駄が生じない。

【選択図】図2A

Description

一方の表面に内層回路層が設けられ、前記内層回路層に電気的に接続される複数の内層導電ビアが設けられた第1の補助誘電体層と、

前記第1の補助誘電体層の他方の表面の上に設けられ、前記内層導電ビアの各々に接続された金属バンプであって、前記内層導電ビアの電気的に接続された一端の孔径が、前記内層導電ビアの前記金属バンプが電気的に接続された一端の孔径より大きいようにする複数の金属バンプと、

前記第1の補助誘電体層と前記内層回路層の上に設けられ、少なくとも一つの第1の誘電体層、前記第1の誘電体層の上に設けられた第1の回路層と、前記第1の誘電体層に設けられ前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含むビルドアップ構造であって、このビルドアップ構造の最外層の第1の回路層が複数の第1の電気接触パッドを有するビルドアップ構造と、

前記ビルドアップ構造の上に設けられ、前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を有する第1の絶縁保護層と、

を備えるパッケージ基板を提供する。

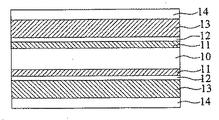

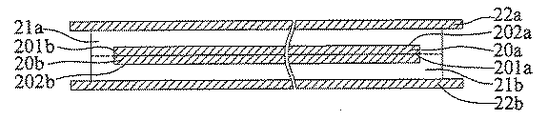

対向してラミネートされ、対向する第1の表面と第2の表面を有し、前記第1の表面で相互に結合する二つの第1の金属層と、

前記第1の金属層の第2の表面の上にそれぞれ設けられ、二つの前記第1の金属層を覆う二つの第1の補助誘電体層と、

前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、

を含む基材を提供する。

対向してラミネートされ、対向する第1の表面と第2の表面を有し、前記第1の表面で相互的に結合する二つの第1の金属層と、

前記第1の金属層の前記第2の表面の上にそれぞれ設けられ、二つの前記第1の金属層を覆う二つの第1の補助誘電体層と、

前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、

前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、

前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、を含む基材を提供する。

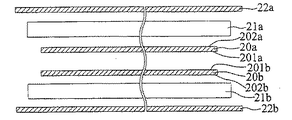

対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体でああって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆う基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成する工程と、

前記第1の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成することにより全体構造を形成する工程であって、前記ビルドアップ構造は、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を少なくとも含む工程と、

を含むパッケージ基板の製造方法を提供する。

対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層を提供する工程と、

前記第1の金属層の前記第2の表面の上に前記第1の補助誘電体層をラミネートする工程と、

前記第1の補助誘電体層が露出した表面の上に前記第2の金属層をラミネートし、これらの前記第1の金属層、前記第1の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ、二つの前記第1の金属層を覆う工程と、

を含む。

対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体でああって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆う基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成し、前記第1の補助誘電体層に前記内層回路層と前記第1の金属層に電気的に接続される複数の内層導電ビアを形成する工程と、

前記第1の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成し、前記ビルドアップ構造が、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアとを含み、前記ビルドアップ構造の最外層の前記第1の回路層が複数の第1の電気接触パッドを有する工程と、

前記ビルドアップ構造の上に第1の絶縁保護層を形成することにより全体構造を形成し、前記第1の絶縁保護層に前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、

前記第1の金属層の各々を分離することにより、二つの基礎基板を形成する工程と、

を含むパッケージ基板の製造方法を提供する。

対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層を提供する工程と、

前記第1の金属層の前記第2の表面の上に前記第1の補助誘電体層をラミネートする工程と、

前記第1の補助誘電体層が露出した表面の上に前記第2の金属層をラミネートし、これらの前記第1の金属層、前記第1の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ、二つの前記第1の金属層を覆う工程と、を含む。

対向する第1の表面と第2の表面を有し前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体でああって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆い、前記コア層の両表面には第1の電気接触パッドと第2の電気接触パッドを複数有し、前記第2の電気接触パッドが前記第1の補助誘電体層の上にあるようにする基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成し、前記第2の補助誘電体層には前記内層回路層と前記第1の電気接触パッドに電気的に接続される複数の内層導電ビアを形成する工程と、

前記第2の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成することにより全体構造を形成し、前記ビルドアップ構造が、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアを含む工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、

前記第1の金属層の各々を分離することにより、二つの基礎基板を形成する工程と、

を含むパッケージ基板の製造方法を提供する。

対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートする二つの第1の金属層、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの前記第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層、前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層、及び前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層を提供する工程と、

これらの前記第1の金属層、前記第1の補助誘電体層、前記コア層、前記第2の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ二つの前記第1の金属層を覆い、前記第2の電気接触パッドを前記第1の補助誘電体層の表面に嵌め込む工程と、

を含む。

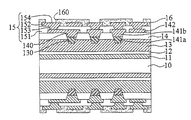

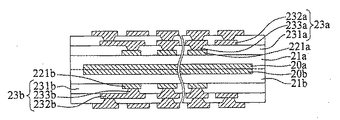

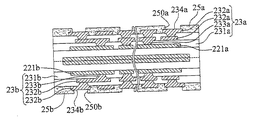

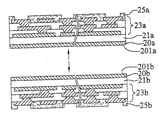

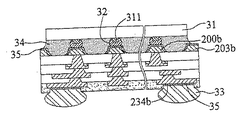

図2A乃至図2Fは、本発明に係るパッケージ基板及びその製造方法の第1の実施例を模式的に示す断面図である。

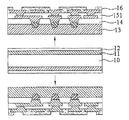

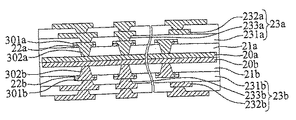

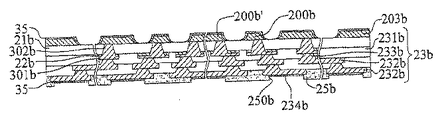

図3A乃至図3Dは、本発明に係るパッケージ基板及びその製造方法の第2の実施例を模式的に示す断面図である。

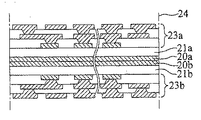

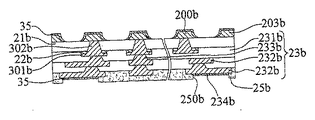

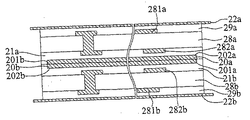

図4A乃至図4Fは、本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である。図4Gと図4Hは本実施例の他の実施態様を示す。

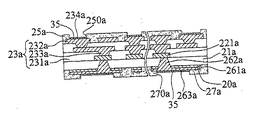

図5A乃至図5Gは、本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。

11 薄膜金属層

12 離型層

13 キャリア金属層

14、231a、231b 第1の誘電体層

15、23a、23b ビルドアップ構造

16 絶縁保護層

20a、20b 第1の金属層

21a、21b 第1の補助誘電体層

22a、22b 第2の金属層

24 切断ライン

25a、25b 第1の絶縁保護層

27a 第2の絶縁保護層

28a、28b コア層

29a、29b 第2の補助誘電体層

31 半導体チップ

31a 作用面

31b 非作用面

32、141a 半田バンプ

33 半田ボール

34 充填材料

35 表面処理層

36 ボンディングワイヤ

37 モールド化合物

130 凹部

140 ビア

141b、233a、233b 第1の導電ビア

142、232a、232b 第1の回路層

151 第2の誘電体層

152、261a 第2の回路層

153、262a 第2の導電ビア

154 電気接触パッド

160 絶縁保護層開孔

200b 金属バンプ

200b ヒートシンク

201a、201b 第1の表面

202a、202b 第2の表面

203b 金属支持フレーム

210a 開孔

221a、221b、301a、301b 内層回路層

234a、234b 第1の電気接触パッド

250a、250b 第1の絶縁保護層開孔

263a 第2の電気接触パッド

270a 第2の絶縁保護層開孔

281a、281b 第1の電気接触パッド

282a、282b 第2の電気接触パッド

283a、283b 導電ビア

302a、302b 内層導電ビア

311 電極パッド

2210 第3の電気接触パッド

Claims (26)

- 一方の表面に内層回路層が設けられ、前記内層回路層に電気的に接続される複数の内層導電ビアが設けられる第1の補助誘電体層と、

前記第1の補助誘電体層の他方の表面の上に設けられ、前記内層導電ビアの各々に接続された金属バンプであって、前記内層導電ビアの、前記内層回路層に電気的に接続された一端の孔径が、前記内層導電ビアの、金属バンプに電気的に接続された一端の孔径より大きい複数の金属バンプと、

前記第1の補助誘電体層と前記内層回路層の上に設けられ、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に設けられる第1の回路層と、前記第1の誘電体層に設けられ前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含むビルドアップ構造であって、前記ビルドアップ構造の最外層の前記第1の回路層が複数の第1の電気接触パッドを有するビルドアップ構造と、

前記ビルドアップ構造の上に設けられ、前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を有する第1の絶縁保護層と、

を含むことを特徴とするパッケージ基板。 - 前記金属バンプはソルダーバンプパッドであり、フリップチップパッケージの電気的接続に用いられることを特徴とする請求項1に記載のパッケージ基板。

- 前記金属バンプはヒートシンク及びその周囲に設けられる複数のボンディングパッドであり、前記ボンディングパッドはボンディングパッケージの電気的接続に用いられることを特徴とする請求項1に記載のパッケージ基板。

- 前記第1の補助誘電体層の上に設けられる金属支持フレームをさらに含むことを特徴とする請求項1に記載のパッケージ基板。

- 対向してラミネートされ、それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で相互いに結合される二つの第1の金属層と、

前記第1の金属層の前記第2の表面の上にそれぞれ設けられ、二つの前記第1の金属層を覆う二つの第1の補助誘電体層と、

前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、

を含むことを特徴とする基材。 - 前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項5に記載の基材。

- 対向してラミネートされ、対向する第1の表面と第2の表面を有し、前記第1の表面で相互に結合される二つの第1の金属層と、

前記第1の金属層の前記第2の表面の上にそれぞれ設けられ、二つの前記第1の金属層を覆う二つの第1の補助誘電体層と、

前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、

前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、

前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、

を含むことを特徴とする基材。 - 前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項7に記載の基材。

- それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体であって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆う基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成する工程と、

前記第1の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成することにより全体構造を形成する工程であって、前記ビルドアップ構造は、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含む工程と、

を含むことを特徴とするパッケージ基板の製造方法。 - 前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項9に記載のパッケージ基板の製造方法。

- 前記基材の製造方法は、

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層を提供する工程と、

前記第1の金属層の前記第2の表面の上に前記第1の補助誘電体層をラミネートする工程と、

前記第1の補助誘電体層が露出した表面の上に前記第2の金属層をラミネートし、これらの前記第1の金属層、前記第1の補助誘電体層、及び前記第2の金属層を圧着させることにより、二つの前記第1の補助誘電体層を一体に結合させ、二つの前記第1の金属層を覆う工程と、

を含むことを特徴とする請求項9に記載のパッケージ基板の製造方法。 - 切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断し、前記第1の金属層の各々を分離させることにより、二つの基礎基板を形成する工程をさらに含むことを特徴とする請求項9に記載のパッケージ基板の製造方法。

- 前記ビルドアップ構造の最外層の前記第1の回路層はさらに複数の第1の電気接触パッドを有し、前記ビルドアップ構造の上に第1の絶縁保護層が形成され、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔が形成されることを特徴とする請求項12に記載のパッケージ基板の製造方法。

- 前記第1の金属層をパターニングすることにより第2の回路層を形成し、前記第1の補助誘電体層には前記内層回路層と前記第2の回路層に電気的に接続される複数の第2の導電ビアを形成する工程をさらに含み、

前記第2の回路層はさらに複数の第2の電気接触パッドを有し、前記第1の補助誘電体層の上には第2の絶縁保護層を形成し、前記第2の絶縁保護層には前記第2の電気接触パッドの各々を露出させるための複数の第2の絶縁保護層開孔が形成されることを特徴とする請求項12に記載のパッケージ基板の製造方法。 - 前記ビルドアップ構造の最外層の前記第1の回路層はさらに複数の第1の電気接触パッドを有し、

前記ビルドアップ構造の上に第1の絶縁保護層を形成し、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、

前記第1の金属層の各々を分離させることにより、二つの基礎基板を形成する工程と、

をさらに含むことを特徴とする請求項9に記載のパッケージ基板の製造方法。 - 前記第1の金属層を除去することにより前記第1の補助誘電体層を露出させ、前記第1の補助誘電体層には前記内層回路層の一部を露出させる複数の開孔を形成する工程をさらに含むことを特徴とする請求項15に記載のパッケージ基板の製造方法。

- それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体であであって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆う基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成し、前記第1の補助誘電体層には前記内層回路層と前記第1の金属層に電気的に接続される複数の内層導電ビアを形成する工程と、

前記第1の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成し、前記ビルドアップ構造が、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含み、前記ビルドアップ構造の最外層の前記第1の回路層が複数の第1の電気接触パッドを有する工程と、

前記ビルドアップ構造の上に第1の絶縁保護層を形成することにより全体構造を形成し、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、

前記第1の金属層の各々を分離させることにより、二つの基礎基板を形成する工程と、

を含むことを特徴とするパッケージ基板の製造方法。 - 前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項17に記載のパッケージ基板の製造方法。

- 前記基材の製造方法は、

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面でラミネートされる二つの第1の金属層を提供する工程と、

前記第1の金属層の前記第2の表面の上に前記第1の補助誘電体層をラミネートする工程と、

前記第1の補助誘電体層が露出した表面の上に前記第2の金属層をラミネートし、これらの前記第1の金属層、前記第1の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ、二つの前記第1の金属層を覆う工程と、

を含むことを特徴とする請求項17に記載のパッケージ基板の製造方法。 - 前記第1の金属層の一部を除去することにより、前記導電内層ビアの各々に接続される複数の金属バンプを形成することを特徴とする請求項17に記載のパッケージ基板の製造方法。

- 前記第1の金属層の一部を除去することにより、前記第1の補助誘電体層の上に金属支持フレームを形成することを特徴とする請求項20に記載のパッケージ基板の製造方法。

- それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体であって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆い、前記コア層の両表面にはそれぞれ第1の電気接触パッドと第2の電気接触パッドを複数有し、前記第2の電気接触パッドが前記第1の補助誘電体層の上にあるようにする基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成し、前記第2の補助誘電体層には前記内層回路層と前記第1の電気接触パッドに電気的に接続される複数の内層導電ビアを形成する工程と、

前記第2の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成することにより全体構造を形成し、前記ビルドアップ構造が、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含む工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、

前記第1の金属層の各々を分離させることにより、二つの基礎基板を形成する工程と、

を含むことを特徴とするパッケージ基板の製造方法。 - 前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項22に記載のパッケージ基板の製造方法。

- 前記基材の製造方法は、

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層を提供する工程と、

これらの前記第1の金属層、前記第1の補助誘電体層、前記コア層、前記第2の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ二つの前記第1の金属層を被覆させ、前記第2の電気接触パッドを前記第1の補助誘電体層の表面に嵌め込む工程と、

を含むことを特徴とする請求項22に記載のパッケージ基板の製造方法。 - 前記ビルドアップ構造の最外層の前記第1の回路層は、さらに複数の第1の電気接触パッドを有し、前記ビルドアップ構造の上に第1の絶縁保護層を形成し、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程を含むことを特徴とする請求項22に記載のパッケージ基板の製造方法。

- 前記第1の金属層をパターニングすることにより第2の回路層を形成し、前記第1の補助誘電体層には前記第2の電気接触パッドと前記第2の回路層に電気的に接続される複数の第2の導電ビアを形成し、前記第2の回路層が複数の第2の電気接触パッドを有し、前記第1の補助誘電体層の上に第2の絶縁保護層を形成し、前記第2の絶縁保護層に前記第2の電気接触パッドの各々を露出させるための複数の第2の絶縁保護層開孔を形成する工程を含むことを特徴とする請求項22に記載のパッケージ基板の製造方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW098120959A TWI390692B (zh) | 2009-06-23 | 2009-06-23 | 封裝基板與其製法暨基材 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013225193A Division JP2014017531A (ja) | 2009-06-23 | 2013-10-30 | パッケージ基板及びその製造方法、並びにその基材 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011009686A true JP2011009686A (ja) | 2011-01-13 |

| JP2011009686A5 JP2011009686A5 (ja) | 2013-01-10 |

Family

ID=43353307

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009263132A Pending JP2011009686A (ja) | 2009-06-23 | 2009-11-18 | パッケージ基板及びその製造方法、並びにその基材 |

| JP2013225193A Pending JP2014017531A (ja) | 2009-06-23 | 2013-10-30 | パッケージ基板及びその製造方法、並びにその基材 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013225193A Pending JP2014017531A (ja) | 2009-06-23 | 2013-10-30 | パッケージ基板及びその製造方法、並びにその基材 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US8354598B2 (ja) |

| JP (2) | JP2011009686A (ja) |

| TW (1) | TWI390692B (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103035756A (zh) * | 2011-10-08 | 2013-04-10 | 威奈联合科技股份有限公司 | 光电元件及其制造方法 |

| JP2013128000A (ja) * | 2011-12-16 | 2013-06-27 | Advance Materials Corp | パッケージ基板及びその製造方法 |

| WO2014054803A1 (ja) * | 2012-10-04 | 2014-04-10 | Jx日鉱日石金属株式会社 | 多層プリント配線基板の製造方法及びベース基材 |

| JP2014082489A (ja) * | 2012-09-28 | 2014-05-08 | Hitachi Chemical Co Ltd | 多層配線基板の製造方法 |

| JP2014123772A (ja) * | 2014-03-17 | 2014-07-03 | Advance Materials Corp | パッケージ基板 |

| US11640934B2 (en) * | 2018-03-30 | 2023-05-02 | Intel Corporation | Lithographically defined vertical interconnect access (VIA) in dielectric pockets in a package substrate |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5003812B2 (ja) * | 2009-12-10 | 2012-08-15 | イビデン株式会社 | プリント配線板及びプリント配線板の製造方法 |

| US20110253439A1 (en) * | 2010-04-20 | 2011-10-20 | Subtron Technology Co. Ltd. | Circuit substrate and manufacturing method thereof |

| JP5590985B2 (ja) * | 2010-06-21 | 2014-09-17 | 新光電気工業株式会社 | 半導体装置及びその製造方法 |

| US20120055706A1 (en) * | 2010-09-03 | 2012-03-08 | Samsung Electro-Mechanics Co., Ltd. | Printed circuit board and method of manufacturing the same |

| TW201241969A (en) | 2011-04-08 | 2012-10-16 | Unimicron Technology Corp | Method for fabricating heat dissipation substrate |

| TWI453872B (zh) * | 2011-06-23 | 2014-09-21 | 矽品精密工業股份有限公司 | 半導體封裝件及其製法 |

| CN102956575A (zh) * | 2011-08-24 | 2013-03-06 | 国碁电子(中山)有限公司 | 封装结构及制造方法 |

| US9230899B2 (en) | 2011-09-30 | 2016-01-05 | Unimicron Technology Corporation | Packaging substrate having a holder, method of fabricating the packaging substrate, package structure having a holder, and method of fabricating the package structure |

| CN103066048B (zh) * | 2011-10-21 | 2015-11-25 | 欣兴电子股份有限公司 | 具有支撑体的封装基板、封装结构及其制法 |

| CN103066049B (zh) * | 2011-10-24 | 2015-09-02 | 联致科技股份有限公司 | 封装基板及其制法 |

| TWI560835B (en) * | 2011-11-07 | 2016-12-01 | Siliconware Precision Industries Co Ltd | Package substrate and fabrication method thereof |

| CN103137568B (zh) * | 2011-12-02 | 2017-05-03 | 欣兴电子股份有限公司 | 具有支撑体的封装基板及其制法 |

| TWI444123B (zh) * | 2012-02-16 | 2014-07-01 | Via Tech Inc | 線路板製作方法及線路板 |

| TWI484600B (zh) * | 2012-08-15 | 2015-05-11 | Unimicron Technology Corp | 無核心封裝基板及其製法 |

| CN103681586B (zh) * | 2012-08-30 | 2016-07-06 | 欣兴电子股份有限公司 | 无核心封装基板及其制法 |

| CN104685980B (zh) * | 2012-10-04 | 2018-11-23 | Jx日矿日石金属株式会社 | 多层印刷配线基板的制造方法及基底基材 |

| JP2014075515A (ja) * | 2012-10-05 | 2014-04-24 | Shinko Electric Ind Co Ltd | 配線基板及び配線基板の製造方法 |

| JP2014086651A (ja) * | 2012-10-26 | 2014-05-12 | Ibiden Co Ltd | プリント配線板及びプリント配線板の製造方法 |

| JP2014127623A (ja) | 2012-12-27 | 2014-07-07 | Shinko Electric Ind Co Ltd | 配線基板及び配線基板の製造方法 |

| JP2014130856A (ja) * | 2012-12-28 | 2014-07-10 | Kyocer Slc Technologies Corp | 配線基板の製造方法 |

| JP6478309B2 (ja) | 2012-12-31 | 2019-03-06 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 多層基板及び多層基板の製造方法 |

| US8659173B1 (en) * | 2013-01-04 | 2014-02-25 | International Business Machines Corporation | Isolated wire structures with reduced stress, methods of manufacturing and design structures |

| US9275925B2 (en) * | 2013-03-12 | 2016-03-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | System and method for an improved interconnect structure |

| US10464836B2 (en) | 2013-10-10 | 2019-11-05 | Medtronic, Inc. | Hermetic conductive feedthroughs for a semiconductor wafer |

| CN104576596B (zh) * | 2013-10-25 | 2019-01-01 | 日月光半导体制造股份有限公司 | 半导体基板及其制造方法 |

| US9609751B2 (en) * | 2014-04-11 | 2017-03-28 | Qualcomm Incorporated | Package substrate comprising surface interconnect and cavity comprising electroless fill |

| TWI529883B (zh) * | 2014-05-09 | 2016-04-11 | 矽品精密工業股份有限公司 | 封裝堆疊結構及其製法暨無核心層式封裝基板及其製法 |

| CN204014250U (zh) * | 2014-05-16 | 2014-12-10 | 奥特斯(中国)有限公司 | 用于生产电子元件的连接系统的半成品 |

| US9603247B2 (en) * | 2014-08-11 | 2017-03-21 | Intel Corporation | Electronic package with narrow-factor via including finish layer |

| TWI576025B (zh) * | 2014-10-29 | 2017-03-21 | 矽品精密工業股份有限公司 | 基板結構及其製法 |

| JP6615701B2 (ja) * | 2016-06-24 | 2019-12-04 | 新光電気工業株式会社 | 配線基板、半導体装置及び配線基板の製造方法 |

| US10515888B2 (en) | 2017-09-18 | 2019-12-24 | Taiwan Semiconductor Manufacturing Company Ltd. | Semiconductor device and method for manufacturing the same |

| TWI693874B (zh) * | 2018-06-08 | 2020-05-11 | 欣興電子股份有限公司 | 線路載板結構及其製作方法 |

| US11637060B2 (en) | 2019-07-18 | 2023-04-25 | Unimicron Technology Corp. | Wiring board and method of manufacturing the same |

| TWI751506B (zh) * | 2020-03-06 | 2022-01-01 | 欣興電子股份有限公司 | 線路板及其製造方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002026171A (ja) * | 2000-07-06 | 2002-01-25 | Sumitomo Bakelite Co Ltd | 多層配線板の製造方法および多層配線板 |

| JP2004186265A (ja) * | 2002-11-29 | 2004-07-02 | Ngk Spark Plug Co Ltd | 多層配線基板の製造方法 |

| JP2004214272A (ja) * | 2002-12-27 | 2004-07-29 | Ngk Spark Plug Co Ltd | 片面積層配線基板の製造方法 |

| JP2006080214A (ja) * | 2004-09-08 | 2006-03-23 | Cmk Corp | プリント配線板とその製造方法 |

| WO2009037939A1 (ja) * | 2007-09-20 | 2009-03-26 | Ibiden Co., Ltd. | プリント配線板及びその製造方法 |

| JP2009088429A (ja) * | 2007-10-03 | 2009-04-23 | Nec Toppan Circuit Solutions Inc | 印刷配線板及びその製造方法ならびに半導体装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62252189A (ja) * | 1986-04-25 | 1987-11-02 | 株式会社日立製作所 | 銅張積層板 |

| JP4082995B2 (ja) * | 2001-11-30 | 2008-04-30 | 日本特殊陶業株式会社 | 配線基板の製造方法 |

| JP2006049660A (ja) * | 2004-08-06 | 2006-02-16 | Cmk Corp | プリント配線板の製造方法 |

| KR100674319B1 (ko) * | 2004-12-02 | 2007-01-24 | 삼성전기주식회사 | 얇은 코어층을 갖는 인쇄회로기판 제조방법 |

| TWI315657B (en) * | 2005-06-07 | 2009-10-01 | Phoenix Prec Technology Corp | Reverse build-up structure of circuit board |

| JP5356647B2 (ja) * | 2006-12-25 | 2013-12-04 | 新光電気工業株式会社 | 実装基板及び電子装置 |

| KR100929839B1 (ko) * | 2007-09-28 | 2009-12-04 | 삼성전기주식회사 | 기판제조방법 |

| JP5080234B2 (ja) * | 2007-12-19 | 2012-11-21 | 新光電気工業株式会社 | 配線基板およびその製造方法 |

| JP5203045B2 (ja) * | 2008-05-28 | 2013-06-05 | 日本特殊陶業株式会社 | 多層配線基板の中間製品、多層配線基板の製造方法 |

| KR20090130612A (ko) * | 2008-06-16 | 2009-12-24 | 삼성전기주식회사 | 웨이퍼 레벨 패키지 및 그 제조방법 |

| TWI365026B (en) | 2009-06-11 | 2012-05-21 | Unimicron Technology Corp | Method for fabricating packaging substrate and base therefor |

-

2009

- 2009-06-23 TW TW098120959A patent/TWI390692B/zh not_active IP Right Cessation

- 2009-11-18 JP JP2009263132A patent/JP2011009686A/ja active Pending

-

2010

- 2010-03-25 US US12/731,480 patent/US8354598B2/en not_active Expired - Fee Related

-

2013

- 2013-01-10 US US13/738,526 patent/US20130118680A1/en not_active Abandoned

- 2013-10-30 JP JP2013225193A patent/JP2014017531A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002026171A (ja) * | 2000-07-06 | 2002-01-25 | Sumitomo Bakelite Co Ltd | 多層配線板の製造方法および多層配線板 |

| JP2004186265A (ja) * | 2002-11-29 | 2004-07-02 | Ngk Spark Plug Co Ltd | 多層配線基板の製造方法 |

| JP2004214272A (ja) * | 2002-12-27 | 2004-07-29 | Ngk Spark Plug Co Ltd | 片面積層配線基板の製造方法 |

| JP2006080214A (ja) * | 2004-09-08 | 2006-03-23 | Cmk Corp | プリント配線板とその製造方法 |

| WO2009037939A1 (ja) * | 2007-09-20 | 2009-03-26 | Ibiden Co., Ltd. | プリント配線板及びその製造方法 |

| JP2009088429A (ja) * | 2007-10-03 | 2009-04-23 | Nec Toppan Circuit Solutions Inc | 印刷配線板及びその製造方法ならびに半導体装置 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103035756A (zh) * | 2011-10-08 | 2013-04-10 | 威奈联合科技股份有限公司 | 光电元件及其制造方法 |

| JP2013128000A (ja) * | 2011-12-16 | 2013-06-27 | Advance Materials Corp | パッケージ基板及びその製造方法 |

| JP2014082489A (ja) * | 2012-09-28 | 2014-05-08 | Hitachi Chemical Co Ltd | 多層配線基板の製造方法 |

| WO2014054803A1 (ja) * | 2012-10-04 | 2014-04-10 | Jx日鉱日石金属株式会社 | 多層プリント配線基板の製造方法及びベース基材 |

| JP2014123772A (ja) * | 2014-03-17 | 2014-07-03 | Advance Materials Corp | パッケージ基板 |

| US11640934B2 (en) * | 2018-03-30 | 2023-05-02 | Intel Corporation | Lithographically defined vertical interconnect access (VIA) in dielectric pockets in a package substrate |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014017531A (ja) | 2014-01-30 |

| TWI390692B (zh) | 2013-03-21 |

| US20100319966A1 (en) | 2010-12-23 |

| US20130118680A1 (en) | 2013-05-16 |

| TW201101441A (en) | 2011-01-01 |

| US8354598B2 (en) | 2013-01-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2011009686A (ja) | パッケージ基板及びその製造方法、並びにその基材 | |

| CN101989592B (zh) | 封装基板与其制法 | |

| JP4251421B2 (ja) | 半導体装置の製造方法 | |

| US7591067B2 (en) | Thermally enhanced coreless thin substrate with embedded chip and method for manufacturing the same | |

| US8749073B2 (en) | Wiring board, method of manufacturing the same, and semiconductor device | |

| US8181342B2 (en) | Method for manufacturing a coreless packaging substrate | |

| TWI446464B (zh) | 封裝結構及其製作方法 | |

| JP5607086B2 (ja) | 半導体パッケージの製造方法 | |

| JP3813402B2 (ja) | 半導体装置の製造方法 | |

| TWI442530B (zh) | 封裝載板、封裝結構以及封裝載板製程 | |

| JP5390346B2 (ja) | パッケージ基板の製造方法 | |

| TWI512926B (zh) | 電路板層疊封裝結構及其製作方法 | |

| TWI474450B (zh) | 封裝載板及其製作方法 | |

| JP2003297968A (ja) | 半導体パッケージの製造方法 | |

| JP2011009686A5 (ja) | ||

| TWI517321B (zh) | 封裝結構及其製作方法 | |

| JP2008103615A (ja) | 電子部品搭載多層配線基板及びその製造方法 | |

| US10096491B2 (en) | Method of fabricating a packaging substrate including a carrier having two carrying portions | |

| JP2016063130A (ja) | プリント配線板および半導体パッケージ | |

| JP2015225895A (ja) | プリント配線板および半導体パッケージ、ならびにプリント配線板の製造方法 | |

| TWI474449B (zh) | 封裝載板及其製作方法 | |

| TW202101708A (zh) | 半導體裝置及製造半導體裝置的方法 | |

| TW200910561A (en) | Packaging substrate structure with capacitor embedded therein and method for fabricating the same | |

| KR101061801B1 (ko) | 칩 내장형 다층 인쇄회로기판 및 그 제조방법 | |

| CN101299413A (zh) | 线路板制造工艺 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121116 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121116 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130711 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130730 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20131224 |