JP2010079956A - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP2010079956A JP2010079956A JP2008244454A JP2008244454A JP2010079956A JP 2010079956 A JP2010079956 A JP 2010079956A JP 2008244454 A JP2008244454 A JP 2008244454A JP 2008244454 A JP2008244454 A JP 2008244454A JP 2010079956 A JP2010079956 A JP 2010079956A

- Authority

- JP

- Japan

- Prior art keywords

- refresh

- signal

- data

- memory

- activated

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/04—Arrangements for selecting an address in a digital store using a sequential addressing device, e.g. shift register, counter

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

- G11C11/40615—Internal triggering or timing of refresh, e.g. hidden refresh, self refresh, pseudo-SRAMs

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/401—Indexing scheme relating to cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C2211/4016—Memory devices with silicon-on-insulator cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/401—Indexing scheme relating to cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C2211/406—Refreshing of dynamic cells

- G11C2211/4067—Refresh in standby or low power modes

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

Abstract

【解決手段】メモリは、ワード線とビット線との交点に対応して設けられたメモリセルを含み、データ読出しまたは書込みの単位であるメモリアレイブロックと、ワード線を駆動するロウデコーダと、ビット線を介してデータを検出するセンスアンプと、メモリセルブロックごとに設けられ、データ読出しまたは書込みのために該メモリアレイブロックへアクセスされた回数をカウントし、該アクセス回数が所定回数に達した場合にリフレッシュ要求信号を活性化するアクセスカウンタとを備え、アクセスカウンタのリフレッシュ要求信号が活性化されている期間中に、ロウデコーダは、該アクセスカウンタに対応するメモリアレイブロックのワード線を周期的に順番に活性化し、センスアンプは、活性化されたワード線に接続されたメモリセルをリフレッシュする。

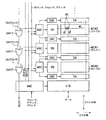

【選択図】図3

Description

Takashi Ohsawa et. al. "An 18.5ns 128Mb SOI DRAM with a Floating Body Cell" , ISSCC2005 Digest of Technical Papers, pp.458-459

前記アクセスカウンタの前記リフレッシュ要求信号が活性化されている期間中に、前記ロウデコーダは、該アクセスカウンタに対応する前記メモリアレイブロックの前記ワード線を周期的に順番に活性化し、前記センスアンプは、活性化された前記ワード線に接続された前記メモリセルの劣化したデータを回復させるリフレッシュ動作を実行することを特徴とする。

図1は、本発明に係る実施形態に従ったFBCメモリの構成を示すブロック図である。FBCメモリは、複数のビット線BLと、複数のワード線WLと、メモリアレイブロックとしてのメモリセルアレイを備えておりそのうちの3つMCA0〜MCA2を図示している。ビット線BLとワード線WLとは、互いに直交している。複数のメモリセルMCが、ビット線BLとワード線WLとの交点に対応して設けられている。複数のメモリセルMCがマトリクス状に二次元配置されメモリセルアレイMCA0〜MCA2を構成している。メモリセルアレイMCA0〜MCA2は、データ読出し動作またはデータ書込み動作の単位である。よって、データ読出し動作またはデータ書込み動作(以下、アクセスともいう)において、メモリセルアレイMCAi(iは整数)に格納されたデータが1単位として読み出され、あるいは、書込みデータはメモリセルアレイMCAiを1単位として書き込まれる。

t1において、読出し命令または書込み命令が入力される。これにより、ブロック活性化信号ACTが活性化される。ブロックアドレスで示されたブロックのANDゲートG41が信号ACTpyyを活性化させる。信号ACTpyyの活性化に伴い、ANDゲートG45がロウアドレスROWADDを通過させる。また、信号ACTpyyの活性化によって、次のクロックで信号LACTpが活性化される。信号LACTpは、ラッチ回路L43でラッチされる。

アクセス回数が所定値に達した場合、t2に示すように、リフレッシュ要求信号CLMTpが活性化される。t2から1クロック後のt3において、信号REFDURpおよび信号CLMTpxが活性化される。尚、信号REFDURpおよび信号CLMTpxの動作は、ラッチ回路L412およびL413によりリフレッシュ要求信号CLMTpよりも1クロック遅延される。信号REFDURpの活性状態は、ラッチ回路L412でラッチされる。信号REFDURpが活性である期間がリフレッシュ期間である。

図8は、本発明に係る第2の実施形態に従ったアレイブロックコントローラABCの構成を示すブロック図である。第2の実施形態は、ANDゲートG414が設けられていない点で第1の実施形態と異なる。第2の実施形態のその他の構成は、第1の実施形態の構成と同様でよい。従って、第2の実施形態は、信号REFEpおよびREFOpに依らず、アクセス回数が所定値に達したときに、そのメモリセルアレイMCA内のワード線WLを連続して選択してリフレッシュ動作を実行する。このとき、連続した一連のクロック信号CLKに合わせて、ワード線WLがアドレス順に連続的に駆動され、かつ、そのワード線WLに接続されたメモリセルMCがリフレッシュされる。

Claims (5)

- 複数のワード線と、

複数のビット線と、

前記ワード線と前記ビット線との交点に対応して設けられたメモリセルを含み、データ読出し動作またはデータ書込み動作の単位であるメモリアレイブロックと、

前記ワード線を選択的に駆動するロウデコーダと、

前記ビット線を介して前記メモリセルからのデータを検出し、あるいは、前記メモリセルへデータを書き込むセンスアンプと、

前記メモリセルブロックごとに設けられ、データ読出しまたはデータ書込みのために該メモリアレイブロックへアクセスされた回数をカウントし、該アクセス回数が所定回数に達した場合にリフレッシュ要求信号を活性化するアクセスカウンタとを備え、

前記アクセスカウンタの前記リフレッシュ要求信号が活性化されている期間中に、前記ロウデコーダは、該アクセスカウンタに対応する前記メモリアレイブロックの前記ワード線を周期的に順番に活性化し、前記センスアンプは、活性化された前記ワード線に接続された前記メモリセルの劣化したデータを回復させるリフレッシュ動作を実行することを特徴とする半導体記憶装置。 - 前記メモリアレイブロックへのアクセスされた回数は、前記メモリセルブロック内のワード線が活性化された回数であることを特徴とする請求項1に記載の半導体記憶装置。

- 或るメモリアレイブロックの前記リフレッシュ動作において、前記ワード線ごとに実行されるリフレッシュサイクルの回数をカウントするリフレッシュカウンタをさらに備え、

前記リフレッシュカウンタは、前記リフレッシュサイクルの回数が所定値に達したとき、前記リフレッシュ動作を終了させるために前記リフレッシュ要求信号を不活性化させることを特徴とする請求項1または請求項2のいずれかに記載の半導体記憶装置。 - 前記メモリアレイブロックに対応して設けられ、前記ワード線ごとに前記リフレッシュ動作が実行されるときに活性化されるリフレッシュ命令を受けて、該リフレッシュ命令が活性状態であるときに、前記メモリセルへのアクセスを禁止するビジー信号を当該装置の外部へ出力するゲート回路をさらに備えたことを特徴とする請求項1から請求項3のいずれかに記載の半導体記憶装置。

- 前記リフレッシュ要求信号が活性化されたときに、前記ロウデコーダは、該アクセスカウンタに対応する前記メモリアレイブロックの前記ワード線を連続して活性化し、前記センスアンプは、活性化された前記ワード線に対して前記リフレッシュ動作を実行することを特徴とする請求項1に記載の半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008244454A JP4843655B2 (ja) | 2008-09-24 | 2008-09-24 | 半導体記憶装置 |

| US12/550,663 US8027216B2 (en) | 2008-09-24 | 2009-08-31 | Semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008244454A JP4843655B2 (ja) | 2008-09-24 | 2008-09-24 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010079956A true JP2010079956A (ja) | 2010-04-08 |

| JP4843655B2 JP4843655B2 (ja) | 2011-12-21 |

Family

ID=42037547

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008244454A Active JP4843655B2 (ja) | 2008-09-24 | 2008-09-24 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8027216B2 (ja) |

| JP (1) | JP4843655B2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013239228A (ja) * | 2012-05-14 | 2013-11-28 | Samsung Electronics Co Ltd | メモリ装置、メモリシステム及びその動作方法 |

| WO2014125937A1 (ja) * | 2013-02-12 | 2014-08-21 | ピーエスフォー ルクスコ エスエイアールエル | 半導体装置 |

| JP2016504702A (ja) * | 2012-11-30 | 2016-02-12 | インテル・コーポレーション | 格納されたロウハンマ閾値に基づくロウハンマの監視 |

| JP2016536666A (ja) * | 2013-10-08 | 2016-11-24 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッドAdvanced Micro Devices Incorporated | 信頼性の高い動作に適したメモリコントローラを有するデータプロセッサ及び方法 |

| JP6429260B1 (ja) * | 2017-11-09 | 2018-11-28 | 華邦電子股▲ふん▼有限公司Winbond Electronics Corp. | 疑似スタティックランダムアクセスメモリおよびそのリフレッシュ方法 |

Families Citing this family (49)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8174881B2 (en) * | 2009-11-24 | 2012-05-08 | Micron Technology, Inc. | Techniques for reducing disturbance in a semiconductor device |

| US20140085995A1 (en) * | 2012-09-25 | 2014-03-27 | Zvika Greenfield | Method, apparatus and system for determining a count of accesses to a row of memory |

| KR20140042546A (ko) * | 2012-09-28 | 2014-04-07 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그 동작 방법 |

| US9286964B2 (en) | 2012-12-21 | 2016-03-15 | Intel Corporation | Method, apparatus and system for responding to a row hammer event |

| US9324398B2 (en) | 2013-02-04 | 2016-04-26 | Micron Technology, Inc. | Apparatuses and methods for targeted refreshing of memory |

| US9047978B2 (en) | 2013-08-26 | 2015-06-02 | Micron Technology, Inc. | Apparatuses and methods for selective row refreshes |

| US9396786B2 (en) * | 2013-09-25 | 2016-07-19 | SK Hynix Inc. | Memory and memory system including the same |

| KR102122892B1 (ko) * | 2013-09-25 | 2020-06-15 | 에스케이하이닉스 주식회사 | 메모리 및 이를 포함하는 메모리 시스템 |

| JP2015076110A (ja) * | 2013-10-08 | 2015-04-20 | マイクロン テクノロジー, インク. | 半導体装置及びこれを備えるデータ処理システム |

| KR102193993B1 (ko) | 2014-02-21 | 2020-12-22 | 삼성전자주식회사 | 메모리 장치 및 이를 포함하는 메모리 시스템 |

| KR102194003B1 (ko) | 2014-02-25 | 2020-12-22 | 삼성전자주식회사 | 메모리 모듈 및 이를 포함하는 메모리 시스템 |

| JP2015219938A (ja) | 2014-05-21 | 2015-12-07 | マイクロン テクノロジー, インク. | 半導体装置 |

| JP2017182854A (ja) | 2016-03-31 | 2017-10-05 | マイクロン テクノロジー, インク. | 半導体装置 |

| US9959921B2 (en) * | 2016-04-01 | 2018-05-01 | Micron Technology, Inc. | Apparatuses and methods for refresh control |

| KR102559530B1 (ko) | 2016-09-19 | 2023-07-27 | 에스케이하이닉스 주식회사 | 저항성 메모리 장치, 이를 위한 디스터번스 방지 회로 및 방법 |

| US10490251B2 (en) | 2017-01-30 | 2019-11-26 | Micron Technology, Inc. | Apparatuses and methods for distributing row hammer refresh events across a memory device |

| US10580475B2 (en) | 2018-01-22 | 2020-03-03 | Micron Technology, Inc. | Apparatuses and methods for calculating row hammer refresh addresses in a semiconductor device |

| WO2019222960A1 (en) | 2018-05-24 | 2019-11-28 | Micron Technology, Inc. | Apparatuses and methods for pure-time, self adopt sampling for row hammer refresh sampling |

| US11152050B2 (en) | 2018-06-19 | 2021-10-19 | Micron Technology, Inc. | Apparatuses and methods for multiple row hammer refresh address sequences |

| US10685696B2 (en) | 2018-10-31 | 2020-06-16 | Micron Technology, Inc. | Apparatuses and methods for access based refresh timing |

| WO2020117686A1 (en) | 2018-12-03 | 2020-06-11 | Micron Technology, Inc. | Semiconductor device performing row hammer refresh operation |

| CN111354393B (zh) | 2018-12-21 | 2023-10-20 | 美光科技公司 | 用于目标刷新操作的时序交错的设备和方法 |

| US10770127B2 (en) | 2019-02-06 | 2020-09-08 | Micron Technology, Inc. | Apparatuses and methods for managing row access counts |

| US11043254B2 (en) | 2019-03-19 | 2021-06-22 | Micron Technology, Inc. | Semiconductor device having cam that stores address signals |

| US11227649B2 (en) | 2019-04-04 | 2022-01-18 | Micron Technology, Inc. | Apparatuses and methods for staggered timing of targeted refresh operations |

| US11264096B2 (en) | 2019-05-14 | 2022-03-01 | Micron Technology, Inc. | Apparatuses, systems, and methods for a content addressable memory cell with latch and comparator circuits |

| US11158364B2 (en) | 2019-05-31 | 2021-10-26 | Micron Technology, Inc. | Apparatuses and methods for tracking victim rows |

| US11069393B2 (en) | 2019-06-04 | 2021-07-20 | Micron Technology, Inc. | Apparatuses and methods for controlling steal rates |

| US11158373B2 (en) | 2019-06-11 | 2021-10-26 | Micron Technology, Inc. | Apparatuses, systems, and methods for determining extremum numerical values |

| US11139015B2 (en) | 2019-07-01 | 2021-10-05 | Micron Technology, Inc. | Apparatuses and methods for monitoring word line accesses |

| US10832792B1 (en) | 2019-07-01 | 2020-11-10 | Micron Technology, Inc. | Apparatuses and methods for adjusting victim data |

| US11386946B2 (en) | 2019-07-16 | 2022-07-12 | Micron Technology, Inc. | Apparatuses and methods for tracking row accesses |

| US10943636B1 (en) | 2019-08-20 | 2021-03-09 | Micron Technology, Inc. | Apparatuses and methods for analog row access tracking |

| US10964378B2 (en) | 2019-08-22 | 2021-03-30 | Micron Technology, Inc. | Apparatus and method including analog accumulator for determining row access rate and target row address used for refresh operation |

| US11302374B2 (en) | 2019-08-23 | 2022-04-12 | Micron Technology, Inc. | Apparatuses and methods for dynamic refresh allocation |

| US11200942B2 (en) | 2019-08-23 | 2021-12-14 | Micron Technology, Inc. | Apparatuses and methods for lossy row access counting |

| US11302377B2 (en) | 2019-10-16 | 2022-04-12 | Micron Technology, Inc. | Apparatuses and methods for dynamic targeted refresh steals |

| US11309010B2 (en) | 2020-08-14 | 2022-04-19 | Micron Technology, Inc. | Apparatuses, systems, and methods for memory directed access pause |

| US11348631B2 (en) | 2020-08-19 | 2022-05-31 | Micron Technology, Inc. | Apparatuses, systems, and methods for identifying victim rows in a memory device which cannot be simultaneously refreshed |

| US11380382B2 (en) | 2020-08-19 | 2022-07-05 | Micron Technology, Inc. | Refresh logic circuit layout having aggressor detector circuit sampling circuit and row hammer refresh control circuit |

| US11222682B1 (en) | 2020-08-31 | 2022-01-11 | Micron Technology, Inc. | Apparatuses and methods for providing refresh addresses |

| US11557331B2 (en) | 2020-09-23 | 2023-01-17 | Micron Technology, Inc. | Apparatuses and methods for controlling refresh operations |

| US11222686B1 (en) | 2020-11-12 | 2022-01-11 | Micron Technology, Inc. | Apparatuses and methods for controlling refresh timing |

| US11462291B2 (en) | 2020-11-23 | 2022-10-04 | Micron Technology, Inc. | Apparatuses and methods for tracking word line accesses |

| US11264079B1 (en) | 2020-12-18 | 2022-03-01 | Micron Technology, Inc. | Apparatuses and methods for row hammer based cache lockdown |

| US11482275B2 (en) | 2021-01-20 | 2022-10-25 | Micron Technology, Inc. | Apparatuses and methods for dynamically allocated aggressor detection |

| US11600314B2 (en) | 2021-03-15 | 2023-03-07 | Micron Technology, Inc. | Apparatuses and methods for sketch circuits for refresh binning |

| US11664063B2 (en) | 2021-08-12 | 2023-05-30 | Micron Technology, Inc. | Apparatuses and methods for countering memory attacks |

| US11688451B2 (en) | 2021-11-29 | 2023-06-27 | Micron Technology, Inc. | Apparatuses, systems, and methods for main sketch and slim sketch circuit for row address tracking |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09265784A (ja) * | 1996-03-25 | 1997-10-07 | Sharp Corp | 不揮発性半導体記憶装置 |

| JP2003007051A (ja) * | 2001-06-27 | 2003-01-10 | Sanyo Electric Co Ltd | メモリおよびその動作方法 |

| JP2004079162A (ja) * | 2002-08-12 | 2004-03-11 | Samsung Electronics Co Ltd | リフレッシュフラグを発生させる半導体メモリ装置及び半導体メモリシステム |

| JP2005251256A (ja) * | 2004-03-02 | 2005-09-15 | Toshiba Microelectronics Corp | 半導体記憶装置 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07153266A (ja) * | 1993-11-26 | 1995-06-16 | Mitsubishi Electric Corp | Dram制御回路 |

| US6741515B2 (en) * | 2002-06-18 | 2004-05-25 | Nanoamp Solutions, Inc. | DRAM with total self refresh and control circuit |

| JP4362573B2 (ja) * | 2005-07-28 | 2009-11-11 | パトレネラ キャピタル リミテッド, エルエルシー | メモリ |

| JP5157207B2 (ja) * | 2007-03-16 | 2013-03-06 | 富士通セミコンダクター株式会社 | 半導体メモリ、メモリコントローラ、システムおよび半導体メモリの動作方法 |

-

2008

- 2008-09-24 JP JP2008244454A patent/JP4843655B2/ja active Active

-

2009

- 2009-08-31 US US12/550,663 patent/US8027216B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09265784A (ja) * | 1996-03-25 | 1997-10-07 | Sharp Corp | 不揮発性半導体記憶装置 |

| JP2003007051A (ja) * | 2001-06-27 | 2003-01-10 | Sanyo Electric Co Ltd | メモリおよびその動作方法 |

| JP2004079162A (ja) * | 2002-08-12 | 2004-03-11 | Samsung Electronics Co Ltd | リフレッシュフラグを発生させる半導体メモリ装置及び半導体メモリシステム |

| JP2005251256A (ja) * | 2004-03-02 | 2005-09-15 | Toshiba Microelectronics Corp | 半導体記憶装置 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013239228A (ja) * | 2012-05-14 | 2013-11-28 | Samsung Electronics Co Ltd | メモリ装置、メモリシステム及びその動作方法 |

| JP2016504702A (ja) * | 2012-11-30 | 2016-02-12 | インテル・コーポレーション | 格納されたロウハンマ閾値に基づくロウハンマの監視 |

| WO2014125937A1 (ja) * | 2013-02-12 | 2014-08-21 | ピーエスフォー ルクスコ エスエイアールエル | 半導体装置 |

| JP2016536666A (ja) * | 2013-10-08 | 2016-11-24 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッドAdvanced Micro Devices Incorporated | 信頼性の高い動作に適したメモリコントローラを有するデータプロセッサ及び方法 |

| JP6429260B1 (ja) * | 2017-11-09 | 2018-11-28 | 華邦電子股▲ふん▼有限公司Winbond Electronics Corp. | 疑似スタティックランダムアクセスメモリおよびそのリフレッシュ方法 |

| CN109767797A (zh) * | 2017-11-09 | 2019-05-17 | 华邦电子股份有限公司 | 伪静态随机存取存储器及其刷新的方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4843655B2 (ja) | 2011-12-21 |

| US8027216B2 (en) | 2011-09-27 |

| US20100074042A1 (en) | 2010-03-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4843655B2 (ja) | 半導体記憶装置 | |

| KR100443909B1 (ko) | 반도체 메모리 장치의 부분 어레이 셀프 리플레쉬 동작을수행하기 위한 장치 및 방법 | |

| JP4609813B2 (ja) | 半導体装置 | |

| JP4524645B2 (ja) | 半導体装置 | |

| KR100269526B1 (ko) | 데이타유지모드시전류소비가감소된반도체기억장치 | |

| US7352642B2 (en) | Semiconductor memory device | |

| US10504582B2 (en) | Timing control circuit shared by a plurality of banks | |

| JP2005158199A (ja) | 半導体集積回路装置 | |

| JP2003297080A (ja) | 半導体記憶装置 | |

| KR20150033949A (ko) | 메모리 및 이를 포함하는 메모리 시스템 | |

| JP4362573B2 (ja) | メモリ | |

| KR100412131B1 (ko) | 반도체 메모리 장치의 셀 데이타 보호회로 | |

| KR100524844B1 (ko) | 완전 히든 리프레쉬 다이나믹 랜덤 액세스 메모리 | |

| JP2018125058A (ja) | メモリデバイス及びメモリデバイスの動作方法 | |

| KR100805528B1 (ko) | 반도체 메모리 장치에서의 선택적 리프레시 방법 및 시스템 | |

| JP2004062925A (ja) | 半導体メモリ | |

| US6501701B2 (en) | Semiconductor memory device | |

| JP2015232772A (ja) | システムの制御方法及びシステム | |

| US11837276B2 (en) | Apparatuses and methods for 1T and 2T memory cell architectures | |

| KR100857428B1 (ko) | 반도체 메모리 장치의 워드 라인 선택회로 및 방법 | |

| US20060215475A1 (en) | Wordline enable circuit in semiconductor memory device and method thereof | |

| KR100352967B1 (ko) | 제어 신호에 노이즈가 중첩되어도 리프레시 동작의오동작이 생기지 않는 반도체 기억 장치 | |

| KR100665903B1 (ko) | 반도체 메모리 장치 | |

| KR100630976B1 (ko) | 로우 바운더리 구간에서 리프레쉬가 수행되는 디램셀에스램 | |

| JP2015191676A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100914 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110111 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110114 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110314 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110405 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110909 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111007 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4843655 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141014 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |