JP2010040820A - 不揮発性記憶装置及びその製造方法 - Google Patents

不揮発性記憶装置及びその製造方法 Download PDFInfo

- Publication number

- JP2010040820A JP2010040820A JP2008202771A JP2008202771A JP2010040820A JP 2010040820 A JP2010040820 A JP 2010040820A JP 2008202771 A JP2008202771 A JP 2008202771A JP 2008202771 A JP2008202771 A JP 2008202771A JP 2010040820 A JP2010040820 A JP 2010040820A

- Authority

- JP

- Japan

- Prior art keywords

- film

- phase change

- interlayer film

- metal

- change material

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/231—Multistable switching devices, e.g. memristors based on solid-state phase change, e.g. between amorphous and crystalline phases, Ovshinsky effect

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5678—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using amorphous/crystalline phase transition storage elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0004—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising amorphous/crystalline phase transition cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/20—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having two electrodes, e.g. diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

- H10B63/84—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays arranged in a direction perpendicular to the substrate, e.g. 3D cell arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/061—Shaping switching materials

- H10N70/063—Shaping switching materials by etching of pre-deposited switching material layers, e.g. lithography

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/861—Thermal details

- H10N70/8616—Thermal insulation means

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

- H10N70/8825—Selenides, e.g. GeSe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

- H10N70/8828—Tellurides, e.g. GeSbTe

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/72—Array wherein the access device being a diode

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S438/00—Semiconductor device manufacturing: process

- Y10S438/90—Bulk effect device making

Landscapes

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

Abstract

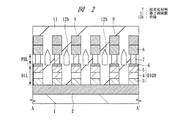

【解決手段】第1方向に沿って延びる複数の第1金属配線2と、第1方向と直交する第2方向に沿って延びる複数の第3金属配線9との交点に、相変化材料7からなる記憶素子と、第1多結晶シリコン膜3、第2多結晶シリコン膜4及び第3多結晶シリコン膜5の積層構造のダイオードからなる選択素子とによって構成されるメモリセルを配置し、隣接する選択素子の間及び隣接する記憶素子の間に層間膜(例えば第2層間膜11)を形成し、隣接する記憶素子の間に設けられた層間膜に空隙(例えば空隙12b)を形成する。

【選択図】図2

Description

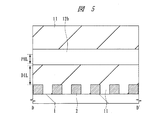

本実施の形態1による相変化メモリのメモリマトリクスを図1〜図5を用いて説明する。図1はメモリマトリクスの上面図、図2は図1のA−A’線におけるメモリマトリクスの要部断面図、図3は図1のB−B’線におけるメモリマトリクスの要部断面図、図4は図1のC−C’線におけるメモリマトリクスの要部断面図、図5は図1のD−D’線におけるメモリマトリクスの要部断面図である。図1では、メモリマトリクスの構造をわかりやすくするために、第3金属配線、第1金属配線及び半導体基板のみを示している。

本実施の形態2による相変化メモリのメモリマトリクスについて図23〜図25を用いて説明する。図23はメモリマトリクスの上面図、図24は図23のA−A’線におけるメモリマトリクスの要部断面図、図25は図23のB−B’線におけるメモリマトリクスの要部断面図である。図23では、メモリマトリクスの構造をわかりやすくするために、第3金属配線、第1金属配線及び半導体基板のみを示している。図中、前述した実施の形態1と同様に、符号1は半導体基板、符号2は第1方向に沿って延びる第1金属配線である。また、符号3は第1多結晶シリコン膜、符号4は第2多結晶シリコン膜、符号5は第3多結晶シリコン膜であり、これら3層で選択素子であるダイオードDIODを形成している。また、符号6はバッファ層(例えばTiN)、符号7は記憶素子である相変化材料(例えばGe2Sb2Te5)、符号8は第2金属配線(例えばTiN)、符号9は第3金属配線である。さらに、符号21は第1層間膜(例えばTEOS)、22は第1層間膜の被覆形状により生じる空間を充填する第2層間膜(例えばポーラスMSQ(Methylsilses-quioxane))、23は第3層間膜(例えばTEOS)、24は第3層間膜の被覆形状により生じる空間を充填する第4層間膜(例えばポーラスMSQ)である。TEOSの熱伝導率は約1.4W/(m・K)、ポーラスMSQの熱伝導率は約0.2W/(m・K)である。

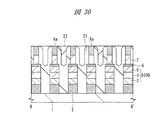

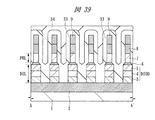

本実施の形態3による相変化メモリのメモリマトリクスについて図38〜図40を用いて説明する。図38はメモリマトリクスの上面図、図39は図38のA−A’線におけるメモリマトリクスの要部断面図、図40は図38のB−B’線におけるメモリマトリクスの要部断面図である。図38では、メモリマトリクスの構造をわかりやすくするために、第3金属配線、第1金属配線及び半導体基板のみを示している。図中、前述した実施の形態1と同様に、符号1は半導体基板、符号2は第1方向に沿って延びる第1金属配線である。また、符号3は第1多結晶シリコン膜、符号4は第2多結晶シリコン膜、符号5は第3多結晶シリコン膜であり、これら3層で選択素子であるダイオードDIODを形成している。また、符号6はバッファ層(例えばTiN)、符号7は記憶素子である相変化材料(例えばGe2Sb2Te5)、符号8は第2金属配線(例えばTiN)、符号9は第3金属配線である。さらに、符号31は第1層間膜(例えばTEOS)、32は第1層間膜の被覆形状により生じる空間を充填する第2層間膜(例えばポーラスMSQ)、33は第3層間膜(例えばTEOS)、34は第3層間膜の被覆形状により生じる空間を充填する第4層間膜(例えばポーラスMSQ)である。

本実施の形態4による相変化メモリのメモリマトリクスについて図47〜図49を用いて説明する。図47はメモリマトリクスの上面図、図48は図47のA−A’線におけるメモリマトリクスの要部断面図、図49は図47のB−B’線におけるメモリマトリクスの要部断面図である。図47では、メモリマトリクスの構造をわかりやすくするために、第3金属配線、第1金属配線及び半導体基板のみを示している。図中、前述した実施の形態1と同様に、符号1は半導体基板、符号2は第1方向に沿って延びる第1金属配線である。また、符号3は第1多結晶シリコン膜、符号4は第2多結晶シリコン膜、符号5は第3多結晶シリコン膜であり、これら3層で選択素子であるダイオードDIODを形成している。また、符号7は記憶素子である相変化材料(例えばGe2Sb2Te5)、符号8は第2金属配線(例えばTiN)、符号9は第3金属配線である。さらに、符号41a,41bはバッファ層(例えばTiN)、符号42は第1層間膜(例えばTEOS)、43は第2層間膜(例えばTEOS)、44は第3層間膜(例えばポーラスMSQ)、45は第4層間膜(例えばポーラスMSQ)である。

2,2A 第1金属配線

2a 第1金属膜

3,3A 第1多結晶シリコン膜

4,4A 第2多結晶シリコン膜

5,5A 第3多結晶シリコン膜

6,6A バッファ層

7,7A 相変化材料

8,8A 第2金属配線

8a 第2金属膜

9,9A 第3金属配線

9a 第3金属膜

10 第1層間膜

11,11A 第2層間膜

12a,12b,12bA 空隙

21 第1層間膜

22 第2層間膜

23,23A 第3層間膜

24,24A 第4層間膜

31 第1層間膜

32 第2層間膜

33 第3層間膜

34 第4層間膜

41a,41b バッファ層

42 第1層間膜

43 第2層間膜

44 第3層間膜

45 第4層間膜

101 半導体基板

102 第1金属配線

103 第1多結晶シリコン膜

104 第2多結晶シリコン膜

105 第3多結晶シリコン膜

106 バッファ層

107 相変化材料

108 第2金属配線

109 第3金属配線

110 層間膜

DIOD,CDIOD ダイオード

DIL,CDIL ダイオードが設けられた層

PHL,CPHL 相変化材料が設けられた層

WL1 1番目のワード線

WL2 2番目のワード線

WLi i番目のワード線

WLm m番目のワード線

BL1 1番目のビット線

BL2 2番目のビット線

BLj j番目のビット線

BLn n番目のビット線

SE 選択素子

VR 相変化抵抗素子

MC11 1番目のワード線と1番目のビット線の交点にあるメモリセル

MCi1 i番目のワード線と1番目のビット線の交点にあるメモリセル

MCm1 m番目のワード線と1番目のビット線の交点にあるメモリセル

MC1j 1番目のワード線とj番目のビット線の交点にあるメモリセル

MCij i番目のワード線とj番目のビット線の交点にあるメモリセル

MCmj m番目のワード線とj番目のビット線の交点にあるメモリセル

MC1n 1番目のワード線とn番目のビット線の交点にあるメモリセル

MCin i番目のワード線とn番目のビット線の交点にあるメモリセル

MCmn m番目のワード線とn番目のビット線の交点にあるメモリセル

GAT ゲート

DIF 拡散層

A1ST,A2ST トランジスタ

A1CNT,A2CNT コンタクト

A1M1,A1M2,A1M3,A1M4 金属電極

A2M1,A2M2,A2M3,A2M4 金属配線

A1M1M,A1M2M 金属配線

A2M3M,A2M4M 金属配線

A1TH1,A1TH2,A1TH3 プラグ電極

A2TH1,A2TH2,A2TH3 プラグ電極

B1ST,B2ST トランジスタ

B1CNT,B2CNT コンタクト

B1M1,B1M2,B1M3,B1M4,B1M5 金属配線

B2M1,B2M2,B2M3,B2M4,B2M5 金属配線

B1M2M,B1M3M,B1M4M,B1M5M 金属配線

B2M1M,B2M2M,B2M3M,B2M4M 金属配線

B1TH1,B1TH2,B1TH3 プラグ電極

B2TH1,B2TH2,B2TH3 プラグ電極

GWL グローバルワード線

GBL グローバルビット線

Claims (23)

- 第1方向に沿って延びる複数の第1金属配線と、

前記第1方向と直交する第2方向に沿って延びる複数の第3金属配線と、

前記第1金属配線と前記第3金属配線との交点に記憶素子と選択素子とから成るメモリセルによって構成された不揮発性メモリを有する不揮発性記憶装置において、

前記メモリセルは、

半導体基板と、

前記半導体基板上に周辺回路と電気的に接続して設けられた前記第1金属配線と、

前記第1金属配線上に前記第1金属配線と電気的に接続して設けられた前記選択素子と、

前記選択素子上に前記選択素子と電気的に接続して設けられた前記記憶素子と、

前記記憶素子上に前記記憶素子と電気的に接続して設けられた第2金属配線と、

前記第2金属配線上に前記第2金属配線と電気的に接続し、かつ周辺回路と電気的に接続して設けられた前記第3金属配線と、

隣接する前記記憶素子間に空隙を有して、隣接する記憶素子間及び隣接する選択素子間を埋める層間膜とを含むことを特徴とする不揮発性記憶装置。 - 請求項1記載の不揮発性記憶装置において、前記選択素子はダイオードであり、前記記憶素子は相変化材料であることを特徴とする不揮発性記憶装置。

- 請求項1記載の不揮発性記憶装置において、前記記憶素子の幅が前記選択素子の幅よりも狭く、かつ前記第2金属配線の幅が前記記憶素子の幅よりも大きいことを特徴とする不揮発性記憶装置。

- 請求項1記載の不揮発性記憶装置において、隣接する前記選択素子間の前記層間膜の充填率は、選択素子の重心とこれに隣接する選択素子の重心とを結ぶ平面において75%以上であり、隣接する前記記憶素子間の前記層間膜の充填率は、記憶素子の重心とこれに隣接する記憶素子の重心とを結ぶ平面において75%以下50%以上であることを特徴とする不揮発性記憶装置。

- 請求項1記載の不揮発性記憶装置において、前記第1方向に隣接する前記記憶素子間の前記層間膜に形成された前記空隙の幅が、前記第2方向に隣接する前記記憶素子間の前記層間膜に形成された前記空隙の幅よりも広いことを特徴とする不揮発性記憶装置。

- 第1方向に沿って延びる複数の第1金属配線と、

前記第1方向と直交する第2方向に沿って延びる複数の第3金属配線と、

前記第1金属配線と前記第3金属配線との交点に記憶素子と選択素子とから成るメモリセルによって構成された不揮発性メモリを有する不揮発性記憶装置において、

前記メモリセルは、

半導体基板と、

前記半導体基板上に周辺回路と電気的に接続して設けられた前記第1金属配線と、

前記第1金属配線上に前記第1金属配線と電気的に接続して設けられた前記選択素子と、

前記選択素子上に前記選択素子と電気的に接続して設けられた前記記憶素子と、

前記記憶素子上に前記記憶素子と電気的に接続して設けられた第2金属配線と、

前記第2金属配線上に前記第2金属配線と電気的に接続し、かつ周辺回路と電気的に接続して設けられた前記第3金属配線と、

隣接する前記記憶素子間を埋めずに前記記憶素子の側面を被覆し、隣接する前記選択素子間を埋める第1熱伝導率の層間膜と、

前記記憶素子の側面を被覆する前記第1熱伝導率の層間膜により形成される空間を埋める第2熱伝導率の層間膜とを含み、

前記第2熱伝導率が前記第1熱伝導率よりも低いことを特徴とする不揮発性記憶装置。 - 請求項6記載の不揮発性記憶装置において、前記選択素子はダイオードであり、前記記憶素子は相変化材料であることを特徴とする不揮発性記憶装置。

- 請求項6記載の不揮発性記憶装置において、前記第1熱伝導率の層間膜はTEOSであり、前記第2熱伝導率の層間膜はポーラスMSQであることを特徴とする不揮発性記憶装置。

- 請求項6記載の不揮発性記憶装置において、隣接する前記選択素子間の前記第2熱伝導率の層間膜の充填率は、選択素子の重心とこれに隣接する選択素子の重心とを結ぶ平面において25%以下であり、隣接する前記記憶素子間の前記第2熱伝導率の層間膜の充填率は、記憶素子の重心とこれに隣接する記憶素子の重心とを結ぶ平面において50%以下25%以上であることを特徴とする不揮発性記憶装置。

- 第1方向に沿って延びる複数の第1金属配線と、

前記第1方向と直交する第2方向に沿って延びる複数の第3金属配線と、

前記第1金属配線と前記第3金属配線との交点に記憶素子と選択素子とから成るメモリセルによって構成された不揮発性メモリを有する不揮発性記憶装置において、

前記メモリセルは、

半導体基板と、

前記半導体基板上に周辺回路と電気的に接続して設けられた前記第1金属配線と、

前記第1金属配線上に前記第1金属配線と電気的に接続して設けられた前記選択素子と、

前記選択素子上に前記選択素子と電気的に接続して設けられた前記記憶素子と、

前記記憶素子上に前記記憶素子と電気的に接続して設けられた第2金属配線と、

前記第2金属配線上に前記第2金属配線と電気的に接続し、かつ周辺回路と電気的に接続して設けられた前記第3金属配線と、

隣接する前記選択素子間を埋める第1熱伝導率の層間膜と、

隣接する前記記憶素子間を埋める第2熱伝導率の層間膜とを含み、

前記第2熱伝導率が前記第1熱伝導率よりも低いことを特徴とする不揮発性記憶装置。 - 請求項10記載の不揮発性記憶装置において、前記選択素子はダイオードであり、前記記憶素子は相変化材料であることを特徴とする不揮発性記憶装置。

- 請求項10記載の不揮発性記憶装置において、前記第1熱伝導率の層間膜はTEOSであり、前記第2熱伝導率の層間膜はポーラスMSQであることを特徴とする不揮発性記憶装置。

- 請求項1、6または10のいずれか1項に記載の不揮発性記憶装置において、前記選択素子と前記記憶素子との間にはバッファ層が形成されていることを特徴とする不揮発性記憶装置。

- (a)半導体基板上に第1金属膜、選択素子材料、バッファ層、相変化材料及び第2金属膜を順次形成する工程と、

(b)第1方向に沿って前記第2金属膜、前記相変化材料、前記バッファ層、前記選択素子材料及び前記第1金属膜を順次エッチングして、前記相変化材料の幅が前記バッファ層または前記選択素子材料の幅よりも狭いストライプ状に加工する工程と、

(c)前記半導体基板上に第1層間膜を形成して、隣接する前記第2金属膜、前記相変化材料、前記バッファ層、前記選択素子材料及び前記第1金属膜の積層パターンの間を前記第1層間膜により埋める工程と、

(d)前記第1層間膜の表面を研磨して、前記第2金属膜の上面を露出させる工程と、

(e)前記半導体基板上に第3金属膜を形成する工程と、

(f)前記第1方向と直交する第2方向に沿って前記第3金属膜、前記第2金属膜、前記相変化材料、前記バッファ層及び前記選択素子材料を順次エッチングして、前記相変化材料の幅が前記バッファ層または前記選択素子材料の幅よりも狭いストライプ状に加工する工程と、

(g)前記半導体基板上に第2層間膜を形成して、隣接する前記第3金属膜、前記第2金属膜、前記相変化材料、前記バッファ層、前記選択素子材料及び前記第1金属膜の積層パターンの間を前記第2層間膜により埋める工程と、

を有し、

隣接する前記相変化材料の間の前記(c)工程で形成される前記第1層間膜及び前記(g)工程で形成される前記第2層間膜に、空隙を形成することを特徴とする不揮発性記憶装置の製造方法。 - (a)半導体基板上に第1金属膜、選択素子材料、バッファ層、相変化材料及び第2金属膜を順次形成する工程と、

(b)第1方向に沿って前記第2金属膜、前記相変化材料、前記バッファ層、前記選択素子材料及び前記第1金属膜を順次エッチングして、ストライプ状に加工する工程と、

(c)前記第2金属膜及び前記相変化材料の前記第1方向に沿った側面をエッチングして、前記第2金属膜及び前記相変化材料を細く加工する工程と、

(d)前記半導体基板上に第1層間膜を形成して、前記第2金属膜及び前記相変化材料の側面を被覆して、隣接する前記第2金属膜及び前記相変化材料の積層パターンの間を埋めずに空間を形成し、同時に、隣接する前記バッファ層、前記選択素子材料及び前記第1金属膜の積層パターンの間を埋める工程と、

(e)前記第1層間膜をエッチバックする工程と、

(f)前記半導体基板上に第2層間膜を形成して、隣接する前記第2金属膜及び前記相変化材料の積層パターンの間の空間を埋めた後、前記第2層間膜の表面を研磨して前記第2金属膜の上面を露出させる工程と、

(g)前記半導体基板上に第3金属膜を形成する工程と、

(h)前記第1方向と直交する第2方向に沿って前記第3金属膜、前記第2金属膜、前記相変化材料、前記バッファ層及び前記選択素子材料を順次エッチングして、ストライプ状に加工する工程と、

(i)前記第2金属膜及び前記相変化材料の前記第2方向に沿った側面をエッチングして、前記第2金属膜及び前記相変化材料を細く加工する工程と、

(j)前記半導体基板上に第3層間膜を形成して、前記第2金属膜及び前記相変化材料の側面を被覆して、隣接する前記第2金属膜及び前記相変化材料の積層パターンの間を埋めずに空間を形成し、同時に、隣接する前記バッファ層、前記選択素子材料及び前記第1金属膜の積層パターンの間を埋める工程と、

(k)前記第3層間膜をエッチバックする工程と、

(l)前記半導体基板上に第4層間膜を形成して、隣接する前記第2金属膜及び前記相変化材料の積層パターンの間の空間を埋める工程と、

を有することを特徴とする不揮発性記憶装置の製造方法。 - (a)半導体基板上に第1金属膜、選択素子材料、バッファ層、相変化材料及び第2金属膜を順次形成する工程と、

(b)第1方向に沿って前記第2金属膜、前記相変化材料、前記バッファ層、前記選択素子材料及び前記第1金属膜を順次エッチングして、ストライプ状に加工する工程と、

(c)前記第2金属膜及び前記相変化材料の前記第1方向に沿った側面をエッチングして、前記第2金属膜及び前記相変化材料を細く加工する工程と、

(d)前記半導体基板上に第1層間膜を形成して、隣接する前記第2金属膜、前記相変化材料、前記バッファ層、前記選択素子材料及び前記第1金属膜の積層パターンの間を埋める工程と、

(e)前記第1層間膜をエッチバックして、隣接する前記第2金属膜及び前記相変化材料の積層パターンの間の前記第1層間膜を除去する工程と、

(f)前記半導体基板上に第2層間膜を形成して、隣接する前記第2金属膜及び前記相変化材料の積層パターンの間を埋めた後、前記第2層間膜の表面を研磨して前記第2金属膜の上面を露出させる工程と、

(g)前記半導体基板上に第3金属膜を形成する工程と、

(h)前記第1方向と直交する第2方向に沿って前記第3金属膜、前記第2金属膜、前記相変化材料、前記バッファ層及び前記選択素子材料を順次エッチングして、ストライプ状に加工する工程と、

(i)前記第2金属膜及び前記相変化材料の前記第2方向に沿った側面をエッチングして、前記第2金属膜及び前記相変化材料を細く加工する工程と、

(j)前記半導体基板上に第3層間膜を形成して、隣接する前記第2金属膜、前記相変化材料、前記バッファ層、前記選択素子材料及び前記第1金属膜の積層パターンの間を埋める工程と、

(k)前記第3層間膜をエッチバックして、隣接する前記第3金属膜、前記第2金属膜及び前記相変化材料の積層パターンの間の前記第3層間膜を除去する工程と、

(l)前記半導体基板上に第4層間膜を形成して、隣接する前記第3金属膜、前記第2金属膜及び前記相変化材料の積層パターンの間を埋める工程と、

を有することを特徴とする不揮発性記憶装置の製造方法。 - 請求項15、または16のいずれか1項に記載の不揮発性記憶装置の製造方法において、前記第2層間膜及び前記第4層間膜の熱伝導率が前記第1層間膜及び前記第3層間膜の熱伝導率よりも低いことを特徴とする不揮発性記憶装置の製造方法。

- 請求項15、または16のいずれか1項に記載の不揮発性記憶装置の製造方法において、前記第1層間膜及び前記第3層間膜はTEOSであり、前記第2層間膜及び前記第4層間膜はポーラスMSQであることを特徴とする不揮発性記憶装置の製造方法。

- (a)半導体基板上に第1金属膜、選択素子材料及び第1バッファ層を順次形成する工程と、

(b)第1方向に沿って前記第1バッファ層、前記選択素子材料及び前記第1金属膜を順次エッチングして、ストライプ状に加工する工程と、

(c)前記半導体基板上に第1層間膜を形成して、隣接する前記第1バッファ層、前記選択素子材料及び前記第1金属膜の積層パターンの間を埋める工程と、

(d)前記第1層間膜の表面を研磨して前記第1バッファ層の上面を露出させる工程と、

(e)前記第1方向と直交する第2方向に沿って前記第1バッファ層及び前記選択素子材料を順次エッチングして、ストライプ状に加工する工程と、

(f)前記半導体基板上に第2層間膜を形成して、隣接する前記第1バッファ層、前記選択素子材料及び第1金属膜の積層パターンの間を埋める工程と、

(g)前記第2層間膜の表面を研磨して前記第1バッファ層の上面を露出させる工程と、

(h)前記半導体基板上に第2バッファ層、相変化材料及び第2金属膜を順次形成する工程と、

(i)前記第1方向に沿って前記第2金属膜、前記相変化材料及び前記第2バッファ層を順次エッチングして、ストライプ状に加工する工程と、

(j)前記半導体基板上に第3層間膜を形成して、隣接する前記第2金属膜、前記相変化材料及び前記第2バッファ層の積層パターンの間を埋める工程と、

(k)前記第3層間膜の表面を研磨して前記第2金属膜の上面を露出させる工程と、

(l)前記第2方向に沿って前記第2金属膜、前記相変化材料及び前記第2バッファ層を順次エッチングして、ストライプ状に加工する工程と、

(m)前記半導体基板上に第4層間膜を形成して、隣接する前記第2金属膜、前記相変化材料及び前記第2バッファ層の積層パターンの間を埋める工程と、

(n)前記第4層間膜の表面を研磨して前記第2金属膜の上面を露出させる工程と、

(o)前記半導体基板上に第3金属膜を形成する工程と、

(p)前記第2方向に沿って前記第3金属膜をエッチングして、ストライプ状に加工する工程と、

を有することを特徴とする不揮発性記憶装置の製造方法。 - 請求項19記載の不揮発性記憶装置の製造方法において、前記第3層間膜及び前記第4層間膜の熱伝導率が前記第1層間膜及び前記第2層間膜の熱伝導率よりも低いことを特徴とする不揮発性記憶装置の製造方法。

- 請求項19記載の不揮発性記憶装置の製造方法において、前記第1層間膜及び前記第2層間膜はTEOSであり、前記第3層間膜及び前記第4層間膜はポーラスMSQであることを特徴とする不揮発性記憶装置の製造方法。

- 請求項14、15、16または19のいずれか1項に記載の不揮発性記憶装置の製造方法において、前記選択素子材料は、第1多結晶シリコン膜、第2多結晶シリコン膜及び第3多結晶シリコン膜を下層から順に積層した構造であり、前記第1多結晶シリコン膜は第1導電型の不純物を含み、第3多結晶シリコン膜は前記第1導電型と異なる第2導電型を含み、前記第1多結晶シリコン膜及び前記第3多結晶シリコン膜の不純物濃度は前記第2多結晶シリコン膜の不純物濃度よりも高いことを特徴とする不揮発性記憶装置の製造方法。

- 請求項14、15、16または19のいずれか1項に記載の不揮発性記憶装置の製造方法において、前記相変化材料は、カルコゲン元素のうちの少なくとも1元素を含むことを特徴とする不揮発性記憶装置の製造方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008202771A JP5342189B2 (ja) | 2008-08-06 | 2008-08-06 | 不揮発性記憶装置及びその製造方法 |

| TW098112705A TWI400797B (zh) | 2008-08-06 | 2009-04-16 | 非揮發性記憶裝置及其製造方法 |

| US12/434,633 US8129705B2 (en) | 2008-08-06 | 2009-05-02 | Nonvolatile memory device and method of manufacturing the same |

| KR1020090044433A KR101148693B1 (ko) | 2008-08-06 | 2009-05-21 | 불휘발성 기억 장치 및 그 제조 방법 |

| CN200910139391.4A CN101645453B (zh) | 2008-08-06 | 2009-05-21 | 非易失性存储装置及其制造方法 |

| US13/366,544 US8604456B2 (en) | 2008-08-06 | 2012-02-06 | Nonvolatile memory device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008202771A JP5342189B2 (ja) | 2008-08-06 | 2008-08-06 | 不揮発性記憶装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010040820A true JP2010040820A (ja) | 2010-02-18 |

| JP2010040820A5 JP2010040820A5 (ja) | 2011-04-14 |

| JP5342189B2 JP5342189B2 (ja) | 2013-11-13 |

Family

ID=41652030

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008202771A Expired - Fee Related JP5342189B2 (ja) | 2008-08-06 | 2008-08-06 | 不揮発性記憶装置及びその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US8129705B2 (ja) |

| JP (1) | JP5342189B2 (ja) |

| KR (1) | KR101148693B1 (ja) |

| CN (1) | CN101645453B (ja) |

| TW (1) | TWI400797B (ja) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010186872A (ja) * | 2009-02-12 | 2010-08-26 | Toshiba Corp | 半導体記憶装置、及びその製造方法 |

| WO2011086725A1 (ja) * | 2010-01-15 | 2011-07-21 | 株式会社日立製作所 | 不揮発性記憶装置およびその製造方法 |

| JP2011243738A (ja) * | 2010-05-18 | 2011-12-01 | Hitachi Ltd | 不揮発性記憶装置およびその製造方法 |

| JP2012059827A (ja) * | 2010-09-07 | 2012-03-22 | Elpida Memory Inc | 半導体装置およびその製造方法 |

| JP2014120606A (ja) * | 2012-12-17 | 2014-06-30 | Hitachi Ltd | 不揮発性記憶装置 |

| US8785980B2 (en) | 2012-03-23 | 2014-07-22 | Kabushiki Kaisha Toshiba | Semiconductor memory device having a low resistance wiring line and method of manufacturing the same |

| JP2017537470A (ja) * | 2014-11-07 | 2017-12-14 | マイクロン テクノロジー, インク. | クロスポイントメモリと、その製造方法 |

| JP2018512728A (ja) * | 2015-03-19 | 2018-05-17 | マイクロン テクノロジー, インク. | 積層メモリアレイを含む構造体 |

| WO2018203459A1 (ja) * | 2017-05-01 | 2018-11-08 | ソニーセミコンダクタソリューションズ株式会社 | 選択素子および記憶装置 |

| JP2020515046A (ja) * | 2017-01-17 | 2020-05-21 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | 閾値スイッチング材料による閉じ込め相変化メモリの集積 |

Families Citing this family (60)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8203134B2 (en) * | 2009-09-21 | 2012-06-19 | Micron Technology, Inc. | Memory devices with enhanced isolation of memory cells, systems including same and methods of forming same |

| JP2011171393A (ja) * | 2010-02-16 | 2011-09-01 | Toshiba Corp | 不揮発性記憶装置 |

| US9601692B1 (en) | 2010-07-13 | 2017-03-21 | Crossbar, Inc. | Hetero-switching layer in a RRAM device and method |

| US9570678B1 (en) | 2010-06-08 | 2017-02-14 | Crossbar, Inc. | Resistive RAM with preferental filament formation region and methods |

| US8946046B1 (en) | 2012-05-02 | 2015-02-03 | Crossbar, Inc. | Guided path for forming a conductive filament in RRAM |

| US8168506B2 (en) | 2010-07-13 | 2012-05-01 | Crossbar, Inc. | On/off ratio for non-volatile memory device and method |

| US8569172B1 (en) | 2012-08-14 | 2013-10-29 | Crossbar, Inc. | Noble metal/non-noble metal electrode for RRAM applications |

| US8884261B2 (en) | 2010-08-23 | 2014-11-11 | Crossbar, Inc. | Device switching using layered device structure |

| US9401475B1 (en) | 2010-08-23 | 2016-07-26 | Crossbar, Inc. | Method for silver deposition for a non-volatile memory device |

| US8492195B2 (en) | 2010-08-23 | 2013-07-23 | Crossbar, Inc. | Method for forming stackable non-volatile resistive switching memory devices |

| US8830740B2 (en) * | 2010-09-08 | 2014-09-09 | Hitachi, Ltd. | Semiconductor storage device |

| US8558212B2 (en) | 2010-09-29 | 2013-10-15 | Crossbar, Inc. | Conductive path in switching material in a resistive random access memory device and control |

| US8391049B2 (en) | 2010-09-29 | 2013-03-05 | Crossbar, Inc. | Resistor structure for a non-volatile memory device and method |

| US8502185B2 (en) | 2011-05-31 | 2013-08-06 | Crossbar, Inc. | Switching device having a non-linear element |

| USRE46335E1 (en) | 2010-11-04 | 2017-03-07 | Crossbar, Inc. | Switching device having a non-linear element |

| US8361833B2 (en) * | 2010-11-22 | 2013-01-29 | Micron Technology, Inc. | Upwardly tapering heaters for phase change memories |

| KR20120077505A (ko) * | 2010-12-30 | 2012-07-10 | 삼성전자주식회사 | 비휘발성 반도체 메모리 장치 및 그 제조 방법 |

| US8513136B2 (en) | 2011-05-31 | 2013-08-20 | Samsung Electronics Co., Ltd. | Memory devices and method of manufacturing the same |

| US9620206B2 (en) | 2011-05-31 | 2017-04-11 | Crossbar, Inc. | Memory array architecture with two-terminal memory cells |

| US8619459B1 (en) | 2011-06-23 | 2013-12-31 | Crossbar, Inc. | High operating speed resistive random access memory |

| US9564587B1 (en) | 2011-06-30 | 2017-02-07 | Crossbar, Inc. | Three-dimensional two-terminal memory with enhanced electric field and segmented interconnects |

| US9627443B2 (en) | 2011-06-30 | 2017-04-18 | Crossbar, Inc. | Three-dimensional oblique two-terminal memory with enhanced electric field |

| US9166163B2 (en) | 2011-06-30 | 2015-10-20 | Crossbar, Inc. | Sub-oxide interface layer for two-terminal memory |

| US8946669B1 (en) | 2012-04-05 | 2015-02-03 | Crossbar, Inc. | Resistive memory device and fabrication methods |

| WO2013015776A1 (en) | 2011-07-22 | 2013-01-31 | Crossbar, Inc. | Seed layer for a p + silicon germanium material for a non-volatile memory device and method |

| KR20130043533A (ko) * | 2011-10-20 | 2013-04-30 | 삼성전자주식회사 | 도전성 버퍼 패턴을 갖는 비-휘발성 메모리소자 및 그 형성 방법 |

| US9685608B2 (en) | 2012-04-13 | 2017-06-20 | Crossbar, Inc. | Reduced diffusion in metal electrode for two-terminal memory |

| US8658476B1 (en) | 2012-04-20 | 2014-02-25 | Crossbar, Inc. | Low temperature P+ polycrystalline silicon material for non-volatile memory device |

| US9583701B1 (en) | 2012-08-14 | 2017-02-28 | Crossbar, Inc. | Methods for fabricating resistive memory device switching material using ion implantation |

| US9741765B1 (en) | 2012-08-14 | 2017-08-22 | Crossbar, Inc. | Monolithically integrated resistive memory using integrated-circuit foundry compatible processes |

| US8946673B1 (en) | 2012-08-24 | 2015-02-03 | Crossbar, Inc. | Resistive switching device structure with improved data retention for non-volatile memory device and method |

| US9312483B2 (en) | 2012-09-24 | 2016-04-12 | Crossbar, Inc. | Electrode structure for a non-volatile memory device and method |

| US9576616B2 (en) | 2012-10-10 | 2017-02-21 | Crossbar, Inc. | Non-volatile memory with overwrite capability and low write amplification |

| KR101994449B1 (ko) * | 2012-11-08 | 2019-06-28 | 삼성전자주식회사 | 상변화 메모리 소자 및 그 제조방법 |

| US9412790B1 (en) | 2012-12-04 | 2016-08-09 | Crossbar, Inc. | Scalable RRAM device architecture for a non-volatile memory device and method |

| KR20150090472A (ko) | 2014-01-29 | 2015-08-06 | 삼성전자주식회사 | 가변 저항 메모리 장치 및 그 제조 방법 |

| US10290801B2 (en) | 2014-02-07 | 2019-05-14 | Crossbar, Inc. | Scalable silicon based resistive memory device |

| US11223014B2 (en) | 2014-02-25 | 2022-01-11 | Micron Technology, Inc. | Semiconductor structures including liners comprising alucone and related methods |

| US9806129B2 (en) * | 2014-02-25 | 2017-10-31 | Micron Technology, Inc. | Cross-point memory and methods for fabrication of same |

| US9484196B2 (en) | 2014-02-25 | 2016-11-01 | Micron Technology, Inc. | Semiconductor structures including liners comprising alucone and related methods |

| US9577010B2 (en) | 2014-02-25 | 2017-02-21 | Micron Technology, Inc. | Cross-point memory and methods for fabrication of same |

| WO2017052583A1 (en) * | 2015-09-25 | 2017-03-30 | Intel Corporation | Thermally insulated resistive random access memory |

| US10249819B2 (en) | 2014-04-03 | 2019-04-02 | Micron Technology, Inc. | Methods of forming semiconductor structures including multi-portion liners |

| KR102210329B1 (ko) | 2014-08-14 | 2021-02-01 | 삼성전자주식회사 | 저항 변화 메모리 소자 및 그 제조 방법 |

| US9768378B2 (en) | 2014-08-25 | 2017-09-19 | Micron Technology, Inc. | Cross-point memory and methods for fabrication of same |

| US10734447B2 (en) * | 2018-10-22 | 2020-08-04 | International Business Machines Corporation | Field-effect transistor unit cells for neural networks with differential weights |

| KR102821718B1 (ko) * | 2019-03-05 | 2025-06-18 | 에스케이하이닉스 주식회사 | 전자 장치 및 그 제조 방법 |

| JP2020145364A (ja) * | 2019-03-08 | 2020-09-10 | キオクシア株式会社 | 記憶装置 |

| KR102668222B1 (ko) | 2019-05-22 | 2024-05-24 | 에스케이하이닉스 주식회사 | 전자 장치 및 그 제조 방법 |

| US10872835B1 (en) | 2019-07-03 | 2020-12-22 | Micron Technology, Inc. | Semiconductor assemblies including vertically integrated circuits and methods of manufacturing the same |

| KR102817555B1 (ko) * | 2019-09-11 | 2025-06-10 | 에스케이하이닉스 주식회사 | 전자 장치 및 그 제조 방법 |

| KR102773656B1 (ko) | 2019-10-23 | 2025-02-28 | 삼성전자주식회사 | 가변 저항 메모리 장치 |

| US11114335B1 (en) * | 2020-04-14 | 2021-09-07 | Nanya Technology Corporation | Semiconductor device structure with air gap structure and method for forming the same |

| KR102675158B1 (ko) * | 2020-08-24 | 2024-06-12 | 삼성전자주식회사 | 반도체 메모리 장치 및 그 제조 방법 |

| WO2022073222A1 (en) * | 2020-10-10 | 2022-04-14 | Yangtze Advanced Memory Industrial Innovation Center Co., Ltd | Method to reduce thermal cross talk in 3d x-point memory array |

| KR102792188B1 (ko) * | 2020-10-14 | 2025-04-04 | 삼성전자주식회사 | 반도체 메모리 장치 및 그 제조 방법 |

| US11950434B2 (en) * | 2021-08-26 | 2024-04-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory device for reducing thermal crosstalk |

| WO2023028722A1 (zh) * | 2021-08-28 | 2023-03-09 | 华为技术有限公司 | 一种相变存储器及相变存储器的制作方法 |

| US12402545B2 (en) | 2021-12-08 | 2025-08-26 | International Business Machines Corporation | Stacked cross-point phase change memory |

| US12507599B2 (en) | 2023-02-13 | 2025-12-23 | SK Hynix Inc. | Semiconductor device and method of manufacturing the same |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002141436A (ja) * | 2000-11-01 | 2002-05-17 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2005064050A (ja) * | 2003-08-14 | 2005-03-10 | Toshiba Corp | 半導体記憶装置及びそのデータ書き込み方法 |

| JP2005536052A (ja) * | 2002-08-14 | 2005-11-24 | オヴォニクス,インコーポレイテッド | プログラム可能デバイスのためのコンタクト改善方法及び装置 |

| JP2007019559A (ja) * | 2006-10-23 | 2007-01-25 | Hitachi Ltd | 半導体記憶装置及びその製造方法 |

| JP2007194426A (ja) * | 2006-01-19 | 2007-08-02 | Toshiba Corp | 半導体記憶装置 |

| JP2009218598A (ja) * | 2008-03-11 | 2009-09-24 | Samsung Electronics Co Ltd | 抵抗メモリ素子及びその形成方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6927430B2 (en) * | 2001-06-28 | 2005-08-09 | Sharp Laboratories Of America, Inc. | Shared bit line cross-point memory array incorporating P/N junctions |

| JP3749847B2 (ja) * | 2001-09-27 | 2006-03-01 | 株式会社東芝 | 相変化型不揮発性記憶装置及びその駆動回路 |

| JP3948292B2 (ja) | 2002-02-01 | 2007-07-25 | 株式会社日立製作所 | 半導体記憶装置及びその製造方法 |

| US6579760B1 (en) * | 2002-03-28 | 2003-06-17 | Macronix International Co., Ltd. | Self-aligned, programmable phase change memory |

| KR100642186B1 (ko) * | 2002-04-04 | 2006-11-10 | 가부시끼가이샤 도시바 | 상-변화 메모리 디바이스 |

| US7767993B2 (en) * | 2002-04-04 | 2010-08-03 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US7078814B2 (en) * | 2004-05-25 | 2006-07-18 | International Business Machines Corporation | Method of forming a semiconductor device having air gaps and the structure so formed |

| KR100675279B1 (ko) * | 2005-04-20 | 2007-01-26 | 삼성전자주식회사 | 셀 다이오드들을 채택하는 상변이 기억소자들 및 그제조방법들 |

| KR100872880B1 (ko) * | 2006-09-11 | 2008-12-10 | 삼성전자주식회사 | 상변화 메모리 장치의 테스트 방법 및 상변화 메모리 장치 |

| KR100782496B1 (ko) * | 2006-11-09 | 2007-12-05 | 삼성전자주식회사 | 자기 정렬된 셀 다이오드를 갖는 반도체 소자의 제조방법및 이를 이용하는 상변화 기억소자의 제조방법 |

| KR101390341B1 (ko) * | 2007-11-15 | 2014-04-30 | 삼성전자주식회사 | 상변화 메모리 소자 |

| US7768016B2 (en) * | 2008-02-11 | 2010-08-03 | Qimonda Ag | Carbon diode array for resistivity changing memories |

| KR100929297B1 (ko) | 2008-07-16 | 2009-11-27 | 주식회사 하이닉스반도체 | 상 변화 메모리 장치, 형성 방법 및 이를 이용한멀티미디어 저장 장치 |

-

2008

- 2008-08-06 JP JP2008202771A patent/JP5342189B2/ja not_active Expired - Fee Related

-

2009

- 2009-04-16 TW TW098112705A patent/TWI400797B/zh not_active IP Right Cessation

- 2009-05-02 US US12/434,633 patent/US8129705B2/en not_active Expired - Fee Related

- 2009-05-21 CN CN200910139391.4A patent/CN101645453B/zh not_active Expired - Fee Related

- 2009-05-21 KR KR1020090044433A patent/KR101148693B1/ko not_active Expired - Fee Related

-

2012

- 2012-02-06 US US13/366,544 patent/US8604456B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002141436A (ja) * | 2000-11-01 | 2002-05-17 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2005536052A (ja) * | 2002-08-14 | 2005-11-24 | オヴォニクス,インコーポレイテッド | プログラム可能デバイスのためのコンタクト改善方法及び装置 |

| JP2005064050A (ja) * | 2003-08-14 | 2005-03-10 | Toshiba Corp | 半導体記憶装置及びそのデータ書き込み方法 |

| JP2007194426A (ja) * | 2006-01-19 | 2007-08-02 | Toshiba Corp | 半導体記憶装置 |

| JP2007019559A (ja) * | 2006-10-23 | 2007-01-25 | Hitachi Ltd | 半導体記憶装置及びその製造方法 |

| JP2009218598A (ja) * | 2008-03-11 | 2009-09-24 | Samsung Electronics Co Ltd | 抵抗メモリ素子及びその形成方法 |

Cited By (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010186872A (ja) * | 2009-02-12 | 2010-08-26 | Toshiba Corp | 半導体記憶装置、及びその製造方法 |

| WO2011086725A1 (ja) * | 2010-01-15 | 2011-07-21 | 株式会社日立製作所 | 不揮発性記憶装置およびその製造方法 |

| JP2011146590A (ja) * | 2010-01-15 | 2011-07-28 | Hitachi Ltd | 不揮発性記憶装置およびその製造方法 |

| US9070621B2 (en) | 2010-05-18 | 2015-06-30 | Hitachi, Ltd. | Nonvolatile semiconductor memory device and manufacturing method thereof |

| JP2011243738A (ja) * | 2010-05-18 | 2011-12-01 | Hitachi Ltd | 不揮発性記憶装置およびその製造方法 |

| JP2012059827A (ja) * | 2010-09-07 | 2012-03-22 | Elpida Memory Inc | 半導体装置およびその製造方法 |

| US9142512B2 (en) | 2012-03-23 | 2015-09-22 | Kabushiki Kaisha Toshiba | Semiconductor memory device having a wiring in which a step is provided |

| US8785980B2 (en) | 2012-03-23 | 2014-07-22 | Kabushiki Kaisha Toshiba | Semiconductor memory device having a low resistance wiring line and method of manufacturing the same |

| JP2014120606A (ja) * | 2012-12-17 | 2014-06-30 | Hitachi Ltd | 不揮発性記憶装置 |

| JP2017537470A (ja) * | 2014-11-07 | 2017-12-14 | マイクロン テクノロジー, インク. | クロスポイントメモリと、その製造方法 |

| JP2019165235A (ja) * | 2014-11-07 | 2019-09-26 | マイクロン テクノロジー,インク. | クロスポイントメモリと、その製造方法 |

| JP2018512728A (ja) * | 2015-03-19 | 2018-05-17 | マイクロン テクノロジー, インク. | 積層メモリアレイを含む構造体 |

| US10396127B2 (en) | 2015-03-19 | 2019-08-27 | Micron Technology, Inc. | Constructions comprising stacked memory arrays |

| JP2020515046A (ja) * | 2017-01-17 | 2020-05-21 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | 閾値スイッチング材料による閉じ込め相変化メモリの集積 |

| JP7175896B2 (ja) | 2017-01-17 | 2022-11-21 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 閾値スイッチング材料による閉じ込め相変化メモリの集積 |

| WO2018203459A1 (ja) * | 2017-05-01 | 2018-11-08 | ソニーセミコンダクタソリューションズ株式会社 | 選択素子および記憶装置 |

| JPWO2018203459A1 (ja) * | 2017-05-01 | 2020-05-14 | ソニーセミコンダクタソリューションズ株式会社 | 選択素子および記憶装置 |

| US11152428B2 (en) | 2017-05-01 | 2021-10-19 | Sony Semiconductor Solutions Corporation | Selection device and storage apparatus |

| TWI759463B (zh) * | 2017-05-01 | 2022-04-01 | 日商索尼半導體解決方案公司 | 選擇元件及記憶裝置 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20100018445A (ko) | 2010-02-17 |

| US20100032637A1 (en) | 2010-02-11 |

| US8604456B2 (en) | 2013-12-10 |

| US20120132879A1 (en) | 2012-05-31 |

| TWI400797B (zh) | 2013-07-01 |

| CN101645453B (zh) | 2011-07-27 |

| CN101645453A (zh) | 2010-02-10 |

| TW201007941A (en) | 2010-02-16 |

| KR101148693B1 (ko) | 2012-05-25 |

| JP5342189B2 (ja) | 2013-11-13 |

| US8129705B2 (en) | 2012-03-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5342189B2 (ja) | 不揮発性記憶装置及びその製造方法 | |

| US8169819B2 (en) | Semiconductor storage device | |

| US7808816B2 (en) | Semiconductor memory device and method for fabricating semiconductor memory device | |

| JP2009123725A (ja) | 不揮発性半導体記憶装置 | |

| JP5420436B2 (ja) | 不揮発性記憶装置およびその製造方法 | |

| JP5268376B2 (ja) | 不揮発性記憶装置およびその製造方法 | |

| JP4577693B2 (ja) | 不揮発性メモリ素子及びその製造方法 | |

| JP2009267219A (ja) | 半導体記憶装置およびその製造方法 | |

| US7582889B2 (en) | Electrically rewritable non-volatile memory element and method of manufacturing the same | |

| JP2011233831A (ja) | 半導体記憶装置 | |

| WO2010140210A1 (ja) | 半導体記憶装置およびその製造方法 | |

| KR20090123291A (ko) | 상변화 메모리 소자와 그 제조 및 동작 방법 | |

| KR100876767B1 (ko) | 상 변화 메모리 장치의 형성 방법 | |

| JP2010161137A (ja) | 半導体記憶装置の製造方法 | |

| JP2011114011A (ja) | 不揮発性記憶装置およびその製造方法 | |

| JP2016119373A (ja) | 半導体記憶装置及びその製造方法 | |

| JP2008103541A (ja) | 相変化メモリおよびその製造方法 | |

| JP4437297B2 (ja) | 半導体記憶装置及び半導体記憶装置の製造方法 | |

| JP2006332671A (ja) | 相変化記憶素子及びその製造方法 | |

| JP2009076596A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110301 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110301 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130308 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130312 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130419 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130716 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130809 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5342189 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |