JP2010008772A - レチクルデータ作成方法、レチクルデータ作成装置及びウェハ - Google Patents

レチクルデータ作成方法、レチクルデータ作成装置及びウェハ Download PDFInfo

- Publication number

- JP2010008772A JP2010008772A JP2008168725A JP2008168725A JP2010008772A JP 2010008772 A JP2010008772 A JP 2010008772A JP 2008168725 A JP2008168725 A JP 2008168725A JP 2008168725 A JP2008168725 A JP 2008168725A JP 2010008772 A JP2010008772 A JP 2010008772A

- Authority

- JP

- Japan

- Prior art keywords

- area

- dummy

- data

- chip

- reticle

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W46/00—Marks applied to devices, e.g. for alignment or identification

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/68—Preparation processes not covered by groups G03F1/20 - G03F1/50

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F9/00—Registration or positioning of originals, masks, frames, photographic sheets or textured or patterned surfaces, e.g. automatically

- G03F9/70—Registration or positioning of originals, masks, frames, photographic sheets or textured or patterned surfaces, e.g. automatically for microlithography

- G03F9/7073—Alignment marks and their environment

- G03F9/7076—Mark details, e.g. phase grating mark, temporary mark

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F9/00—Registration or positioning of originals, masks, frames, photographic sheets or textured or patterned surfaces, e.g. automatically

- G03F9/70—Registration or positioning of originals, masks, frames, photographic sheets or textured or patterned surfaces, e.g. automatically for microlithography

- G03F9/7073—Alignment marks and their environment

- G03F9/7084—Position of mark on substrate, i.e. position in (x, y, z) of mark, e.g. buried or resist covered mark, mark on rearside, at the substrate edge, in the circuit area, latent image mark, marks in plural levels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W46/00—Marks applied to devices, e.g. for alignment or identification

- H10W46/501—Marks applied to devices, e.g. for alignment or identification for use before dicing

- H10W46/507—Located in dummy chips or in reference chips

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Preparing Plates And Mask In Photomechanical Process (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

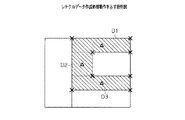

【解決手段】プロセスパターンからメインチップの未配置領域を検出する工程と、未配置領域を矩形に分割する工程と、分割された矩形をダミーチップとしてスクライブデータを発生させる工程と、ダミーチップにダミーパターンを発生させる工程とを備えた。

【選択図】図2

Description

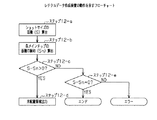

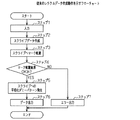

上記のようなマルチダイ用レチクルを生成するためのCADデータを生成する工程におけるスクライブデータの作成工程を図18に示す。

このような処理により、スクライブライン上へ各種マークを配置し、スクライブ領域とメインチップ領域とを平坦化する処理が行われる。

前記未配置領域を矩形に分割する工程と、前記分割された矩形をダミーチップとしてスクライブデータを発生させる工程と、前記ダミーチップにダミーパターンを発生させる工程とを備えたレチクルデータ作成方法により達成される。

ファイル8にはスクライブ領域に配置するマークに関するライブラリデータと、各マークを配置する際の配置制約条件データが格納され、前記処理装置2はその配置制約条件データに基づいてマークの配置処理を行う。

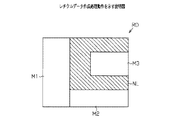

次に、上記のようなCADデータ作成装置の処理装置2でレチクルのチップ未配置領域へのデータ生成動作を図2〜図4に示すフローチャートと図5〜図12に示すレチクルイメージを示す説明図に基づいて説明する。

ステップ12−cにおいて、S−Snが0以下である場合にはステップ12−eに移行し、S−Snが0である場合には未配置領域NLがないので、次のステップに移行する。また、S−Snが0未満である場合には、エラーを出力する。

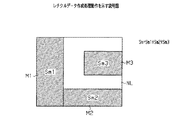

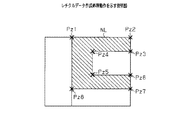

次いで、必要なマークを配置できたか否かを判定し(ステップ18)、配置できている場合にはステップ19に移行して、スクライブ領域に平坦化用のダミーパターンを生成する。そして、ダミーチップD1〜D3あるいは同D4〜D6に平坦化用のダミーパターン生成する(ステップ20)。

ステップ18において、必要なマークが配置できていない場合には、ステップ22に移行して、ステップ15で生成したダミーチップにマークを配置可能か否かをファイル8の配置制約条件データに基づいて判定する。そして、配置可能であれば、ダミーチップ領域にマークを配置し(ステップ23)、再度ステップ18に移行して、マーク配置結果を判定する。

図13は、上記のような処理により、未配置領域を矩形に分割し、さらに多数のダミーチップDとして平坦化ダミーパターンを生成したCADデータを示す。このような処理により、すべての未配置領域にダミーチップを生成可能としたレチクルデータが生成される。

(1)マルチダイ用レチクルのチップ未配置領域にダミーパターンを備えたダミーチップ領域を生成することができる。従って、このマルチダイ用レチクルで生成したウェハのメインチップ領域と未配置領域を平坦化することができる。

(2)未配置領域にダミーパターンを備えたダミーチップをレイアウトすることができる。従って、図14に示すように、ウェハ上の未配置領域に形成されるダミーパターンDPにより、未配置領域の配線間絶縁層の物理的強度を確保して、ダイシング時の配線間絶縁層の剥がれを防止することができる。

(3)ダミーチップ領域にもプロセスパターンのマークを配置することができる。従って、ダイシング領域に配置しきれないマークをダミーチップ領域に配置して、マーク数の増大に対処することができる。

(4)未配置領域を矩形に分割し、その矩形をダミーチップとしてスクライブ領域を生成するので、ウェハ基板上に形成されたメインチップ及びダミーチップは、スクライブ領域に沿ってダイシングすることにより容易に取り出すことができる。

・ダミーチップに生成するダミーパターンは、平坦化の観点からメインチップと同一数の配線層を形成することが望ましいが、少なくとも1層、任意の層に生成すれば、配線間絶縁層の剥がれを防止することができる。

ターン発生手段(処理装置)

4〜12 記憶手段

M,M1〜M3 メインチップ

NL 未配置領域

D,D1〜D6 ダミーチップ

DP ダミーパターン

Claims (10)

- プロセスパターンからメインチップの未配置領域を検出する工程と、

前記未配置領域を矩形に分割する工程と、

前記分割された矩形をダミーチップとしてスクライブデータを発生させる工程と、

前記ダミーチップにダミーパターンを発生させる工程と

を備えたことを特徴とするレチクルデータ作成方法。 - 前記ダミーパターンとして、少なくとも1層の金属配線を生成することを特徴とする請求項1記載のレチクルデータ作成方法。

- 前記ダミーパターンとして、メインチップと同一の配線層を生成することを特徴とする請求項1記載のレチクルデータ作成方法。

- 前記ダミーチップのスクライブデータを発生させる工程において、

前記ダミーチップのスクライブ領域にすべてのマークを配置できるか否かを判定する工程と、

すべてのマークを配置できないとき、前記ダミーチップの領域内に前記マークを配置する工程と

を備えたことを特徴とする請求項1乃至3のいずれか1項に記載のレチクルデータ作成方法。 - 前記未配置領域を矩形に分割する工程において、

前記未配置領域を分割する方向は、前記メインチップのスクライブ領域の幅が広い方向に一致させる方向とすることを特徴とする請求項1乃至4のいずれか1項に記載のレチクルデータ作成方法。 - プロセスパターンからメインチップの未配置領域を検出する未配置領域検出手段と、

前記未配置領域を矩形に分割する矩形分割手段と、

前記分割された矩形をダミーチップとしてスクライブデータを発生させるスクライブデータ発生手段と、

前記ダミーチップにダミーパターンを発生させるダミーパターン発生手段と

を備えたことを特徴とするレチクルデータ作成装置。 - 前記スクライブデータ発生手段は、

前記ダミーチップのスクライブ領域にすべてのマークを配置できるか否かを判定する判定手段と、

すべてのマークを配置できないとき、前記ダミーチップの領域内に前記マークを配置する再配置手段と

を備えたことを特徴とする請求項6記載のレチクルデータ作成装置。 - 前記未配置領域検出手段で検出された未配置領域データを格納する記憶手段と、

前記矩形分割手段で矩形に分割された未配置領域データを格納する記憶手段と、

前記プロセスパターンのマークデータを格納した記憶手段と、

前記ダミーパターンを発生させるためのルールを格納した記憶手段と

を備えたことを特徴とする請求項6又は7記載のレチクルデータ作成装置。 - 請求項1乃至5のいずれか1項に記載のレチクルデータ作成方法に基づいて生成されたレチクルを使用して露光処理を行うことを特徴とするウェハ。

- メインチップの未配置領域を矩形に分割した矩形分割領域を備えたダミーチップと、

前記ダミーチップに設けたダミーパターンと

を備えたことを特徴とするウェハ。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008168725A JP5309728B2 (ja) | 2008-06-27 | 2008-06-27 | レチクルデータ作成方法及びレチクルデータ作成装置 |

| US12/485,396 US8513777B2 (en) | 2008-06-27 | 2009-06-16 | Method and apparatus for generating reticle data |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008168725A JP5309728B2 (ja) | 2008-06-27 | 2008-06-27 | レチクルデータ作成方法及びレチクルデータ作成装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010008772A true JP2010008772A (ja) | 2010-01-14 |

| JP5309728B2 JP5309728B2 (ja) | 2013-10-09 |

Family

ID=41446375

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008168725A Expired - Fee Related JP5309728B2 (ja) | 2008-06-27 | 2008-06-27 | レチクルデータ作成方法及びレチクルデータ作成装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8513777B2 (ja) |

| JP (1) | JP5309728B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8423945B2 (en) * | 2010-05-18 | 2013-04-16 | International Business Machines Corporation | Methods and systems to meet technology pattern density requirements of semiconductor fabrication processes |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000147742A (ja) * | 1998-11-12 | 2000-05-26 | Fujitsu Ltd | 露光用マスクの製造方法 |

| JP2004022631A (ja) * | 2002-06-13 | 2004-01-22 | Mitsubishi Electric Corp | 半導体装置およびパターン配置方法 |

| JP2004069829A (ja) * | 2002-08-02 | 2004-03-04 | Toshiba Corp | マスク、マスクの作成方法、および半導体装置の製造方法 |

| JP2004294664A (ja) * | 2003-03-26 | 2004-10-21 | Fujitsu Ltd | レチクルの作成方法、およびレチクルの作成プログラム |

| JP2006189674A (ja) * | 2005-01-07 | 2006-07-20 | Fujitsu Ltd | プロセスパターンの配置方法及びプロセスパターンデータ作成装置 |

| JP2007027290A (ja) * | 2005-07-14 | 2007-02-01 | Renesas Technology Corp | 半導体集積回路のレイアウト設計方法 |

| JP2007287770A (ja) * | 2006-04-13 | 2007-11-01 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

Family Cites Families (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5612644A (en) | 1979-07-12 | 1981-02-07 | Matsushita Electric Ind Co Ltd | Manufacture of photomask |

| JPS6254921A (ja) | 1985-09-04 | 1987-03-10 | Nec Corp | 半導体装置の製造方法 |

| JPS63236045A (ja) | 1987-03-25 | 1988-09-30 | Matsushita Electronics Corp | フオトマスク |

| JP2516403B2 (ja) * | 1988-06-01 | 1996-07-24 | 富士通株式会社 | ウエハ・スケ―ル・メモリ |

| JP3638778B2 (ja) * | 1997-03-31 | 2005-04-13 | 株式会社ルネサステクノロジ | 半導体集積回路装置およびその製造方法 |

| JPH1174229A (ja) * | 1997-08-29 | 1999-03-16 | Toshiba Microelectron Corp | 半導体装置 |

| JP3065309B1 (ja) * | 1999-03-11 | 2000-07-17 | 沖電気工業株式会社 | 半導体装置の製造方法 |

| US6396158B1 (en) * | 1999-06-29 | 2002-05-28 | Motorola Inc. | Semiconductor device and a process for designing a mask |

| JP2001160577A (ja) * | 1999-12-02 | 2001-06-12 | Nec Corp | 半導体装置の製造方法と半導体ウェハ |

| JP4307664B2 (ja) * | 1999-12-03 | 2009-08-05 | 株式会社ルネサステクノロジ | 半導体装置 |

| JP3651344B2 (ja) * | 2000-02-03 | 2005-05-25 | セイコーエプソン株式会社 | 半導体装置の製造方法 |

| JPWO2003038880A1 (ja) * | 2001-10-31 | 2005-02-24 | 三星ダイヤモンド工業株式会社 | 半導体ウエハのスクライブ線の形成方法およびスクライブ線の形成装置 |

| JP4149715B2 (ja) * | 2002-02-28 | 2008-09-17 | 富士通株式会社 | パターン作成方法及びフォトマスク |

| US20030173648A1 (en) * | 2002-03-16 | 2003-09-18 | Sniegowski Jeffry Joseph | Multi-die chip and method for making the same |

| US6914002B2 (en) * | 2002-12-28 | 2005-07-05 | Intel Corporation | Differential planarization |

| JP4136684B2 (ja) * | 2003-01-29 | 2008-08-20 | Necエレクトロニクス株式会社 | 半導体装置及びそのダミーパターンの配置方法 |

| US6900075B2 (en) * | 2003-10-31 | 2005-05-31 | Lsi Logic Corporation | Mixed LVR and HVR reticle set design for the processing of gate arrays, embedded arrays and rapid chip products |

| JP4619705B2 (ja) * | 2004-01-15 | 2011-01-26 | 株式会社東芝 | 半導体装置 |

| JP4377300B2 (ja) * | 2004-06-22 | 2009-12-02 | Necエレクトロニクス株式会社 | 半導体ウエハおよび半導体装置の製造方法 |

| JP4741822B2 (ja) * | 2004-09-02 | 2011-08-10 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2006344795A (ja) * | 2005-06-09 | 2006-12-21 | Disco Abrasive Syst Ltd | ウエーハの分割方法 |

| US7755207B2 (en) * | 2005-07-27 | 2010-07-13 | Ricoh Company, Ltd. | Wafer, reticle, and exposure method using the wafer and reticle |

| JP4278645B2 (ja) * | 2005-09-30 | 2009-06-17 | 株式会社リコー | 半導体ウェハ及びそのレイアウト設定方法並びにレチクルレイアウト設定方法 |

| US7696607B2 (en) * | 2006-08-10 | 2010-04-13 | Panasonic Corporation | Semiconductor device |

| JP5023653B2 (ja) * | 2006-10-19 | 2012-09-12 | 富士通セミコンダクター株式会社 | 露光用マスク、電子装置の製造方法、及び露光用マスクの検査方法 |

| US7387950B1 (en) * | 2006-12-17 | 2008-06-17 | United Microelectronics Corp. | Method for forming a metal structure |

| JP2009081219A (ja) * | 2007-09-26 | 2009-04-16 | Ricoh Co Ltd | 半導体ウェハ、その半導体ウェハから切り出した半導体チップ及び半導体ウェハの製造方法 |

| JP5194770B2 (ja) * | 2007-12-20 | 2013-05-08 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法及びそのプログラム |

| JP2010003949A (ja) * | 2008-06-23 | 2010-01-07 | Nec Electronics Corp | 半導体集積回路装置のレイアウト検証方法 |

| JP2011134893A (ja) * | 2009-12-24 | 2011-07-07 | Renesas Electronics Corp | 半導体装置 |

-

2008

- 2008-06-27 JP JP2008168725A patent/JP5309728B2/ja not_active Expired - Fee Related

-

2009

- 2009-06-16 US US12/485,396 patent/US8513777B2/en not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000147742A (ja) * | 1998-11-12 | 2000-05-26 | Fujitsu Ltd | 露光用マスクの製造方法 |

| JP2004022631A (ja) * | 2002-06-13 | 2004-01-22 | Mitsubishi Electric Corp | 半導体装置およびパターン配置方法 |

| JP2004069829A (ja) * | 2002-08-02 | 2004-03-04 | Toshiba Corp | マスク、マスクの作成方法、および半導体装置の製造方法 |

| JP2004294664A (ja) * | 2003-03-26 | 2004-10-21 | Fujitsu Ltd | レチクルの作成方法、およびレチクルの作成プログラム |

| JP2006189674A (ja) * | 2005-01-07 | 2006-07-20 | Fujitsu Ltd | プロセスパターンの配置方法及びプロセスパターンデータ作成装置 |

| JP2007027290A (ja) * | 2005-07-14 | 2007-02-01 | Renesas Technology Corp | 半導体集積回路のレイアウト設計方法 |

| JP2007287770A (ja) * | 2006-04-13 | 2007-11-01 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5309728B2 (ja) | 2013-10-09 |

| US8513777B2 (en) | 2013-08-20 |

| US20090321891A1 (en) | 2009-12-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6581195B2 (en) | Method and apparatus for extracting parasitic element of semiconductor circuit | |

| US8522186B2 (en) | Method and apparatus of an integrated circuit | |

| US9672611B2 (en) | Pattern analysis method of a semiconductor device | |

| US7640520B2 (en) | Design flow for shrinking circuits having non-shrinkable IP layout | |

| US8136084B2 (en) | Arranging through silicon vias in IC layout | |

| TWI735851B (zh) | 用於設計虛設圖案的系統和方法 | |

| US20080178142A1 (en) | Hotspot detection method for design and validation of layout for semiconductor device | |

| JP5309728B2 (ja) | レチクルデータ作成方法及びレチクルデータ作成装置 | |

| CN114330207B (zh) | 芯片焊盘的信息提取方法、系统及电子设备 | |

| US20060289750A1 (en) | Macro-placement designing apparatus, program product, and method considering density | |

| JP2003282569A (ja) | 半導体集積回路装置及びダミーメタルの挿入方法 | |

| JP2006165091A (ja) | 半導体集積装置、その設計方法、設計装置、およびプログラム | |

| US20040188849A1 (en) | Semiconductor device and pattern generating method | |

| US9305863B2 (en) | Semiconductor device | |

| JP4799858B2 (ja) | 半導体集積回路の自動設計方法 | |

| US6500722B2 (en) | Inductor recognition method, layout inspection method, computer readable recording medium in which a layout inspection program is recorded and process for a semiconductor device | |

| JPH04218918A (ja) | 半導体装置及びその製造方法 | |

| JP2002171099A (ja) | 回路基板の実装品質チェック方法及びその装置 | |

| US20100122226A1 (en) | Layout density verification system and layout density verification method | |

| JP2012028403A (ja) | 半導体装置の製造方法 | |

| JP2009123966A (ja) | 半導体集積回路のレイアウトパターン設計方法、レイアウトパターン設計装置およびレイアウトパターン設計用プログラム | |

| JP2008040811A (ja) | 情報処理装置、配線設計方法及びプログラム | |

| JPH10312408A (ja) | 半導体設計検証装置及び半導体設計検証方法 | |

| TWI434375B (zh) | 獲得積體電路佈局設計的方法 | |

| JP4943918B2 (ja) | 実形状検証装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110126 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120607 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120612 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120810 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130604 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130617 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |