JP2005294443A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2005294443A JP2005294443A JP2004105834A JP2004105834A JP2005294443A JP 2005294443 A JP2005294443 A JP 2005294443A JP 2004105834 A JP2004105834 A JP 2004105834A JP 2004105834 A JP2004105834 A JP 2004105834A JP 2005294443 A JP2005294443 A JP 2005294443A

- Authority

- JP

- Japan

- Prior art keywords

- back surface

- semiconductor device

- semiconductor element

- terminal

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/0198—Manufacture or treatment batch processes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/541—Dispositions of bond wires

- H10W72/5449—Dispositions of bond wires not being orthogonal to a side surface of the chip, e.g. fan-out arrangements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/931—Shapes of bond pads

- H10W72/932—Plan-view shape, i.e. in top view

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/131—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being only partially enclosed

- H10W74/142—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being only partially enclosed the encapsulations exposing the passive side of the semiconductor body

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/751—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires

- H10W90/756—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires between a chip and a stacked lead frame, conducting package substrate or heat sink

Landscapes

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

- Lead Frames For Integrated Circuits (AREA)

Abstract

【課題】 安価なリードフレームを用い、ダイパッドを不要にして、半導体装置の薄型化、小型化、多ピン化を低コストで実現し、半導体素子を安定に固定し、接続信頼性及び封止の安定性、更には実装の信頼性と安定性を向上させること。

【解決手段】 リードフレーム24から作製された端子(外部端子)5と半導体素子(ICチップ)1とがワイヤ4でワイヤボンディングされ、封止樹脂7で封止され、半導体素子1の裏面に接して絶縁性樹脂層21が予めコーティング等で形成され、この絶縁性樹脂層21が封止樹脂7の裏面側に露出しており、端子5の裏面と同一平面上に存在している装置(半導体パッケージ)20。

【選択図】 図1

【解決手段】 リードフレーム24から作製された端子(外部端子)5と半導体素子(ICチップ)1とがワイヤ4でワイヤボンディングされ、封止樹脂7で封止され、半導体素子1の裏面に接して絶縁性樹脂層21が予めコーティング等で形成され、この絶縁性樹脂層21が封止樹脂7の裏面側に露出しており、端子5の裏面と同一平面上に存在している装置(半導体パッケージ)20。

【選択図】 図1

Description

本発明は、半導体素子と端子とが接続され、封止材で封止された半導体装置及びその製造方法に関するものである。

近年の電子機器への要求は、小型、薄型、軽量、高性能、高機能、低コストなどであるが、SIP(System In Package)等は、まさにこれらの要求から生み出されたものである。しかしながら、半導体集積回路(IC)チップを実装するためのインターポーザーと呼ばれる配線回路基板が必要であるため、低コスト化、薄型化の要求を十分に満足していない。

図8には、ダイパッド非露出型の半導体装置(半導体パッケージ)10を示すが、これは、安価なリードフレームを用い、隅部のリード部6で支持されたダイパッド3上に半導体素子であるICチップ1をダイボンド材8によって固定し、金属ワイヤ4によってICチップ1の電極パッド2と端子5とをワイヤボンディングで接続し、端子5の裏面及び側面以外をモールド樹脂7で封止したものである(例えば後記の特許文献1参照)。

この半導体パッケージでは、リードフレームから作製された端子5が外部(接続)端子として用いられ、プリント配線板(図示せず)に直接はんだ付けされて実装される。

一方、リードフレームから作製された端子を用いるが、上記のようなダイパッドは用いないで樹脂封止したパッケージ(例えば後記の特許文献2参照)や、リードフレーム及びダイパッドを共に用いないで樹脂封止したパッケージ(例えば後記の特許文献3参照)も知られている。

図8に示した如き特許文献1に示されたダイパッド非露出型の半導体装置10は、ダイパッド3を半導体装置内部にディプレス加工でアップセットしてダイパッド3の非露出化を実現しているため、次の(1)〜(5)の問題点がある。

(1)ダイパッド3を露出させたパッケージと比較して、半導体装置の薄型化が困難で ある。

(2)ダイパッド3及びそれを支える吊り部6が必要であり、半導体装置の小型化及び 多ピン化の妨げとなる。

(3)ダイパッド3の下面をハーフエッチングしたもの(図示せず)が知られているが 、この場合も、リードフレームに樹脂フィルムを貼り付けてダイボンドするときに、ダ イパッド3の沈み込みが発生するので、半導体素子1を所定の位置に搭載し難くなる。

(4)また、そのようにリードフレームに樹脂フィルムを貼り付ける場合、樹脂フィル ムが破れる等の問題があり、ヒートプレートをダイパッド部に接触させるのが困難であ るため、ワイヤボンディング時の熱、荷重、超音波が半導体素子1に均一に伝わらず、 ワイヤボンディングの接続不良が発生し易い。

(5)また、射出成形等で樹脂封止7を行なう場合に、ダイパッド3のシフト等が発生 し、ボンディングワイヤ4の切断等の不良が発生し易いと共に、ダイパッド3裏面への 樹脂の充填性が悪く、ボイドや未充填等の不良が発生し易い。

また、特許文献2に示された半導体パッケージでは、ダイパッド自体をなくして半導体素子の裏面が露出しているので、上記した問題はある程度は解消されるものの、実装過程において半導体素子の裏面の損傷が生じ易いと共に、プリント配線板への実装時に絶縁手段をプリント配線板側に設ける必要があって、実装の作業性及び信頼性に問題がある。

また、特許文献3に示された半導体パッケージでは、半導体素子の裏面は絶縁材で保護されるが、端子がリードフレームから作製されるものではなく、メタルフレーム上への金属ワイヤの接続後にメタルフレームを溶解除去してワイヤ付きの端子を形成しているので、端子の形成がそれ程容易ではなく、その接合強度も不十分となり、更にはプリント配線板への接合も不良となり易いので、端子部にはスタッド端子を付加する必要がある。

本発明の目的は、安価なリードフレームを用い、ダイパッドを不要にして、半導体装置の薄型化、小型化、多ピン化を低コストで実現し、半導体素子を安定に固定し、接続信頼性及び封止の安定性、更には実装の信頼性と安定性を向上させることにある。

即ち、本発明は、リードフレームから作製された端子と半導体素子とが接続され、封止材で封止された半導体装置において、前記半導体素子の裏面に接して絶縁物質層が形成され、この絶縁物質層が前記封止材の裏面側に露出していることを特徴とする半導体装置に係るものである。

本発明はまた、リードフレームから作製された端子と半導体素子とが接続され、封止材で封止された半導体装置の製造方法において、半導体ウェハの裏面に接して絶縁物質層を形成する工程と、前記半導体ウェハを個片化して、裏面に接して前記絶縁物質層が形成された半導体素子を得る工程と、この半導体素子をリードフレーム間に配置する工程と、前記絶縁物質層及び前記リードフレームの裏面を除いて前記半導体素子及び前記リードフレームを封止材で封止する工程と、前記リードフレームの所定箇所を前記封止材と共に切断して、前記端子を形成すると共に、前記絶縁物質層が前記封止材の裏面側に露出した半導体装置を得る工程とを有することを特徴とする半導体装置の製造方法も提供するものである。

本発明の半導体装置及びその製造方法によれば、安価なリードフレームを用いて、半導体素子を接続する端子を形成し、前記半導体素子の裏面に接して形成された絶縁物質層を封止材の裏面側に露出させた構造とし、またこの構造を製造する方法として、半導体ウェハの裏面に接して絶縁物質層を形成した後に前記半導体ウェハを個片化して、裏面に接して前記絶縁物質層が形成された半導体素子を得、この半導体素子をリードフレーム間に配置して、前記絶縁物質層及び前記リードフレームの裏面を除いて前記半導体素子及び前記リードフレームを封止材で封止した後、前記リードフレームの所定箇所を前記封止材と共に切断して、前記端子を形成すると共に、前記絶縁物質層が前記封止材の裏面側に露出した半導体装置を得ているので、次の(a)〜(h)に示す顕著な作用効果を得ることができる。

(a)半導体素子を搭載するためのダイパッドが不要になり(ダイパッドに必要とされ る厚みが不要となり)、ダイパッドをアップセットする必要がないため、半導体装置の 薄型化が可能となる。

(b)また、ダイパッドを非露出とするのに必要なダイパッドのディプレス加工も不要 になるので、リードフレームのコストダウンが図れる。

(c)ダイパッドのみならず、ダイパッド吊り部が不要となるため、外部端子を配置す る上での制約が緩和され、半導体装置の小型化及び多ピン化を実現できる。

(d)ダイパッドを不要として半導体素子を絶縁物質層を介して樹脂フィルムに固定し て半導体素子をダイボンドできるので、ダイボンド時に半導体素子のずれが発生しにく い。

(e)ダイパッドを不要として半導体素子は絶縁物質層を介して樹脂フィルムに直接固 定してワイヤボンディングできるので、ワイヤボンド時に熱、荷重、超音波が均一に伝 わり、ワイヤボンディングの接続信頼性が向上する。

(f)ダイパッドが不要であって、半導体素子の裏面を予め絶縁物質層で覆っておくた め、射出成形等での樹脂封止を行なう場合のダイパッドのシフトによるワイヤの切断等 や、ダイパッド裏面のボイド、未充填等の不良が発生しない。

(g)半導体素子の裏面が予め絶縁物質層で保護されているので、実装過程において半 導体素子の裏面の損傷を防止でき、かつプリント配線板への実装時にプリント配線板と 半導体素子との絶縁を容易に行い、実装信頼性が向上する。

(h)リードフレームから端子を形成し、これに半導体素子をワイヤボンディングする ことによって、端子の形成が容易であると同時に、端子での接合強度が十分となり、接 合不良をなくすことができる。

本発明の半導体装置及びその製造方法においては、前記半導体素子が前記端子にワイヤボンディングで接続され、リードフレームから加工された前記端子が外部(接続)端子として前記封止材の少なくとも裏面側に露出していることが望ましい。

このためには、前記リードフレームを支持体上に固定した後、前記半導体ウェハの個片化によって得られた前記半導体素子を前記絶縁物質層の側で前記リードフレームのない前記支持体上に固定し、前記半導体素子と前記リードフレームとをワイヤボンディングで接続し、前記封止材を前記半導体素子及び前記リードフレーム上に被着し、更に前記リードフレームの所定箇所を前記封止材と共に切断して、前記封止材の少なくとも裏面側に前記端子を外部端子として露出させると共に前記封止材の裏面側に前記絶縁物質層を露出させた前記半導体装置を得るのがよい。

この場合、半導体素子をリードフレームにワイヤボンディングすることによって、ボンディング接続部の接合強度が良好であって熱的ストレスに十分に耐え、また低コストでの接続を行うことができる。そして、前記絶縁物質層の裏面と前記封止材及び前記端子の裏面とを同一面上に存在させるのが、パッケージの薄型化に有利であると共に、樹脂フィルム等に半導体素子及び端子を安定して保持し、ワイヤボンディング及び樹脂封止を安定かつ信頼性良く高歩留で行うことができる。

この絶縁物質層は、絶縁性樹脂層、絶縁膜、絶縁基板又は片面接着テープからなり、前記半導体ウェハの裏面に形成しておくのがよい。

この場合、前記半導体ウェハの裏面に、前記絶縁性樹脂層をスピンコート、トランスファー形成、印刷又はポッティングにより形成し、絶縁膜をスパッタ又は蒸着により形成し、前記絶縁基板を接着し、前記片面接着テープを接着することができる。

次に、本発明の好ましい実施の形態を図面参照下に説明する。

第1の実施の形態

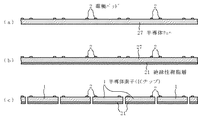

図1〜図4は、本発明の第1の実施の形態を示すものである。

図1〜図4は、本発明の第1の実施の形態を示すものである。

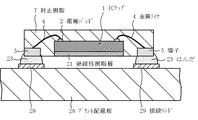

図1(A)は本実施の形態による半導体装置(半導体パッケージ)20の断面図、図1(B)はその平面図、図1(C)はその裏面図である。この半導体装置20は、半導体素子(ICチップ)1の裏面に予めコーティングした絶縁性樹脂層21を半導体装置(又は封止材7)裏面に露出させ、かつリードフレームから作製された端子(外部端子)5の裏面及び側面も露出させ、絶縁性樹脂層21の裏面と端子5の裏面とを同一平面上に存在させた構造となっていることを特徴としている。その他は、図8に示した従来構造と同様である。

この半導体装置20を製造するには、まず、図3(a)に示すように、各素子領域を

作り込み、表面に各電極パッド2を形成した半導体ウェハ27の裏面に接して、図3(b)に示すように、エポキシ樹脂等の絶縁性樹脂層21をコーティングし、更に図3(c)に示すように、半導体ウェハ27をダイシングにより個片化して、裏面に接して絶縁性樹脂層21が形成された半導体素子1を作製する。

作り込み、表面に各電極パッド2を形成した半導体ウェハ27の裏面に接して、図3(b)に示すように、エポキシ樹脂等の絶縁性樹脂層21をコーティングし、更に図3(c)に示すように、半導体ウェハ27をダイシングにより個片化して、裏面に接して絶縁性樹脂層21が形成された半導体素子1を作製する。

ここで、半導体素子1裏面に絶縁性樹脂層21をウェハ状態でスピンコート、トランスファー成形、印刷、ポッティング等により形成した後、ダイシング装置によって個片に分割する。

次いで、図2(a)に示すように、リードフレーム24と、リードフレーム24及び半導体素子1を固定するための樹脂フィルム25とを準備し、リードフレーム24を樹脂フィルム25上に固定する。このリードフレーム24は半導体装置が複数個取れる構造になっており、最終的に個片に分割される。この場合、予めNi−Pd−Au等のめっき処理がされたリードフレームを用いることもできる。

次いで、図2(b)に示すように、裏面に予め絶縁性樹脂層21がコーティングされた半導体素子1をリードフレーム24間の樹脂フィルム25上の所定のエリアに接着する。

次いで、図2(c)に示すように、半導体素子1の電極2とリードフレーム24のリード部(端子)5とをワイヤボンディング装置によってAu、Al等のワイヤ4で接続する。

次いで、図2(d)に示すように、半導体装置全体を射出成形法やポッティング法、印刷法等によってエポキシ樹脂等の樹脂7で封止する。この封止樹脂7は、熱硬化性樹脂や紫外線硬化性樹脂等、半導体パッケージに用いられる一般的なものでよい。

次いで、図2(e)に示すように、樹脂フィルム25に加熱処理、UV(紫外線)照射等を施して、樹脂フィルム25をピールオフにより除去する。リードフレーム24に予めめっき処理がされていない場合には、樹脂フィルム25の除去後にSn−BiやSn−Ag−Cu、Ni−Au等のめっき処理を行なう。

次いで、図2(f)に示すように、リードフレーム24の所定箇所を封止樹脂7と共にダイシング装置によるブレード26で分割し、図1(A)に示した如き各半導体装置1に個片化する。

図4には、こうして得られた半導体装置1の端子5をはんだ23によってプリント配線板28上の接続ランド29に接合して、半導体装置1を実装した状態を示す。

本実施の形態によるパッケージ構造とその製造方法によれば、半導体素子1を搭載するためのダイパッドを不要としているので、ダイパッドに必要とされる厚みや、ダイパッド裏面を非露出とするためのディプレス加工によるダイパッドのアップセットが不要となるため、半導体装置20の薄型化とコストダウンが可能となる。

また、ダイパッドのみならず、ダイパッド吊り部が不要となるため、外部端子5を配置する上での制約が緩和され、半導体装置20の小型化及び多ピン化を実現できる。

そして、ダイパッドを不要として半導体素子1を絶縁性樹脂層21を介して樹脂フィルム25に固定して半導体素子1をダイボンドできるので、ダイボンド時に半導体素子1のずれが発生しにくくなると共に、その樹脂フィルム25に半導体素子1を絶縁性樹脂層21を介して固定してワイヤボンディングできるので、ワイヤボンド時に熱、荷重、超音波が均一に伝わり、ワイヤボンディングの接続信頼性が向上する。

また、ダイパッドが不要であって、ウェハ状態で個片化前の半導体素子1の裏面を予めエポキシ樹脂等の絶縁性樹脂層21で覆っておき、個片化後の半導体素子1を絶縁性樹脂層21を介して樹脂フィルム25上に固定しているので、射出成形等での樹脂封止を行なう場合のダイパッドのシフトによるワイヤ4の切断等や、ダイパッド裏面のボイド、未充填等の不良が発生しない。

そして、半導体素子1の裏面が予め絶縁性樹脂層21で覆われて保護されているので、実装過程において半導体素子1の裏面の損傷を防止でき、かつ半導体素子1の裏面の電気的絶縁性を確保してプリント配線板28への実装時にプリント配線板28と半導体素子1との絶縁を容易に行い、実装信頼性が向上する。

しかも、リードフレーム24から端子5を形成し、これに半導体素子1をワイヤボンディングすることによって、端子5の形成が容易であると同時に、端子5での接合強度が十分となり、接合不良をなくすことができる。

なお、絶縁性樹脂層21は、上記の電気的絶縁性の確保のためには、20〜100μmの厚みを有することが望ましく、また材質的には、半導体素子1との間及び封止樹脂7との間にクラックが入り難いものであることが望ましく、封止樹脂7と熱膨張係数等の近いエポキシ系樹脂やポリイミド系樹脂からなるのがよい。

また、半導体素子1をリードフレーム24にワイヤボンディングすることによって、ボンディング接続部の接合強度が良好であって熱的ストレスに十分に耐え、また低コストでの接続を行うことができる。そして、半導体素子の裏面に予め形成した絶縁性樹脂層21の裏面とリードフレーム24の裏面とを同一平面上に存在させているので、パッケージの薄型化に有利であると共に、樹脂フィルム25に半導体素子1及びリードフレーム24を安定して保持し、ワイヤボンディング及び樹脂封止を安定かつ信頼性良く高歩留で行うことができる。

第2の実施の形態

図5は、本発明の第2の実施の形態を示すものである。

図5は、本発明の第2の実施の形態を示すものである。

図5(A)は本実施の形態による半導体装置(半導体パッケージ)30の断面図、図5(B)はその平面図、図5(C)はその裏面図である。この半導体装置30は、半導体素子(ICチップ)1の裏面に予めスパッタリング又は真空蒸着で形成したSiO2等の絶縁膜31を半導体装置(または封止材7)裏面に露出させ、かつリードフレームから作製された端子(外部端子)5の裏面及び側面を露出させ、絶縁膜31の裏面と端子5の裏面とを同一平面上に存在させた構造となっていることを特徴としている。その他は、図8に示した従来構造と同様である。

本実施の形態によれば、半導体ウェハの状態でその裏面にSiO2等の絶縁膜31をスパッタリング等により成膜した後は、図2(a)〜(f)に示した工程によって図5に示した半導体パッケージ30を作製する。従って、上述した第1の実施の形態と同様の作用効果を得ることができる。

第3の実施の形態

図6は、本発明の第3の実施の形態を示すものである。

図6は、本発明の第3の実施の形態を示すものである。

図6(A)は本実施の形態による半導体装置(半導体パッケージ)40の断面図、図6(B)はその平面図、図6(C)はその裏面図である。この半導体装置40は、半導体素子(ICチップ)1の裏面に予め接着剤42(又は接着テープ)等により接着したガラス、セラミックス等の絶縁基板41を半導体装置(又は封止材7)裏面に露出させ、かつリードフレームから作製された端子(外部端子)5の裏面及び側面を露出させ、絶縁基板41の裏面と端子5の裏面とを同一平面上に存在させた構造となっていることを特徴としている。その他は、図8に示した従来構造と同様である。

本実施の形態によれば、半導体ウェハの状態でその裏面にガラス等の絶縁基板41を被着した後は、図2(a)〜(f)に示した工程によって図6に示した半導体パッケージ40を作製する。従って、上述した第1の実施の形態と同様の作用効果を得ることができる。

第4の実施の形態

図7は、本発明の第4の実施の形態を示すものである。

図7は、本発明の第4の実施の形態を示すものである。

図7(A)は本実施の形態による半導体装置(半導体パッケージ)50の断面図、図6(B)はその平面図、図6(C)はその裏面図である。この半導体装置50は、半導体素子(ICチップ)1の裏面に予め接着した片面接着テープ51を半導体装置(または封止材7)裏面に露出させ、かつリードフレームから作製された端子(外部端子)5の裏面及び側面を露出させ、片面接着テープ51の裏面と端子5の裏面とを同一平面上に存在させた構造となっていることを特徴としている。その他は、図8に示した従来構造と同様である。

本実施の形態によれば、半導体ウェハの状態でその裏面に片面接着テープ51を接着した後は、図2(a)〜(f)に示した工程によって図7に示した半導体パッケージ50を作製する。従って、上述した第1の実施の形態と同様の作用効果を得ることができる。上記の片面接着テープ51は、半導体素子1側に接着面を有し、ウェハ状態で接着されるものであるが、ダイシングシートに接着させたものや、ダイシングシート自体を用いることも可能である。

以上に述べた各実施の形態は、本発明の技術的思想に基づいて種々に変形が可能である。

例えば、上述した半導体パッケージの各構成部分の材質や形状等は種々に変更してよいし、端子の配置やパターンも上述したものに限定されることはない。

1…ICチップ(半導体素子)、2…電極パッド、3…ダイパッド、4…金属ワイヤ、5…端子(外部端子)、7…封止樹脂、8…ダイボンド材、

10、20、30、40、50…半導体パッケージ、21…絶縁性樹脂層、

23…はんだ、24…リードフレーム、25…樹脂フィルム、26…ブレード、

27…半導体ウェハ、28…プリント基板、29…接続ランド、31…絶縁膜、

41…絶縁基板、42…接着剤、51…片面接着テープ

10、20、30、40、50…半導体パッケージ、21…絶縁性樹脂層、

23…はんだ、24…リードフレーム、25…樹脂フィルム、26…ブレード、

27…半導体ウェハ、28…プリント基板、29…接続ランド、31…絶縁膜、

41…絶縁基板、42…接着剤、51…片面接着テープ

Claims (10)

- リードフレームから作製された端子と半導体素子とが接続され、封止材で封止された半導体装置において、前記半導体素子の裏面に接して絶縁物質層が形成され、この絶縁物質層が前記封止材の裏面側に露出していることを特徴とする半導体装置。

- 前記半導体素子が前記端子にワイヤボンディングで接続され、リードフレームから加工された前記端子が外部端子として前記封止材の少なくとも裏面側に露出している、請求項1に記載した半導体装置。

- 前記絶縁物質層の裏面と前記封止材及び前記端子の裏面とが同一面上に存在している、請求項2に記載した半導体装置。

- 前記絶縁物質層が前記半導体素子の裏面に予め形成されたものである、請求項1に記載した半導体装置。

- 前記絶縁物質層が、絶縁性樹脂層、絶縁膜、絶縁基板又は片面接着テープからなる、請求項4に記載した半導体装置。

- 半導体素子と端子とが接続され、封止材で封止された半導体装置の製造方法において、半導体ウェハの裏面に接して絶縁物質層を形成する工程と、前記半導体ウェハを個片化して、裏面に接して前記絶縁物質層が形成された半導体素子を得る工程と、この半導体素子をリードフレーム間に配置する工程と、前記絶縁物質層及び前記リードフレームの裏面を除いて前記半導体素子及び前記リードフレームを封止材で封止する工程と、前記リードフレームの所定箇所を前記封止材と共に切断して、前記端子を形成すると共に、前記絶縁物質層が前記封止材の裏面側に露出した半導体装置を得る工程とを有することを特徴とする半導体装置の製造方法。

- 前記リードフレームを支持体上に固定した後、前記半導体ウェハの個片化によって得られた前記半導体素子を前記絶縁物質層の側で前記リードフレームのない前記支持体上に固定し、前記半導体素子と前記リードフレームとをワイヤボンディングで接続し、前記封止材を前記半導体素子及び前記リードフレーム上に被着し、更に前記リードフレームの所定箇所を前記封止材と共に切断して、前記封止材の少なくとも裏面側に前記端子を外部端子として露出させると共に前記封止材の裏面側に前記絶縁物質層を露出させた前記半導体装置を得る、請求項6に記載した半導体装置の製造方法。

- 前記絶縁物質層の裏面と前記封止材及び前記端子の裏面とを同一面上に存在させる、請求項7に記載した半導体装置の製造方法。

- 絶縁性樹脂層、絶縁膜、絶縁基板又は片面接着テープからなる前記絶縁物質層を前記半導体ウェハの裏面に形成する、請求項6に記載した半導体装置の製造方法。

- 前記半導体ウェハの裏面に、前記絶縁性樹脂層をスピンコート、トランスファー成形、印刷又はポッティングにより形成し、前記絶縁膜をスパッタ又は蒸着により形成し、前記絶縁基板を接着し、前記片面接着テープを接着する、請求項9に記載した半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004105834A JP2005294443A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004105834A JP2005294443A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294443A true JP2005294443A (ja) | 2005-10-20 |

Family

ID=35327058

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004105834A Pending JP2005294443A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294443A (ja) |

Cited By (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007052476A1 (ja) * | 2005-11-02 | 2007-05-10 | Matsushita Electric Industrial Co., Ltd. | 電子回路装置およびその製造方法 |

| JP2009076658A (ja) * | 2007-09-20 | 2009-04-09 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| JP2009253014A (ja) * | 2008-04-07 | 2009-10-29 | Denso Corp | 電子装置の製造方法 |

| JP2013038214A (ja) * | 2011-08-08 | 2013-02-21 | Renesas Electronics Corp | 半導体装置の製造方法 |

| WO2013065895A1 (ko) * | 2011-11-03 | 2013-05-10 | 주식회사 네패스 | 리드프레임을 이용한 팬-아웃 반도체 패키지 제조방법, 이에 의한 반도체 패키지 및 패키지 온 패키지 |

| JP2013235999A (ja) * | 2012-05-10 | 2013-11-21 | Renesas Electronics Corp | 半導体装置の製造方法および半導体装置 |

| WO2014091714A1 (ja) * | 2012-12-14 | 2014-06-19 | 旭化成エレクトロニクス株式会社 | 磁気センサ及び磁気センサ装置、磁気センサの製造方法 |

| CN105185900A (zh) * | 2014-06-17 | 2015-12-23 | 旭化成微电子株式会社 | 霍尔传感器 |

| JP2016021549A (ja) * | 2014-06-17 | 2016-02-04 | 旭化成エレクトロニクス株式会社 | ホールセンサ |

| CN104170109B (zh) * | 2012-12-14 | 2016-11-30 | 旭化成微电子株式会社 | 磁传感器和磁传感器装置 |

| CN106686920A (zh) * | 2016-12-23 | 2017-05-17 | 华中科技大学 | 一种提升电路稳定性的方法 |

| JP2018032852A (ja) * | 2016-08-22 | 2018-03-01 | ローム株式会社 | 半導体装置、半導体装置の実装構造 |

| JP2019220607A (ja) * | 2018-06-21 | 2019-12-26 | 株式会社加藤電器製作所 | 半導体装置の製造方法 |

| CN111261595A (zh) * | 2020-01-20 | 2020-06-09 | 上海艾为电子技术股份有限公司 | 一种无基岛框架封装结构及其制备方法 |

| JP2020123641A (ja) * | 2019-01-30 | 2020-08-13 | 新日本無線株式会社 | 半導体装置およびその製造方法 |

| CN117238877A (zh) * | 2023-11-14 | 2023-12-15 | 青岛泰睿思微电子有限公司 | Dfn框架封装结构及封装方法 |

-

2004

- 2004-03-31 JP JP2004105834A patent/JP2005294443A/ja active Pending

Cited By (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7910406B2 (en) | 2005-11-02 | 2011-03-22 | Panasonic Corporation | Electronic circuit device and method for manufacturing same |

| WO2007052476A1 (ja) * | 2005-11-02 | 2007-05-10 | Matsushita Electric Industrial Co., Ltd. | 電子回路装置およびその製造方法 |

| US8558362B2 (en) | 2007-09-20 | 2013-10-15 | Renesas Electronics Corporation | Semiconductor device and manufacturing method of the same |

| JP2009076658A (ja) * | 2007-09-20 | 2009-04-09 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| JP2009253014A (ja) * | 2008-04-07 | 2009-10-29 | Denso Corp | 電子装置の製造方法 |

| JP2013038214A (ja) * | 2011-08-08 | 2013-02-21 | Renesas Electronics Corp | 半導体装置の製造方法 |

| US8513060B2 (en) | 2011-08-08 | 2013-08-20 | Renesas Electronics Corporation | Manufacturing method using multi-step adhesive curing for sealed semiconductor device |

| US8941226B2 (en) | 2011-08-08 | 2015-01-27 | Renesas Electronics Corporation | Sealed semiconductor device having adhesive patch with inwardly sloped side surfaces |

| KR101297015B1 (ko) | 2011-11-03 | 2013-08-14 | 주식회사 네패스 | 리드프레임을 이용한 팬-아웃 반도체 패키지 제조방법, 이에 의한 반도체 패키지 및 패키지 온 패키지 |

| WO2013065895A1 (ko) * | 2011-11-03 | 2013-05-10 | 주식회사 네패스 | 리드프레임을 이용한 팬-아웃 반도체 패키지 제조방법, 이에 의한 반도체 패키지 및 패키지 온 패키지 |

| JP2013235999A (ja) * | 2012-05-10 | 2013-11-21 | Renesas Electronics Corp | 半導体装置の製造方法および半導体装置 |

| US9269671B2 (en) | 2012-05-10 | 2016-02-23 | Renesas Electronics Corporation | Semiconductor device manufacturing method and semiconductor device |

| WO2014091714A1 (ja) * | 2012-12-14 | 2014-06-19 | 旭化成エレクトロニクス株式会社 | 磁気センサ及び磁気センサ装置、磁気センサの製造方法 |

| CN104170109A (zh) * | 2012-12-14 | 2014-11-26 | 旭化成微电子株式会社 | 磁传感器和磁传感器装置以及磁传感器的制造方法 |

| CN106848055A (zh) * | 2012-12-14 | 2017-06-13 | 旭化成微电子株式会社 | 磁传感器和磁传感器装置以及磁传感器的制造方法 |

| JPWO2014091714A1 (ja) * | 2012-12-14 | 2017-01-05 | 旭化成エレクトロニクス株式会社 | 磁気センサの製造方法 |

| CN104170109B (zh) * | 2012-12-14 | 2016-11-30 | 旭化成微电子株式会社 | 磁传感器和磁传感器装置 |

| JP2016021549A (ja) * | 2014-06-17 | 2016-02-04 | 旭化成エレクトロニクス株式会社 | ホールセンサ |

| JP2018137470A (ja) * | 2014-06-17 | 2018-08-30 | 旭化成エレクトロニクス株式会社 | ホールセンサ |

| CN105185900A (zh) * | 2014-06-17 | 2015-12-23 | 旭化成微电子株式会社 | 霍尔传感器 |

| JP2017120927A (ja) * | 2014-06-17 | 2017-07-06 | 旭化成エレクトロニクス株式会社 | ホールセンサ |

| CN107195772A (zh) * | 2014-06-17 | 2017-09-22 | 旭化成微电子株式会社 | 霍尔传感器 |

| CN107195772B (zh) * | 2014-06-17 | 2019-06-25 | 旭化成微电子株式会社 | 霍尔传感器 |

| CN105185900B (zh) * | 2014-06-17 | 2018-07-06 | 旭化成微电子株式会社 | 霍尔传感器 |

| JP2018032852A (ja) * | 2016-08-22 | 2018-03-01 | ローム株式会社 | 半導体装置、半導体装置の実装構造 |

| CN106686920A (zh) * | 2016-12-23 | 2017-05-17 | 华中科技大学 | 一种提升电路稳定性的方法 |

| JP2019220607A (ja) * | 2018-06-21 | 2019-12-26 | 株式会社加藤電器製作所 | 半導体装置の製造方法 |

| JP2020123641A (ja) * | 2019-01-30 | 2020-08-13 | 新日本無線株式会社 | 半導体装置およびその製造方法 |

| JP7243016B2 (ja) | 2019-01-30 | 2023-03-22 | 日清紡マイクロデバイス株式会社 | 半導体装置およびその製造方法 |

| CN111261595A (zh) * | 2020-01-20 | 2020-06-09 | 上海艾为电子技术股份有限公司 | 一种无基岛框架封装结构及其制备方法 |

| CN117238877A (zh) * | 2023-11-14 | 2023-12-15 | 青岛泰睿思微电子有限公司 | Dfn框架封装结构及封装方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6441475B2 (en) | Chip scale surface mount package for semiconductor device and process of fabricating the same | |

| JP3461720B2 (ja) | 樹脂封止型半導体装置 | |

| JP5529371B2 (ja) | 半導体装置及びその製造方法 | |

| JP3189703B2 (ja) | 半導体装置及びその製造方法 | |

| US7405486B2 (en) | Circuit device | |

| JP5065586B2 (ja) | 半導体装置の製造方法 | |

| JP2001015679A (ja) | 半導体装置及びその製造方法 | |

| JP2002026233A (ja) | 半導体装置およびその製造方法 | |

| JP2017147272A (ja) | 半導体装置およびその製造方法、ならびに、半導体装置の製造に使用されるリードフレーム中間体 | |

| US10943857B2 (en) | Substrate with multi-layer resin structure and semiconductor device including the substrate | |

| JP2005294443A (ja) | 半導体装置及びその製造方法 | |

| JP3660663B2 (ja) | チップパッケージの製造方法 | |

| TWI834888B (zh) | 封裝基板 | |

| KR101394647B1 (ko) | 반도체 패키지 및 그 제조방법 | |

| JP2001332580A (ja) | 半導体装置及びその製造方法 | |

| JP2004063804A (ja) | 半導体装置、積層型半導体装置およびそれらの製造方法 | |

| KR100831481B1 (ko) | 반도체 장치와 그것을 이용한 반도체 패키지 및 회로 장치 | |

| JP4140012B2 (ja) | チップ状電子部品、その製造方法及び実装構造 | |

| JP4881369B2 (ja) | 半導体装置の製造方法 | |

| JP4356196B2 (ja) | 半導体装置組立体 | |

| JP4311294B2 (ja) | 電子装置およびその製造方法 | |

| JP2002124597A (ja) | プラスチックで取り囲まれた構成素子を製作する方法及びプラスチックで取り囲まれた構成素子 | |

| JP4597183B2 (ja) | 半導体装置の製造方法 | |

| JP2001127196A (ja) | ターミナルランドフレーム及びその製造方法、並びに樹脂封止型半導体装置及びその製造方法 | |

| JP4179702B2 (ja) | 半導体装置の製造方法 |