JP2005222581A - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP2005222581A JP2005222581A JP2004026999A JP2004026999A JP2005222581A JP 2005222581 A JP2005222581 A JP 2005222581A JP 2004026999 A JP2004026999 A JP 2004026999A JP 2004026999 A JP2004026999 A JP 2004026999A JP 2005222581 A JP2005222581 A JP 2005222581A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- circuit

- output

- clock

- semiconductor memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

- G11C11/40615—Internal triggering or timing of refresh, e.g. hidden refresh, self refresh, pseudo-SRAMs

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/18—Address timing or clocking circuits; Address control signal generation or management, e.g. for row address strobe [RAS] or column address strobe [CAS] signals

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/401—Indexing scheme relating to cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C2211/406—Refreshing of dynamic cells

- G11C2211/4061—Calibration or ate or cycle tuning

Abstract

【解決手段】 トリガ生成回路104は、トリガ信号を出力する。遅延回路110は、トリガ信号を受けて、トリガ信号を遅延させた遅延信号を出力する。クロックカウンタ106は、クロックを受け、トリガ信号が受けてから遅延信号を受けるまでの間、受けたクロックの数をカウントし、カウント結果を出力する。判定回路107は、クロックの数とレイテンシとの対応関係を記憶し、クロックカウンタから出力されるカウント結果に対応するレイテンシを判定する。レイテンシ用レジスタ108は、判定されたレインテンシを保持する。WAIT制御回路109は、レイテンシ用レジスタ108に保持されたレインテンシに基づき、外部にWAIT信号を出力する。

【選択図】 図1

Description

本実施の形態は、レイテンシを適切なタイミングで内部で自動的に適切な値に設定する同期式擬似SRAMに関する。

(構成)

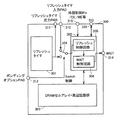

図1は、本実施の形態に係る同期式擬似SRAM100の構成を示す。同図を参照して、この同期式擬似SRAM100は、DRAMセルアレイ+周辺回路群101と、アドレスバッファ103と、制御回路102とを含む。

第1の実施形態において、トリガ生成回路104は、読出し信号READが生成されたことを検知して、トリガ信号Triggerを生成したが、これに限定するものではない。たとえば、以下のような場合に、トリガ信号Triggerを生成するものとしてもよい。

本実施の形態は、セルフリフレッシュするバンクを適切に切替えて、WAIT期間を短くした同期式擬似SRAMに関する。

図4は、本実施の形態に係る同期式擬似SRAM200の構成を示す。同図を参照して、この同期式擬似SRAM200は、DRAMセルアレイ+周辺回路群201と、制御回路202とを備える。

第1比較回路225は、2つのバンクアドレスが異なるときには、リフレッシュ実施済/未実施判定回路223から受けたバンクアドレスをリフレッシュ制御回路211に送るとともに、リフレッシュ実施済みバンク保持回路224にそのバンクアドレスを出力し保持させる。第1比較回路225は、2つのバンクアドレスが同一のときには、次のバンクアドレスを指示する信号NEXTを出力する。

第2比較回路227は、2つのバンクアドレスが異なるときには、リフレッシュ実施済/未実施判定回路223から受けたバンクアドレスをリフレッシュ制御回路211に送るとともに、リフレッシュ実施済みバンク保持回路224にそのバンクアドレスを出力し保持させる。第2比較回路227は、2つのバンクアドレスが同一のときには、リフレッシュ実施済/未実施判定回路223から受けたバンクアドレスと、そのバンクアドレスのバンクの読出し動作終了後にリフレッシュを行なう旨の指令とをリフレッシュ制御回路211に送る。

まず、本実施の形態に係る同期式擬似SRAM200の動作の比較のため、従来の同期式擬似SRAMの動作を説明する。

図7は、本実施の形態に係る同期式擬似SRAM200の動作例を説明するための図である。

図8は、本実施の形態に係る同期式擬似SRAM200の別の動作例を説明するための図である。

本実施の形態は、複数個の同期式擬似SRAMを1つのパッケージに収容し、複数個の同期式擬似SRAMのリフレッシュのタイミングを同一にする構成に関する。

図9は、本実施の形態に係る1つのパッケージに収容される各同期式擬似SRAM300の構成を示す。この同期式擬似SRAM300は、リフレッシュタイマ301と、制御回路302と、DRAMセルアレイ+周辺回路群303と、スイッチ304とを含む。

図11は、本実施の形態に係る2個の同期式擬似SRAMを収納したパッケージの構成を示す。同図を参照して、第1の同期式擬似SRAM300aおよび第2の同期式擬似SRAM300bは、それぞれ、図9の同期式擬似SRAMと同様の構成である。第1の同期式擬似SRAM300aのボンディングオプションPAD313aは、開放されており、スイッチ304aは、リフレッシュタイマ301aから出力されたリフレッシュサイクル信号/Refcycをリフレッシュ制御回路305aに送る。

WAIT制御回路306aは、WAIT端子314aおよび314を通じてWAIT信号を出力し、WAIT制御回路306bは、WAIT端子314bおよび314を通じてWAIT信号を出力する。リフレッシュ制御回路305aおよび305bのリフレッシュのタイミングが同一となるので、各WAIT信号が「L」に変化するタイミングも同一となる。

本実施の形態は、バースト読出し/書込みにおいて、読出しまたは書込み信号が生成された第1のクロックに従って先頭から数個のビットの読出し/書込みを行ない、コマンドレイテンシCLで規定される第2のクロック以降のクロックに従って、残りのビットの読出し/書込みを行なう同期式擬似SRAMに関する。

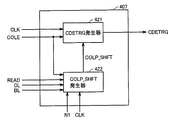

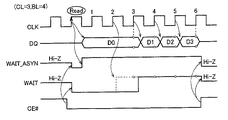

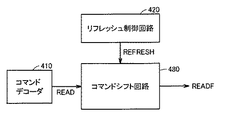

図12は、本実施の形態に係る同期式擬似SRAM400の構成を示す。同図を参照して、この同期式擬似SRAM400は、DRAMセルアレイ401と、制御回路402と、アドレスバッファ403と、RCR(Refresh Configuration Register)404と、BCR405(Bus Configuration Register)と、入出力回路およびバッファ406とを備える。

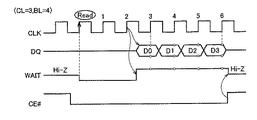

図17は、従来の同期式擬似SRAMのWAIT信号のタイミングを表す図である。同図に示すように、読出し信号READが入力され、かつ、外部チップイネーブル信号CE#が「L」に活性化されていることに応じて、WAIT信号は、「L」になる。その後、(CL−1)(CL=3)の個数のクロックを受けた後、WAIT信号が「H」になる。その後、外部チップイネーブル信号CE#が「H」に非活性化されたことに応じて、WAIT信号は、Hi−Zになる。

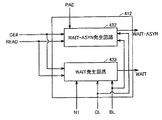

図18は、本実施の形態の同期式擬似SRAM400のWAIT_ASYN信号およびWAIT信号のタイミングを表す図である。同図に示すように、読出し信号READが入力され、かつ、外部チップイネーブル信号CE#が「L」に活性化されていることに応じて、WAIT_ASYN信号は、「L」になる。その後、プリアンプ活性化信号PAEを受けた後、先頭のビットのデータD0がデータ出力端子DQから出力されるのに要する所定時間の経過後、WAIT_ASYN信号は、「H」になる。これにより、クロックCLK0に従ってコラムアクセスが行なわれる先頭のビットのデータD0が出力されるタイミングを外部のシステム側に通知することができる。その後、外部チップイネーブル信号CE#が「H」に非活性化されたことに応じて、WAIT_ASYN信号はHi−Zになる。

図20は、本実施の形態の同期式擬似SRAM400の動作を示すタイミングチャートである。同図を参照して、まず、読出し信号READが生成されたクロックCLK0(第1のクロック)の立ち上がりに同期して、以下のようにロウアクセス処理が行なわれる。

本変形例は、リフレッシュ動作中に読出し信号READまたは書込み信号WRITEが生成されたときにおいても、第4の実施形態と同様に、バースト読出し/書込みにおいて、第1のクロックに従って先頭から数個のビットを読出し/書込みし、コマンドレイテンシCLで規定される第2のクロック以降のクロックに従って、残りのビットを読出し/書込みする同期式擬似SRAMに関する。

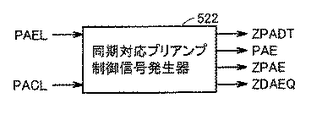

本実施の形態は、同期モードと、非同期モードの両方のモードを有し、それぞれのモードに適した第2の増幅回路であるプリアンプを有する同期式擬似SRAMに関する。なお、第1の増幅回路であるセンスアンプは、ビット線対BL,ZBLの電位を増幅するものであり、第2の増幅回路であるプリアンプは、複数のビット線対BL,ZBLに接続されたグローバルビット線対GIO,ZGIOの電位を増幅するものである。

図25は、本実施の形態に係る同期式擬似SRAM500の構成を示す。同図を参照して、この同期式擬似SRAM500は、DRAMセルアレイ501と、制御回路502と、周辺回路群504と、アドレスバッファ503とを含む。

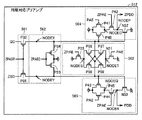

図35は、同期対応プリアンプ512の構成を示す。同図に示すように、この同期対応プリアンプ512は、反転プリアンプ接続信号ZPADTで制御されるスイッチ部561と、反転プリアンプイコライズ信号ZPAEQで制御されるイコライズ部562と、プリアンプ活性化信号PAEおよび反転プリアンプ活性化信号ZPAEで制御される増幅部563と、プリアンプ活性化信号PAEおよび反転プリアンプ活性化信号ZPAEで制御されるバッファ部564,565とを備える。

図37は、非同期対応プリアンプ513の構成を示す。同図に示すように、この非同期対応プリアンプ513は、差動式のカレントミラータイプの増幅器である。

本実施の形態は、バイトマスク機能を有する同期式擬似SRAMに関する。同期式擬似SRAMには、上位バイトまたは下位バイトのマスクを行なうことで、メモリセルから読み出したデータを外部へ出力させないようにすることができる。ところで、バーストモードにおいて、ノーラップモードというものがある。ノーラップモードでは、バースト読出しまたは書込みの途中に最後のコラムに達すると、次のロウへ移行する。この場合、選択していたワード線の不活性化、新たに選択するワード線の活性化、およびセンスアンプによる増幅処理などのロウアクセス処理が必要となる。ロウアクセス処理が行なわれている間、外部に対してWAIT信号が出力される。外部のシステム側は、このWAIT信号が解除されてから、バイトマスク信号を与えればよいが、外部のシステムにとっては、このような次のロウへ移行するためのロウアクセス処理の有無に係らず、同一の方法でバイトマスクの設定ができた方が望ましい。本実施の形態は、バースト読出しまたはバースト書込みが第1のロウと第2のロウの2つのロウに渡り、途中で第1のロウの最後のコラムに達したため第2のロウへ移行する場合においても、外部からは2つのロウに渡らない場合と同様にしてバイトマスク信号を与えることを可能とする同期式擬似SRAMに関する。

提供する。

図44は、本実施の形態に係る同期式擬似SRAM600の構成を示す。同図を参照して、この同期式擬似SRAM600は、DRAMセルアレイ601と、CLKバッファ604と、UBバッファ605と、LBバッファ606と、WEバッファ607と、ADVバッファ608と、制御回路602と、周辺回路群603と、BCR(Bus Configuration Register)610とを備える。

図54は、本実施の形態の同期式擬似SRAM600におけるバースト読出し時に次のロウへの移行を伴わないときの信号の変化を表すタイミングチャートである。同図を参照して、例1〜例3の動作を説明する。

外部バイトマスク信号LB#,UB#は、「H」となることがない。この場合には、第1出力イネーブル信号OE1、第2出力イネーブル信号OE2、および第3出力イネーブル信号OE3は、全期間「H」となる。

外部バイトマスク信号LB#,UB#は、同図の(1)において、「H」となる。この場合には、第1出力イネーブル信号OE1および第3出力イネーブル信号OE3は、全期間「H」となる。一方、第2出力イネーブル信号OE2は、同図の(2)に示すように、第2ビットが出力回路620から出力されるタイミング(クロックCLK3の立ち上がりからクロックCLK4の立ち上がりまで)において「L」となる。

外部バイトマスク信号LB#,UB#は、同図の(3)において、「H」となる。この場合には、第2出力イネーブル信号OE2および第3出力イネーブル信号OE3は、全期間「H」となる。第1出力イネーブル信号OE1は、同図の(4)に示すように、外部バイトマスク信号LB#,UB#が「H」となったクロックCLKから、第1ビットが出力回路620から出力されるタイミングを含む時点まで(クロックCLK0の立ち上がりからクロックCLK3の立ち上がりまで)、「L」となる。

図55は、本実施の形態の同期式擬似SRAM600におけるノーラップモード設定時に、バースト読出し時に次のロウへの移行を伴うときの変化を表すタイミングチャートである。同図を参照して、例1〜例3の動作を説明する。

外部バイトマスク信号LB#,UB#は、「H」となることがない。第1出力イネーブル信号OE1、第2出力イネーブル信号OE2、および第3出力イネーブル信号OE3は、全期間「H」となる。

外部バイトマスク信号LB#,UB#は、同図の(1)において、「H」となる。この場合には、第1出力イネーブル信号OE1および第2出力イネーブル信号OE2は、全期間「H」となる。第3出力イネーブル信号OE3は、同図の(3)に示すように、WAIT信号が「H」となったときのタイミング(クロックCLK7の立ち上がりからクロックCLK8の立ち上がりまで)において「L」となる。

外部バイトマスク信号LB#,UB#は、同図の(3)において、「H」となる。この場合、第1出力イネーブル信号OE1および第3出力イネーブル信号OE3は、全期間「H」となる。第2出力イネーブル信号OE2は、同図の(4)に示すように、第3ビットが出力回路620から出力されるタイミング(クロックCLK8の立ち上がりからクロックCLK9の立ち上がりまで)において「L」となる。

図示しないが、図54の(例3)のとき同一である。

本実施の形態は、モバイルRAMと、セルラーRAMの両方の機能を備えたモバイル/セルラー兼用RAMに関する。ここで、セルラーRAMとは、非特許文献1に記載されている同期型の擬似SRAMである。モバイルRAMは、携帯電話用の特有の機能を備えた擬似SRAMである。

図56は、本実施の形態のモバイル/セルラー兼用RAM700の構成を示す。同図を参照して、このモバイル/セルラー兼用RAM700は、DRAMセルアレイ701と、制御回路707と、入出力回路705とを備える。

本実施の形態は、バーストレングスカウンタを用いてプリチャージを実行する同期式擬似SRAMに関する。

図60は、本実施の形態に係る同期式擬似SRAM800の構成を示す。同図を参照して、この同期式擬似SRAM800は、DRAMセルアレイ+周辺回路群801と、制御回路802と、コマンドデコーダ803と、BCR(Burst Configuration Register)804と、バーストレングスカウンタ805とを備える。

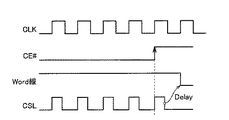

図62は、ワード線が非活性化されるタイミングチャートを示す。同図に示すように、読出し信号READまたは書込み信号WRITEを受けたクロックのタイミングをクロックCLK0とした時に、コマンドレイテンシCL=2、バーストレングスBL=4より、バーストアクセスの最後のコラムの選択のためのコラム選択信号CSLがクロックCLK4のタイミングで活性化される。バーストレングスカウンタ805は、CLK0から、(CL+BL−1)=5個後のクロックであるクロックCLK5のタイミングで、バーストレングスリセット信号BLRSTを「H」に活性化する。そして、このバーストレングスリセット信号BLRSTに基づいて、プリチャージ信号PRCが活性化され、選択されていたワード線(X0)が非活性化され、ビット線対がプリチャージされる。

本実施の形態は、同期モード固定のモードを有する同期式擬似SRAMに関する。

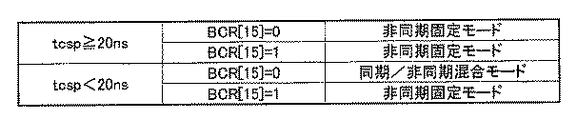

まず、従来のCellularRAM(R)の同期/非同期モードの設定について説明する。

図65は、本実施の形態の同期/非同期モードの設定方法を表す図である。同図に示すように、BCR[16]の値が0のときには、tCSP、およびBCR[15]の値に係らず、同期固定モードに設定される。一方、BCR[16]の値が1のときには、tCSPおよびBCR[15]の値に応じて、従来と同様に設定される。

図66は、本実施の形態に係る同期式擬似SRAM900の構成を示す。同図を参照して、この同期式擬似SRAM900は、DRAMセルアレイ+周辺回路群901と、BCR(Bus Configuration Register)903と、tCSP判定回路906と、同期制御回路904と、非同期制御回路905と、共通制御回路902とを含む。

本実施の形態は、外部チップイネーブル信号CE#によって、入力バッファの活性/非活性を制御するともに、外部チップイネーブル信号CE#をクロックに同期せずに活性化したときの問題を回避する同期式擬似SRAMに関する。

図67は、本実施の形態に係る同期式擬似SRAM1000の構成を示す。同図を参照して、この同期式擬似SRAM1000は、DRAMセルアレイ+周辺回路群1001と、制御回路1002と、CEバッファ1003と、CLKバッファ1004と、制御バッファ1005と、アドレスバッファ1006とを含む。

図68は、従来のADV0発生回路1050の構成を示す。同図を参照して、反転内部アドレス取込み信号ZINTADVがクロックドインバータCIV1に入力される。クロックドインバータCIV1の出力と、内部クロックINTCLKとが反転論理積回路NAND1に入力され、反転論理積回路NAND1の出力がインバータIV1に入力される。インバータIV1の出力がアドレス取込みトリガ信号ADV0となる。

従来のADV0発生回路を用いた場合に、外部クロックCLKと同期せずに、非同期に外部チップイネーブル信号CE#を変化させたときに発生する問題について説明する。

上述の問題を回避するために、本実施の形態のADV0発生回路の構成は、従来のものと相違する。

図71は、本実施の形態のADV0発生回路1010を用いたときの各信号の変化のタイミングを表す図である。

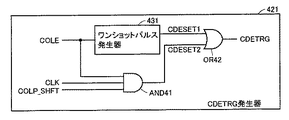

42,56,57 インバータ、48 バッファ、43,49,58 遅延回路、45,52 フリップフロップ、61,バッファ回路、100,200,300,300a,300b 同期式擬似SRAM、101,201,801,901,1001 DRAMセルアレイ+周辺回路群、102,202,302,302a,302b,402,502,602,802,1002 制御回路、103,403,503,1006 アドレスバッファ、104 トリガ生成回路、105 カウンタイネーブル回路、106 クロックカウンタ、107 判定回路、108 レイテンシ用レジスタ、109,306,306a,306b,412,511,619 WAIT制御回路、110 遅延回路、111,211,305,305a,305b,420,510,620 リフレッシュ制御回路、121 ラッチ回路、212,301,301a,301b,721 リフレッシュタイマ、213 リフレッシュバンクアドレス指定回路、214,417,803 コマンドデコーダ、221 論理和回路、222 バンクアドレスカウンタ、223 リフレッシュ実施済/未実施判定回路、224 リフレッシュ実施済バンク保持回路、225 第1比較回路、226 読出し/書込み動作バンク検知回路、227 第2比較回路、303,303a,303b,401,501,601,701 DRAMセルアレイ、304 スイッチ、311,311a,311b リフレッシュタイマ出力PAD、312,312a,312b リフレッシュタイマ入力PAD、313,313a,313b ボンディングオプションPAD、314,314a,314b WAIT端子、315,315a,315b 制御信号端子、316,316a,316b データ入出力端子、407,505 コラム制御回路、409,499,618,806 ロウ制御回路、410,506,611 コマンドデコーダ、421 CDETRG発生器、422 COLP_SHFT発生器、431 ワンショットパルス発生器、432 WAIT_ASYN発生回路、433 WAIT発生回路、408,504,603 周辺回路群、480 コマンドシフト回路、507 共通信号生成回路、508 同期対応プリアンプ制御回路、508 同期対応プリアンプ制御回路、509 非同期対応プリアンプ制御回路、404 RCR、405,610,903 BCR、406 入出力回路およびバッファ、417 コラムデコーダ、418 ロウデコーダ、512 同期対応プリアンプ、513 非同期対応プリアンプ、514 同期対応DBドライバ、515,620 出力回路、516 非同期対応DBドライバ、521 基準信号発生器、522 同期対応プリアンプ制御信号発生器、523 プリアンプ活性化準備信号発生器、524 同期指示信号発生器、561 スイッチ部、562 イコライズ部、563 増幅部、564,565 バッファ部、590 共用DBドライバ、596 同期対応プリアンプ配置領域、577 非同期対応プリアンプ配置領域、598 同期/非同期対プリアンプ配置領域、604,1004 CLKバッファ、605 UBバッファ、606 LBバッファ、607 WEバッファ、608 ADVバッファ、609,1003 CEバッファ、612 ZRST生成回路、613 ZUB0生成回路、614 ZLB0生成回路、615 ADV0生成回路、616 ZWE0生成回路、617 マスク制御回路、631 第1制御回路、632 第2制御回路、633 第3制御回路、702 共通部、703 モバイルRAM専用部、704 セルラーRAM専用部、705 入出力回路、706 モバイルRAM/セルラーRAM判定回路、722 センス動作制御回路、723 アドレスキュー対策回路、724 入出力バッファ、731 コマンドモード回路、732 バーストリフレッシュ回路、733 アーリーライト回路、734 データ保持ブロック制御回路、741 同期インタフェース回路、742 ZADV制御回路、743 NORインタフェース回路、744 その他のセルラー互換動作制御回路、745 BCR/RCRセット回路、804 BCR、805 バーストレングスカウンタ、902 共通制御回路、904 同期制御回路、905 非同期制御回路、906 tCSP判定回路、400,500,600,800,900,1000 同期式擬似SRAM、700 モバイル/セルラー兼用RAM、999 CSLカウンタ、1005 制御バッファ、1010 ADV0発生回路、1011 RAS発生回路、221,OR42 論理和回路、AND1,AND41,AND101 論理積回路、IV1〜IV3,IV11,IV12,IV21〜IV44,IV51,IV52〜IV56,IV59,IV71〜IV74,IV81〜IV89 インバータ、OR42 論理和回路、NOR21,NOR22,NOR71,NOR81〜NOR85,NOR95,NOR98,NOR99 反転論理和回路、NAND1,NAND21〜NAND36,NAND53〜NAND58,NAND60,NAND81〜NAND91 反転論理積回路、DL11,DL21,DL51〜DL54,DL81〜DL83,DL99,DL101,DL102,DL191,DL192 遅延回路(Delay)、HDL53 High側Delay、C コンデンサ、R 負荷、P31〜P45,P51〜P62,P71〜P76 PチャネルMOSトランジスタ、N31〜N33,N51〜N62,N71〜N76 NチャネルMOSトランジスタ、CV1、CV61〜CV64 クロックドインバータ。

Claims (23)

- クロックに同期して動作する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

トリガ信号を出力するトリガ生成回路と、

前記トリガ信号を受けて、前記トリガ信号を遅延させた遅延信号を出力する遅延回路と、

前記クロックを受け、前記トリガ信号を受けてから前記遅延信号を受けるまでの間、受けたクロックの数をカウントし、カウント結果を出力するクロックカウンタと、

クロックの数とレイテンシとの対応関係を記憶し、前記クロックカウンタから出力されるカウント結果に対応するレイテンシを判定する判定回路と、

前記判定されたレインテンシを保持するレジスタと、

前記レジスタに保持されたレインテンシに基づき、外部にウエイト信号を出力するウエイト制御回路とを備えた半導体記憶装置。 - 前記トリガ生成回路は、

外部信号をラッチしてラッチ信号を生成する回路と、

前記ラッチ信号の組合せに応じて、読出し信号または書込み信号ととともに前記トリガ信号を出力する論理回路とを備えた請求項1記載の半導体記憶装置。 - 行列状に配置された複数のダイナミックランダムアクセスメモリのメモリセルを有し、1度のリフレッシュの単位となるバンクを複数個有するメモリアレイと、

リフレッシュのトリガを出力する回路と、

前記リフレッシュトリガを受けたときに、外部から指示された動作を実行中のときに、前記動作を実行中のバンクと異なるバンクを選択して、前記選択したバンクのアドレスを出力するバンク選択回路と、

前記受けたアドレスのバンクのリフレッシュを実行するリフレッシュ制御回路とを備え、

前記バンク選択回路は、

リフレッシュが実施済みのバンクのアドレスを保持し、すべてのバンクのアドレスが保持されると、保持されているすべてのアドレスが消去されるレジスタと、

前記リフレッシュトリガを受けたときに、前記レジスタを参照してリフレッシュが未実施のバンクのアドレスを特定する特定回路と、

前記未実施のバンクアドレスと、前記動作を実行中のバンクアドレスとを比較し、異なる場合に、前記未実施のバンクアドレスを出力する比較回路とを含む半導体記憶装置。 - 行列状に配置された複数のダイナミックランダムアクセスメモリのメモリセルを有するメモリアレイと、

リフレッシュのタイミングを規定する第1の信号を生成する第1の回路と、

前記第1の信号を出力する出力端子と、

外部からリフレッシュのタイミングを規定する第2の信号を受ける入力端子と、

前記第1の信号および前記第2の信号を受けて、いずれかの信号を出力するスイッチと、

前記スイッチから出力される信号を受けて、当該信号に基づきリフレッシュ制御を行なう第2の回路とを備えた半導体記憶装置。 - 前記半導体記憶装置は、さらに、

前記第2の回路でリフレッシュ制御が実行されている間、外部にウエイト信号を出力するウエイト制御回路を備えた請求項4記載の半導体記憶装置。 - 前記第1の回路は、前記第1の信号として一定周期の信号を出力するタイマである、請求項5記載の半導体記憶装置。

- クロックに同期して動作し、バーストモードでのアクセスを行ない、読出し信号または

書込み信号が生成されるのに先立って、ロウアドレスおよびコラムアドレスを取得する半導体記憶装置であって、

行列上に配置された複数のメモリセルを有するメモリアレイと、

外部から受けた制御信号によって読出し信号または書込み信号が生成された第1のクロックに同期して、選択されたロウのロウアクセス処理と、先頭から1個以上かつバーストレングス以下である第1の個数のコラムのコラムアクセス処理を行ない、

レイテンシで規定される第2のクロック以降のクロックに同期して、バーストモードアクセスの残りの第2の個数のコラムのコラムアクセス処理を行なうように制御する制御回路とを備えた半導体記憶装置。 - 前記半導体記憶装置は、

前記メモリセルに接続されたビット線対の電位を増幅するセンスアンプ回路と、

前記コラムを選択するコラムデコーダとを含み、

前記制御回路は、

前記センスアンプ回路を活性化させる信号が生成された後のタイミングで、前記第1のクロックに同期して活性化されるロウ活性化信号に応じてコラムイネーブル信号を生成する第1の制御回路と、

前記コラムイネーブル信号に応じて、前記第1の個数のコラムを活性化させる第1の指示信号を前記コラムデコーダに出力し、前記第2のクロック以降のクロックに同期して前記第2の個数のコラムを活性化させる第2の指示信号を前記コラムデコーダに出力する第2の制御回路とを備える、請求項7記載の半導体記憶装置。 - 前記制御回路は、前記第1のクロックに同期してコラムアクセス処理が行なわれて出力される先頭のデータのタイミングを外部に通知する信号を生成する回路を含む、請求項8記載の半導体記憶装置。

- 前記制御回路は、前記第2のクロック以降のクロックに同期してコラムアクセス処理が行なわれて出力される先頭のデータのタイミングを外部に通知する信号を生成する回路を含む、請求項8記載の半導体記憶装置。

- リフレッシュ動作、読出し動作、または書込み動作を実行中に、前記読出しまたは書込み要求信号が生成されたときには、前記動作の実行終了後の次のクロックを前記第1のクロックとして動作させるためのシフト回路とを備えた請求項8記載の半導体記憶装置。

- 外部信号の組合せによって、複数の動作モードのいずれかのモードに設定される半導体記憶装置であって、

行列上に配置された複数のメモリセルを有するメモリアレイと、

前記メモリセルに各々接続されたビット線対と、

前記ビット線対の電位を増幅する第1の増幅回路と、

複数の前記ビット線対に接続されたIO線対と、

前記各モードに応じていずれかが活性化され、前記IO線対の電位を増幅する2種類以上の第2の増幅回路とを備えた半導体記憶装置。 - 前記複数の動作モードは、外部から入力されるクロックに同期した同期動作モードと、クロックに同期しない非同期動作モードであり、

前記第2の増幅回路は、

同期動作モードに対応した第1の種類の増幅回路と、

非同期動作モードに対応した第2の種類の増幅回路とである、請求項12記載の半導体記憶装置。 - 前記半導体記憶装置は、

同期モードに設定されたときに、前記第1の種類の増幅回路を活性化するとともに、前記第2の種類の増幅回路を非活性化し、

非同期モードに設定されたときに、前記第1の種類の増幅回路を非活性化するとともに、前記第2の種類の増幅回路を活性化させる制御回路と、

前記第1の種類の増幅回路の出力、および前記第2の種類の増幅回路の出力と接続され、前記第1の種類の増幅回路の出力または前記第2の種類の増幅回路の出力のいずれかをデータバスへ出力するデータバスドライバとを備えた請求項13記載の半導体記憶装置。 - 前記第1の種類の増幅回路は、クロックに同期した信号に基づき、前記IO線対と当該第1の種類の増幅回路内の増幅部との間の接続を切断するスイッチ部を備え、

前記第2の種類のプリアンプは、前記IO線対と当該第2の種類の増幅回路内の増幅部との間の接続を切断するスイッチ部を有しない、請求項14記載の半導体記憶装置。 - 前記IO線と接続する前記第1の種類の増幅回路および前記第2の種類の増幅回路は、コラム方向に並んで配置され、

前記IO線対は、分岐を有せずに、前記第1の種類の増幅回路および前記第2の種類の増幅回路と接続する、請求項13記載の半導体記憶装置。 - クロックに同期して動作する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

外部からバイトマスク信号を受けて、前記バイトマスク信号に基づきバイトマスク処理を制御するバイトマスク制御回路と、

前記メモリセルから出力されたデータを受けて、前記バイトマスク制御回路による指示に従って、前記メモリセルから出力されたデータの前記バイトマスク信号に対応するバイトの出力を行なわない出力回路とを備え、

前記バイトマスク制御回路は、連続読出しまたは連続書込みが第1のロウと第2のロウの2つのロウに渡る場合、途中で第1のロウの最後のコラムに達したため第2のロウへの移行のためロウアクセス処理を行なっている間に、外部からバイトマスク信号を受けたときに、前記バイトマスク信号に対応するバイトのマスク処理を、前記ロウアクセスが終了し、次のビットのデータが出力されるタイミングまで延長する、半導体記憶装置。 - 前記半導体記憶装置は、さらに、

前記次のロウへの移行のためロウアクセス処理を行なっている間、データが出力されるまで待つことを外部に知らせるウエイト信号を出力するウエイト制御回路を備え、

前記バイトマスク制御回路は、各バイトごとに、

前記バイトマスク信号が前記連続読出しまたは書込みの先頭のビット以外のビットのバイトマスクを行なうことを示す場合において、前記次のロウへの移行のためロウアクセス処理を行なわないとした場合に前記ビットが前記出力回路から出力されるタイミングに前記ウエイト信号が出力されているときに、前記バイトに対応する出力イネーブル信号をディセーブルにせずに、前記バイトマスク信号に基づいて生成された信号を出力する第1回路と、

前記バイトマスク信号に基づいて生成された信号を受けて保持し、前記ウエイト信号が解除されたタイミングに、前記バイトに対応する出力イネーブル信号をディセーブルにする第2回路とを含み、

前記出力回路は、前記出力イネーブル信号がディセーブルを示すときに、前記メモリセルから出力されたデータの前記ディセーブルの出力イネーブル信号に対応するバイトの出力を行なわない、請求項17記載の半導体記憶装置。 - クロックに同期して動作する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

前記メモリセルに接続されたビット線対と、

コラム選択信号を受けて、バーストアクセスの最後のカラムを選択する選択信号が活性化された後の次のクロックでバーストレングスリセット信号を出力するバーストレングスカウンタと、

前記バーストレングスリセット信号を受けて、前記ビット線対をプリチャージする制御回路とを備えた半導体記憶装置。 - 前記制御回路は、前記バーストレングスリセット信号を受けて、プリチャージ信号を活性化して、前記プリチャージ信号の活性化によって前記ビット線対をプリチャージする、請求項19記載の半導体記憶装置。

- クロックに同期して動作する同期モードと、非同期で動作する非同期モードとを有する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

同期固定モードと、非同期固定モードと、同期および非同期の混載モードのいずれかに設定可能な設定回路と、

前記混載モード時に、外部チップイネーブル信号がアサートされてから、外部クロックの立ち上がりまでの時間が所定値以上か否かを調べ、前記所定値以上のときに、非同期固定モードに移行する非同期移行回路と、

同期固定モードまたは混載モードに設定されたときに同期動作を制御する同期制御回路と、

非同期固定モード若しくは混載モードに設定されたとき、または非同期固定モードに移行したときに、非同期動作を制御する非同期制御回路とを備え、

前記非同期移行回路は、前記設定回路の出力に応じて非活性化される、半導体記憶装置。 - 前記設定回路は、バスコンフィギュレーションレジスタの所定の2個のビットであり、

前記非同期移行回路は、前記ビットの値が同期固定モードまたは非同期固定モードを示すときには、前記移行動作の処理を停止する、請求項21記載の半導体記憶装置。 - クロックに同期して動作する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

外部チップイネーブル信号を受けて内部チップイネーブル信号を生成するチップイネーブルバッファと、

外部クロックを受けて内部クロックを生成するクロックバッファと、

外部アドレス信号を受けて内部アドレス信号を生成するアドレスバッファと、

外部チップイネーブル信号以外の外部制御信号を受けて内部制御信号を生成する制御バッファとを備え、

前記クロックバッファ、前記アドレスバッファ、および前記制御バッファは、前記内部チップイネーブル信号を受けて、前記内部チップイネーブル信号がチップの非活性を示すときに、その動作を停止し、

前記クロックバッファ、前記アドレスバッファ、および前記制御バッファは、前記内部チップイネーブル信号が活性化を示すときに、動作を実行し、

前記制御バッファは、外部アドレス取込信号を受けて、内部アドレス取込信号を生成し、

前記半導体記憶装置は、さらに、

前記内部アドレス取込信号を所定の遅延量だけ遅延させる遅延回路と、

前記遅延回路の出力と前記内部クロックとを受けるクロックドインバータと、

前記クロックドインバータの出力と前記内部クロックとの論理積信号を出力する論理回路と、

前記論理積信号の先頭のパルスに基づき、ロウアドレスストローブ信号を活性化する回路とを備え、

前記論理積信号の先頭のパルスが、前記外部アドレス取込み信号が活性化されている間に立ち上がる外部クロックパルスから生成された内部クロックパルスとなるように、前記遅延回路の所定の遅延量が定められている、半導体記憶装置。

Priority Applications (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004026999A JP2005222581A (ja) | 2004-02-03 | 2004-02-03 | 半導体記憶装置 |

| TW103122670A TWI517151B (zh) | 2004-02-03 | 2005-01-31 | 半導體記憶裝置 |

| TW100114414A TWI460725B (zh) | 2004-02-03 | 2005-01-31 | 半導體記憶裝置 |

| TW094102871A TWI383394B (zh) | 2004-02-03 | 2005-01-31 | 半導體記憶裝置 |

| KR1020050009640A KR101120838B1 (ko) | 2004-02-03 | 2005-02-02 | 휴대 단말기에 탑재하기 적합한 반도체 기억 장치 |

| US11/049,059 US7336557B2 (en) | 2004-02-03 | 2005-02-03 | Semiconductor memory device suitable for mounting on portable terminal |

| US12/007,032 US7480200B2 (en) | 2004-02-03 | 2008-01-04 | Semiconductor memory device suitable for mounting on portable terminal |

| US12/333,913 US7983103B2 (en) | 2004-02-03 | 2008-12-12 | Semiconductor memory device suitable for mounting on portable terminal |

| US13/081,821 US20110199844A1 (en) | 2004-02-03 | 2011-04-07 | Semiconductor Memory Device Suitable for Mounting on a Portable Terminal |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004026999A JP2005222581A (ja) | 2004-02-03 | 2004-02-03 | 半導体記憶装置 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010112253A Division JP5058295B2 (ja) | 2010-05-14 | 2010-05-14 | 半導体記憶装置 |

| JP2010112252A Division JP5048102B2 (ja) | 2010-05-14 | 2010-05-14 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005222581A true JP2005222581A (ja) | 2005-08-18 |

| JP2005222581A5 JP2005222581A5 (ja) | 2007-03-08 |

Family

ID=34805858

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004026999A Pending JP2005222581A (ja) | 2004-02-03 | 2004-02-03 | 半導体記憶装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (4) | US7336557B2 (ja) |

| JP (1) | JP2005222581A (ja) |

| KR (1) | KR101120838B1 (ja) |

| TW (3) | TWI517151B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010033695A (ja) * | 2008-07-29 | 2010-02-12 | Internatl Business Mach Corp <Ibm> | 組み込みdram用リフレッシュ・コントローラ及びリフレッシュ制御方法 |

| JP2012221540A (ja) * | 2011-04-13 | 2012-11-12 | Elpida Memory Inc | 半導体装置及びシステム |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6209071B1 (en) * | 1996-05-07 | 2001-03-27 | Rambus Inc. | Asynchronous request/synchronous data dynamic random access memory |

| US7245552B2 (en) * | 2005-06-22 | 2007-07-17 | Infineon Technologies Ag | Parallel data path architecture |

| EP2098969A4 (en) * | 2006-12-26 | 2013-01-02 | Nec Corp | LOGIC CIRCUIT DESIGN DEVICE FOR ASYNCHRONOUS LOGIC CIRCUITS, LOGIC CIRCUIT DESIGN METHOD, AND LOGIC CIRCUIT DESIGN PROGRAM |

| KR100856130B1 (ko) * | 2007-01-08 | 2008-09-03 | 삼성전자주식회사 | 동기/ 비동기 동작이 가능한 반도체 메모리 장치 및 상기반도체 메모리 장치의 데이터 입/ 출력 방법 |

| JP4679528B2 (ja) * | 2007-01-30 | 2011-04-27 | 株式会社東芝 | リフレッシュトリガー付き半導体記憶装置 |

| KR100945802B1 (ko) * | 2008-06-24 | 2010-03-08 | 주식회사 하이닉스반도체 | 클럭을 생성하는 반도체 집적 회로 |

| KR101697686B1 (ko) * | 2009-07-01 | 2017-01-20 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그 구동 방법 |

| JP2011018427A (ja) * | 2009-07-10 | 2011-01-27 | Renesas Electronics Corp | 半導体記憶装置 |

| KR101043722B1 (ko) * | 2010-02-04 | 2011-06-27 | 주식회사 하이닉스반도체 | 레이턴시 제어회로 및 이를 포함하는 반도체 메모리장치 |

| US8422315B2 (en) * | 2010-07-06 | 2013-04-16 | Winbond Electronics Corp. | Memory chips and memory devices using the same |

| KR20120081352A (ko) * | 2011-01-11 | 2012-07-19 | 에스케이하이닉스 주식회사 | 리프레시 제어 회로, 이를 이용한 메모리 장치 및 그 리프레시 제어 방법 |

| US9129666B1 (en) * | 2011-08-25 | 2015-09-08 | Rambus Inc. | Robust commands for timing calibration or recalibration |

| TWI498889B (zh) * | 2012-03-26 | 2015-09-01 | Etron Technology Inc | 記憶體及更新記憶體的方法 |

| US9350386B2 (en) * | 2012-04-12 | 2016-05-24 | Samsung Electronics Co., Ltd. | Memory device, memory system, and method of operating the same |

| JP2013229068A (ja) * | 2012-04-24 | 2013-11-07 | Ps4 Luxco S A R L | 半導体装置及びこれを備える情報処理システム |

| US8754691B2 (en) | 2012-09-27 | 2014-06-17 | International Business Machines Corporation | Memory array pulse width control |

| JP2014096191A (ja) | 2012-11-09 | 2014-05-22 | Renesas Electronics Corp | 半導体記憶装置 |

| US9147461B1 (en) * | 2012-11-28 | 2015-09-29 | Samsung Electronics Co., Ltd. | Semiconductor memory device performing a refresh operation, and memory system including the same |

| US20150003172A1 (en) * | 2013-06-26 | 2015-01-01 | Sua KIM | Memory module including buffer chip controlling refresh operation of memory devices |

| TWI553641B (zh) * | 2013-12-09 | 2016-10-11 | 慧榮科技股份有限公司 | 資料儲存裝置及其模式偵測方法 |

| US9600179B2 (en) * | 2014-07-30 | 2017-03-21 | Arm Limited | Access suppression in a memory device |

| US10394641B2 (en) * | 2017-04-10 | 2019-08-27 | Arm Limited | Apparatus and method for handling memory access operations |

| JP6871286B2 (ja) * | 2019-02-21 | 2021-05-12 | 華邦電子股▲ふん▼有限公司Winbond Electronics Corp. | 疑似スタティックランダムアクセスメモリの制御回路及び制御方法 |

| JP6894459B2 (ja) * | 2019-02-25 | 2021-06-30 | 華邦電子股▲ふん▼有限公司Winbond Electronics Corp. | 疑似スタティックランダムアクセスメモリとその動作方法 |

| KR20210143078A (ko) * | 2020-05-19 | 2021-11-26 | 에스케이하이닉스 주식회사 | 커맨드 입력을 제어하기 위한 전자장치 |

| TWI740581B (zh) * | 2020-07-20 | 2021-09-21 | 華邦電子股份有限公司 | 虛擬靜態隨機存取記憶體裝置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09259080A (ja) * | 1996-03-19 | 1997-10-03 | Fujitsu Ltd | 半導体装置 |

| WO2003005368A1 (en) * | 2001-07-04 | 2003-01-16 | Hitachi, Ltd. | Semiconductor device and memory module |

| JP2004005821A (ja) * | 2002-05-31 | 2004-01-08 | Toshiba Corp | 同期型半導体記憶装置 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6310821B1 (en) * | 1998-07-10 | 2001-10-30 | Kabushiki Kaisha Toshiba | Clock-synchronous semiconductor memory device and access method thereof |

| US5537564A (en) * | 1993-03-08 | 1996-07-16 | Zilog, Inc. | Technique for accessing and refreshing memory locations within electronic storage devices which need to be refreshed with minimum power consumption |

| KR950014089B1 (ko) | 1993-11-08 | 1995-11-21 | 현대전자산업주식회사 | 동기식 디램의 히든 셀프 리프레쉬 방법 및 장치 |

| JP3625955B2 (ja) * | 1996-04-16 | 2005-03-02 | 沖電気工業株式会社 | 画像用半導体メモリ回路 |

| TW430793B (en) * | 1999-05-20 | 2001-04-21 | Ind Tech Res Inst | Self-row identification hidden-type refresh-circuit and refresh method |

| JP2001035149A (ja) * | 1999-06-30 | 2001-02-09 | Ind Technol Res Inst | 行セルフ識別隠れ式リフレッシュ回路及び方法 |

| KR100311044B1 (ko) * | 1999-10-05 | 2001-10-18 | 윤종용 | 클럭 주파수에 따라 레이턴시 조절이 가능한 레이턴시 결정 회로 및 레이턴시 결정 방법 |

| JP2002324393A (ja) * | 2001-04-25 | 2002-11-08 | Mitsubishi Electric Corp | 半導体記憶装置 |

| KR100390906B1 (ko) * | 2001-05-25 | 2003-07-12 | 주식회사 하이닉스반도체 | 가상형 스태틱 랜덤 억세스 메모리장치 및 그의 구동방법 |

| JP4743999B2 (ja) | 2001-05-28 | 2011-08-10 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| JP4262912B2 (ja) * | 2001-10-16 | 2009-05-13 | Necエレクトロニクス株式会社 | 半導体記憶装置 |

| JP4022392B2 (ja) * | 2001-12-11 | 2007-12-19 | Necエレクトロニクス株式会社 | 半導体記憶装置およびそのテスト方法並びにテスト回路 |

| JP2003289103A (ja) * | 2002-03-28 | 2003-10-10 | Mitsubishi Electric Corp | 半導体装置と半導体実装装置 |

| JP2003297080A (ja) * | 2002-03-29 | 2003-10-17 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2004102508A (ja) * | 2002-09-06 | 2004-04-02 | Renesas Technology Corp | 半導体記憶装置 |

| JP4184104B2 (ja) * | 2003-01-30 | 2008-11-19 | 株式会社ルネサステクノロジ | 半導体装置 |

| JP2004259318A (ja) * | 2003-02-24 | 2004-09-16 | Renesas Technology Corp | 同期型半導体記憶装置 |

| JP4191018B2 (ja) * | 2003-11-26 | 2008-12-03 | エルピーダメモリ株式会社 | 半導体記憶装置のリフレッシュ制御方式 |

| JP5038742B2 (ja) * | 2007-03-01 | 2012-10-03 | ルネサスエレクトロニクス株式会社 | セルフリフレッシュ制御回路、半導体装置 |

-

2004

- 2004-02-03 JP JP2004026999A patent/JP2005222581A/ja active Pending

-

2005

- 2005-01-31 TW TW103122670A patent/TWI517151B/zh not_active IP Right Cessation

- 2005-01-31 TW TW094102871A patent/TWI383394B/zh not_active IP Right Cessation

- 2005-01-31 TW TW100114414A patent/TWI460725B/zh not_active IP Right Cessation

- 2005-02-02 KR KR1020050009640A patent/KR101120838B1/ko not_active IP Right Cessation

- 2005-02-03 US US11/049,059 patent/US7336557B2/en not_active Expired - Fee Related

-

2008

- 2008-01-04 US US12/007,032 patent/US7480200B2/en not_active Expired - Fee Related

- 2008-12-12 US US12/333,913 patent/US7983103B2/en not_active Expired - Fee Related

-

2011

- 2011-04-07 US US13/081,821 patent/US20110199844A1/en not_active Abandoned

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09259080A (ja) * | 1996-03-19 | 1997-10-03 | Fujitsu Ltd | 半導体装置 |

| WO2003005368A1 (en) * | 2001-07-04 | 2003-01-16 | Hitachi, Ltd. | Semiconductor device and memory module |

| JP2004005821A (ja) * | 2002-05-31 | 2004-01-08 | Toshiba Corp | 同期型半導体記憶装置 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010033695A (ja) * | 2008-07-29 | 2010-02-12 | Internatl Business Mach Corp <Ibm> | 組み込みdram用リフレッシュ・コントローラ及びリフレッシュ制御方法 |

| JP2012221540A (ja) * | 2011-04-13 | 2012-11-12 | Elpida Memory Inc | 半導体装置及びシステム |

| US8958259B2 (en) | 2011-04-13 | 2015-02-17 | Ps4 Luxco S.A.R.L. | Device performing refresh operations of memory areas |

Also Published As

| Publication number | Publication date |

|---|---|

| US7983103B2 (en) | 2011-07-19 |

| US7480200B2 (en) | 2009-01-20 |

| US20080123456A1 (en) | 2008-05-29 |

| TW200603159A (en) | 2006-01-16 |

| US7336557B2 (en) | 2008-02-26 |

| KR20060041602A (ko) | 2006-05-12 |

| US20110199844A1 (en) | 2011-08-18 |

| TWI460725B (zh) | 2014-11-11 |

| TW201203245A (en) | 2012-01-16 |

| KR101120838B1 (ko) | 2012-06-27 |

| TW201440044A (zh) | 2014-10-16 |

| TWI517151B (zh) | 2016-01-11 |

| US20090091997A1 (en) | 2009-04-09 |

| TWI383394B (zh) | 2013-01-21 |

| US20050169091A1 (en) | 2005-08-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101120838B1 (ko) | 휴대 단말기에 탑재하기 적합한 반도체 기억 장치 | |

| US6330636B1 (en) | Double data rate synchronous dynamic random access memory device incorporating a static RAM cache per memory bank | |

| US6188641B1 (en) | Synchronous semiconductor memory device having input circuit with reduced power consumption | |

| JP4249412B2 (ja) | 半導体記憶装置 | |

| JP4014669B2 (ja) | 同期型半導体記憶装置 | |

| JP2004145955A (ja) | 半導体記憶装置及びその制御方法 | |

| JP2003059264A (ja) | 半導体記憶装置 | |

| US7227812B2 (en) | Write address synchronization useful for a DDR prefetch SDRAM | |

| JP4236903B2 (ja) | 半導体記憶装置及びその制御方法 | |

| JP3341710B2 (ja) | 半導体記憶装置 | |

| JP3951202B2 (ja) | 同期式半導体メモリ装置 | |

| JP2002074952A (ja) | 同期型半導体記憶装置及びその入力回路の制御方法 | |

| JP3689229B2 (ja) | 半導体メモリ装置のカラム選択ラインイネーブル回路 | |

| KR20030009057A (ko) | 클럭 신호에 동기하여 동작하는 반도체 기억 장치 | |

| KR20080114406A (ko) | 컬럼 어드레스 제어 회로 | |

| JP5048102B2 (ja) | 半導体記憶装置 | |

| JP5058295B2 (ja) | 半導体記憶装置 | |

| JP5328957B2 (ja) | 半導体記憶装置 | |

| US7154795B2 (en) | Clock signal initiated precharge technique for active memory subarrays in dynamic random access memory (DRAM) devices and other integrated circuit devices incorporating embedded DRAM | |

| KR100481819B1 (ko) | 디램 셀을 사용하며, 칩 디스에이블 구간 중에 발생하는신호에 의하여 리프레쉬가 수행되도록 제어되는 동기식에스램 호한 메모리 | |

| JP2002197864A (ja) | マルチポートメモリおよびその制御方法 | |

| JP2003233986A (ja) | 半導体記憶装置 | |

| KR100401235B1 (ko) | 디램 셀을 이용한 에스램 호환 메모리 장치의 로우 제어회로 | |

| JPH04229482A (ja) | Dramメモリ・システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070119 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070119 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100305 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100316 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100426 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100713 |