-

Die vorliegende Erfindung betrifft

ein Verfahren zum Betreiben einer Halbleiterspeichervorrichtung,

die eine Vielzahl von Operationsmodi hat, und eine Halbleiterspeichervorrichtung,

die eine Vielzahl von Operationsmodi hat.

-

Halbleiterspeichervorrichtungen wie

etwa DRAMs können

zwei verschiedene Adressensignale von demselben Adressenanschluß jeweilig

zu verschiedenen Zeiten empfangen, um die Anzahl von Anschlüssen zu

reduzieren. Solch eine Halbleiterspeichervorrichtunq, die multiplexierte

Adressensignale empfängt,

kann trotz ihrer großen

Speicherkapazität

in einer kleinen Packung geformt sein.

-

Ein synchroner DRAM (SDRAM)

ist eine andere Halbleiterspeichervorrichtung, die multiplexierte Adressensignale

empfangen kann. Der SDRAM ist eine Speichervorrichtung,

die Eingangs-/Ausgangsschnittstellenschaltungen mit hoher Geschwindigkeit

synchron mit einem Taktsignal betreibt und Daten mit hoher Geschwindigkeit

schreibt und liest.

-

Der SDRAM ist zum Ausführen von

Lese- und Schreiboperationen mit hoher Geschwindigkeit in einer Vielzahl

von Speicherzellen in der Lage, die mit derselben Wortleitung verbunden

sind. In Speicherzellen, die mit verschiedenen Wortleitungen verbunden

sind, müssen

die Wortleitungen jedoch zu einer Zeitlage ähnlich wie bei den zuvor betrachteten DRAMs selektiert

werden. Deshalb ist eine Zugriffszeit bei einem wahlfreien Zugriff

mit jener bei den DRAMs äquivalent.

-

Ein Operationsmodus von SDRAMs wird

beim Eingeben eines Befehls einmal bestimmt; dann führen die SDRAMs den

bestimmten Operationsmodus aus. Auf Grund dessen ist eine Anzahl

von Anschlüssen

zum Empfangen von multiplen Befehlssignalen erforderlich, wie etwa

von einem Chipselektionssignal (/CS), einem Reihenadressen-Strobe-Signal

(/RAS), einem Spaltenadressen-Strobe-Signal (/CAS),

einem Schreibfreigabesignal (/WE) und einem Taktfreigabesignal

(CKE). Da die Sequenz zum Eingeben von Befehlen nicht vorbestimmt

ist, kann zusätzlich

eine Zeitlage zum Ausführen

einer Vorladeoperation einer Bitleitung nicht innerhalb eines Chips

erzeugt werden. Daher muß ein

Vorladen einer Bitleitung ausgeführt

werden, indem ein chipexterner Befehl zugeführt wird.

-

In den letzten Jahren ist ein RAM mit

schnellem Zyklus [fast cycle RAM (FCRAM)] als DRAM entwickelt

worden, dessen Operationszyklus signifikant verkürzt wurde, um Datenlese-/ -schreiboperationen

mit hoher Geschwindigkeit während

des wahlfreien Zugriffs auszuführen.

-

Der FCRAM ist so konstruiert,

daß seine

interne Operation in drei Stufen unterteilt ist. Eine Operation in

jeder Stufe wird automatisch vollendet. Dadurch wird es möglich, eine

Pipeline-Verarbeitung nicht nur für Dateneingabe-/ -ausgabeeinheiten

auszuführen,

sondern auch für

eine Adresse, die eine Operation akzeptiert, und eine Operation

einer Speicherkerneinheit. Der Einsatz von solch einer Pipeline-Verarbeitung

ermöglicht es,

den Operationszyklus zu verkürzen.

Da der FCRAM zusätzlich

so konstruiert ist, um vorrangig das Verkürzen einer Zugriffszeit zu

erreichen, sind Adressenanschlüsse

nicht multiplexiert, und alle Adressensignale werden zu derselben

Zeit der Eingabe eines Befehls zugeführt. Beim Eingeben eines einzelnen

Befehls wird ein Operationsmodus bestimmt, und dann wird der vorbestimmte

Operationsmodus ausgeführt.

-

Die oben beschriebenen SDRAMs haben

den Nachteil, daß sie

eine große

Anzahl von Befehlseingabeanschlüssen

erfordern. Eine Erhöhung

der Anzahl von Befehlseingabeanschlüssen kompliziert eine Konfiguration

der Schaltung, die eine Befehlseingabe steuert, auf gedruckten Verdrahtungsplatten.

-

Die obenerwähnten FCRAMs haben den Nachteil,

daß sie

im Vergleich zu DRAMs und SDRAMs, die gleiche

Speicherkapazitä ten

aufweisen, auf Grund der nichtmultiplexierten Adressierung mehr

Anschlüsse

erfordern. Eine Erhöhung

der Anschlußanzahl

führt zur

Zunahme von zugeordneten Komponenten, wie etwa von Adressenkontaktstellen

und Adresseneingangsschaltungen und anderen, wodurch das Problem

verursacht wird, daß der

Chip größer wird.

Ein anderer Nachteil ist der, daß solch eine Erhöhung der

Anschlußanzahl

bewirken kann, daß die

Packungsgröße ebenfalls

zunimmt. Im besonderen sind im Falle der CSP (chip size

package: Packung in Chipgröße), die

zu einer Hauptströmung

in der Technik geworden ist, Kugeln, die mit einer gedruckten Verdrahtungsplatte

verbunden sind, in Form einer zweidimensionalen Anordnung an ihr

vorgesehen. Dies kann zu einer Zunahme der Packungsgröße in Abhängigkeit

von der Anzahl von Anschlüssen

führen.

-

Deshalb ist es wünschenswert, die Anzahl von

Anschlüssen

zu reduzieren, die zur Eingabe von Befehlen und Adressen benötigt werden.

-

Es ist auch wünschenswert, eine Zunahme der

Größe des Chips

und der Packungsgröße desselben durch

Reduzieren der Anzahl von Anschlüssen

zu verhindern.

-

Weiterhin ist es wünschenswert,

einen Operationszyklus mit hoher Geschwindigkeit beizubehalten, auch

wenn die Anzahl von Anschlüssen

verringert wird.

-

Ferner ist es wünschenswert, ein Signal mit

hoher Geschwindigkeit zu akzeptieren, um einen Operationszyklus

mit hoher Geschwindigkeit beizubehalten.

-

Es kann davon ausgegangen werden,

daß US-5,749,086

ein Verfahren zum Betreiben einer Halbleiterspeichervorrichtung

mit einer Vielzahl von Operationsmodi zum Steuern einer internen

Schaltung umfaßt, welches

Verfahren das sukzessive Holen einer Serie von Befehlen enthält, die

dazu dienen, einen der Operationsmodi zu selektieren, wobei die

Selektion durch jeden sukzessiven Befehl der genannten Serie be schränkt wird,

und die folgenden Schritte umfaßt:

Initiieren einer ersten Operation als Antwort auf einen ersten Befehl in

der Serie von Befehlen; und Fortsetzen der ersten Operation, wenn

ein zweiter Befehl, der dem ersten Befehl in der Serie von Befehlen

folgt, die erste Operation verlangt.

-

Ein Verfahren zum Betreiben einer

Halbleiterspeichervorrichtung gemäß einem ersten Aspekt der vorliegenden

Erfindung ist gekennzeichnet durch das Beenden der ersten Operation

als Antwort auf den zweiten Befehl, wenn der zweite Befehl nicht

wenigstens die Fortsetzung der ersten Operation verlangt, und ferner

dadurch gekennzeichnet, daß der

zweite Befehl, der die genannte Fortsetzung nicht verlangt, eine

zweite Operation verlangt und die zweite Operation durch den zweiten

Befehl initiiert wird.

-

Da die Informationen, die zur Bestimmung

eines Operationsmodus erforderlich sind, zu einer Vielzahl von Zeiten

akzeptiert werden, kann die Anzahl von Anschlüssen, die zum Eingeben von

Befehlen benötigt

werden, reduziert werden. Im besonderen sind im Falle der Eingabe

von Befehlen an einem dedizierten Anschluß dessen Eingangskontaktstellen,

Eingangsschaltungen oder dergleichen nicht mehr erforderlich, so

daß die Chipgröße verkleinert

werden kann. Bei einem Beispiel können jeweilig vier oder acht

Operationsmodi identifiziert werden, wenn Befehle an zwei Anschlüssen zu

zwei oder drei Zeiten akzeptiert werden. Die Verkleinerung wird

durch das Reduzieren der Anzahl von Anschlüssen erreicht, wodurch der

Packungsgröße Grenzen gesetzt

werden.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, werden

Befehle vorzugsweise zu zwei Zeiten akzeptiert. In diesem Fall wird

die Anzahl von Operationsmodi durch den ersten Befehl eingeschränkt. Dabei

wird ein Teil der Schaltung betrieben, der zum Ausführen eines

vorbestimmten Opera tionsmodus von den eingeschränkten Operationsmodi erforderlich

ist. Dann wird ein Operationsmodus durch den zweiten Befehl bestimmt;

wenn der Operationsmodus ein vorbestimmter Operationsmodus ist,

wird der Rest der Schaltung betrieben. Das Ausführen eines Teils des vorbestimmten Operationsmodus

im voraus ermöglicht

es, die Zugriffszeit auch in dem Fall zu verkürzen, wenn Befehle zu zwei

Zeiten akzeptiert werden.

-

Bei einem Verfahren zum Steuern einer

Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, ist

vorzugsweise ein Modusregistereinstellmodus vorgesehen, der nicht

mit einer internen Operation einhergeht, so daß die Operation innerhalb einer

vorbestimmten Periode vollendet werden kann, auch wenn eine Operation

nach dem Empfang des zweiten Befehls initiiert wird. Ähnlich ist

vorzugsweise ein Datenhaltemodus vorgesehen, der das Eingeben/Ausgeben

von Daten von/nach außen

nicht erfordert, so daß die

Operation innerhalb einer vorbestimmten Periode vollendet werden

kann, auch wenn die Operation nach dem Empfang des zweiten Befehls

initiiert wird.

-

Bei einem Verfahren zum Steuern einer

Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, ist

es vorzugsweise unnötig,

Informationen zum Einstellen des Modusregisters zusammen mit dem ersten

Befehl von einem Adressenanschluß zu akzeptieren. Deshalb ist

es in diesem Fall unnötig,

die Informationen zu halten, bis der zweite Befehl zugeführt wird;

als Resultat ist es möglich,

die Komplikation einer Steuerschaltung zu verhindern.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

die Steuerung, die zum Umstellen auf den Datenhaltemodus erforderlich

ist, vorzugsweise dann ausgeführt,

wenn ein durch den zweiten Befehl bestimmter Operationsmodus ein

Datenhaltemodus ist. Danach wird vorzugsweise die Steuerung zum

Umstellen auf einen Bereitschaftsmodus ausgeführt, wenn ein Signal, das einem

vorbestimmten Anschluß zugeführt wird,

während

des Datenhaltemodus auf einen vorbestimmten Pegel gesetzt wird.

Durch das Überwachen

eines Signals an einem vorbestimmten Anschluß, das nicht durch einen Befehl

erfolgt, ist es möglich,

während

eines vorbestimmten Operationsmodus auf einen anderen Operationsmodus

zu schalten.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

die Steuerung, die zum Umstellen auf einen Selbstauffrischmodus

erforderlich ist, vorzugsweise dann ausgeführt, wenn ein Signal, das einem

vorbestimmten Anschluß zugeführt wird,

während

eines automatischen Auffrischmodus auf einen vorbestimmten Pegel

gesetzt wird. Der Unterschied zwischen dem automatischen Auffrischmodus

und dem Selbstauffrischmodus ist der, daß ersterem eine Auffrischzeitlage

von außen

zugeteilt wird, während

letzterer solch eine Zeitlage selbst erzeugt. Eine identische Schaltung

kann zum Ausführen

sowohl einer Auffrischzähleroperation

als auch einer Auffrischoperation verwendet werden. Deshalb wird

der automatische Auffrischmodus kontinuierlich und reibungslos auf

den Selbstauffrischmodus umgestellt, wodurch die für das Umstellen

erforderliche Zeit verkürzt

wird.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

die Akzeptanz des ersten Befehls vorzugsweise durch ein Signal verhindert,

das einem vorbestimmten Anschluß zugeführt wird,

und die Vorrichtung wird in einen Bereitschaftszustand versetzt.

Wenn ein Signal, das einem anderen vorbestimmten Anschluß zugeführt wird,

in dem Bereitschaftszustand einen vorbestimmten Pegel erreicht,

wird vorzugsweise die Steuerung zur Umstellung auf den Bereitschaftsmodus ausgeführt. Durch

das Überwachen

eines Signals an einem vorbestimmten Anschluß während der Verhinderung der

Eingabe des ersten Befehls ist ein Umstellen auf einen anderen Operationsmodus

möglich,

wobei dies nicht durch einen Befehl erfolgt.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

dann, wenn ein Signal, das einem vorbestimmten Anschluß zugeführt wird,

einen vorbestimmten Pegel erreicht, während die Vorrichtung in dem

Bereitschaftszustand ist, vorzugsweise die Steuerung zum Umstellen

auf einen Modus mit niedrigem Energieverbrauch ausgeführt. In

diesem Modus mit niedrigem Energieverbrauch ist die Vorrichtung

in einem statischen Zustand und steht nicht direkt mit einer Zugriffsoperation in

Verbindung. Die Steuerung zur Umstellung auf den Modus mit niedrigem

Energieverbrauch wird vorzugsweise ausgeführt, indem ein vorbestimmtes

Signal einem Anschluß zugeführt wird,

woraus sich die verbesserte Nutzbarkeit ergibt.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, werden

die ersten und zweiten Befehle vorzugsweise synchron mit einem Taktsignal

akzeptiert. Der zweite Befehl wird vorzugsweise einen halben oder

einen Takt nach der Akzeptanz des ersten Befehls akzeptiert. Daher

sind die Informationen des zweiten Befehls in kurzer Zeit nach der

Akzeptanz des ersten Befehls erhältlich.

Als Resultat kann eine etwaige Verzögerung beim Steuern des zweiten

Befehls minimiert werden, wenn Befehle zu zwei Zeiten akzeptiert

werden.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, werden

ein Schreiboperationsmodus und ein Leseoperationsmodus vorzugsweise

durch den ersten Befehl unterschieden. Mit anderen Worten, die durch

den ersten Befehl einge schränkten

Operationsmodi enthalten nicht sowohl den Schreib- als auch den

Leseoperationsmodus. Nach der Akzeptanz des ersten Befehls initiiert

die Schaltung, die sowohl dem Schreib- als auch dem Leseoperationsmodus

gemeinsam ist, die Operation. Das Starten der Operation von solch

einer Schaltung, die für

die Schreib- und Leseoperationsmodi erforderlich ist, im voraus

macht es möglich,

die Zugriffszeit zu verkürzen.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

ein Signal, das einem Adressenanschluß durch den ersten Befehl zugeführt wird,

vorzugsweise als Teil einer Adresse akzeptiert, die für eine Schreib-

oder Leseoperation erforderlich ist. Wenn ein durch den zweiten

Befehl bestimmter Operationsmodus entweder der Schreib- oder der

Leseoperationsmodus ist, wird ein Signal, das dem Adressenanschluß zugeführt wird,

vorzugsweise als Rest der Adresse akzeptiert, die für die Schreib-

oder die Leseoperation benötigt

wird. Das Akzeptieren der Adresse, die für die Schreib- oder die Leseoperation

erforderlich ist, zu zwei Zeiten führt zu einem signifikanten

Reduzieren der Anzahl von Adressenanschlüssen. Demzufolge wird die Anzahl

von Adressenkontaktstellen, Adresseneingangsschaltungen oder dergleichen

verringert und kann die Chipgröße verkleinert

werden. Die Verkleinerung wird erreicht, indem die Anzahl von Anschlüssen reduziert

wird, wodurch der Packungsgröße Grenzen

gesetzt werden.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

eine Wortleitung vorzugsweise vor dem Empfang des zweiten Befehls

selektiert, um die Zugriffszeit zu verkürzen.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

dann, wenn ein durch den zweiten Befehl bestimmter Operationsmodus

ein automatischer Auffrischmodus ist, eine Wortleitung, die der

zusammen mit dem ersten Befehl akzeptierten Adresse entspricht,

vorzugsweise nicht selektiert. Dann wird vorzugsweise eine Wortleitung

selektiert, die einer intern erzeugten Auffrischadresse entspricht.

Speicherzellen werden durch das Umschalten der Selektion einer Wortleitung

zuverlässig

aufgefrischt.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

vorzugsweise wenigstens eine Subwortleitung gemäß einer Adresse, die zusammen

mit dem ersten Befehl akzeptiert wurde, spezifiziert und selektiert.

Nach der Akzeptanz des ersten Befehls ist es möglich, die Schaltung, die zum

Betreiben von vorbestimmten Speicherzellen erforderlich ist, vor

dem Empfang des zweiten Befehls zu steuern. Daher kann die Zugriffszeit

verkürzt

werden.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

die Aktivierung eines Spaltendecodierers vorzugsweise durch den

ersten Befehl zuerst initiiert. Wenn der durch den zweiten Befehl

bestimmte Operationsmodus entweder ein Schreiboperationsmodus oder ein

Leseoperationsmodus ist, wird vorzugsweise eine akzeptierte Adresse

verwendet, um eine Spaltenselektionsleitung zu selektieren. Die

Zugriffszeit kann verkürzt

werden, da der Spaltendecodierer im voraus vor dem Bestimmen der

Adresse zum Selektieren der Spaltenselektionsleitung aktiviert wird.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

ein Signal, das einem vorbestimmten Anschluß zugeführt wird, vorzugsweise als

Informationen zum Spezifizieren der Länge von Schreibdaten akzeptiert,

wenn der durch den zweiten Befehl bestimmte Operationsmodus der

Schreiboperationsmodus ist. Vorzugsweise wird die Länge von

Schreibdaten auf der Basis der akzeptierten Informationen direkt

gesteuert. Falls eine Vielzahl von Daten in Folge von einem Eingangs-/Ausgangsanschluß (von Eingangs-/Ausgangsanschlüssen) während der

Schreiboperation akzeptiert wird, ist es daher möglich, die Länge von

akzeptierten Daten bei den einfachen Steuerprozeduren zu verändern. In

bezug auf Daten, die nicht geschrieben zu werden brauchen (das heißt, ein

Abschnitt, der länger

als die spezifizierte Datenlänge

ist), ist zusätzlich

keine Schreibsteuerung erforderlich. Dadurch wird Zeit eingespart,

die zum Steuern der Schreiboperation benötigt wird. Daher ist es möglich, eine

Eingabezeitlage des ersten Befehls im nächsten Zyklus früher anzuordnen.

Die Länge

von Schreibdaten kann nur durch die Steuerung der Eingangs-/Ausgangsschaltungen

verändert

werden, so daß die

Steuerung durch das Akzeptieren von Informationen zusammen mit dem

zweiten Befehl zuverlässig

ausgeführt

werden kann.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

ein Signal, das einem vorbestimmten Anschluß zugeführt wird, vorzugsweise als

Maskierungsinformationen akzeptiert, die einen Teil von Schreibdaten

ungültig

machen, die in Folge zugeführt

werden, wenn der durch den zweiten Befehl bestimmte Operationsmodus

der Schreiboperationsmodus ist. Ein Teil der Schreibdaten wird vorzugsweise

auf der Basis der akzeptierten Maskierungsinformationen maskiert.

Um die Maskierungsinformationen durch einen dedizierten Anschluß zu steuern,

müssen

die Informationen von dem dedizierten Anschluß immer dann akzeptiert werden,

wenn die Schreiboperation ausgeführt

wird, und dadurch wird die Steuerprozedur kompliziert. Das Akzeptieren

der Maskierungsinformationen zusammen mit dem zweiten Befehl ermöglicht ein

einfaches Steuern der Maskierung von Schreibdaten.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

ein Signal, das einem vorbestimmten Anschluß zugeführt wird, vorzugsweise als

Informationen zum Spezifizieren der Länge von Lesedaten akzeptiert,

wenn der durch den zweiten Befehl bestimmte Operationsmodus der

Leseoperationsmodus ist. Vorzugsweise wird die Länge von Lesedaten auf der Basis der

akzeptierten Informationen direkt gesteuert. Falls eine Vielzahl

von Daten von einem Eingangs-/Ausgangsanschluß (von Eingangs- und Ausgangsanschlüssen) während der

Leseoperation in Folge akzeptiert wird, ist es daher möglich, die

Länge von

akzeptierten Daten bei der einfachen Steuerprozedur zu verändern. In

bezug auf Daten, die zum Lesen nicht benötigt werden (das heißt, ein

Abschnitt, der länger

als die Länge

von spezifizierten Daten ist), ist zusätzlich keine Ausgangssteuerung

erforderlich. Dadurch wird Zeit eingespart, die zum Steuern der

Leseoperation benötigt

wird. Daher ist es möglich,

eine Eingabezeitlage des ersten Befehls in dem nächsten Zyklus früher anzuordnen.

Die Länge

von Lesedaten kann nur durch die Steuerung der Eingangs-/Ausgangsschaltungen

verändert

werden, so daß die

Steuerung zuverlässig

ausgeführt

wird, indem Informationen zusammen mit dem zweiten Befehl akzeptiert

werden.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

ein Signal, das einem vorbestimmten Anschluß zugeführt wird, vorzugsweise als

Maskierungsinformationen akzeptiert, die einen Teil von Lesedaten,

die in Folge zugeführt

werden, ungültig

machen, wenn der durch den zweiten Befehl bestimmte Operationsmodus

der Leseoperationsmodus ist. Vorzugsweise wird ein Teil der Lesedaten

auf der Basis der akzeptierten Maskierungsinformationen maskiert.

Um die Maskierungsinformationen durch einen dedizierten Anschluß zu steuern,

müssen

die Informationen immer dann, wenn die Schreiboperation ausgeführt wird,

von dem dedizierten Anschluß akzeptiert

werden, und dadurch wird die Steuerprozedur kompliziert. Das Akzeptieren

der Maskierungsinformationen zusammen mit dem zweiten Befehl macht

es möglich,

die Maskierung von Schreibdaten leicht zu steuern.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, werden

in dem Fall, wenn die Operationsmodi, die dem ersten Befehl entsprechen,

den Schreiboperationsmodus enthalten, vorzugsweise die Schreibdaten

und die Adressen verwendet, die in dem vorhergehenden Schreiboperationsmodus

akzeptiert wurden, um die Schreiboperation auszuführen. Dadurch

wird es möglich,

den Schreibzyklus früh

zu vollenden. Falls eine Leseoperation nach einer Schreiboperation

ausgeführt

wird, ist es möglich,

die Leseoperation früh

zu initiieren.

-

Bei einem Verfahren zum Betreiben

einer Halbleiterspeichervorrichtung, das die vorliegende Erfindung verkörpert, wird

in dem Fall, wenn die Operationsmodi, die eingeschränkt werden,

bei der Eingabe des ersten Befehls einen Schreiboperationsmodus

enthalten, vorzugsweise ein Teil der Schaltung betrieben, der zum Ausführen einer

Schreiboperation erforderlich ist. Wenn der durch die Eingabe des

zweiten Befehls bestimmte Operationsmodus ein automatischer Auffrischmodus

ist, wird vorzugsweise eine Auffrischoperation nach Ausführung der

Schreiboperation ausgeführt.

Daher ist es möglich,

die Schreiboperation effektiv auszuführen, indem die Schaltung genutzt

wird, die ihre Operation durch die Eingabe des ersten Befehls initiiert

hat.

-

Gemäß einem anderen Aspekt der

vorliegenden Erfindung ist eine Halbleiterspeichervorrichtung vorgesehen,

mit einer Vielzahl von Operationsmodi zum Steuern einer internen

Schaltung, welche Vorrichtung eine Steuerschaltung zum sukzessiven

Holen einer Serie von Befehlen umfaßt, die dazu dienen, einen

der Operationsmodi zu bestimmen, wobei die Selektion durch jeden

sukzessiven Befehl von der Serie beschränkt wird und die Steuerschaltung

betriebsfähig

ist, um: eine erste Operation als Antwort auf einen ersten Befehl

in der Serie von Befehlen zu initiieren; und die erste Operation

fortzusetzen, wenn ein zweiter Befehl, der dem ersten Befehl in

der Serie von Befehlen folgt, die erste Operation verlangte gekennzeichnet

durch das Beenden der ersten Operation als Antwort auf den zweiten

Befehl, wenn der zweite Befehl nicht wenigstens die Fortsetzung

der ersten Operation verlangte und ferner dadurch gekennzeichnet,

daß der

zweite Befehl, der die genannte Fortsetzung nicht verlangt, eine

zweite Operation verlangt und die zweite Operation durch den zweiten Befehl

initiiert wird.

-

Da die Informationen, die zum Bestimmen

des Operationsmodus erforderlich sind, zu einer Vielzahl von Zeiten

akzeptiert werden, kann die Anzahl von Anschlüssen reduziert werden, die

zur Eingabe von Befehlen benötigt

werden. Im besonderen sind in dem Fall, wenn Befehle an einem dedizierten

Anschluß eingegeben

werden, dessen Eingangskontaktstellen, Eingangsschaltungen oder

dergleichen nicht mehr erforderlich, so daß die Chipgröße verkleinert

werden kann. Die Verkleinerung wird durch das Reduzieren der Anzahl

von Anschlüssen

erreicht, wodurch der Packungsgröße Grenzen

gesetzt werden. Bei einem Beispiel können jeweilig vier oder acht

Operationsmodi identifiziert werden, wenn Befehle an zwei Anschlüssen zu

zwei oder drei Zeiten akzeptiert werden.

-

In einer Halbleiterspeichervorrichtung,

die die vorliegende Erfindung verkörpert, akzeptiert die Befehlssteuerschaltung

vorzugsweise Befehle zu zwei Zeiten, schränkt eine Vielzahl von Operationsmodi

durch den ersten Befehl ein und betreibt einen Teil der Schaltung,

der zum Ausführen

eines vorbestimmten Operationsmodus von den eingeschränkten Operationsmodi

erforderlich ist. Die Befehlssteuerschaltung bestimmt einen Operationsmodus

vorzugsweise durch den zweiten Befehl. Wenn der Operationsmodus

ein vorbestimmter Operationsmodus ist, wird vorzugsweise der Rest

der Schaltung betrieben.

-

Die Anzahl von Anschlüssen, die

zum Akzeptieren von Befehlen benötigt

werden, kann reduziert werden, da die Informationen, die zum Bestimmen

eines Operationsmodus erforderlich sind, zu einer Vielzahl von Zeiten

akzeptiert werden. Falls Befehle an einem dedizierten Anschluß eingegeben

werden, sind im besonderen dessen Eingangskontaktstellen, Eingangsschaltungen

oder dergleichen nicht mehr erforderlich, so daß die Chipgröße verkleinert

werden kann. Die Verkleinerung wird durch das Reduzieren der Anzahl

von Anschlüssen erreicht,

wodurch der Packungsgröße Grenzen

gesetzt werden. Das Ausführen

eines Teils des vorbestimmten Operationsmodus im voraus macht es

möglich,

die Zugriffszeit zu verkürzen,

auch wenn Befehle zu zwei Zeiten akzeptiert werden.

-

In einer Halbleiterspeichervorrichtung,

die die vorliegende Erfindung verkörpert, umfaßt die Befehlssteuerschaltung

vorzugsweise eine Vielzahl von Akzeptanzschaltungen. Jede der Akzeptanzschaltungen

akzeptiert jeweilig Signale, die jeweils zu einer Vielzahl von Zeiten

zugeführt

werden. Mit anderen Worten, gemäß der Zeitlage

der Signalzuführung

wird jeweilig eine verschiedene Akzeptanzschaltung betrieben und

die interne Schaltung gesteuert. Daher kann eine Be fehlssteuerschaltung

ohne weiteres auch in der Halbleiterspeichervorrichtung konstruiert

werden, die eine komplizierte Befehlskombination hat. Demzufolge

kann die Verifizierung der Konstruktion erleichtert werden.

-

In einer Halbleiterspeichervorrichtung,

die die vorliegende Erfindung verkörpert, akzeptiert jede der Akzeptanzschaltungen

vorzugsweise Signale synchron mit den verschiedenen Flanken eines

Taktsignals. Auf Grund des direkten Akzeptierens der Signale durch

dasselbe Taktsignal wird die Geschwindigkeit der Akzeptanzprozedur

erhöht.

Dadurch wird es möglich,

eine Operation der internen Schaltung früh zu initiieren und die Zugriffszeit

zu verkürzen.

-

In einer Halbleiterspeichervorrichtung,

die die vorliegende Erfindung verkörpert, ist vorzugsweise ein Zeitlagengenerator

vorgesehen, der eine Vielzahl von Akzeptanzsignalen auf der Basis

eines Taktsignals erzeugt. Jede der Akzeptanzschaltungen akzeptiert

jeweilig Signale synchron mit den Akzeptanzsignalen. Es ist nicht

mehr erforderlich, das Taktsignal mit der Vielzahl von Akzeptanzschaltungen

zu verdrahten, da die Signale unter Verwendung der Akzeptanzsignale

akzeptiert werden, die aus dem Taktsignal erzeugt werden. Selbst

wenn Signale, die zugeführt

werden, und die Akzeptanzschaltungen eine beachtliche Anzahl haben, können die

Signale als Resultat akzeptiert werden, ohne die Belastung des Taktsignals

zu erhöhen.

-

Als Beispiel wird nun Bezug auf die

beiliegenden Zeichnungen genommen, in denen:

-

1 ein

Flußdiagramm

ist, welches das Grundprinzip der ersten Ausführungsform bei dem Verfahren zum

Betreiben der Halbleiterspeichervorrichtung gemäß der vorliegenden Erfindung

zeigt;

-

2 ein

Blockdiagramm ist, das die Grundprinzipien der ersten Ausführungsform

der Halbleiterspeichervorrichtung gemäß der vorliegenden Erfindung

zeigt;

-

3 ein

Zustandsübergangsdiagramm

ist, das eine Ausführungsform

des Verfahrens zum Betreiben der Halbleiterspeichervorrichtung und

die Halbleiterspeichervorrichtung gemäß der vorliegenden Erfindung zeigt;

-

4 ein

Diagramm der gesamten Konfiguration eines Chips in der ersten Ausführungsform

des Verfahrens zum Betreiben der Halbleiterspeichervorrichtung und

der Halbleiterspeichervorrichtung gemäß der vorliegenden Erfindung

ist;

-

5 ein

Blockdiagramm ist, das die Details einer Decodiereinheit von 4 zeigt;

-

6 ein

schematisches Diagramm ist, das die Details eines Modusregisters

von 5 zeigt

-

7 ein

Blockdiagramm ist, das die Details einer Speicheroperationseinheit

von 4 zeigt;

-

8 ein

Schaltungsdiagramm ist, das die Details eines Spaltendecodierers

von 7 zeigt;

-

9 ein

Blockdiagramm ist, das die Details einer Speicherkerneinheit von 7 zeigt;

-

10 ein

Blockdiagramm ist, das die Details einer Eingabe-/Ausgabeeinheit

von 4 zeigt;

-

11 ein

Zeitlagendiagramm ist, welches das Verfahren zum Betreiben der Halbleiterspeichervorrichtung

und eine Leseoperation in der ersten Ausführungsform der Halbleiterspeichervorrichtung

gemäß der vorliegenden

Erfindung zeigt;

-

12 ein

Blockdiagramm ist, das ein anderes Beispiel für die Konfiguration der Speicheroperationseinheit

zeigt;

-

13 ein

Blockdiagramm ist, das die zweite Ausführungsform der Halbleiterspeichervorrichtung

gemäß der vorliegenden

Erfindung zeigt;

-

14 ein

Blockdiagramm ist, das die Details eines Puffers und eines Befehlsdecodierers

zeigt;

-

15 ein

Blockdiagramm ist, das die dritte Ausführungsform der Halbleiterspeichervorrichtung

gemäß der vorliegenden

Erfindung zeigt;

-

16 ein

Diagramm der gesamten Konfiguration eines Chips in der zweiten Ausführungsform

des Verfahrens zum Betreiben einer Halbleiterspeichervorrichtung

und auch in der vierten Ausführungsform

der Halbleitervorrichtung gemäß der vorliegenden

Erfindung ist;

-

17 ein

Blockdiagramm ist, das die Details eines Decodierers und einer Eingabe-/Ausgabeeinheit von 16 zeigt;

-

18 ein

Blockdiagramm ist, das die Details einer Speichersteuereinheit und

einer Speicheroperationseinheit von 16 zeigt;

-

19 ein

Zeitlagendiagramm ist, das Leseoperationen der Halbleiterspeichervorrichtung

von 16 zeigt;

-

20 ein

Zeitlagendiagramm ist, das Schreiboperationen der Halbleiterspeichervorrichtung

von 16 zeigt;

-

21 ein

Diagramm der gesamten Konfiguration eines Chips in der dritten Ausführungsform

des Verfahrens zum Betreiben einer Halbleiterspeichervorrichtung

und auch in der fünften

Ausführungsform

der Halbleitervorrichtung gemäß der vorliegenden

Erfindung ist;

-

22 ein

Blockdiagramm ist, das die Details einer Speichersteuereinheit und

einer Speicheroperationseinheit von 16 zeigt;

-

23 ein

Zeitlagendiagramm ist, das Leseoperationen der Halbleiterspeichervorrichtung

von 21 zeigt; und

-

24 ein

Zeitlagendiagramm ist, das Schreiboperationen der Halbleiterspeichervorrichtung

von 21 zeigt.

-

Unter Bezugnahme auf die beiliegenden

Zeichnungen werden nun einige bevorzugte Ausführungsformen der vorliegenden

Erfindung eingehend erläutert.

-

1 ist

ein Flußdiagramm,

welches das Grundprinzip der ersten Ausführungsform in dem Verfahren zum

Betreiben der Halbleiterspeichervorrichtung gemäß der vorliegenden Erfindung

zeigt.

-

In dieser Ausführungsform werden zuerst eine

Befehlseingabe und eine Adressenakzeptanz ausgeführt und wird die Anzahl von

Operationsmodi eingeschränkt.

Der Ausdruck "Einschränken

der Anzahl von Operationsmodi" kann sich zum Beispiel darauf beziehen,

ob es eine Möglichkeit

zum Ausführen

eines Schreiboperationsmodus oder eines Leseoperationsmodus gibt.

Danach wird ein Teil von Schaltungen in der Speichervorrichtung

betrieben und der nächste

Befehl eingegeben. Ein Operationsmodus wird durch diesen Befehl bestimmt,

wobei dadurch der Rest der Schaltungen zu arbeiten beginnen kann.

Wenn der bestimmte Operationsmodus entweder die Schreiboperation

oder die Leseoperation ist, werden Adressen akzeptiert.

-

2 ist

ein Blockdiagramm, welches das Grundprinzip der ersten Ausführungsform

in der Halbleiterspeichervorrichtung gemäß der vorliegenden Erfindung

zeigt.

-

Die Halbleiterspeichervorrichtung

umfaßt

Befehlssteuerschaltungen 39, 41. Die Befehlssteuerschaltungen 39, 41 akzeptieren

Signale, die von einem vorbestimmten Anschluß zugeführt werden, als Befehle zu einer

Vielzahl von Zeiten und schränken

die Anzahl von Operationsmodi auf der Basis des jeweiligen Befehls sequentiell

ein und steuern eine interne Schaltung gemäß dem eingeschränkten Operationsmodus.

Zum Beispiel akzeptieren die Befehlssteuerschaltungen 39, 41 Signale,

die von dem vorbestimmten Anschluß zugeführt werden, als Befehle zu

zwei Zeiten. Die Befehlssteuerschaltun gen 39, 41 schränken die

Anzahl von Operationsmodi zu der Zeit der Eingabe des ersten Befehls

ein und betreiben einen Teil von Schaltungen, der zum Ausführen eines

vorbestimmten Operationsmodus von den eingeschränkten Operationsmodi erforderlich

ist. Die Befehlssteuerschaltungen 39, 41 bestimmen

dann einen Operationsmodus zu der Zeit der Eingabe des zweiten Befehls

und betreiben den Rest der Schaltungen, wenn der bestimmte Operationsmodus

der vorbestimmte Operationsmodus ist.

-

3 zeigt

ein Zustandsübergangsdiagramm

in den ersten Ausführungsformen

des Verfahrens zum Betreiben einer Halbleiterspeichervorrichtung

und einer Halbleiterspeichervorrichtung gemäß der vorliegenden Erfindung.

-

Die Halbleiterspeichervorrichtung

dieser Ausführungsform

ist als dynamischer Speicher mit wahlfreiem Zugriff (DRAM) gebildet,

wobei dessen interne Schaltung in drei Stufen unterteilt ist, und

funktioniert so, daß jede

von ihnen eine Pipeline-Operation ausführen kann.

-

Der DRAM hat sechs verschiedene

Operationsmodi und drei Operationszustände. Die Operationsmodi umfassen

einen Modus mit niedrigem Energieverbrauch, einen Modusregistereinstellmodus,

einen Leseoperationsmodus, einen Schreiboperationsmodus, einen automatischen

Auffrischmodus und einen Selbstauffrischmodus. Die Operationszustände enthalten

einen Bereitschaftszustand, einen Aktivierungszustand R und einen

Aktivierungszustand W.

-

Jeder der Operationsmodi und Operationszustände wird

in einen anderen versetzt, wenn irgendeiner von einem RDA-Befehl, einem WRA-Befehl,

einem DESL-Befehl, einem MRS-Befehl,

einem LAL-Befehl, einem REF-Befehl, einem SELFN-Befehl, einem SELFX-Befehl, einem PDEX-Befehl

und einem PDEN-Befehl empfangen wird. Pfeile werden zum Bezeichnen

der Richtungen verwendet.

-

Der RDA-Befehl, der WRA-Befehl, der

DESL-Befehl, der MRS-Befehl, der LAL-Befehl und der REF-Befehl sind

durch ein Chipselektionssignal /CS und ein Funktionssignal FN bestimmbar,

wie es später

beschrieben ist. Der RDA-Befehl, der WRA-Befehl und der DESL-Befehl, die in der

Zeichnung durch dicke durchgehende Linien gekennzeichnet sind, werden

als erste Befehle bezeichnet, die im Bereitschaftszustand akzeptabel

sind. Der MRS-Befehl, der LAL-Befehl und der REF-Befehl, die durch

dicke unterbrochene Linien gekennzeichnet sind, werden als zweite

Befehle bezeichnet, die in dem Aktivierungszustand R oder

dem Aktivierungszustand W akzeptabel sind. Mit anderen

Worten, die zweiten Befehle können

akzeptiert werden, nachdem die ersten Befehle empfangen worden sind.

Demzufolge erfolgt das Umstellen auf den Leseoperationsmodus, den

Schreiboperationsmodus, den Modusregistereinstellmodus und den automatischen

Auffrischmodus durch das Empfangen des zweiten Befehls, nachdem

der erste Befehl empfangen worden ist. Zusätzlich ist der Aktivierungszustand R ein

Zustand mit einer Möglichkeit

zum Umstellen auf den Leseoperationsmodus nach Empfang des zweiten

Befehls. Der Aktivierungszustand W ist ein Zustand mit

einer Möglichkeit

zum Umstellen auf den Schreiboperationsmodus nach Empfang des zweiten

Befehls.

-

Der SELFN-Befehl, der SELFX-Befehl,

der PDEN-Befehl und der PDEX-Befehl, die durch dünne durchgehende Linien gekennzeichnet

sind, werden in Abhängigkeit

davon bestimmt, ob ein Energieabschaltsignal PD, das später beschrieben

ist, auf seinem hohen Pegel oder niedrigen Pegel ist. Genauer gesagt,

wenn das Energieabschaltsignal PD in dem automatischen

Auffrischmodus auf L schaltet, tritt die Vorrichtung in

den Selbstauffrischmodus ein (SELFN-Befehl). Wenn das Energieabschaltsignal PD in

dem Selbstauffrischmodus auf H schaltet, wird die Vorrichtung in

den Bereitschaftszustand versetzt (SELFX-Befehl). Wenn das Energieabschaltsignal PD im

Bereitschaftszustand auf L schaltet, tritt die Vorrichtung

in den Modus mit niedrigem Energieverbrauch ein (PDEN-Befehl). Wenn

das Energieabschaltsignal PD in dem Modus mit niedrigem

Energieverbrauch auf H schaltet, wird die Vorrichtung in

den Bereitschaftszustand versetzt (PDEX-Befehl).

-

Die dünnen unterbrochenen Linien

geben an, daß das

Umstellen auf den Bereitschaftszustand nach dem Ausführen der

Operationsmodi automatisch erfolgt. Nach der Leseoperation, der

Schreiboperation, der Modusregistereinstelloperation oder der automatischen

Auffrischoperation erreicht die Vorrichtung den Bereitschaftszustand.

-

-

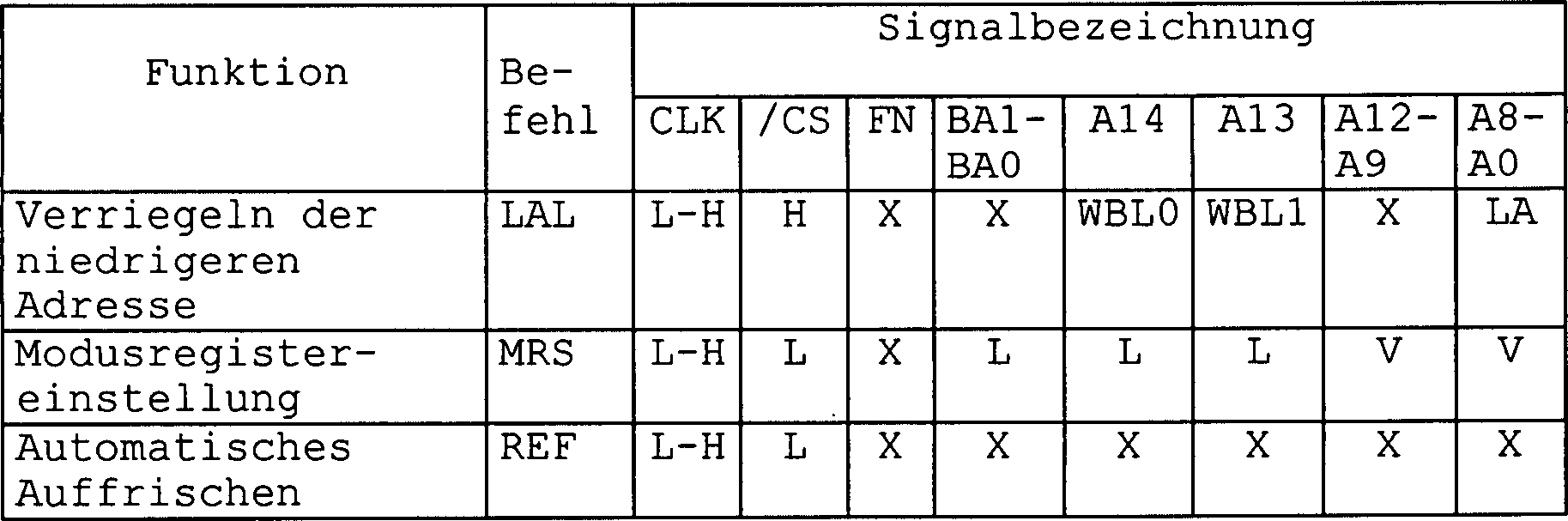

Tabelle 1 zeigt mehrere Zustände von

Signalen bei dem ersten Befehl. In dieser Tabelle bezeichnet das

Symbol "L–H"

eine Veränderung

von dem niedrigen Pegel auf den hohen Pegel; bezeichnet "H"

den hohen Pegel; bezeichnet "L" den niedrigen Pegel; "X"

den hohen oder niedrigen Pegel; "BA" eine spezifizierte

Bankadresse; "UA" eine spezifizierte höhere Adresse.

-

Der DESL-Befehl kann bei der ansteigenden

Flanke eines Taktsignals CLK empfangen werden, wenn das

Chipselektions signal /CS auf dem hohen Pegel ist. Nach

Empfang des DESL-Befehls

wird die Vorrichtung wieder in den Bereitschaftszustand versetzt.

Der DESL-Befehl hält

den Nichtselektionszustand der Vorrichtung.

-

Der ADA-Befehl kann bei der ansteigenden

Flanke des Taktsignals CLK empfangen werden, wenn das Chipselektionssignal

/CS auf dem niedrigen Pegel ist und das Funktionssignal FN auf

dem hohen Pegel ist. Zu derselben Zeit, zu der der ADA-Befehl empfangen

wird, werden Bankadressensignale BA1, BA0 als Bankadressen

akzeptiert und Adressensignale A14–A0 als höhere Adressen

(z. B. Reihenadressen) akzeptiert. Die Vorrichtung wird bei Empfang

des ADA-Befehls in den Aktivierungszustand R versetzt.

-

Der WRA-Befehl kann bei der ansteigenden

Flanke des Taktsignals CLK empfangen werden, wenn das Chipselektionssignal

/CS auf dem niedrigen Pegel ist und das Funktionssignal FN auf

dem niedrigen Pegel ist. Zu derselben Zeit, zu der der WRA-Befehl

empfangen wird, werden die Bankadressensignale BA1, BA0 als

Bankadressen akzeptiert und die Adressensignale A14–A0 als

höhere

Adressen (z. B. Reihenadressen) akzeptiert. Die Vorrichtung wird

bei Empfang des WRA-Befehls in den Aktivierungszustand W versetzt.

-

Tabelle 2 zeigt einige Zustände von

Signalen für

die Akzeptanz der zweiten Befehle. In dieser Tabelle bezeichnen

die Symbole "V", "WBLO" und "WBL1" entweder

einen hohen Pegel oder einen niedrigen Pegel, und das Symbol "LA"

bezeichnet die spezifizierte niedrigere Adresse.

-

Der LAL-Befehl wird bei der ansteigenden

Flanke des Taktsignals CLK empfangen, wenn das Chipselektionssignal

/CS auf dem hohen Pegel ist. Zu derselben Zeit, zu der

der LAL-Befehl empfangen

wird, werden Bankadressensignale BA1, BA0 als

Bankadressen akzeptiert und wird ein Adressensignal A14 als

Bit WBLO geladen, wird ein Adressensignal A13 als

Bit WBL1 akzeptiert und werden Adressensignale A12–A0 als

niedrigere Adressen (z. B. Spaltenadressen) akzeptiert. Bei Empfang

des LAL-Befehls im Aktivierungszustand R tritt die Vorrichtung

in den Leseoperationsmodus zum Ausführen der Leseoperation ein.

Bei Empfang des LAL-Befehls im Aktivierungszustand W tritt

die Vorrichtung in den Schreiboperationsmodus zum Ausführen der

Schreiboperation ein. Genauer gesagt, auf der Basis des bereits

empfangenen Befehls (RDA- oder WRA-Befehl)

wird die Anzahl von Operationsmodi als Antwort auf den neu empfangenen

LAL-Befehl eingeschränkt.

Mit anderen Worten, durch den LAL-Befehl allein werden keine Operationsmodi

bestimmt.

-

Der MRS-Befehl wird bei der ansteigenden

Flanke des Taktsignals CLK empfangen, wenn das Chipselektionssignal

/CS auf dem niedrigen Pegel ist. Zu der Zeit, wenn der

MRS-Befehl empfangen

wird, werden die niedrigen Pegel der Bankadressensignale BA1, BA0 und

Adressensignale A14–A13 akzeptiert

und wird der spezifizierte Wert von den Adressensignalen A12–A0 akzeptiert.

Die Werte von solchen Adressensignalen A12–A0 werden verwendet,

um ein Modusregister 49 einzustellen, wie es später beschrieben

ist.

-

-

Der REF-Befehl wird bei der ansteigenden

Flanke des Taktsignals CLK empfangen, wenn das Chipselektionssignal

/CS auf dem niedrigen Pegel ist. Bei Empfang des REF-Befehls

tritt die Vorrichtung in den automatischen Auffrischmodus zum Ausführen einer

automatischen Auffrischoperation ein.

-

Der LAL-Befehl wird gewöhnlich zum

Ausführen

der Schreib- oder der Leseoperation verwendet. Ob die Schreiboperation

oder die Leseoperation ausgeführt

wird, hängt

von dem ersten Befehl nach dem LAL-Befehl ab. Zusätzlich sind

der MRS-Befehl und der REF-Befehl akzeptabel, wenn das Chipselektionssignal

/CS auf dem niedrigen Pegel ist.

-

Deshalb kann ein DRAM, der

diese Erfindung verkörpert,

irgendeines von der Leseoperation, der Schreiboperation, der Modusregistereinstellung

und der automatischen Auffrischoperation selektiv ausführen, indem

lediglich das Chipselektionssignal /CS und das Funktionssignal FN als

Befehlssignale verwendet werden. Zusätzlich ist es unnötig, Lese-/Schreibanschlüsse wie

etwa /WE oder dergleichen zum Ausführen der Lese- und Schreiboperationen

zu steuern.

-

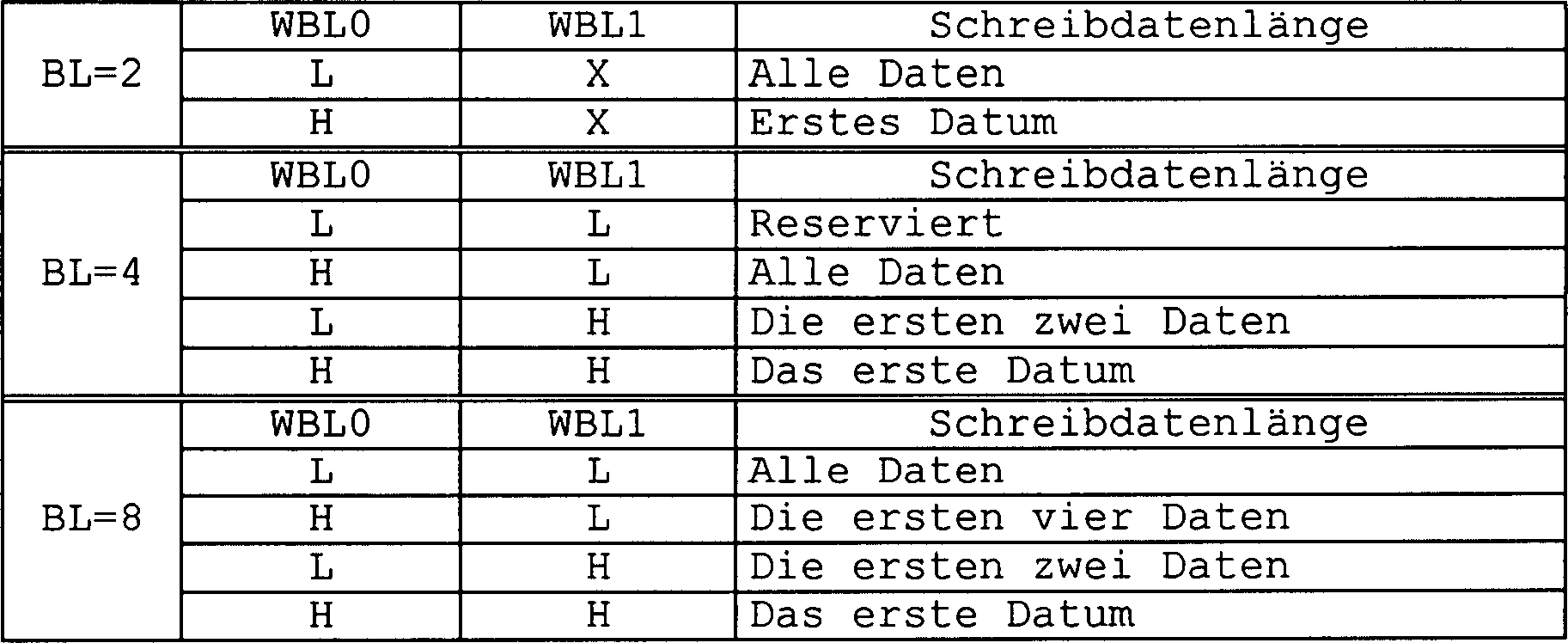

Tabelle 3 zeigt die Einzelheiten

des Bits WBL0 und des Bits WBL1, so wie sie mit den LAL-Befehlen, die

in Tabelle 2 gezeigt sind, eingestellt werden. Das Bit WBL0 und

das Bit WBL1 werden verwendet, um eine Anzahl von Schreibdaten

bei der Schreiboperation einzustellen, die später beschrieben wird. Die Burst-Länge BL kann

die Anzahl von Datensignalen bezeichnen, die während einer einzelnen Schreib-

oder Leseoperation eingegeben und ausgegeben werden kann.

-

-

Falls die Burst-Länge BL auf "2"

eingestellt ist, wird die Schreiboperation aller Datenbits ausgeführt, wenn

das Bit WBL0 auf dem niedrigen Pegel ist. Wenn das Bit WBL0 auf

dem hohen Pegel ist, wird nur das erste Datum geschrieben.

-

Falls die Burst-Länge BL auf "4"

eingestellt ist, wird die Schreiboperation aller Datenbits ausgeführt, wenn

das Bit WBL0 auf dem hohen Pegel ist und das Bit WBL1 auf

dem niedrigen Pegel ist. Wenn das Bit WBL0 auf dem niedrigen

Pegel ist und das Bit WBL1 auf dem hohen Pegel ist, werden

nur die ersten zwei Daten geschrieben. Wenn sowohl das Bit WBL0 als

auch das Bit WBL1 auf dem hohen Pegel ist, wird nur das erste

Datum geschrieben.

-

Falls die Burst-Länge BL auf "r"

eingestellt ist, wird die Schreiboperation aller Daten ausgeführt, wenn das

Bit WBL0 und das Bit WBL1 beide auf dem niedrigen

Pegel sind. Wenn das Bit WBL0 auf dem hohen Pegel ist und

das Bit WBL1 auf dem niedrigen Pegel ist, werden nur die

ersten vier Datenbits dem Schreiben unterzogen. Wenn das Bit WBL0 auf

dem niedrigen Pegel ist und WBL1 auf dem hohen Pegel ist,

werden nur die ersten zwei Daten geschrieben. Wenn die beiden Bits WBL0 und WBL1 auf

dem hohen Pegel sind, wird nur das erste Datum geschrieben.

-

Nach der Schreiboperation entsprechend

der eingestellten Anzahl der Schreibdatenbits geht die Vorrichtung

von dem Schreiboperationsmodus sofort in den Bereitschaftszustand über. Auf

Grund dessen führt das

Verhindern jeglicher unnötigen

Schreiboperationen zur Verkürzung

der Zeit, die für

einen Schreibzyklus benötigt

wird.

-

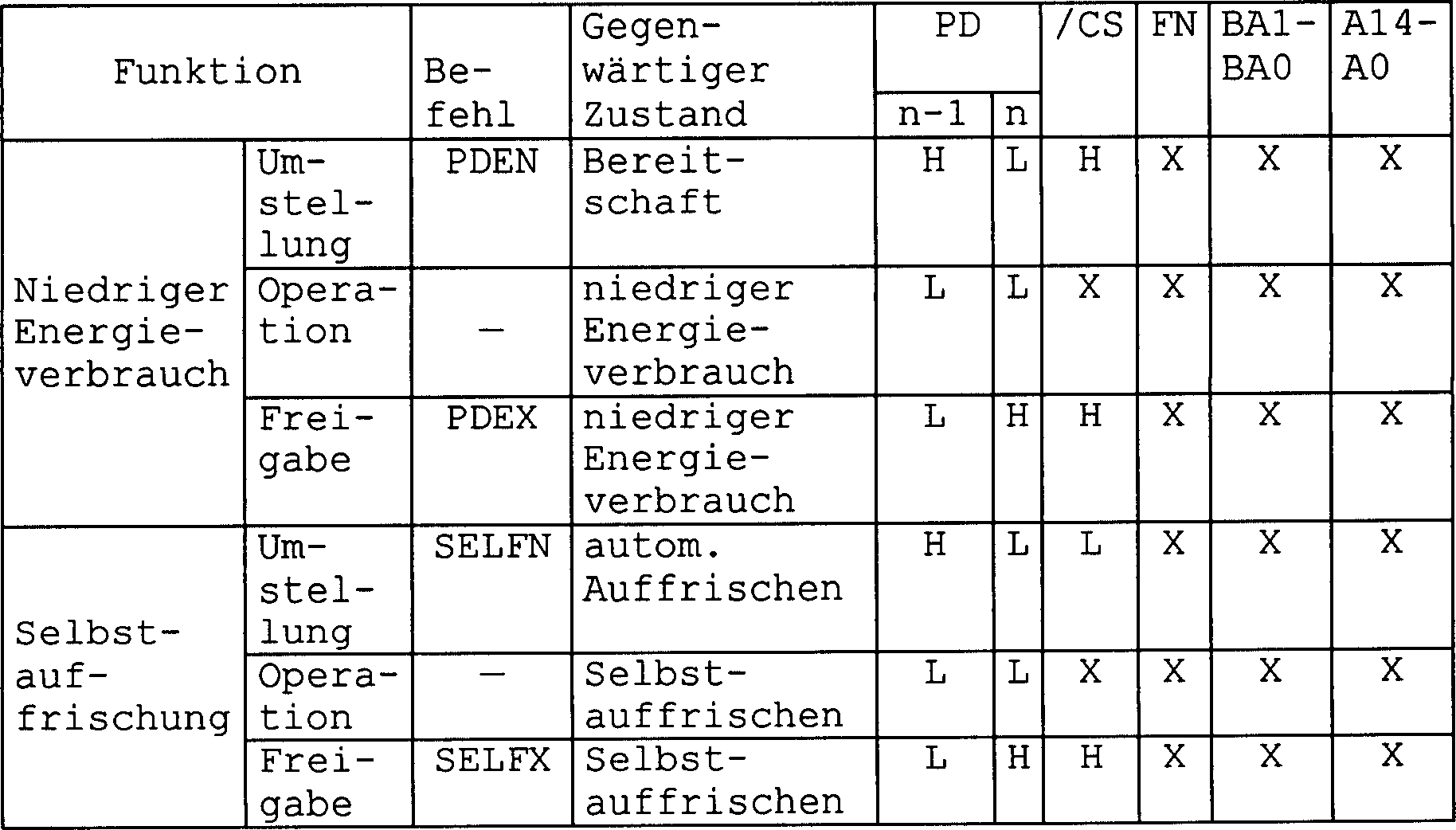

Tabelle 4 zeigt einige Zustände von

Signalen in dem Modus mit niedrigem Energieverbrauch und dem Selbstauffrischmodus.

-

Die Umstellung auf den Modus mit

niedrigem Energieverbrauch erfolgt dann, wenn in dem Bereitschaftszustand

das Energieabschaltsignal PD von seinem hohen Pegel auf

den niedrigen Pegel wechselt, während

das Chipselektionssignal /CS auf dem hohen Pegel bleibt

(PDEN-Befehl). Der Modus mit niedrigem Energieverbrauch wird beibehalten,

indem das Energieabschaltsignal PD auf dem niedrigen Pegel

gehalten wird. Alle Schaltungen außer einem Eingabepuffer zum

Empfangen des Energieabschaltsignals PD werden inaktiviert,

wie es später

beschrieben ist. Der Modus mit niedrigem Energieverbrauch wird freigegeben,

wenn das Energieabschaltsignal PD potentiell von dem niedrigen

Pegel auf den hohen Pegel wechselt, während das Chipselektionssignal

/CS auf dem hohen Pegel bleibt (PDEX-Befehl).

-

Die Umstellung auf den Selbstauffrischmodus

erfolgt dann, wenn sich das Energieabschaltsignal PD in

dem automatischen Auffrischmodus von seinem hohen Pegel auf den

niedrigen Pegel verändert,

während das

Chipselektionssignal /CS auf dem niedrigen Pegel ist (SELFN-Befehl).

Der Zustand des Selbstauffrischmodus wird beibehalten, indem das

Energieabschaltsignal PD auf dem niedrigen Pegel gehalten

wird. Zu dieser Zeit wird die Selbstauffrischoperation kontinuierlich

ausgeführt.

Der Selbstauffrischmodus wird gesperrt, wenn das Energieabschaltsignal PD von

dem niedrigen Pegel auf den hohen Pegel wechselt, während das Chipselektionssignal

/CS auf dem hohen Pegel bleibt (SELFX-Befehl).

-

4 zeigt

die gesamte Konfiguration eines DRAM, der auf eine Ausführungsform

der vorliegenden Erfindung angewendet wird.

-

Der DRAM umfaßt eine Decodierereinheit 21,

vier separate Speicheroperationseinheiten 23 und eine Eingabe-/Ausgabeeinheit 25.

Die Decodierereinheit 21 ist ein Schaltungsblock zum Steuern

der ersten Stufe. Die Speicheroperationseinheiten 23 sind

Blöcke

zum Steuern der zweiten Stufe. Die Eingabe-/Ausgabeeinheit 25 ist

ein Block zum Steuern der dritten Stufe. Jeder von diesen drei Blöcken hat

unabhängig

voneinander eine Funktion zum Ausführen einer Pipeline-Operation. Jede Speicheroperationseinheit 23 enthält eine

Speicherkerneinheit 27.

-

-

Die Decodierereinheit 21 empfängt jeweilig

das Taktsignal CLK, das Energieabschaltsignal PD,

das Chipselektions- signal

/CS, das Funktionssignal FN, die Bankadressensignale BA1, BA0 und

Adressensignale A14–A0 über einen

Taktanschluß CLK,

einen Energieabschaltanschluß PD,

einen Chipselektionsanschluß /CS,

einen Funktionsanschluß FN, über Bankadressenanschlüsse BA1, BA0 und über Adressenanschlüsse A14–A0 von

außen.

Die Decodierereinheit 21 gibt Aktivierungssignale ACT,

Bankadressensignale B-ADD, ein internes Taktsignal CLKIN,

Steuersignale CNT1 und ein Modussteuersignal MD aus.

-

Jede der Speicheroperationseinheiten 23 empfängt die

Aktivierungssignale ACT und die Bankadressensignale B-ADD.

-

Jede Speicheroperationseinheit 23 gibt

Steuersignale CNT2, ein Vordecodiersignal PDECC und

Lesedatensignale RDATA an die Eingabe-/Ausgabeeinheit 25 aus

und empfängt

Schreibdatensignale WDATA von der Eingabe-/Ausgabeeinheit 25.

-

Die Eingabe-/Ausgabeeinheit 25 empfängt Dateneingangs-/

-ausgangssignale DQ15–DQ0 über Dateneingangs-/-ausgangsanschlüsse DQ15–DQ0 von

außen.

Die Eingabe-/Ausgabeeinheit 25 empfängt von der Decodierereinheit 21 die

Steuersignale CNT1, das interne Taktsignal CLKIN und

das Modussteuersignal MD.

-

Die dicken durchgehenden Linien in

der Zeichnung bezeichnen eine Vielzahl von Signalleitungen. Es sei

erwähnt,

daß zum

Vereinfachen der Erläuterung

das Taktsignal CLK beispielsweise einfach als "CLK-Signal"

bezeichnet wird ähnlich

wird der Kürze

halber das Chipselektionssignal /CS als "/CS-Signal" bezeichnet.

-

5 zeigt

die Einzelheiten der Decodierereinheit 21 von 4. Die Decodierereinheit 21 ist

ein Block, dessen Hauptfunktion das Empfangen und Decodieren von

Befehlen und Adressen ist. Nachdem die Signale decodiert sind, wird

die Decodierereinheit 21 automatisch zurückgesetzt

und ist sie zum Empfang der nächsten

Befehle und Adressen bereit.

-

Die Decodierereinheit 21 enthält einen

Taktpuffer 29, einen Steuersignalpuffer 31, eine

Energieabschaltsignalverriegelung 33, einen Reihenadressenpuffer 35,

einen Spaltenadressenpuffer 37, einen Befehlsdecodierer 39,

eine Befehlsverriegelung 41, einen Auffrischzähler 43,

eine Reihenadressenverriegelung 45, eine Spaltenadressenverriegelung 47,

ein Modusregister 49 und eine Modussteuerschaltung 51.

-

Der Taktpuffer 29 empfängt das

Taktsignal CLK und gibt das interne Taktsignal CLKIN aus.

Der Steuersignalpuffer 31 akzeptiert das Chipselektionssignal

/CS und das Funktionssignal FN synchron mit dem

internen Taktsignal CLKIN und gibt solche empfangenen Signale

jeweilig an den Befehlsdecodierer 39 als interne Signale CIN aus.

Die Energieabschaltsignalverriegelung 33 akzeptiert das

Energieabschaltsignal PD synchron mit dem internen Taktsignal CLKIN und

gibt dann das akzeptierte Signal an den Befehlsdecodierer 39 als

internes Energieabschaltsignal PDIN aus. Der Reihenadressenpuffer 35 akzeptiert

die Bankadressensignale BA1–BA0 und

Adressensignale A14–A0 synchron

mit dem internen Taktsignal CLKIN und gibt solche akzeptierten

Signale an die Reihenadressenverriegelung 45 und das Modusregister 49 als

interne Reihenadressensignale ADRIN aus. Der Spaltenadressenpuffer 37 akzeptiert

Adressensignale A8–A0 synchron

mit dem internen Taktsignal CLKIN und gibt die akzeptierten

Signale an die Spaltenadressenverriegelung 47 und das Modusregister 49 als

interne Spaltenadressensignale ADCIN aus. Jedes der Steuersignale CNT1,

das dem Reihenadressenpuffer 35 und dem Spaltenadressenpuffer 37 zugeführt wird,

wird zum jeweiligen Inaktivieren des Reihenadressenpuffers 35 und

des Spaltenadressenpuffers 37 in dem Modus mit niedrigem

Energieverbrauch verwendet.

-

Der Befehlsdecodierer 39 decodiert

Befehle bei Empfang des internen Taktsignals CLKIN, der

internen Signale CIN und des internen Energieabschaltsignals PDIN und

erzeugt die Steuersignale CNT1 zum Steuern anderer Schaltungen

und Aktivierungssignale ACT, um die Speicheroperationseinheiten 23 zu

steuern. Die Steuersignale CNT1 können eine Vielzahl von Signalen

zum Steuern jeder der Schaltungen umfassen. Der Befehlsdecodierer 39 gibt

den akzeptierten ersten Befehl an die Befehlsverriegelung 41 als

Befehlssignal CMD1 aus. Der Befehlsdecodierer 39 empfängt die

Informationen des ersten Befehls, der in der Befehlsverriegelung 41 verriegelt

wurde, durch ein Befehlssignal CMD2. Die Befehlsverriegelung 41 hat

eine Funktion zum Verriegeln der Informationen des ersten Befehls

und zum Speichern des Zustandes der Vorrichtung, der entweder der

Aktivierungszustand R oder der Aktivierungszustand W ist,

der in 3 gezeigt ist.

-

Der Auffrischzähler 43 empfängt das

spezifizierte Steuersignal CNT1 und gibt seine intern erzeugten Auffrischadressensignale ADREF aus,

wenn ein gegenwärtiger

Operationsmodus entweder der automatische Auffrischmodus oder der

Selbstauffrischmodus ist.

-

Die Reihenadressenverriegelung 45 gibt

entweder die internen Reihenadressensignale ADRIN oder die

Ruffrischadressen ADREF als Bankadressensignale B-ADD aus.

Die Spaltenadressenverriegelung 47 gibt entweder die internen

Spaltenadressensignale ADCIN oder die Auffrischadressen ADREF als

Bankadressensignale B-ADD aus.

-

Das Modusregister 49 ist

ein Register zum Einstellen eines Operationszustandes der Vorrichtung.

Das Modusregister 49 empfängt die internen Reihenadressensignale ADRIN,

die internen Spaltenadressensignale ADCIN und ein spezifiziertes

Steuersignal CNT1 und gibt dann ein Moduseinstellsignal MSET aus.

-

Die Modussteuerschaltung 51 empfängt die

im Modusregister 49 eingestellten Informationen (wie etwa

eine Daten latenz DL, einen Burst-Typ BT, eine

Burst-Länge BL,

wie später

eingehend beschrieben) durch das Moduseinstellsignal MSET und gibt

ein Modussteuersignal MD aus.

-

6 zeigt

Bitinhalte des Modusregisters 49. Das Modusregister 49 umfaßt fünfzehn (15)

Bits, die in der Anzahl den Bankadressensignalen BA1, BA0 und

den Adressensignalen A12–A0 entsprechen.

8 Bits von ihnen, die den Bankadressensignalen BA1, BA0 und

den Adressensignalen A12– A7 entsprechen,

sind dafür bestimmt,

um die Signale immer mit niedrigem Pegel zu schreiben. Weitere 3 Bits,

die den Adressensignalen A6–A4 entsprechen,

werden zum Einstellen der Datenlatenz DL entweder auf "2"

oder auf "3" verwendet, welche Latenz zum Bestimmen einer

Eingabe-/Ausgabezeitlage eines Datensignals dient. Ein Bit, das

dem Adressensignal A3 entspricht, wird zum Einstellen des

Burst-Typs BT, der eine Sequenz der Eingabe/Ausgabe von Datensignalen

angibt, entweder auf "sequentiell" oder "verschachtelt" verwendet.

Die übrigen

3 Bits, die den Adressensignalen A2–A0 entsprechen, werden

zum Einstellen der Burst-Länge

BL entweder auf "2", "4" oder "8" verwendet.

-

7 zeigt

die Einzelheiten der Speicheroperationseinheiten 23. Die

Speicheroperationseinheit 23 enthält einen RAS-Generator 53,

einen Vorladegenerator 55, eine erste Steuerschaltung 57,

Vordecodierer 59a, 59b, einen Blockdecodierer 61,

einen Wortdecodierer 63, einen Viertel-(1/4)-Decodierer 65,

einen BLT-Decodierer 67, einen Leseverstärkergenerator 69,

einen Spaltendecodierer 71, eine zweite Steuerschaltung 73 und

einen Lese-/Schreibpuffer 75.

-

Der RRS-Generator 53 empfängt das

Aktivierungssignal ACT, um ein Vorladesteuersignal PRE und ein

Wortleitungsselektionssignal RASZ an die erste Steuerschaltung 57 auszugeben.

Der RAS-Generator 53 gibt an den Vorladegenerator 55 auch

ein Steuersignal P1 aus, das im wesentlichen die selbe Zeitlage

wie das Wortleitungsselektionssignal RASZ hat, und empfängt ein

Steuersignal P2 von dem Vorladegenerator 55. Der Vorladegenerator 55 gibt

das Steuersignal P2 eine vorbestimmte Zeit nach Empfang

des Steuersignals P1 aus.

-

Die erste Steuerschaltung 57 empfängt das

Vorladesteuersignal PRE und das Wortleitungsselektionssignal RASZ und

gibt die Steuersignale CNT2 aus. Das Steuersignal CNT2 umfaßt eine

Vielzahl von Signalen, die dem Wortdecodierer 63, dem 1/4-Decodierer 65,

dem BLT-Decodierer 67, den Vordecodierern 59a, 59b, dem

Leseverstärkergenerator 69,

dem Spaltendecodierer 71, der zweiten Steuerschaltung 73 bzw.

der Eingabe-/Ausgabeeinheit 25 von 5 zugeführt werden. Zwei Steuersignale CNT2 werden

der Eingabe-/Ausgabeeinheit 25 zugeführt.

-

Der Vordecodierer 59a empfängt das

spezifizierte Steuersignal CNT2 und die Bankadressen B-ADD und

gibt Vordecodiersignale PDECB und ein Vordecodiersignal PDECB aus.

Der Vordecodierer 59b empfängt das spezifizierte Steuersignal CNT2 und

Bankadressen B-ADD und gibt Vordecodiersignale PDECC aus.

-

Der Blockdecodierer 61 empfängt das

Vordecodiersignal PDECB von dem Vordecodierer 59a und

gibt Decodiersignale DECB aus.

-

Der Wortdecodierer 63 empfängt das

spezifizierte Steuersignal CNT2, die Decodiersignale DECB und die

Vordecodiersignale PDECR und gibt an die Speicherkerneinheit 27 Hauptwortleitungsdecodiersignale WDEC aus.

-

Der 1/4-Decodierer 65 empfängt das

spezifizierte Steuersignal CNT2 und die Vordecodiersignale PDECR, PDECC und

gibt Subwortleitungsdecodiersignale 1/4DEC an die Speicherkerneinheit 27 aus.

Die Subwortleitungsdecodiersignale 1/4DEC dienen zum Selektieren

irgendeiner der vier Subwort leitungen, die von einer selektierten

Hauptwortleitung abzweigen.

-

Der BLT-Decodierer 67 empfängt das

spezifizierte Steuersignal CNT2, die Decodiersignale DECB und die

Vordecodiersignale PDECR und gibt Bitleitungsübertragungsdecodiersignale BLT an

die Speicherkerneinheit 27 aus.

-

Der Leseverstärkergenerator 69 empfängt das

spezifizierte Steuersignal CNT2, die Decodiersignale DECB und

die Vordecodiersignale PDECR, PDECC und gibt Leseverstärkeraktivierungssignale MW, SW an die

Speicherkerneinheit 27 aus.

-

Der Spaltendecodierer 71 empfängt das

spezifizierte Steuersignal CNT2 und die Vordecodiersignale PDECC und

gibt an die Speicherkerneinheit 27 Spaltenleitungsselektionssignale

CL zum Selektieren einer Spaltenselektionsleitung (nicht gezeigt)

aus. Der Spaltendecodierer 71 ist, wie in 8 gezeigt, aus einer Vielzahl von Decodierschaltungen 71a konfiguriert.

Jede Decodierschaltung 71a umfaßt NAND-Gatter 71b, 71c, die

durch einen Inverter kaskadiert sind, und eine Vielzahl von Invertern.

Das NAND-Gatter 71b auf der Eingangsseite empfängt die

Vordecodiersignale PDECC(a), PDECC(b), PDECC(c).

Das NAND-Gatter 71c auf der Ausgangsseite empfängt ein

Ausgangssignal des NAND-Gatters 71b und das Steuersignal CNT2.

-

Die in 7 gezeigte

zweite Steuerschaltung 73 empfängt das spezifizierte Steuersignal CNT2 und die

Vordecodiersignale PDECC und gibt ein Steuersignal CNT3 zur

Steuerung des Lese-/Schreibpuffers 75 aus.

-

Der Lese-/Schreibpuffer 75 arbeitet

unter der Steuerung des Steuersignals CNT3, so daß dieser

Puffer Schreibdatensignale WDATA, die von der Eingabe-/Ausgabeeinheit 25 gesendet

werden, während

der Schreiboperation zu der Speicherkerneinheit 27 überträgt; während der

Leseoperation überträgt er Lesedatensignale RDATA,

die von der Speicherkerneinheit 27 ausgegeben wurden, zu

der Eingabe-/Ausgabeeinheit 25.

-

9 gibt

einen kleinen Überblick über die

Speicherkerneinheiten 27 von 4.

Die Speicherkerneinheit 27 enthält Hauptwortdecodierer 27a,

1/4-Wortselektoren 27b, Subwortleitungstreiber 27c,

Subwortdecodierer 27d, Leseverstärker 27e und Speicherzellen

MC, die alle mehrfach angeordnet sind.

-

Jeder der Hauptwortdecodierer 27a empfängt das

Hauptwortleitungsdecodiersignal WDEC und selektiert die

spezifizierte Hauptwortleitung MWL. Die 1/4-Wortselektoren 27c,

die Subwortleitungstreiber 27b und die Subwortdecodierer 27d empfangen

das Subwortleitungsdecodiersignal 1/4DEC und selektieren die spezifizierte

Subwortleitung SWL. Zum Beispiel werden die Hauptwortleitung MWL und

die Subwortleitung SWL, wie es durch dicke Linien gekennzeichnet

ist, in einem einzelnen Leseoperationsvorgang selektiert. Daten

werden von den Speicherzellen MC ausgegeben, die mit der selektierten

Hauptwortleitung MWL und der Subwortleitung SWL verbunden

sind.

-

Der Leseverstärker 27e verstärkt Daten,

wie sie während

der Leseoperation von den Speicherzellen MC ausgegeben

werden, und schreibt die verstärkten

Daten in den Speicherzellen um.

-

10 zeigt

die Einzelheiten der Eingabe-/Ausgabeeinheit 25. Die Eingabe-/Ausgabeeinheit 25 enthält einen

Datenkonverter 77 zur Leseoperation, einen Datenkonverter 79 zur

Schreiboperation, einen Datenausgabepuffer 81, einen Dateneingabepuffer 83 und

eine Schreibdatenlängensteuerschaltung 85.

-

Der Datenkonverter 77 konvertiert

parallele Lesedatensignale RDATA, die von dem Lese-/Schreibpuffer 75 von 7 zugeführt werden, in serielle Datensignale

und gibt die konvertierten Daten DOUT an den Datenausgabepuffer 81 aus.

Der Datenkonverter 79 konvertiert serielle Lesedaten DIN,

die von dem Dateneingabepuffer 83 zugeführt werden, in parallele Daten

und gibt die konvertierten Schreibdatensignale WDATA an

den Lese-/Schreibpuffer 75 von 7 aus. Die Datenkonverter 77, 79 empfangen

die spezifizierten Steuersignale CNT1, CNT2, die

Vordecodiersignale PDECC, das Modussteuersignal MD mit

den Informationen über

die Datenlatenz DL bzw. das interne Taktsignal CLKIN.

-

Die Schreibdatenlängensteuerschaltung 85 empfängt das

spezifizierte Steuersignal CNT1 und gibt an den Datenkonverter 79 ein

Steuersignal CNT3 zum Steuern der Datenlänge während der

Schreiboperation aus. Die Schreibdatenlänge wird durch die Bits WBL0, WBL1,

wie sie von den Adressenanschlüssen A14–A13 zugeführt werden,

beim Eingeben eines LAL-Befehls während der Schreiboperation

spezifiziert (siehe Tabelle 3).

-

Unten wird eine Leseoperation als

typische Operation des DRAM erläutert.

-

Wie in 3 gezeigt,

wird die Leseoperation so ausgeführt,

daß die

Vorrichtung durch den LAL-Befehl (zweiter Befehl) in den Leseoperationsmodus

eintritt, nachdem die Vorrichtung ausgehend von dem Bereitschaftsmodus

durch einen RDA-Befehl (erster Befehl) den Aktivierungszustand R einnimmt.

-

11 zeigt

die Zeitlagen von einigen Hauptsignalen während der Leseoperation.

-

Zuerst akzeptiert der Steuersignalpuffer 31 von 5 den ersten Befehl synchron

mit der ansteigenden Flanke des CLK-Signals (11(a)).

Der Befehlsdecodierer 39 empfängt ein internes Signal CIN,

das durch den Steuersignalpuffer 31 akzeptiert wurde, und

verändert

dann den Pegel des ACT- Signals

für eine

vorbestimmte Periode auf einen hohen Pegel (11(b)).

-

Der Reihenadressenpuffer 35 von 5 akzeptiert zu derselben

Zeit, zu der der erste Befehl akzeptiert wird, Adressen von den

Signalen BA1–BA0 und

den Signalen A14–A0.

Die Reihenadressenverriegelung 45 gibt die internen Reihenadressensignale ADRIN,

die von dem Reihenadressenpuffer 35 ausgegeben wurden,

als Bankadressen B-ADD aus (11(c)).

-

Als Antwort auf den RDA-Befehl geht

die Vorrichtung in den Aktivierungszustand R über. Die

Leseoperation und die Schreiboperation sind zu dieser Zeit voneinander

unterscheidbar, da der Aktivierungszustand R nie in den

Schreiboperationsmodus eintritt. Mit anderen Worten, die Anzahl

von Operationsmodi wird als Antwort auf die Akzeptanz des ersten

Befehls eingeschränkt.

-

Bei Empfang eines ACT-Signals verändert der

RAS-Generator 53 von 7 den

Pegel des Wortleitungsselektionssignals RASZ für eine vorbestimmte

Periode auf den hohen Pegel und jenen des Vorladesteuersignals PRE

auf den niedrigen Pegel (11(d)). Danach

ist das Vorladen der Bitleitungen beendet. Ferner werden die spezifizierte

Hauptwortleitung MWL und die Subwortleitung SWL selektiert,

ohne den zweiten Befehl zu empfangen. In dem Zustand, wenn der erste

Befehl akzeptiert worden ist, beginnt die Steuerung der zweiten

Stufe, das heißt,

die Speicheroperationseinheit 23 wird zur Operation aktiv

gemacht.

-

An diesem Punkt empfängt der

Spaltendecodierer 71 ein Steuersignal CNT2 an

dem NAND-Gatter 71c vor dem Empfang der Vordecodiersignale PDECC(a), PDECC(b) und PDECC(c),

wie in 8 gezeigt. Der

Spaltendecodierer 71 tritt zum Empfangen der Vordecodiersignale PDECC(a), PDECC(b) und PDECC(c) in

den Bereitschaftszustand ein, so daß die Geschwindigkeit der Operation

erhöht

wird.

-

Der Steuersignalpuffer 31 von 5 akzeptiert den zweiten

Befehl bei der ansteigenden Flanke des CLK-Signals, die jener des

ersten Befehls am nächsten

ist (11(e)). Deshalb werden die Informationen,

die erhalten werden, wenn der zweite Befehl eingegeben wird, in

der Steuerung in kurzer Zeit nach Eingabe des ersten Befehls widergespiegelt.

Dies führt

zum Minimieren der Verzögerung

bei der Steuerprozedur, die dem zweiten Befehl entspricht, wenn

Befehle zu zwei Zeiten eingegeben werden. Die obenerwähnte Steuerprozedur

ist auch auf den WRA-Befehl anwendbar.

-

Der Befehlsdecodierer 39 empfängt das

interne Signal CIN und decodiert dann den eingegebenen Befehl als

LAL-Befehl. Der

Zustand der Vorrichtung geht durch den LAL-Befehl in den Leseoperationsmodus über. Mit

anderen Worten, der Operationsmodus wird bestimmt, indem Befehle

zu zwei Zeiten eingegeben werden. Da die Anzahl von Operationsmodi

sequentiell eingeschränkt

wird, werden die Anschlüsse,

die für

die Befehlseingaben erforderlich sind, in der Anzahl reduziert.

-

Der Spaltenadressenpuffer 37 akzeptiert

die Adressen als Signale A8–A0 zu

derselben Zeit, zu der der zweite Befehl akzeptiert wird. Die Spaltenadressenverriegelung 47 gibt

interne Spaltenadressensignale ADCIN, die von dem Spaltenadressenpuffer 37 ausgegeben

wurden, als Bankadressen B-ADD aus (11(f)).

Da die Adressen, die zum Ausführen

der Leseoperation erforderlich sind, zu zwei Zeiten akzeptiert werden,

werden die Adressenanschlüsse

in der Anzahl signifikant reduziert. Dies führt zu einer Verringerung der

Anzahl von Adressenkontaktstellen, Adresseneingangsschaltungen oder

dergleichen, wodurch die Chipgröße entsprechend

verkleinert wird. Diese Verkleinerung wird durch Verringerung der

Anzahl von Anschlüssen

erreicht, wodurch der Pakkungsgröße Grenzen

gesetzt werden.

-

Es sei erwähnt, daß die Speicheroperationseinheit 23 nach

Empfang des ersten Befehls weiterarbeitet. Lesedaten werden von

den Speicherzellen MC, die mit der selektierten Subwortleitung

SWL verbunden sind, an eine Bitleitung (nicht gezeigt) ausgegeben

(11(g)).

-

Der BLT-Decodierer 67 von 7 empfängt das Signal CNT2 und die

spezifizierte Adresse zum Verändern

des Pegels des Signals BLT auf den niedrigen Pegel (11(h)). Der Leseverstärkergenerator 69 empfängt das

Signal CNT2 und die spezifizierte Adresse und verändert den

Pegel der Leseverstärkeraktivierungssignale

MW, SW auf den hohen Pegel ( 11(j)).

-

Auf Grund des hohen Pegels der Leseverstärkeraktivierungssignale MW, SW wird

der Leseverstärker aktiviert

(bei "ACTV" in 11),

und der Signalpegel einer Bitleitung wird verstärkt (11(k)).

-

Der Spaltendecodierer 71 empfängt das

Signal CNT2 und die Vordecodiersignale PDECC und

verändert

den Pegel des Spaltenleitungsselektionssignals CL auf den

hohen Pegel (11(1)). Auf Grund des hohen

Pegels des CL-Signals werden die Datensignale DATA von

der Speicherkerneinheit 27 an den Lese-/Schreibpuffer 75 ausgegeben

(11(m)).

-

Der Lese-/Schreibpuffer 75 gibt

die Datensignale DATA als Lesedatensignale RDATA an

den Datenkonverter 77 von 10 aus.

Der Datenkonverter 77 wendet eine Parallel-Seriell-Konvertierung auf

die Lesedatensignale RDATA an und gibt die konvertierten

Signale als Dateneingangs-/-ausgangssignale DQ15–DQ0 durch

den Datenausgabepuffer 81 aus (11(n)).

-

Der RAS-Generator 53 von 7 empfängt das Ausgangssignal P2 von

dem Vorladegenerator 55 und verändert den Pegel des PRE-Signals

auf den hohen Pegel (11(o)). Auf Grund

des niedrigen Pegels des PRE-Signals gibt die erste Steuerschaltung 57 Steuersignale CNT2 jeweilig

an den BLT- Decodierer 67 und

den Leseverstärkergenerator 69 aus.

Der BLT-Decodierer 67 verändert den Pegel des BLT-Signals

auf den hohen Pegel und beendet das Ausgeben von Daten von dem (den)

Leseverstärker(n)

(11(p)). Der Leseverstärkergenerator 69 verändert die

Pegel des MW-Signals und des SW-Signals

auf den niedrigen Pegel (11(q)) und

inaktiviert die Leseverstärker

("RESET" von 11).

-

Des weiteren wird bei dem vierten

Taktsignal nach Akzeptanz des ersten Befehls der erste Befehl für die nächste Leseoperation

akzeptiert. Das ACT-Signal bleibt für eine vorbestimmte Periode

bei Empfang des Eingangsbefehls auf dem hohen Pegel (11(r)). Auf Grund des hohen Pegels des

ACT-Signals verändert sich

der Pegel des PRE-Signals auf L, wodurch das Vorladen der

Bitleitung ausgeführt

wird ( 11(s)). Mit anderen Worten,

die Vorladeoperation wird im Inneren der Vorrichtung als Antwort

auf den ersten Befehl in dem nächsten

Zyklus automatisch ausgeführt.

-

Zu dieser Zeit führen die Speicheroperationseinheit 23 und

die Eingabe-/Ausgabeeinheit 25 die Leseoperation in dem

ersten Lesezyklus aus. Solch eine Pipeline-Operation ist deshalb

erreichbar, weil die Decodierereinheit 21, die Speicheroperationseinheit 23 und

die Eingabe-/Ausgabeeinheit 25 unabhängig voneinander betriebsfähig sind.

Danach erfolgt die Akzeptanz des ersten Befehls bei der nächsten Leseoperation

in Intervallen von vier Taktsignalen.

-

In dem in 11 gezeigten Zeitlagendiagramm ist eine

Operation von einer von vier Bänken

gezeigt. In der Praxis können

Lesedaten synchron mit jedem Taktimpuls ohne Intervalle durch alternierendes

Vorsehen eines Zugriffs zu zwei Zeiten Bänke in Intervallen von zwei

Takten ausgegeben werden.

-

Als nächstes wird unten eine Schreiboperation

erläutert.

-

Die Schreiboperation ist im wesentlichen

dieselbe wie die oben beschriebene Leseoperation bis zu der Adressenakzeptanz

auf der Basis des zweiten Befehls.

-

Zuerst geht die Vorrichtung, wie

in 3 gezeigt, wenn der

WRA-Befehl als erster Befehl im Bereitschaftszustand empfangen wird,

in den Aktivierungszustand W über. Gleichzeitig werden die

oberen Schreibadressen (BA1–BA0, A14–A0)

akzeptiert.

-

Bei Empfang des LAL-Befehls als zweiten

Befehl geht die Vorrichtung danach in den Schreiboperationsmodus über. Gleichzeitig

werden die unteren Schreibadressen (A8–A0) und die Schreibdatenlängen (WBL0

, WBL1)

akzeptiert. Zusätzlich

werden synchron mit dem CLK-Signal die Schreibdaten (DQ15– DQ0) sukzessive

akzeptiert.

-

Die Anzahl von Ereignissen zum Akzeptieren

von Schreibdaten ist bestimmbar, wenn die in dem Modusregister eingestellte

Burst-Länge

deren Maximalanzahl ist. Bei der tatsächlichen Akzeptanz wird die

Anzahl von Ereignissen in Abhängigkeit

von der Länge

von Schreibdaten bestimmt, so wie sie gleichzeitig mit dem zweiten

Befehl akzeptiert werden. Wenn die Burst-Länge zum Beispiel auf "4"

eingestellt ist, ist dann, wenn , WBL1, die als

Schreibdatenlängen

akzeptiert werden, auf dem niedrigen Pegel bzw. dem hohen Pegel

sind, die Anzahl von Ereignissen zum Akzeptieren der Schreibdaten

so wie in Tabelle 3 gezeigt. Auf der Basis der Schreibdatenlänge, die

zusammen mit dem zweiten Befehl zu derselben Zeit akzeptiert wird,

wird die Anzahl von Ereignissen für das Akzeptieren direkt durch

die Schreibdatenlängensteuerschaltung 85 gesteuert;

demnach kann dann, wenn eine Vielzahl von Datenbits sukzessive akzeptiert

wird, die Schreibdatenlänge

ohne weiteres gesteuert werden. Da es möglich ist, die Schreibdatenlänge nur

durch die Eingabe-/Ausgabeeinheit 25 zu

steuern, wird die Schreibdatenlänge, so

wie sie beim Eingeben des zweiten Befehls akzeptiert wird, zur Steuerung

von solch einer Schreiboperation mit Toleranz verwendet.

-

Die sukzessive akzeptierten Schreibdaten

werden durch den Dateneingabepuffer 83, der in 10 gezeigt ist, sequentiell

dem Datenkonverter 79 zugeführt. Der Datenkonverter 79 konvertiert

solche seriellen Daten in parallele Daten. Der Datenkonverter 79 gibt

auch die konvertierten Daten an die Speicheroperationseinheit 23 als

Schreibdaten WDATA aus. Die Speicheroperationseinheit 23 schreibt

die Daten in spezifizierte Speicherzellen.

-

Hier arbeiten die Eingabe-/Ausgabeeinheit 25 und

die Speicheroperationseinheit 23 mit der eingestellten

Anzahl von Ereignissen für

die Akzeptanz. Nach diesen Operationen ist der Schreiboperationsmodus

vollendet und tritt die Vorrichtung in den Bereitschaftszustand

ein. Kurz gesagt, Daten, die nicht geschrieben werden müssen (ein

Teil, der länger

als die spezifizierte Datenlänge

ist), werden nicht gesteuert, so daß die für die Schreiboperation benötigte Zeit

eingespart werden kann. Als Resultat wird die Eingabezeitlage des

ersten Befehls im nächsten

Zyklus bestimmt.

-

Als nächstes wird unten der Modusregistereinstellmodus

erläutert.

-

Die Umstellung auf den Modusregistereinstellmodus

erfolgt bei Empfang des MRS-Befehls als zweiten Befehl, während die

Vorrichtung im Aktivierungszustand R ist. Wenn auf den

Modusregistereinstellmodus zu derselben Zeit umgestellt wird, zu

der der MRS-Befehl akzeptiert wird, werden die Signale BA0–BA1 und

die Signale A14–A0 akzeptiert,

um einen Wert des Modusregisters einzustellen. Der Modusregistereinstellmodus, der

mit keiner internen Operation einhergeht, kann den spezifizierten

Wert innerhalb einer vorbestimmten Periode einstellen, auch wenn

solch eine Steuerprozedur nach Empfang des zweiten Befehls beginnt.

Zu der Zeit der Eingabe des ersten Befehls ist es nicht erforderlich,

den spezifizierten Wert des Modusregisters einzustellen, so daß der Einstellwert

nicht mehr gehalten zu werden braucht, bis der zweite Befehl eingegeben