CN100456734C - 使用多端口存储器的体系结构、装置、系统及其使用方法 - Google Patents

使用多端口存储器的体系结构、装置、系统及其使用方法 Download PDFInfo

- Publication number

- CN100456734C CN100456734C CNB2004100084978A CN200410008497A CN100456734C CN 100456734 C CN100456734 C CN 100456734C CN B2004100084978 A CNB2004100084978 A CN B2004100084978A CN 200410008497 A CN200410008497 A CN 200410008497A CN 100456734 C CN100456734 C CN 100456734C

- Authority

- CN

- China

- Prior art keywords

- data

- port

- memory

- read

- write

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 230000015654 memory Effects 0.000 title claims abstract description 246

- 238000000034 method Methods 0.000 title claims abstract description 45

- 239000000872 buffer Substances 0.000 claims abstract description 124

- 230000005540 biological transmission Effects 0.000 claims abstract description 8

- 238000003860 storage Methods 0.000 claims description 96

- 230000003139 buffering effect Effects 0.000 claims description 33

- 238000004891 communication Methods 0.000 abstract description 12

- 230000008878 coupling Effects 0.000 abstract description 2

- 238000010168 coupling process Methods 0.000 abstract description 2

- 238000005859 coupling reaction Methods 0.000 abstract description 2

- 230000008030 elimination Effects 0.000 abstract 1

- 238000003379 elimination reaction Methods 0.000 abstract 1

- 230000000630 rising effect Effects 0.000 description 21

- 230000001360 synchronised effect Effects 0.000 description 13

- 238000012545 processing Methods 0.000 description 11

- 238000005516 engineering process Methods 0.000 description 9

- 210000004027 cell Anatomy 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 7

- 238000010586 diagram Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 6

- 239000000126 substance Substances 0.000 description 6

- 230000004913 activation Effects 0.000 description 5

- 239000003550 marker Substances 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 230000008859 change Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 238000013500 data storage Methods 0.000 description 3

- 210000000352 storage cell Anatomy 0.000 description 3

- 230000009471 action Effects 0.000 description 2

- 230000008676 import Effects 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 1

- 230000033228 biological regulation Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000012856 packing Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1075—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers for multiport memories each having random access ports and serial ports, e.g. video RAM

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Static Random-Access Memory (AREA)

- Dram (AREA)

- Multi Processors (AREA)

- Information Transfer Systems (AREA)

Abstract

Description

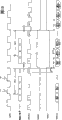

| 宽度 | 信号名称 | 类型 | 文字说明 |

| 1 | WPCK | 输入 | 端口写时钟脉冲。一个专用时钟应对应每个写端口以同步加载写数据至写入页输入内。若时序允许电源不重要则可对所有端口使用一个公共时钟。 |

| 1 | NWSE0 | 输入 | 写入线选择信号。当其为低时激活具有写双重缓冲器的0线路。当对整个线路写入时,NWSE0必须在32个WPCK周期保持为低。若NWSE0和NWSE1两者均得到认定(asserted),则将相同的数据写至两个线路。 |

| 1 | NWSE1 | 输入 | 写入线选择信号。当其为低时激活具有写双重缓冲器的1线路。当对整个线路写入时,NWSE1必须在32个WPCK周期保持为低。若NWSE0和NWSE1两者均得到认定,则将相同的数据写至两个线路。 |

| 1 | WEPR | 输入 | 写输入选择指示器复位信号。该信号与NWSE结合使用且与WPCK同步。WEPR相对于WPCK的上升沿而认定,将选定的写输入选择指示器设为输入0。若NWSE0和NWSE1两者均得到认定,则写输入选择指示器对两个写入线均被复位到输入0。在认定WEPR之后,WPCK的各后续周期使选定写输入选择指示器前进。在输入选择指示器前进到最后的输入之后,所有后续的WPCK周期将产生空值指示字。当在WPCK的上升沿上接着认定了WEPR时,选定的写指示器将指向输入0 |

| 8 | WD[7:0] | 输入 | 端口写8位数据总线。 |

| 宽度 | 信号名称 | 类型 | 文字说明 |

| 1 | RPCK | 输入 | 端口读时钟。该时钟选通数据从读输入缓冲器到端口读数据总线上。一个专用时钟可以伴随每个读端口去从读页输入同步读数据。 |

| 1 | NRSE0 | 输入 | 读出线0选择信号。当其为低时激活具有读双重缓冲器的0线路。为移出32个输入的内容,在32个RPCK周期上认定NRSE0。 |

| 1 | NRSE1 | 输入 | 读出线1选择信号。当其为低时激活具有读双重缓冲器的1线路。为移出32个输入的内容,在32个RPCK周期上认定NRSE1。 |

| 8 | RD[7:0] | 输出 | 端口读8位数据总线。 |

| 1 | PWCK | 输入 | 并行写端口时钟。 |

| 1 | LPWR | 输入 | 并行加载写寄存器。与PWCK同步。 |

| N*8 | PRD[N*8-1:0] | 输出 | 用于并行读端口的读总线。与MCK同步。 |

| N*8 | PWD[N*8-1:0] | 输入 | 用于并行写端口的写总线。与PWCK同步。 |

| N*8 | SBUS[N*8-1:0] | 输出 | 用于窥探寄存器的读总线。与MCK同步。 |

| 1 | SLD | 输入 | 窥探寄存器加载信号。与MCK同步。 |

| 1 | NRST | 输入 | 端口逻辑复位信号。 |

| 1 | NWR | 输入 | 存储器写信号。低电平有效。与MCK时钟同步。当被认定时,存储器使用源(PA)和目标(MA)地址执行写操作。指定端口页的内容被写入指定的存储块页内。 |

| 1 | NRD | 输入 | 存储器读信号。低电平有效。与MCK同步。当被认定时,存储器使用源(MA)和目标(PA)地址执行读操作。内容被读进指定的端口页内。 |

| 5 | PA[4:0] | 输入 | 端口地址。最大30个端口(用于一个5位地址)。这是用于从端口页至主存储器的写操作的源地址,或者用于从主存储器到端口页的读操作的目的地地址。 |

| 1 | PL | 输入 | 指定从双重缓冲页的哪一个线路访问。“0”指定线路0。“1”指定线路1。不用于单重缓冲器结构。 |

| 12 | MA[11:0] | 输入 | 用于读或者写操作的存储页地址。最大4096页。这是用于写存储操作的端口页的目的地地址,以及用于读到端口页的存储页的源地址。 |

| 宽度 | 信号名称 | 类型 | 文字说明 |

| 1 | MCK | 输入 | MCK是用于存储块的时钟。可以与PCK异步。所有存储块操作均与MCK同步。 |

| 1 | FDINH | 输入 | 在系统复位之后,从熔线盒(fuse block)经由本端口加载的用于存储器子模块H的冗余信息。 |

| 1 | FDINL | 输入 | 在系统复位之后,从熔线盒经由本端口加载的用于存储器子模块L的冗余信息。 |

| 1 | FSCKH | 输入 | 根据FDINH用以由熔线盒锁存数据的时钟。 |

| 宽度 | 信号名称 | 类型 | 文字说明 |

| 1 | FSCKL | 输入 | 根据FDINH用以由熔线盒锁存数据的时钟。 |

| 2(或更多) | WTC | 输入 | 用于设置内部的写入定时余量的代码。可以输入到可编程寄存器中。 |

| 3(或更多) | RTC | 输入 | 用于设置内部的写入定时余量的代码。可以输入到可编程寄存器中。 |

Claims (14)

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US45444303P | 2003-03-13 | 2003-03-13 | |

| US60/454,443 | 2003-03-13 | ||

| US10/702,744 US7571287B2 (en) | 2003-03-13 | 2003-11-05 | Multiport memory architecture, devices and systems including the same, and methods of using the same |

| US10/702,744 | 2003-11-05 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1531275A CN1531275A (zh) | 2004-09-22 |

| CN100456734C true CN100456734C (zh) | 2009-01-28 |

Family

ID=32776312

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2004100084978A Expired - Lifetime CN100456734C (zh) | 2003-03-13 | 2004-03-12 | 使用多端口存储器的体系结构、装置、系统及其使用方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (4) | US7571287B2 (zh) |

| EP (1) | EP1457993B1 (zh) |

| JP (2) | JP2004288355A (zh) |

| CN (1) | CN100456734C (zh) |

| DE (1) | DE602004028981D1 (zh) |

| TW (1) | TWI263228B (zh) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI453443B (zh) * | 2012-12-28 | 2014-09-21 | Zeroplus Technology Co Ltd | Data analysis method |

| TWI453444B (zh) * | 2013-01-04 | 2014-09-21 | Zeroplus Technology Co Ltd | Displays the method of the detection process |

| TWI472783B (zh) * | 2012-12-28 | 2015-02-11 | Zeroplus Technology Co Ltd | Data capture and detection method |

Families Citing this family (50)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7571287B2 (en) | 2003-03-13 | 2009-08-04 | Marvell World Trade Ltd. | Multiport memory architecture, devices and systems including the same, and methods of using the same |

| KR100546331B1 (ko) * | 2003-06-03 | 2006-01-26 | 삼성전자주식회사 | 스택 뱅크들 마다 독립적으로 동작하는 멀티 포트 메모리장치 |

| US7100002B2 (en) * | 2003-09-16 | 2006-08-29 | Denali Software, Inc. | Port independent data transaction interface for multi-port devices |

| US7159049B2 (en) * | 2003-10-31 | 2007-01-02 | Lucent Technologies Inc. | Memory management system including on access flow regulator for a data processing system |

| US7162551B2 (en) * | 2003-10-31 | 2007-01-09 | Lucent Technologies Inc. | Memory management system having a linked list processor |

| FR2864320A1 (fr) * | 2003-12-19 | 2005-06-24 | St Microelectronics Sa | Nouvelle architecture de memoire fifo et procede de gestion d'une telle memoire. |

| US8560795B2 (en) * | 2005-06-30 | 2013-10-15 | Imec | Memory arrangement for multi-processor systems including a memory queue |

| JP2007053536A (ja) * | 2005-08-17 | 2007-03-01 | Winbond Electron Corp | 画像信号の符号化処理装置におけるラスタ/ブロック変換用のバッファメモリシステム |

| KR100815176B1 (ko) * | 2005-09-28 | 2008-03-19 | 주식회사 하이닉스반도체 | 멀티포트 메모리 장치 |

| EP1932158A4 (en) | 2005-09-30 | 2008-10-15 | Mosaid Technologies Inc | MEMORY WITH OUTPUT CONTROL |

| US7747833B2 (en) | 2005-09-30 | 2010-06-29 | Mosaid Technologies Incorporated | Independent link and bank selection |

| US7652922B2 (en) * | 2005-09-30 | 2010-01-26 | Mosaid Technologies Incorporated | Multiple independent serial link memory |

| US11948629B2 (en) | 2005-09-30 | 2024-04-02 | Mosaid Technologies Incorporated | Non-volatile memory device with concurrent bank operations |

| US20070076502A1 (en) | 2005-09-30 | 2007-04-05 | Pyeon Hong B | Daisy chain cascading devices |

| US7600081B2 (en) * | 2006-01-18 | 2009-10-06 | Marvell World Trade Ltd. | Processor architecture having multi-ported memory |

| EP2008164A2 (en) * | 2006-03-30 | 2008-12-31 | Silicon Image, Inc. | Inter-port communication in a multi- port memory device |

| US9383938B2 (en) * | 2006-04-18 | 2016-07-05 | International Business Machines Corporation | Method, system, and apparatus for re-conveying input/output operations utilizing a sequential-access data storage device secondary communication port |

| US8234425B1 (en) | 2007-06-27 | 2012-07-31 | Marvell International Ltd. | Arbiter module |

| US7949817B1 (en) | 2007-07-31 | 2011-05-24 | Marvell International Ltd. | Adaptive bus profiler |

| US7882325B2 (en) * | 2007-12-21 | 2011-02-01 | Intel Corporation | Method and apparatus for a double width load using a single width load port |

| CN101217733B (zh) * | 2008-01-18 | 2012-05-23 | 中兴通讯股份有限公司 | 一种双模智能移动终端及其内部通讯方法 |

| US8131915B1 (en) | 2008-04-11 | 2012-03-06 | Marvell Intentional Ltd. | Modifying or overwriting data stored in flash memory |

| US8683085B1 (en) | 2008-05-06 | 2014-03-25 | Marvell International Ltd. | USB interface configurable for host or device mode |

| US8938590B2 (en) | 2008-10-18 | 2015-01-20 | Micron Technology, Inc. | Indirect register access method and system |

| US8370557B2 (en) * | 2008-12-19 | 2013-02-05 | Intel Corporation | Pseudo dual-port SRAM and a shared memory switch using multiple memory banks and a sideband memory |

| US8036061B2 (en) * | 2009-02-13 | 2011-10-11 | Apple Inc. | Integrated circuit with multiported memory supercell and data path switching circuitry |

| US9489326B1 (en) * | 2009-03-09 | 2016-11-08 | Cypress Semiconductor Corporation | Multi-port integrated circuit devices and methods |

| US8423710B1 (en) | 2009-03-23 | 2013-04-16 | Marvell International Ltd. | Sequential writes to flash memory |

| US8213236B1 (en) | 2009-04-21 | 2012-07-03 | Marvell International Ltd. | Flash memory |

| WO2011063832A1 (en) * | 2009-11-25 | 2011-06-03 | Telefonaktiebolaget L M Ericsson (Publ) | Addressable fifo |

| US8688922B1 (en) | 2010-03-11 | 2014-04-01 | Marvell International Ltd | Hardware-supported memory management |

| US8315081B2 (en) * | 2010-03-22 | 2012-11-20 | Qualcomm Incorporated | Memory cell that includes multiple non-volatile memories |

| US8756394B1 (en) | 2010-07-07 | 2014-06-17 | Marvell International Ltd. | Multi-dimension memory timing tuner |

| TWI452465B (zh) * | 2010-08-19 | 2014-09-11 | Zeroplus Technology Co Ltd | Method of arranging and processing the electronic measuring device and its tandem parallel data |

| US9158541B2 (en) * | 2010-11-03 | 2015-10-13 | Apple Inc. | Register renamer that handles multiple register sizes aliased to the same storage locations |

| US20130027416A1 (en) * | 2011-07-25 | 2013-01-31 | Karthikeyan Vaithianathan | Gather method and apparatus for media processing accelerators |

| JP2014067241A (ja) * | 2012-09-26 | 2014-04-17 | Fujitsu Semiconductor Ltd | 半導体記憶装置及び電子装置 |

| US9304693B1 (en) | 2012-12-17 | 2016-04-05 | Marvell International Ltd. | System and method for writing data to a data storage structure |

| US9019832B2 (en) * | 2013-03-14 | 2015-04-28 | Mediatek Inc. | Network switching system and method for processing packet switching in network switching system |

| CN110299157B (zh) * | 2013-11-11 | 2023-04-28 | 拉姆伯斯公司 | 使用标准控制器部件的大容量存储系统 |

| US9720036B2 (en) * | 2014-08-18 | 2017-08-01 | Duke University | Signal tracing using on-chip memory for in-system post-fabrication debug |

| WO2016176593A1 (en) * | 2015-04-30 | 2016-11-03 | Microchip Technology Incorporated | Central processing unit with enhanced instruction set |

| CN106201431B (zh) | 2015-05-28 | 2020-03-24 | 东芝存储器株式会社 | 半导体装置 |

| US10360952B2 (en) | 2016-12-20 | 2019-07-23 | Omnivision Technologies, Inc. | Multiport memory architecture for simultaneous transfer |

| US10922258B2 (en) * | 2017-12-22 | 2021-02-16 | Alibaba Group Holding Limited | Centralized-distributed mixed organization of shared memory for neural network processing |

| US10990517B1 (en) * | 2019-01-28 | 2021-04-27 | Xilinx, Inc. | Configurable overlay on wide memory channels for efficient memory access |

| JP2020166346A (ja) * | 2019-03-28 | 2020-10-08 | ラピスセミコンダクタ株式会社 | 半導体記憶装置 |

| US11360905B2 (en) * | 2019-05-24 | 2022-06-14 | Texas Instmments Incorporated | Write merging on stores with different privilege levels |

| EP4089543A4 (en) * | 2020-02-13 | 2023-01-04 | Huawei Technologies Co., Ltd. | MEMORY, NETWORK DEVICE, AND DATA ACCESS METHOD |

| CN112540642B (zh) * | 2020-11-27 | 2023-09-05 | 山东云海国创云计算装备产业创新中心有限公司 | 一种多时钟域处理方法、装置、设备和介质 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5307343A (en) * | 1989-11-30 | 1994-04-26 | Italtel Societa Italiana Telecommunicazioni S.P.A. | Basic element for the connection network of a fast packet switching node |

| US5440523A (en) * | 1993-08-19 | 1995-08-08 | Multimedia Communications, Inc. | Multiple-port shared memory interface and associated method |

| CN1209213A (zh) * | 1995-12-29 | 1999-02-24 | 穆凯什·查特 | 高性能通用多端口内部高速缓存的动态随机存取存储器系统、体系结构和方法 |

| US6081528A (en) * | 1995-06-01 | 2000-06-27 | Micron Technology, Inc. | Shared buffer memory architecture for asynchronous transfer mode switching and multiplexing technology |

| US6167491A (en) * | 1994-09-01 | 2000-12-26 | Mcalpine; Gary L. | High performance digital electronic system architecture and memory circuit therefor |

Family Cites Families (154)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4611299A (en) * | 1982-02-22 | 1986-09-09 | Hitachi, Ltd. | Monolithic storage device |

| JP2566911B2 (ja) * | 1985-08-20 | 1996-12-25 | 日本電気株式会社 | デユアルポ−トメモリ |

| EP0269803A3 (de) * | 1986-12-05 | 1990-03-07 | ANT Nachrichtentechnik GmbH | Schaltungsanordnung zur Vermittlung von PCM-Kanälen |

| JPH01162294A (ja) * | 1987-12-18 | 1989-06-26 | Sharp Corp | ダイナミックram |

| JPH01204293A (ja) * | 1988-02-09 | 1989-08-16 | Nec Corp | 半導体メモリ |

| US5844842A (en) | 1989-02-06 | 1998-12-01 | Hitachi, Ltd. | Nonvolatile semiconductor memory device |

| JP3035995B2 (ja) * | 1990-06-29 | 2000-04-24 | ソニー株式会社 | マルチポートメモリ |

| US5260905A (en) * | 1990-09-03 | 1993-11-09 | Matsushita Electric Industrial Co., Ltd. | Multi-port memory |

| JP3021810B2 (ja) | 1990-09-03 | 2000-03-15 | 松下電器産業株式会社 | マルチポートメモリ |

| JPH04289584A (ja) * | 1991-03-19 | 1992-10-14 | Fujitsu Ltd | 半導体メモリ装置 |

| JPH0546527A (ja) * | 1991-08-14 | 1993-02-26 | Matsushita Electric Ind Co Ltd | デユアルポートメモリ回路 |

| JP3088516B2 (ja) | 1991-10-18 | 2000-09-18 | 株式会社マック・サイエンス | X線回折測定方法及び装置 |

| JPH05282870A (ja) * | 1992-03-31 | 1993-10-29 | Fujitsu Ltd | デュアルポート型ランダム・アクセス・メモリ |

| US5732041A (en) * | 1993-08-19 | 1998-03-24 | Mmc Networks, Inc. | Memory interface unit, shared memory switch system and associated method |

| US5701517A (en) | 1994-12-22 | 1997-12-23 | Cirrus Logic, Inc. | Pipelined alignment shifter and method for universal bit field boundary alignment |

| US5680595A (en) * | 1995-06-07 | 1997-10-21 | Micron Technology, Inc. | Programmable data port clocking system for clocking a plurality of data ports with a plurality of clocking signals in an asynchronous transfer mode system |

| US5742602A (en) * | 1995-07-12 | 1998-04-21 | Compaq Computer Corporation | Adaptive repeater system |

| US5680425A (en) * | 1995-09-28 | 1997-10-21 | Micron Technology, Inc. | Self-queuing serial output port |

| US5875470A (en) * | 1995-09-28 | 1999-02-23 | International Business Machines Corporation | Multi-port multiple-simultaneous-access DRAM chip |

| JP3648304B2 (ja) | 1995-11-17 | 2005-05-18 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US5799211A (en) * | 1996-03-22 | 1998-08-25 | General Electric Company | Shift register having latch cell operable in serial-in/parallel-out and parallel-in/serial-out modes in response to a sequence of commands for controlling appropriate switches |

| US5815447A (en) * | 1996-08-08 | 1998-09-29 | Micron Technology, Inc. | Memory device having complete row redundancy |

| US6487207B1 (en) * | 1997-02-26 | 2002-11-26 | Micron Technology, Inc. | Shared buffer memory architecture for asynchronous transfer mode switching and multiplexing technology |

| US5996051A (en) * | 1997-04-14 | 1999-11-30 | Advanced Micro Devices, Inc. | Communication system which in a first mode supports concurrent memory acceses of a partitioned memory array and in a second mode supports non-concurrent memory accesses to the entire memory array |

| DE69841486D1 (de) * | 1997-05-31 | 2010-03-25 | Texas Instruments Inc | Verbesserte Paketvermittlung |

| US6000006A (en) | 1997-08-25 | 1999-12-07 | Bit Microsystems, Inc. | Unified re-map and cache-index table with dual write-counters for wear-leveling of non-volatile flash RAM mass storage |

| US6034957A (en) * | 1997-08-29 | 2000-03-07 | Extreme Networks, Inc. | Sliced comparison engine architecture and method for a LAN switch |

| US6295299B1 (en) * | 1997-08-29 | 2001-09-25 | Extreme Networks, Inc. | Data path architecture for a LAN switch |

| US6446173B1 (en) * | 1997-09-17 | 2002-09-03 | Sony Corporation | Memory controller in a multi-port bridge for a local area network |

| US6199145B1 (en) * | 1998-02-27 | 2001-03-06 | Intel Corporation | Configurable page closing method and apparatus for multi-port host bridges |

| US6115389A (en) * | 1998-04-17 | 2000-09-05 | Advanced Micro Devices, Inc. | Auto-negotiation for multiple ports using shared logic |

| US6216205B1 (en) * | 1998-05-21 | 2001-04-10 | Integrated Device Technology, Inc. | Methods of controlling memory buffers having tri-port cache arrays therein |

| US6067301A (en) * | 1998-05-29 | 2000-05-23 | Cabletron Systems, Inc. | Method and apparatus for forwarding packets from a plurality of contending queues to an output |

| FR2779843A1 (fr) | 1998-06-16 | 1999-12-17 | Busless Computers | Composant memoire multiport serie et application a un ordinateur |

| US6735773B1 (en) | 1998-06-27 | 2004-05-11 | Intel Corporation | Method and apparatus for issuing commands to a network processor configured to provide a plurality of APIs |

| US6230191B1 (en) * | 1998-10-05 | 2001-05-08 | Alcatel Internetworking (Pe), Inc. | Method and apparatus for regulating the amount of buffer memory requested by a port in a multi-port switching device with shared buffer memory |

| US6876702B1 (en) | 1998-10-13 | 2005-04-05 | Stmicroelectronics Asia Pacific (Pte) Ltd. | Motion vector detection with local motion estimator |

| US6468160B2 (en) | 1999-04-08 | 2002-10-22 | Nintendo Of America, Inc. | Security system for video game system with hard disk drive and internet access capability |

| JP4439033B2 (ja) * | 1999-04-16 | 2010-03-24 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| US6618390B1 (en) * | 1999-05-21 | 2003-09-09 | Advanced Micro Devices, Inc. | Method and apparatus for maintaining randomly accessible free buffer information for a network switch |

| US6785272B1 (en) * | 1999-06-24 | 2004-08-31 | Allied Telesyn, Inc. | Intelligent stacked switching system |

| US6535963B1 (en) * | 1999-06-30 | 2003-03-18 | Cisco Technology, Inc. | Memory apparatus and method for multicast devices |

| US6804239B1 (en) | 1999-08-17 | 2004-10-12 | Mindspeed Technologies, Inc. | Integrated circuit that processes communication packets with co-processor circuitry to correlate a packet stream with context information |

| US6535939B1 (en) | 1999-11-09 | 2003-03-18 | International Business Machines Corporation | Dynamically configurable memory bus and scalability ports via hardware monitored bus utilizations |

| US6539467B1 (en) | 1999-11-15 | 2003-03-25 | Texas Instruments Incorporated | Microprocessor with non-aligned memory access |

| US6539488B1 (en) * | 1999-11-30 | 2003-03-25 | Agere Systems Inc. | System with a plurality of media access control circuits with a shared memory for storing data and synchronizing data from a clock domain to a host clock domain |

| TW451193B (en) | 1999-11-30 | 2001-08-21 | Via Tech Inc | A method to determine the timing setting value of dynamic random access memory |

| US6615324B1 (en) | 2000-01-07 | 2003-09-02 | Cygnal Integrated Products, Inc. | Embedded microprocessor multi-level security system in flash memory |

| DE60133595T2 (de) | 2000-01-07 | 2009-04-30 | Nippon Telegraph And Telephone Corp. | Funktionsrekonfigurierbare Halbleitervorrichtung und integrierte Schaltung zum Konfigurieren der Halbleitervorrichtung |

| US6741589B1 (en) * | 2000-01-24 | 2004-05-25 | Advanced Micro Devices, Inc. | Apparatus and method for storing data segments in a multiple network switch system using a memory pool |

| US6732184B1 (en) * | 2000-01-31 | 2004-05-04 | Advanced Micro Devices, Inc. | Address table overflow management in a network switch |

| US6714643B1 (en) | 2000-02-24 | 2004-03-30 | Siemens Information & Communication Networks, Inc. | System and method for implementing wait time estimation in automatic call distribution queues |

| CA2411361A1 (en) * | 2000-06-02 | 2001-12-13 | Inrange Technologies Corporation | Fibre channel address adaptor having data buffer extension and address mapping in a fibre channel switch |

| JP4997663B2 (ja) * | 2000-12-27 | 2012-08-08 | 富士通セミコンダクター株式会社 | マルチポートメモリおよびその制御方法 |

| US6957304B2 (en) | 2000-12-20 | 2005-10-18 | Intel Corporation | Runahead allocation protection (RAP) |

| US7099325B1 (en) * | 2001-05-10 | 2006-08-29 | Advanced Micro Devices, Inc. | Alternately accessed parallel lookup tables for locating information in a packet switched network |

| JP2002366421A (ja) | 2001-06-07 | 2002-12-20 | Oki Electric Ind Co Ltd | メモリ制御回路とメモリ制御方法 |

| JP4812192B2 (ja) * | 2001-07-27 | 2011-11-09 | パナソニック株式会社 | フラッシュメモリ装置、及び、それに記憶されたデータのマージ方法 |

| US6898652B2 (en) | 2001-08-22 | 2005-05-24 | General Atomics | Wireless device attachment and detachment system, apparatus and method |

| US6717847B2 (en) | 2001-09-17 | 2004-04-06 | Sandisk Corporation | Selective operation of a multi-state non-volatile memory system in a binary mode |

| US7340495B2 (en) | 2001-10-29 | 2008-03-04 | Intel Corporation | Superior misaligned memory load and copy using merge hardware |

| US6870770B2 (en) | 2001-12-12 | 2005-03-22 | Micron Technology, Inc. | Method and architecture to calibrate read operations in synchronous flash memory |

| WO2003067787A2 (en) | 2002-02-08 | 2003-08-14 | I/O Integrity, Inc. | Redirecting local disk traffic to network attached storage |

| JP4061094B2 (ja) | 2002-03-15 | 2008-03-12 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 音声認識装置、その音声認識方法及びプログラム |

| US6567304B1 (en) | 2002-05-09 | 2003-05-20 | Matrix Semiconductor, Inc | Memory device and method for reliably reading multi-bit data from a write-many memory cell |

| JP4170682B2 (ja) | 2002-06-18 | 2008-10-22 | 株式会社東芝 | 不揮発性半導体メモリ装置 |

| WO2004015563A1 (en) | 2002-08-09 | 2004-02-19 | Intel Corporation | Multimedia coprocessor control mechanism including alignment or broadcast instructions |

| JP2006500679A (ja) | 2002-09-24 | 2006-01-05 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | Usb接続のためのインタフェース集積回路デバイス |

| US7395366B1 (en) | 2002-09-27 | 2008-07-01 | Cypress Semiconductor Corp. | System, method, and apparatus for connecting USB peripherals at extended distances from a host computer |

| US7233984B2 (en) | 2002-11-12 | 2007-06-19 | Microsoft Corporation | Light weight file I/O over system area networks |

| US7225301B2 (en) * | 2002-11-22 | 2007-05-29 | Quicksilver Technologies | External memory controller node |

| US7822955B2 (en) | 2003-01-21 | 2010-10-26 | Arm Limited | Data processing apparatus and method for utilizing endianess independent data values |

| US7571287B2 (en) * | 2003-03-13 | 2009-08-04 | Marvell World Trade Ltd. | Multiport memory architecture, devices and systems including the same, and methods of using the same |

| US7337290B2 (en) | 2003-04-03 | 2008-02-26 | Oracle International Corporation | Deadlock resolution through lock requeing |

| US7076631B2 (en) | 2003-04-14 | 2006-07-11 | Adtran, Inc. | Mechanism for on-the-fly handling of unaligned memory accesses |

| US7136953B1 (en) | 2003-05-07 | 2006-11-14 | Nvidia Corporation | Apparatus, system, and method for bus link width optimization |

| US7469311B1 (en) | 2003-05-07 | 2008-12-23 | Nvidia Corporation | Asymmetrical bus |

| JP3649227B2 (ja) | 2003-06-06 | 2005-05-18 | セイコーエプソン株式会社 | データ転送制御装置、電子機器及びデータ転送制御方法 |

| US7003597B2 (en) | 2003-07-09 | 2006-02-21 | International Business Machines Corporation | Dynamic reallocation of data stored in buffers based on packet size |

| EP1508853A1 (en) | 2003-08-19 | 2005-02-23 | STMicroelectronics Limited | Computer system and method for loading non-aligned words |

| US7649539B2 (en) | 2004-03-10 | 2010-01-19 | Microsoft Corporation | Image formats for video capture, processing and display |

| US7606960B2 (en) | 2004-03-26 | 2009-10-20 | Intel Corporation | Apparatus for adjusting a clock frequency of a variable speed bus |

| GB2414573B (en) | 2004-05-26 | 2007-08-08 | Advanced Risc Mach Ltd | Control of access to a shared resource in a data processing apparatus |

| US20060031628A1 (en) | 2004-06-03 | 2006-02-09 | Suman Sharma | Buffer management in a network device without SRAM |

| US7197591B2 (en) | 2004-06-30 | 2007-03-27 | Intel Corporation | Dynamic lane, voltage and frequency adjustment for serial interconnect |

| US7480808B2 (en) | 2004-07-16 | 2009-01-20 | Ati Technologies Ulc | Method and apparatus for managing power consumption relating to a differential serial communication link |

| TW200513865A (en) | 2004-09-17 | 2005-04-16 | Via Tech Inc | USB control circuit with function of switching between host mode and controlled mode and its operating method |

| US20060075144A1 (en) | 2004-09-24 | 2006-04-06 | International Business Machines Corp. | Remote access to a local hard drive |

| US7734874B2 (en) | 2004-10-06 | 2010-06-08 | Thomson Licensing | Method and system for caching data using future access request information |

| US7038950B1 (en) | 2004-11-05 | 2006-05-02 | Spansion Llc | Multi bit program algorithm |

| US20060106962A1 (en) | 2004-11-17 | 2006-05-18 | Woodbridge Nancy G | USB On-The-Go implementation |

| US7313019B2 (en) | 2004-12-21 | 2007-12-25 | Intel Corporation | Step voltage generation |

| JP4746326B2 (ja) | 2005-01-13 | 2011-08-10 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| TWI280710B (en) | 2005-03-04 | 2007-05-01 | Behavior Tech Computer Corp | Two-way electrical device with USB interface |

| US8452929B2 (en) | 2005-04-21 | 2013-05-28 | Violin Memory Inc. | Method and system for storage of data in non-volatile media |

| US20060288188A1 (en) | 2005-06-17 | 2006-12-21 | Intel Corporation | Translating a string operation |

| JP4688584B2 (ja) | 2005-06-21 | 2011-05-25 | 株式会社日立製作所 | ストレージ装置 |

| US7738451B2 (en) | 2005-07-01 | 2010-06-15 | Faraday Technology Corp. | Method and device for flexible buffering in networking system |

| US7624221B1 (en) | 2005-08-01 | 2009-11-24 | Nvidia Corporation | Control device for data stream optimizations in a link interface |

| US7606641B2 (en) | 2005-08-04 | 2009-10-20 | The Boeing Company | Fuel consumption data tracking/collection and aircraft/route optimization |

| US7539809B2 (en) | 2005-08-19 | 2009-05-26 | Dell Products L.P. | System and method for dynamic adjustment of an information handling systems graphics bus |

| US7583600B1 (en) | 2005-09-07 | 2009-09-01 | Sun Microsytems, Inc. | Schedule prediction for data link layer packets |

| US7447824B2 (en) | 2005-10-26 | 2008-11-04 | Hewlett-Packard Development Company, L.P. | Dynamic lane management system and method |

| US7427990B2 (en) | 2006-01-30 | 2008-09-23 | Ati Technologies, Inc. | Data replacement method and circuit for motion prediction cache |

| US7685322B2 (en) | 2006-02-28 | 2010-03-23 | Microsoft Corporation | Port number emulation for wireless USB connections |

| US8111264B2 (en) | 2006-03-30 | 2012-02-07 | Ati Technologies Ulc | Method of and system for non-uniform image enhancement |

| US7630253B2 (en) | 2006-04-05 | 2009-12-08 | Spansion Llc | Flash memory programming and verification with reduced leakage current |

| US7467253B2 (en) | 2006-04-13 | 2008-12-16 | Sandisk Corporation | Cycle count storage systems |

| KR100725932B1 (ko) | 2006-05-02 | 2007-06-11 | 삼성전자주식회사 | 무선 유에스비 장치의 동작 방법 및 이를 이용한 무선유에스비 장치 |

| US20070271609A1 (en) | 2006-05-18 | 2007-11-22 | Phison Electronics Corp. | Security system of flash memory and method thereof |

| US7480757B2 (en) | 2006-05-24 | 2009-01-20 | International Business Machines Corporation | Method for dynamically allocating lanes to a plurality of PCI Express connectors |

| US7478188B2 (en) | 2006-06-02 | 2009-01-13 | Hewlett-Packard Development Company, L.P. | System and method for connecting a WUSB device to multiple WUSB hosts |

| US8250316B2 (en) | 2006-06-06 | 2012-08-21 | Seagate Technology Llc | Write caching random data and sequential data simultaneously |

| US7391650B2 (en) | 2006-06-16 | 2008-06-24 | Sandisk Corporation | Method for operating non-volatile memory using temperature compensation of voltages of unselected word lines and select gates |

| US7536490B2 (en) | 2006-07-20 | 2009-05-19 | Via Technologies, Inc. | Method for link bandwidth management |

| US7496707B2 (en) | 2006-08-22 | 2009-02-24 | International Business Machines Corporation | Dynamically scalable queues for performance driven PCI express memory traffic |

| KR100866130B1 (ko) | 2006-09-29 | 2008-10-31 | 주식회사 하이닉스반도체 | 반도체 메모리 장치의 데이터 정렬 회로 및 데이터 정렬방법 |

| KR100830580B1 (ko) | 2006-10-20 | 2008-05-21 | 삼성전자주식회사 | 플래시 메모리 장치를 포함한 메모리 시스템의 데이터 복원방법 |

| KR100826500B1 (ko) | 2006-10-23 | 2008-05-02 | 삼성전자주식회사 | 비휘발성 반도체 메모리 장치 및 상기 비휘발성 반도체메모리 장치의 데이터 복구 방법 |

| US7941590B2 (en) | 2006-11-06 | 2011-05-10 | Marvell World Trade Ltd. | Adaptive read and write systems and methods for memory cells |

| US7966457B2 (en) | 2006-12-15 | 2011-06-21 | Microchip Technology Incorporated | Configurable cache for a microprocessor |

| US8117475B2 (en) | 2006-12-15 | 2012-02-14 | Microchip Technology Incorporated | Direct memory access controller |

| CN102681957B (zh) | 2006-12-22 | 2015-04-29 | 高通股份有限公司 | 增强的无线 usb 协议和集线器 |

| KR100799018B1 (ko) | 2006-12-27 | 2008-01-28 | 주식회사 하이닉스반도체 | 불휘발성 메모리 소자 및 자기 보상 방법 |

| KR100720708B1 (ko) | 2007-01-26 | 2007-05-21 | 주식회사 유비콘테크놀로지 | 무선 usb drd 시스템 |

| KR100817087B1 (ko) | 2007-02-13 | 2008-03-27 | 삼성전자주식회사 | 플래시 메모리를 구비하는 스토리지 장치에서의 버퍼 캐시운용 방법 |

| JP4911508B2 (ja) | 2007-03-30 | 2012-04-04 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置及びその動作方法 |

| US7865660B2 (en) | 2007-04-16 | 2011-01-04 | Montage Technology Group Ltd. | Calibration of read/write memory access via advanced memory buffer |

| US7660925B2 (en) | 2007-04-17 | 2010-02-09 | International Business Machines Corporation | Balancing PCI-express bandwidth |

| US20080265838A1 (en) | 2007-04-24 | 2008-10-30 | Saurabh Garg | Battery charging using a USB-ID pin of a USB interface |

| KR100826654B1 (ko) | 2007-04-24 | 2008-05-06 | 주식회사 하이닉스반도체 | 플래시 메모리소자의 동작방법 및 이를 위한 제어회로 |

| US20080294951A1 (en) | 2007-05-01 | 2008-11-27 | Ahmad Mustafa S | Methods and devices for testing computer memory |

| US7577036B2 (en) | 2007-05-02 | 2009-08-18 | Micron Technology, Inc. | Non-volatile multilevel memory cells with data read of reference cells |

| US8214571B2 (en) | 2007-06-25 | 2012-07-03 | Arssov Paul Plamen | Simple serial interface—method of communication and information exchange, and electronic devices based on this method |

| US8234425B1 (en) | 2007-06-27 | 2012-07-31 | Marvell International Ltd. | Arbiter module |

| US7949817B1 (en) | 2007-07-31 | 2011-05-24 | Marvell International Ltd. | Adaptive bus profiler |

| US8127104B1 (en) | 2007-08-06 | 2012-02-28 | Marvell International Ltd. | Alignment matrix memory copy |

| US9131213B2 (en) | 2007-09-07 | 2015-09-08 | Evertz Microsystems Ltd. | Method of generating a blockiness indicator for a video signal |

| US20090113166A1 (en) | 2007-10-31 | 2009-04-30 | Agere Systems Inc. | Hashing method for nand flash memory |

| US7924628B2 (en) | 2007-11-14 | 2011-04-12 | Spansion Israel Ltd | Operation of a non-volatile memory array |

| US7814276B2 (en) | 2007-11-20 | 2010-10-12 | Solid State System Co., Ltd. | Data cache architecture and cache algorithm used therein |

| US7945825B2 (en) | 2007-11-25 | 2011-05-17 | Spansion Isreal, Ltd | Recovery while programming non-volatile memory (NVM) |

| US7613045B2 (en) | 2007-11-26 | 2009-11-03 | Sandisk Il, Ltd. | Operation sequence and commands for measuring threshold voltage distribution in memory |

| JP4282733B1 (ja) | 2007-12-13 | 2009-06-24 | 株式会社東芝 | ディスク記憶装置及びデータ書き込み方法 |

| US8084987B2 (en) | 2008-02-13 | 2011-12-27 | Active-Semi, Inc. | USB port with smart power management |

| US7903462B1 (en) | 2008-04-04 | 2011-03-08 | Link A Media Devices Corporation | E/P durability by using a sub-range of a full programming range |

| US8131915B1 (en) | 2008-04-11 | 2012-03-06 | Marvell Intentional Ltd. | Modifying or overwriting data stored in flash memory |

| US8683085B1 (en) | 2008-05-06 | 2014-03-25 | Marvell International Ltd. | USB interface configurable for host or device mode |

| US8135890B2 (en) | 2008-05-28 | 2012-03-13 | Rambus Inc. | Selective switching of a memory bus |

| US8213228B1 (en) | 2008-11-06 | 2012-07-03 | Marvell International Ltd. | Flash memory read performance |

| KR20100090439A (ko) | 2009-02-06 | 2010-08-16 | 주식회사 하이닉스반도체 | 불휘발성 메모리 장치의 독출 방법 및 이를 구현하는 불휘발성 메모리 장치 |

| US8423710B1 (en) | 2009-03-23 | 2013-04-16 | Marvell International Ltd. | Sequential writes to flash memory |

| US8213236B1 (en) | 2009-04-21 | 2012-07-03 | Marvell International Ltd. | Flash memory |

| US8688922B1 (en) | 2010-03-11 | 2014-04-01 | Marvell International Ltd | Hardware-supported memory management |

-

2003

- 2003-11-05 US US10/702,744 patent/US7571287B2/en active Active

-

2004

- 2004-03-11 TW TW93106492A patent/TWI263228B/zh not_active IP Right Cessation

- 2004-03-12 JP JP2004071574A patent/JP2004288355A/ja active Pending

- 2004-03-12 CN CNB2004100084978A patent/CN100456734C/zh not_active Expired - Lifetime

- 2004-03-12 EP EP04006012A patent/EP1457993B1/en not_active Expired - Lifetime

- 2004-03-12 DE DE200460028981 patent/DE602004028981D1/de not_active Expired - Lifetime

-

2008

- 2008-10-21 JP JP2008270813A patent/JP5107204B2/ja not_active Expired - Lifetime

-

2009

- 2009-06-29 US US12/494,076 patent/US8335878B2/en not_active Expired - Fee Related

-

2012

- 2012-12-17 US US13/716,481 patent/US8688877B1/en not_active Expired - Lifetime

-

2014

- 2014-03-31 US US14/230,555 patent/US9105319B2/en not_active Expired - Lifetime

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5307343A (en) * | 1989-11-30 | 1994-04-26 | Italtel Societa Italiana Telecommunicazioni S.P.A. | Basic element for the connection network of a fast packet switching node |

| US5440523A (en) * | 1993-08-19 | 1995-08-08 | Multimedia Communications, Inc. | Multiple-port shared memory interface and associated method |

| US6167491A (en) * | 1994-09-01 | 2000-12-26 | Mcalpine; Gary L. | High performance digital electronic system architecture and memory circuit therefor |

| US6081528A (en) * | 1995-06-01 | 2000-06-27 | Micron Technology, Inc. | Shared buffer memory architecture for asynchronous transfer mode switching and multiplexing technology |

| CN1209213A (zh) * | 1995-12-29 | 1999-02-24 | 穆凯什·查特 | 高性能通用多端口内部高速缓存的动态随机存取存储器系统、体系结构和方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI453443B (zh) * | 2012-12-28 | 2014-09-21 | Zeroplus Technology Co Ltd | Data analysis method |

| TWI472783B (zh) * | 2012-12-28 | 2015-02-11 | Zeroplus Technology Co Ltd | Data capture and detection method |

| TWI453444B (zh) * | 2013-01-04 | 2014-09-21 | Zeroplus Technology Co Ltd | Displays the method of the detection process |

Also Published As

| Publication number | Publication date |

|---|---|

| US8688877B1 (en) | 2014-04-01 |

| EP1457993A2 (en) | 2004-09-15 |

| JP2004288355A (ja) | 2004-10-14 |

| CN1531275A (zh) | 2004-09-22 |

| US9105319B2 (en) | 2015-08-11 |

| US7571287B2 (en) | 2009-08-04 |

| US20040205305A1 (en) | 2004-10-14 |

| US20140215164A1 (en) | 2014-07-31 |

| EP1457993B1 (en) | 2010-09-08 |

| DE602004028981D1 (de) | 2010-10-21 |

| US8335878B2 (en) | 2012-12-18 |

| US20090307437A1 (en) | 2009-12-10 |

| JP5107204B2 (ja) | 2012-12-26 |

| TWI263228B (en) | 2006-10-01 |

| TW200428406A (en) | 2004-12-16 |

| EP1457993A3 (en) | 2005-07-27 |

| JP2009064548A (ja) | 2009-03-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100456734C (zh) | 使用多端口存储器的体系结构、装置、系统及其使用方法 | |

| CN105117360B (zh) | 基于fpga的接口信号重映射方法 | |

| US7047375B2 (en) | Memory system and method for two step memory write operations | |

| US7680968B2 (en) | Switch/network adapter port incorporating shared memory resources selectively accessible by a direct execution logic element and one or more dense logic devices in a fully buffered dual in-line memory module format (FB-DIMM) | |

| CN103597460B (zh) | 用于利用存储命令的系统和方法 | |

| US6216205B1 (en) | Methods of controlling memory buffers having tri-port cache arrays therein | |

| CN101149963B (zh) | 多端口存储设备 | |

| CN101611452B (zh) | 互连系统中的偏斜管理 | |

| US5999478A (en) | Highly integrated tri-port memory buffers having fast fall-through capability and methods of operating same | |

| US5982700A (en) | Buffer memory arrays having nonlinear columns for providing parallel data access capability and methods of operating same | |

| US20050125590A1 (en) | PCI express switch | |

| CN101568904A (zh) | 非易失性存储器的成扇形展开的高速系统体系结构和输入/输出电路 | |

| CN101694512A (zh) | 测试电路和片上系统 | |

| CN100407109C (zh) | 数据转换电路和半导体装置 | |

| CN101031860B (zh) | 用于分配时钟信号的装置、系统和方法 | |

| EP0673137A1 (en) | Virtual interconnection memory | |

| EP0695988A2 (en) | A first-in first-out memory | |

| CN108459876A (zh) | 用于缩减面积的控制寄存器电路的方法与装置 | |

| CN101034585B (zh) | 一种无需灵敏放大器的sram体系电路 | |

| Elrabaa | A new FIFO design enabling fully-synchronous on-chip data communication network | |

| US6480031B2 (en) | High speed latch/register | |

| CN206282270U (zh) | 一种处理器 | |

| CN103594110A (zh) | 替代双端口静态存储器的存储器结构 | |

| US8164973B2 (en) | Storage apparatus and method of controlling storage apparatus | |

| JP3108421B2 (ja) | メモリアクセス装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C56 | Change in the name or address of the patentee | ||

| CP02 | Change in the address of a patent holder |

Address after: Babado J San Michaele Patentee after: MARVELL WORLD TRADE Ltd. Address before: Barbados Bermuda Patentee before: MARVELL WORLD TRADE Ltd. |

|

| TR01 | Transfer of patent right |

Effective date of registration: 20201214 Address after: Shin ha Po Patentee after: Marvell Asia Pte. Ltd. Address before: Grand Cayman Islands Patentee before: Kavim International Inc. Effective date of registration: 20201214 Address after: Grand Cayman Islands Patentee after: Kavim International Inc. Address before: Hamilton, Bermuda Patentee before: Marvell International Ltd. Effective date of registration: 20201214 Address after: Hamilton, Bermuda Patentee after: Marvell International Ltd. Address before: Babado J San Michaele Patentee before: MARVELL WORLD TRADE Ltd. |

|

| TR01 | Transfer of patent right | ||

| CX01 | Expiry of patent term |

Granted publication date: 20090128 |

|

| CX01 | Expiry of patent term |